MVME135, MVME135-1 MVME135A, MVME136, AND MVME136A 32-Bit Microcomputers User's Manual

MVME135/L3 SEPTEMBER 1987

# MVME135/135-1/MVME136 CUSTOMER LETTER

This letter is directed to customers using MVME135Bug, Revision 1.0, and to software designers writing code for the MC68681 DUART on the MVME135. The purpose is to clarify an error in the data sheet on the MC68681 which defines the reset condition of the Interrupt Status Register (ISR) as \$00. Two potential situations exist that can cause this register to not be read as \$00 after a power-up or reset condition.

The first case involves bits two and six of the ISR, the Delta Break bits for each serial port. Due to an anomaly in the chip circuitry, either of these bits may be set after a power-up condition. This anomaly has been verified by both vendors of the chip (Motorola and Signetics) and should not be considered fatal faults in the part, as their power-up conditions will not affect normal operation of these bits. The proper initialization sequence for these bits is to write all port control registers to desired values, then issue a "Reset Channel x Break Change Interrupt" command for each channel. At this point, the state of these bits will be valid and further operations of these bits will be accurate.

The second case involves bit three of the ISR, the Counter/Timer Ready bit. This bit may be set after a power-up or reset condition and prior to being read by software in the ISR. The reason for this is that the MC68681 powers up in the free running timer mode, and the timer may reach the end of a count-down sequence, setting the Counter/Timer Ready bit at any time after release of the reset line. This status condition is normal to the device and will not affect normal operation of the part. The proper initialization sequence for the MC68681 timer is to initialize the desired timer modes, then perform a read of the Stop Counter command address to clear ISR bit three. At this point, further setting of the bit will be due to normal counter/timer operation and may be considered valid.

Due to operation of the ISR in the MC68681 as described above, intermittent failures of the MVME135Bug, Revision 1.0, confidence test at test \$AO may be observed. These failures are related to the ISR not containing \$00 after reset. As described, this is not a fatal error, and the MVME135Bug will operate normally after exiting the confidence test. Future releases of the MVME135Bug will correct for the operation of the MC68681 and will not demonstrate this error.

We apologize for any inconvenience this may cause.

|                     |     |                                                 |           |                     |                          | NO POSTAGE<br>NECESSARY<br>IF MAILED<br>IN THE<br>UNITED STATES |

|---------------------|-----|-------------------------------------------------|-----------|---------------------|--------------------------|-----------------------------------------------------------------|

| B<br>FIRST CLASS M  |     | S REPLY MAIL<br>IT NO. 2565 PHOENIX,            | , ARIZONA |                     |                          |                                                                 |

| Compute<br>2900 Sou | TOR | COLA INC<br>Microcomputer Divis<br>Way<br>-9741 | ion, DW16 | 4<br><mark>.</mark> | الملطاساة                |                                                                 |

| Otherod □Fair □Poor |     | air the product                                 |           | ephone Number       | n. Please use this form. | ENTS                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | the manual are most useful (tables, figures, appendixes, index, etc.)? |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Is the information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n easy to understand? 🗆 Yes 🗆 No If you checked no, please explain:    |

| Is the information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n easy to find?   Yes   No If you checked no, please explain:          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                        |

| THE RESERVE AND ADDRESS OF THE PARTY OF THE |                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | acy: □ Excellent □ Very Good □ Good □ Fair □ Poor                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | d technical or typographical errors, please list them here.            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                        |

| If you have found                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | d technical or typographical errors, please list them here.            |

| If you have found                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | d technical or typographical errors, please list them here.            |

| If you have found                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | d technical or typographical errors, please list them here.            |

| If you have found                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | d technical or typographical errors, please list them here.            |

| If you have found                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | d technical or typographical errors, please list them here.            |

# SAFETY SUMMARY SAFETY DEPENDS ON YOU

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Motorola Inc. assumes no liability for the customer's failure to comply with these requirements. The safety precautions listed below represent warnings of certain dangers of which we are aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### GROUND THE INSTRUMENT.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. The equipment is supplied with a three-conductor ac power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter, with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

#### DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE.

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

#### KEEP AWAY FROM LIVE CIRCUITS.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified maintenance personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### DO NOT SERVICE OR ADJUST ALONE.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### USE CAUTION WHEN EXPOSING OR HANDLING THE CRT.

Breakage of the Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, avoid rough handling or jarring of the equipment. Handling of the CRT should be done only by qualified maintenance personnel using approved safety mask and gloves.

#### DO NOT SUBSTITUTE PARTS OR MODIFY EQUIPMENT.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the equipment. Contact Motorola Field Service Division for service and repair to ensure that safety features are maintained.

#### DANGEROUS PROCEDURE WARNINGS.

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

#### WARNING

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

#### PREFACE

This manual provides general information, hardware preparation, installation instructions, functional description, and support information for the MVME135/MVME136 Monoboard Series of 32-Bit Microcomputers.

This manual is intended for anyone who wants to design OEM systems, supply additional capability to an existing compatible system or in a lab environment for experimental purposes.

A basic knowledge of computers and digital logic is assumed.

To use this manual, you should be faimilar with the publications listed in the *Related Documentation* paragraph in Chapter 1 of this manual.

The computer programs stored in the read only memories of this device contain material copyrighted by Motorola Inc., first published 1988, and may be used only under a license such as the License for Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

## WARNING

THIS EQUIPMENT GENERATES, USES, AND CAN RADIATE RADIO ENERGY AND IF NOT INSTALLED AND USED IN ACCORDANCE WITH THE INSTRUCTIONS MANUAL, MAY INTERFERENCE TO RADIO COMMUNICATIONS. IT HAS BEEN TESTED AND FOUND TO COMPLY WITH THE LIMITS FOR A CLASS A COMPUTING DEVICE PURSUANT TO SUBPART J OF PART 15 OF FCC RULES, WHICH ARE DESIGNED TO PROVIDE REASONABLE PROTECTION AGAINST SUCH INTERFERENCE WHEN OPERATED IN A COMMERCIAL ENVIRONMENT. OPERATION OF THIS EQUIPMENT IN A RESIDENTIAL AREA IS LIKELY TO CAUSE INTERFERENCE IN WHICH CASE THE USER, AT HIS OWN EXPENSE, WILL BE REQUIRED TO TAKE WHATEVER MEASURES NECESSARY TO CORRECT THE INTERFERENCE.

VMEmodule, VSBbus, and 135bug are trademarks of Motorola Inc.

Second Edition

Copyright 1989 by Motorola Inc.

First Edition April 1987

MVME135, MVME135-1, MVME135A,

MVME136, AND MVME136A

32-BIT MICROCOMPUTERS

USER'S MANUAL

(MVME135/D2)

The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, Motorola reserves the right to make changes to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights or the rights of others.

# TABLE OF CONTENTS

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| CHAPTER 1 - GENERAL INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                            |

| 1.1 INTRODUCTION 1.2 FEATURES 1.3 SPECIFICATIONS 1.3.1 Cooling Requirements 1.3.2 FCC Compliance 1.4 GENERAL DESCRIPTION 1.5 MVME135/136 CONFIGURATIONS 1.6 REFERENCE DOCUMENTATION 1.7 MANUAL TERMINOLOGY                                                                                                                                                                                                                                                                                            | 1-1<br>1-2<br>1-4<br>1-4<br>1-5<br>1-5<br>1-6                                              |

| CHAPTER 2 - HARDWARE PREPARATION AND INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                            |

| 2.1 INTRODUCTION 2.2 UNPACKING INSTRUCTIONS 2.3 HARDWARE PREPARATION 2.3.1 VMEbus Lock For VSBbus (J1) 2.3.2 Bus Grant/Request Level Select (J2) 2.3.3 Factory Test Jumper (J5) 2.3.4 RAM Acknowledge Mode (J6) 2.3.5 ROM Size Select (J7) 2.3.6 DRAM Address Multiplex Select (J8) 2.3.7 Local/VMEbus Timeout Disable (J11) 2.3.8 DRAM Cycle Start Mode Select (J12) 2.3.9 External Timer Select (J13,J14) 2.4 SERIAL PORT CABLING 2.4.1 DB-9 To DB-25 Cable Connection 2.5 VME CHASSIS INSTALLATION | 2-1<br>2-1<br>2-4<br>2-4<br>2-6<br>2-6<br>2-7<br>2-8<br>2-8<br>2-9<br>2-10<br>2-11<br>2-12 |

| CHAPTER 3 - OPERATING INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                            |

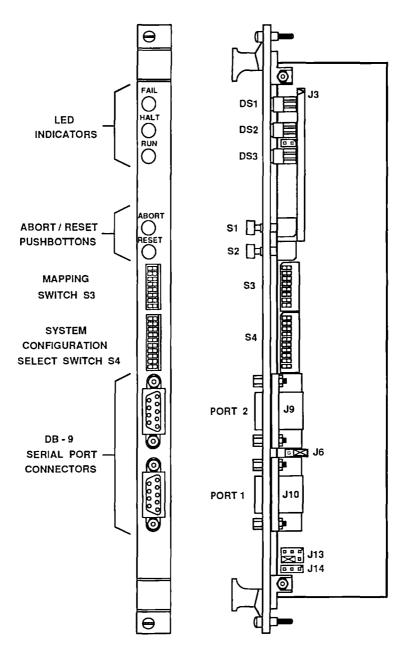

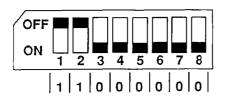

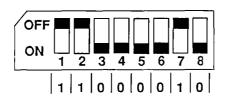

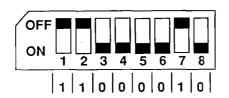

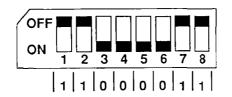

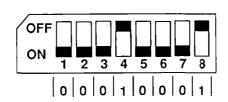

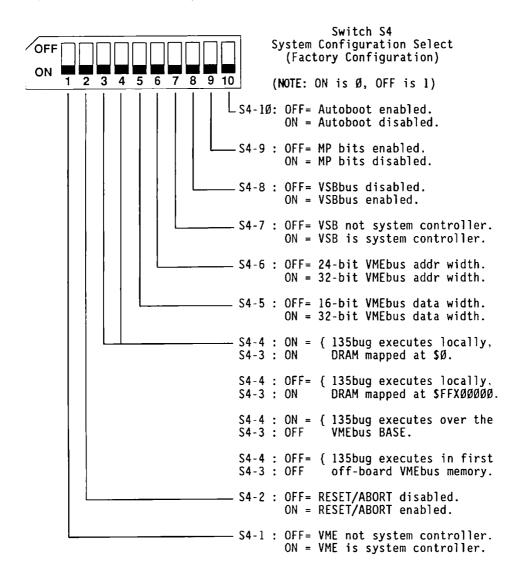

| 3.1 INTRODUCTION 3.2 FRONT PANEL 3.2.1 LED Indicators 3.2.2 ABORT Switch (S1) 3.2.3 RESET Switch (S2) 3.2.4 Mapping Switch (S3) 3.2.5 System Configuration Switch (S4) 3.3 MEMORY MAP AND MAP DECODER 3.3.1 MVME135/135-1/135A Main Memory Map 3.3.2 MVME136/135A Main Memory Map                                                                                                                                                                                                                     | 3-1<br>3-1<br>3-1<br>3-1<br>3-3<br>3-10<br>3-11<br>3-12<br>3-13                            |

# TABLE OF CONTENTS (cont.)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 4 - FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                 |

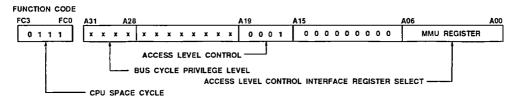

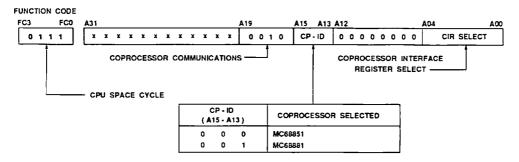

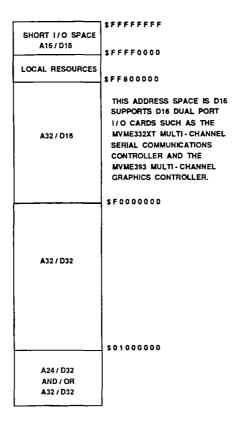

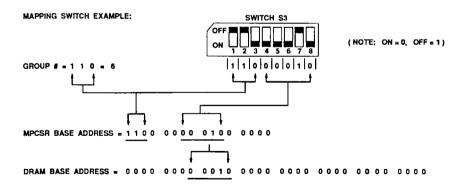

| 4.1 INTRODUCTION 4.2 GENERAL DESCRIPTION 4.2.1 Data Bus Structure 4.2.2 Memory Map 4.2.3 Timing 4.2.4 MWMEI35/135-1/136 DRAM Cycle Times 4.2.5 MVMEI35A/136A DRAM Cycle Times 4.2.6 ROM/PROM/EPROM/EPROM Cycle Times 4.2.7 VMEBUS Cycle Times 4.2.8 VMEBUS Arbitration Time 4.3 MC68829 MPU 4.4 MC68881 FPCP 4.5 MC68851 PMMU 4.6 DEBUG MONITOR FIRMWARE 4.7 VME SUBSYSTEM BUS (VSBbus) 4.8 DYNAMIC RAM 4.9 FUNCTION CODE ASSIGNMENTS 4.10 MVMEI35/136 USE OF CPU SPACE 4.10.1 MC68851 Breakpoint Support 4.10.2 MC68851 Breakpoint Support 4.10.2 MC68851 Breakpoint Architecture 4.10.4 MC68851 Breakpoint Architecture 4.10.5 Access Level Control 4.10.5 Access Level Control 4.10.6 Copprocessor Communications 4.11 INTERRUPT HANDLER 4.12 ONBOARD ROM/PROM/EPROM 4.13 DUAL SERIAL PORTS 4.14 MVME135/136 TIMER 4.15 LOCAL CONTROL/STATUS REGISTERS 4.15.1 Status Register Format And Functions 4.16 MULTIPROCESSOR CONTROL/STATUS REGISTERS 4.15.1 Status Register Format And Functions 4.16 MULTIPROCESSOR CONTROL/STATUS REGISTERS 4.15.1 VSBBUS CONTROL/STATUS REGISTERS 4.16.1 Base Address Selection 4.17 VSBBUS CONTROL/STATUS REGISTER 4.17.1 VSBBUS CONTROL/STATUS REGISTER 4.17.1 VSBBUS CONTROL/STATUS REGISTER 4.17.1 VSBBUS CONTROL/STATUS REGISTER 4.18 CONFIGURING A VME SUBSYSTEM BUS  CHAPTER 5 - SUPPORT INFORMATION | 4-1<br>4-1<br>4-1<br>4-1<br>4-1<br>4-4<br>4-5<br>4-6<br>4-6<br>4-7<br>4-7<br>4-1<br>4-1<br>4-1<br>4-1<br>4-1<br>4-1<br>4-1<br>4-1<br>4-1<br>4-1 |

| 5.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-1                                                                                                                                             |

| 5.2 INTERCONNECTION SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-1<br>5-1                                                                                                                                      |

# TABLE OF CONTENTS (cont.)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 5.2.2 Connector P2 Interconnect Signals 5.2.3 Connector J3 Interconnect Signals 5.2.4 Connector J4 Interconnect Signals 5.2.5 Connector J9 Interconnect Signals 5.2.6 Connector J1Ø Interconnect Signals 5.3 PARTS LIST 5.4 SCHEMATIC DIAGRAMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-6<br>5-13<br>5-15<br>5-19<br>5-20<br>5-21<br>5-43                                            |

| APPENDIX A - MVME135/135-1/136 PAL2 SOURCE LISTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A-1                                                                                            |

| APPENDIX B - MVME135A/136A PAL2 SOURCE LISTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | B-1                                                                                            |

| APPENDIX C - MVME135/136 LOCAL MEMORY MAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C - 1                                                                                          |

| LIST OF ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                |

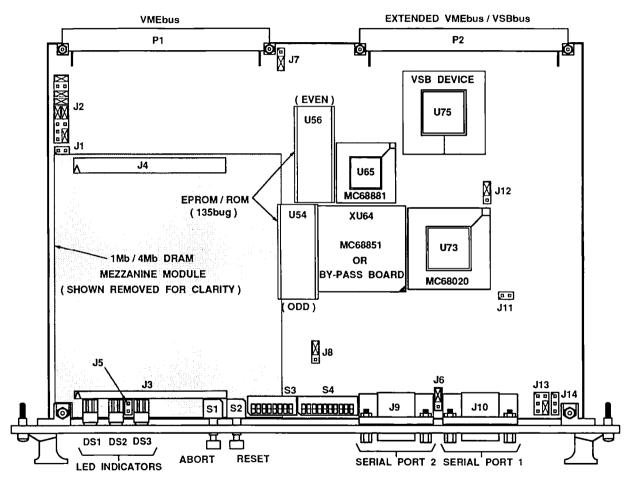

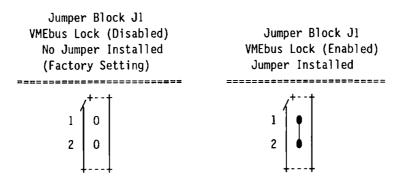

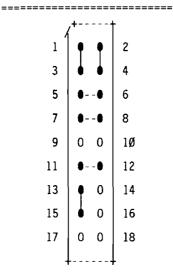

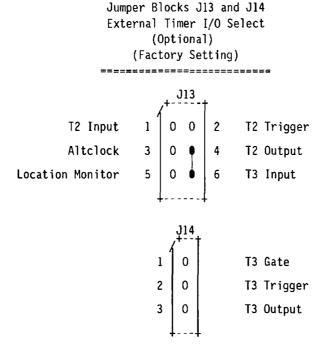

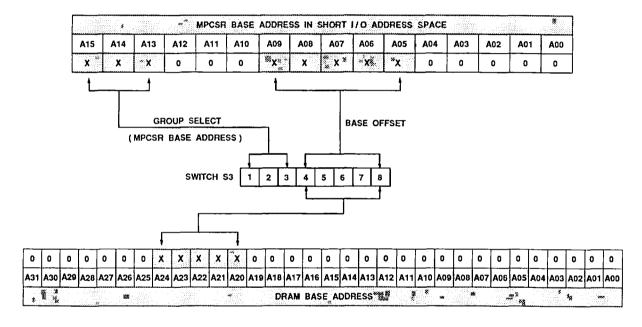

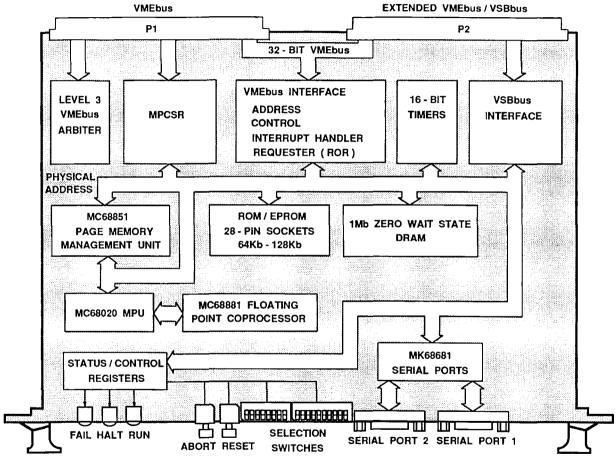

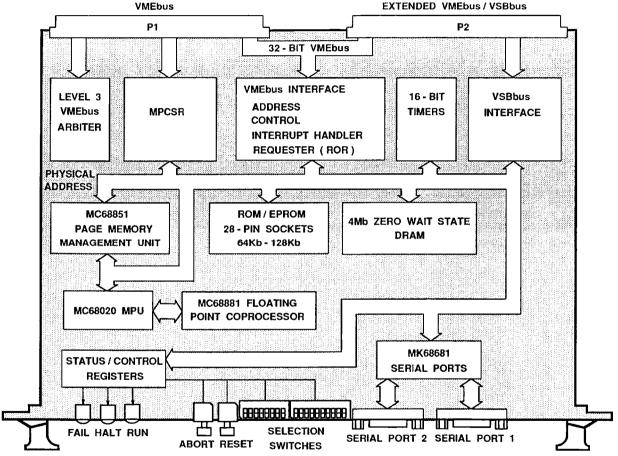

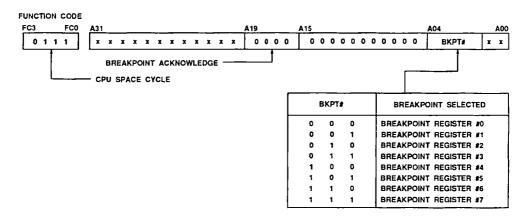

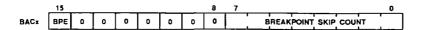

| FIGURE 2-1. Jumper, Connector, And Switch Location Diagram  FIGURE 3-1. MVME135/136 Front Panel  FIGURE 3-2. MVME135/135-1/136 Slave Access Addressing  FIGURE 3-3. MVME135A/136A Slave Access Addressing  FIGURE 4-1. MVME135/135-1/136 Block Diagram  FIGURE 4-2. MVME135A/136A Block Diagram  FIGURE 4-3. CPU Space Type Field Encoding  FIGURE 4-4. Breakpoint Acknowledge Cycle Address Encoding  FIGURE 4-5. Breakpoint Registers  FIGURE 4-6. Breakpoint Acknowledge Data Register Format  FIGURE 4-7. Breakpoint Acknowledge Control Register Format  FIGURE 4-8. ALC Interface Logical Address Bus Encoding  FIGURE 4-9. Coprocessor Interface Address Bus Encoding  FIGURE 4-10. Serial Port Interconnections  FIGURE 4-11. D16/D32 Default Data Segmentation  FIGURE 4-12. MPCSR And DRAM Address Mapping  FIGURE 5-1. MVME135/136 Parts Location Diagram  FIGURE 5-3. 4Mb DRAM Mezzanine Board Parts Location Diagram  FIGURE 5-4. MVME135/136 By-Pass Board Parts Location Diagram  FIGURE 5-5. MVME135/136 Schematic Diagram  FIGURE 5-5. MVMF135/136 Schematic Diagram  FIGURE 5-5. MVMF135/136 Schematic Diagram  FIGURE 5-5. MVMF135/136 Schematic Diagram | 2-2<br>3-4<br>3-7<br>4-2<br>4-3<br>4-9<br>4-11<br>4-11<br>4-12<br>4-13<br>5-33<br>5-42<br>5-45 |

# TABLE OF CONTENTS (cont.)

|                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| FIGURE 5-6.<br>FIGURE 5-7.<br>FIGURE 5-8.                                                                                                                            | 1Mb DRAM Mezzanine Schematic Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-113                                                                                                 |

|                                                                                                                                                                      | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

| TABLE 1-1. TABLE 1-2. TABLE 2-1. TABLE 3-1. TABLE 3-2. TABLE 3-3. TABLE 3-4. TABLE 4-1. TABLE 4-2. TABLE 4-2. TABLE 4-5. TABLE 4-6. TABLE 4-7. TABLE 4-8. TABLE 5-1. | MVME135/136 Specifications MVME135/136 Configurations Jumper Block Placements MVME135/136 Front Panel LED Status Function Code Assignments MVME135/135-1/136 Main Memory Map MVME135/136 Timing Function Code Assignments ALC Interface Registers Map MC68851 Coprocessor Interface Register Map MC68881 Coprocessor Interface Register Map Interrupt Handler Priority Assignments Multiprocessor Control/Status Registers Mapping On The VMEbus Connector P1 Interconnect Signals | 1-2<br>1-6<br>2-3<br>3-3<br>3-11<br>3-12<br>3-13<br>4-3<br>4-9<br>4-13<br>4-15<br>4-28<br>4-30<br>5-1 |

| TABLE 5-2. TABLE 5-3. TABLE 5-4. TABLE 5-5. TABLE 5-6. TABLE 5-7. TABLE 5-8. TABLE 5-9. TABLE 5-10                                                                   | Connector P2 Interconnect Signals Connector J3 Interconnect Signals Connector J4 Interconnect Signals Connector J9 Interconnect Signals Connector J1Ø Interconnect Signals MVME135/136 Parts List IMb DRAM Mezzanine Board Parts List 4Mb DRAM Mezzanine Board Parts List PMMU By-Pass Board Parts List                                                                                                                                                                            | 5-6<br>5-13<br>5-15<br>5-19<br>5-20<br>5-21<br>5-37<br>5-39<br>5-41                                   |

#### CHAPTER 1 - GENERAL INFORMATION

#### 1.1 INTRODUCTION

This user's manual provides general information, preparation and installation instructions, operating instructions, functional description, and support information for the MVME135/MVME136 series of 32-bit microcomputers (refer to section 1.5 for the different module configurations). Unless otherwise specified, these microcomputers are referred to as the MVME135/136 throughout the contents of this user's manual.

#### 1.2 FEATURES

The features of the MVME135/136 include:

- MC68Ø2Ø Virtual Memory Microprocessor with 32-bit address and data at 16.67 MHz or 2Ø.ØØ MHz.

- 1Mb of shared local DRAM with no wait cycles, 32-bit wide; accessible from the VMEbus with optional parity (MVME135, MVME135-1, and MVME136 versions only).

- 4Mb of shared local DRAM with one wait cycle, 32-bit wide; accessible from the VMEbus with optional parity (MVME135A version only).

- 4Mb of shared local DRAM with two wait cycles, 32-bit wide; accessible from the VMEbus with optional parity (MVME136A version only). Parity does not add any additional wait cycles for this version.

- On-board socket for MC68881 Floating Point Coprocessor (FPCP) at 16.67 MHz or 20.00 MHz.

- On-board socket for MC68851 Demand Paged Memory Management Unit (PMMU) at 16.67 MHz (MVME136 and MVME136A versions only).

- Multi-master VME Subsystem Bus (VSBbus) interface; 32-bit secondary bus support.

- VMEbus interface; 32-bit address and data.

- VMEbus Interrupt Handler.

- Z8Ø36A Programmable Timer Module.

- Periodic tick interrupt (level 6).

- Watchdog reset (momentary local reset, local reset and hold, or a system level reset may be software selected).

- VSBbus can eliminate "software holes" in VMEbus memory map caused by exception tables and stacks.

- Single level system controller capability (level is jumper selectable).

- High level multiprocessor control and status registers used for inter-processor signaling and communication.

- Round Robin requesting provides fairness of VMEbus mastership for systems with multiple MVME135/136s (software selectable).

- Two front panel RS-232C serial ports with level translators; eliminating the need for a transition board between the MVME135/136 and a terminal or modem.

- Two on-board ROM sockets for a capacity of 128Kb (configured for Industry Standard JEDEC 28-pin ROM/PROM/EPROM devices; user provided).

#### 1.3 SPECIFICATIONS

General specifications for the MVME135/136 are provided in the following table. Sections 1.2.2 and 1.2.3 detail cooling requirements and FCC compliance, respectively.

TABLE 1-1. MVME135/136 SPECIFICATIONS

| Characteristic                                      | Specification                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microprocessor                                      | MC68Ø2Ø 32-bit microprocessor                                                                                                                                                                                                                                                 |

| Clock signal:<br>MVME135/135A/136/136A              | 16.67 MHz CPU clock frequency                                                                                                                                                                                                                                                 |

| MVME135-1                                           | 20.00 MHz CPU clock frequency                                                                                                                                                                                                                                                 |

| Power requirements: MVME135/135-1/135A MVME136/136A | +5 Vdc, 6.75 A maximum (5.6 A typical) +12 Vdc, 5Ø mA maximum (1Ø mA typical) -12 Vdc, 9Ø mA maximum (3Ø mA typical) +5 Vdc, 7.ØØ A maximum (5.8 A typical) +12 Vdc, 5Ø mA maximum (1Ø mA typical) -12 Vdc, 9Ø mA maximum (3Ø mA typical)                                     |

|                                                     | NOTE: Backplane Connectors The P2 backplane is not only necessary for 32-bit operation but is also used to connect +5 V to the MVME135/136 module for current distribution. The module draws 5.6 A under typical operation and should not be operated without a P2 backplane. |

TABLE 1-1. MVME135/136 SPECIFICATIONS (cont.)

| IABLE 1-1. M                         | VME135/136 SPECIFICATIONS (CONT.)                                                                                                                           |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Characteristic                       | Specification                                                                                                                                               |  |

| Addressing:                          |                                                                                                                                                             |  |

| System Size<br>(Total on-/off-board) | 32-bits = 4 gigabytes linear address space                                                                                                                  |  |

| ROM/EPROM                            | Two EPROM/ROM sockets for 16Kb or 32Kb devices using +5 Vdc only (JEDEC standard 28-pin devices; user supplied).                                            |  |

| Serial I/O ports                     | Two multi-protocol serial communications channels with RS-232C interface (connection made via two DB-9 connectors from the front panel).                    |  |

| Timer                                | A Z8Ø36A programmable timer module with three independent $16\text{-bit}$ timers.                                                                           |  |

| Interrupts                           | Any seven possible VMEbus interrupts can be received by the MVME135/136. VSBbus has interrupt capability. as do most on-board devices.                      |  |

| On-board memory                      |                                                                                                                                                             |  |

| MVME135/135-1                        | $1\mbox{Mb},$ Ø wait state without parity and $1$ wait state with parity.                                                                                   |  |

| MVME136                              | 1Mb, I wait state without parity and 2 wait states with parity. The MC68851 Paged Memory Management Unit (PMMU) adds I wait state to local memory accesses. |  |

| MVME135A                             | 4Mb, 1 wait state with or without parity.                                                                                                                   |  |

| MVME136A                             | 4Mb, 2 wait states with or without parity. The MC68851 Paged Memory Management Unit (PMMU) adds 1 wait state to local memory accesses.                      |  |

| Temperatures:                        |                                                                                                                                                             |  |

| Operating                            | $\emptyset$ to $5\emptyset$ degrees C (inlet air temperature with forced air cooling)                                                                       |  |

| Storage                              | -4Ø to 85 degrees C                                                                                                                                         |  |

| Relative humidity                    | 5% to 95% (non-condensing)                                                                                                                                  |  |

| Physical size (PCB):                 | (not including the front panel)                                                                                                                             |  |

| Height x width<br>Thickness          | 6.30 inches (16.00 cm) x 9.19 inches (23.34 cm)                                                                                                             |  |

| III (CKHE22                          | Ø.Ø62 inch (Ø.157 cm)                                                                                                                                       |  |

TABLE 1-1. MVME135/136 SPECIFICATIONS (cont.)

| Characteristic    | Specification                        |  |  |

|-------------------|--------------------------------------|--|--|

| Part projections: |                                      |  |  |

| Component side    | Ø.5Ø inch (1.27 cm) maximum          |  |  |

| Solder side       | Ø.Ø67 inch (Ø.17 cm) maximum         |  |  |

| Connectors:       |                                      |  |  |

| VMEbus/VSBbus     | DIN triple row, 96-pin male (P1, P2) |  |  |

| RS-232C           | DB-9, 9-pin female (J9, J1Ø)         |  |  |

# 1.3.1 Cooling Requirements

Motorola VMEmodules are specified, designed, and tested to operate reliably with an incoming air temperature range from Ø degrees C to 5Ø degrees C (32 degrees F to 122 degrees F) with forced air cooling. Temperature qualification is performed in a standard Motorola VMEsystem 1ØØ chassis. Twenty-five watt load boards are inserted in the two card slots, one on each side, adjacent to the board under test to simulate a high power density system configuration. An assembly of three axial fans, rated at 1ØØ CFM per fan, is placed directly under the MVME card cage. The incoming air temperature is measured between the fan assembly and the card cage where the incoming airstream first encounters the board under test. Test software is executed as the module is subjected to ambient temperature variations. Case temperatures of critical, high power density integrated circuits are monitored to ensure component vendors specifications are not exceeded.

While the exact amount of airflow required for cooling depends on the ambient air temperature and the type, number, and location of boards and other heat sources, adequate cooling can usually be achieved with 10 CFM flowing over the module. Less air flow is required to cool the module in environments having lower maximum ambients. Under more favorable thermal conditions it may be possible to operate the module reliably at higher than 50 degrees C with increased air flow. It is important to note that there are several factors, in addition to the rated CFM of the air mover, which determine the actual volume of air flowing over a module.

#### 1.3.2 FCC Compliance

The MVME135/136 module is tested in an FCC-compliant chassis, and meets the requirements for Class A equipment. FCC compliance was achieved under the following conditions:

- 1. Shielded cables on all external I/O ports.

- Cable shields connected to earth ground via metal shell connectors bonded to a conductive module front panel.

- 3. Conductive chassis rails connected to earth ground. This provides the path for connecting shields to earth ground.

- 4. Front panel screws properly tightened.

For minimum RF emissions, it is essential that the conditions above be implemented; failure to do so could compromise the FCC compliance of the equipment containing the modules.

#### 1.4 GENERAL DESCRIPTION

The MVME135/136 is a high performance MC68020 microprocessor-based module implemented on a VME double-high, single-wide form-factor. The MVME135/136 incorporates an MC68020, a 32-bit address and data microprocessor, a high level multiprocessor CSR, and 1Mb or 4Mb of fast DRAM. Other main features provided include a Demand Paged Memory Management Unit (PMMU), a Floating Point Coprocessor (FPCP), and interfaces to the VMEbus and the VSBbus.

The MVME135/136 is designed for those applications which require fast on-board RAM and a secondary bus (VSBbus). The features of the MVME135/136 include high performance and an elegant architecture. The MVME135/136 is especially suited to applications requiring multiple processors where the efficiency of inter-processor communication is important.

The 135bug resident debug package (refer to Motorola publication MVME135BUG) is the firmware package designed for use with the MVME135/136 module. 135bug provides a powerful system debugging tool for VMEmodule systems. This firmware features a one line assembler/disassembler, provisions for upload/download, and disk bootstrap commands. 135bug is available as an EPROM-based resident package which is plugged into IC sockets U54 and U56 on the MVME135/136.

#### 1.5 MVME135/136 CONFIGURATIONS

There are five module configurations available in the MVME135/136 series of 32-bit microcomputers. These configurations are listed in the following table.

| Module<br>Designation | CPU Clock<br>Cycle (MHz) | On-Board<br>Memory | MC68881<br>(FPCP) | MC68851<br>(PMMU) |

|-----------------------|--------------------------|--------------------|-------------------|-------------------|

| MVME135               | 16.67                    | 1Mb                | Yes               | No                |

| MVME135-1             | 20.00                    | 1Mb                | Yes               | No                |

| MVME135A              | 16.67                    | 4Mb                | Yes               | No                |

| MVME136               | 16.67                    | 1Mb                | Yes               | Yes               |