# MVME162 Embedded Controller Installation Guide

(MVME162IG/D2)

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

No part of this material may be reproduced or copied in any tangible medium, or stored in a retrieval system, or transmitted in any form, or by any means, radio, electronic, mechanical, photocopying, recording or facsimile, or otherwise, without the prior written permission of Motorola, Inc.

It is possible that this publication may contain reference to, or information about Motorola products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

# **Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

#### **Preface**

This manual provides a general board level hardware description, hardware preparation and installation instructions, debugger general information, and using the debugger in the MVME162 Embedded Controller. The information contained in this manual applies to the following MVME162 models:

| MVME162-001 | MVME162-010 | MVME162-020 | MVME162-030 | MVME162-040 |

|-------------|-------------|-------------|-------------|-------------|

| MVME162-002 | MVME162-011 | MVME162-021 | MVME162-031 | MVME162-041 |

| MVME162-003 | MVME162-012 | MVME162-022 | MVME162-032 | MVME162-042 |

|             | MVME162-013 | MVME162-023 | MVME162-033 | MVME162-043 |

|             | MVME162-014 | MVME162-026 |             |             |

This manual is intended for anyone who wants to provide OEM systems, supply additional capability to an existing compatible system, or work in a lab environment for experimental purposes.

A basic knowledge of computers and digital logic is assumed.

After using this manual, you may wish to become familiar with the publications listed in the *Related Documentation* section in Chapter 1 of this manual. This installation guide is based on these other documents.

The computer programs stored in the Read Only Memory of this device contain material copyrighted by Motorola Inc., first published 1990, and may be used only under a license such as the License for Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the documentation for this product, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A Computing Device pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user, at the user's own expense, will be required to take whatever measures necessary to correct the interference.

Motorola and the Motorola symbol are registered trademarks of Motorola, Inc.

Delta Series, MC68040, MC68LC040, VMEexec, VMEmodule, and VMEsystem are trademarks of Motorola, Inc.

IndustryPack and IP are trademarks of GreenSpring Computers, Inc.

Timekeeper and Zeropower are trademarks of Thompson Components.

All other products mentioned in this document are trademarks or registered trademarks of their respective holders

© Copyright Motorola 1993, 1994

All Rights Reserved

Printed in the United States of America

August 1994

# Safety Summary Safety Depends On You

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Motorola, Inc. assumes no liability for the customer's failure to comply with these requirements.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. The equipment is supplied with a three-conductor AC power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter, with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

#### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

#### **Keep Away From Live Circuits.**

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified maintenance personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### Do Not Service or Adjust Alone.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### Use Caution When Exposing or Handling the CRT.

Breakage of the Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, avoid rough handling or jarring of the equipment. Handling of the CRT should be done only by qualified maintenance personnel using approved safety mask and gloves.

#### Do Not Substitute Parts or Modify Equipment.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that safety features are maintained.

#### **Dangerous Procedure Warnings.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

# Introduction

This chapter describes the board level hardware features of the MVME162 Embedded Controller. The chapter is organized with a board level overview and features list in this introduction, followed by a more detailed hardware functional description. Front panel switches and indicators are included in the detailed hardware functional description. The chapter closes with some general memory maps.

All programmable registers in the MVME162 that reside in ASICs are covered in the MVME162 Embedded Controller Programmer's Reference Guide.

#### Overview

The MVME162 is based on the MC68040 or MC68LC040 microprocessor. Various versions of the MVME162 have 1 MB, 4 MB, or 8 MB of parity-protected DRAM, 8 KB of SRAM (with battery backup), time of day clock (with battery backup), Ethernet transceiver interface, two serial ports with EIA-232-D or EIA-530 interface, six tick timers, watchdog timer, a PROM socket, 1 MB Flash memory (one or four Flash devices), four IndustryPack (IP) interfaces, SCSI bus interface with DMA, VMEbus controller, and 512 KB of SRAM with battery backup.

The I/O on the MVME162 is connected to the VMEbus P2 connector. The main board is connected through a P2 transition board and cables to the transition boards. The MVME162 supports the transition boards MVME712-12, MVME712-13, MVME712M, MVME712A, MVME712AM, and MVME712B (referred to in this manual as MVME712X, unless separately specified). The MVME712X transition boards provide configuration headers and provide industry standard connectors for the I/O devices.

The I/O connection for the serial ports on the MVME162 is also provided by two DB-25 front panel I/O connectors. The MVME712 series transition boards were designed to support the MVME167 boards, but can be used on the MVME162 by following some special precautions. (Refer to the section on the Serial Communications Interface, later in this chapter, for more information.) These transition boards provide configuration headers, serial port drivers and industry standard connectors for the I/O devices.

The VMEbus interface is provided by an ASIC called the VMEchip2. The VMEchip2 includes two tick timers, a watchdog timer, programmable map decoders for the master and slave interfaces, and a VMEbus to/from local bus DMA controller, a VMEbus to/from local bus non-DMA programmed access interface, a VMEbus interrupter, a VMEbus system controller, a VMEbus interrupt handler, and a VMEbus requester.

Processor-to-VMEbus transfers can be D8, D16, or D32. VMEchip2 DMA transfers to the VMEbus, however, can be D16, D32, D16/BLT, D32/BLT, or D64/MBLT.

The MCchip ASIC provides four tick timers, the interface to the LAN chip, SCSI chip, serial port chip, BBRAM, and the programmable interface for the parity-protected DRAM and/or SRAM mezzanine board.

The IndustryPack Interface Controller (IPIC) ASIC provides control and status information for up to four single size IndustryPacks (IPs) or up to two double size IPs that can be plugged into the MVME162 main module.

#### **Related Documentation**

The MVME162 does not ship with all of the documentation that is available for the product. The MVME162 instead ships with a start-up installation guide (the document you are presently reading) that includes all the information necessary to begin working with these products: installation instructions, jumper configuration information, memory maps, debugger/monitor commands, and any other information needed for start-up of the board. The installation guide is MVME162IG/D for the MVME162.

The following publications are applicable to the MVME162 and may provide additional helpful information. They may be purchased by contacting your local Motorola sales office. Non-Motorola documents may be purchased from the sources listed.

| Document Title                                                | Motorola<br>Publication Number |

|---------------------------------------------------------------|--------------------------------|

| MVME162 Embedded Controller User's Manual                     | MVME162                        |

| MVME162 Embedded Controller Support Information               | SIMVME162                      |

| MVME162Bug Debugging Package User's Manual                    | MVME162BUG                     |

| Debugging Package for Motorola 68K CISC CPUs User's<br>Manual | 68KBUG                         |

| Document Title                                                                                                    | Motorola<br>Publication Number |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Single Board Computers SCSI Software User's Manual                                                                | SBCSCSI                        |

| MVME162 Embedded Controller Programmer's Reference<br>Guide                                                       | MVME162PG                      |

| MVME712M Transition Module and P2 Adapter Board User's Manual                                                     | MVME712M                       |

| MVME712-12, MVME712-13, MVME712A, MVME712AM, and MVME712B Transition Modules and LCP2 Adapter Board User's Manual | MVME712A                       |

| M68040 Microprocessors User's Manual                                                                              | M68040UM                       |

# Notes

The SIMVME162 manual contains the connector interconnect signal information, parts lists, and schematics for the MVME162.

Although not shown in the above list, each Motorola Computer Group manual publication number is suffixed with characters which represent the revision level of the document, such as "/D2" (the second revision of a manual); a supplement bears the same number as a manual but has a suffix such as "/D2A1" (the first supplement to the second edition of the manual).

These manuals may also be ordered in documentation sets as follows:

68-MVME162SET for use with the MVME162.

MVME162/D MVME162BUG/D 68KBUG/D SBCSCSI/D MVME162PG/D SIMVME162/D

To further assist your development effort, Motorola has collected user's manuals for each of the peripheral controllers used on the MVME162 and other boards from the suppliers. This bundle includes manuals and data sheets, including the following:

**68-1X7DS** for use with the MVME162 and 167.

NCR 53C710 SCSI Controller Data Manual and Programmer's Guide Intel i82596 Ethernet Controller User's Manual Cirrus Logic CD2401 Serial Controller User's Manual SGS-Thompson MK48T08 NVRAM/TOD Clock Data Sheet

The following publications are also available from the sources indicated.

Versatile Backplane Bus: VMEbus, ANSI/IEEE Std 1014-1987, The Institute of Electrical and Electronics Engineers, Inc., 345 East 47th Street, New York, NY 10017 (VMEbus Specification). This is also available as *Microprocessor system bus for 1 to 4 byte data, IEC 821 BUS*, Bureau Central de la Commission Electrotechnique Internationale; 3, rue de Varembé, Geneva, Switzerland.

ANSI Small Computer System Interface-2 (SCSI-2), Draft Document X3.131-198X, Revision 10c; Global Engineering Documents, P.O. Box 19539, Irvine, CA 92714.

*IndustryPack Logic Interface Specification*, Revision 1.0; GreenSpring Computers, Inc., 1204 O'Brien Drive, Menlo Park, CA 94025.

Z85230 Serial Communications Controller data sheet; Zilog, Inc., 210 Hacienda Ave., Campbell, California 95008-6609.

82596CA Local Area Network Coprocessor Data Sheet, order number 290218; and 82596 User's Manual, order number 296853; Intel Corporation, Literature Sales, P.O. Box 58130, Santa Clara, CA 95052-8130.

NCR 53C710 SCSI I/O Processor Data Manual, order number NCR53C710DM; and NCR 53C710 SCSI I/O Processor Programmer's Guide, order number NCR53C710PG; NCR Corporation, Microelectronics Products Division, Colorado Springs, CO.

*MK48T08(B) Timekeepe*r <sup>TM</sup> *and 8Kx8 Zeropower* <sup>TM</sup> *RAM* data sheet in *Static RAMs Databook*, order number DBSRAM71; SGS-THOMPSON Microelectronics Group; North & South American Marketing Headquarters, 1000 East Bell Road, Phoenix, AZ 85022-2699.

28F008SA Flash Memory Data Sheet, order number 2904351; Intel Literature Sales, P.O. Box 7641, Mt. Prospect, IL 60056-7641.

*i28F020 Flash Memory Data Sheet*, order number 290245; Intel Literature Sales, P.O. Box 7641, Mt. Prospect, IL 60056-7641.

# Requirements

|       |      | ese boards are designed to conform to the requirements of the following cuments:                                                                                          |  |  |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|       |      | VMEbus Specification (IEEE 1014-87)                                                                                                                                       |  |  |

|       |      | EIA-232-D Serial Interface Specification, EIA                                                                                                                             |  |  |

|       |      | SCSI Specification, ANSI                                                                                                                                                  |  |  |

|       |      | IndustryPack Specification, GreenSpring                                                                                                                                   |  |  |

| Featu | ıres |                                                                                                                                                                           |  |  |

|       |      | 25MHz 32-bit MC68040 or MC68LC040 Microprocessor                                                                                                                          |  |  |

|       |      | 1 MB, 4 MB, or 8 MB of shared DRAM with parity protection                                                                                                                 |  |  |

|       |      | 512 KB of SRAM with battery backup                                                                                                                                        |  |  |

|       |      | One JEDEC standard 32-pin PLCC EPROM socket (EPROMs may be shipped separately from the MVME162)                                                                           |  |  |

|       |      | One Intel 28F008SA 1M x 8 Flash memory device or four Intel 28F020 256K x 8 Flash memory devices (1 MB Flash memory total)                                                |  |  |

|       |      | 8K by 8 Non-Volatile RAM and time of day clock with battery backup                                                                                                        |  |  |

|       |      | Four 32-bit Tick Timers (in the MCchip ASIC) for periodic interrupts                                                                                                      |  |  |

|       |      | Two 32-bit Tick Timers (in the VMEchip2 ASIC) for periodic interrupts                                                                                                     |  |  |

|       |      | Watchdog timer                                                                                                                                                            |  |  |

|       |      | Eight software interrupts (for MVME162 versions that have the VMEchip2)                                                                                                   |  |  |

|       |      | I/O                                                                                                                                                                       |  |  |

|       |      | <ul> <li>Two serial ports (one EIA-232-D DCE; one EIA-232-D or EIA-530<br/>DCE/DTE)</li> </ul>                                                                            |  |  |

|       |      | <ul> <li>Serial port controller (Zilog Z85230)</li> </ul>                                                                                                                 |  |  |

|       |      | <ul> <li>Optional Small Computer Systems Interface (SCSI) bus interface with<br/>32-bit local bus burst Direct Memory Access (DMA) (NCR 53C710<br/>controller)</li> </ul> |  |  |

|       |      | <ul> <li>Optional LAN Ethernet transceiver interface with 32-bit local bus<br/>DMA (Intel 82596CA controller)</li> </ul>                                                  |  |  |

|       |      | <ul> <li>Four MVIP IndustryPack interfaces</li> </ul>                                                                                                                     |  |  |

|       |      | VMEbus interface                                                                                                                                                          |  |  |

|       |      | - VMFbus system controller functions                                                                                                                                      |  |  |

- VMEbus interface to local bus (A24/A32, D8/D16/D32 (D8/D16/D32/D64 BLT) (BLT = Block Transfer)

- Local bus to VMEbus interface (A16/A24/A32, D8/D16/D32)

- VMEbus interrupter

- VMEbus interrupt handler

- Global CSR for interprocessor communications

- DMA for fast local memory VMEbus transfers (A16/A24/A32, D16/D32 (D16/D32/D64 BLT)

- ☐ Switches and Light-Emitting Diodes (LEDs)

- Two pushbutton switches (ABORT and RESET)

- Eight LEDs (FAIL, STAT, RUN, SCON, LAN, FUSE, SCSI, and VME)

## **Specifications**

General specifications for the MVME162 are listed in Table 1-1.

Characteristics **Specifications**  $+5V (\pm 5\%), 3.5 A typical, 4.5 A max.$ Power requirements (with PROM; without IPs)  $+12 \text{ Vdc} (\pm 5\%), 100 \text{ mA (max.)}$ -12 Vdc (± 5%), 100 mA (max.) Operating temperature 0° to 70° C exit air with forced air cooling (see NOTE) Storage temperature -40° to +85° C Relative humidity 5% to 90% (noncondensing) Physical dimensions Double-high VMEboard PC board with mezzanine module only Height 9.187 inches (233.35 mm) Depth 6.299 inches (160.00 mm) Thickness 0.662 inch (16.77 mm) PC board with connectors and front panel Height 10.309 inches (261.85 mm) Depth 7.4 inches (188 mm) Thickness 0.80 inch (20.32 mm)

Table 1-1. MVME162 Specifications

**NOTE**: Refer to the following section on "Special Considerations for Elevated Temperature Operation," and to "Cooling Requirements" in the *MVME162 Embedded Controller User's Manual*.

# **Special Considerations for Elevated Temperature Operation**

The following information is for the user who has an application for the MVME162 which will subject it to high temperature.

The MVME162 uses commercial grade devices. Therefore, it can operate in an environment with ambient air temperature from  $0^{\circ}$  C to  $70^{\circ}$  C. There are many factors that affect the ambient temperature seen by components on the MVME162: inlet air temperature; air flow characteristics; number, types, and locations of IndustryPack (IP) modules; power dissipation of adjacent boards in the system; etc.

A temperature profile was performed for the MVME162-23 in an MVME945 12-slot VME chassis. This board was loaded with one GreenSpring IP-Dual P/T module (position a) and three GreenSpring IP-488 modules (positions b, c, and d). One twenty-five watt load board was installed adjacent to each side of the board under test. The exit air velocity was approximately 200 LFM between the MVME162 and the IP-Dual P/T module. Under these circumstances, a 10° C rise between the inlet and exit air was observed. At 70° C exit air temperature (60° C inlet air), the junction temperatures of devices on the MVME162 were calculated (from the measured case temperatures) and do not exceed 100° C.

For elevated temperature operation, the user must perform similar measurements and calculations to determine what operating margin exists for any specific environment.

The following are some steps that the user can take to help make elevated temperature operation possible:

- 1. Position the MVME162 board in the chassis for maximum airflow over the component side of the board.

- 2. Avoid placing boards with high power dissipation adjacent to the MVME162.

- 3. Use low power IP modules only. The preferred locations for IP modules are position a (J2 and J3) and position d (J18 and J19).

# **Manual Terminology**

Throughout this manual, a convention is used which precedes data and address parameters by a character identifying the numeric format as follows:

| \$ | dollar    | specifies a hexadecimal character |

|----|-----------|-----------------------------------|

| %  | percent   | specifies a binary number         |

| &  | ampersand | specifies a decimal number        |

For example, "12" is the decimal number twelve, and "\$12" is the decimal number eighteen.

Unless otherwise specified, all address references are in hexadecimal.

An asterisk (\*) following the signal name for signals which are *level significant* denotes that the signal is true or valid when the signal is low.

An asterisk (\*) following the signal name for signals which are *edge significant* denotes that the actions initiated by that signal occur on high to low transition.

In this manual, *assertion* and *negation* are used to specify forcing a signal to a particular state. In particular, assertion and assert refer to a signal that is active or *true*; negation and negate indicate a signal that is inactive or *false*. These terms are used independently of the voltage level (high or low) that they represent.

Data and address sizes are defined as follows:

- ☐ A *byte* is eight bits, numbered 0 through 7, with bit 0 being the least significant.

- ☐ A *two-byte* is 16 bits, numbered 0 through 15, with bit 0 being the least significant. For the MVME162 and other CISC modules, this is called a *word*.

- ☐ A *four-byte* is 32 bits, numbered 0 through 31, with bit 0 being the least significant. For the MVME162 and other CISC modules, this is called a *longword*.

The terms *control bit* and *status bit* are used extensively in this document. The term control bit is used to describe a bit in a register that can be set and cleared under software control. The term true is used to indicate that a bit is in the state that enables the function it controls. The term false is used to indicate that the bit is in the state that disables the function it controls. In all tables, the terms 0 and 1 are used to describe the actual value that should be written to the bit, or the value that it yields when read. The term status bit is used to describe a bit in a register that reflects a specific condition. The status bit can be read by software to determine operational or exception conditions.

# **Block Diagram**

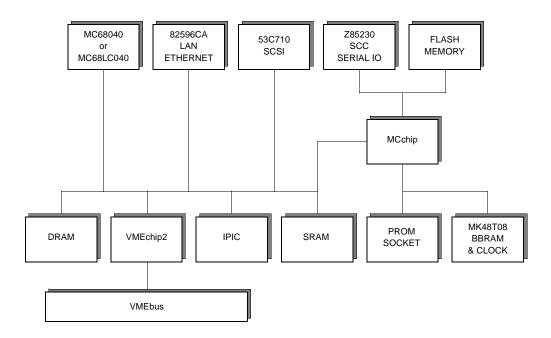

Figure 1-1 is a general block diagram of the MVME162.

bd072 9212

Figure 1-1. MVME162 Block Diagram

# **Functional Description**

This section contains a functional description of the major blocks on the MVME162 Embedded Controller.

#### Front Panel Switches and Indicators

There are switches and LEDs on the front panel of the MVME162. The switches are RESET and ABORT. The RESET switch resets all onboard devices and drives SYSRESET\* if the board is system controller. The RESET switch may be disabled by software.

When enabled by software, the ABORT switch generates an interrupt at a user-programmable level. It is normally used to abort program execution and return to the debugger.

There are eight LEDs on the MVME162 front panel: FAIL, STAT, RUN, SCON, LAN, FUSE (LAN power), SCSI, and VME.

The red FAIL LED (part of DS1) lights when the BRDFAIL signal line is active.

The MC68040 status lines are decoded, on the MVME162, to drive the yellow STAT (status) LED (part of DS1). In this case, a halt condition from the processor lights the LED.

The green RUN LED (part of DS2) lights when the local bus TIP\* signal line is low. This indicates one of the local bus masters is executing a local bus cycle.

The green SCON LED (part of DS2) lights when the VMEchip2 is the VMEbus system controller.

The green LAN LED (part of DS3) lights when the LAN chip is local bus master.

The MVME162 supplies +12Vdc power to the Ethernet transceiver interface through a fuse. The green FUSE (LAN power) LED (part of DS3) lights when power is available to the transceiver interface.

The green SCSI LED (part of DS4) lights when the SCSI chip is local bus master.

The green VME LED (part of DS4) lights when the board is using the VMEbus (VMEbus AS\* is asserted by the VMEchip2) or when the board is accessed by the VMEbus (VMEchip2 is the local bus master).

#### **Data Bus Structure**

The local data bus on the MVME162 is a 32-bit synchronous bus that is based on the MC68040 bus, and which supports burst transfers and snooping. The various local bus master and slave devices use the local bus to communicate. The local bus is arbitrated by priority type arbiter and the priority of the local bus masters from highest to lowest is: 82596CA LAN, 53C710 SCSI, VMEbus, and MPU. Generally speaking, any master can access any slave; however, not all combinations pass the common sense test. Refer to the MVME162 Embedded Controller Programmer's Reference Guide and to the user's guide for each device to determine its port size, data bus connection, and any restrictions that apply when accessing the device.

#### MC68040 or MC68LC040 MPU

The MC68040 or MC68LC040 processor is used on the MVME162. The MC68040 has on-chip instruction and data caches and a floating point processor. The major difference between the two processors is that the MC68040 has a floating point coprocessor. Refer to the *M68040 Microprocessor User's Manual* for more information.

#### MC68xx040 Cache

The MVME162 local bus masters (VMEchip2, MC68xx040, 53C710 SCSI controller, and 82596CA Ethernet controller) have programmable control of the snoop/caching mode. The MVME162 local bus slaves which support MC68xx040 bus snooping are defined in the Local Bus Memory Map table later in this chapter.

# **No-VMEbus-Interface Option**

The MVME162 can be operated as an embedded controller without the VMEbus interface. To support this feature, certain logic in the VMEchip2 has been duplicated in the MCchip. This logic is inhibited in the MCchip if the VMEchip2 is present. The enables for these functions are controlled by software and MCchip hardware initialization.

Contact your local Motorola sales office for ordering information.

# **Memory Options**

The following memory options are used on the different versions of MVME162 boards.

### **DRAM Options**

The MVME162 implementation includes a 1 MB, 4 MB, or 8 MB DRAM option. The DRAM architecture is non-interleaved for 1 MB and 8 MB; while the 4 MB architecture is interleaved. Parity protection can be enabled with interrupts or bus exception when a parity error is detected. DRAM performance is specified in the section on the DRAM Memory Controller in the MCchip Programming Model in the MVME162 Embedded Controller Programmer's Reference Guide.

#### **SRAM Options**

The MVME162 implementation includes a 512 KB SRAM option. SRAM architecture is single non-interleaved. SRAM performance is specified in the section on the SRAM Memory Controller in the MCchip Programming Model in the *MVME162 Embedded Controller Programmer's Reference Guide*. A battery supplies VCC to the SRAMs when main power is removed. The worst case elapsed time for battery protection is 200 days.

The SRAM arrays are not parity protected.

The MVME162 SRAM battery backup function is provided by a Dallas DS1210S. The DS1210S supports primary and secondary power sources. When the main board power fails, the DS1210S selects the source with the highest voltage. If one source should fail, the DS1210S switches to the redundant source. Each time the board is powered, the DS1210S checks power sources and if the voltage of the backup sources is less than two volts, the second memory cycle is blocked. This allows software to provide an early warning to avoid data loss. Because the DS1210S may block the second access, the software should do at least two accesses before relying on the data.

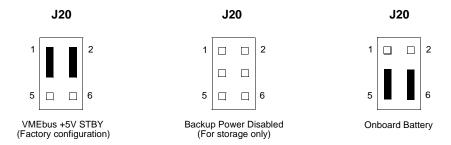

The MVME162 provides jumpers (on J20) that allow either power source of the DS1210S to be connected to the VMEbus +5 V STDBY pin or to one cell of the onboard battery. For example, the primary system backup source may be a battery connected to the VMEbus +5 V STDBY pin and the secondary source may be the onboard battery. If the system source should fail or the board is removed from the chassis, the onboard battery takes over. Refer to Chapter 2 for the jumper configurations.

# Caution

For proper operation of the SRAM, some jumper combination must be installed on the Backup Power Source Select Header (J20). If one of the jumpers is used to select the battery, the battery must be installed on the MVME162. The SRAM may malfunction if inputs to the DS1210S are left unconnected.

The SRAM is controlled by the MCchip, and the access time is programmable. Refer to the MCchip description in the *MVME162 Embedded Controller Programmer's Reference Guide* for more detail.

#### **About the Battery**

The power source for the onboard SRAM is a RAYOVAC FB1225 battery with two BR1225 type lithium cells which is socketed for easy removal and replacement. A small capacitor is provided to allow the battery to be quickly replaced without data loss.

The lifetime of the battery is very dependent on the ambient temperature of the board and the power-on duty cycle. The lithium battery supplied on the MVME162 should provide at least two years of backup time with the board powered off and with an ambient temperature of  $40^{\circ}$  C. If the power-on duty cycle is 50% (the board is powered on half of the time), the battery lifetime is four years. At lower ambient temperatures the backup time is greatly extended and may approach the shelf life of the battery.

When a board is stored, the battery should be disconnected to prolong battery life. This is especially important at high ambient temperatures. The MVME162 is shipped with the batteries disconnected (i.e., with VMEbus +5V standby voltage selected as both primary and secondary power source). If you intend to use the battery as a power source, whether primary or secondary, it is necessary to reconfigure the jumpers on J20 before installing the module. Refer to SRAM Backup Power Source Select Header J20 in Chapter 2 for available jumper configurations.

The power leads from the battery are exposed on the solder side of the board, therefore the board should not be placed on a conductive surface or stored in a conductive bag unless the battery is removed.

☐ Do not short circuit

Lithium batteries incorporate inflammable materials such as lithium and organic solvents. If lithium batteries are mistreated or handled incorrectly, they may burst open and ignite, possible resulting in injury and/or fire. When dealing with lithium batteries, carefully follow the precautions listed below in order to prevent accidents.

| _  | Do not short circuit.                                               |

|----|---------------------------------------------------------------------|

|    | Do not disassemble, deform, or apply excessive pressure.            |

|    | Do not heat or incinerate.                                          |

|    | Do not apply solder directly.                                       |

|    | Do not use different models, or new and old batteries together.     |

|    | Do not charge.                                                      |

|    | Always check proper polarity.                                       |

| То | remove the battery from the module, carefully pull the battery from |

To remove the battery from the module, carefully pull the battery from the socket.

Before installing a new battery, ensure that the battery pins are clean. Note the battery polarity and press the battery into the socket. When the battery is in the socket, no soldering is required.

#### **EPROM** and Flash

The MVME162 implementation includes 1 MB of Flash memory (an 8-Mbit Flash device organized as a 1M X 8, or four 2-Mbit Flash devices organized as 256Kbit x 8). For information on programming Flash, refer to the Intel documents listed in Related Documentation in this chapter. The EPROM location is a standard JEDEC 32-pin PLCC capable of 4 Mbit densities organized as a 512 KB X 8 device. Depending on a jumper setting (GPIO3, pins 9-10 on J22), the MC68xx040 reset code can be fetched from either the Flash (GPIO3 installed) or EPROM (GPIO3 removed).

# **Battery Backed Up RAM and Clock**

The MK48T08 RAM and clock chip is used on the MVME162. This chip provides a time of day clock, oscillator, crystal, power failure detection, memory write protection, 8KB of RAM, and a battery in one 28-pin package. The clock provides seconds, minutes, hours, day, date, month, and year in BCD 24-hour format. Corrections for 28- day, 29-day (leap year), and 30-day months are automatically made. No interrupts are generated by the clock. The MK48T08

is an 8 bit device; however, the interface provided by the MCchip supports 8-bit, 16-bit, and 32-bit accesses to the MK48T08. Refer to the MCchip description in the *MVME162 Embedded Controller Programmer's Reference Guide* and to the MK48T08 data sheet for detailed programming and battery life information.

# VMEbus Interface and VMEchip2

The local bus to VMEbus interface and the VMEbus to local bus interface are provided by the optional VMEchip2. The VMEchip2 can also provide the VMEbus system controller functions. Refer to the VMEchip2 description in the MVME162 Embedded Controller Programmer's Reference Guide for detailed programming information.

Note that the ABORT switch logic in the VMEchip2 is not used. The GPI inputs to the VMEchip2 which are located at \$FFF40088 bits 7-0 are not used. The ABORT switch interrupt is integrated into the MCchip ASIC at location \$FFF42043. The GPI inputs are integrated into the MCchip ASIC at location \$FFF4202C bits 23-16.

#### I/O Interfaces

The MVME162 provides onboard I/O for many system applications. The I/O functions include serial ports, IndustryPack (IP) interfaces, optional LAN Ethernet transceiver interface, and optional SCSI mass storage interface.

#### **Serial Communications Interface**

The MVME162 uses a Zilog Z85230 serial communications controller to implement the two serial communications interfaces. Each interface supports CTS, DCD, RTS, and DTR control signals; as well as the TxD and RxD transmit/receive data signals, and TxC/RxC synchronous clock signals.

The Z85230 supports synchronous (SDLC/HDLC) and asynchronous protocols. The MVME162 hardware supports asynchronous serial baud rates of 110b/s to 38.4Kb/s.

The Z85230 supplies an interrupt vector during interrupt acknowledge cycles. The vector is modified based upon the interrupt source within the Z85230. Interrupt request levels are programmed via the MCchip. Refer to the Z85230 data sheet listed in this chapter, and to the MCchip Programming Model in the MVME162 Embedded Controller Programmer's Reference Guide, for information.

#### **MVME162 Serial Port 1**

The A port of the Z85230 is interfaced as DCE (data circuit-terminating equipment) with the EIA-232-D interface and is routed to:

- ☐ The DB-25 connector marked SERIAL PORT 1/CONSOLE on the front panel of the **MVME162**. SERIAL PORT 1/CONSOLE is an EIA-232-D DCE port.

- NOTE: This port can be connected to the TX and RX clocks which may be present on the DB-25 connector. These connections are made via jumper header J11 on the MVME162 board. (The TxC and RxC clock lines are not available on the MVME712X transition modules.)

- One of the following output connectors on the MVME712X transition module:

**MVME712M**: The DB-25 connector marked SERIAL PORT 2 on the front panel. SERIAL PORT 2 can be configured as an EIA-232-D DTE or DCE port, via jumper headers J16 and J17.

**MVME712A or MVME712-12**: The DB-9 connector marked SERIAL PORT 2 on the front panel. SERIAL PORT 2 is hardwired as an EIA-232-D DTE port.

MVME712AM or MVME712-13: The DB-9 connector marked SERIAL PORT 2 *OR* the RJ-11 jack on the front panel. SERIAL PORT 2 is hardwired as EIA-232-D DTE; the RJ-11 jack utilizes the built-in modem. Setting the jumper headers J16 and J17 on the MVME712AM/-13 configures the output as EIA-232-D DTE at SERIAL PORT 2 or as a modem at the RJ-11 jack.

#### **MVME162 Serial Port 2**

The configuration of the B port of the Z85230 is determined via a Serial Interface Module (SIM) which is installed at connector J10 on the MVME162 board. There are four SIMs available:

SIM05 -- DTE with EIA-232-D interface

SIM06 -- DCE with EIA-232-D interface

SIM07 -- DTE with EIA-530 interface

SIM08 -- DCE with EIA-530 interface

Port B is routed, via the SIM, to:

☐ The DB-25 connector marked SERIAL PORT 2 on the front panel of the MVME162. SERIAL PORT 2 will be an EIA-232-D DCE or DTE port, or an EIA-530 DCE or DTE port, depending upon which SIM is installed.

NOTE: This port can be connected to the TX and RX clocks which may be present on the DB-25 connector. These connections are made via jumper header J12 on the MVME162 board. (The TxC and RxC clock lines are available at the MVME712M SERIAL PORT 4 via header J15, but are not available on the other MVME712X transition modules.)

One of the following output connectors on the MVME712X transition module:

**MVME712M**: The DB-25 connector marked SERIAL PORT 4 on the front panel. SERIAL PORT 4 can be configured as an EIA-232-D DTE or DCE port, via the jumper headers J18 and J19 on the MVME712M.

**MVME712A**, **AM**, -**12**, **or** -**13**: The DB-9 connector marked SERIAL PORT 4 on the front panel. SERIAL PORT 4 is hard-wired as an EIA-232-D DTE port.

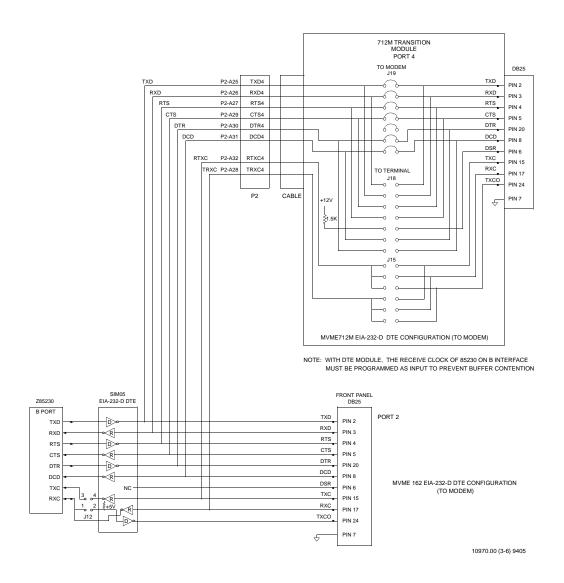

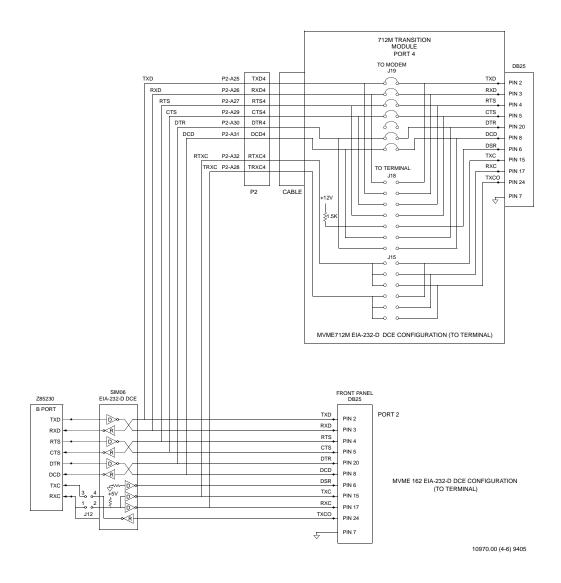

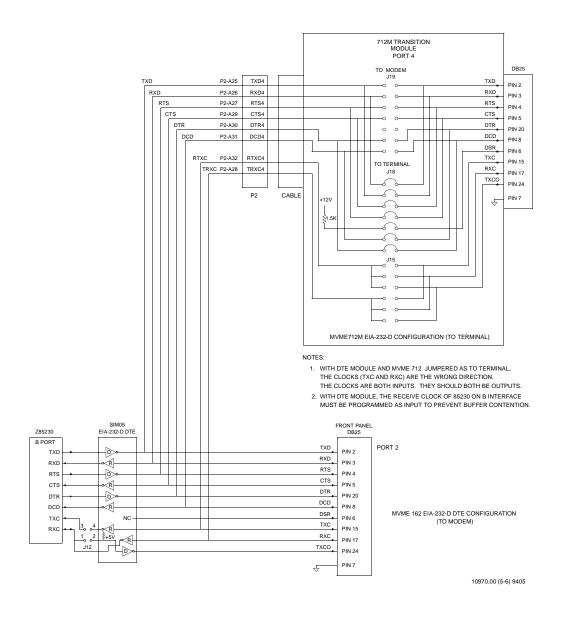

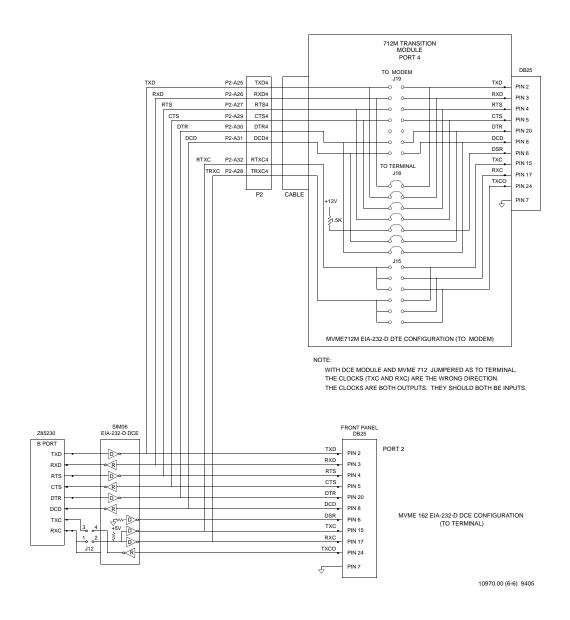

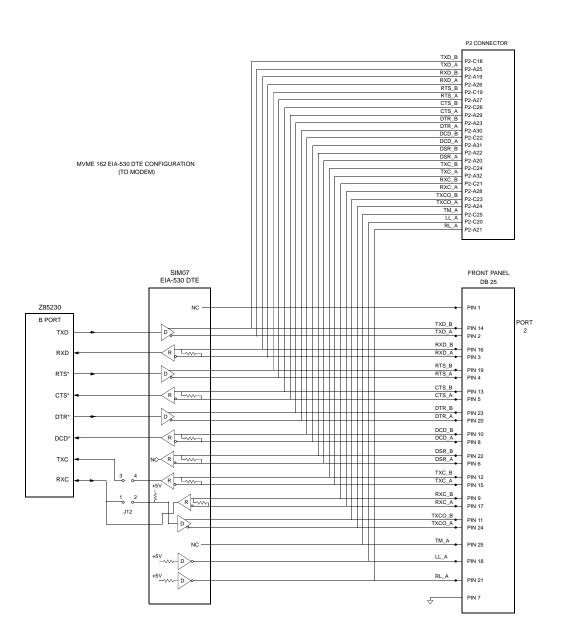

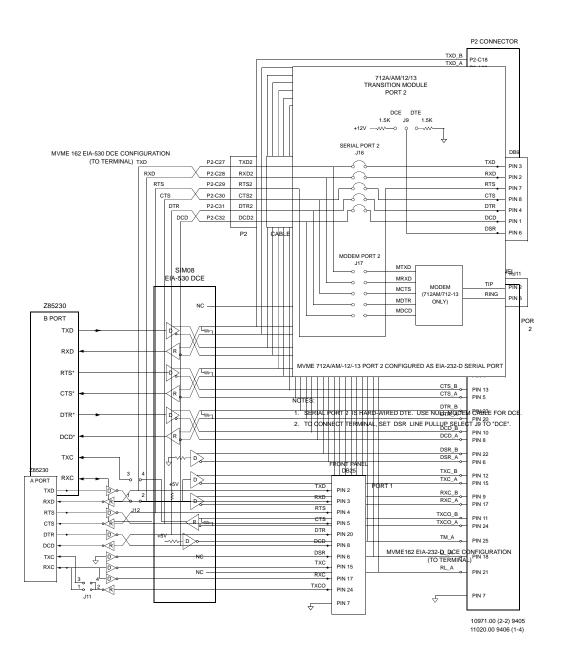

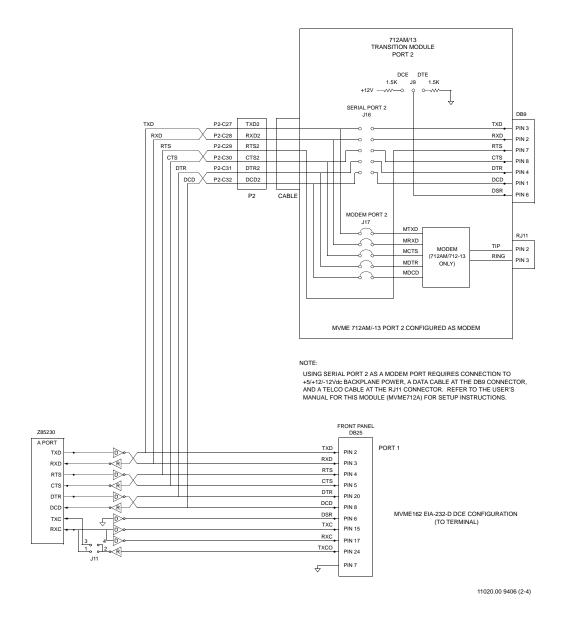

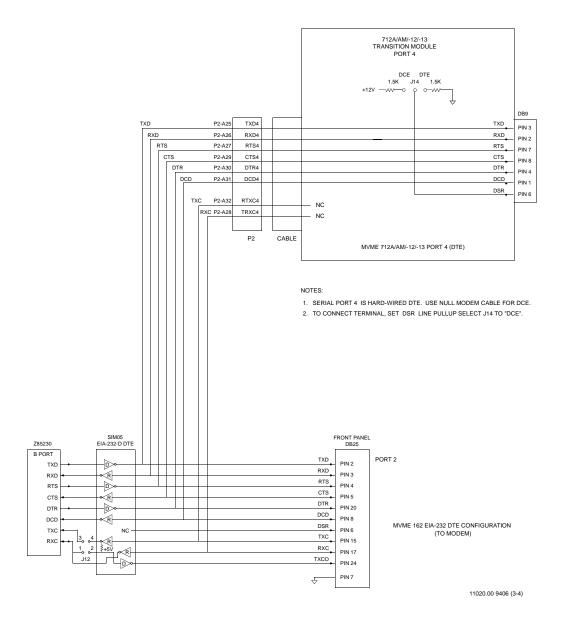

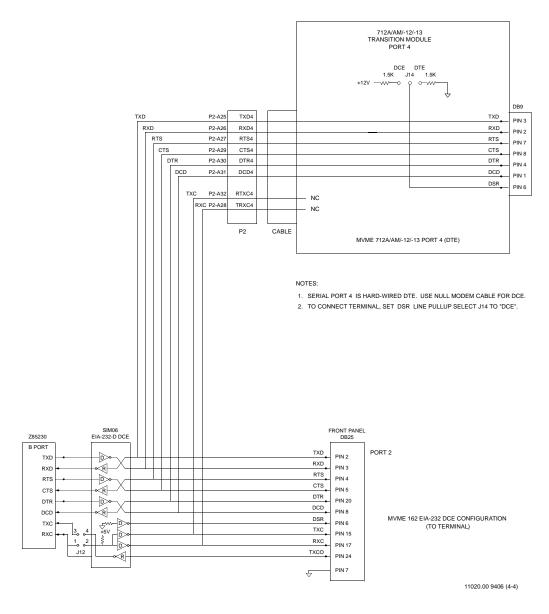

Figure 2-3 (sheets 1 through 6) in Chapter 2 illustrates the six configurations available for Port B when the MVME162 is used with an MVME712M. Note that the port configurations shown in Figure 2-3 sheets 5 and 6 are not recommended for synchronous applications because of the incorrect clock direction. Figure 2-4 (sheets 1 and 2) shows an MVME162 with the two configurations available with EIA-530 SIMs. Figure 2-5 (sheets 1 through 4) shows the four configurations available for Port B when the MVME162 is used with an MVME712A/AM/-12/-13.

# Caution

Do not simultaneously connect serial data devices to the equivalent ports on the MVME712 series transition module and the MVME162 front panel. This could result in simultaneous transmission of conflicting data.

# Caution

Do not connect peripheral devices to Port 1, Port 3, or the Centronics printer port on the MVME712X module.

# Caution

When using an EIA-530 SIM, do not connect the MVME162 to an MVME712X board. The EIA-530 signals are not supported by the P2 adapter and the transition boards.

## IndustryPack (IP) Interfaces

The IPIC ASIC on the MVME162 supports four IndustryPack (IP) interfaces: these are accessible from the front panel. Refer to the IPIC Programming Model in the *MVME162 Embedded Controller Programmer's Reference Guide* for details of the IP interface. Refer to the *MVME162 Embedded Controller Support Information* manual for the pin assignments of the IP connectors.

# **Optional LAN Ethernet Interface**

The MVME162 uses the 82596CA to implement the Ethernet transceiver interface. The 82596CA accesses local RAM using DMA operations to perform its normal functions. Because the 82596CA has small internal buffers and the

VMEbus has an undefined latency period, buffer overrun may occur if the DMA is programmed to access the VMEbus. Therefore, the 82596CA should not be programmed to access the VMEbus.

Every MVME162 that has the Ethernet interface is assigned an Ethernet Station Address. The address is \$08003E2XXXXX where XXXXX is the unique 5-nibble number assigned to the board (i.e., every MVME162 has a different value for XXXXX).

Each board has an Ethernet Station Address displayed on a label attached to the VMEbus P2 connector. In addition, the six bytes including the Ethernet address are stored in the configuration area of the BBRAM. That is, 08003E2XXXXX is stored in the BBRAM. At an address of \$FFFC1F2C, the upper four bytes (08003E2X) can be read. At an address of \$FFFC1F30, the lower two bytes (XXXX) can be read. The MVME162 debugger has the capability to retrieve or set the Ethernet address.

If the data in the BBRAM is lost, the user should use the number on the VMEbus P2 connector label to restore it.

The Ethernet transceiver interface is located on the MVME162 main board, and the industry DB15 standard connector is located on the MVME712X transition board.

Support functions for the 82596CA are provided by the MCchip ASIC. Refer to the 82596CA user's guide for detailed programming information.

# **Optional SCSI Interface**

The MVME162 may provide for mass storage subsystems through the industry-standard SCSI bus. These subsystems may include hard and floppy disk drives, streaming tape drives, and other mass storage devices. The SCSI interface is implemented using the NCR 53C710 SCSI I/O controller.

Support functions for the 53C710 are provided by the MCchip ASIC. Refer to the 53C710 user's guide for detailed programming information.

#### **SCSI Termination**

The system configurer must ensure that the SCSI bus is properly terminated at both ends. On the MVME162, sockets are provided for the terminators on the P2 adapter board or the LCP2 adapter board. If the SCSI bus ends at the adapter board, then termination resistors must be installed on the adapter board. +5V power to the SCSI bus TERM power line and termination resistors is provided through a fuse located on the adapter board.

#### **Local Resources**

The MVME162 includes many resources for the local processor. These include tick timers, software-programmable hardware interrupts, watchdog timer, and local bus timeout.

#### **Programmable Tick Timers**

Six 32-bit programmable tick timers with 1  $\mu$ s resolution are provided, two in the VMEchip2 and four in the MCchip. The tick timers can be programmed to generate periodic interrupts to the processor. Refer to the VMEchip2 and MCchip in the MVME162 Embedded Controller Programmer's Reference Guide for detailed programming information.

#### **Watchdog Timer**

A watchdog timer function is provided in the VMEchip2 and the MCchip. When the watchdog timer is enabled, it must be reset by software within the programmed time or it times out. The watchdog timer can be programmed to generate a SYSRESET signal, local reset signal, or board fail signal if it times out. Refer to the VMEchip2 and the MCchip in the MVME162 Embedded Controller Programmer's Reference Guide for detailed programming information.

The watchdog timer logic is duplicated in the VMEchip2 and MCchip ASICs. Because the watchdog timer function in the VMEchip2 is a superset of that function in the MCchip (system reset function), the timer in the VMEchip2 is used in all cases except for the version of the MVME162 which does not include the VMEbus interface ("No VMEbus Interface" option).

#### **Software-Programmable Hardware Interrupts**

Eight software-programmable hardware interrupts are provided by the VMEchip2. These interrupts allow software to create a hardware interrupt.

#### **Local Bus Timeout**

The MVME162 provides a timeout function in the VMEchip2 and the MCchip for the local bus. When the timer is enabled and a local bus access times out, a Transfer Error Acknowledge (TEA) signal is sent to the local bus master. The timeout value is selectable by software for 8  $\mu$ sec, 64  $\mu$ sec, 256  $\mu$ sec, or infinity. The local bus timer does not operate during VMEbus bound cycles. VMEbus bound cycles are timed by the VMEbus access timer and the VMEbus global timer.

The access timer logic is duplicated in the VMEchip2 and MCchip ASICs. Because the local bus timer in the VMEchip2 can detect an offboard access and the MCchip local bus timer cannot, the timer in the VMEchip2 is used in all cases except for the version of the MVME162 which does not include the VMEbus interface ("No-VMEbus-Interface option").

#### Local Bus Arbiter

The local bus arbiter implements a fixed priority which is described in the following table.

| Device    | Priority | Note        |

|-----------|----------|-------------|

| LAN       | 0        | Highest     |

| SCSI      | 1        |             |

| VMEbus    | 2        | Next Lowest |

| MC68xx040 | 3        | Lowest      |

Table 1-2. Local Bus Arbitration Priority

#### **Connectors**

The MVME162 has two 96-position DIN connectors: P1 and P2. P1 rows A, B, C, and P2 row B provide the VMEbus interconnection. P2 rows A and C provide the connection to the SCSI bus, serial ports, and Ethernet. The MVME162 has a 20-pin connector J4 mounted behind the front panel. When the MVME162 board is enclosed in a chassis and the front panel is not visible, this connector allows the reset, abort, and LED functions to be extended to the control panel of the system, where they are visible. The serial ports on the MVME162 are also connected to two 25-pin DB-25 female connectors J9 and J15 on the front panel. The four IPs connect to the MVME162 by four pairs of 50-pin connectors. Four 50-pin connectors behind the front panel are for external connections to IP signals. The memory chip mezzanine board is plugged into two 40-pin connectors.

# **Memory Maps**

There are two points of view for memory maps: 1) the mapping of all resources as viewed by local bus masters (local bus memory map), and 2) the mapping of onboard resources as viewed by VMEbus Masters (VMEbus memory map).

The memory and I/O maps which are described in the following tables are correct for all local bus masters. There is some address translation capability in the VMEchip2. This allows multiple MVME162s on the same VMEbus with different virtual local bus maps as viewed by different VMEbus masters.

# **Local Bus Memory Map**

The local bus memory map is split into different address spaces by the transfer type (TT) signals. The local resources respond to the normal access and interrupt acknowledge codes.

#### **Normal Address Range**

The memory map of devices that respond to the normal address range is shown in the following tables. The normal address range is defined by the Transfer Type (TT) signals on the local bus. On the MVME162, Transfer Types 0, 1, and 2 define the normal address range. Table 1-3 is the entire map from \$000000000 to \$FFFFFFFF. Many areas of the map are user-programmable, and suggested uses are shown in the table. The cache inhibit function is programmable in the MC68xx040 MMU. The onboard I/O space must be marked cache inhibit and serialized in its page table. Table 1-4 further defines the map for the local I/O devices.

Table 1-3. Local Bus Memory Map

| Address Range           | Devices Accessed | Port Width | Size          | Software<br>Cache<br>Inhibit | Note(s) |

|-------------------------|------------------|------------|---------------|------------------------------|---------|

| Programmable            | DRAM on board    | D32        | 1MB-4MB       | N                            | 2       |

| Programmable            | SRAM             | D32        | 128KB-<br>2MB | N                            | 2       |

| Programmable            | VMEbus A32/A24   | D32/D16    |               | ?                            | 4       |

| Programmable            | IP a Memory      | D32-D8     | 64KB-8MB      | ?                            | 2, 4    |

| Programmable            | IP b Memory      | D32-D8     | 64KB-8MB      | ?                            | 2, 4    |

| Programmable            | IP c Memory      | D32-D8     | 64KB-8MB      | ?                            | 2, 4    |

| Programmable            | IP d Memory      | D32-D8     | 64KB-8MB      | ?                            | 2, 4    |

| \$FF800000 - \$FF9FFFFF | Flash/PROM       | D32        | 2MB           | N                            | 1, 5    |

| \$FFA00000 - \$FFBFFFFF | PROM/Flash       | D32        | 2MB           | N                            | 6       |

| \$FFC00000 - \$FFCFFFFF | not decoded      |            | 1MB           | N                            | 7       |

| \$FFD00000 - \$FFDFFFFF | not decoded      |            | 1MB           | N                            | 7       |

| \$FFE00000 - \$FFE7FFFF | SRAM default     | D32        | 512KB         | N                            |         |

| \$FFE80000 - \$FFEFFFFF | not decoded      |            | 512KB         | N                            | 7       |

| \$FFF00000 - \$FFFEFFFF | Local I/O        | D32-D8     | 878KB         | Y                            | 3       |

| \$FFFF0000 - \$FFFFFFF  | VMEbus A16       | D32/D16    | 64KB          | ?                            | 2, 4    |

#### NOTES:

- 1. Reset enables the decoder for this space of the memory map so that it will decode address spaces \$FF800000 \$FF9FFFFF and \$00000000 \$003FFFFF. The decode at 0 must be disabled in the MCchip before DRAM is enabled. DRAM is enabled with the DRAM Control Register at address \$FFF42048, bit 24. PROM/Flash is disabled at the low address space with PROM Control Register at address \$FFF42040, bit 20.

- 2. This area is user-programmable. The DRAM and SRAM decoder is programmed in the MCchip, the local-to-VMEbus decoders are programmed in the VMEchip2, and the IP memory space is programmed in the IPIC.

- 3. Size is approximate.

- 4. Cache inhibit depends on devices in area mapped.

- 5. The PROM and Flash are sized by the MCchip ASIC from an 8-bit private bus to the 32-bit MPU local bus. Because the device size is less than the allocated memory map size for some entries, the device contents repeat for those entries.

If jumper GPI3 is installed, the Flash device is accessed. If GPI3 is not installed, the PROM is accessed.

- 6. The Flash and PROM are sized by the MCchip ASIC from an 8-bit private bus to the 32-bit MPU local bus. Because the device size is less than the allocated memory map size for some entries, the device contents repeat for those entries.

If jumper GPI3 is installed, the PROM is accessed. If GPI3 is not installed, the Flash device is accessed.

- 7. These areas are not decoded unless one of the programmable decoders are initialized to decode this space. If they are not decoded, an access to this address range will generate a local bus timeout. The local bus timer must be enabled.

The following table focuses on the Local I/O Devices portion of the local bus Main Memory Map.

Table 1-4. Local Bus I/O Devices Memory Map

| Address Range           | Device                         | Port Width | Size  | Note(s) |

|-------------------------|--------------------------------|------------|-------|---------|

| \$FFF00000 - \$FFF3FFFF | reserved                       |            | 256KB | 4       |

| \$FFF40000 - \$FFF400FF | VMEchip2 (LCSR)                | D32        | 256B  | 1, 3    |

| \$FFF40100 - \$FFF401FF | VMEchip2 (GCSR) registers      | D32-D8     | 256B  | 1, 3    |

| \$FFF40200 - \$FFF40FFF | reserved                       |            | 3.5KB | 4, 5    |

| \$FFF41000 - \$FFF41FFF | reserved                       |            | 4KB   | 4       |

| \$FFF42000 - \$FFF42FFF | MCchip                         | D32-D8     | 4KB   | 1       |

| \$FFF44300 - \$FFF44FFF | reserved                       |            | 8KB   | 4       |

| \$FFF45000 - \$FFF45FFF | SCC (Z85230)                   | D8         | 4KB   | 1, 2    |

| \$FFF46000 - \$FFF46FFF | LAN (82596CA)                  | D32        | 4KB   | 1, 6    |

| \$FFF47000 - \$FFF47FFF | SCSI (53C710)                  | D32-D8     | 4KB   | 1       |

| \$FFF48000 - \$FFF57FFF | reserved                       |            | 64KB  | 4       |

| \$FFF58000 - \$FFF5807F | IPIC IP a I/O                  | D16        | 128B  | 1       |

| \$FFF58080 - \$FFF580FF | IPIC IP a ID                   | D16        | 128B  | 1       |

| \$FFF58100 - \$FFF5817F | IPIC IP b I/O                  | D16        | 128B  | 1       |

| \$FFF58180 - \$FFF581FF | IPIC IP b ID Read              | D16        | 128B  | 1       |

| \$FFF58200 - \$FFF5827F | IPIC IP c I/O                  | D16        | 128B  | 1       |

| \$FFF58280 - \$FFF582FF | IPIC IP c ID                   | D16        | 128B  | 1       |

| \$FFF58300 - \$FFF5837F | IPIC IP d I/O                  | D16        | 128B  | 1       |

| \$FFF58380 - \$FFF583FF | IPIC IP d ID Read              | D16        | 128B  | 1       |

| \$FFF58400 - \$FFF584FF | IPIC IP ab I/O                 | D32-D16    | 256B  | 1       |

| \$FFF58500 - \$FFF585FF | IPIC IP cd I/O                 | D32-D16    | 256B  | 1       |

| \$FFF58600 - \$FFF586FF | IPIC IP ab I/O repeated        | D32-D16    | 256B  | 1       |

| \$FFF58700 - \$FFF587FF | IPIC IP cd I/O repeated        | D32-D16    | 256B  | 1       |

| \$FFF58800 - \$FFF5887F | reserved                       |            | 128B  | 1       |

| \$FFF58880 - \$FFF588FF | reserved                       |            | 128B  | 1       |

| \$FFF58900 - \$FFF5897F | reserved                       |            | 128B  | 1       |

| \$FFF58980 - \$FFF589FF | reserved                       |            | 128B  | 1       |

| \$FFF58A00 - \$FFF58A7F | reserved                       |            | 128B  | 1       |

| \$FFF58A80 - \$FFF58AFF | reserved                       |            | 128B  | 1       |

| \$FFF58B00 - \$FFF58B7F | reserved                       |            | 128B  | 1       |

| \$FFF58B80 - \$FFF58BFF | reserved                       |            | 128B  | 1       |

| \$FFF58C00 - \$FFF58CFF | reserved                       |            | 256B  | 1       |

| \$FFF58D00 - \$FFF58DFF | reserved                       |            | 256B  | 1       |

| \$FFF58E00 - \$FFF58EFF | reserved                       |            | 256B  | 1       |

| \$FFF58F00 - \$FFF58FFF | reserved                       |            | 256B  | 1       |

| \$FFFBC000 - \$FFFBC01F | IPIC registers                 | D32-D8     | 2KB   | 1       |

| \$FFFBC800 - \$FFFBC81F | reserved                       |            | 2KB   | 1       |

| \$FFFBD000 - \$FFFBFFFF | reserved                       |            | 12KB  | 4       |

| \$FFFC0000 - \$FFFC7FFF | MK48T08 (BBRAM, TOD clock)     | D32-D8     | 32KB  | 1       |

| \$FFFC8000 - \$FFFCBFFF | MK48T08 & disable Flash writes | D32-D8     | 16KB  | 1, 7    |

| \$FFFCC000 - \$FFFCFFFF | MK48T08 & enable Flash writes  | D32-D8     | 16KB  | 1, 7    |

| \$FFFD0000 - \$FFFEFFFF | reserved                       |            | 128KB | 4       |

#### **NOTES:**

- 1. For a complete description of the register bits, refer to the *MVME162 Embedded Controller Programmer's Reference Guide* or to the data sheet for the specific chip.

- 2. The SCC is an 8-bit device located on an MCchip private data bus. Byte access is required.

- 3. Writes to the LCSR in the VMEchip2 must be 32 bits. LCSR writes of 8 or 16 bits terminate with a TEA signal. Writes to the GCSR may be 8, 16 or 32 bits. Reads to the LCSR and GCSR may be 8, 16 or 32 bits. Byte reads should be used to read the interrupt vector.

- 4. This area does not return an acknowledge signal. If the local bus timer is enabled, the access times out and is terminated by a TEA signal.

- 5. Size is approximate.

- 6. Port commands to the 82596CA must be written as two 16-bit writes: upper word first and lower word second.

- 7. Refer to the Flash and PROM Interface section in the MCchip description in the MVME162 Embedded Controller Programmer's Reference Guide.

# **VMEbus Memory Map**

This section describes the mapping of local resources as viewed by VMEbus masters. Default addresses for the slave, master, and GCSR address decoders are provided by the ENV command. Refer to Appendix A.

#### **VMEbus Accesses to the Local Bus**

The VMEchip2 includes a user-programmable map decoder for the VMEbus to local bus interface. The map decoder allows you to program the starting and ending address and the modifiers the MVME162 responds to.

#### **VMEbus Short I/O Memory Map**

The VMEchip2 includes a user-programmable map decoder for the GCSR. The GCSR map decoder allows you to program the starting address of the GCSR in the VMEbus short I/O space.

## Introduction

This chapter provides unpacking instructions, hardware preparation, and installation instructions for the MVME162 Embedded Controller. Hardware preparation for the MVME712 series transition modules is provided in separate manuals. Refer to the *Related Documentation* section in Chapter 1.

# **Unpacking Instructions**

If the shipping carton is damaged upon receipt, request carrier's agent be present during unpacking and inspection of equipment.

Unpack equipment from shipping carton. Refer to packing list and verify that all items are present. Save packing material for storing and reshipping of equipment.

Avoid touching areas of integrated circuitry; static discharge can damage circuits.

# **Hardware Preparation**

To select the desired configuration and ensure proper operation of MVME162, certain option modifications may be necessary before installation. MVME162 provides software control for most of these options. Some options can not be performed in software, so are performed by installing or removing header jumpers or interface modules. Most other modifications are performed by setting bits in control registers after MVME162 has been installed in a system. (For more information on the MVME162 registers refer to the MVME162 Embedded Controller Programmer's Reference Guide listed in Related Documentation in Chapter 1.)

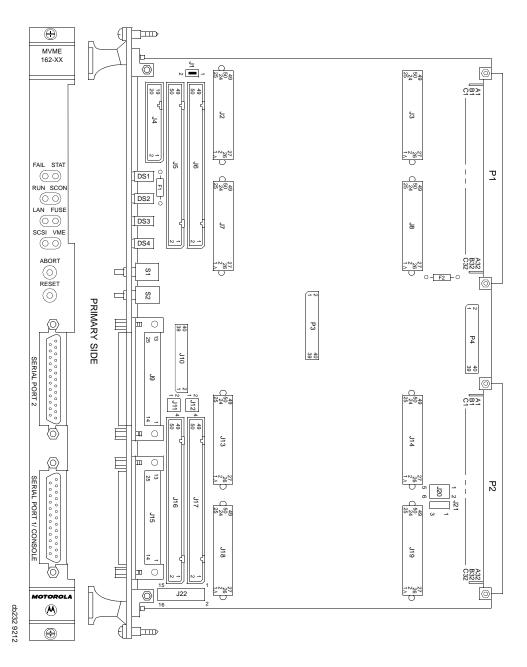

The locations of the switches, jumper headers, connectors, and LEDs on the MVME162 are illustrated in Figure 2-1. MVME162 has been factory tested and is shipped with the factory jumper settings described in the following sections.

MVME162 operates with its required and factory-installed Debug Monitor, MVME162Bug (162Bug), with these factory jumper settings. Manually configurable items include:

| SIM selection for serial port B configuration (J10)         |

|-------------------------------------------------------------|

| System controller selection (J1)                            |

| Synchronous clock selection (J11) for Serial Port 1/Console |

| Synchronous clock selection (J12) for Serial Port 2         |

| SRAM backup power source selection (J20)                    |

| EPROM size selection (J21)                                  |

☐ General-purpose readable register configuration (J22)

#### SIM Selection

Port B of the MVME162's Z85230 serial communications controller is configurable via a serial interface module (SIM) which is installed at connector J10 on the MVME162 board. Four serial interface modules are available:

| EIA-232-D (DCE and DTE |

|------------------------|

| EIA-530 (DCE and DTE)  |

You can change Port B from an EIA-232-D to an EIA-530 interface (or viceversa) by mounting the appropriate serial interface module. Port B is routed (via the SIM at J10) to the 25-pin DB25 front panel connector marked SERIAL PORT 2.

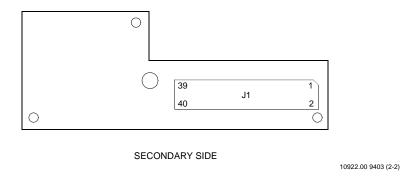

For the location of SIM connector J10 on the MVME162, refer to Figure 2-1. Figure 2-2 illustrates the secondary side (bottom) of a serial interface module, showing the J1 connector which plugs into SIM connector J10 on the MVME162. Figure 2-3 (sheets 3-6) and Figure 2-4 illustrate the six configurations available for Port B.

For the part numbers of the serial interface modules, refer to Table 2-1. The part numbers are ordinarily printed on the primary side (top) of the SIMs, but may be found on the secondary side in some versions.

If you need to replace an existing serial interface module with a SIM of another type, go to *Removal of Existing SIM* below. If there is no SIM on the main board, skip to *Installation of New SIM*.

Figure 2-1. MVME162 Switches, Headers, Connectors, Fuses, and LEDs

EIA Model Configuration **Part Number** Standard Number EIA-232-D DTE 01-W3846B SIM05 DCE 01-W3865B SIM<sub>06</sub> EIA-530 DTE 01-W3868B SIM07 DCE 01-W3867B SIM08

Table 2-1. Serial Interface Module Part Numbers

Figure 2-2. Serial Interface Module, Connector Side

# Removal of Existing SIM

- 1. Each serial interface module is retained by two 4-40 x  $^3$ /16 " Phillips-head screws in opposite corners. Remove the two screws and store them in a safe place for later use.

- 2. Grasp opposite sides of the SIM and gently lift straight up.

# Avoid lifting the SIM by one side only, as the connector can be damaged on the SIM or the main board.

3. Place the SIM in a static-safe container for possible reuse.

#### Installation of New SIM

- 1. Observe the orientation of the connector keys on SIM connector J1 and MVME162 connector J10. Turn the SIM so that the keys line up and place it gently on connector J10, aligning the mounting holes at the SIM corners with the matching standoffs on the MVME162.

- Gently press the top of the SIM to seat it on the connector. If the SIM does not seat with gentle pressure, recheck the orientation. If the SIM connector is oriented incorrectly, the mounting holes will not line up with the standoffs.

# Caution

Do not attempt to force the SIM on if it is oriented incorrectly.

3. Place the two 4-40 x  $^3/_{16}$ " Phillips-head screws that you previously removed (or that were supplied with the new SIM) into the two opposite-corner mounting holes. Screw them into the standoffs but do not overtighten them.

The signal relationships and signal connections in the various serial configurations available for ports A and B are illustrated in Figures 2-3 and 2-4.

### System Controller Select Header (J1)

The MVME162 is factory-configured as a VMEbus system controller (i.e., a jumper is installed across pins 1 and 2 of header J1). Remove the J1 jumper if the MVME162 is not to be the system controller. Note that when the MVME162 is functioning as system controller, the SCON LED is turned on.

For MVME162s without the optional VMEbus interface (i.e., no VMEchip2), the jumper may be installed or removed without affecting normal operation.

System Controller (factory configuration)

Not System Controller

### Synchronous Clock Select Header (J11) for Serial Port 1/Console

The MVME162 is shipped from the factory with the SERIAL PORT 1/CONSOLE header configured for asynchronous communications (i.e., jumpers removed). To select synchronous communications for the SERIAL PORT 1/CONSOLE connection, install jumpers across pins 1 and 2 and pins 3 and 4.

Internal Clock (factory configuration)

External Clock

### Clock Select Header (J12) for Serial Port 2

The MVME162 is shipped from the factory with the SERIAL PORT 2 header configured for asynchronous communications (i.e., jumpers removed). To select synchronous communications for the SERIAL PORT 2 connection, install jumpers across pins 1 and 2 and pins 3 and 4.

Internal Clock (factory configuration)

External Clock

### **SRAM Battery Backup Source Select Header (J20)**

The MVME162 is factory-configured to use VMEbus +5V Standby power as a backup power source for the SRAM (i.e., jumpers are installed across pins 1 and 3 and 2 and 4). To select the onboard battery as the backup power source, install the jumpers across pins 3 and 5 and 4 and 6.

For MVME162s without optional VMEbus interface (i.e., without VMEchip2 ASIC), you must select the onboard battery for the backup power source.

# Caution

Removing all jumpers may temporarily disable the SRAM. Do not remove all jumpers from J20, except for storage

### **EPROM Size Select Header (J21)**

The MVME162 is factory-configured for a 4Mbit EPROM (i.e., a jumper is installed across pins 2 and 3). This is the only size currently available; if a larger PROM becomes available, this jumper will allow it to be selected.

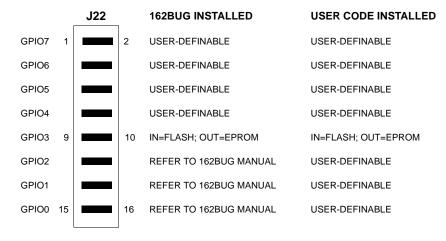

### **General Purpose Readable Jumpers Header (J22)**

Header J22 provides eight readable jumpers. These jumpers are read as a register (at \$FFF4202D) in the MCchip LCSR (local control/status register). The bit values are read as a zero when the jumper is installed and as a one when the jumper is removed.

If the MVME162BUG firmware is installed, four jumpers are user-definable (pins 1-2, 3-4, 5-6, 7-8). If the MVME162BUG firmware is not installed, seven jumpers are user-definable (pins 1-2, 3-4, 5-6, 7-8, 11-12, 13-14, 15-16).

Pins 9-10 (GPIO3) are reserved to select either the Flash memory map (jumper installed) or the EPROM memory map (jumper removed). They are not user-definable.

The MVME162 is shipped from the factory with J22 set to all zeros (jumpers on all pins).

EPROMs Selected (factory configuration)

#### Installation Instructions

The following sections discuss the installation of IndustryPacks (IPs) on the MVME162, the installation of the MVME162 into a VME chassis, and the system considerations relevant to the installation. Before installing IndustryPacks, ensure that the serial ports and all header jumpers are configured as desired.

#### **IP Installation on the MVME162**

Up to four IndustryPack (IP) modules may be installed on the MVME162. Install the IPs on the MVME162 as follows:

- 1. Each IP has two 50-pin connectors that plug into two corresponding 50-pin connectors on the MVME162: J2/J3, J7/J8, J13/J14, J18/J19. See Figure 2-1 for the MVME162 connector locations.

- Orient the IP(s) so that the tapered connector shells mate properly.

Plug IP\_a into connectors J2 and J3; plug IP\_b into J7 and J8. Plug IP\_c into J13 and J14; plug IP\_d into J18 and J19. If a double-sized IP is used, plug IP\_ab into J2, J3, J7, and J8; plug IP\_cd into J13, J14, J18, and J19.

- 2. Four additional 50-pin connectors (J6, J5, J17, and J16) are provided behind the MVME162 front panel for external cabling connections to the IP modules. There is a one-to-one correspondence between the signals on the cabling connectors and the signals on the associated IP connectors (i.e., J6 has the same IP\_a signals as J2; J5 has the same IP\_b signals as J7; J17 has the same IP\_c signals as J13; and J16 has the same IP\_d signals as J18.

- Connect user-supplied 50-pin cables to J6, J5, J17, and J16 as needed.

Because of the varying requirements for each different kind of IP,

Motorola does not supply these cables.

- Bring the IP cables out the narrow slots in the MVME162 front panel and attach them to the appropriate external equipment, depending on the nature of the particular IP(s).

#### **MVME162 Module Installation**

With EPROM, IndustryPack, and SIMs installed and headers properly configured, proceed as follows to install the MVME162 in the VME chassis:

1. Turn all equipment power OFF and disconnect the power cable from the AC power source.

## Caution

Inserting or removing modules while power is applied could result in damage to module components.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

- 2. Remove the chassis cover as instructed in the user's manual for the equipment.

- 3. Remove the filler panel from the card slot where you are going to install the MVME162.

- If you intend to use the MVME162 as system controller, it must occupy

the leftmost card slot (slot 1). The system controller must be in slot 1

to correctly initiate the bus-grant daisy-chain and to ensure proper

operation of the IACK daisy-chain driver.

- If you do not intend to use the MVME162 as system controller, it can occupy any unused double-height card slot.

- 4. Slide the MVME162 into the selected card slot. Be sure the module is seated properly in the P1 and P2 connectors on the backplane. Do not damage or bend connector pins.

- 5. Secure the MVME162 in the chassis with the screws provided, making good contact with the transverse mounting rails to minimize RF emissions.

- 6. Install the MVME712 series transition module in the front or the rear of the VME chassis. (To install an MVME712M, which has a double-wide front panel, you may need to shift other modules in the chassis.)

- 7. On the chassis backplane, remove the INTERRUPT ACKNOWLEDGE (IACK) and BUS GRANT (BG) jumpers from the header for the card slot occupied by the MVME162.

- 8. Connect the P2 Adapter Board or LCP2 Adapter Board and cable(s) to MVME162 backplane connector P2. This provides a connection point for terminals or other peripherals at the EIA-232-D serial ports, SCSI ports, and LAN Ethernet port.

- For information on installing the P2 or LCP2 Adapter Board and the MVME712 series transition module(s), refer to the manuals listed in *Related Documentation* in Chapter 1 (the *MVME162 Embedded Controller Programmer's Reference Guide* provides some connection diagrams.)

- 9. Connect the appropriate cable(s) to the panel connectors for the EIA-232-D serial ports, SCSI port, and LAN Ethernet port.

- Note that some cables are not provided with the MVME712 series module and must be made or purchased by the user. (Motorola recommends shielded cable for all peripheral connections to minimize radiation.)

- 10. Connect the peripheral(s) to the cable(s). Appendix A supplies detailed information on the EIA-232-D signals supported. Appendix B describes the Ethernet LAN (*Local Area Network*) port connections. Appendix C describes the SCSI (*Small Computer System Interface*) I/O bus connections.

- 11. Install any other required VMEmodules in the system.

- 12. Replace the chassis cover.

- 13. Connect the power cable to the AC power source and turn the equipment power ON.

### **System Considerations**

The MVME162 draws power from VMEbus backplane connectors P1 and P2. P2 is also used for the upper 16 bits of data in 32-bit transfers, and for the upper 8 address lines used in extended addressing mode. The MVME162 may not function properly without its main board connected to VMEbus backplane connectors P1 and P2.

Whether MVME162 operates as VMEbus master or VMEbus slave, it is configured for 32 bits of address and 32 bits of data (A32/D32). However, it handles A16 or A24 devices in the address ranges indicated in Chapter 1. D8 and/or D16 devices in the system must be handled by the MC68040/MC68LC040 software. Refer to the memory maps in the MVME162 Embedded Controller Programmer's Reference Guide.)

The MVME162 contains shared onboard DRAM whose base address is software-selectable. Both the onboard processor and offboard VMEbus devices see this local DRAM at base physical address \$00000000, as

programmed by the MVME162Bug firmware. This may be changed via software to any other base address. Refer to *MVME162 Embedded Controller Programmer's Reference Guide* for more information.

If the MVME162 tries to access offboard resources in a nonexistent location and is not system controller, and if the system does not have a global bus timeout, the MVME162 waits forever for the VMEbus cycle to complete. This will cause the system to lock up. There is only one situation in which the system might lack this global bus timeout: when the MVME162 is not the system controller and there is no global bus timeout elsewhere in the system.

Multiple MVME162s may be installed in a single VME chassis. In general, hardware multiprocessor features are supported.

If you are installing multiple MVME162s in an MVME945 chassis, do not install an MVME162 in slot 12. The height of the IP modules may cause clearance difficulties in that slot position.

Other MPUs on the VMEbus can interrupt, disable, communicate with, and determine the operational status of the processor(s). One register of the GCSR (global control/status register) set includes four bits that function as location monitors to allow one MVME162 processor to broadcast a signal to any other MVME162 processors. All eight registers are accessible from any local processor as well as from the VMEbus.

The MVME162 provides +5 Vdc power to the remote LED/switch connector (J4) through a 1A fuse (F1) located near J4. Connector J4 is the interface for a remote control and indicator panel. If none of the LEDs light and the ABORT and RESET switches do not operate, check fuse F1.

The MVME162 provides +12 Vdc power to the Ethernet transceiver interface through a 1A fuse (F2) located near diode CR1. The FUSE LED lights to indicate that +12 Vdc is available. When the MVME712M module is used, the yellow DS1 LED on the MVME712M illuminates when LAN power is available, which indicates that the fuse is good. If the Ethernet transceiver fails to operate, check fuse F2.

The MVME162 provides SCSI terminator power through a 1A fuse (F1) located on the P2 Adapter Board or LCP2 Adapter Board. If the fuse is blown, the SCSI device(s) may function erratically or not at all. When the P2 Adapter Board is used with an MVME712M and the SCSI bus is connected to the MVME712M, the green DS2 LED on the MVME712M front panel illuminates when SCSI terminator power is available. If the green DS2 LED flickers during SCSI bus operation, check P2 Adapter Board fuse F1.

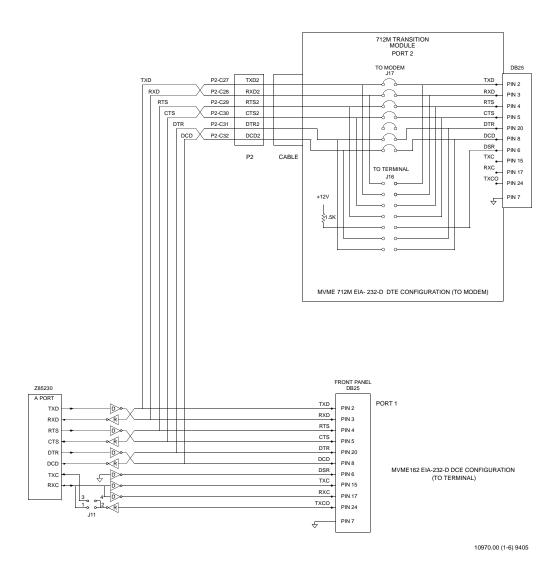

Figure 2-3. MVME162 EIA-232-D Connection Diagram, MVME712M (Sheet 1 of 6)

Figure 2-3. MVME162 EIA-232-D Connection Diagram, MVME712M (Sheet 2 of 6)

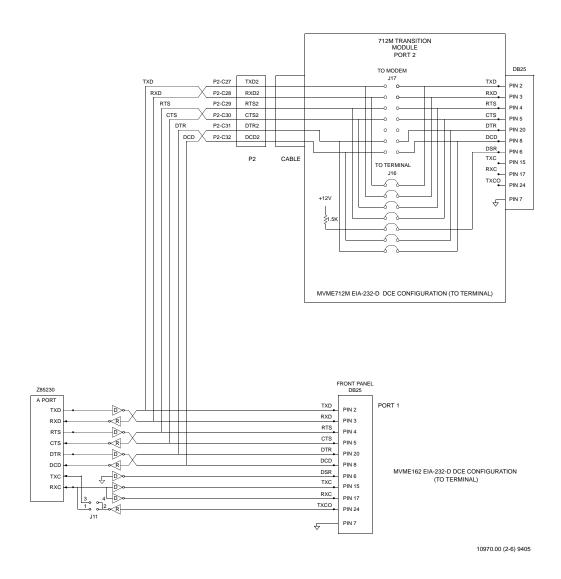

Figure 2-3. MVME162 EIA-232-D Connection Diagram, MVME712M (Sheet 3 of 6)

Figure 2-3. MVME162 EIA-232-D Connection Diagram, MVME712M (Sheet 4 of 6)