# MVME2600 Series Single Board Computer Programmer's Reference Guide

V2600A/PG1

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

No part of this material may be reproduced or copied in any tangible medium, or stored in a retrieval system, or transmitted in any form, or by any means, radio, electronic, mechanical, photocopying, recording or facsimile, or otherwise, without the prior written permission of Motorola, Inc.

It is possible that this publication may contain reference to, or information about Motorola products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

### **Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

#### **Preface**

The MVME2600 Series Single Board Computer Programmer's Reference Guide provides brief board level information, complete memory maps, and detailed ASIC chip information including register bit descriptions for the MVME2600 series Single Board Computers (also called MVME2603 and MVME2604 in this manual). The information contained in this manual applies to the single board computers built from some of the plug-together components listed in the following table.

| MVME2603-1121 | MVME2603-2121 | RAM200-042 |

|---------------|---------------|------------|

| MVME2603-1131 | MVME2603-2131 | RAM200-043 |

| MVME2603-1141 | MVME2603-2141 | RAM200-044 |

| MVME2603-1191 | MVME2603-2191 | RAM200-049 |

```

MVME2604-1021 MVME2604-1121 MVME2604-2021 MVME2604-2121 MVME2604-1031 MVME2604-1131 MVME2604-2031 MVME2604-2131 MVME2604-1041 MVME2604-1141 MVME2604-2041 MVME2604-2141 MVME2604-1091 MVME2604-1191 MVME2604-2091 MVME2604-2191

```

This manual is intended for anyone who wants to program these boards in order to design OEM systems, supply additional capability to an existing compatible system, or work in a lab environment for experimental purposes.

A basic knowledge of computers and digital logic is assumed.

To use this manual, you should be familiar with the publications listed in *Appendix A*, *Related Documentation*.

The following conventions are used in this document:

#### bold

is used for user input that you type just as it appears. Bold is also used for commands, options and arguments to commands, and names of programs, directories, and files.

#### italic

is used for names of variables to which you assign values. Italic is also used for comments in screen displays and examples.

#### courier

is used for system output (e.g., screen displays, reports), examples, and system prompts.

#### <RETURN> or <CR>

represents the carriage return or enter key.

#### CTRL.

represents the Control key. Execute control characters by pressing the CTRL key and the letter simultaneously, e.g., CTRL-d.

The computer programs stored in the Read Only Memory of this device contain material copyrighted by Motorola Inc., first published 1990, and may be used only under a license such as the License for Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

All Motorola PWBs (printed wiring boards) are manufactured by UL-recognized manufacturers, with a flammability rating of 94V-0.

This equipment generates, uses, and can radiate electromagnetic energy. It may cause or be susceptible to electromagnetic interference (EMI) if not installed and used in a cabinet with adequate EMI protection.

Motorola<sup>®</sup> and the Motorola symbol are registered trademarks of Motorola, Inc.

PowerStack<sup>TM</sup>, VMEmodule<sup>TM</sup>, and VMEsystem<sup>TM</sup> are trademarks of Motorola, Inc.

PowerPC<sup>TM</sup>, PowerPC 603<sup>TM</sup>, and PowerPC 604<sup>TM</sup> are trademarks of IBM Corp, and are used by Motorola, Inc. under license from IBM Corp.

AIX<sup>TM</sup> is a trademark of IBM Corp.

$\mathsf{Timekeeper}^{\mathsf{TM}}$  and  $\mathsf{Zeropower}^{\mathsf{TM}}$  are trademarks of Thompson Components.

All other products mentioned in this document are trademarks or registered trademarks of their respective holders.

©Copyright Motorola 1996

All Rights Reserved

Printed in the United States of America

November 1996

# Safety Summary Safety Depends On You

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Motorola, Inc. assumes no liability for the customer's failure to comply with these requirements.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. The equipment is supplied with a three-conductor ac power cable. The power cable must be plugged into an approved three-contact electrical outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

### **Keep Away From Live Circuits.**

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified maintenance personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

### Do Not Service or Adjust Alone.

Do not attempt internal service or adjustment unless another person capable of rendering first aid and resuscitation is present.

### Use Caution When Exposing or Handling the CRT.

Breakage of the Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, avoid rough handling or jarring of the equipment. Handling of the CRT should be done only by qualified maintenance personnel using approved safety mask and gloves.

## Do Not Substitute Parts or Modify Equipment.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that safety features are maintained.

### **Dangerous Procedure Warnings.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

# **Contents**

```

Introduction 1-1

Manual Terminology 1-1

Overview 1-3

Feature Summary 1-3

System Block Diagram 1-4

Functional Description 1-6

Overview 1-6

Programming Model 1-7

Memory Maps 1-7

Processor Memory Maps 1-7

PCI Memory Maps 1-13

VMEbus Mapping 1-20

Falcon-Controlled System Registers 1-26

System Configuration Register (SYSCR) 1-27

Memory Configuration Register (MEMCR) 1-29

System External Cache Control Register (SXCCR) 1-30

CPU Control Register 1-32

ISA Local Resource Bus 1-33

W83C553 PIB Registers 1-33

PC87308VUL Super I/O (ISASIO) Strapping 1-33

NVRAM/RTC & Watchdog Timer Registers 1-33

Module Configuration and Status Registers 1-34

CPU Configuration Register 1-35

Base Module Feature Register 1-36

Base Module Status Register (BMSR) 1-37

Seven-Segment Display Register 1-38

VME Registers 1-38

LM/SIG Control Register 1-39

LM/SIG Status Register 1-40

Location Monitor Upper Base Address Register 1-41

Location Monitor Lower Base Address Register 1-42

Semaphore Register 1 1-42

Semaphore Register 2 1-43

VME Geographical Address Register (VGAR) 1-43

Z85230 ESCC and Z8536 CIO Registers and Port Pins 1-44

Z8536/Z85230 Registers 1-44

Z8536 CIO Port Pins 1-45

```

```

ISA DMA Channels 1-48

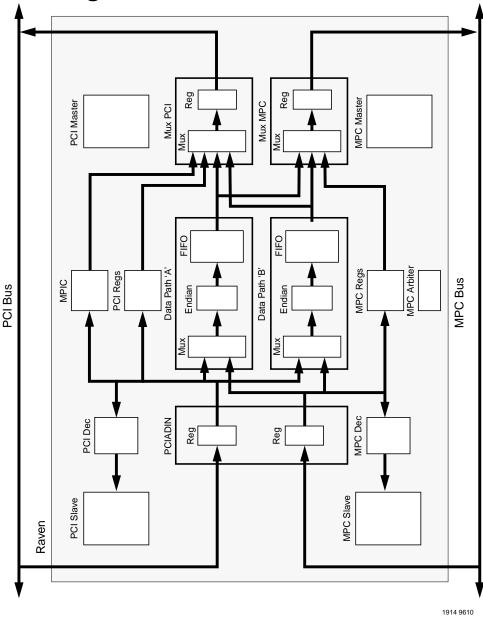

Introduction 2-1

Overview 2-1

Requirements 2-2

Features 2-2

Block Diagram 2-4

Functional Description 2-5

MPC Bus Interface 2-5

MPC Arbiter 2-5

MPC Map Decoders 2-7

MPC Write Posting 2-8

MPC Master 2-9

MPC Bus Timer 2-10

PCI Interface 2-11

PCI Map Decoders 2-11

PCI Configuration Space 2-12

PCI Write Posting 2-12

PCI Master 2-13

Generating PCI Memory and I/O Cycles 2-14

Generating PCI Configuration Cycles 2-15

Generating PCI Special Cycles 2-16

Generating PCI Interrupt Acknowledge Cycles 2-16

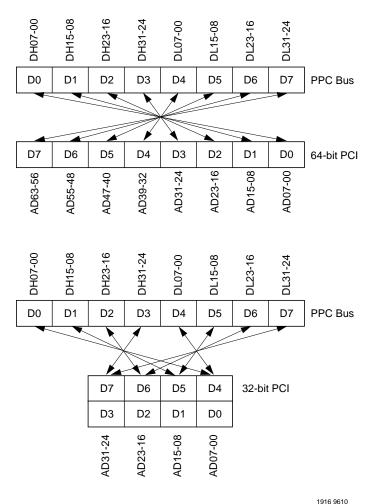

Endian Conversion 2-17

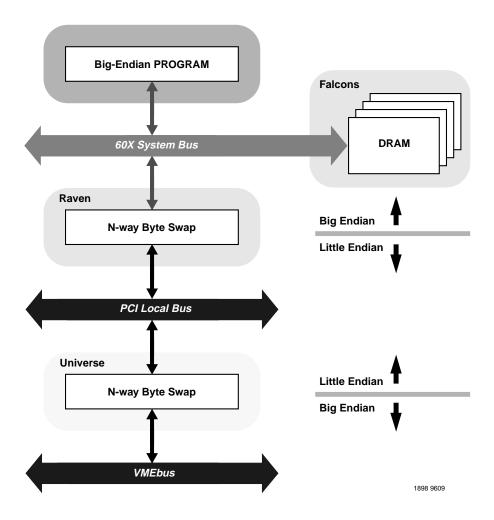

When MPC Devices are Big-Endian 2-17

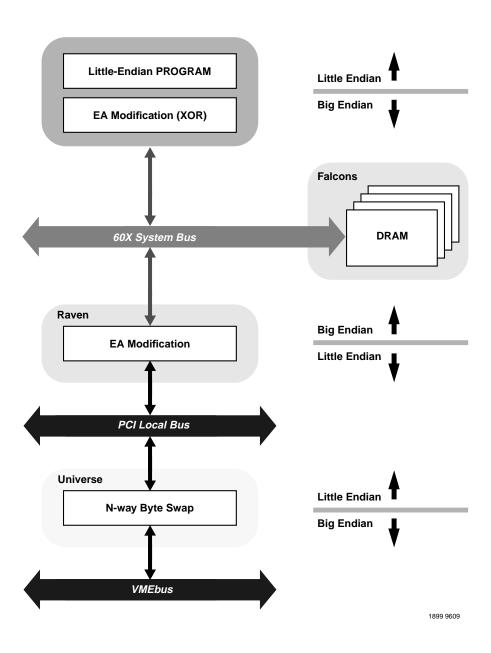

When MPC Devices are Little Endian 2-18

Cycles Originating From PCI 2-19

Error Handling 2-19

PCI/MPC Contention Handling 2-21

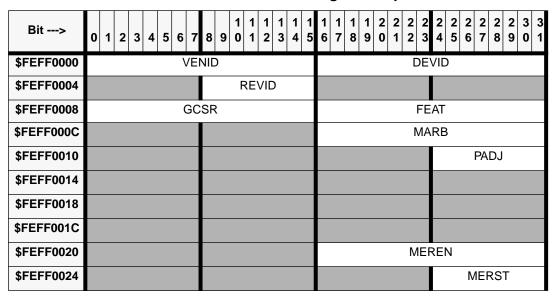

Registers 2-23

MPC Registers 2-23

Vendor ID/Device ID Registers 2-25

Revision ID Register 2-25

General Control-Status/Feature Registers 2-26

MPC Arbiter Control Register 2-29

Prescaler Adjust Register 2-30

MPC Error Enable Register 2-31

MPC Error Status Register 2-34

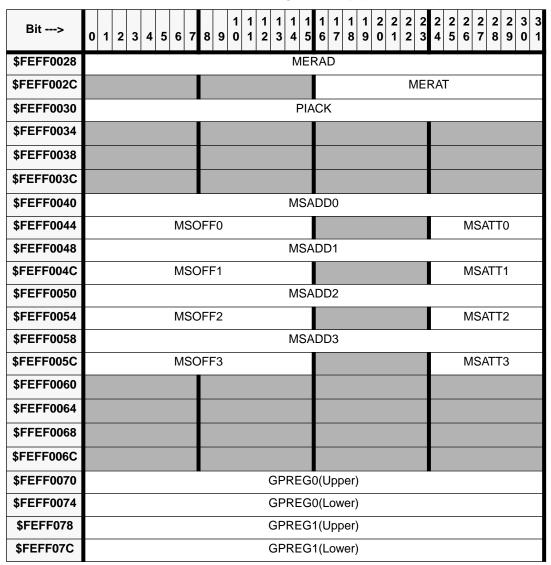

MPC Error Address Register 2-36

MPC Error Attribute Register - MERAT 2-36

PCI Interrupt Acknowledge Register 2-38

MPC Slave Address (0,1 and 2) Registers 2-39

```

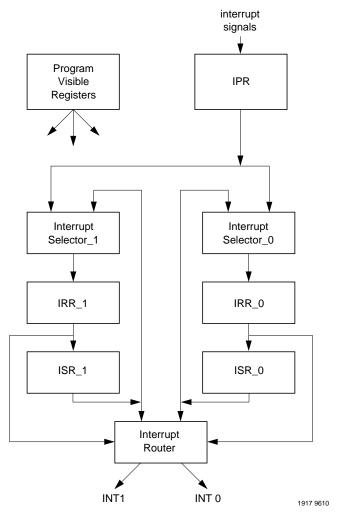

MPC Slave Offset / Attribute (0,1 and 2) Registers 2-41 MPC Slave Offset / Attribute (3) Registers 2-42 General Purpose Registers 2-43 PCI Registers 2-43 Vendor ID / Device ID Registers 2-45 PCI Command / Status Registers 2-45 Revision ID/ Class Code Registers 2-47 I/O Base Register 2-48 Memory Base Register 2-49 PCI Slave Address (0,1,2 and 3) Registers 2-50 PCI Slave Attribute / Offset (0,1,2 and 3) Registers 2-51 **CONFIG ADDRESS 2-52** PCI I/O CONFIG\_ADDRESS Register 2-52 PCI I/O CONFIG\_DATA Register 2-54 Raven Interrupt Controller Implementation 2-55 Introduction 2-55 The Raven Interrupt Controller (RavenMPIC) Features 2-55 Architecture 2-55 CSR's Readability 2-56 Interrupt Source Priority 2-56 Processor's Current Task Priority 2-56 Nesting of Interrupt Events 2-56 Spurious Vector Generation 2-57 Interprocessor Interrupts (IPI) 2-57 8259 Compatibility 2-57 Raven-Detected Errors 2-58 Timers 2-58 Interrupt Delivery Modes 2-58 Block Diagram Description 2-60 Program Visible Registers 2-61 Interrupt Pending Register (IPR) 2-61 Interrupt Selector (IS) 2-61 Interrupt Request Register (IRR) 2-62 In-Service Register (ISR) 2-62 Interrupt Router 2-62 MPIC Registers 2-64 RavenMPIC Registers 2-64 Feature Reporting Register 2-69 Global Configuration Register 2-70 Vendor Identification Register 2-71 Processor Init Register 2-71

MPC Slave Address (3) Register 2-40

```

IPI Vector/Priority Registers 2-72

Spurious Vector Register 2-73

Timer Frequency Register 2-73

Timer Current Count Registers 2-74

Timer Basecount Registers 2-74

Timer Vector/Priority Registers 2-75

Timer Destination Registers 2-76

External Source Vector/Priority Registers 2-77

External Source Destination Registers 2-78

Raven-Detected Errors Vector/Priority Register 2-79

Raven-Detected Errors Destination Register 2-80

Interprocessor Interrupt Dispatch Registers 2-80

Interrupt Task Priority Registers 2-81

Interrupt Acknowledge Registers 2-82

End-of-Interrupt Registers 2-82

Programming Notes 2-83

External Interrupt Service 2-83

Reset State 2-84

Operation 2-85

Interprocessor Interrupts 2-85

Dynamically Changing I/O Interrupt Configuration 2-85

EOI Register 2-86

Interrupt Acknowledge Register 2-86

8259 Mode 2-86

Current Task Priority Level 2-86

Architectural Notes 2-87

Introduction 3-1

Overview 3-1

Bit Ordering Convention 3-1

Features 3-1

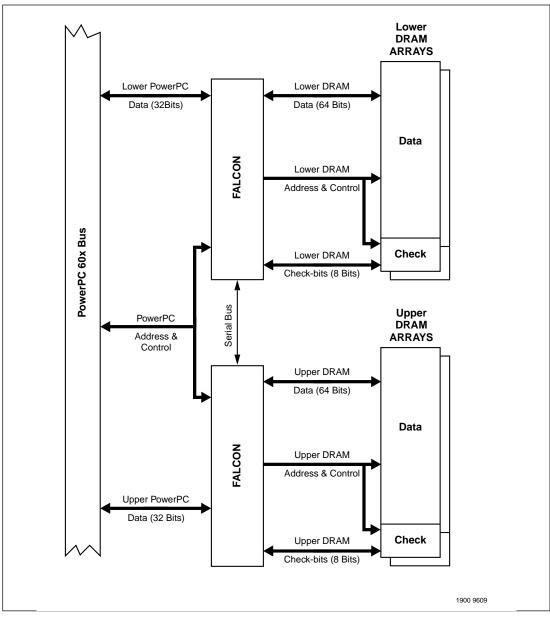

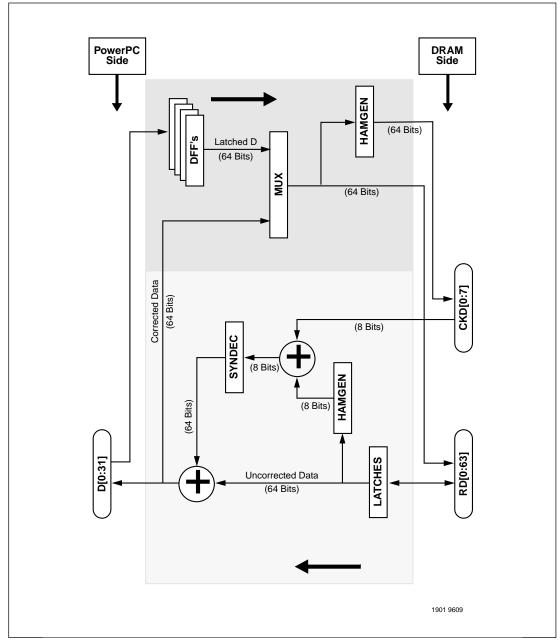

Block Diagrams 3-2

Functional Description 3-6

Performance 3-6

Four-beat Reads/Writes 3-6

Single-beat Reads/Writes 3-7

DRAM Speeds 3-7

ROM/Flash Speeds 3-11

PowerPC 60x Bus Interface 3-12

Responding to Address Transfers 3-12

Completing Data Transfers 3-12

Cache Coherency 3-12

```

```

Cache Coherency Restrictions 3-13

L2 Cache Support 3-13

ECC 3-13

Cycle Types 3-13

Error Reporting 3-14

Error Logging 3-15

DRAM Tester 3-15

ROM/Flash Interface 3-16

Refresh/Scrub 3-20

Blocks A and/or B Present, Blocks C and D Not Present 3-20

Blocks A and/or B Present, Blocks C and/or D present 3-21

DRAM Arbitration 3-22

Chip Defaults 3-22

External Register Set 3-23

CSR Accesses 3-23

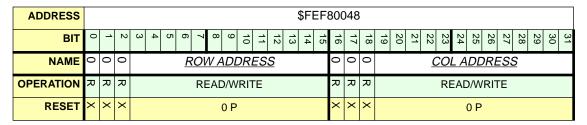

Programming Model 3-24

CSR Architecture 3-24

Register Summary 3-29

Detailed Register Bit Descriptions 3-32

Vendor/Device Register 3-33

Revision ID/ General Control Register 3-33

DRAM Attributes Register 3-35

DRAM Base Register 3-37

CLK Frequency Register 3-37

ECC Control Register 3-38

Error Logger Register 3-41

Error_Address Register 3-43

Scrub/Refresh Register 3-43

Refresh/Scrub Address Register 3-44

ROM A Base/Size Register 3-45

ROM B Base/Size Register 3-48

DRAM Tester Control Registers 3-51

32-Bit Counter 3-51

Test SRAM 3-52

Power-Up Reset Status Register 1 3-53

Power-Up Reset Status Register 2 3-53

External Register Set 3-54

Software Considerations 3-55

Parity Checking on the PowerPC Bus 3-55

Programming ROM/Flash Devices 3-55

Writing to the Control Registers 3-55

```

```

Sizing DRAM 3-56

ECC Codes 3-59

Data Paths 3-61

General Information 4-1

Introduction 4-1

Product Overview - Features 4-1

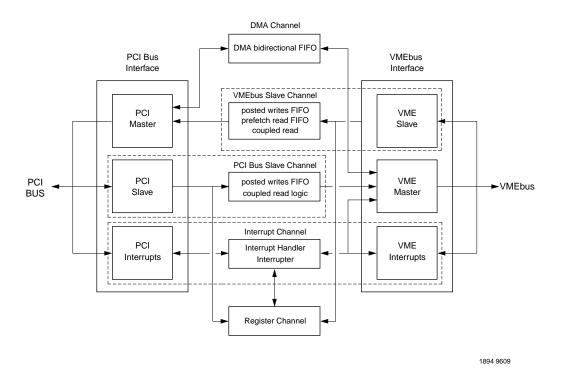

Functional Description 4-2

Architectural Overview 4-2

VMEbus Interface 4-4

PCI Bus Interface 4-5

Interrupter and Interrupt Handler 4-6

DMA Controller 4-7

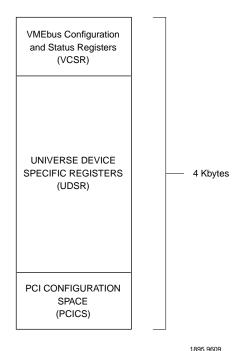

Registers - Universe Control and Status Registers (UCSR) 4-8

Universe Register Map 4-9

Universe Chip Problems after a PCI Reset 4-14

Problem Description 4-14

Examples 4-16

Example 1: MVME2600 Series Board Exhibits Problem 4-16

Example 2: MVME3600 Series Board Acts Differently 4-17

Example 3: Universe Chip is Checked at Tundra 4-19

Introduction 5-1

PCI Arbitration 5-1

Interrupt Handling 5-2

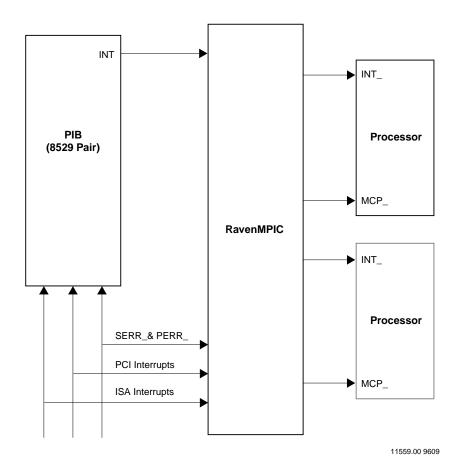

RavenMPIC 5-3

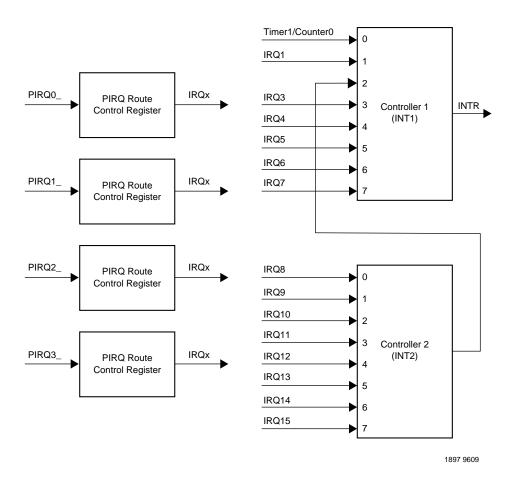

8259 Interrupts 5-4

ISA DMA Channels 5-7

Exceptions 5-8

Sources of Reset 5-8

Soft Reset 5-9

Universe Chip Problems after a PCI Reset 5-9

Error Notification and Handling 5-10

Endian Issues 5-11

Processor/Memory Domain 5-14

Raven's Involvement 5-14

PCI Domain 5-14

PCI-SCSI 5-14

PCI-Ethernet 5-15

PCI-Graphics 5-15

Universe's Involvement 5-15

VMEbus Domain 5-15

ROM/Flash Initialization 5-16

```

Motorola Computer Group Documents A-1 Manufacturers' Documents A-2 Related Specifications A-7 Abbreviations, Acronyms, and Terms to Know GL-1

# **List of Figures**

MVME2600 Series System Block Diagram 1-5

VMEbus Master Mapping 1-21

VMEbus Slave Mapping 1-23

Raven Block Diagram 2-4

PCI Spread I/O Cycle Mapping 2-15

Big to Little Endian Data Swap 2-18

RavenMPIC Block Diagram 2-60

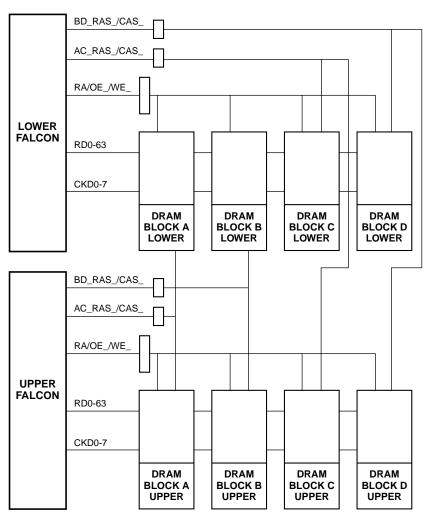

Falcon Pair Used with DRAM in a System 3-3

Falcon Internal Data Paths (Simplified) 3-4

Overall DRAM Connections 3-5

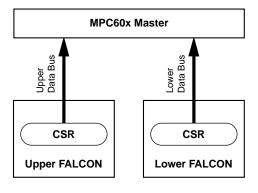

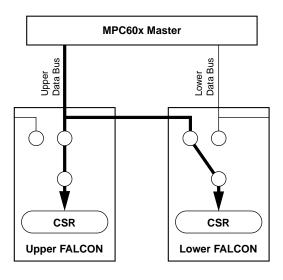

Data Path for Reads from the Falcon Internal CSRs 3-24

Data Path for Writes to the Falcon Internal CSRs 3-25

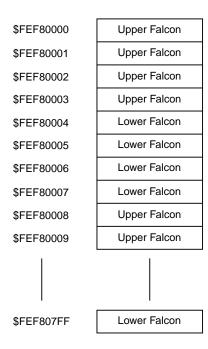

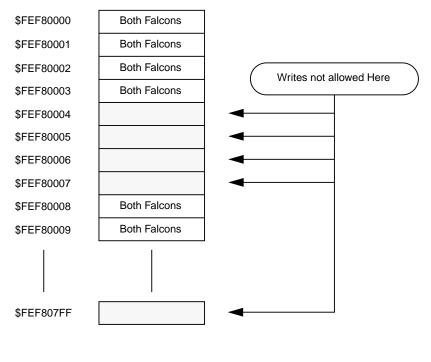

Memory Map for Byte Reads to the CSR 3-26

Memory Map for Byte Writes to the Internal Register Set and Test SRAM 3-27

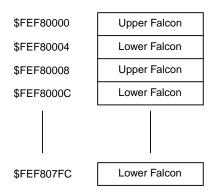

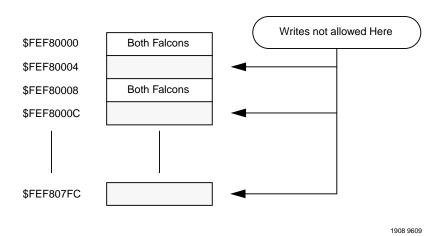

Memory Map for 4-Byte Reads to the CSR 3-28

Memory Map for 4-Byte Writes to the Internal Register Set and Test SRAM 3-28

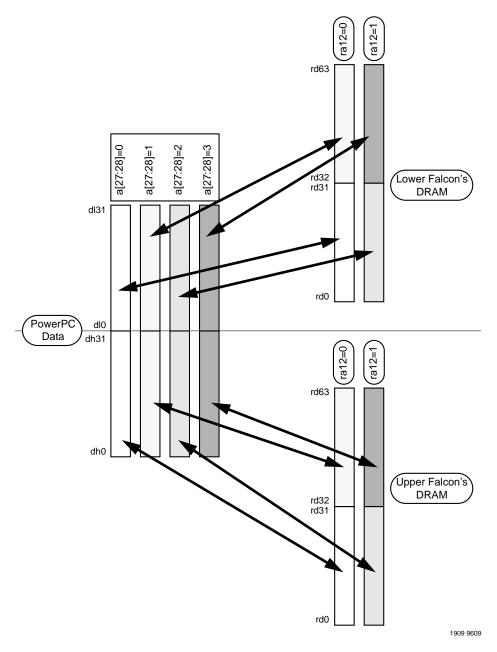

PowerPC Data to DRAM Data Correspondence 3-62

Architectural Diagram for the Universe 4-3

UCSR Access Mechanisms 4-8

MVME2600 Series Interrupt Architecture 5-2

PIB Interrupt Handler Block Diagram 5-5

Big-Endian Mode 5-12

Little-Endian Mode 5-13

# **List of Tables**

MVME2600 Series Features Summary 1-3

Default Processor Memory Map 1-8

CHRP Memory Map Example 1-9

Raven MPC Register Values for CHRP Memory Map 1-10

PREP Memory Map Example 1-11

Raven MPC Register Values for PREP Memory Map 1-12

PCI CHRP Memory Map 1-13

Raven PCI Register Values for CHRP Memory Map 1-15

Universe PCI Register Values for CHRP Memory Map 1-15

PCI PREP Memory Map 1-17

Raven PCI Register Values for PREP Memory Map 1-18

Universe PCI Register Values for PREP Memory Map 1-19

Universe PCI Register Values for VMEbus Slave Map Example 1-24

VMEbus Slave Map Example 1-25

System Register Summary 1-26

Strap Pins Configuration for the PC87308VUL 1-33

MK48T59/559 Access Registers 1-34

Module Configuration and Status Registers 1-35

VME Registers 1-39

Z8536/Z85230 Access Registers 1-44

Z8536 CIO Port Pins Assignment 1-45

Interpretation of MID3-MID0 1-47

PIB DMA Channel Assignments 1-48

CHRP Compliant Memory Map 2-7

MPC Transfer Types 2-10

PCI Command Codes 2-13

Address Modification for Little Endian Transfers 2-19

Raven MPC Register Map 2-23

Raven PCI Configuration Register Map 2-44

Raven PCI I/O Register Map 2-44

RavenMPIC Register Map 2-65

PowerPC 60x Bus to DRAM Access Timing When Configured for

70ns Page Devices 3-8

PowerPC 60x Bus to DRAM Access Timing When Configured for 60ns Page Devices. 3-9

PowerPC 60x Bus to DRAM Access Timing When Configured for 50ns Hyper Devices 3-10

PowerPC 60x Bus to ROM/Flash Access Timing When Configured for 32/64-bit Devices 3-11

PowerPC 60x Bus to ROM/Flash Access Timing When Configured for 8-bit Devices 3-11

**Error Reporting 3-14**

PowerPC 60x to ROM/Flash Address Mapping with Two 8-bit Devices 3-18 PowerPC 60x Address to ROM/Flash Address Mapping with Two 32-bit or One

64-bit Device(s) 3-19

Register Summary 3-30

ram spd1,ram spd0 and DRAM Type 3-34

Block\_A/B/C/D Configurations 3-36

rtest encodings 3-44

ROM Block A Size Encoding 3-46

rom\_a\_rv and rom\_b\_rv encoding 3-47

Read/Write to ROM/Flash 3-48

ROM Block B Size Encoding 3-50

Sizing Addresses 3-57

PowerPC 60x Address to DRAM Address Mappings 3-58

Syndrome Codes Ordered by Bit in Error 3-59

Single-Bit Errors Ordered by Syndrome Code 3-60

PowerPC Data to DRAM Data Mapping 3-63

Universe Register Map 4-9

PCI Arbitration Assignments 5-1

RavenMPIC Interrupt Assignments 5-3

PIB PCI/ISA Interrupt Assignments 5-6

Reset Sources and Devices Affected 5-9

Error Notification and Handling 5-10

ROM/FLASH Bank Default 5-16

# 1

# Introduction

This manual provides programming information for the MVME2603 and MVME2604 Single Board Computers (SBCs), that are based on the MVME260*x*-*xxxx* base board and the RAM200 mezzanine modules. Extensive programming information is provided for several Application-Specific Integrated Circuit (ASIC) devices used on the boards. Reference information is included in Appendix A for the Large Scale Integration (LSI) devices used on the boards and sources for additional information are listed.

This chapter briefly describes the board level hardware features of the MVME2600 series Single Board Computers. The chapter begins with a board level overview and features list. Memory maps are next, and are the major feature of this chapter.

Programmable registers in the MVME2600 series that reside in ASICs are covered in the chapters on those ASICs. Chapter 2 covers the Raven chip, Chapter 3 covers the Falcon chip set, Chapter 4 covers the Universe chip, and Chapter 5 covers certain programming features, such as interrupts and exceptions. Appendix A lists all related documentation.

# Manual Terminology

Throughout this manual, a convention is used which precedes data and address parameters by a character identifying the numeric format as follows:

\$ dollar specifies a hexadecimal character

% percent specifies a binary number

& ampersand specifies a decimal number

For example, "12" is the decimal number twelve, and "\$12" is the decimal number eighteen.

1-1

Unless otherwise specified, all address references are in hexadecimal.

An asterisk (\*) following the signal name for signals which are *level* significant denotes that the signal is *true* or valid when the signal is low.

An asterisk (\*) following the signal name for signals which are *edge significant* denotes that the actions initiated by that signal occur on high to low transition.

**Note** In some places in this document, an underscore (\_) following the signal name is used to indicate an active low signal.

In this manual, assertion and negation are used to specify forcing a signal to a particular state. In particular, assertion and assert refer to a signal that is active or true; negation and negate indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

Data and address sizes for MPC60x chips are defined as follows:

- □ A *byte* is eight bits, numbered 0 through 7, with bit 0 being the least significant.

- □ A *half-word* is 16 bits, numbered 0 through 15, with bit 0 being the least significant.

- □ A *word* or *single word* is 32 bits, numbered 0 through 31, with bit 0 being the least significant.

- □ A *double word* is 64 bits, numbered 0 through 63, with bit 0 being the least significant.

Refer to Chapter 5 for *Endian Issues*, which covers which parts of the MVME2600 series use *big-endian* byte ordering, and which use *small-endian* byte ordering.

The terms *control bit* and *status bit* are used extensively in this document. The term control bit is used to describe a bit in a register that can be set and cleared under software control. The term *true* is

used to indicate that a bit is in the state that enables the function it controls. The term *false* is used to indicate that the bit is in the state that disables the function it controls. In all tables, the terms 0 and 1 are used to describe the actual value that should be written to the bit, or the value that it yields when read. The term *status bit* is used to describe a bit in a register that reflects a specific condition. The status bit can be read by software to determine operational or exception conditions.

# **Overview**

The MVME2600 series SBC family, hereafter sometimes referred to simply as the MVME2600 or the V2600 series, provides many standard features required by a computer system: SCSI, Ethernet interface, keyboard interface, mouse interface, sync and async serial ports, parallel port, boot Flash, and up to 256MB of ECC DRAM.

# **Feature Summary**

There are many models based on the MVME2600 series architecture. The following table summarizes the major features of the MVME2600 series:

Table 1-1. MVME2600 Series Features Summary

| Feature    | Description                                                                                    |

|------------|------------------------------------------------------------------------------------------------|

| Processors | Single Supports BGA processors only: MPC603, MPC604. Bus Clock Frequencies up to 66MHz         |

| L2 Cache   | Build-option for 256KB Look-aside L2 Cache                                                     |

| Flash      | 4MB or 8MB (64-bit wide), with socketed 1MB (16-bit wide)                                      |

| DRAM       | 16MB to 256MB, ECC Protected (Single-bit Correction, Double-bit Detection) Two-way Interleaved |

| NVRAM      | 8KB                                                                                            |

Table 1-1. MVME2600 Series Features Summary (Continued)

| Feature               | Description                                                                                                                                                                                                                                                                              |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTC                   | MK48T59/559 Device                                                                                                                                                                                                                                                                       |

| Peripheral<br>Support | Two async serial ports Two sync/async serial ports One (IEEE1284, or printer) Parallel Port 8-bit or 16-bit single-ended SCSI interface AUI or 10Base-T/100Base-TX Ethernet interface NO Graphics Interface on MVME2600 series One PS/2 Keyboard and one PS/2 Mouse One PS/2 Floppy Port |

| VME Interface         | 32-bit Address/64-bit Data PCI A32/A24/A16, D64 (MBLT)/D32/D16/D08 Master and Slave Programmable Interrupter & Interrupt Handler Full System Controller Functions Programmable DMA Controller with link list support Location Monitor                                                    |

| PMC Slots             | One 32/64-bit Slot                                                                                                                                                                                                                                                                       |

| Miscellaneous         | RESET/ABORT Switch<br>Status LEDs                                                                                                                                                                                                                                                        |

# **System Block Diagram**

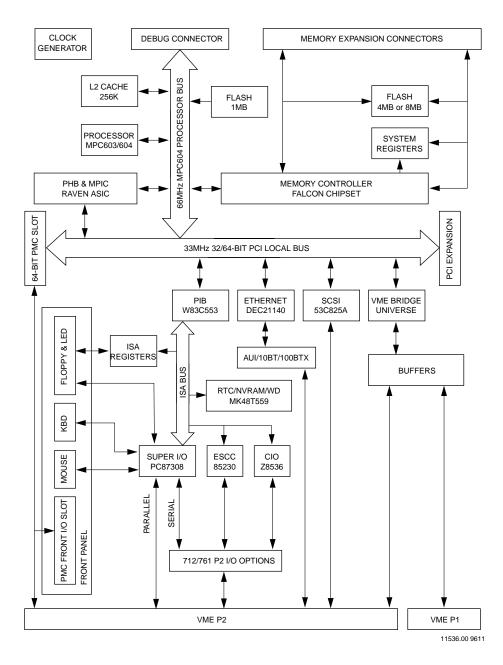

The MVME2600 series provides the 256KB look-aside external cache option. The Falcon chip set controls the boot Flash and the ECC DRAM. The Raven ASIC functions as the 64-bit PCI host bridge and the MPIC interrupt controller. PCI devices include: SCSI, VME, Ethernet, and one PMC slot. Standard I/O functions are provided by the Super I/O device which resides on the ISA bus. The NVRAM/RTC and the optional synchronous serial ports also reside on the ISA bus. The general system block diagram for MVME2600 series is shown below:

Figure 1-1. MVME2600 Series System Block Diagram

# **Functional Description**

### Overview

The MVME2600 series is a family of single-slot SBCs. It consists of the MPC603/604 processor, the Raven PCI Bridge & Interrupt Controller, the ECC Memory Controller Falcon chipset, 5MB or 9MB of Flash memory, 16MB to 256MB of ECC-protected DRAM, and a rich set of features of I/O peripherals.

I/O peripheral devices on the PCI bus are: SCSI chip, Ethernet chip, Universe VMEbus interface ASIC, and one PMC slot. Functions provided from the ISA bus are: a P1284/Parallel port, two asynchronous serial ports, two sync/async serial ports, a real-time clock, and counters/timers.

The MVME2600 series board interfaces to the VMEbus via the P1 and P2 connectors, which use the new 5-row 160-pin connectors as specified in the proposed VME64 Extension Standard. It also draws +5V, +12V, and -12V power from the VMEbus backplane through these two connectors. 3.3V supply is regulated onboard from the +5V power.

Front panel connectors on the MVME2600 series board include: a 6-pin circular DIN connector for the keyboard interface, a 6-pin circular DIN connector for the mouse interface, and a 50-pin connector for the floppy and status LEDs. All signals for the serial ports, the P1284/Printer port, the SCSI interface, and the Ethernet interface are routed to P2.

There are two P2 I/O options supported by the MVME2600 series: the MVME712M mode and the MVME761 mode. The MVME761 mode provides the enhanced P1284 parallel port interface and the full synchronous support for Serial Ports 3 and 4. The MVME712M version provides backward compatibility with previous SBCs. In either mode, 16-bit SCSI capability can only be used by systems with 5-row DIN support because the additional 8 bits of SCSI data lines reside on row Z of P2.

The MVME2600 series contains one IEEE1386.1 PCI Mezzanine Card (PMC) slot. This PMC slot is 64-bit capable and supports both front and rear I/O. Pins 1 through 30 of the PMC connector J14 are routed to pins D1 through D30 of the 5-row DIN P2 connector. J14 pin 31 is connected to P2 pin Z29, and J14 pin 32 is connected to P2 pin Z31.

Additional PCI expansion is supported with a 114-pin Mictor connector. This connection allows stacking of a carrier board to increase the I/O capability, such as a dual-PMC carrier board.

# **Programming Model**

# **Memory Maps**

The following sections describe the memory maps for the MVME2600 series.

### **Processor Memory Maps**

The Processor memory map is controlled by the Raven ASIC and the Falcon chipset. The Raven ASIC and the Falcon chipset have flexible programming Map Decoder registers to customize the system to fit many different applications.

### **Default Processor Memory Map**

After a reset, the Raven ASIC and the Falcon chipset provide the default processor memory map as shown in the following table.

Table 1-2. Default Processor Memory Map

| Processor Address |           | Size               | Definition                 | Z     |

|-------------------|-----------|--------------------|----------------------------|-------|

| Start             | End       | Size               | Deminion                   | Notes |

| 0000 0000         | 7FFF FFFF | 2G                 | Not mapped                 |       |

| 8000 0000         | 8001 FFFF | 128K               | PCI/ISA I/O Space          | 1     |

| 8002 0000         | FEF7 FFFF | 2G - 16M<br>- 640K | Not mapped                 |       |

| FEF8 0000         | FEF8 FFFF | 64K                | Falcon Registers           |       |

| FEF9 0000         | FEFE FFFF | 384K               | Not mapped                 |       |

| FEFF 0000         | FEFF FFFF | 64K                | Raven Registers            |       |

| FF00 0000         | FFEF FFFF | 15M                | Not mapped                 |       |

| FFF0 0000         | FFFF FFFF | 1M                 | ROM/FLASH Bank A or Bank B | 2     |

### Notes:

- This default map for PCI/ISA I/O space allows software to determine if the system is MPC105-based or Falcon/Ravenbased by examining either the PHB Device ID or the CPU Type Register.

- The first one Mbyte of ROM/FLASH Bank A appears at this range after a reset if the *rom\_b\_rv* control bit is cleared. If the *rom\_b\_rv* control bit is set then this address range maps to ROM/FLASH Bank B.

### **Processor CHRP Memory Map**

The following table shows a recommended CHRP memory map from the point of view of the processor.

Table 1-3. CHRP Memory Map Example

| Processor Address |           | Size Definition |                                                                 | Notes |

|-------------------|-----------|-----------------|-----------------------------------------------------------------|-------|

| Start             | End       | Size            | Demitton                                                        |       |

| 0000 0000         | top_dram  | dram_size       | System Memory (onboard DRAM)                                    | 1, 2  |

| 4000 0000         | FCFF FFFF | 3G - 48M        | 3G - 48M PCI Memory Space:<br>4000 0000 to FCFF FFFF            |       |

| FD00 0000         | FDFF FFFF | 16M             | Zero-Based PCI/ISA Memory Space (mapped to 00000000 to 00FFFFF) | 3,8   |

| FE00 0000         | FE7F FFFF | 8M              | Zero-Based PCI/ISA I/O Space (mapped to 00000000 to 007FFFFF)   | 3,5,8 |

| FE80 0000         | FEF7 FFFF | 7.5M            | Reserved                                                        |       |

| FEF8 0000         | FEF8 FFFF | 64K             | Falcon Registers                                                |       |

| FEF9 0000         | FEFE FFFF | 384K            | Reserved                                                        |       |

| FEFF 0000         | FEFF FFFF | 64K             | Raven Registers                                                 | 9     |

| FF00 0000         | FF7F FFFF | 8M              | ROM/FLASH Bank A                                                | 1,7   |

| FF80 0000         | FF8F FFFF | 1M              | ROM/FLASH Bank B                                                | 1,7   |

| FF50 0000         | FFEF FFFF | 6M              | Reserved                                                        |       |

| FFF0 0000         | FFFF FFFF | 1M              | ROM/FLASH Bank A or Bank B                                      | 7     |

### Notes:

- 1. Programmable via Falcon chipset.

- 2. To enable the "Processor-hole" area, program the Falcon chipset to ignore 0x000A0000 0x000BFFFF address range and program the Raven to map this address range to PCI memory space.

- 3. Programmable via Raven ASIC.

- 4. CHRP requires the starting address for the PCI memory space to be 256MB-aligned.

- 5. Programmable via Raven ASIC for either contiguous or spread-I/O mode.

- 6. The actual size of each ROM/FLASH bank may vary.

- 7. The first one Mbyte of ROM/FLASH Bank A appears at this range after a reset if the *rom\_b\_rv* control bit is cleared. If the *rom\_b\_rv* control bit is set then this address range maps to ROM/FLASH Bank B.

- 8. This range can be mapped to the VMEbus by programming the Universe ASIC accordingly. The map shown is the recommended setting which uses the Special PCI Slave Image and two of the four programmable PCI Slave Images.

- 9. The only method to generate a PCI Interrupt Acknowledge cycle (8259 IACK) is to perform a read access to the Raven's PIACK register at 0xFEFF0030.

The following table shows the programmed values for the associated Raven MPC registers for the processor CHRP memory map.

Table 1-4. Raven MPC Register Values for CHRP Memory Map

| Address   | Register Name   | Register Value |

|-----------|-----------------|----------------|

| FEFF 0040 | MSADD0          | 4000 FCFF      |

| FEFF 0044 | MSOFF0 & MSATT0 | 0000 00C2      |

| FEFF 0048 | MSADD1          | FD00 FDFF      |

| FEFF 004C | MSOFF1 & MSATT1 | 0300 00C2      |

| FEFF 0050 | MSADD2          | 0000 0000      |

| FEFF 0054 | MSOFF2 & MSATT2 | 0000 0002      |

| FEFF 0058 | MSADD3          | FE00 FE7F      |

| FEFF 005C | MSOFF3 & MSATT3 | 0200 00C0      |

### **Processor PREP Memory Map**

The Raven/Falcon chipset can be programmed for PREP-compatible memory map. The following table shows the PREP memory map of the MVME2600 series from the point of view of the processor.

**Table 1-5. PREP Memory Map Example**

| Processor Address |           | Size Definition |                                                        | Notes |

|-------------------|-----------|-----------------|--------------------------------------------------------|-------|

| Start             | End       | Size            | Demnition                                              |       |

| 0000 0000         | top_dram  | dram_size       | System Memory (onboard DRAM)                           | 1     |

| 8000 0000         | BFFF FFFF | 1G              | 1G Zero-Based PCI I/O Space:<br>0000 0000 - 3FFFF FFFF |       |

| C000 0000         | FCFF FFFF | 1G - 48M        | Zero-Based PCI/ISA Memory Space: 0000 0000 - 3CFFFFFF  | 2, 5  |

| FD00 0000         | FEF7 FFFF | 40.5M           | Reserved                                               |       |

| FEF8 0000         | FEF8 FFFF | 64K             | Falcon Registers                                       |       |

| FEF9 0000         | FEFE FFFF | 384K            | 384K Reserved                                          |       |

| FEFF 0000         | FEFF FFFF | 64K             | Raven Registers                                        | 6     |

| FF00 0000         | FF7F FFFF | 8M              | ROM/FLASH Bank A                                       | 1, 3  |

| FF80 0000         | FF8F FFFF | 1M              | ROM/FLASH Bank B                                       | 1, 3  |

| FF90 0000         | FFEF FFFF | 6M              | Reserved                                               |       |

| FFF0 0000         | FFFF FFFF | 1M              | ROM/FLASH Bank A or Bank B                             | 4     |

#### Notes:

- 1. Programmable via Falcon chipset.

- 2. Programmable via Raven ASIC.

- 3. The actual size of each ROM/FLASH bank may vary.

- 4. The first 1 Mbyte of ROM/FLASH Bank A appears at this range after a reset if the *rom\_b\_rv* control bit is cleared. If the

*rom\_b\_rv* control bit is set then this address range maps to ROM/FLASH Bank B.

- 5. This range can be mapped to the VMEbus by programming the Universe ASIC accordingly.

- 6. The only method to generate a PCI Interrupt Acknowledge cycle (8259 IACK) is to perform a read access to the Raven's PIACK register at 0xFEFF0030.

The following table shows the programmed values for the associated Raven MPC registers for the processor PREP memory map.

Table 1-6. Raven MPC Register Values for PREP Memory Map

| Address   | Register Name   | Register Value |

|-----------|-----------------|----------------|

| FEFF 0040 | MSADD0          | C000 FCFF      |

| FEFF 0044 | MSOFF0 & MSATT0 | 4000 00C2      |

| FEFF 0048 | MSADD1          | 0000 0000      |

| FEFF 004C | MSOFF1 & MSATT1 | 0000 0002      |

| FEFF 0050 | MSADD2          | 0000 0000      |

| FEFF 0054 | MSOFF2 & MSATT2 | 0000 0002      |

| FEFF 0058 | MSADD3          | 8000 BFFF      |

| FEFF 005C | MSOFF3 & MSATT3 | 8000 00C0      |

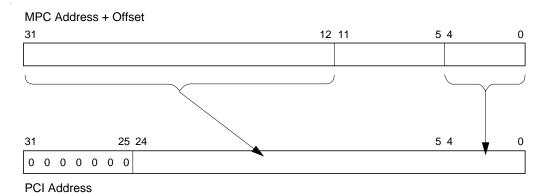

### **PCI Configuration Access**

PCI Configuration accesses are accomplished via the CONFIG\_ADD and CONFIG\_DAT registers. These two registers are implemented by the Raven ASIC. In the CHRP memory map example, the CONFIG\_ADD and CONFIG\_DAT registers are located at 0xFE000CF8 and 0xFE000CFC, respectively. With the PREP memory map, the CONFIG\_ADD register and the CONFIG\_DAT register are located at 0x80000CF8 and 0x80000CFC, respectively.

### **PCI Memory Maps**

The PCI memory map is controlled by the Raven ASIC and the Universe ASIC. The Raven ASIC and the Universe ASIC have flexible programming Map Decoder registers to customize the system to fit many different applications.

### **Default PCI Memory Map**

After a reset, the Raven ASIC and the Universe ASIC turn all the PCI slave map decoders off. Software must program the appropriate map decoders for a specific environment.

# PCI CHRP Memory Map

The following table shows a PCI memory map of the MVME2600 series that is CHRP-compatible from the point of view of the PCI local bus.

Table 1-7. PCI CHRP Memory Map

| PCI Address |           | Size Definition | Notes                          |       |

|-------------|-----------|-----------------|--------------------------------|-------|

| Start       | End       | Size Definition |                                | rotes |

| 0000 0000   | top_dram  | dram_size       | Onboard ECC DRAM               | 1     |

| 4000 0000   | EFFF FFFF | 3G - 256M       | VMEbus A32/D32 (Super/Program) | 3     |

| F000 0000   | F7FF FFFF | 128M            | VMEbus A32/D16 (Super/Program) | 3     |

| F800 0000   | F8FE FFFF | 16M - 64K       | VMEbus A24/D16 (Super/Program) | 4     |

| F8FF 0000   | F8FF FFFF | 64K             | VMEbus A16/D16 (Super/Program) | 4     |

| F900 0000   | F9FE FFFF | 16M - 64K       | VMEbus A24/D32 (Super/Data)    | 4     |

| F9FF 0000   | F9FF FFFF | 64K             | VMEbus A16/D32 (Super/Data)    | 4     |

| FA00 0000   | FAFE FFFF | 16M - 64K       | VMEbus A24/D16 (User/Program)  | 4     |

| FAFF 0000   | FAFF FFFF | 64K             | VMEbus A16/D16 (User/Program)  | 4     |

| FB00 0000   | FBFE FFFF | 16M - 64K       | VMEbus A24/D32 (User/Data)     | 4     |

| FBFF 0000   | FBFF FFFF | 64K             | VMEbus A16/D32 (User/Data)     | 4     |

**Table 1-7. PCI CHRP Memory Map (Continued)**

| PCI A     | PCI Address |            | - Size Definition                                                                    |       | Cina Definition |  | Sina Definition D | Notes |

|-----------|-------------|------------|--------------------------------------------------------------------------------------|-------|-----------------|--|-------------------|-------|

| Start     | End         | Size       | Delinition                                                                           | Notes |                 |  |                   |       |

| FC00 0000 | FC03 FFFF   | 256K       | RavenMPIC                                                                            | 1     |                 |  |                   |       |

| FC04 0000 | FCFF FFFF   | 16M - 256K | PCI Memory Space                                                                     |       |                 |  |                   |       |

| FD00 0000 | FDFF FFFF   | 16M        | PCI Memory Space or<br>System Memory Alias Space<br>(mapped to 00000000 to 00FFFFFF) | 1     |                 |  |                   |       |

| FE00 0000 | FFFF FFFF   | 48M        | Reserved                                                                             |       |                 |  |                   |       |

### Notes:

- 1. Programmable via the Raven's PCI Configuration registers.

- 2. To enabled the CHRP "io-hole", program the Raven to ignore the 0x000A0000 0x000FFFFF address range.

- 3. Programmable mapping via the four PCI Slave Images in the Universe ASIC.

- 4. Programmable mapping via the Special Slave Image (SLSI) in the Universe ASIC.

The following table shows the programmed values for the associated Raven PCI registers for the PCI CHRP memory map.

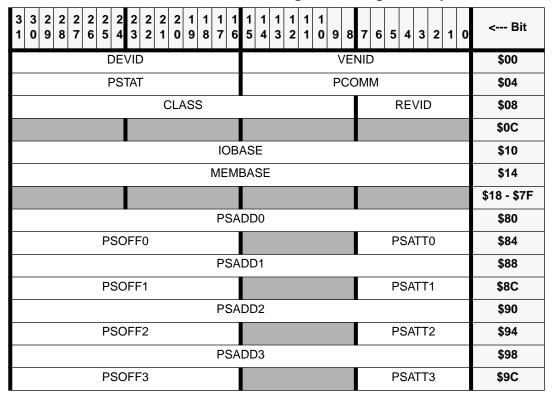

Table 1-8. Raven PCI Register Values for CHRP Memory Map

| Configuration<br>Address<br>Offset | Configuration<br>Register Name | Register Value<br>(Aliasing OFF) | Register Value<br>(Aliasing ON) |

|------------------------------------|--------------------------------|----------------------------------|---------------------------------|

| \$14                               | RavenMPIC MBASE                | FC00 0000                        | FC00 0000                       |

| \$80                               | PSADD0                         | 0000 3FFF                        | 0100 3FFF                       |

| \$84                               | PSOFF0 & PSATT0                | 0000 00FX                        | 0000 00FX                       |

| \$88                               | PSADD1                         | 0000 0000                        | FD00 FDFF                       |

| \$8C                               | PSOFF1 & PSATT1                | 0000 0000                        | 0000 00FX                       |

| \$90                               | PSADD2                         | 0000 0000                        | 0000 0000                       |

| \$94                               | PSOFF2 & PSATT2                | 0000 0000                        | 0000 0000                       |

| \$98                               | PSADD3                         | 0000 0000                        | 0000 0000                       |

| \$9C                               | PSOFF3 & PSATT3                | 0000 0000                        | 0000 0000                       |

The next table shows the programmed values for the associated Universe PCI registers for the PCI CHRP memory map.

Table 1-9. Universe PCI Register Values for CHRP Memory Map

| Configuration<br>Address<br>Offset | Configuration<br>Register Name | Register Value |

|------------------------------------|--------------------------------|----------------|

| \$100                              | LSI0_CTL                       | C082 5100      |

| \$104                              | LSI0_BS                        | 4000 0000      |

| \$108                              | LSI0_BD                        | F000 0000      |

| \$10C                              | LSI0_TO                        | XXXX 0000      |

| \$114                              | LSI1_CTL                       | C042 5100      |

| \$118                              | LSI1_BS                        | F000 0000      |

Table 1-9. Universe PCI Register Values for CHRP Memory Map (Continued)

| Configuration<br>Address<br>Offset | Configuration<br>Register Name | Register Value |

|------------------------------------|--------------------------------|----------------|

| \$11C                              | LSI1_BD                        | F800 0000      |

| \$120                              | LSI1_TO                        | XXXX 0000      |

| \$128                              | LSI2_CTL                       | 0000 0000      |

| \$12C                              | LSI2_BS                        | XXXX XXXX      |

| \$130                              | LSI2_BD                        | XXXX XXXX      |

| \$134                              | LSI2_TO                        | XXXX XXXX      |

| \$13C                              | LSI3_CTL                       | 0000 0000      |

| \$140                              | LSI3_BS                        | XXXX XXXX      |

| \$144                              | LSI3_BD                        | XXXX XXXX      |

| \$148                              | LSI3_TO                        | XXXX XXXX      |

| \$188                              | SLSI                           | C0A053F8       |

### **PCI PREP Memory Map**

The following table shows a PCI memory map of the MVME2600 series that is PREP-compatible from the point of view of the PCI local bus.

Table 1-10. PCI PREP Memory Map

| PCI Address |           | G:         | D (1.11)                       | Natas |

|-------------|-----------|------------|--------------------------------|-------|

| Start       | End       | Size       | Definition                     | Notes |

| 0000 0000   | 00FF FFFF | 16M        | PCI/ISA Memory Space           |       |

| 0100 0000   | 2FFF FFFF | 752M       | VMEbus A32/D32 (Super/Program) | 3     |

| 3000 0000   | 37FF FFFF | 128M       | VMEbus A32/D16 (Super/Program) | 3     |

| 3800 0000   | 38FE FFFF | 16M - 64K  | VMEbus A24/D16 (Super/Program) | 4     |

| 38FF 0000   | 38FF FFFF | 64K        | VMEbus A16/D16 (Super/Program) | 4     |

| 3900 0000   | 39FE FFFF | 16M - 64K  | VMEbus A24/D32 (Super/Data)    | 4     |

| 39FF 0000   | 39FF FFFF | 64K        | VMEbus A16/D32 (Super/Data)    | 4     |

| 3A00 0000   | 3AFE FFFF | 16M - 64K  | VMEbus A24/D16 (User/Program)  | 4     |

| 3AFF 0000   | 3AFF FFFF | 64K        | VMEbus A16/D26 (User/Program)  | 4     |

| 3B00 0000   | 3BFE FFFF | 16M - 64K  | VMEbus A24/D32 (User/Data)     | 4     |

| 3BFF 0000   | 3BFF FFFF | 64K        | VMEbus A16/D32 (User/Data)     | 4     |

| 3C00 0000   | 7FFF FFFF | 1G + 64M   | PCI Memory Space               |       |

| 8000 0000   | FBFF FFFF | 2G - 64M   | Onboard ECC DRAM               | 1     |

| FC00 0000   | FC03 FFFF | 256K       | RavenMPIC                      | 1     |

| FC04 0000   | FFFF FFFF | 64M - 256K | PCI Memory Space               |       |

### Notes:

- 1. Programmable via the Raven's PCI Configuration registers.

- 2. To enabled the CHRP "io-hole", program the Raven to ignore the 0x000A0000 0x000FFFFF address range.

- 3. Programmable mapping via the four PCI Slave Images in the Universe ASIC.

- 4. Programmable mapping via the Special Slave Image (SLSI) in the Universe ASIC.

The following table shows the programmed values for the associated Raven PCI registers for the PREP-compatible memory map.

Table 1-11. Raven PCI Register Values for PREP Memory Map

| Configuration<br>Address<br>Offset | Configuration<br>Register Name | Register Value |

|------------------------------------|--------------------------------|----------------|

| \$14                               | RavenMPIC MBASE                | FC00 0000      |

| \$80                               | PSADD0                         | 8000 FBFF      |

| \$84                               | PSOFF0 & PSATT0                | 8000 00FX      |

| \$88                               | PSADD1                         | 0000 0000      |

| \$8C                               | PSOFF1 & PSATT1                | 0000 0000      |

| \$90                               | PSADD2                         | 0000 0000      |

| \$94                               | PSOFF2 & PSATT2                | 0000 0000      |

| \$98                               | PSADD3                         | 0000 0000      |

| \$9C                               | PSOFF3 & PSATT3                | 0000 0000      |

The next table shows the programmed values for the associated Universe PCI registers for the PCI PREP memory map.

Table 1-12. Universe PCI Register Values for PREP Memory Map

| Configuration<br>Address<br>Offset | Configuration<br>Register Name | Register Value |

|------------------------------------|--------------------------------|----------------|

| \$100                              | LSI0_CTL                       | C082 5100      |

| \$104                              | LSI0_BS                        | 0100 0000      |

| \$108                              | LSI0_BD                        | 3000 0000      |

| \$10C                              | LSI0_TO                        | XXXX 0000      |

| \$114                              | LSI1_CTL                       | C042 5100      |

| \$118                              | LSI1_BS                        | 3000 0000      |

| \$11C                              | LSI1_BD                        | 3800 0000      |

| \$120                              | LSI1_TO                        | XXXX 0000      |

| \$128                              | LSI2_CTL                       | 0000 0000      |

| \$12C                              | LSI2_BS                        | XXXX XXXX      |

| \$130                              | LSI2_BD                        | XXXX XXXX      |

| \$134                              | LSI2_TO                        | XXXX XXXX      |

| \$13C                              | LSI3_CTL                       | 0000 0000      |

| \$140                              | LSI3_BS                        | XXXX XXXX      |

| \$144                              | LSI3_BD                        | XXXX XXXX      |

| \$148                              | LSI3_TO                        | XXXX XXXX      |

| \$188                              | SLSI                           | C0A05338       |

# **VMEbus Mapping**

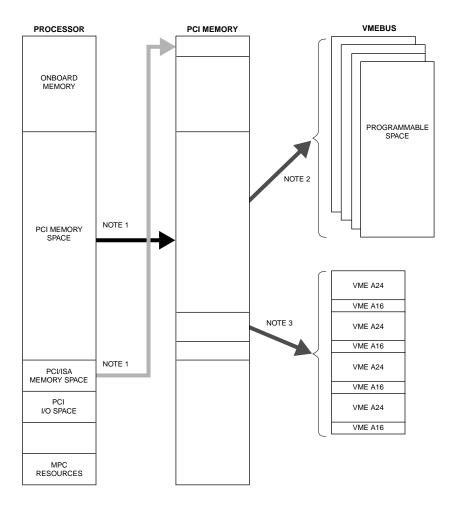

### VMEbus Master Map

The processor can access any address range in the VMEbus with the help from the address translation capabilities of the Universe ASIC. The recommended mapping is shown in the *Processor Memory Map* section. The following figure illustrates how the VMEbus master mapping is accomplished.

11553.00 9609

Figure 1-2. VMEbus Master Mapping

Notes:

1. Programmable mapping done by the Raven ASIC.

- 2. Programmable mapping via the four PCI Slave Images in the Universe ASIC.

- 3. Programmable mapping via the Special Slave Image (SLSI) in the Universe ASIC.

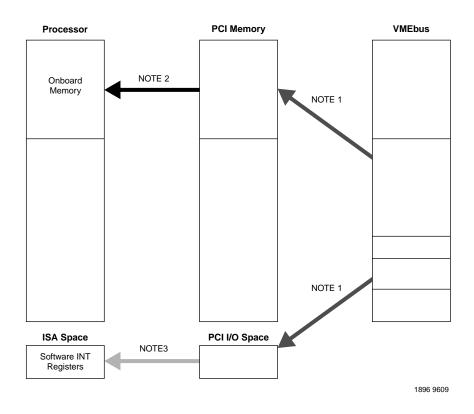

#### VMEbus Slave Map

The four programmable VME Slave Images in the Universe ASIC allow other VMEbus masters to get to any devices on the MVME2600 series. The combination of the four Universe VME Slave Images and the four Raven PCI Slave Decoders offers a lot of flexibility for mapping the system resources as seen from the VMEbus. In most applications, the VMEbus only needs to see the system memory and, perhaps, the software interrupt registers (SIR1 and SIR2 registers). An example of the VMEbus slave map is shown below:

Figure 1-3. VMEbus Slave Mapping

#### Notes:

- 1. Programmable mapping via the four VME Slave Images in the Universe ASIC.

- 2. Programmable mapping via PCI Slave Images in the Raven ASIC.

- 3. Fixed mapping via the PIB device.

The following table shows the programmed values for the associated Universe registers for the VMEbus slave function.

Table 1-13. Universe PCI Register Values for VMEbus Slave Map Example

| Configuration<br>Address<br>Offset | Configuration<br>Register Name | Register Value<br>(CHRP) | Register Value<br>(PREP) |  |  |

|------------------------------------|--------------------------------|--------------------------|--------------------------|--|--|

| \$F00                              | VSI0_CTL                       | C0F2 0001                | C0F2 0001                |  |  |

| \$F04                              | VSI0_BS                        | 4000 0000                | 4000 0000                |  |  |

| \$F08                              | VSI0_BD                        | 4000 1000                | 4000 1000                |  |  |

| \$F0C                              | VSI0_TO                        | C000 1000                | C000 1000                |  |  |

| \$F14                              | VSI1_CTL                       | E0F2 00C0                | E0F2 00C0                |  |  |

| \$F18                              | VSI1_BS                        | 1000 0000                | 1000 0000                |  |  |

| \$F1C                              | VSI1_BD                        | 2000 0000                | 2000 0000                |  |  |

| \$F20                              | VSI1_TO                        | F000 0000                | 7000 0000                |  |  |

| \$F28                              | VSI2_CTL                       | 0000 0000                | 0000 0000                |  |  |

| \$F2C                              | VSI2_BS                        | xxxx xxxx                | XXXX XXXX                |  |  |

| \$F30                              | VSI2_BD                        | XXXX XXXX                | XXXX XXXX                |  |  |

| \$F34                              | VSI2_TO                        | xxxx xxxx                | XXXX XXXX                |  |  |

| \$F3C                              | VSI3_CTL                       | 0000 0000                | 0000 0000                |  |  |

| \$F40                              | VSI3_BS                        | xxxx xxxx                | XXXX XXXX                |  |  |

| \$F44                              | VSI3_BD                        | xxxx xxxx                | XXXX XXXX                |  |  |

| \$F48                              | VSI3_TO                        | xxxx xxxx                | xxxx xxxx                |  |  |

The above register values yield the following VMEbus slave map:

Table 1-14. VMEbus Slave Map Example

| VMEbu                    | s Address                          | Size | CHDD Man                                                         | DDED More                                                        |  |  |  |  |

|--------------------------|------------------------------------|------|------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| Range                    | Mode                               | Size | CHRP Map                                                         | PREP Map                                                         |  |  |  |  |

| 4000 0000 -<br>4000 0FFF | A32 U/S/P/D 4K<br>D08/16/32        |      | PCI/ISA I/O Space:<br>0000 1000 - 0000 1FFF                      | PCI/ISA I/O Space:<br>0000 1000 - 0000 1FFF                      |  |  |  |  |

| 1000 0000 -<br>1FFF FFFF | A32 U/S/P/D<br>D08/16/32/64<br>RMW | 256M | PCI/ISA Memory Space<br>(On-board DRAM)<br>0000 0000 - 0FFF FFFF | PCI/ISA Memory Space<br>(On-board DRAM)<br>8000 0000 - 8FFF FFFF |  |  |  |  |

# **Falcon-Controlled System Registers**

The Falcon chipset latches the states of the DRAM data lines onto the PR\_STAT1 and PR\_STAT2 registers. The MVME2600 series uses these status registers to provide the system configuration information. In addition, the Falcon chipset performs the decode and control for an external register port. This function is utilized by the MVME2600 series to provide the system control registers.

Table 1-15. System Register Summary

| BIT #>   | 0 1 2 3 4 5 6 7                                         | 11<br>10<br>9<br>8 | 13 14 15 12 | 19<br>18<br>17 | 23<br>22<br>21<br>20 | 26<br>25<br>24 | 31<br>30<br>29<br>28 |  |  |

|----------|---------------------------------------------------------|--------------------|-------------|----------------|----------------------|----------------|----------------------|--|--|

| FEF80400 | System Configuration Register (Upper Falcon's PR_STAT1) |                    |             |                |                      |                |                      |  |  |

| FEF80404 | Memory Configuration Register (Lower Falcon's PR_STAT1) |                    |             |                |                      |                |                      |  |  |

| FEF88000 | System External Cache Control Register                  |                    |             |                |                      |                |                      |  |  |

| FEF88300 | CPU Control Register                                    |                    |             |                |                      |                |                      |  |  |

The following sub-sections describe these system registers in detail.

## System Configuration Register (SYSCR)

The states of the RD[0:31] DRAM data pins, which have weak internal pull-ups, are latched by the upper Falcon chip at a rising edge of the power-up reset and stored in this System Configuration Register to provide some information about the system. Configuration is accomplished with external pull-down resistors. This 32-bit read-only register is defined as follows:

| REG   | System Configuration Register - \$FEF80400 |         |                      |                |                      |                      |                      |  |  |  |  |  |

|-------|--------------------------------------------|---------|----------------------|----------------|----------------------|----------------------|----------------------|--|--|--|--|--|

| BIT   | 5 5 6 7                                    | 10 10 8 | 15<br>14<br>13<br>12 | 19<br>18<br>17 | 23<br>22<br>21<br>20 | 27<br>26<br>25<br>24 | 31<br>30<br>29<br>28 |  |  |  |  |  |

| FIELD | SYSID                                      | SYSCLK  | SYSXC                | POSTAT         | P1STAT               |                      |                      |  |  |  |  |  |

| OPER  | READ ONLY                                  |         |                      |                |                      |                      |                      |  |  |  |  |  |

| RESET | \$FE                                       | Х       | Х                    | Х              | Х                    | \$F                  | \$F                  |  |  |  |  |  |

SYSID

System Identification. This field specifies the type of the overall system configuration so that the software may appropriately handle any software visible differences. For the MVME2600 series, this field returns a value of \$FE.

**SYSCLK** System Clock Speed. This field relays the system clock speed and the PCI clock speed information as follows:

| SYSCLK Value     | System Clock Speed | PCI Clock Speed |  |  |  |  |

|------------------|--------------------|-----------------|--|--|--|--|

| 0b0000 to 0b1100 | Reserved           | Reserved        |  |  |  |  |

| 0b1101           | 50MHz              | 25MHz           |  |  |  |  |

| 0b1110           | 60MHz              | 30MHz           |  |  |  |  |

| 0b1111           | 66.66MHz           | 33.33MHz        |  |  |  |  |

SYSXC System External Cache Size. This field reflects size of the look-aside cache on the system bus.

| SYSXC Value      | External Look-aside Cache Size |

|------------------|--------------------------------|

| 0b0000 to 0b1011 | Reserved                       |

| 0b1100           | 1M                             |

| 0b1101           | 512K                           |

| 0b1110           | 256K                           |

| 0b1111           | None                           |

**P0/1STAT** Processor 0/1 Status. This field is encoded as follows:

| P0/1STAT Value   | Processor 0/1 Present | External In-line<br>Cache Size |

|------------------|-----------------------|--------------------------------|

| 0b0000 to 0b0011 | Reserved              | Reserved                       |

| 0b0100           | YES                   | 1M                             |

| 0b0101           | YES                   | 512K                           |

| 0b0110           | YES                   | 256K                           |

| 0b0111           | YES                   | None                           |

| 0b1000 to 0b1111 | NO                    | N/A                            |

## **Memory Configuration Register (MEMCR)**

The states of the RD[00:31] DRAM data pins, which have weak internal pull-ups, are latched by the lower Falcon chip at a rising edge of the power-up reset and stored in this Memory Configuration Register to provide some information about the system memory. Configuration is accomplished with external pull-down resistors. This 32-bit read-only Register is defined as follows:

| REG   |    | Memory Configuration Register - \$FEF80404 |    |        |    |    |        |        |    |          |          |       |    |          |      |          |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|-------|----|--------------------------------------------|----|--------|----|----|--------|--------|----|----------|----------|-------|----|----------|------|----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| BIT   | 32 | 33                                         | 34 | 35     | 36 | 37 | 38     | 39     | 40 | 41       | 42       | 43    | 44 | 45       | 46   | 47       | 48 | 49 | 50 | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 60 | 61 | 62 | 63 |

| FIELD |    |                                            |    | M_FREF |    |    | M_SPD0 | M_SPD1 |    | R_A_TYP0 | R_A_TYP1 | _A_T\ |    | R_B_TYP0 | _B_T | R_B_TYP2 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| OPER  |    |                                            |    |        |    |    |        |        |    |          |          |       |    |          |      |          |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| RESET | _  | 1                                          | _  | ×      | 1  | 1  | X      | ×      | 1  | X        | ×        | ×     | _  | ×        | X    | ×        | ×  | ×  | ×  | ×  | X  | ×  | ×  | ×  | ×  | ×  | ×  | ×  | ×  | ×  | ×  | ×  |

M\_FREF Block A/B/C/D Fast Refresh. When this bit is set, it indicates that a DRAM block requires faster refresh rate. If any of the four blocks requires faster refresh rate then the ram ref control bit should be set.

**M\_SPD[0:1]** Memory Speed. This field relays the memory speed information as follows:

| M_SPD[0:1] | DRAM Speed | DRAM Type |

|------------|------------|-----------|

| 0b00       | 70ns       | Past Page |

| 0b01       | 60ns       | Fast Page |

| 0b10       | Reserved   | Reserved  |

| 0b11       | 50ns       | EDO       |

These two bits reflect the combined status of the four blocks of DRAM. Initialization software uses this information to program the <a href="ram\_spd0">ram\_spd0</a> and <a href="ram\_spd0">ram\_spd0</a> control bits in the Falcon's Chip Revision Register.

**R\_A/B\_TYP[0:1]** ROM/Flash Type. This field is encoded as follows:

| ROM_A/B_TYP[0:2] | ROM/FLASH Type                                     |

|------------------|----------------------------------------------------|

| 0b000 to 0b101   | Reserved                                           |

| 0b110            | Intel 16-bit wide FLASH with 16K Bottom Boot Block |

| 0b111            | Unknown type (i.e. ROM/FLASH Sockets)              |

Note: The device width is different from the width of the FLASH bank. If the bank width is 64-bit and the device width is 16-bit then the FLASH bank consists of four FLASH devices.

### System External Cache Control Register (SXCCR)

The System Cache Control Register is accessed via the RD[32:39] data lines of the upper Falcon device. This 8-bit register is defined as follows:

| REG   | System External Cache Control Register - \$FEF88000 |          |               |           |   |   |   |   |  |  |  |  |  |

|-------|-----------------------------------------------------|----------|---------------|-----------|---|---|---|---|--|--|--|--|--|

| BIT   | 0                                                   | 1        | 1 2 3 4 5 6 7 |           |   |   |   |   |  |  |  |  |  |

| FIELD | SXC_DIS_                                            | SXC_RST_ | SXC_MI_       | SXC_FLSH_ |   |   |   |   |  |  |  |  |  |

| OPER  |                                                     | R/W      |               |           |   |   |   |   |  |  |  |  |  |

| RESET | 1                                                   | 1        | 1             | 1         | Х | Х | Х | Х |  |  |  |  |  |

- **SXC\_DIS\_**System External Cache Enable. When this bit is cleared, it disables this cache from responding to any bus cycles.

- SXC\_FLSH\_System External Cache Flush. When this bit is pulsed true for at least 8 clock periods, it causes the system external cache to write back dirty cache lines out to system memory and clears all the tag valid bits. This operation causes the Glance pair to request and hold the MPC bus until it has completed the flush operation (approximately 4100 clock cycles). This may be an issue if other devices cannot wait that long to become MPC bus master.

- **SXC\_RST\_**System External Cache Reset. When this bit is cleared, it invalidates all tags and holds the cache in a reset condition. There is a bug in Glance It really does not hold the chip in a reset condition. The tag invalidate still works okay though.

- **SXC\_MI\_** System External Cache Miss Inhibit. When this bit is cleared, it prevents line fills on cache misses.

Software should never clear more than one of these bits at the same time. If more than one is cleared at the same time, the Glance pair behaves indeterminately.

## **CPU Control Register**

The CPU Control Register is accessed via the RD[32:39] data lines of the upper Falcon device. This 8-bit register is defined as follows:

| REG   |   | CPU Control Register - \$FEF88300 |         |         |   |   |   |   |  |  |  |  |  |  |

|-------|---|-----------------------------------|---------|---------|---|---|---|---|--|--|--|--|--|--|

| BIT   | 0 | 1                                 | 2       | 3       | 4 | 5 | 6 | 7 |  |  |  |  |  |  |

| FIELD |   | LEMODE                            | P1_TBEN | P0_TBEN |   |   |   |   |  |  |  |  |  |  |

| OPER  | R | R                                 | R/W     | R/W     | R | R | R | R |  |  |  |  |  |  |

| RESET | Х | 0                                 | 1       | 1       | Х | Х | Х | Х |  |  |  |  |  |  |

**LEMODE** Little Endian Mode. This bit must be set in conjunction with the LEND bit in the Raven for little-endian mode.

**P0/1\_TBEN**Processor 0/1 Time Base Enable. When this bit is cleared, the TBEN pin of Processor 0/1 will be driven low.

# **ISA Local Resource Bus**

# W83C553 PIB Registers

The PIB contains ISA Bridge I/O registers for various functions. These registers are actually accessible from the PCI bus. Refer to the W83C553 Data Book for details.

# PC87308VUL Super I/O (ISASIO) Strapping

The PC87308VUL Super I/O (ISASIO) provides the following functions to the MVME2600 series: a keyboard interface, a PS/2 mouse interface, a PS/2 floppy port, two async serial ports and a parallel port. Refer to the PC87308VUL Data Sheet for additional details and programming information.

The following table shows the hardware strapping for the Super I/O device:

| Pins           | Reset Configuration                                       |

|----------------|-----------------------------------------------------------|

| CFG0           | 0 - FDC, KBC and RTC wake up inactive.                    |

| CFG1           | 1 - Xbus Data Buffer (XDB) enabled.                       |

| CFG3, CFG2     | 00 - Clock source is 24MHz fed via X1 pin.                |

| BADDR1, BADDR2 | 11 - PnP Motherboard, Wake in Config State. Index \$002E. |

| SELCS          | 1 - CS0# on CS0# pin.                                     |

Table 1-16. Strap Pins Configuration for the PC87308VUL

# **NVRAM/RTC & Watchdog Timer Registers**

The MK48T59/559 provides the MVME2600 series with 8K of non-volatile SRAM, a time-of-day clock, and a watchdog timer. Accesses to the MK48T59559 are accomplished via three registers: The NVRAM/RTC Address Strobe 0 Register, the NVRAM/RTC

Address Strobe 1 Register, and the NVRAM/RTC Data Port Register. The NVRAM/RTC Address Strobe 0 Register latches the lower 8 bits of the address and the NVRAM/RTC Address Strobe 1 Register latches the upper 5 bits of the address.

Table 1-17. MK48T59/559 Access Registers

| PCI I/O Address | Function                              |

|-----------------|---------------------------------------|

| 0000 0074       | NVRAM/RTC Address Strobe 0 (A7 - A0)  |

| 0000 0075       | NVRAM/RTC Address Strobe 1 (A15 - A8) |

| 0000 0077       | NVRAM/RTC Data Register               |

The NVRAM and RTC is accessed through the above three registers. When accessing a NVRAM/RTC location, follow the following procedure:

- 1. Write the low address (A7-A0) of the NVRAM to the NVRAM/RTC STB0 register,

- 2. Write the high address (A15-A8) of the NVRAM to the NVRAM/RTC STB1 register, and

- 3. Then read or write the NVRAM/RTC Data Port.

Refer to the MK48T59 Data Sheet for additional details and programming information.

## **Module Configuration and Status Registers**

Four registers provide the configuration and status information about the board. These registers are listed in the following table:

Table 1-18. Module Configuration and Status Registers

| PCI I/O Address       | Function                       |

|-----------------------|--------------------------------|

| 0000 0800             | CPU Configuration Register     |

| 0000 0802             | Base Module Feature Register   |

| 0000 0803             | Base Module Status Register    |

| 0000 08C0 - 0000 08C1 | Seven-Segment Display Register |

The following sub sections describe these registers in detail.

## **CPU Configuration Register**

The CPU Configuration Register is an 8-bit register located at ISA I/O address x0800. This register is defined for the MVME2600 series to provide some backward compatibility with older MVME1600 products. The Base Module Status Register should be used to identify the base module type and the System Configuration Register should be used to obtain information about the overall system.

| REG   |     | Old CPU Configuration Register - \$FE000800                                             |      |  |  |     |   |  |  |  |  |

|-------|-----|-----------------------------------------------------------------------------------------|------|--|--|-----|---|--|--|--|--|

| BIT   | SD7 | SD7         SD6         SD5         SD4         SD3         SD2         SD1         SD0 |      |  |  |     |   |  |  |  |  |

| FIELD |     | CPUT                                                                                    | ГҮРЕ |  |  |     |   |  |  |  |  |

| OPER  |     | F                                                                                       | र    |  |  | F   | 2 |  |  |  |  |

| RESET |     | \$1                                                                                     | E    |  |  | \$1 | F |  |  |  |  |

CPUTYPE CPU Type. This field will always read as \$E for the MVME2600 series. The System Configuration Register should be used for additional information.

#### **Base Module Feature Register**

The Base Module Feature Register is an 8-bit register providing the configuration information about the Genesis Single Board Computer. This read-only register is located at ISA I/O address x0802.

| REG   | Base Module Feature Register - Offset \$0802 |       |        |        |       |       |       |        |  |  |

|-------|----------------------------------------------|-------|--------|--------|-------|-------|-------|--------|--|--|

| BIT   | SD7                                          | SD6   | SD5    | SD4    | SD3   | SD2   | SD1   | SD0    |  |  |

| FIELD |                                              | SCCP_ | PMC2P_ | PMC1P_ | VMEP_ | GFXP_ | LANP_ | SCSIP_ |  |  |

| OPER  | R                                            | R     | R      | R      | R     | R     | R     | R      |  |  |

| RESET | Х                                            | Х     | Х      | Х      | Х     | Х     | Х     | Х      |  |  |

- SCCP\_ Z85230 ESCC Present. If set, there is no on-board sync serial support. If cleared, there is on-board support for sync serial interface.

- PMC2P\_ PMC/PCIX Slot 2 Present. If set, there is no PMC/PCIX device installed in the PMC/PCIX Slot 2. If cleared, the PMC/PCIX Slot 2 contains a PCI Mezzanine Card or a PCI device.

- PMC1P\_ PMC Slot 1 Present. If set, there is no PCI Mezzanine Card installed in the PMC Slot 1. If cleared, the PMC Slot 1 contains a PMC.

- **VMEP**\_ VMEbus Present. If set, there is no VMEbus interface. If cleared, VMEbus interface is supported.

- GFXP\_ Graphics Present. If set, there is no on-board Graphics interface. If cleared, there is an on-board graphics capability.

- **LANP\_** Ethernet Present. If set, there is no Ethernet transceiver interface. If cleared, there is on-board Ethernet support.

SCSIP\_ SCSI Present. If set, there is no on-board SCSI interface. If cleared, on-board SCSI is supported.

## **Base Module Status Register (BMSR)**

The Base Module Status Register is an 8-bit read-only register located at ISA I/O address x0803.

| REG   |     | Base Module Status Register - Offset \$0803                                             |  |    |   |  |  |  |  |  |  |

|-------|-----|-----------------------------------------------------------------------------------------|--|----|---|--|--|--|--|--|--|

| BIT   | SD7 | SD7         SD6         SD5         SD4         SD3         SD2         SD1         SD0 |  |    |   |  |  |  |  |  |  |

| FIELD |     | BASE_TYPE                                                                               |  |    |   |  |  |  |  |  |  |