ECB 885

EINDHOVEN UNIVERSITY OF TECHNOLOGY. DEPARTMENT OF ELECTRICAL ENGINEERING. DIGITAL SYSTEMS DIVISION.

24 MEI 1983

DESIGN OF AN INTELLIGENT WINCHESTER DISK CONTROLLER

by: H.P.M. van Eijkelenburg.

! The department of Electrical Engineering assumes !

! no liability for the contents of this report. !

### SUMMARY .

This report covers the design of an intelligent Winchester Disk Controller. In contrast with traditional controller designs, the Disk Operating System, generally resident at the Host computer, is integrated in the controller.

After an introduction concerning the characteristics and applications of Winchester drives, the problems involved with interfacing these drives to a host computer are discussed.

Chapter three presents the general concept which lead to the final design. A separation is made between hard- and software.

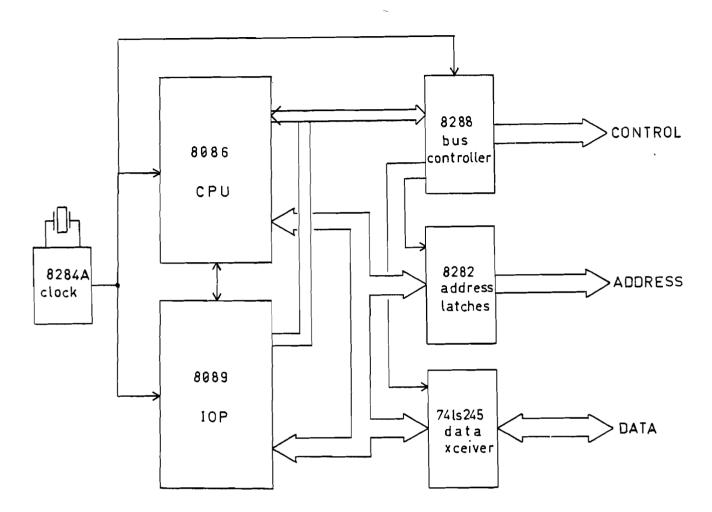

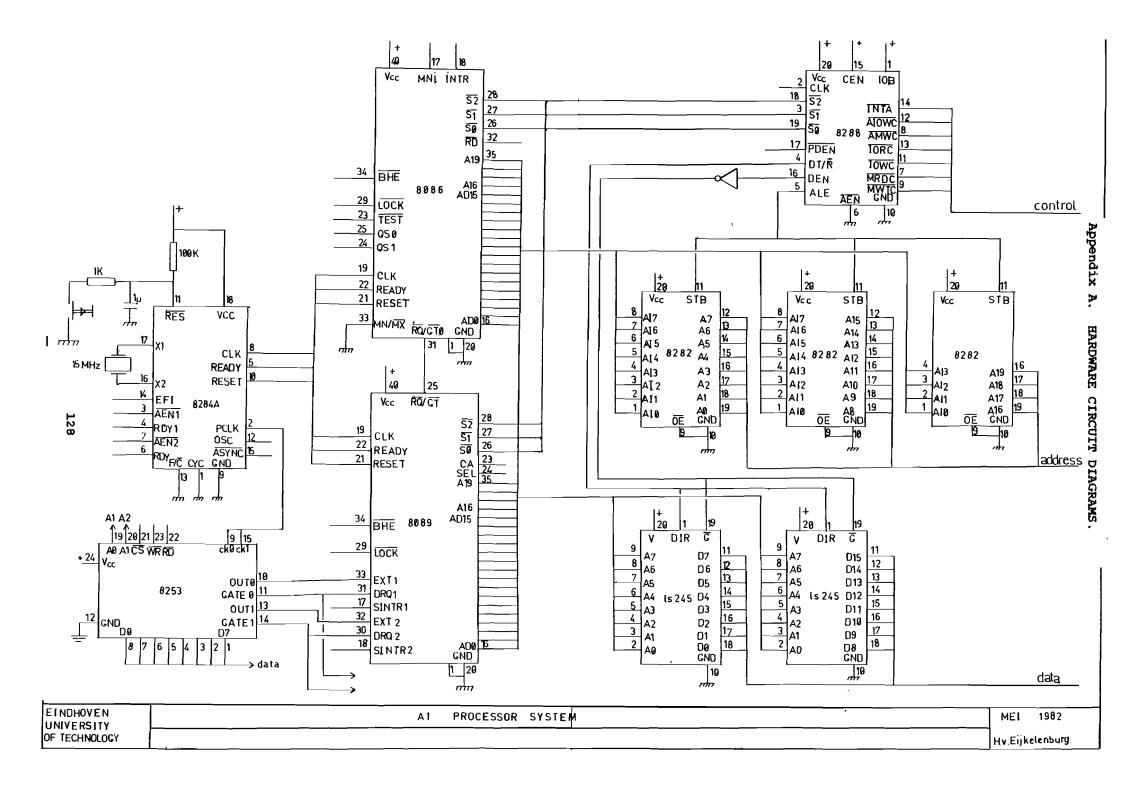

The hardware consists of a Winchester Controller Module, rather than a random logic circuit, a processor system consisting of a 16 bit CPU and an IOP co-processor, buffer- and program memory and an interface to the Host computer.

Chapter five deals with the software involved in this project, in particular the Disk Operating Systems. The UNIX operating system was taken as a guide-line for this purpose.

Though no prototype was built and tested, some conclusions are drawn in the last chapter concerning the feasibility of the design and its advantages over traditional controller designs. In addition, some recommendations for follow-up are made.

KEYWORDS: Design, Disk controller, Winchester, Universal, Communication, DMA, Hardware, Processor system, Software, Disk Operating System, UNIX.

# CONTENTS.

-

| Summaryl                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Contents                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.1.Mass storage devices                                                                                                                                                                                                                                                                                                                                                                                             |

| 2. Problem definition8                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1.1. Disk controller operation                                                                                                                                                                                                                                                                                                                                                                                     |

| 3. Winchester controller concept                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1. Controller hardware.193.1.1. Drive control unit.203.1.2. Processor system.203.1.3. Host interface unit.203.1.4. Memory system.213.2. Disk storage organization.223.2.1. Physical storage.223.2.2. File descriptor.253.2.3. Address information.263.4. Index list.283.5. Command structure.383.4.1. Free block pointer list.383.5.1. File handling commands.383.5.2. Directory commands.473.6. Host Interface.47 |

| 3.6.1. Network solution                                                                                                                                                                                                                                                                                                                                                                                              |

|    | Controlle                                                                                                                                                  | er hardware design51                                                                                                                                                                                                                                                      |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 4.1.                                                                                                                                                       | Introduction                                                                                                                                                                                                                                                              |

|    | 4.2.                                                                                                                                                       | Processor system                                                                                                                                                                                                                                                          |

|    | 4.2.1                                                                                                                                                      | Parallel- versus co-processing51                                                                                                                                                                                                                                          |

|    | 4.2.2.                                                                                                                                                     | I/O processor description55                                                                                                                                                                                                                                               |

|    |                                                                                                                                                            | Central processing unit description55                                                                                                                                                                                                                                     |

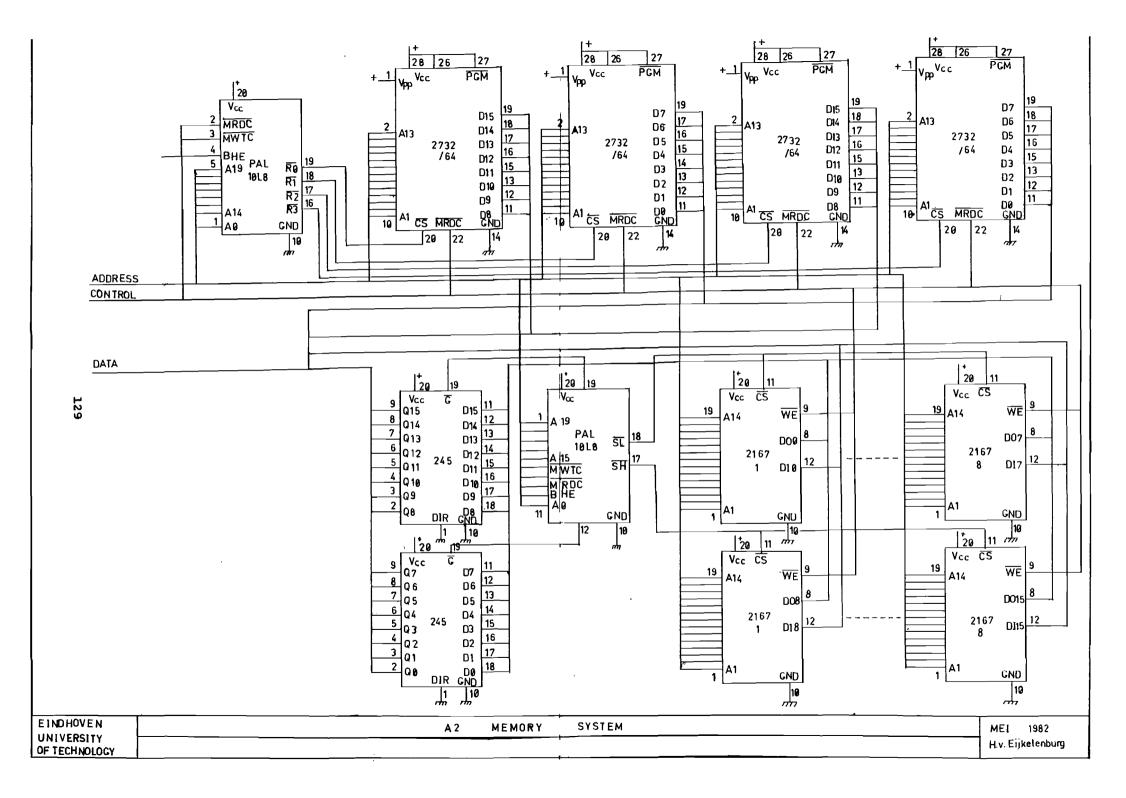

|    | 4.3.                                                                                                                                                       | Memory system                                                                                                                                                                                                                                                             |

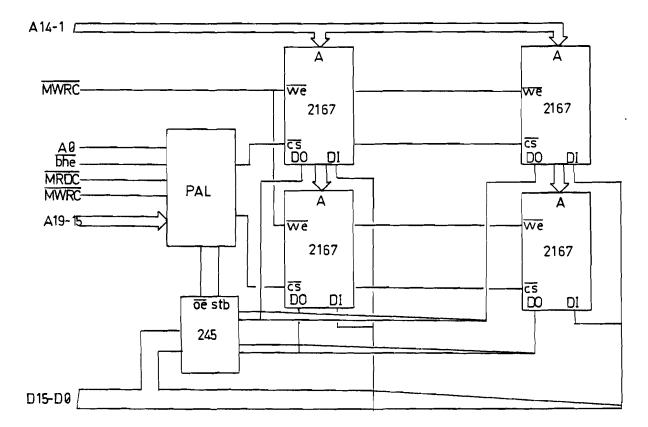

|    | 4.3.1.                                                                                                                                                     | Dynamic RAM system                                                                                                                                                                                                                                                        |

|    |                                                                                                                                                            | Static RAM system                                                                                                                                                                                                                                                         |

|    |                                                                                                                                                            | ROM system                                                                                                                                                                                                                                                                |

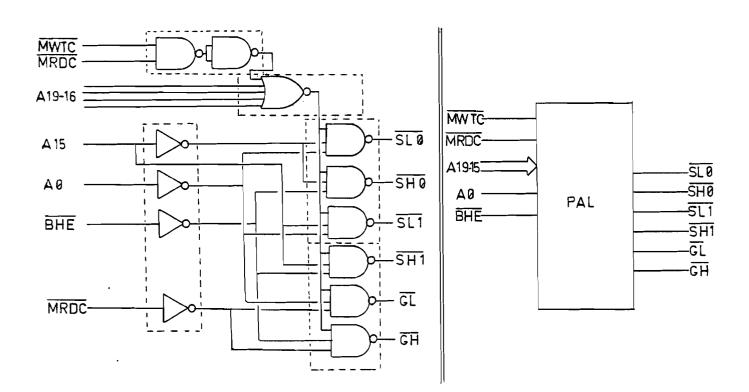

|    |                                                                                                                                                            | Address decoding                                                                                                                                                                                                                                                          |

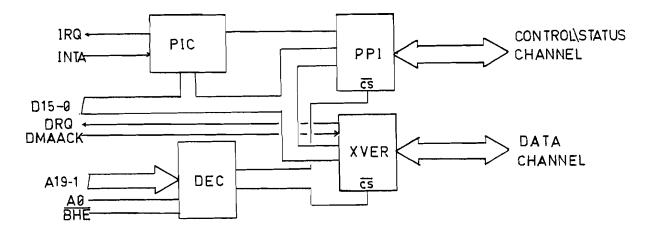

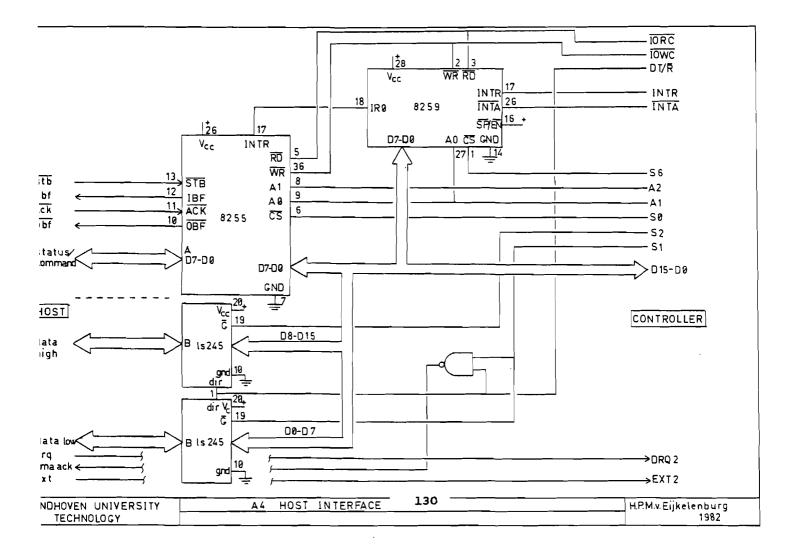

|    | 4.4.                                                                                                                                                       | Host interface                                                                                                                                                                                                                                                            |

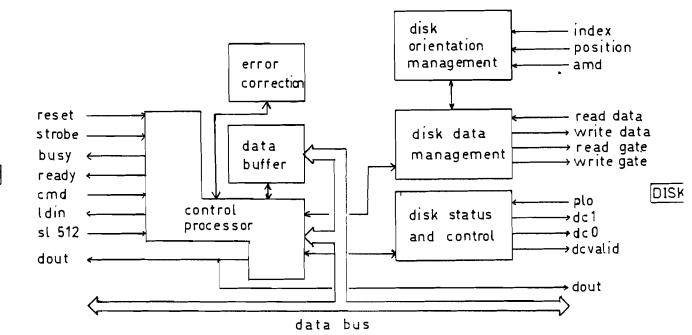

|    | 4.5.                                                                                                                                                       | Drive control unit hardware63                                                                                                                                                                                                                                             |

|    | 4.5.1.                                                                                                                                                     | Standard logic                                                                                                                                                                                                                                                            |

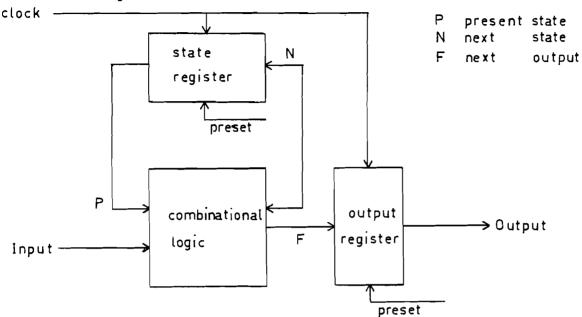

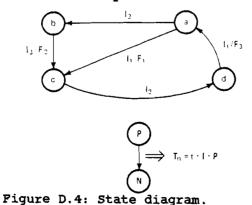

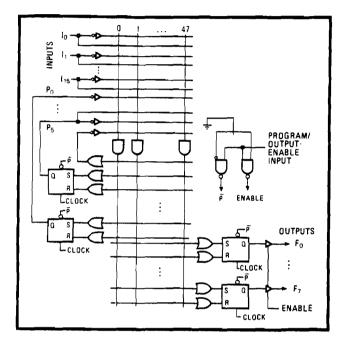

|    |                                                                                                                                                            | Programmable logic63                                                                                                                                                                                                                                                      |

|    |                                                                                                                                                            | Single chip controller63                                                                                                                                                                                                                                                  |

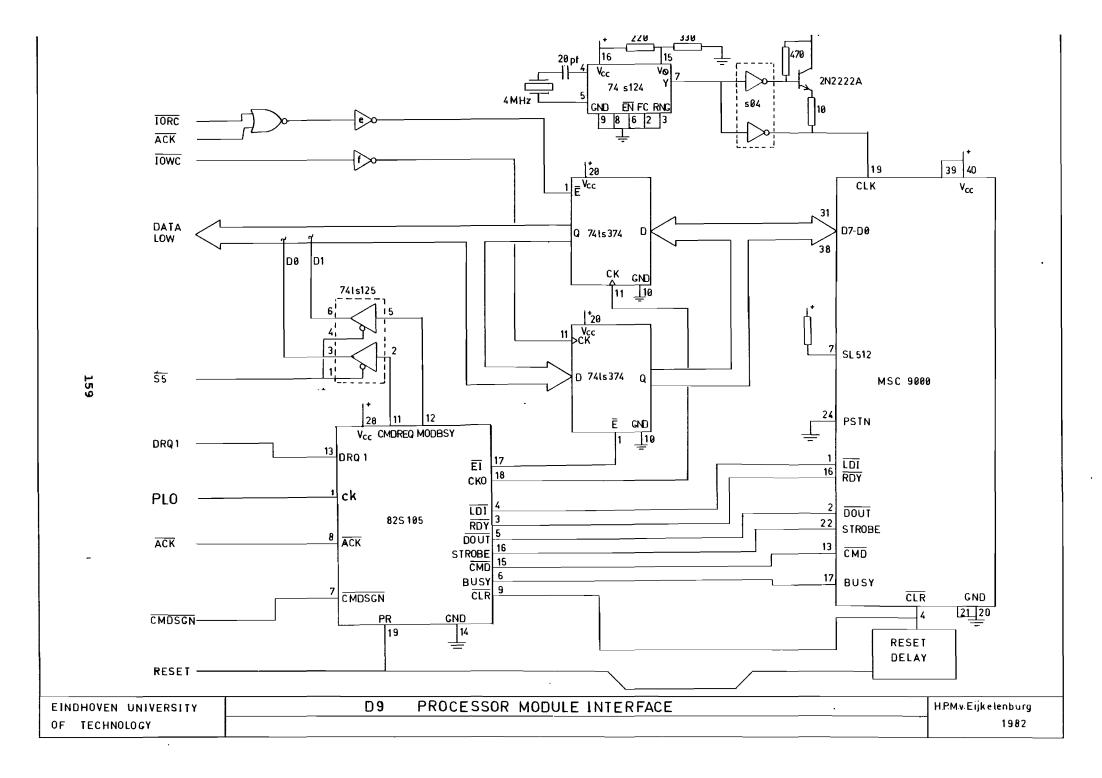

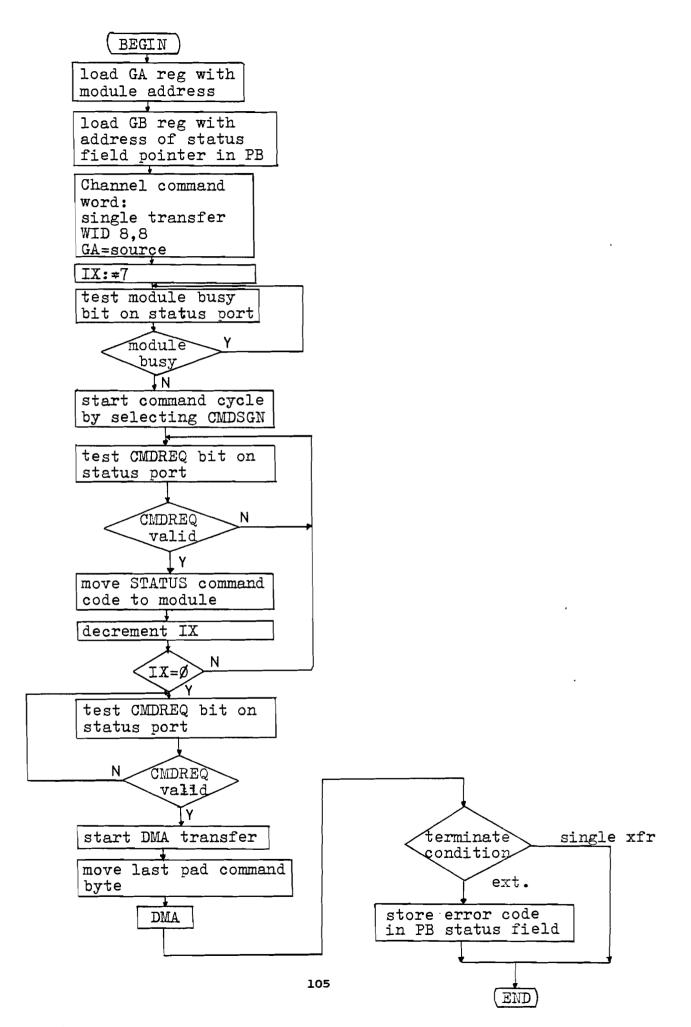

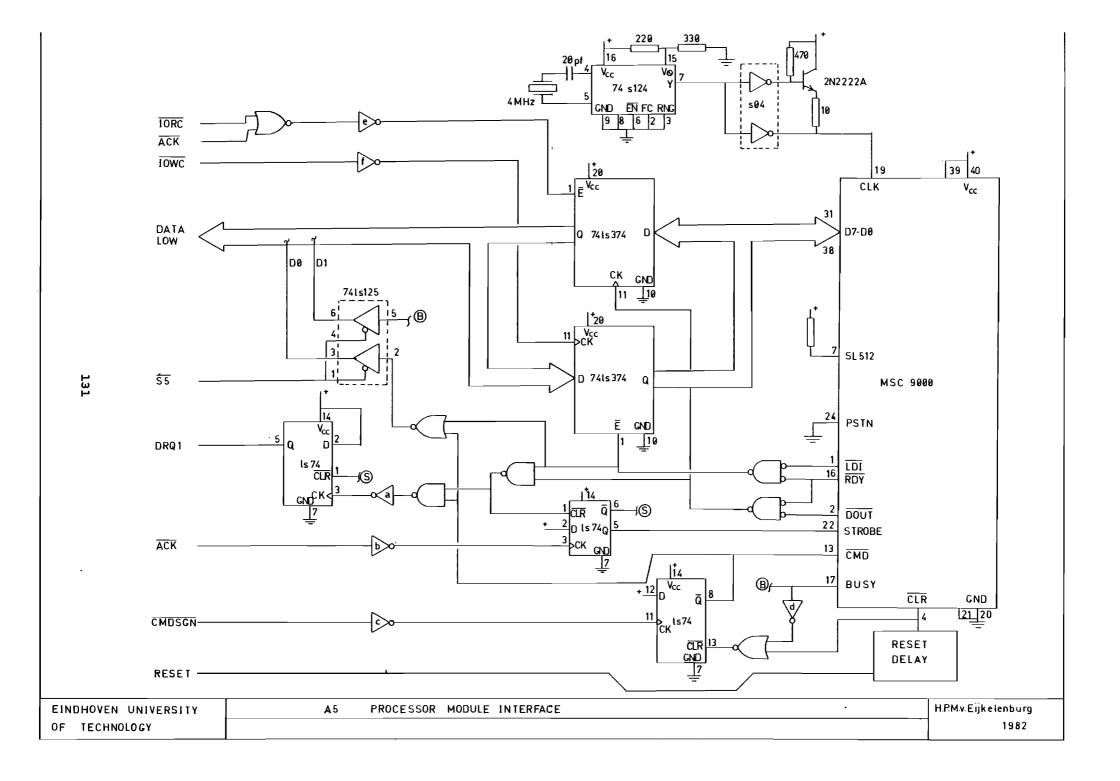

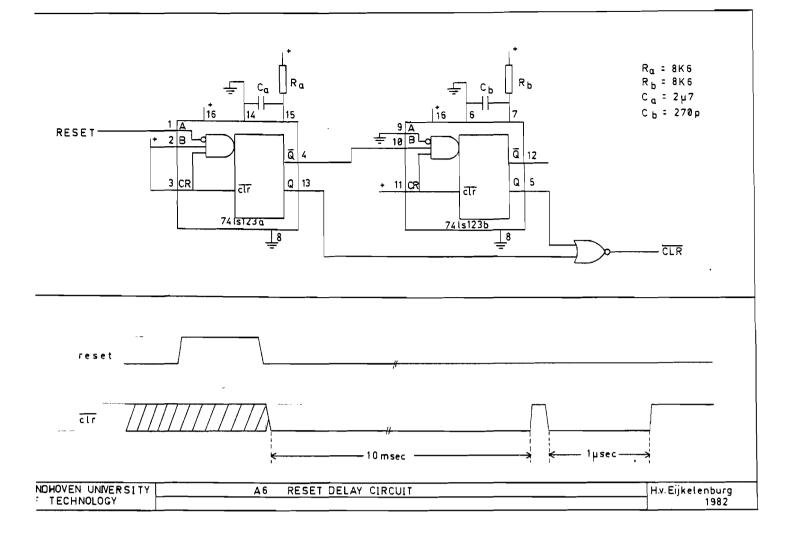

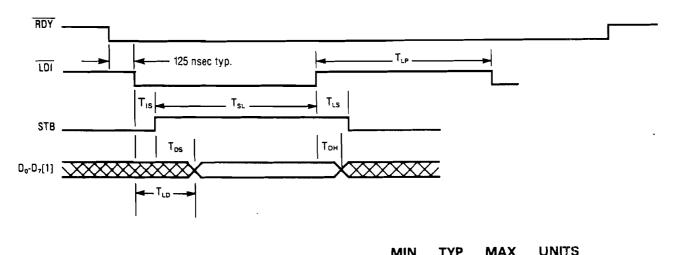

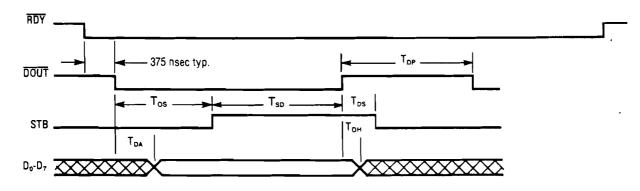

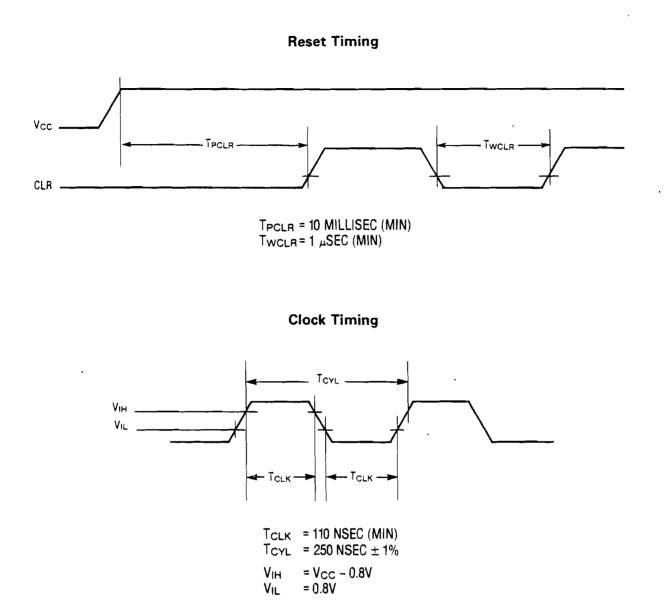

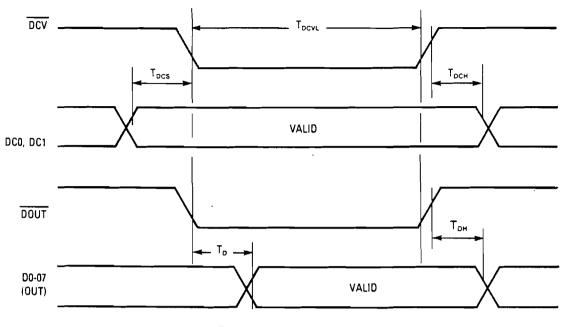

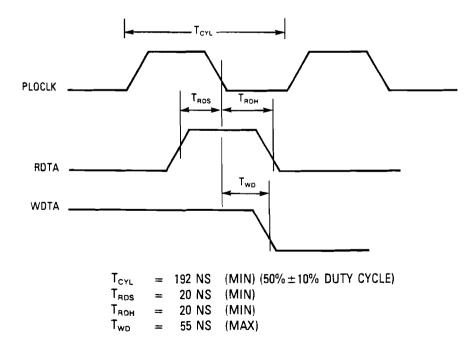

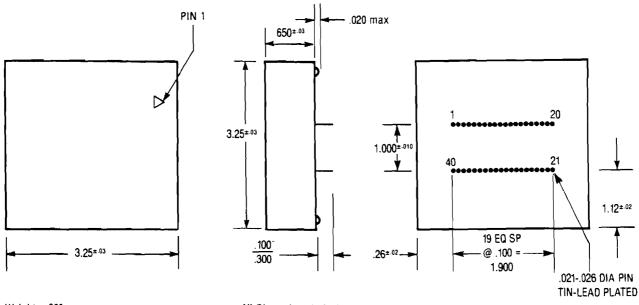

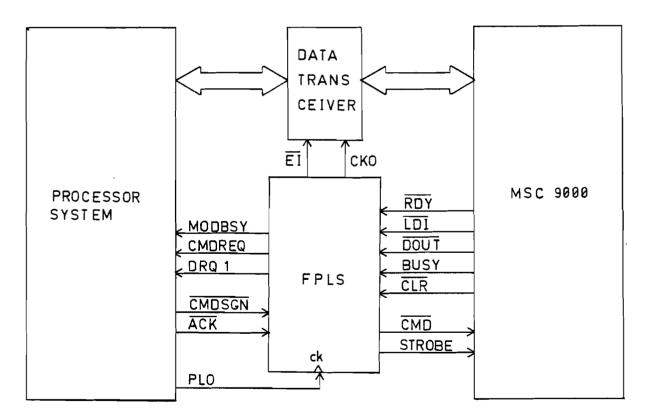

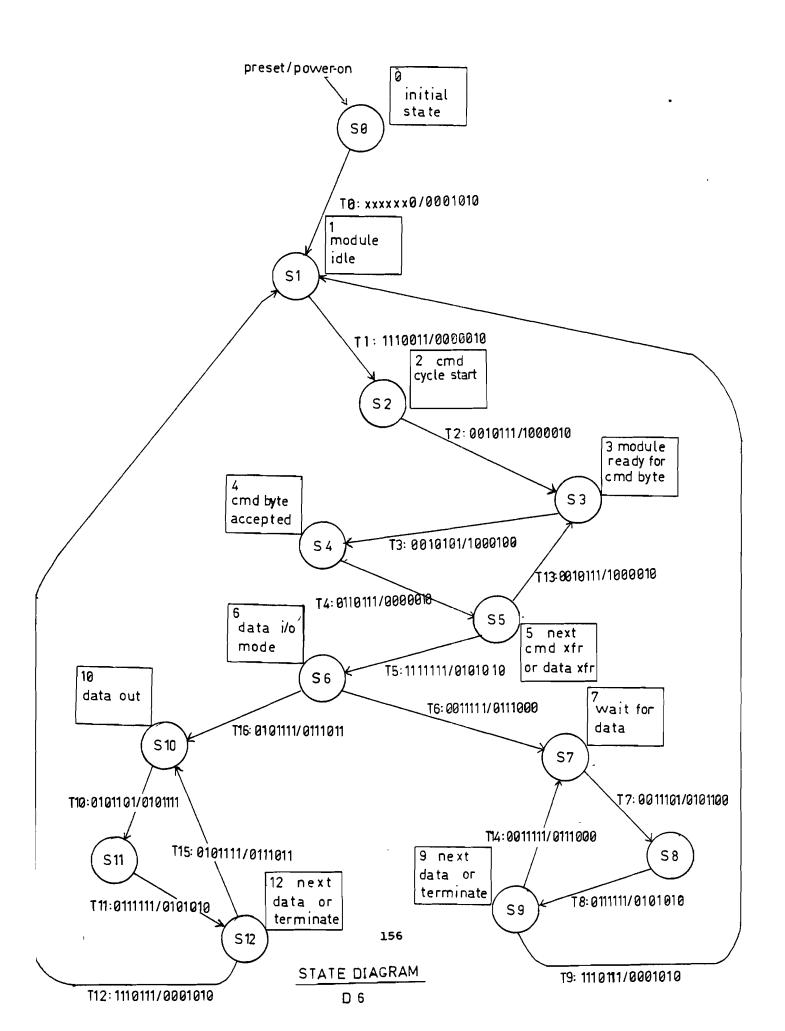

|    |                                                                                                                                                            | Processor module interface                                                                                                                                                                                                                                                |

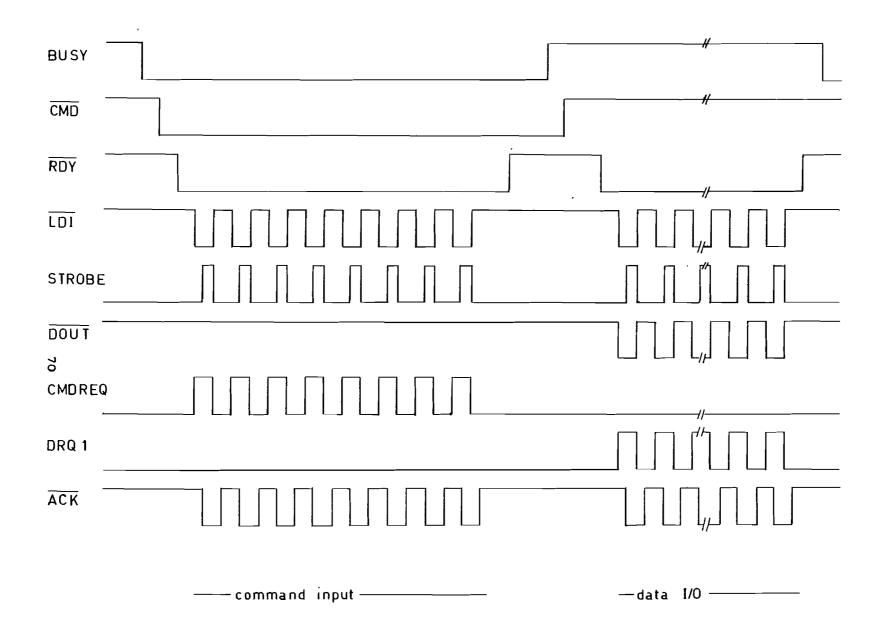

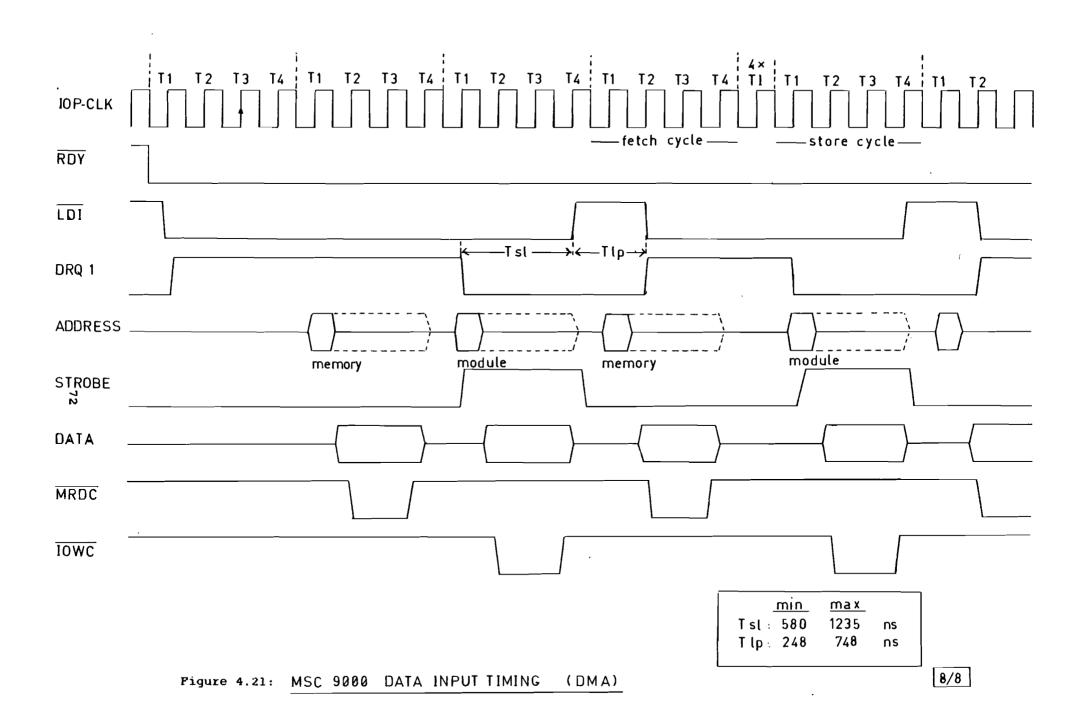

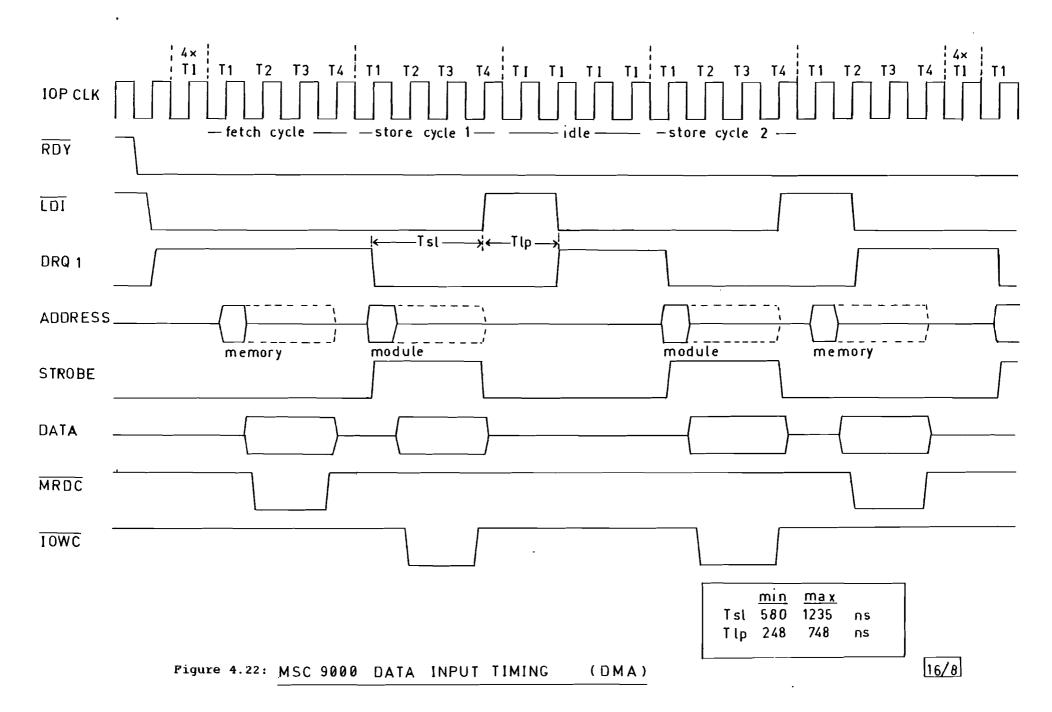

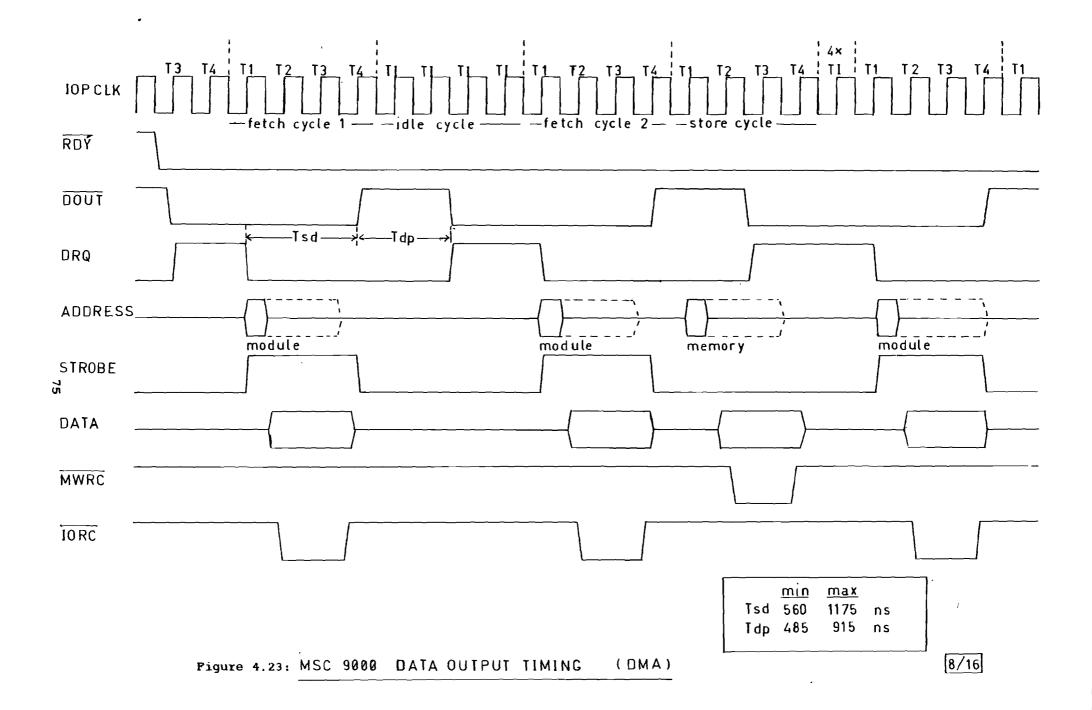

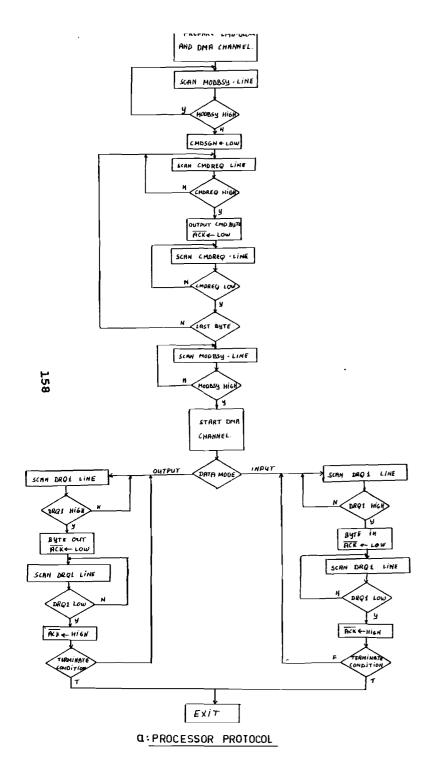

|    |                                                                                                                                                            | DMA transfer timing                                                                                                                                                                                                                                                       |

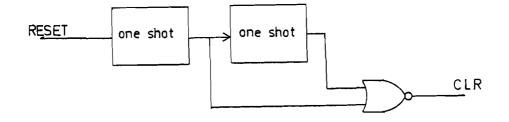

|    |                                                                                                                                                            | DMA termination                                                                                                                                                                                                                                                           |

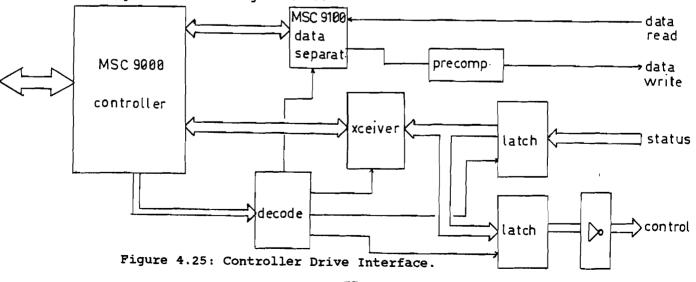

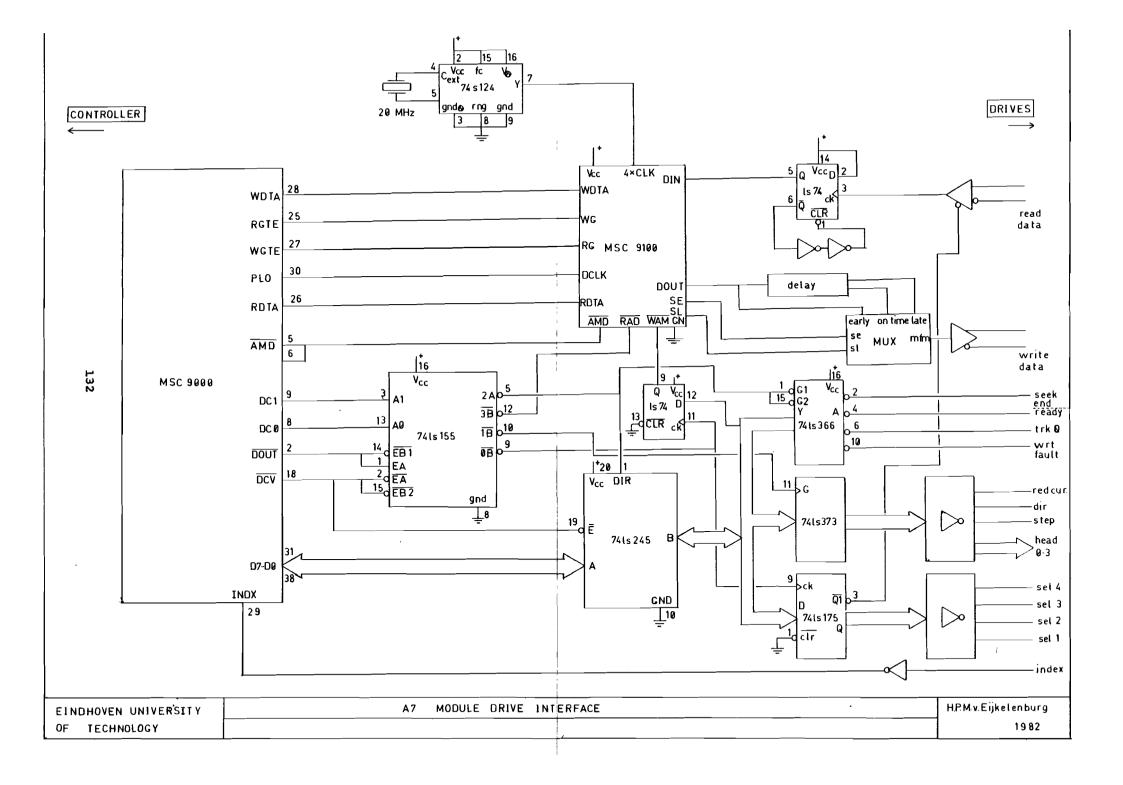

|    | 4.6.                                                                                                                                                       | Drive interface                                                                                                                                                                                                                                                           |

|    | 4.7.                                                                                                                                                       | Interface standards                                                                                                                                                                                                                                                       |

|    |                                                                                                                                                            |                                                                                                                                                                                                                                                                           |

|    |                                                                                                                                                            |                                                                                                                                                                                                                                                                           |

| 5. | Software                                                                                                                                                   | description                                                                                                                                                                                                                                                               |

| 5. | Software                                                                                                                                                   | description                                                                                                                                                                                                                                                               |

| 5. | Software 5.1.                                                                                                                                              | description                                                                                                                                                                                                                                                               |

| 5. |                                                                                                                                                            |                                                                                                                                                                                                                                                                           |

| 5. | 5.1.                                                                                                                                                       | Introduction                                                                                                                                                                                                                                                              |

| 5. | 5.1.<br>5.2.<br>5.3.                                                                                                                                       | Introduction                                                                                                                                                                                                                                                              |

| 5. | 5.1.<br>5.2.<br>5.3.<br>5.3.1.                                                                                                                             | Introduction                                                                                                                                                                                                                                                              |

| 5. | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.                                                                                                                   | Introduction                                                                                                                                                                                                                                                              |

| 5. | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.                                                                                                         | Introduction                                                                                                                                                                                                                                                              |

| 5. | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.3.4.                                                                                               | Introduction                                                                                                                                                                                                                                                              |

| 5. | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.3.4.                                                                                               | Introduction                                                                                                                                                                                                                                                              |

| 5. | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.3.4.<br>5.3.5.<br>5.4.                                                                             | Introduction                                                                                                                                                                                                                                                              |

| 5. | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.3.4.<br>5.3.5.<br>5.4.<br>5.4.1.                                                                   | Introduction                                                                                                                                                                                                                                                              |

| 5. | 5.1.<br>5.2.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.3.4.<br>5.3.5.<br>5.4.<br>5.4.1.<br>5.4.2.                                                                 | Introduction                                                                                                                                                                                                                                                              |

| 5. | 5.1.<br>5.2.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.3.4.<br>5.3.5.<br>5.4.<br>5.4.1.<br>5.4.2.<br>5.4.3.                                                       | Introduction                                                                                                                                                                                                                                                              |

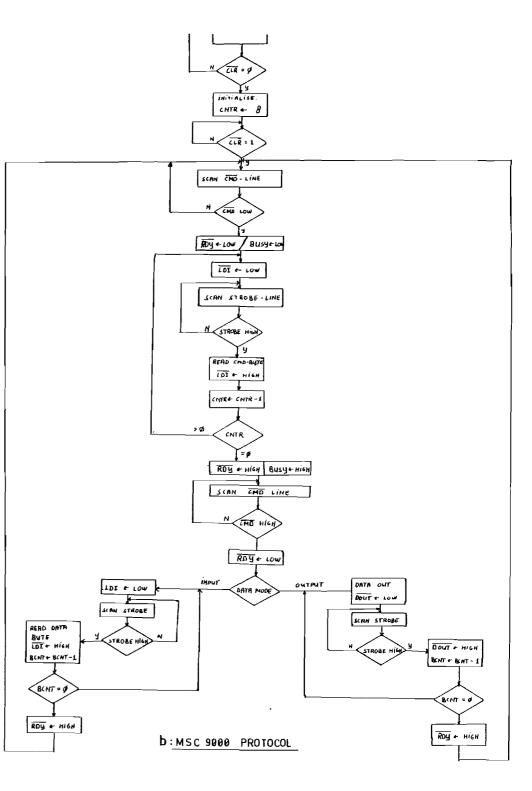

| 5. | 5.1.<br>5.2.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.3.4.<br>5.3.5.<br>5.4.<br>5.4.1.<br>5.4.2.<br>5.4.3.                                                       | Introduction79Initialization80Host protocol handler88Layer model90Application layer91Presentation layer92Transport layer93Data link layer98Disk protocol handler101Commands101Data101Task block program102Disk operating system104                                        |

| 5. | 5.1.<br>5.2.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.3.4.<br>5.4.1.<br>5.4.1.<br>5.4.2.<br>5.4.3.<br>5.4.3.                                                     | Introduction79Initialization80Host protocol handler88Layer model90Application layer91Presentation layer92Transport layer93Data link layer98Disk protocol handler101Commands101Data102Disk operating system104Command handler104                                           |

| 5. | 5.1.<br>5.2.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.3.4.<br>5.4.1.<br>5.4.1.<br>5.4.2.<br>5.4.3.<br>5.5.5.1.                                                   | Introduction                                                                                                                                                                                                                                                              |

| 5. | 5.1.<br>5.2.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.3.4.<br>5.3.5.<br>5.4.1.<br>5.4.2.<br>5.4.2.<br>5.4.3.<br>5.5.1.<br>5.5.2.                                 | Introduction                                                                                                                                                                                                                                                              |

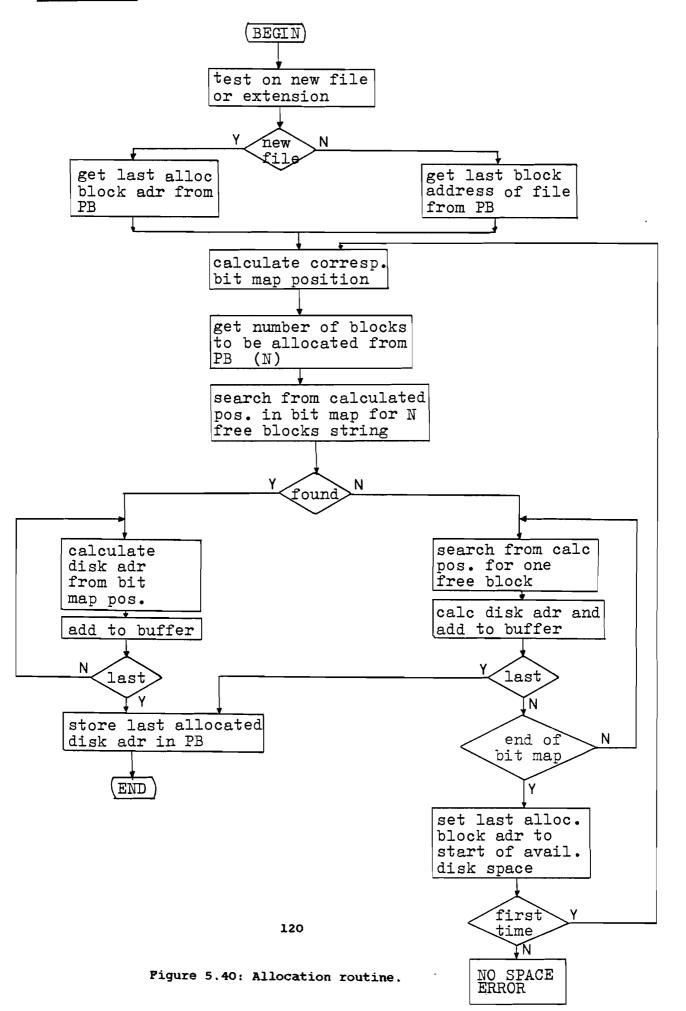

| 5. | 5.1.<br>5.2.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.3.4.<br>5.3.5.<br>5.4.1.<br>5.4.2.<br>5.4.2.<br>5.4.3.<br>5.5.1.<br>5.5.1.<br>5.5.2.<br>5.5.3.<br>5.6.     | Introduction79Initialization80Host protocol handler88Layer model90Application layer91Presentation layer92Transport layer93Data link layer98Disk protocol handler01Commands01Data02Disk operating system04Command handler104Free space administration121File management122 |

| 5. | 5.1.<br>5.2.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.3.4.<br>5.3.5.<br>5.4.1.<br>5.4.2.<br>5.4.2.<br>5.4.3.<br>5.5.5.1.<br>5.5.2.<br>5.5.3.<br>5.5.3.<br>5.6.1. | Introduction                                                                                                                                                                                                                                                              |

| 6. Conclusio             | ons and recommendations124 |

|--------------------------|----------------------------|

| 6.1.<br>6.2.             | Conclusions                |

| 7. Acknowled             | lgements126                |

| Literature 1             | reference list127          |

| Appendix B<br>Appendix C | Hardware circuit diagrams  |

Chapter 1. INTRODUCTION.

1.1. Mass storage devices.

Any user of a digital computer system will agree to the importance of a reliable and fast mass storage device. This background memory is generally used to store user programs and operating data in quantities too large to be kept in the computers core memory. Demands imposed on such storage devices are:

Reliability, to ensure the correct retrieval of stored information.

- Speed, to minimize delays caused by data access on the device.

- Cost-efficiency, meaning the price per unit of stored information should be as low as possible, typically far below the cost of a unit in core memory.

As these requirements are to some extent contradictory, several compromises were made by storage device manufacturers.

Three important kinds of storage devices can be discerned, all of them based on magnetic storage techniques:

- 1. Disk drives.

- 2. Drum devices.

- 3. Tape units.

The first category is by far the most widely used and will be focussed upon in this report. Within the range of disk types, a large variety exists, starting with 3 inch diameter micro floppy disks and ranging to hard disks.

The following table offers an overview of their capacity.

| ہوسے نے۔ ننو ہے۔ دی وہ بکا ہے، من وہ جنہ ہو نہی خرد بنو کہ |      |      |       | ین ہے۔ جب سے بین برنے کے سرحان کی ہے۔ جب کہ کو ہے۔ جب کہ کو ہے۔ ان کا کہ ا |

|------------------------------------------------------------|------|------|-------|----------------------------------------------------------------------------|

| Hard disk                                                  | over | 14   | inch  | over 200 Mbyte.                                                            |

|                                                            |      | 14   | inch  | 20 - 200 Mbyte.                                                            |

|                                                            |      | 8    | inch  | 5 - 40 Mbyte.                                                              |

| Winchester disk                                            |      | 5.25 | inch  | 2 - 10 Mbyte.                                                              |

|                                                            |      | 8    | inch  | 250 -2000 Kbyte.                                                           |

|                                                            |      | 5,25 | inch  | 125 -1000 Kbyte.                                                           |

| Floppy disk                                                |      | з    | inch  | 100 - 250 Kbyte.                                                           |

| DRIVE TYPE.                                                |      | DIAM | ETER. | STORAGE CAPACITY.                                                          |

The choice of a certain type of disk drive will largely depend on its application. Storage capacity will in most cases be the decisive factor allthough access-time and cost-effectiveness play an important role as well.

Very recently, a growing trend towards the application of Winchester drives has developed, espescially for small and medium sized computer systems. The traditional floppy disk drives, commonly found in these applications, are gradually replaced by Winchesters.

The explanation for this development is obvious. Due to finer and more accurate mechanical parts and new head materials, Winchester drives have become a very favourable alternative to floppy disk drives in terms of storage capacity, access-time, reliability and more important, price per bit. It is for these reasons that this report will concentrate on Winchester drives.

1.2. Winchester Disk Drives.

The classification "Winchester" stands for a drive technology that employs a sealed disk and head-positioning assembly.

This eliminates the need for complicated and thus expensive air filtering provisions and air flow control required for hard disks.

The first Winchester type drive was develloped around 1973 by IBM, contained a double 30 Mbyte disk and was given type number 3030 as a result of that. This model number must have been associated by several people with the notorious Winchester double barrel riffle since this nickname was soon used and has been used for this drive technology ever since.

The major advantage Winchesters offer, as opposed to floppy disks, is the fact that the read/write heads fly above the disk surface on an air cushion, as is the case with hard disk drives. This air cushion is created by the speed of the disk in conjunction with the special shaped flexure, the flexure being the metal holder upon which the heads are mounted. The absence of physical head-medium contact enables faster disk speeds and associated data recording speeds. Presently, a recording speed of 5 Mbit/sec is quite common for the smallest Winchester drives.

Table II highlights some of the features of Winchester disk drives compared to floppy disk drives.

|         | DIAMETER<br>(inch) | HEADS | CAPACITY<br>(formatted) | RECORDING<br>DENSITY | TRACK<br>DENSITY |

|---------|--------------------|-------|-------------------------|----------------------|------------------|

| FLOPPY  | 5.25               | 1     | 100 Kb                  |                      | 48 tpi           |

|         |                    | 2     | 200 КЪ                  |                      |                  |

|         | 8                  | 1     | 500 Kb                  |                      | 96 tpi           |

|         |                    | 2     | 1 Mb                    |                      |                  |

| WINCHES | TER 5.25           | 2     | 5 Mb                    | 6 - 10               | 255-980 tpi      |

|         |                    | 4     | 10 Mb                   | 6 - 10               | 255-980 tpi      |

|         | 8                  | 2     | 20 Mb                   | 6 - 10               | 255-980 tpi      |

|         |                    | 4     | 50 Mb                   | 6 - 10               | 255-980 tpi      |

|         |                    |       |                         |                      |                  |

Table II.

### 1.3. Disk controller.

Choosing a Winchester disk drive as a background mass-storage device, is not the complete solution to the problem. A link between the host computer and the drive will have to be established. This link is usually formed by a disk controller device. Either a disk controller is bought or it is developed and built by the purchaser of the drive. When buying a controller, the user has little or no knowledge of its operation and has to settle for a standard controller device. When designing and building however, all customer specific demands and requirements can be taken into account, leading up to a flexible customized controller.

The object of this graduation project was to design a controller, capable of controlling a wide range of Winchester drives and interfacing with an arbitrary host computer system. In the next chapter we will go into the details of this problem.

7

#### Chapter 2. PROBLEM DEFINITION.

Introduction.

Prior to formulating the project covered in this report, a survey of the functions performed by a traditional controller is given. This will give a better insight into the problem at hand. Subsequently, the position of the disk operating system within a computer environment is discussed. Equipped with this knowledge, the project definition is formulated in the last paragraph of this chapter.

2.1. Disk Controller operation.

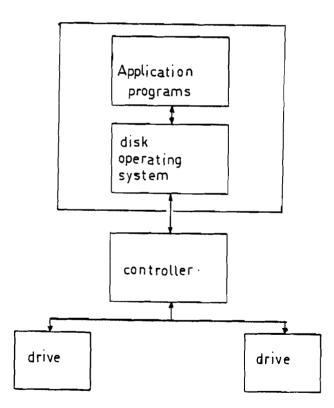

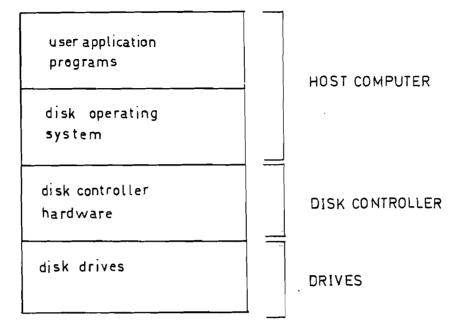

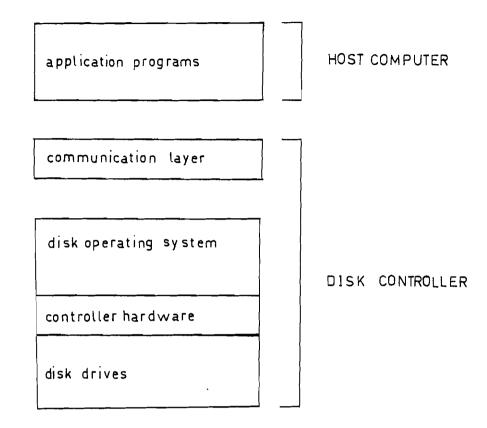

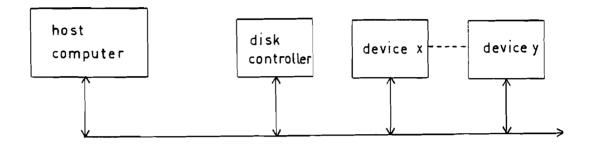

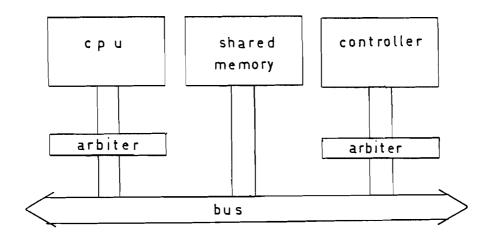

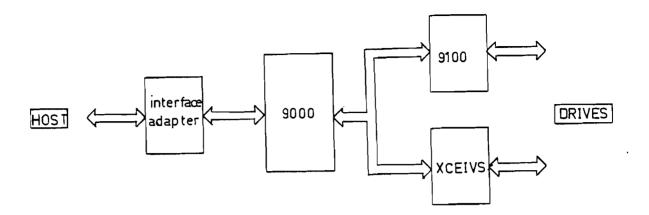

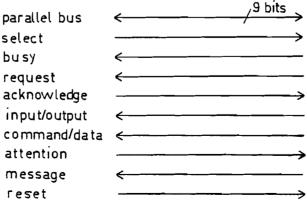

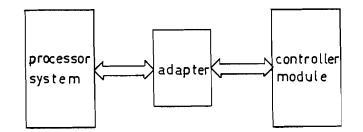

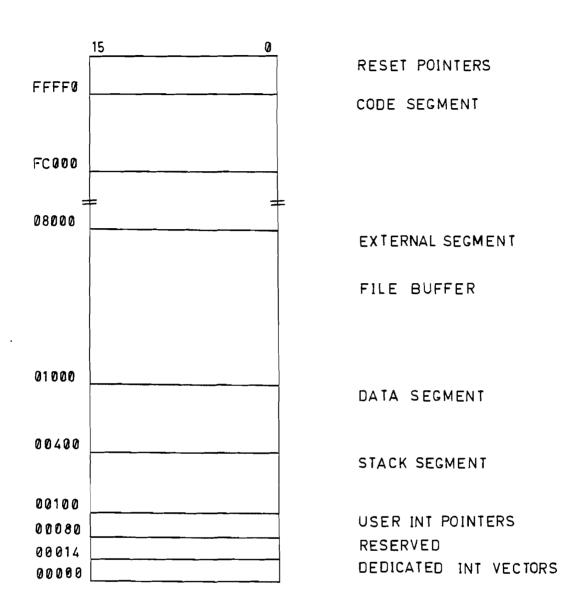

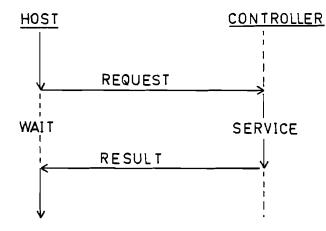

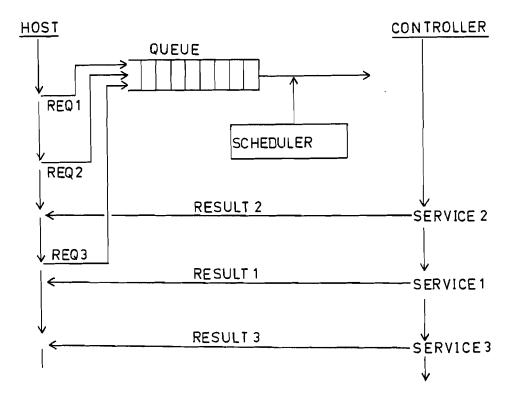

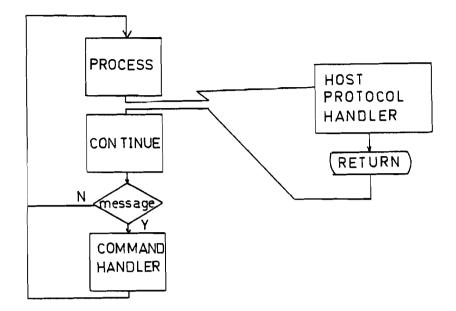

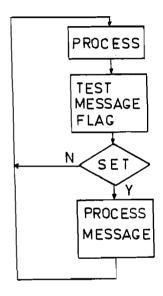

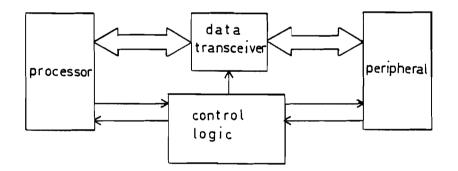

Looking at a conventional computer system which uses disks as background memory, one can abstract a raw system model as is done in figure 2.1.

Figure 2.1: conventional computer system model.

The controller constitutes the link between what will henceforth be called the Host computer and one or more disk drives. For this purpose it entails a number of functional modules which will be described briefly in the next section.

#### 2.1.2. Controller functions.

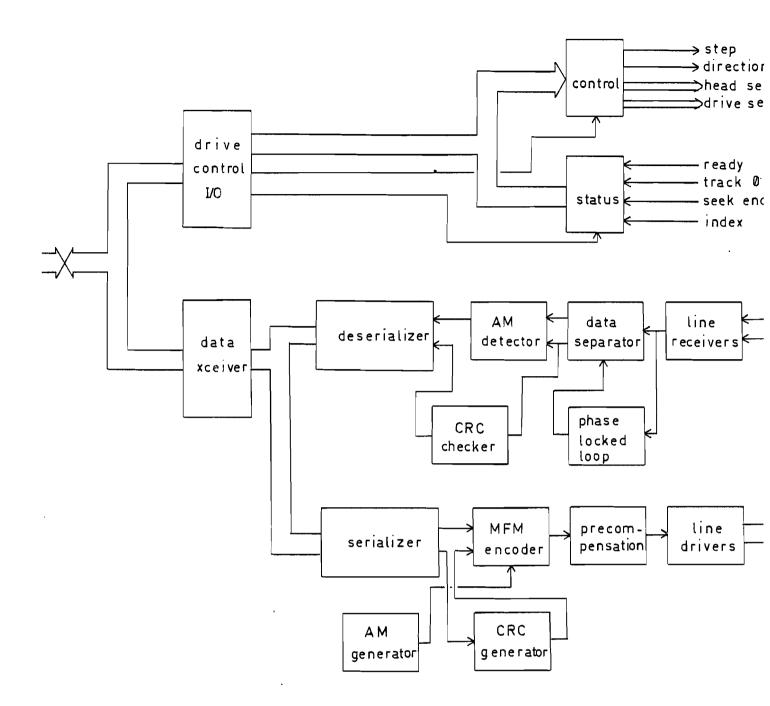

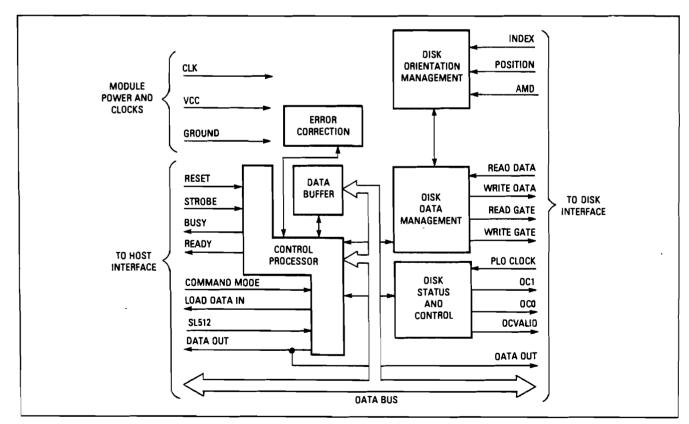

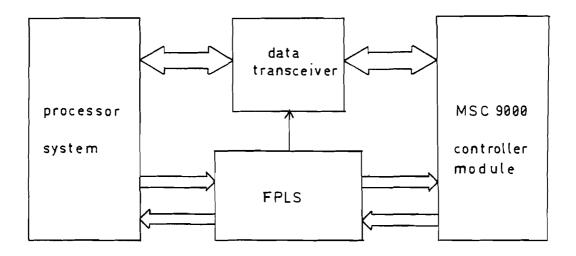

A functional block-diagram of a standard type disk controller is depicted in figure 2.2. In discussing the different modules we will distinguish between three kind of operations:

- 1. Disk write operations.

- 2. Disk read operations.

- 3. Drive control operations.

Disk write operations.

### Serializer.

Data from the host is presented in either bytes or words, generally in a parallel format. Recording on the disk surface however is done serially, implicating the parallel data has to be serialized. The serializer performs this rather straightforward operation by means of a parallel in/serial out shift register.

#### CRC generator.

To increase data integrity, a cyclic redundancy checksum is calculated and added towards the end of a block of data usually the size of one disk sector. This CRC control function enables verification of data upon reading and thus increases the reliability of the disk information.

Using CRC, the serial bits of information are treated as the coefficients of a binairy polynomial P(x). This polynomial is modified to an extent that makes it exactly divisible by a fixed polynomial G(x). The divisor G(x) is referred to as the generator polynomial. The modified polynomial, M(x) of all the data bytes in a block is added. The result of this addition is recorded at the end of the datablock on the disk.

The reason CRC is used as an error detection scheme, is because of its advantages over other methods. Some of these advantages are:

- all errors within n successive bits are detected. (n is the number of bits in P(x).)

- for even G(x), all errors with an odd number of bits in error are detected (50 % of all possible random errors).

- All error patterns that are not divisible by G(x) are detected as erroneous.

Figure 2.2: Controller function block diagram.

On top of this, CRC is efficient in that the number of control bits is relatively small compared to the number of data-bits.

MFM-encoder.

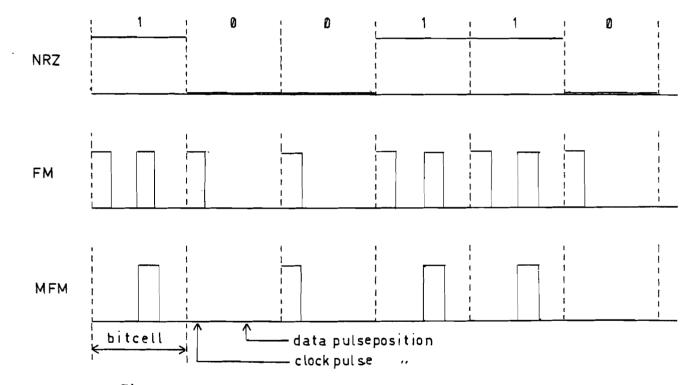

The format in which data from the serializer and the CRC generator is presented, is known as NRZ. (No Return to Zero). This format is unsuitable to cause flux reversals on the disk surface. Furthermore, timing information is stored on disk along with the databits to allow proper readback operation. To overcome this problem, a MFM-encoder is used, converting NRZ data and clock information into MFM data. (FM data representation is not discussed here since it is never used for Winchester drives.)

Figure 2.3 gives a timing diagram of different data representation waveforms used for disk storage.

Figure 2.3: Data representation waveforms.

MFM is generated from NRZ according to the following rules.

1. Every bitcell contains either a data pulse, a clock pulse or no pulse at all.

2. A logic 1 in NRZ is represented by a data pulse in the corresponding bitcell.

3. If the logic bit in NRZ is 0, then no data pulse is present in its corresponding bitcell.

4. If the previous bitcell contained a data pulse, the clock pulse in the next bitcell is missing.5. If the previous bitcell contained no data pulse, there will be a clock pulse in the next bitcell.

This scheme may seem confusing at first but it will no doubt become clear when reading the next paragraph on data reading.

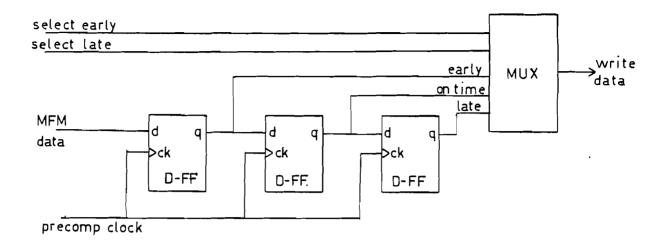

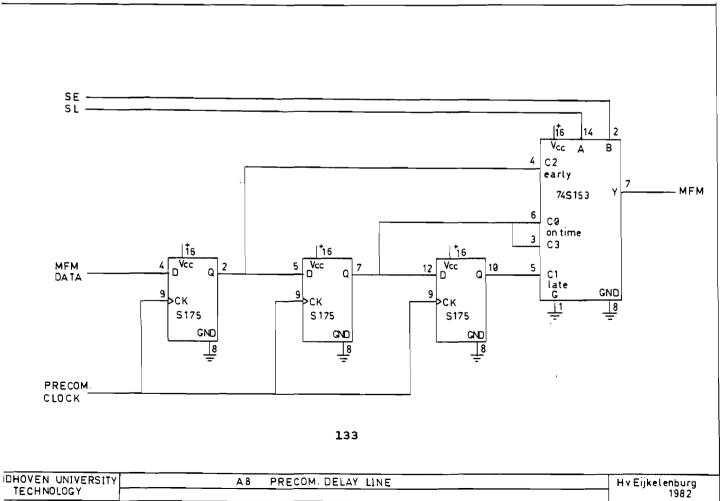

Precompensation.

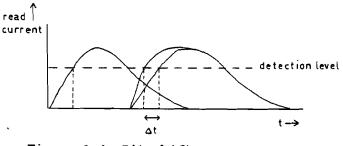

Due to the fact that the rotational velocity of the disk is uniform, there will be an increase in lineair velocity of the disk surface passing under the read/write head. This increase is proportional to the track number, the most inner track having the highest track number.

As a result of this, the spacing between subsequent flux reversals of data and clock bits becomes smaller on the inner tracks of the disk. (bit crowding). If the spacing becomes too small, adjacent flux reversals tend to influence each other, resulting in bit shifts.

During a read operation, the read/write head develops a current as it encounters a flux reversal caused by either a clock or a data bit. It takes a finite time for this current to reach its peak value. During this time, the disk surface passes on and the next flux reversal crowds under the head, resulting in its peak current being summed with the previous one. In effect, this means the bit is shifted from its proper location. Figure 2.4 illustrates this effect.

Figure 2.4: Bit shift

Fortunately, this effect is predictable and can be compensated by pre-shifting the bits in the opposite direction. This preshifting is done by the pre-compensation circuitry. As soon as writing is done on inner tracks - tracknumber greater than a predetermined value - the recorded bits are shifted back (early write), not shifted (on time) or delayed (late write) by a small amounth of time. On reading back the recorded information, the bits will appear to be on time.

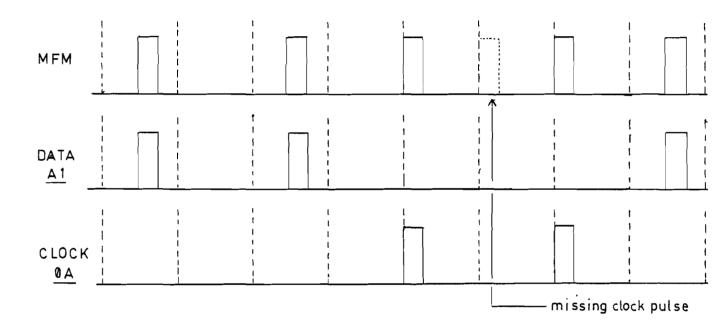

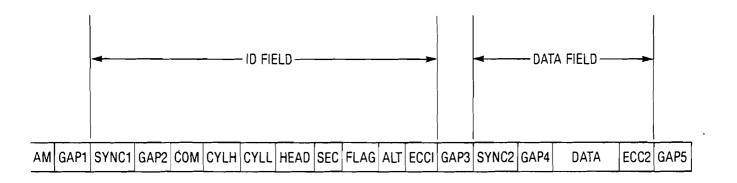

#### Address Mark generator.

As a rule, Winchester disks are soft sectored. Thus address information concerning track and sector number has to be recorded on the disk. This information is present in the form of identity fields or in short ID-fiels. The combination of an ID-field and a Data field forms a sector. The start of an ID field has to be detectable by the controller. For this purpose markers are present called Address Marks or AM. Address Marks distinguish themselves from other bytes by means of a missing clock pulse, i.e. a violation of the MFM encoding rules. Refer to figure 2.5.

Figure 2.5: Address Mark generation.

The address mark generator takes care of this clock bit suppression.

### Line drivers.

To ensure distortion-free transmission of MFM data between controller and drives, differential line drivers are used. The exact electrical specification of these drivers is dependent on the drive manufacturer. Disk read operations.

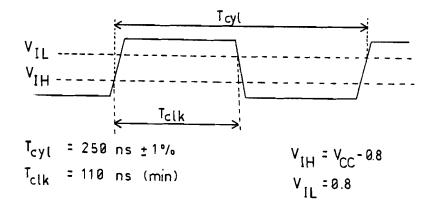

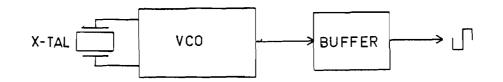

#### Phase locked loop.

The initial phase in the read process, consists of abstracting the timing information recorded on the disk. The most accurate method is to use a phase locked loop, consisting of a phase comparator, a low pass filter and a VCO. The VCO is constantly being adjusted by the information derived from the clock pulses on the disk. As a result of this, the output of the VCO is in synchronization with the data stream from the disk.

#### Data separator.

The data separator, effectively a MFM to NRZ data converter, generates separate data and clock pulses from its MFM input signal. The output of the forementioned VCO is used for synchronizing this data separator.

## Address Mark Detection.

To find the beginning of an ID-field, the controller has to search for an Address mark. The address mark detector triggers on a missing clock pulse in the MFM data stream. Depending on whether the AM belonged to an ID-field or a Data field, subsequent bytes are read and interpreted by the controller.

#### CRC check.

The next phase in the read process is the CRC check. The CRC checksum, calculated by the CRC check circuitry conform paragraph 2.1, is compared with the checksum read from the disk at the end of the data field. A mismatch will result in an error signal, indicating the received data block contains errors.

#### Deserializer.

As is suggested by the name, the deserializer performs the inverse function of the serializer, converting the serial NRZ data from the data-separator in 8 or 16 bit words. Drive control operations.

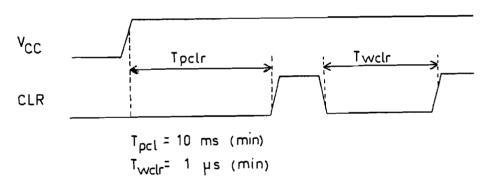

The third section of the controller exists of a number of control and status lines that enable it to control the mechanical parts of the drives connected to it. The most commonly used control and status lines are listed below.

- Moves the head assembly one track. Step Direction Indicates the direction of the head assembly movement. Combining the stepand direction signal allows positioning of the heads on any track of the disk. Head select Selects a single head of the head assembly for reading or writing. Drive select Selects one particular drive in the daisy chain connected to the controller. Indicates the drive is ready for operation. After Ready a start-up, it requires some time for the disk to reach its operating velocity. During this time the drive is not ready. Track 0 Indicates the heads are at track zero. This signal is required for head calibration after a start-up or a reset.

- Seek end Indicates the heads have reached their destination and are stable after a head movement operation.

- Write fault As a result of an incorrect operation, more than one head has been selected for writing or write current is flowing through a deselected head.

# Index The index pulse signals the beginning of a track.

#### 2.1.3. Conclusion.

The above presents a general overview of the most predominant characteristics of a disk controller. A more detailed discussion of this topic is considered superfluous since the controller concept discussed in this report uses advanced integrated modules for implementing these controller functions.

### 2.2. Disk operating system.

So far, we discussed the hardware provisions needed to connect one or more Winchester drives to a host computer. Using this hardware set-up, the host has the capability to control the drive and to store and retrieve data on a sector basis.

The next layer in the hierarchie of data storage lies between this physical disk control layer and the logical data structure of the host computer.

Any user of the host computer system, wanting to manipulate data, does so by using a logical data structure. The most common structure is a file structure. Every collection of data items that meets a certain format is called a file. Files can again be devided into one or more records.

To be able to read and write files to and from a disk, a translation has to be performed between a logical file or record and the physical sectors on the disk where the information contained by that file or record will be stored. Consequently, the host computer has to have knowledge of the physical organization of the disk.

Furthermore, the host computer has to supply the user with an access mechanism that allows easy reading, writing and manipulating of files. Thus a set of commands the user can apply has to be provided by the host computer.

Summarizing, one can list the functions of this intermediate layer between disk controller and host computer as such:

- File structure support.

- Free disk space allocation and administration.

- File directory support.

- File manipulation support.

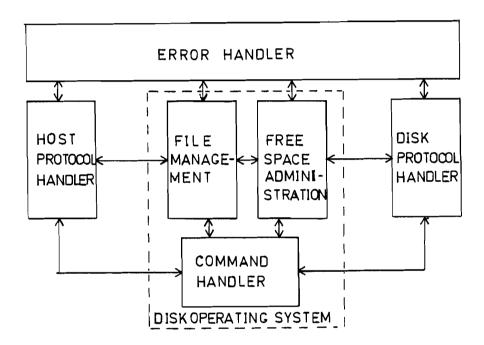

Henceforth, the collection of these functions will be referred to as Disk Operating System (DOS), since they allow the user to operate the disk. Figure 2.6. places the DOS layer in its context.

Figure 2.6: DOS layer position.

2.3. Project definition.

Traditionally, the Disk Operating System forms an integral part of the host computers' overall operating system, as indicated by figure 2.6.

The object of this graduation project was not only to design a universal Winchester disk controller, as mentioned in chapter 1, but also to add to the controller those functions concerning disk storage, normally performed by the host computer operating system. Taking this approach implies the design of an intelligent disk controller, to be used in conjunction with an arbitrary host computer. Figure 2.7. shows the situation that arises when applying an intelligent disk controller.

Figure 2.7: Intelligent Disk Controller position.

This constitutes a new approach towards controller design. Various responsibilities residing in the Host computer, are now being transferred to the controller. This should enable the controller to operate in conjunction with a large variety of host computers.

A further design requirement involves maximum universality of the controller towards different types of Winchester drives. The concept of the intelligent Winchester Disk Controller will be presented in the next chapter.

A summary of the system requirements is given below.

- Integrated Disk Operating System.

- High level communication between controller and Host.

- Support of multiple Winchester Drive types.

### Chapter 3. WINCHESTER CONTROLLER CONCEPT.

## 3. Winchester Disk Controller Concept.

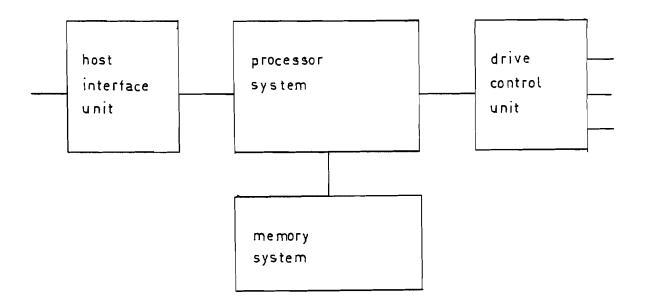

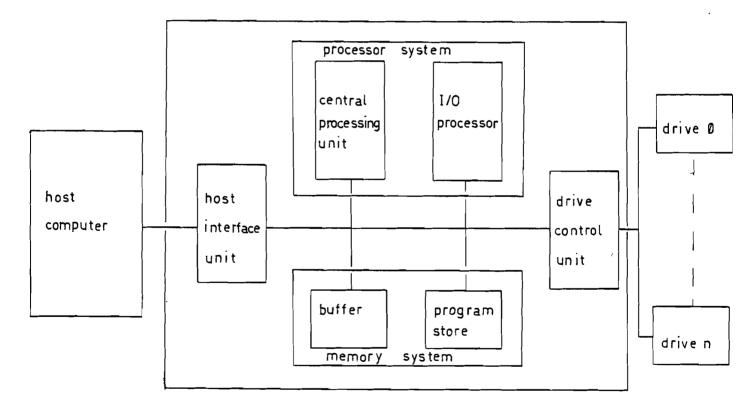

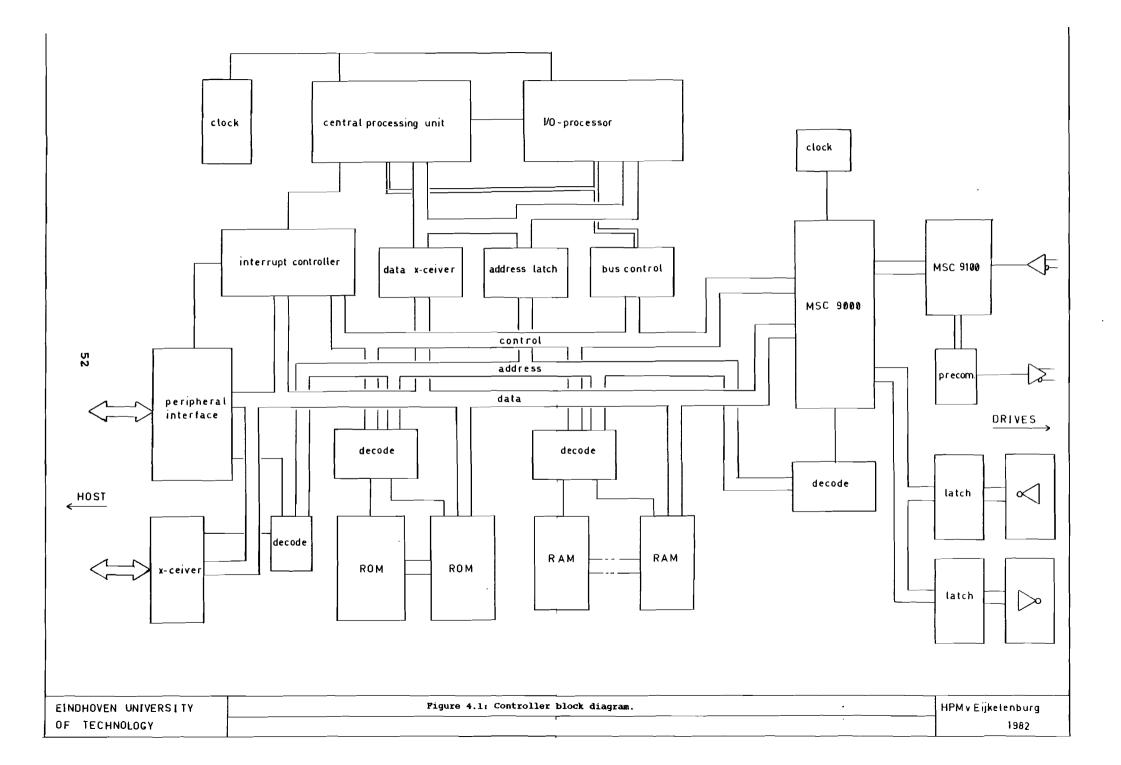

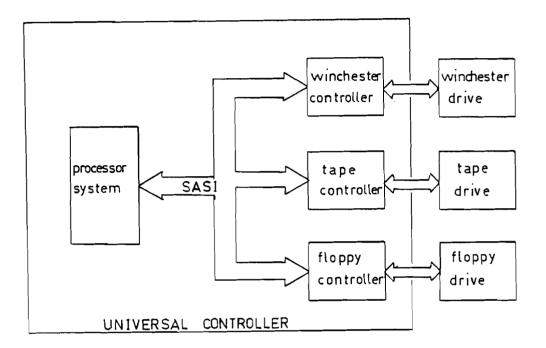

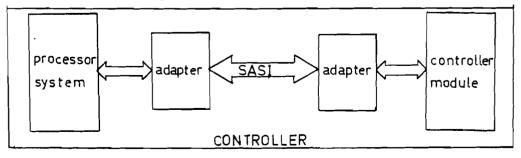

From the requirements mentioned in the previous chapter, two subsytems can be deduced that constitute the Winchester Disk Controller. The first subsystem is formed by the hardware, which is drawn in figure 3.1. The second subsystem is the software which operates the controller.

# 3.1. Controller hardware.

The hardware of the controller can be divided into four parts:

- 1. Drive control unit. (DCU)

- 2. Processor system. (PS)

- 3. Host Interface unit. (HIU)

- 4. Memory system. (MS)

Figure 3.1: Controller block diagram.

3.1.1. Drive Control Unit.

The drive control unit interacts directly with one or more Winchester Disk Drives. Its functions include:

- Selecting the appropriate drive.

- Positioning the heads on a specified track.

- Formatting soft sectored disks.

- Write sector.

- Address Mark Detection.

- Read sector.

In short, this is the part which is commonly regarded as the actual disk controller. In our concept however, it only forms part of the integral controller.

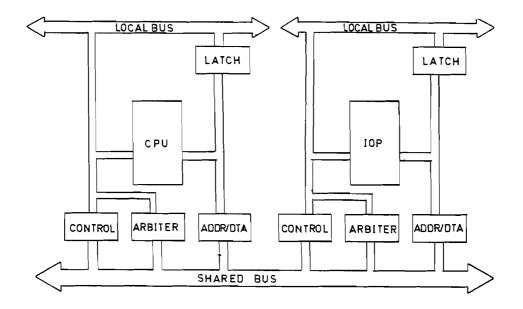

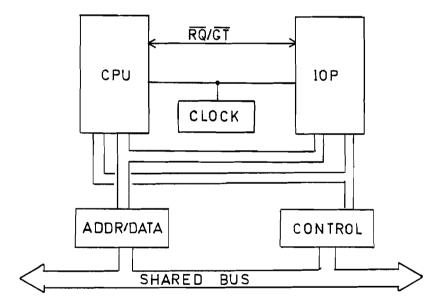

3.1.2. Processor System.

The controllers processor system comprises three different major tasks:

1 DOS execution. 2 Communicating with the disk through the Disk Control Unit. 3 Communicating with the host computer system through

the Host Interface Unit.

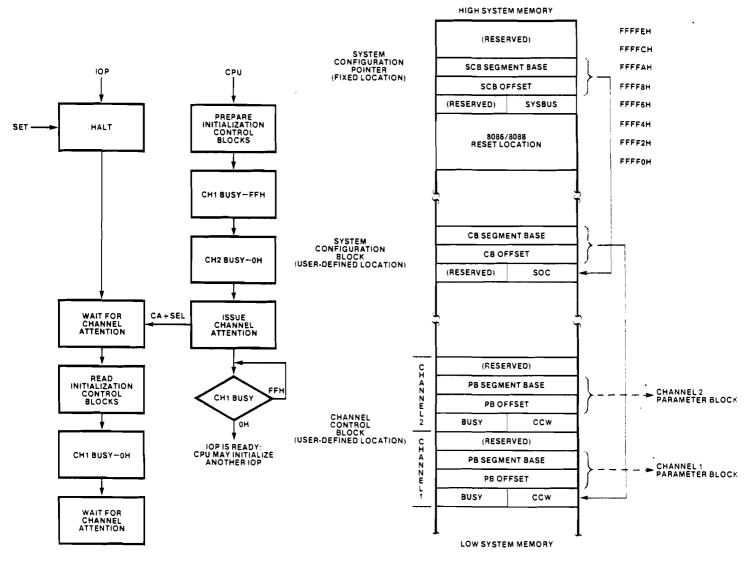

As the nature of these tasks allows for a division in processing (1) and I/O (2,3), the processor system will be separated in two sections. One central processing unit will be used for executing the Disk Operating System, a separate I/O processor will perform all neccessary communication between the Winchester Disk Controller, Winchester Drives and Host Computer.

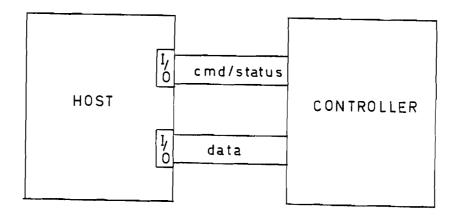

3.1.3. Host Interface Unit.

Obviously some sort of connection has to be established between the controller and the Host Computer. Wether this connection exists of a parallel or a serial link is of no major importance at this stage. There are however some requirements this connection has to meet:

> - Maximum transfer speed of data to minimize delays caused by records or files in transport between Host and Controller. Thus, either a parallel link with DMA capability or a high speed serial data link will be needed.

> - Reliability to prevent the neccessity of retransmission or data inconsistency caused by transmission errors.

At this stage it is premature to dwell upon the possible imple-

mentations of such a communication link as these are to a large extent dependent on the Host Computer used.

3.1.4. Memory System.

The Winchester Disk Controller's memory system serves a dual purpose. Firstly it incorporates the programs neccessary for controller operation. These programs are either permanently stored in ROM or loaded from reserved tracks of a disk into RAM.

Secondly, a data buffer has to be provided for, to compensate for speed differences between disk and host. Furthermore, the DOS needs memory for storage of administrative information. The more information that can be kept in the controllers workspace at a time, the faster file access can be achieved by minimizing the number of disk accesses.

Summarizing, we come to the following hardware concept block diagram. (Figure 3.2.) In chapter 4 we will go into the details of every part of the block diagram.

Figure 3.2: Controller functional block diagram.

### 3.2. Disk Storage Organization.

In order to map the users logical files to the physical disk storage space, an organization has to be set up that performs this task with a minimum amounth of overhead. The choice of the file structure employed is of extreme importance as it has a major impact on the systems performance. Rather than starting from scratch, the UNIX file structure was taken as a guideline. The reasons for this choice are twofold:

First of all, the UNIX Operating System can indulge in a fast growing popularity, especially for use in small to medium computer systems. The multi-user / multi-task facilities offered by UNIX are remarkably powerful. It is on these devices that Winchester Disks are used more and more.

Secondly, UNIX is quite a transparant operating system compared to others. This makes it relatively easy to adopt to specific needs. In spite of this, the software behind UNIX is considered to be sufficiently uncomplicated to be implemented partially the file handling part to be exact - in the Winchester Disk Controller at hand.

As a result of this choice, the reader may discover various aspects in the following section that are very much like UNIX. However, it should be noted that alterations were made at certain points where they were considered useful for this particular application.

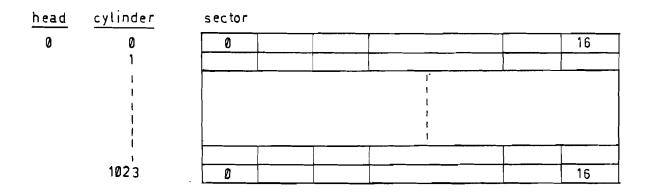

#### 3.2.1. Physical storage.

Information on the disk is stored in blocks of fixed length called sectors. The size of one sector on a Winchester disk is usually selectable between 256, 512, 1024 or more bytes/sector. This selection is made before formatting the disk. Unix assumes a sector length of 512 bytes, a size which is supported by allmost all Winchester drive manufacturers. We will adopt this sector length as well.

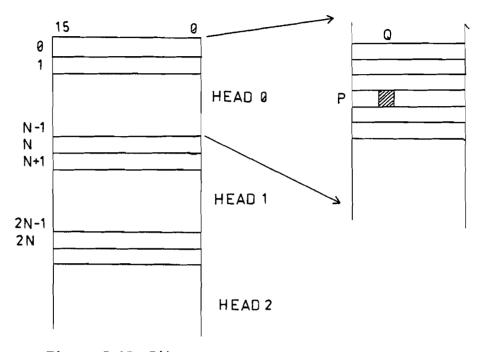

In figure 3.3 a schematic view of a typical Winchester Disk Drive ( 2 disks, 4 heads ) is given. Each individual sector is addressable by specifying head, cylinder and sectornumber.

UNIX treats files as contiguous arrays of characters. Thus a file is mapped on a number of sectors on the disk, large enough to contain the file. Any structuring of data within a file is left to the program that operates on the file. Allthough this kind of unstructured files enables the use of them in many different ways, this loose scheme was considered unsuitable for the application at hand.

The file system we wish to offer the Host computer should have structured files. For this purpose, files are made of one or

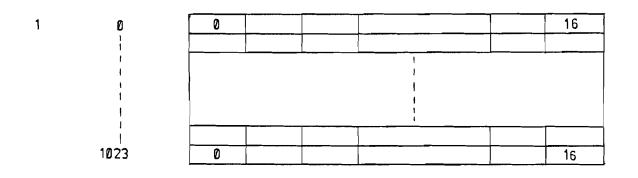

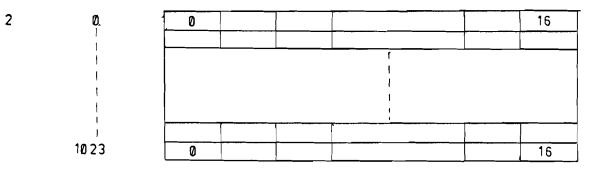

3 0 16

Figure 3. H .- Disk -schematic view.

••

more logical records. The length of these records is determined by the file type. The information concerning the structure of a file is kept in the file descriptor. (refer to 3.2.2.)

The most straightforward method to store structured files is to map each logical record to one or more sectors of the disk. As a rule, the last sector thus used will not be fully occupied with data. They will be filled with empty characters. Figure 3.4 shows a comparison between the UNIX strategy and the alternative solution.

I. UNIX.

| BLOCK 1 | BLOCK 2 | вгоск з | BLOCK 4 | BLOCK 5 | BLOCK 6 |

|---------|---------|---------|---------|---------|---------|

|         | null    | x       |         |         |         |

| ····    |         |         |         |         | ·       |

Π.

| 1          |       | 2          | 3    | 4         |         | 5   | 6 |

|------------|-------|------------|------|-----------|---------|-----|---|

| rec.1 null | гес 2 | null rec 3 | null | rec4 null | rec 5 n | นไไ |   |

Π.

| 1     |     | 2 | 3      | 4 | 5      |   | 6 |

|-------|-----|---|--------|---|--------|---|---|

| Гесог | d 1 |   | record | 2 | record | 3 |   |

Figure 3.4: File storage.

From this comparison it is obvious that the UNIX file scheme uses the available disk space much more efficiently. Only when record lengths are a true multiple of one sectorlength they can be neatly mapped and can the other scheme be used effectively. This implicates a recordlength of 512 bytes for most Winchester drives. Since this is rarely the case, the UNIX scheme for storage will be adopted. However, the controller's DOS will be equipped with routines that offer structured files to the Host computer.

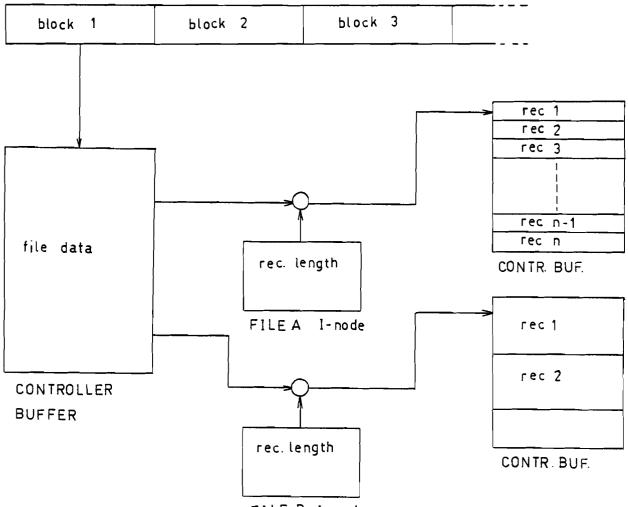

Implementation of these files is achieved by using the information on the record length of a file present in its file descriptor. After reading the required number of blocks in the controllers workspace, the structure of the file is assembled using the file desciptors information. Figure 3.5. illustrates this process. Obviously, this storage method is a trade-off between fast random access to file records and efficient disk space usage.

.

FILE B I-node

Figure 3.5: File structuring.

3.2.2. File descriptor.

Every file is described by a file descriptor containing all the relevant information on that particular file. In UNIX, file descriptors are referred to as Index-nodes or I-nodes. An Index-node contains the following information:

Identification of the user and owner of the file.

Access rights.

Address information concerning the physical location of the file on disk.

File size, i.e. the number of physical blocks it occupies.

Number of links to the file, i.e. number of times it appears in the directory.

File type: User file, record length ; Directory file.

The I-node describes the entire file and provides the information required to access its contents. Notice that some modifications were made to the standard UNIX I-node.

#### 3.2.3. Address information.

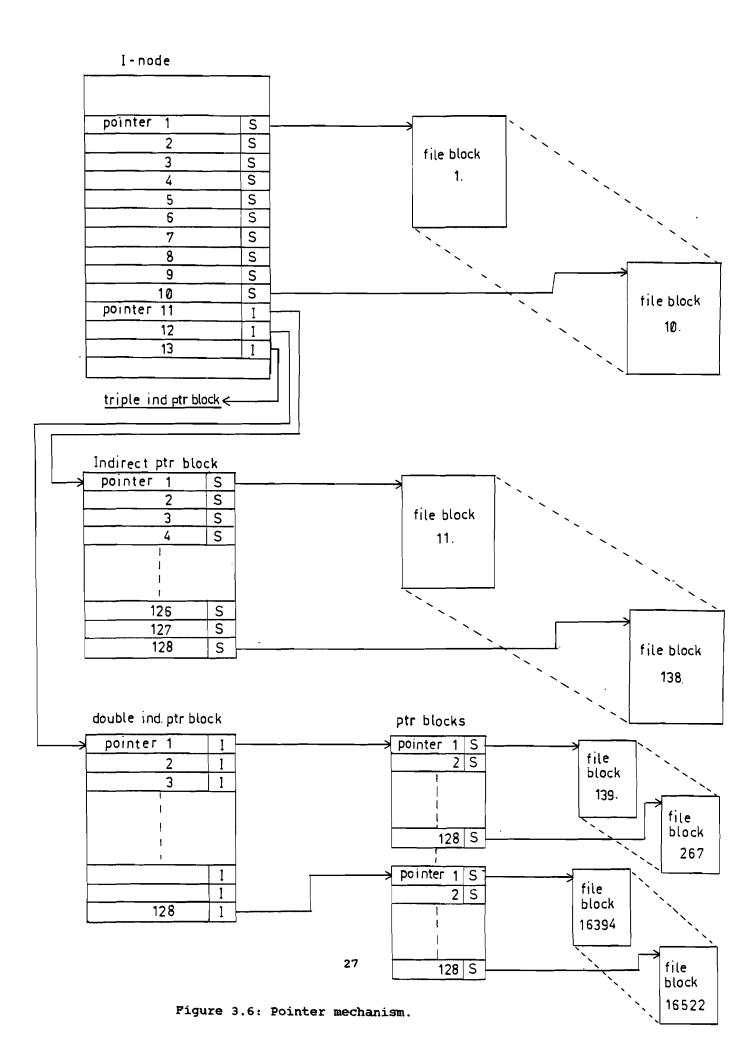

The address information on a file is organised as 13 4 byte pointers. The first 10 pointers correspond directly to the first ten blocks (disk-sectors) of the file. The 11th pointer points to a block containing 128 pointers to the next 128 blocks of the file. If the file is longer than 138 blocks, pointer 12 of the I-node is used as a double indirect pointer. It points to a block of 128 further pointers, each pointing in their turn to pointerblocks, containing pointers to the subsequent blocks of the file. Finally, pointer 13 is used as a tripple indirect pointer. As a result of this, each file can occupy a maximum of 2,113,674 512 byte blocks on the disk. This upper limit is considered sufficient to accomodate most file lengths. Note that large files become increasingly unpractical to operate upon.

This organization allows relatively short files (less than 5120 bytes) to be addressed directly through the I-node. Longer files require an extra indirection i.e. an extra disk access and thus a longer access time, as might have been expected. The end of a file can be signaled by a null pointer, following the pointer to the last block of the file.

Two different pointer types will be used: -Indirect pointer (I): pointing to a pointer block. -Sequential pointer (S): pointing to a file block.

The reason for this distinction will become clear in chapter 5 when discussing record insertions. Obviously pointer 1 through 10 in the I-node are 5-type pointers whereas 11,12 and 13 are I-type.

Refer to figure 3.6. for a graphical representation of the pointer mechanism described.

3.2.4. Index list.

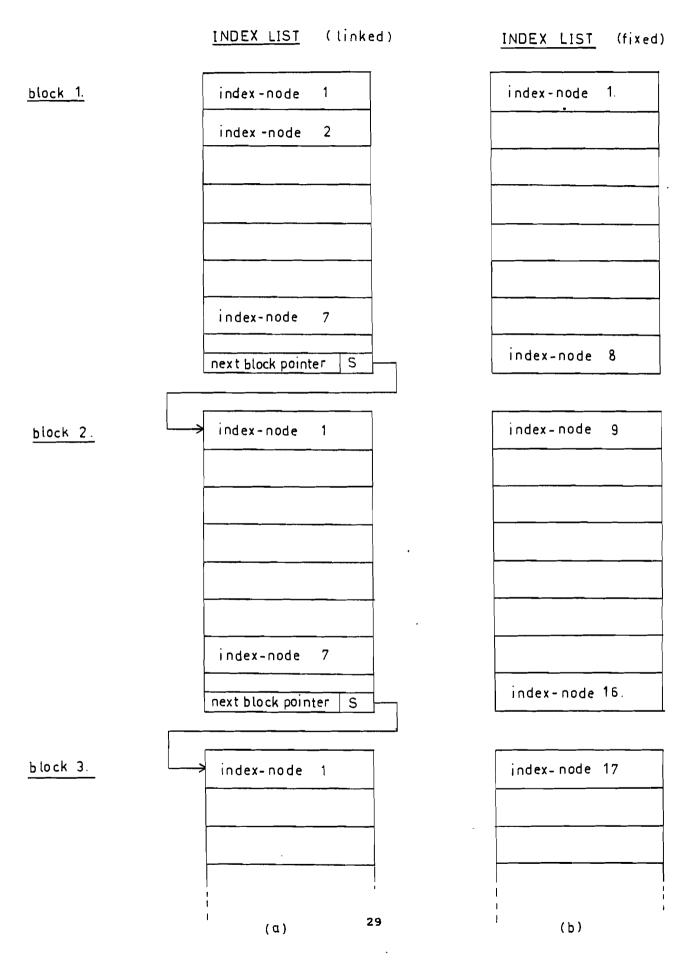

All index nodes, and thus all files, can be found by searching through the Index-list (I-list). The Index-list is a list of all I-nodes in the system and starts at a fixed location on the disk. The length of this list, determined by the number of Inodes, may be such that it covers more than one block of the disk. Therefore the I-list will be dispersed over a number of blocks. We will discuss to possible solutions to organize this Index-list.

- a) Linked list: Using a linked list method, every block of the I-list is terminated by a sequential pointer to the next block of the list. The major advantage of this method is the possibility to expand the I-list when required. However, searching through the list for a particular I-node can only be done linearly by starting from the first block, which is at a known position. This can be a very time consuming process, especially when the I-list becomes dispersed over the disk due to multiple extensions. To overcome this problem, it would be favourable to keep the I-list in the controllers' workspace as much as possible. This would eliminate the need for multiple disk accesses but would on the other hand claim considerable amounths of controller workspace.

- b) Fixed list : Using a fixed list means the I-list is stored on a fixed number of contiguous blocks on the disk. This means a predetermined number of blocks will have to be reserved for the I-list. Expansion of the I-list becomes impossible. Once it is filled, no new I-nodes can be added, unless another I-node is deleted first. Thus there is a maximum number of files that can be resident in the system. Though this method may seem unfavourable, its strength lies in the ability of the controller to access an I-node directly by calculating its position on the disk. Thus the I-list need not be kept in workspace since one integer number is sufficient to locate the proper I-node.

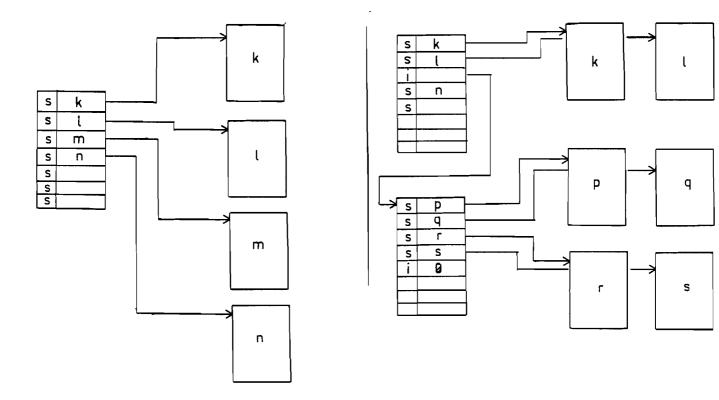

In Figure 3.7. both methods are shown. Allthough a linked I-list offers more flexibility, a fixed list will be used to allow easy access to an I-node and thus a file. The consequence of this choice is the limitation to a predetermined number of files.

#### 3.3. Directory structure.

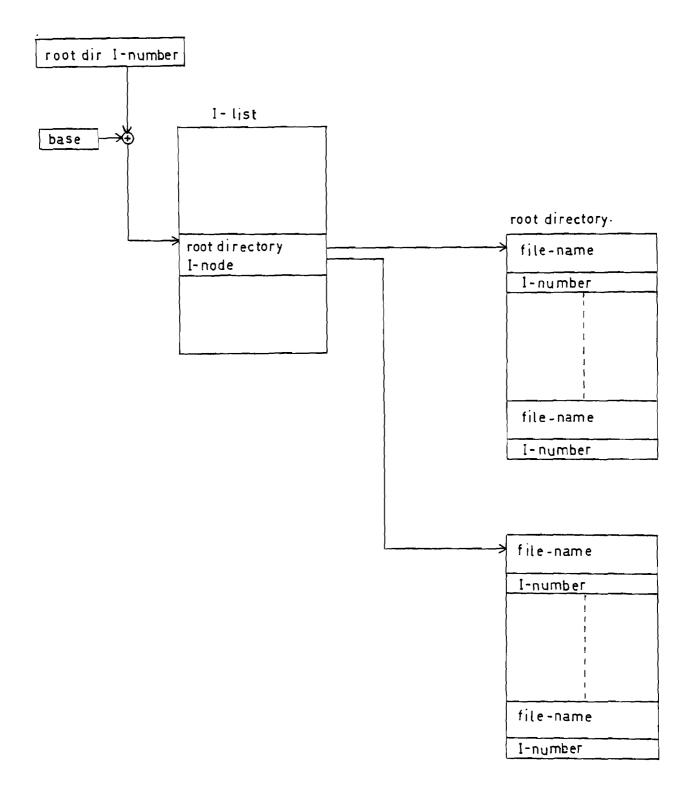

Access to a file is obtained through the Index-node. Rather than searching through the index-list lineairly, looking for a particular Index-node, a hierarchy of directories is added to the controller concept.

In UNIX, a directory is considered as an ordinairy file with limited access rights. Only the system can create, write and

•

Figure 3.7: Index list.

rigure 3.

modify a directory file. A directory file is marked as such in the corresponding Index-node. An entry in a directory file comprises two fields. The first is occupied by a symbolic alpha-numeric name of limited length. The UNIX convention is 14 characters maximum and as this is considered a reasonable amounth, it will be used in this concept as well. The second field contains a two byte integer number, called the

Index-number or I-number. The Index-number is an offset in the Index-list, leading directly to the Index-node of the file that corresponds to the symbolic file name.

Refer to figure 3.8. for a graphic representation of the directory mechanism.

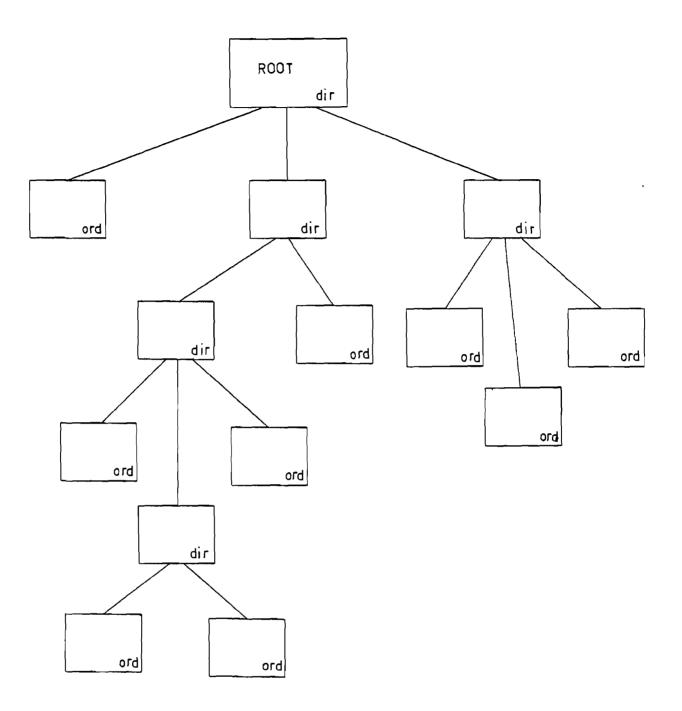

Due to the fact that files refered to in a directory can be either user-files or user defined sub-directories, a tree-like directory structure is created. The user can thus specify a file by its path through this tree structure. The controller converts this pathname into the desired Index-node by starting to look in the current directory of the user at hand. The first component of the pathname is searched in this directory and when found, results in an Index-node. If it was the last component of the pathname, the Index-node found is the final result. If not, the next pathname component is searched in the file corresponding to the Index-node just found. Note that in this case the file type had to be directory. Figure 3.9. illustrates this tree-directory structure.

Apart from its straightforwardness and simplicity of implementation, this directory mechanism offers advantages in respect of access-right validation and file protection.

Two standard entries in every directory are worth mentioning distinctively. UNIX uses a single and a double dot as symbolic name to refer to these entries. The first refers to the directory itself enabling the user to read his current directory without knowing its name. The second refers to the parent of the directory in which it appears, this parent being the directory in which it was created. This entry allows for backtracking through the directory tree.

Figure 3.8: Directory mechanism.

.

Figure 3.9: Tree structure.

3.4. Free space administration.

In order to prevent the controller from writing different files on the same physical location of the disk, it has to keep track of the available space on the disk. Furthermore, it is this part of the DOS that is responsible for allocating disk-space to a new file and re-allocation of space that becomes available on the deletion of a file.

Looking at the UNIX operating system again, one encounters a strategy of blocks containing 50 pointers to free blocks. These pointer blocks form a linked list.

The alternative to this scheme, found in many Disk Operating Systems is the use of a bit-map. A bit-map is an array of bits, each corresponding to one sector or block on the disk. The value of a bit indicates whether the corresponding block is free or not.

The following two paragraphs deal with the advantages and disadvantages of both methods. As a result of this comparison, a choice for either method will have to be made.

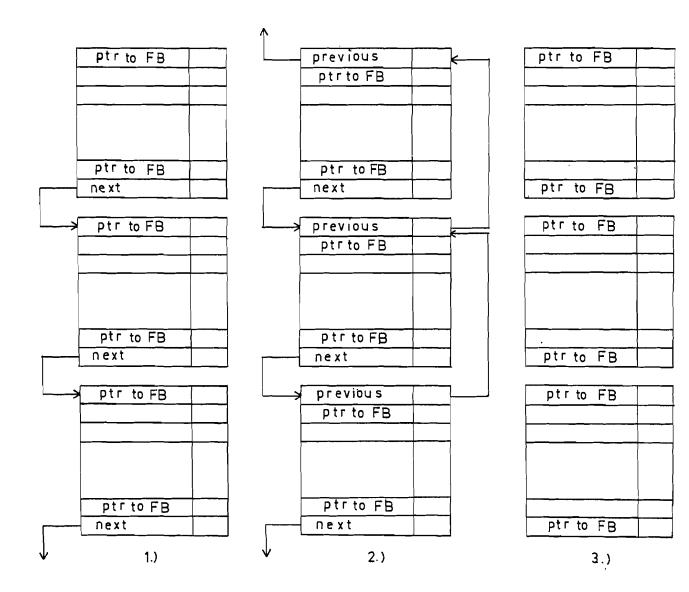

3.4.1. Free block pointer list.

Two disadvantages of the UNIX free block pointer list stand out:

- On starting with an empty disk, pointers to all free blocks on the disk have to be initialized. This leads to a tremenduously long free block pointer list. Alternatively, one could start of with a limited list and add more blocks to the list as disk usage increases.

- 2. Whenever space has to be re-allocated, for instance after deletion of a file, the pointers to the freed blocks have to be added to the list.

The process of re-allocation can best be illustrated by an example.

Assume the controller has a pointer block to the free blocks on the disk in its workspace. This particular block can be considered as the current free block pointer. Part of the blocks pointed to has allready been allocated to different files and therefore marked null. The other part is still available as free space. Refer to figure 3.10.

Two situations can occur at this point:

1. A new file is created and space has to be allocated for this file. The number of blocks to be allocated depends on the file type. Say ten blocks have to be assigned to this file initially. The controller starts looking in its current free block pointer block until it encounters a non-zero pointer which is subsequently assigned to the new file. After the current free-block-pointer block

|            |   | - |

|------------|---|---|

| null       | S |   |

| null       | S |   |

| null       | s |   |

| pointer    | S | I |

| next block | 1 |   |

ASSIGNED BLOCKS

FREE BLOCKS

pointer to next block in free block list

Figure 3.10: Current free block pointer.

assignment, the pointer in the free block pointer block is set to zero. After assigning the last pointer in the free pointer block, the controller will encounter the indirect pointer which points to the next block in the free block list. This block is then loaded in the controllers workspace and becomes the new free block pointer block.

This algorithm is straightforward and causes no serious problems.

2. A file is deleted and the blocks previuosly occupied by this file have to be registered as free blocks. If the number of blocks involved is less than the number of empty entries in the current free block pointer block, no problem occurs. The pointers to the blocks returned by the deleted file are recorded in the current free block pointer block. If however the number of blocks to be freed exceeds the number of unoccupied entries - and this will usually be the case - then a new element in the free block pointer list

will have to be created. The problem with this new element is, where to locate it on the disk. From this example we learn that the major problem using a free

block pointer list lies in the expansion of this list. We offer three alternatives to overcome this problem:

First of all, one could use one of the blocks turned free by the deleted file as the next block in the free block pointer list. Conveniently this would be the block following the last block that could be placed in the current pointer block. This would however lead to a dispersed free block pointer list since the block thus added could be located anywhere on the disk. It is considered good policy to try and confine this list to a restricted area of the disk. This way long access times for allocating free space to a new file can be avoided.

Secondly, one could use a double pointer list, meaning every block in the list contains a pointer to its predecessor and a pointer to its successor. Thus a rather fixed structure of pointer blocks is created which can be restricted to a predetermined area of the disk.

Thirdly, a fixed number of contiguous blocks could be reserved on a restricted area of the disk, similar to the Index-list described in a previous paragraph. This method however comes very close to that of a bit-map, every bit being replaced by a 4 byte pointer.

Summarizing one can say the first method leads to a dispersed free block pointer list which is quite undesirable. The second method requires a seperate adminstration of blocks that can be attached to the free block pointer list. This seperate administration can be conceptually simple, e.g. a bit-map, but the extra overhead involved for expanding the list, is considered a major disadvantage. The third solution finally, involves massive waist of disk space since a 4 byte pointer is reserved for every physical block on the disk.

In figure 3.11. the three different ways to organize the free block pointer list are drawn.

Figure 3.11: Free Block List.

# 3.4.2. Bit-map.

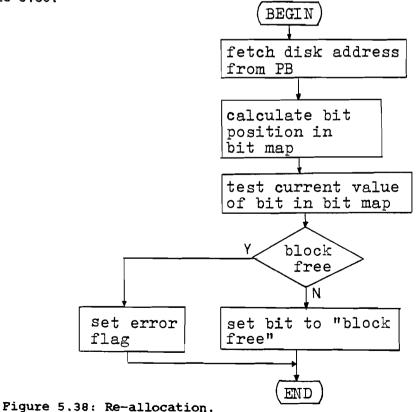

The use of a bit map for free space administration is quite common, due to its conceptual simplicity. Since every block on the disk requires only one bit of administration, the overhead is minimal. The most predominant disadvantage of a bit map solution, lies in the required calculation from bit position within the bit-map to actual block address. Furthermore it is difficult to define a fast algorithm for efficient allocation and re-allocation of free space. From the previous discussion, it is obvious that the bitmap method will be used in this controller, as opposed to the free block pointer list. The processing power of the controller is sufficient enough to overcome the problem of translating bit position within the map to physical disk address.

Concluding this section of chapter 3, I would like to state that some features of the UNIX file system are not present in the concept described here. Partially this is due to the fact that modifications were considered neccessary to meet the requirements of a controller capable for operating in a non-UNIX environment, partially it resulted from pragmatic choices made to enable an easier implementation of the file system on the controllers CPU. 3.5. Command Structure.

The most essential part of a Disk Operating System, from the user point of view, is the command set it offers. The scope of these commands determines the degree of intelligence of the controller as it manifests itself to the user.

In order to reach a functional set of commands to be implemented by the DOS, a few requirements the controller has to meet, have to be kept in mind:

- Function as background storage for user and system files.

- Easy and fast reading and writing of files.

- Both sequential and random access.

- Support of a logical file structure for the purpose of random access.

- The set of commands offered must be as small as possible for ease of use yet sophisticated enough to perform any manipulation the user whishes to do with his files.

Some of these requirements are contradictory to a certain extent so compromising need be done. In order to obtain a general purpose set of commands, a survey was made on existing operating systems and the set of commands they offer. This survey resulted in a command set, described in the following section of this chapter, which is considered to be a reasonable compromise between complexity of implementation and file manipulation capability. Two different classes of functions are distinguished, file handling commands - covered in paragraph 3.5.1. - and directory commands - covered in paragraph 3.5.2.

3.5.1. File handling commands.

Below, a list of available file handling commands is given. Every command will be elaborated upon by giving a functional description, the result of the operation following the command and a list of possible error conditions.

> Create Open Close Delete Read Write Recover Seek Insert Erase

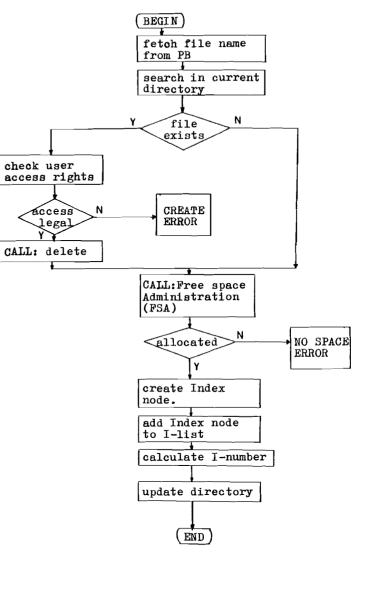

Create.

- Function : Creation of a new file by assembling its Index-node. Information regarding the users identity must be supplied for protection information and access-right validation.

- Result : The create command results in the creation of an Index-node containing all known information on the file created. The Index-node is added to the Index-list for future reference. Furthermore, an entry in the users current directory is made. If necessary, space for either the new Index-node or the directory entry must be allocated.

- Error conditions : 1. Illegal filename. The filename and filetype combination supplied by the user, allready exist in his directory. 2. No space. The physical space required to create the new Index-node and directory entry is not available.

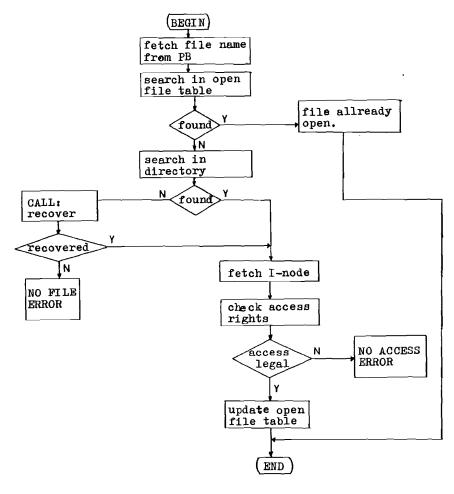

Open.

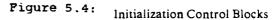

- Function : The open command activates the file specified by the user.

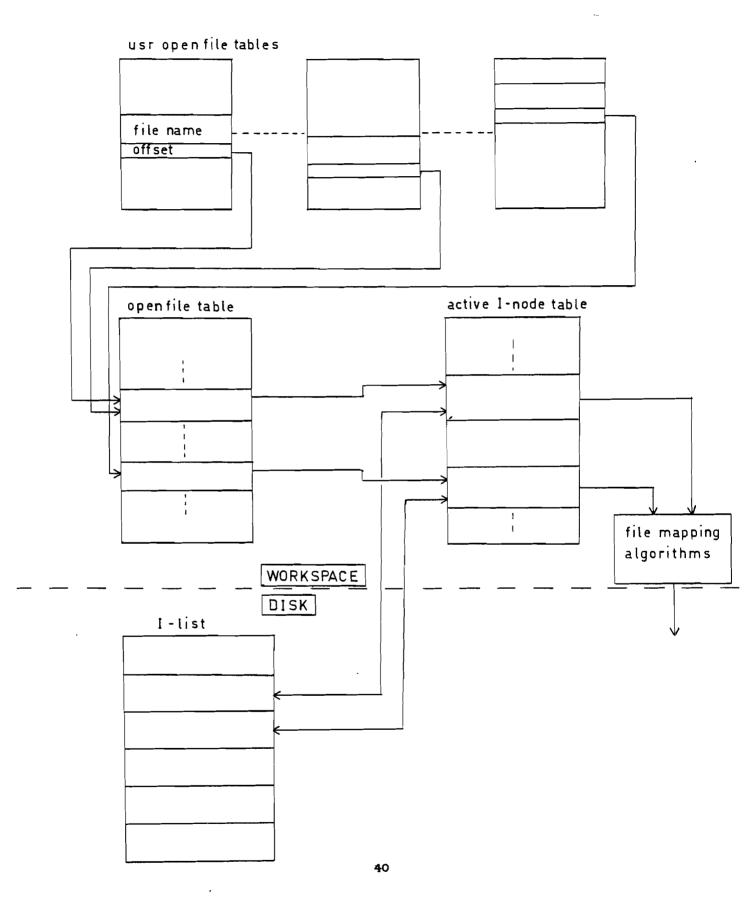

- Result : Activation of a file means the Index-node of the file is fetched from the Index-list and added to the active Index-node table in the controllers workspace. Access to this active Index-node table is obtained through the users open file table. The open file table consists of the users file names which are currently open and an offset into the active Index-node table. This substructure allows for fast access to the file for future reference. Figure 3.12. illustrates this scheme.

- Error conditions : 1. File allready open. Filename and type is encountered in the users open file table, indicating it was opened previously. This is not an error in the true sense since the file will be open after issueing the command. 2. Illegal access. User has no legal access rights to the file he specified. 3. No file. Filename specified by the user is not present in his directory or any of the directories he has access to.

Figure 3.12: File access substructure.

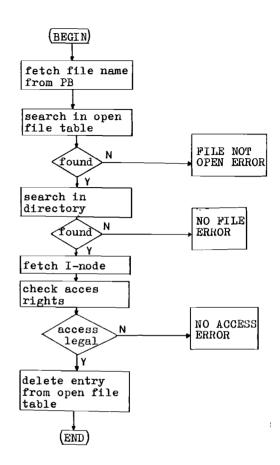

Close.

Function : Closing a file, i.e. remove the access mechanism to the file.

.

- Result : As a result of the close command, the entry in the users open file table is marked "deleted". Thus the information stored in the Index-node is maintained. However, opening of another file by the same user can result in the entry in his open file table being overwritten.

- Error conditions : 1. File not open. Files which were not opened can't be closed. Again, this is not an error in the true sense since the file will be closed after the command is given. 2. Illegal access. User tries to close a file he has no access rights to. 3. No file. File specified is not present in the users directory. Note the difference between this error condition and number 1. 'File not open' means the file exists but was not open. 'No file' means the file does not exist within the users' scope.

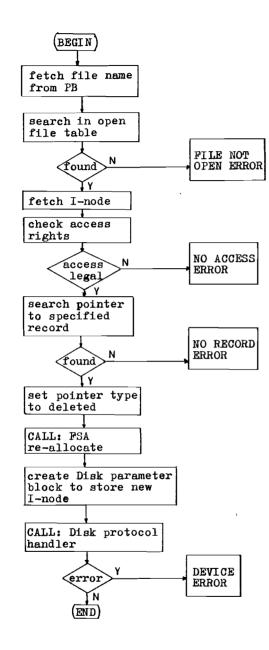

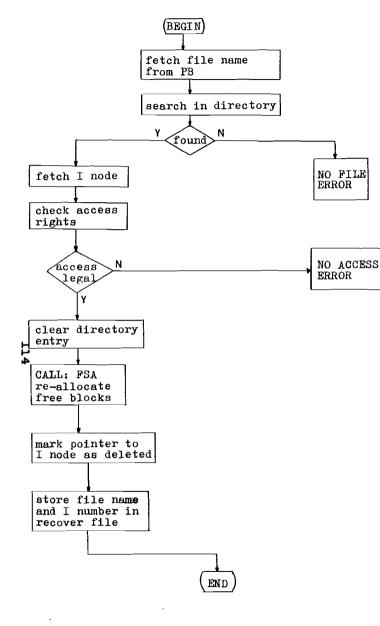

#### Delete.

- Function : Deletion of a file, specified by the user, from his directory.

- Result : Deletion of a file is actuated by marking its Index-node as "deleted". Thus the Indexnode is maintained in the hierarchy but is not available. The space occupied by a deleted Index-node can be overwritten as the result of a subsequent creation of a new file.

- Error conditions : 1. Illegal access. User has no access rights

that allow deletion of a file. Files can

only be deleted by their owner.

2. No file. File specified cannot be found

in the users directory. In essence this is

not a real error condition since the result

of issueing the command will be the absence

of the specified file.

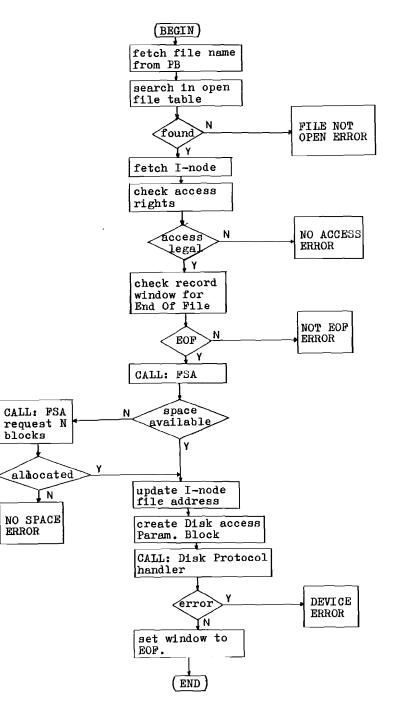

# Read.

Function : Read a logical record from the specified file. The record is obtained from the controllers workspace and transferred to the Host. If the requested record is not present there, part of the file is read from the disk and stored in the controllers workspace. The requested record can subsequently be extracted using the record size information contained in the Index-node.

Result : The result of a read operation is the transfer of a file record in sequential order from the file speciefied. Since files are stored on disk as contiguous blocks of data, the division of a file into logical records has to be done by the controller. Thus, files are allways transferred through the controller buffer.

Error conditions : 1. Illegal access. User does not have the proper access rights to read the specified file. 2. No file. Filename specified cannot be found in the users directory. 3. File not open. File wasn't opened prior to read command. 4. End of file. Either the file being read is empty or the last record of the file has been read on a previous occasion.

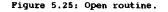

Write.

Function : Write a logical record on disk. The record is added towards the end of the specified file.

Result : The record to be written is transfered to the controller buffer. Physical writing to the disk is not neccessairilly done immediately. Writing from buffer to disk is done whenever a fixed number of blocks - minimum one - can be written at once and bufferspace has to be made available to service another request. As a matter of course, all active records of a file, present in the controllers buffer but not written to disk yet, are transfered to disk prior to a close or read command execution on the same file.

Error conditions : 1. Illegal access. User has no write access to the specified file. 2. No file. Filename specified is not present in the users' directory. 3. File not open. File not open i.e. no entry in users' open file table. 4. Not End of File. Present access location within the specified file is not positioned at the end of the file. Since records are added towards the end of the file, a seek to file end has to preceed the write command. 5. No space. Space required to store the record is not available on disk or in the controller buffer.

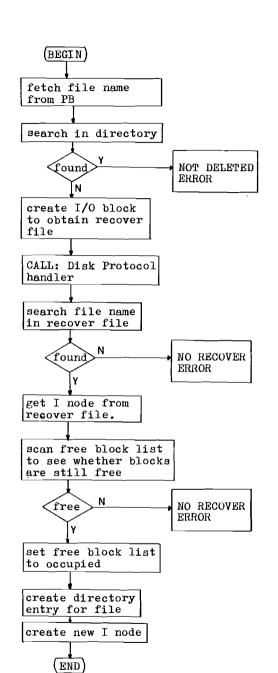

#### Recover.

- Function : Recovering a previously deleted file. The information contained in the recovered file can either be intact or distorted. Information concerning the integrity of the recovered file is supplied to the user after execution of this command.

- Result : The result of this somewhat unusual command, is based on retrieving the Index-node of the file to be recovered, from the Index-list. As described previously, deleting a file results in its Index-node being marked "deleted". This means it is still present in the Index-list where it can be found by the controller, unless the creation of a new file caused the entry to be overwritten by the new Index-node. In this case, recovery of the deleted file is impossible. The Index-number of the deleted file has to

be obtained from the recover file which was specially created for this purpose, since the normal entry in the directory has been removed.

There is yet another complication concerning the disk space previously occupied by the deleted file. Upon deletion of the file, the blocks it occupied were marked as being free . When the file is recovered, a comparison between the address information in the Index-node and the free space adminstration table has to be made. If the blocks of the recovered file are still registered as free blocks, they may still contain the proper information, though this is not neccessarily the case. This however is an uncertainty one has to accept. Therefore the user, after issueing a recover command, should also verify the information contained in the recovered file.

From the above one can conclude that this is a very complicated command with uncertain results. When implementing a command like this, one has to consider whether the advantages compensate for the problems it incures Error conditions : 1. No file. File name specified is not present in the recover file, meaning it was not deleted. 2. No I-node. Index-node of the specified file has been overwritten. 3. No data. One or more blocks previously occupied by the file have been re-allocated to other files.

Seek.

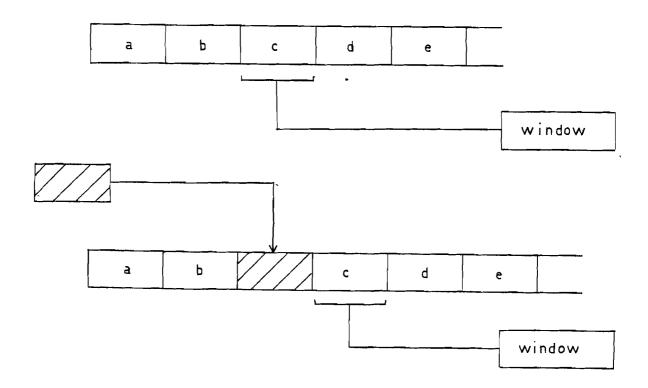

- Function : The seek command moves the window, a pointer to a record within a file, to a specified position. Thus random access within a file is possible.

- Result : The window of a file points to a record within the file. The value of this pointer is stored in the users open file table. Normally the window is incremented after every read or write operation. Thus sequential access is achieved. By means of the seek command, the window can be moved to an arbitrairy position within the file.

- Error conditions : 1. Illegal acces. User has no read access rights to the file he specified. 2. No file. Specified file cannot be found in users open file table. Either it was not opened previously or it doesn't exist at all. 3. No record. Specified record number is out of range. The window is set to EOF as a result of this.

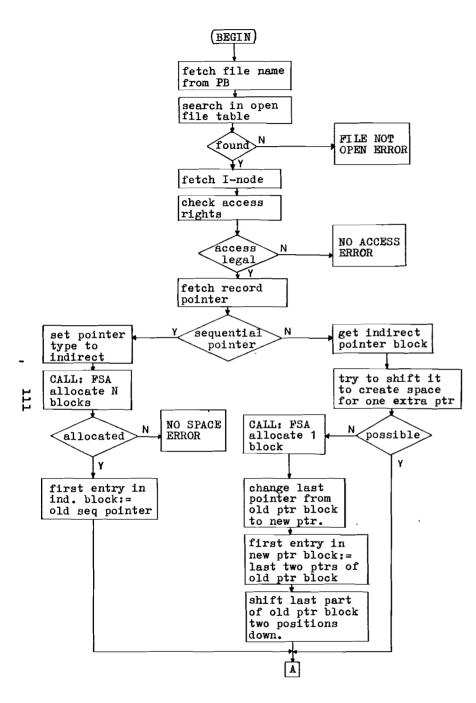

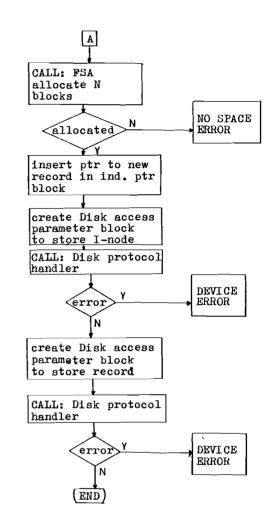

#### Insert.

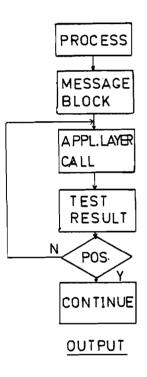

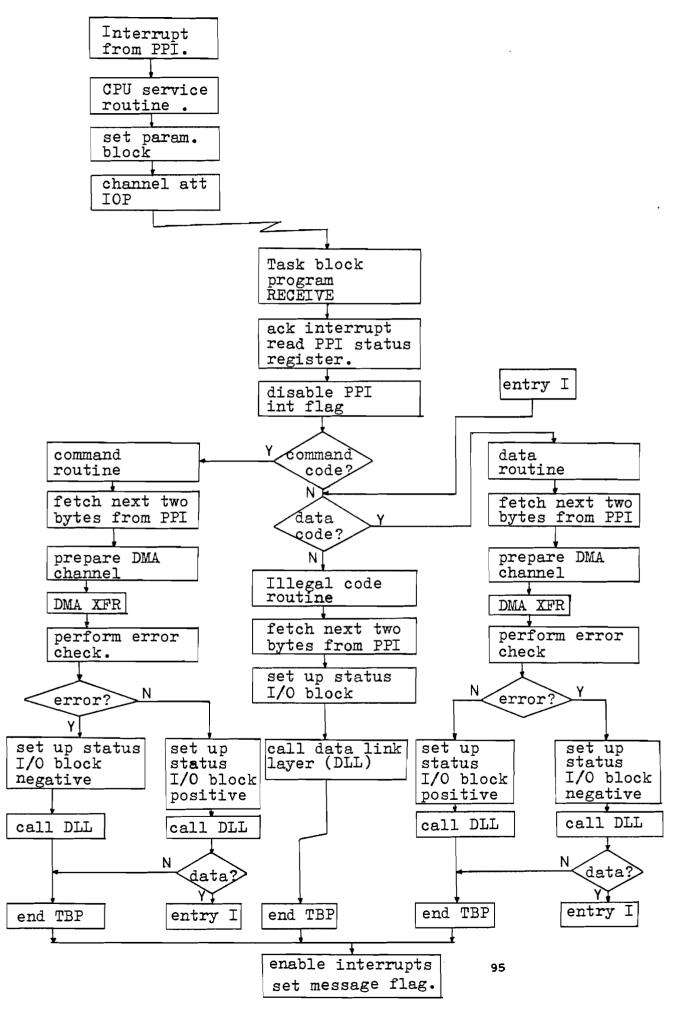

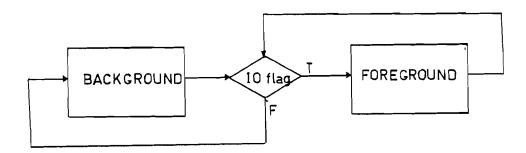

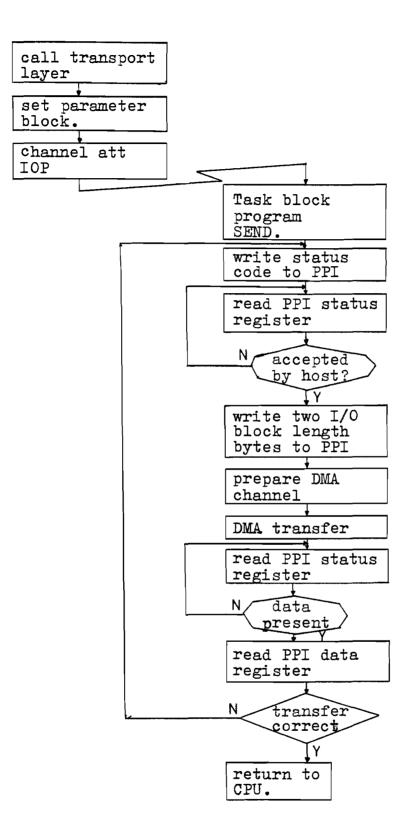

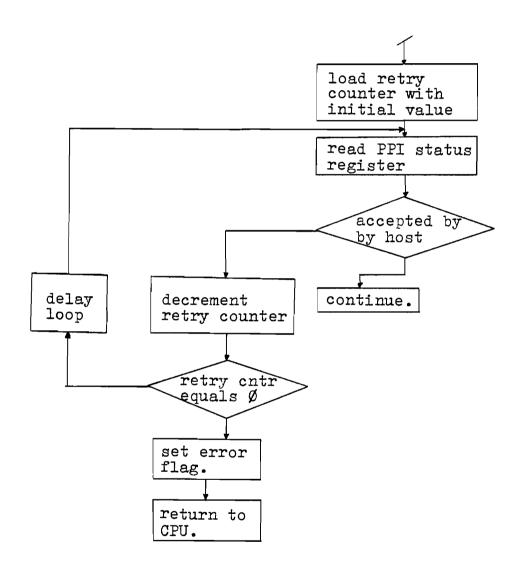

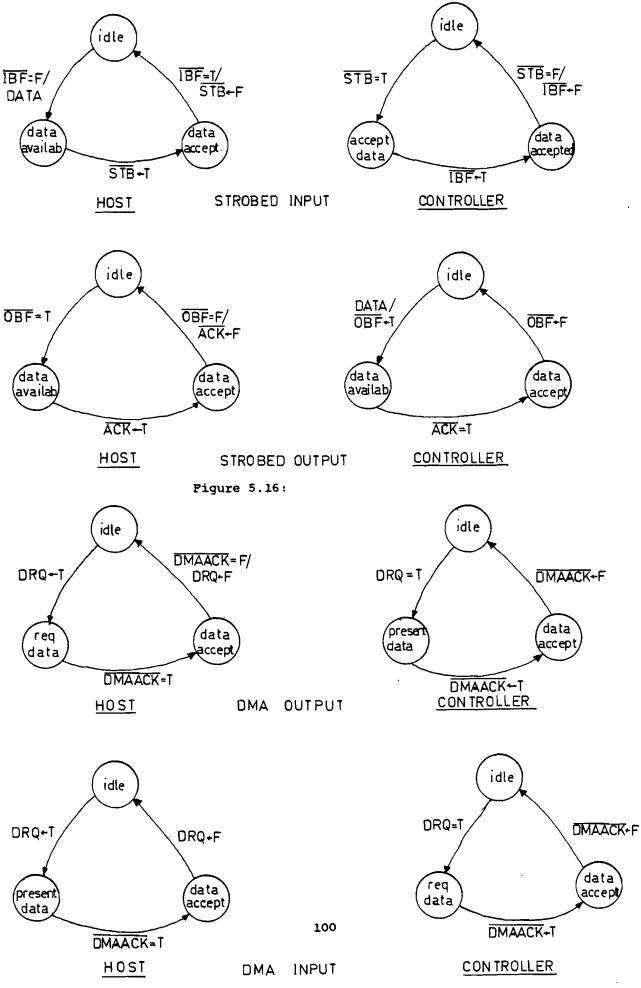

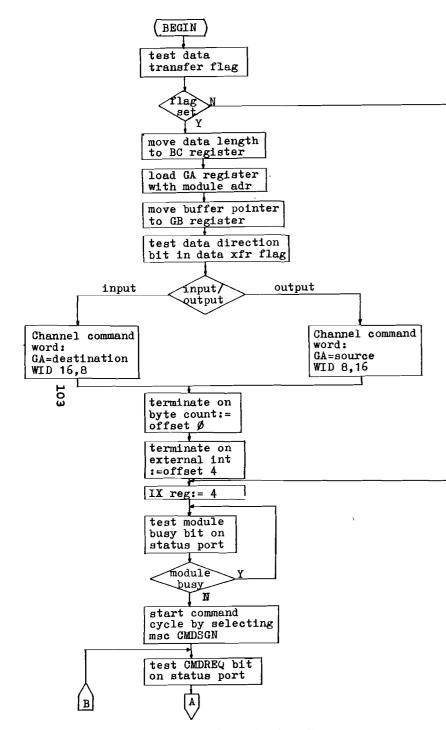

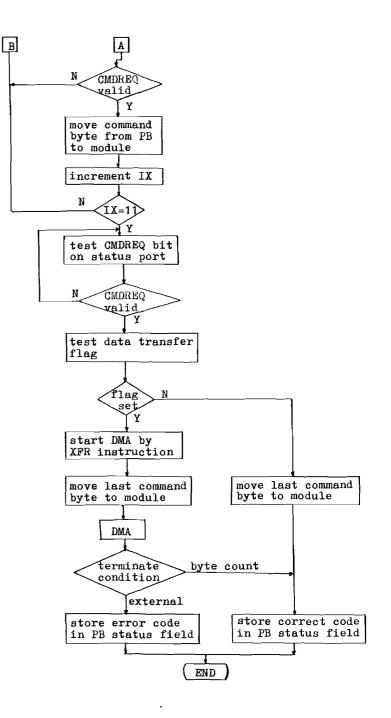

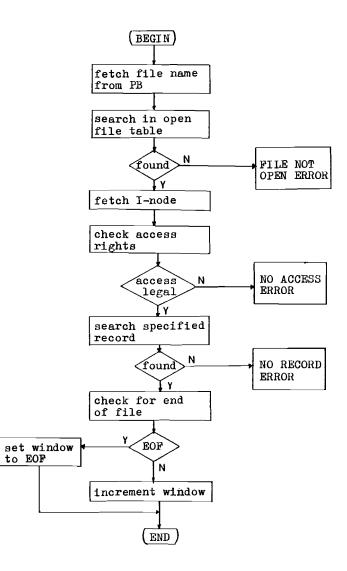

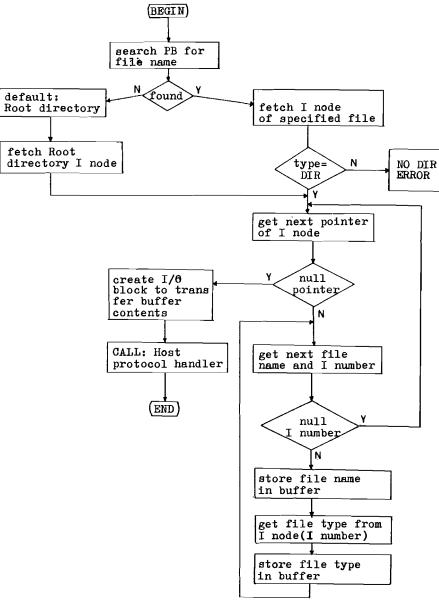

- Function : Insertion of a record in a file at the location pointed to by the window.