# ND—100 Reference Manual

ND-06.014.02 Revision A

# NOTICE

The information in this document is subject to change without notice. Norsk Data A.S assumes no responsibility for any errors that may appear in this document. Norsk Data A.S assumes no responsibility for the use or reliability of its software on equipment that is not furnished or supported by Norsk Data A.S.

The information described in this document is protected by copyright. It may not be photocopied, reproduced or translated without the prior consent of Norsk Data A.S.

Copyright C 1984 by Norsk Data A.S

This manual is in loose leaf form for ease of updating. Old pages may be removed and new pages easily inserted if the manual is revised.

The loose leaf form also allows you to place the manual in a ring binder (A) for greater protection and convenience of use. Ring binders with 4 rings corresponding to the holes in the manual may be ordered in two widths, 30 mm and 40 mm. Use the order form below.

The manual may also be placed in a plastic cover (B). This cover is more suitable for manuals of less than 100 pages than for large manuals. Plastic covers may also be ordered below.

Please send your order to the local ND office or (in Norway) to:

Documentation Department Norsk Data A.S P.O. Box 4, Lindeberg gård Oslo 10

# **ORDER FORM**

| I would like to order |                                             |  |  |

|-----------------------|---------------------------------------------|--|--|

|                       | Ring Binders, 30 mm, at nkr 20,- per binder |  |  |

|                       | Ring Binders, 40 mm, at nkr 25,- per binder |  |  |

|                       | Plastic Covers at nkr 10,- per cover        |  |  |

| Comp<br>Addre         | eanyess                                     |  |  |

|                       |                                             |  |  |

|          | PRINTING RECORD                                                  |

|----------|------------------------------------------------------------------|

| Printing | Notes                                                            |

| 03/79    | ORIGINAL PRINTING                                                |

| 01/82    | SECOND PRINTING                                                  |

| 01/83    | Revision A                                                       |

|          | The following pages are revised or added:                        |

|          | vxiv, 1-16, 1-17, 2-18, 2-19, 2-27, 2-29, 2-41, 2-42             |

|          | 3-1, 3-21, 3-27, 3-38, 3-41, 3-47, 3-48, 3-53, 3-55, 3-58, 3-62, |

|          | 3-72 to 3-74, 3-76, 3-80, 3-83 to 3-94                           |

|          | 4-17, A-9 to A-13, D-1, D-2, E-1, E-2, F-1, F-2                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          | ·                                                                |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

|          |                                                                  |

ND--100 Reference Manual ND--06.014.02 Rev. A

Febr. 1983

NORSK DATA A.S P.O. Box 4, Lindeberg gård Oslo 10, Norway Manuals can be updated in two ways, new versions and revisions. New versions consist of a complete new manual which replaces the old manual. New versions incorporate all revisions since the previous version. Revisions consist of one or more single pages to be merged into the manual by the user, each revised page being listed on the new printing record sent out with the revision. The old printing record should be replaced by the new one.

New versions and revisions are announced in the ND Bulletin and can be ordered as described below.

The reader's comments form at the back of this manual can be used both to report errors in the manual and to give an evaluation of the manual. Both detailed and general comments are welcome.

These forms, together with all types of inquiry and requests for documentation should be sent to the local ND office or (in Norway) to:

Documentation Department Norsk Data A.S P.O. Box 4, Lindeberg gård Oslo 10

# **PREFACE**

# THE PRODUCT

ND-100 is a general purpose computer which is used in many applications like:

- Commercial data processing

- Research

- Education

- Process control

#### THE READER

- Technical and maintenance personnel requiring detailed information about the ND-100 and it's instruction repertoire.

- Programmers and operators needing detailed information about the ND-100 instruction repertoire.

# PREREQUISITE KNOWLEDGE

General computer knowledge is recommended.

# THE MANUAL

This manual contains two main parts:

- Sections 1 and 2 describe the main building blocks of the ND-100 and their functions.

- Section 3 describes the ND-100 instruction repertoire in detail.

Section 4 describes the operator's interactions with the ND-100.

# RELATED MANUALS

The following manuals give more detailed information about the ND-100's building blocks.

- ND-100 Functional Description (ND-06.015).

- ND-100 Input/Output System (ND-06.016).

# TABLE OF CONTENTS

+ + +

| Section:                                 | Page                                                                                                                                           |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                        | INTRODUCTION TO ND-1001—1                                                                                                                      |

| 1.1<br>1.2                               | General Characteristics 1—1 ND-100 Functional Modules 1—3                                                                                      |

| 1.2.1<br>1.2.2                           | General1—3  ND-100 Central Processing Unit (CPU) Module1—5                                                                                     |

| 1.2.2.1                                  | CPU Characteristics1—6                                                                                                                         |

| 1.2.3                                    | ND-100 Architecture1—7                                                                                                                         |

| 1.2.3.1<br>1.2.3.2<br>1.2.3.3<br>1.2.3.4 | General       1-7         ND-100 Configuration Examples       1-8         Multiprocessor Systems       1-9         Remote Operation       1-10 |

| 1.3<br>1.4<br>1.5                        | The Interrupt System                                                                                                                           |

| 1.5.1<br>1.5.2<br>1.5.3                  | Main Memory       1-13         Cache Memory       1-13         Multiport Memory       1-13                                                     |

| 1.6                                      | The Input/Output System1—14                                                                                                                    |

| 1.6.1<br>1.6.2                           | Programmed Input/Output — PIO                                                                                                                  |

| 1.7<br>1.8                               | ND-100 Peripheral Equipment                                                                                                                    |

| 1.8.1<br>1.8.2<br>1.8.3                  | The Operating System                                                                                                                           |

| 2                                        | SYSTEM DESCRIPTION2—1                                                                                                                          |

| 2 1                                      | Central Processor                                                                                                                              |

| Section: | Pa                                                 | age. |

|----------|----------------------------------------------------|------|

| 2.1.1    | General2-                                          | 1    |

| 2.1.2    | Internal Communication2-                           |      |

| 2.1.3    | The Address Arithmetic2-                           |      |

| 2.1.4    | Instruction Fetch2-                                |      |

| 2.1.5    | Prefetch2-                                         |      |

| 2.1.6    | Instruction Execution2-                            |      |

| 2.1.7    | Main Arithmetic2-                                  |      |

| 2.1.8    | The Register File2-                                |      |

| 2.1.9    | Status Indicators2-                                |      |

| 2.2      | The Interrupt System2-                             | -10  |

| 2.2.1    | General2-                                          | -10  |

| 2.2.2    | Functional Description2-                           | -12  |

| 2.2.3    | The External Interrupt System2-                    | -14  |

| 2.2.4    | The Internal Interrupt System2-                    | -16  |

| 2.2.4.1  | The IIC and IIE Registers2-                        | -17  |

| 2.2.4.2  | Internal Hardware Status Interrupts2-              | -18  |

| 2.2.4.3  | Reset of the IIC Register2-                        |      |

| 2.2.5    | Programmming Control of the Interrupt System2-     | -21  |

| 2.2.5.1  | Programmming the PID and PIE Registers2-           | -21  |

| 2.2.5.2  | The WAIT, ION and IOF Instruction2                 | -22  |

| 2.2.5.3  | The Previous Level Register, PVL2-                 | -22  |

| 2.2.5.4  | Vectored Interrupts and the IDENT Instructions .2- |      |

| 2.2.6    | Initializing of the Interrupt System2-             | -24  |

| 2.3      | The Memory Management System2—                     | -25  |

| 2.3.1    | General2—                                          | -25  |

| 2.3.2    | Memory Management Architecture2—                   | -26  |

| 2.3.3    | The Paging System2—                                |      |

| 2.3.4    | The Shadow Memory2—                                |      |

| 2.3.5    | The Page Tables2—                                  |      |

| 2.3.5.1  | Page Used and Written in Page2—                    | -34  |

| 2.3.5.2  | Page Table Selection2—                             | 34   |

| 2.3.6    | Memory Protection System2—                         | -35  |

| 2.3.6.1  | Page Protection System2—                           | -35  |

| 2.3.6.2  | Ring Protection System2—                           |      |

| 2.3.7    | Privileged Instructions2—                          | 39   |

| 2.3.8    | Memory Management Control and Status2—             |      |

| Section:  |                                          | Page: |

|-----------|------------------------------------------|-------|

| 2.3.8.1   | The PON and POF Instructions             | 240   |

| 2.3.8.2   | Paging Control Registers                 | 2—41  |

| 2.3.8.3   | Paging Status Register                   |       |

| 2.3.9     | The SEX and REX Instructions             | 2—43  |

| 2.4       | ND-100 Memory System                     | 2—44  |

| 2.4.1     | General                                  | 2—44  |

| 2.4.2     | ND-100 Memory Architecture               | 2—46  |

| 2.4.2.1   | Local (Main) Memory                      | 2—47  |

| 2.4.2.2   | Memory Module Placement in ND-100 Bus    | 2—47  |

| 2.4.2.3   | The Position Code                        | 2—47  |

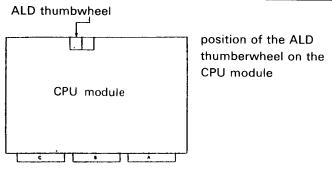

| 2.4.2.4   | The Thumbwheel Setting                   |       |

| 2.4.3     | Memory Error Correction                  | 2—50  |

| 2.4.4     | Memory Control and Status                | 2—52  |

| 2.4.4.1   | Error Correction Control Register (ECCR) | 2—52  |

| 2.4.4.2   | Memory Status Regsiters (PEA and PES)    |       |

| 2.4.5     | Multiport Memory                         | 2—54  |

| 2.4.5.1   | Big Multiport Memory (BMPM)              | 2—54  |

| 2.4.5.2   | Multiport Memory 4 (MPM4)                |       |

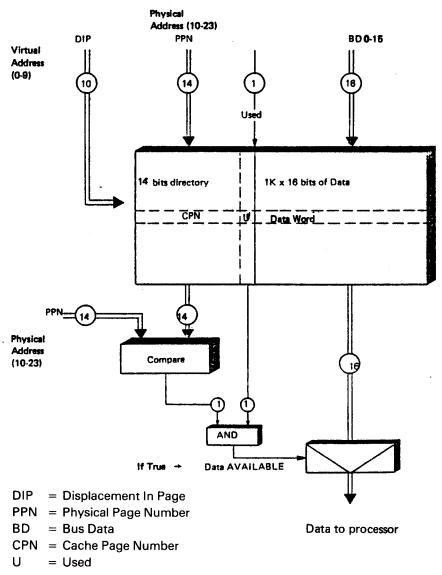

| 2.4.6     | Cache Memory                             | 2—55  |

| 2.4.6.1   | Cache Memory Architecture                | 2—55  |

| 2.4.6.2   | Cache Memory Organization                | 256   |

| 2.4.6.3   | Cache Control and Status                 | 2—58  |

| 2.4.6.3.1 | Cache Control                            | 2—58  |

| 2.4.6.3.2 | Cache Status Register                    |       |

| 2.5       | ND-100 Input/Output System               | 2—60  |

| 2.5.1     | General                                  | 2_60  |

| 2.5.2     | ND-100 I/O Architecture                  |       |

| 2.5.3     | ND-100 Card Crate — Physical Layout      |       |

| 2.5.4     | The ND-100 Bus                           |       |

| 2.5.5     | ND-100 I/O System Functional Description |       |

| 2.5.6     | Programmed Input/Output — PIO            |       |

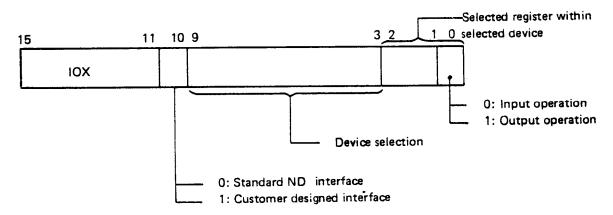

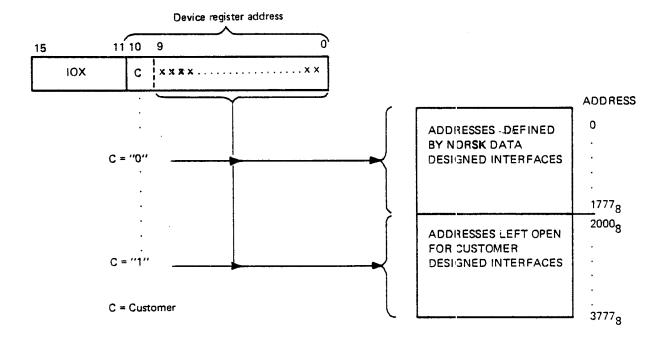

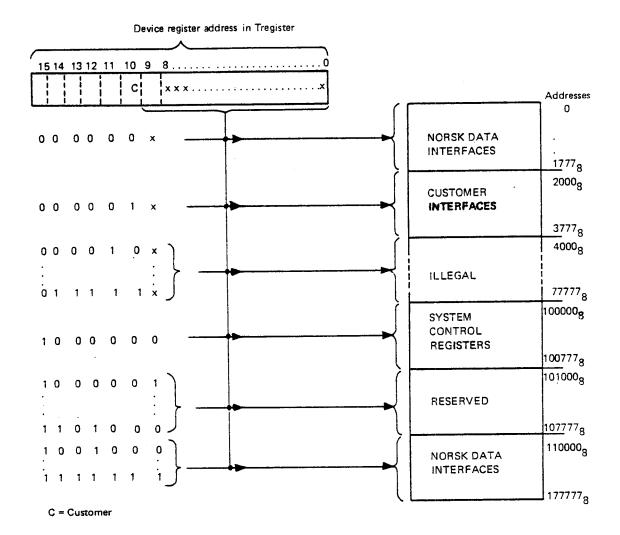

| 2.5.6.1   | The Input/Output Instruction — IOX       | 2 67  |

| 2.5.6.2   | Interface Channels and Registers         |       |

| 2.5.6.3   | Control and Status Registers             |       |

| 2.5.7     | Direct Memory Access (DMA)               | 2_ 72 |

|           | 2.100t Molliony 700033 (DIMA)            | 2—12  |

| Section:  |                                            | Page        |

|-----------|--------------------------------------------|-------------|

| 2.5.7.1   | General                                    | 2—72        |

| 2.5.7.2   | DMA Controller Operation                   |             |

| 2.5.7.2.1 | Initialization                             | 2—73        |

| 2.5.7.2.2 | Transfer                                   | 2—73        |

| 2.5.7.2.3 | Termination and Status Check               | 2—73        |

| 2.5.7.2.4 | General Considerations                     |             |

| 2.5.8     | The I/O System and the Interrupt System    | 2—75        |

| 2.5.8.1   | General                                    | 2—75        |

| 2.5.8.2   | Interrupt Level Usage                      | 2—75        |

| 2.5.8.3   | Device Interrupt Identification            |             |

| 2.5.9     | Programming Specifications for I/O Devices | 0 70        |

|           | on the CPU Board                           | 2—76        |

| 2.5.9.1   | The Real-time Clock                        | 2 77        |

| 2.5.9.2   | The Current Loop Interface                 |             |

| 2.0.0.2   | The durent Loop interface                  | 2—11        |

| 2.6       | ND-100 Bus Extender (BEX)                  | 2—79        |

| 2.6.1     | General                                    | 2—79        |

| 2.6.2     | Bus Extender Architecture                  |             |

| 3         | ND-100 INSTRUCTIONS                        | 3—1         |

|           |                                            |             |

| 3.1       | Introduction to the Instruction Repertoire | 3—1         |

| 3.1.1     | General                                    | <b>3</b> —1 |

| 3.1.2     | Instruction and Data Formats               | 3—3         |

| 3.1.2.1   | Single Bit                                 | 3—3         |

| 3.1.2.2   | 8 Bit Byte                                 | 3—4         |

| 3.1.2.3   | 16 Bit Word                                |             |

| 3.1.2.4   | 32 Bit Double Word                         |             |

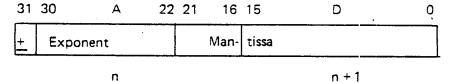

| 3.1.2.5   | 48 Bit Floating Point Word                 |             |

| 3.1.2.6   | 32 Bit Floating Point Word                 |             |

| 3.2       | The Instruction Repertoire                 | 3—9         |

| 3.2.1     | Memory Reference Instructions              | 3—9         |

| 3.2.1.1   | Addressing Structure                       | 3—9         |

| 3.2.1.2   | Store Instructions                         |             |

| 3.2.1.3   | Load Instructions                          |             |

| Section:  |                                           | Page: |

|-----------|-------------------------------------------|-------|

|           |                                           |       |

| 3.2.1.4   | Arithmetical and Logical Instructions     | 3—21  |

| 3.2.1.5   | Sequencing Instructions                   |       |

| 3.2.1.6   | Byte Instructions                         |       |

| 3.2.1.7   | Extended BYTE-instructions                | 3—27  |

| 3.2.2     | Register Instructions                     | 3—30  |

| 3.2.2.1   | Floating Point Conversion Instructions    | 3—30  |

| 3.2.2.1.1 | Standard 48 Bit Floating Point Conversion | 3—30  |

| 3.2.2.1.2 | Optional 32 Bit Floating Point Conversion |       |

| 3.2.2.2   | Shift Instructions                        | 3—33  |

| 3.2.2.3   | Register Operations                       | 3—36  |

| 3.2.2.3.1 | ROP — Register Operation Instructions     | 3—38  |

| 3.2.2.3.2 | Extended Register Operation Instructions  |       |

| *         |                                           |       |

| 3.2.2.4   | Skip Instructions                         | 3—47  |

| 3.2.2.5   | Argument Instructions                     | 3—50  |

| 3.2.2.6   | Bit Operation Instructions                | 3—53  |

| 3.2.2.6.1 | Bit Skip Instructions                     | 3—54  |

| 3.2.2.6.2 | Bit Set Instructions                      | 3—54  |

| 3.2.2.6.3 | One Bit Accumulator Instructions          | 3—55  |

| 3.2.3     | System Control Instruction                | 3—56  |

| 3.2.3.1   | Monitor Call Instruction                  | 3—56  |

| 3.3       | Privileged Instructions                   | 3—57  |

| 3.3.1     | General                                   | 3—57  |

| 3.3.2     | Register Block Instructions               | 3—57  |

| 3.3.3     | Inter-level Register Instructions         | 3—59  |

| 3.3.4     | Accumulator Transfer Instructions         | 3—60  |

| 3.3.5     | Input/Output Control Instructions         | 3—63  |

| 3.3.5.1   | Extension of the Device Register Address  | 3—64  |

| 3.3.6     | System Control Instructions               | 3—64  |

| 3.3.6.1   | Interrupt Control Instructions            | 3—65  |

| 3.3.6.2   | Memory Management Control Instructions    | 3—68  |

| 3.3.6.3   | Wait or Give Up Priority                  | 3—70  |

| 3.3.7     | Examine and Deposit                       | 3—71  |

| 3.3.8     | Load Writeable Control Store              |       |

| 3.3.9     | Customer Specified Instructions           | 3—73  |

| 3.3.10    | Physical Memory Read/Write Instructions   | 3—74  |

|   | Section:  |                                                       | Page |

|---|-----------|-------------------------------------------------------|------|

|   | 3.3.10.1  | Format of Instructions                                | 3—74 |

|   | 3.3.10.2  | Addressing                                            |      |

|   | 3.4       | Instructions in the "Communical Fig. 1.1.             |      |

|   | 0.4       | Instructions in the «Commercial Extended» (CE) Option | 3_76 |

|   |           | (-2) opion                                            |      |

|   | 3.4.1     | Decimal Instructions                                  | 3—76 |

|   | 3.4.1.1   | Data Formats for Decimal Instructions                 | 3—76 |

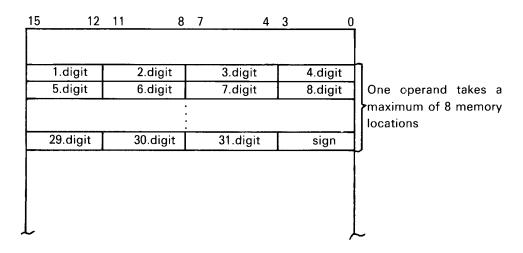

|   | 3.4.1.1.1 | Packed Decimal Number                                 | 3_76 |

|   | 3.4.1.1.2 | ASCII Coded Decimal Number                            |      |

|   | 3.4.1.2   | The Decimal Instructions                              | •    |

|   |           |                                                       |      |

|   | 3.4.2     | Stack Handling Instructions                           | 3—85 |

|   | 3.4.2.1   | Data Structure Operated upon by the                   |      |

|   |           | Instructions                                          | 3—85 |

| 1 | 3.5       | Instructions in the CX-Option                         | 3—87 |

|   | 3.5.1     | Decimal Instructions                                  | 2 07 |

|   | 3.5.2     | Stack Handling Instructions                           |      |

|   | 3.5.3     | Move Words                                            |      |

|   | 3.5.4     | Test and Set                                          |      |

|   | 3.5.5     | Read Don't Use Cache                                  |      |

|   | 3.5.6     | SINTRAN III Segment Change Instructions               | 3—92 |

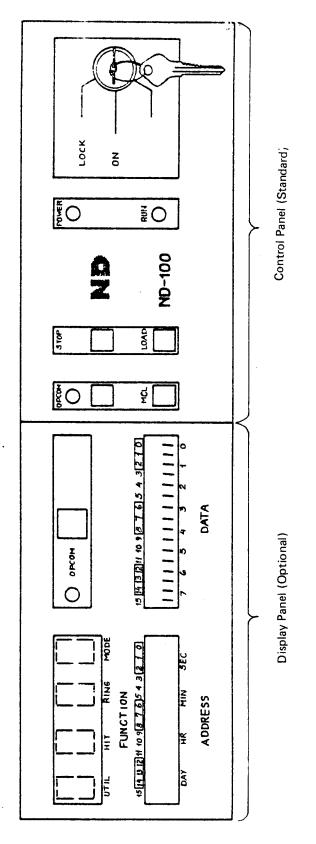

|   | 4         | OPERATOR'S INTERACTION                                | 4—1  |

|   | 4.1       | Control Panel Push Buttons                            | 4—1  |

|   | 4.1.1     | The Panel Lock Key                                    | 4 2  |

|   | 4.1.2     | Status Indicators                                     |      |

|   | 4.2       | Microprogram for Operator's Communication             | 4—4  |

|   | 4.2.1     | General Considerations                                |      |

|   | 4.2.2     | Control Functions                                     |      |

|   |           | Control 1 diletions                                   | 4—0  |

|   | 4.2.2.1   | System Control                                        | 4—6  |

|   | 4.2.2.1.1 | Master Clear                                          | 4—6  |

|   | 4.2.2.1.2 | Stop                                                  |      |

|   | 4.2.2.1.3 | ALD Load                                              |      |

|   | 4.2.2.1.4 | General Load                                          |      |

|   | 4.2.2.1.5 | Leave MOPC                                            | 4—9  |

| Section:  |                                      | Page: |

|-----------|--------------------------------------|-------|

| 4000      |                                      | 4 ^   |

| 4.2.2.2   | Program Execution                    | 4—8   |

| 4.2.2.2.1 | Start Program                        | 4—8   |

| 4.2.2.2.2 | Continue Program                     | 4—8   |

| 4.2.2.2.3 | Single Instruction                   | 4—9   |

| 4.2.2.2.4 | Instruction Breakpoint               | 4—9   |

| 4.2.2.2.5 | Manual Instruction                   | 4—8   |

| 4.2.2.2.6 | Single I/O Instruction Function      | 4—9   |

| 4.2.2.3   | Miscellaneous Functions              | 4—10  |

| 4.2.2.3.1 | Internal Memory Test                 | 4—10  |

| 4.2.2.3.2 | Delete Entry                         | 4—10  |

| 4.2.2.3.3 | Current Location Counter             | 4—10  |

| 4.2.3     | Monitor Functions                    | 4—11  |

| 4.2.3.1   | Memory Functions                     | 4—11  |

| 4.2.3.1.1 | Physical Examine Mode                | 4—11  |

| 4.2.3.1.2 | Virtual Examine Mode                 | 4—11  |

| 4.2.3.1.3 | Memory Examine                       | 4—12  |

| 4.2.3.1.4 | Memory Deposit                       |       |

| 4.2.3.1.5 | Deposit Rules                        | 4—13  |

| 4.2.3.1.6 | Memory Dump                          | 4—13  |

| 4.2.3.2   | Register Functions                   | 4—14  |

| 4.2.3.2.1 | Register Examine                     |       |

| 4.2.3.2.2 | Register Deposit                     |       |

| 4.2.3.2.3 | Register Dump - RD                   |       |

| 4.2.3.2.4 | User Register - U                    |       |

| 4.2.3.2.5 | Operator Panel Switch Register - OPR | 4—16  |

| 4.2.3.3   | Internal Register Functions          | 4—17  |

| 4.2.3.3.1 | Internal Register Examine            |       |

| 4.2.3.3.2 | Internal Register Deposit            |       |

| 4.2.3.3.3 | Internal Register Dump - IRD         |       |

| 4.2.3.3.4 | A Scratch Register Dump - RDE        | 4—19  |

| 4.2.4     | Display Functions                    | 4—20  |

| 4.2.4.1   | Displayed Format                     |       |

| 4.2.4.2   | Display Memory Bus                   |       |

| 4.2.4.3   | Display Activity                     | 421   |

# xiv

| Section:                      |                                                                                       | Page: |

|-------------------------------|---------------------------------------------------------------------------------------|-------|

| 4.2.5                         | Bootstrap Loaders                                                                     | 4—22  |

| 4.2.5.1<br>4.2.5.2<br>4.2.5.3 | Binary Format Load                                                                    | 4—23  |

| 4.3                           | The Display                                                                           | 4—25  |

| 4.3.1<br>4.3.2                | General The Different Display Functions                                               |       |

| Appendixes:                   |                                                                                       | Page: |

| Α                             | ND-100 INSTRUCTIONS                                                                   | A—1   |

| A.1<br>A.2                    | ND-100 Instruction CodesND-100 Instruction Execution Times                            |       |

| В                             | MODEL 33 ASR/KSR TELETYPE CODE (ASCII) IN<br>BINARY FORM                              | B—1   |

| С                             | STANDARD ND-100 DEVICE REGISTER ADDRESSES AND IDENT CODES                             | C—1   |

| D                             | INTERNAL REGISTERS                                                                    | D—1   |

| E                             | OPERATOR'S COMMUNICATION INSTRUCTION SURVEY                                           | E—1   |

| E.1<br>E.2<br>E.3             | Control Functions (Does not affect DISPLAY)  Display Functions (Affects only DISPLAY) | E-2   |

| F                             | ND-100 TECHNICAL SPECIFICATIONS                                                       | F—1   |

| F.1<br>F.2                    | SpecificationsPhysical                                                                |       |

# 1 INTRODUCTION TO ND-100

# 1.1 GENERAL CHARACTERISTICS

ND-100 is a general purpose computer and it is used in many applications like:

- Commercial data processing.

- Research.

- Education.

- Process control.

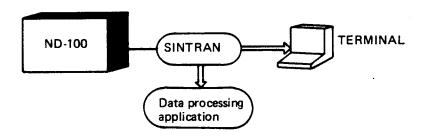

ND-100 is completely software compatible with NORD 10/S and runs the same operating system, SINTRAN III /VS.

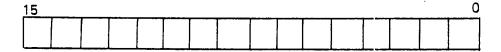

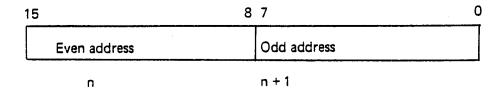

The ND-100 Central Processing Unit (CPU) is placed on a single module. The word length is 16 bits in parallel.

Figure 1.1: The Operating System SINTRAN III/VS allows the ND-100 to be used in many Applications.

# 1.2 ND-100 FUNCTIONAL MODULES

#### 1.2.1 General

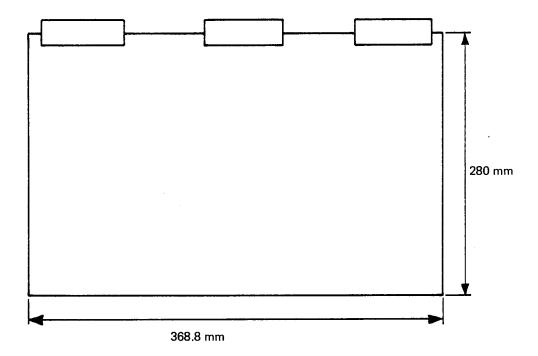

A standard ND-100 printed board module size is 366.8 mm x 280 mm.

The board size, together with the use of Large Scale Integrated (LSI) circuits, allows:

- Small physical dimensions.

- Closely related functions placed on the same module, thus reducing external wiring to a minimum.

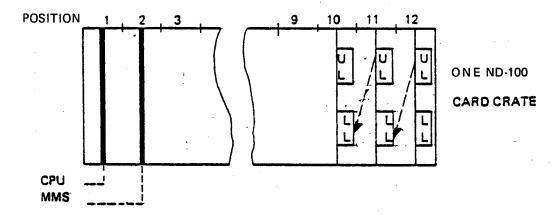

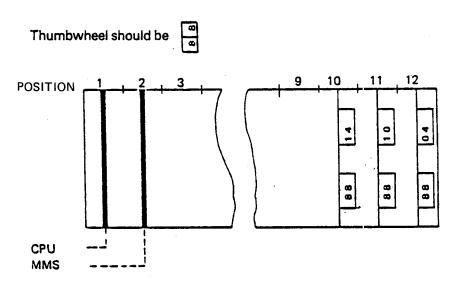

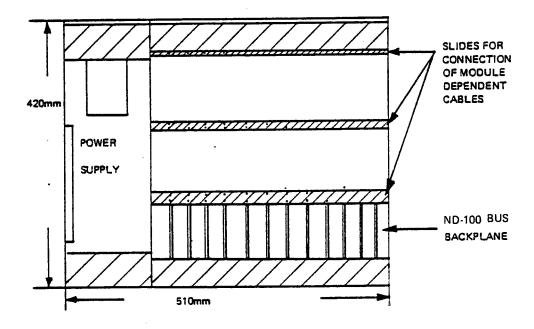

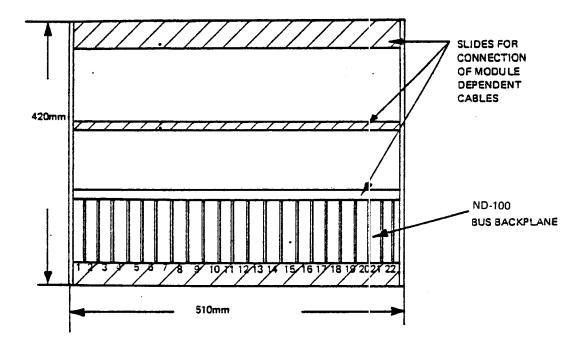

Communication between ND-100 functional modules is done through an advanced high-speed bus, called ND-100 bus. The ND-100 bus is a printed back plane. The bus is available in two versions, one for connecting 12 modules and one for connecting 21 modules. The two versions are mounted in different card crates and different cabinets.

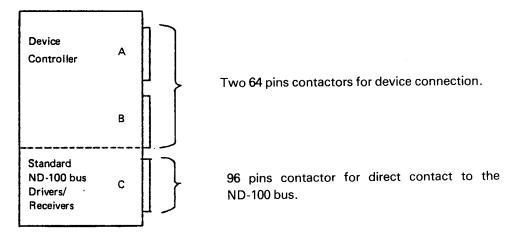

Figure 1.2: The Standard ND-100 Printed Board Module.

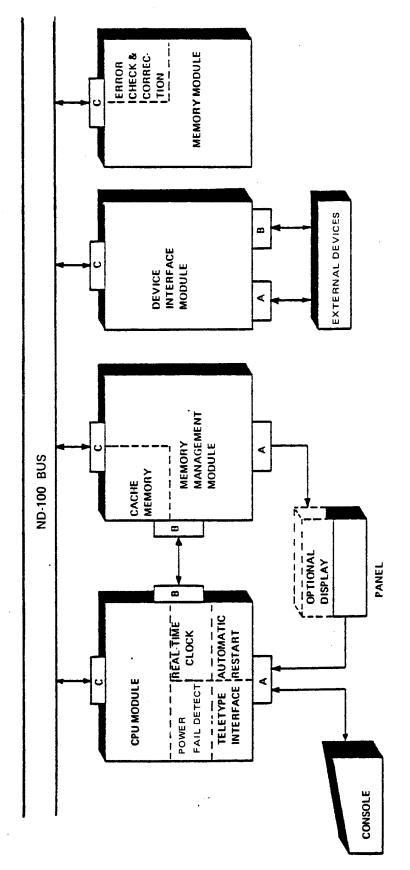

Figure 1.3: ND-100 Modules Connection (A, B and C are Plugs on the Modules).

# 1.2.2 ND-100 Central Processing Unit (CPU) Module

The CPU module contains, in addition to the CPU itself:

- A real-time clock.

- A current loop terminal interface with switch selectable speeds, 110 9600 baud/bps (bits per second).

- Power fail and automatic restart.

# 1.2.2.1 CPU Characteristics

#### The Processor

ND-100 CPU is a 16 bit parallel processor designed around the bit slice ALU (arithmetic logic unit) element.

The processor is controlled by a microprogram. The following is implemented in the microprogram:

- All instructions.

- Operator communication.

- Built-in test routines.

- Bootstrap loaders.

The microprogram is physically located in a 2k word by 64 bit Read Only Memory (ROM). One microinstruction is fetched and executed in the internal CPU cycle time. The cycle time is 150 ns for the fast CPU and 190 ns for the slow version.

#### Instruction Prefetch

A fast processor should not have to wait for instructions. In order to reduce instruction fetch waiting time, the ND-100 CPU will normally hold two instructions, the current executing instruction and the next one. This is accomplished by fetching the next instruction while executing the current instruction.

#### Special Feature

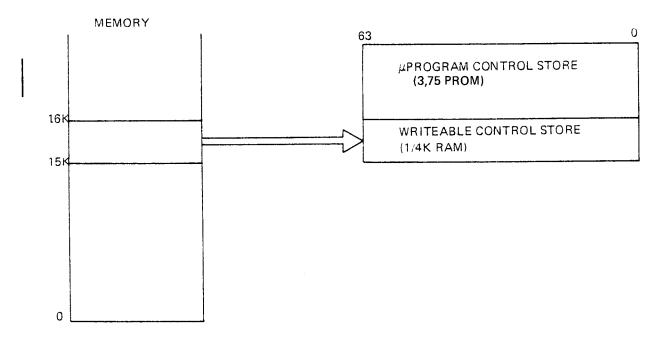

To allow dynamic microprogramming, a 256 word by 64 bit writeable control store is available as an option.

#### Instruction Set and Data Format

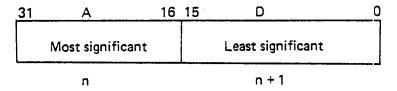

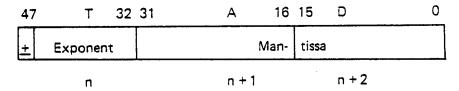

Although a standard ND-100 word is 16 bits, the computer has a comprehensive instruction set which includes operations on:

- Bits.

- Bytes.

- Single words.

- Double words.

- Triple words.

- Register file.

- Fixed or floating point arithmetic (32 or 48 bit word).

# 1.2.3 ND-100 Architecture

#### 1.2.3.1 General

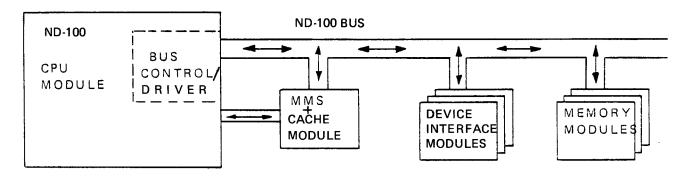

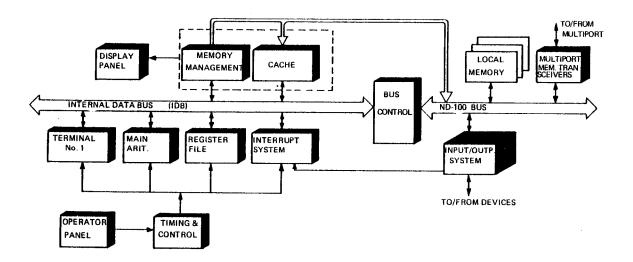

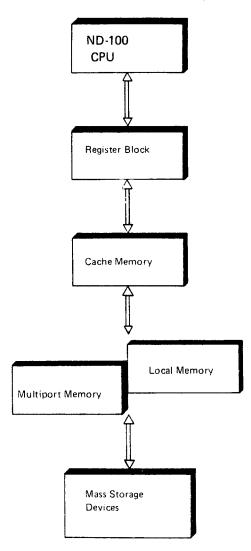

Figure 1.4 shows the ND-100 bus structure. The main highway for data and addresses in the system is the ND-100 bus. Data and address flow are shown by the arrows.

MMS = Memory Management System

Figure 1.4: ND-100 Bus Structure

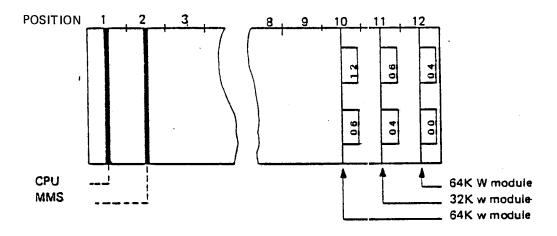

Physically, the bus is organized as a printed backplane containing 12 or 21 "plug in" positions for module connection.

All communication between ND-100 modules except CPU, MMS and CACHE communication, is provided by this bus. That is, the ND-100 bus connects the:

- CPU to the memory system (including MMS and CACHE).

- . CPU to the input/output system.

- DMA controllers to the memory system (DMA = Direct Memory Access). DMA controller is a special device interface module.

A bus control/driver, which is an integrated part of the CPU, controls the activity on the bus. This common bus architecture has several advantages:

- Uniform connection for all modules makes the system flexible and easy to expand.

- No external wiring of busses gives a more reliable system.

- No overhead in connecting several busses between source and destination makes a faster system (one crate system only).

# 1.2.3.2 ND-100 Configuration Examples

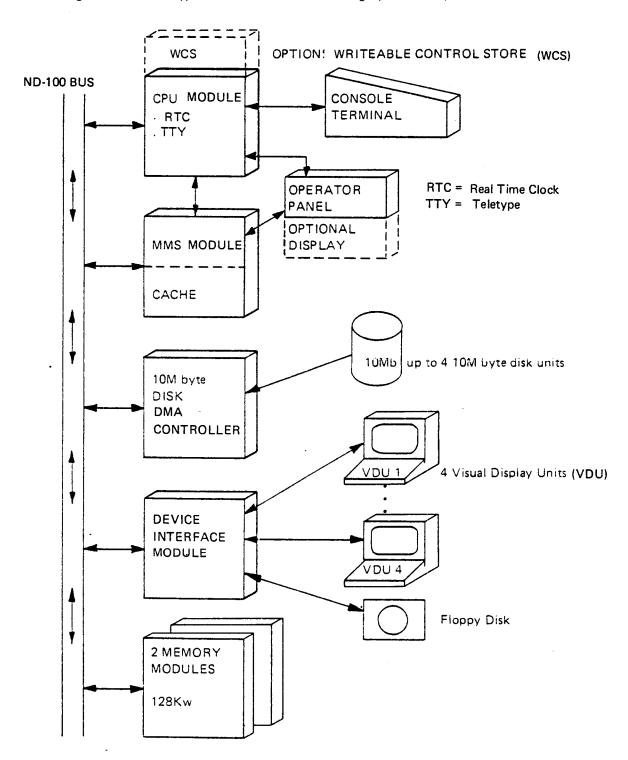

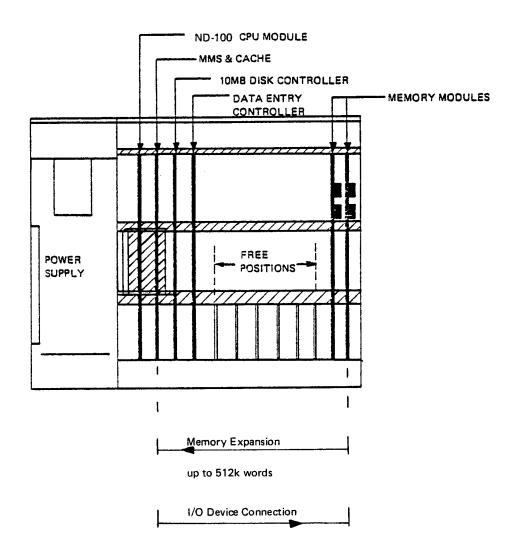

Figure 1.5 shows a typical medium sized ND-100 single processor system.

Figure 1.5: ND-100 Configuration Example

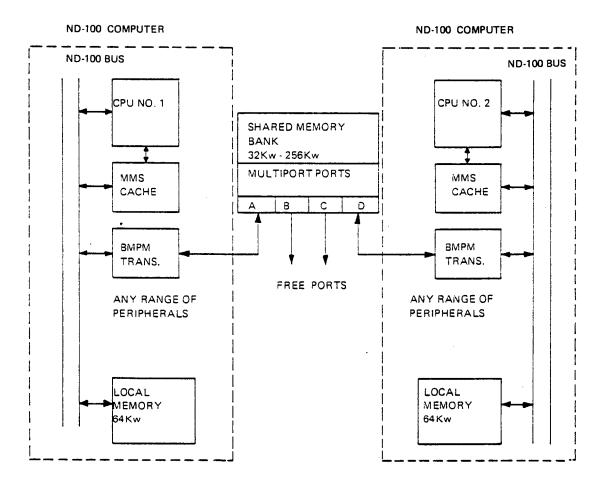

# 1.2.3.3 Multiprocessor Systems

For in-house communication between two ND-100s, between a ND-100 and NORD-10/S, or between a ND-100 and a NORD-50, a shared memory system could be used.

The shared memory system is available through the Big Multiport Memory System (BMPM) which allows up to four sources to access the same physical storage.

#### Example:

Figure 1.6: Communication between two ND-100 Computers using the Multiprocessor System.

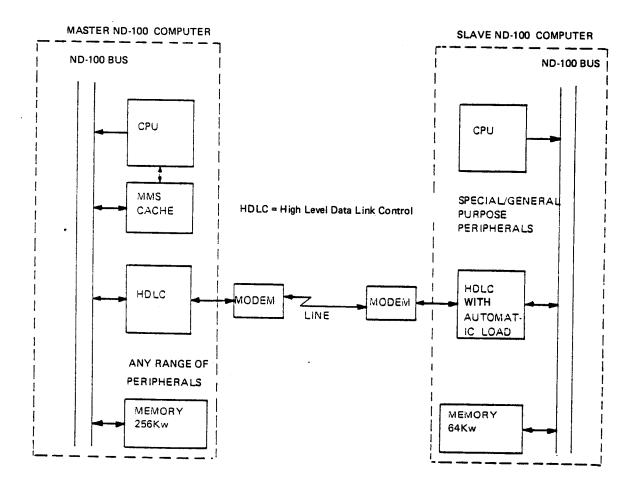

# 1.2.3.4 Remote Operation

Remote operation in this context means one ND-100 being controlled by another ND-100. The two machines may be in the same room or connected via telephone lines using low or high speed modems.

The HDLC module is designed for this kind of operation, including DMA controlled communication. Figure 1.7 shows an example.

Figure 1.7: Connection between two ND-100 computers using a Telephone Line.

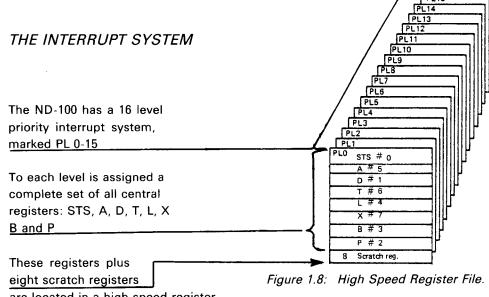

are located in a high speed register

1.3

file close to the the CPU arithmetic both located on the CPU module.

With this architecture, switching between two program levels is reduced to selecting the working set of control registers. The time required for this operation is only  $5~\mu s$ .

All program levels may be activated by software. In addition, each of the levels 10, 11, 12 and 13 may be activated by 512 vectored I/O interrupts. An IDENT instruction is used to identify the interrupting device.

Program level 14 is used by the Internal Interrupt System, which monitors error conditions or traps in the CPU. Program level 15 may only have one I/O interrupt source.

Program level 15 is not used by standard NORD equipment or software, but is available for users who need immediate access to the CPU.

The high speed register file is described in further detail later in this manual.

# 1.4 THE MEMORY MANAGEMENT SYSTEM (MMS)

The hardware memory management module is necessary for running the SINTRAN III/VS (Virtual Storage) operating system. The SINTRAN III/VS operating system includes:

- 64 K words (128 K bytes) virtual address range for each user independent of physical memory capacity.

- Dynamic allocation/relocation of programs in memory.

- Memory protection.

The implementation of the memory management system is based on two major subsystems:

- The Paging System.

- The Memory Protection System.

The paging system maps a 16 bit virtual address (describing a user's 64 K word virtual storage) into a 19 bit physical address, thus extending the physical address space to 512 K words. The paging system also has an extended mode which handles physical memory space up to 16 M words (32 M bytes). This mode gives a 24 bit physical address.

The implementation of paging is based on dividing physical memory into 1 K word pages which, under operating system control, are assigned to active programs.

Four page tables of 64 words each hold the physical page numbers assigned to an active program. These tables are located in high speed registers, reducing paging overhead to practically zero.

The memory protection system may be divided into two subsystems:

- The Page Protect System.

- The Ring Protect System.

The page protect system allows a page to be protected from read, write or instruction fetch accesses or any combination of these.

The *ring protect system* places each page and each user on one of four priority rings.

A page on one specific ring may not be accessed by a program that is assigned a lower priority ring number. This system is used to protect system programs from user programs, the operating system from its subprograms and the system kernel from the rest of the operating system.

# 1.5 THE MEMORY SYSTEM

The memory system has a flexible and hierarchial architecture. The memory system includes:

- 1K words (2K bytes) CACHE memory.

- Up to 16 M words main memory.

- Memory channel to the multiport memory system.

# 1.5.1 Main Memory

Main memory can have any size from:

32K words to 16 M words in steps of 32K words.

Each word in main memory is stored with a 6 bit error correction code which makes it possible to:

- Correct and log single bit errors.

- Detect and report all double errors and most multiple errors.

Seen from the program, memory access time depends on the effect of prefetch.

# 1.5.2 Cache Memory

Cache memory is optional and physically located on the memory management module.

The presence of cache memory will reduce average memory access time significantly. Cache is a high speed bipolar memory.

The purpose of cache memory is to hold the most recent data and instructions to be processed.

# 1.5.3 Multiport Memory

In order for the ND-100 to access the NORD-10/S Big multiport memory, a multiport memory transceiver is available.

# 1.6 THE INPUT/OUTPUT SYSTEM

The ND-100 input/output system is designed to be a flexible system providing communication between slow, character oriented devices as well as high speed, block oriented devices.

Depending on the speed, a device could be connected to ND-100 with:

- CPU controlled, Programmed Input/Output (PIO).

- With Direct Memory Access (DMA).

PIO is used for slow devices and DMA for fast devices.

# 1.6.1 Programmed Input/Output — PIO

Program controlled input/output always operates via the A register, which implies that each word of input/output has to be programmed via this register.

# 1.6.2 Direct Memory Access — DMA

A Direct Memory Access (DMA) channel is used to obtain high transfer rates to and from main memory. CPU activity and DMA transfers may be performed simultaneously, i.e., the DMA transfer is not controlled by the CPU as a PIO transfer is.

More than one DMA device may be active at the same time, sharing the total band width of the DMA channel. Total band width is 1.8 M words per second.

# 1.7 ND-100 PERIPHERAL EQUIPMENT

Most computer peripherals can be connected to ND-100. The range of standard peripherals includes:

#### Sequential Devices

- Terminals.

- Card readers.

- Line printers/plotters.

#### Mass Storage Devices

- Magnetic tapes.

- Disks from 10M bytes to 288M bytes per disk. Up to 4 disks may be connected to each input/output card.

- Floppy disks.

#### Computer networks

- Asynchronous modem controllers.

- Synchronous modem controllers including selectable frame format, HDLC or bisync.

In addition, ND-100 can be equipped with a NORD-10/S bus adapter which gives access to all NORD-10/S peripherals.

# 1.8 ND-100 SOFTWARE

# 1.8.1 The Operating System

The standard operating system for ND-100 computers is SINTRAN III, which may be delivered in two versions:

1. SINTRAN III/VS (Virtual Storage) and VSE (Virtual Storage Extended)

SINTRAN III/VS and VSE are general purpose mass storage based operating systems offering facilities for

- Real-time.

- Timesharing.

- Batch processing.

- 2. SINTRAN III/RT for machines without mass storage devices intended for real-time applications in process control and data communication.

# 1.8.2 Supporting Software

A number of programming languages and software systems complement the capabilities of the ND-100 SINTRAN III/VS and VSE.

- ND standard FORTRAN following the ANSI-77 FORTRAN standards.

- ND COBOL system following the ANSI-74 COBOL standards.

- ND BASIC compiler, an extended version of the program generator for business oriented applications.

- PASCAL

- SIMULA

- PLANC, a high level system programming language.

- MAC assembler with macro expansions.

- PED and QED, interactive text editors.

- The NOTIS office automation system for text and document processing, information retrieval and report generation.

- The SIBAS data base management system, designed in accordance with the Codasyl data base recommendations.

- ND TPS (Transaction Processing System) offering the necessary operational system software for development of transaction processing programs.

- The FOCUS Screen Handling System, an interactive program to create, modify and use screen pictures.

- ND Data Entry System, a set of software modules designed to simplify terminal oriented data entry operations.

Other useful utility programs are ND SORT Package, Scientific Subroutine Library, Commercial Subroutine Library, ND PLOT Package.

For data communication with large scale computers, there are terminal emulator packages for: IBM 360/370, HB-6000, CDC CYBER, UNIVAC and others.

# 1.8.3 Distributed Data Processing

ND NET is a communication system for computer networks, enabling users to communicate with other computers in a network.

# 2 SYSTEM DESCRIPTION

# 2.1 CENTRAL PROCESSOR

# 2.1.1 General

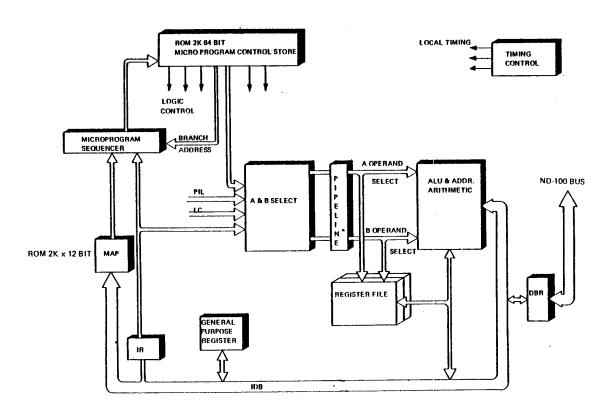

ND-100 is microprogrammed and all instruction execution is in firmware using a 2K x 64 bit, fast Read Only Memory (ROM). To allow dynamic microprogramming, a 256 word by 64 bit writeable control store is optional. This gives the possibility of extending the ND-100 instruction set for special applications. The address arithmetic is also implemented in microprogram. This means that the addressing structure of ND-100 can be changed by rewriting the microprogram.

# 2.1.2 Internal Communication

The internal communication in the CPU is performed over the internal data bus (IDB). A bus is a highway for information, where only one word of information may travel at a time. The microprogram enables the information for the IDB from a certain source, and gives enable signals to the destination parts in the CPU where the information is needed.

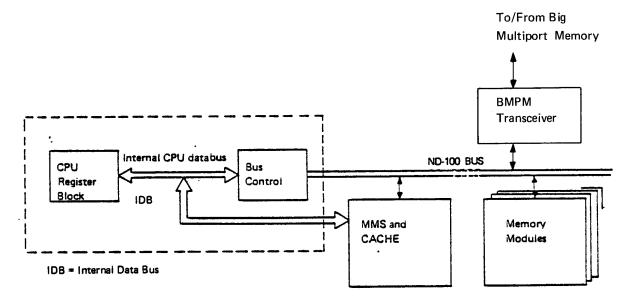

Figure 2.1 shows how the IDB communicates with the central parts in the CPU. The memory management system and cache are connected directly to IDB and ND-100 bus for faster access. The bus control is implemented on the CPU module and controls the activity on the ND-100 bus.

Figure 2.1: ND-100 Bus Structure

## 2.1.3 The Address Arithmetic

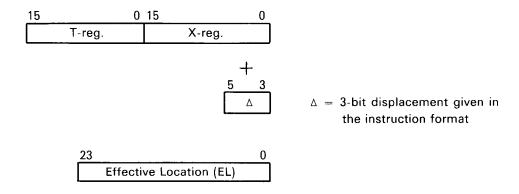

The address arithmetic in the ALU (arithmetic logic unit) forms a 16 bit address. The control of the address arithmetic is implemented in a microprogram. The 16 bit address goes to the memory management system. If the memory management module is not present, the address goes directly to the memory system via the ND-100 bus.

## 2.1.4 Instruction Fetch

The machine instructions to be executed reside in memory. The program counter, PC, is enabled for the ND-100 and a request is sent to memory. The instruction from memory is loaded into the prefetch register.

## 2.1.5 Prefetch

ND-100 uses prefetch. That is, the next instruction is fetched simultaneously with the execution of the current one. Consequently, an instruction fetch consists of copying the prefetch register to the instruction register.

The use of prefetch requires a strictly sequential program. In case of branch instructions or program change (interrupt), the prefetched instruction is skipped and a new instruction found.

Prefetch will not generate page fault if the last instruction before a page limit is a branch instruction.

Prefetch does not give any limitations in programming. For example, STA \* +1 is legal but adds 1  $\mu$  to the execution time compared to STA < disp $\pm$ 1>.

## 2.1.6 Instruction Execution

The instruction to be executed will be loaded into the instruction register (IR) and the instruction map. Refer to Figure 2.2 The lower vector bits of the instruction are taken to IR and the upper operation code bits are taken care of by the map. This is a read only memory (ROM), where each different instruction gives a fixed program address to the microprogram sequencer. Since one machine instruction is executed by a number of instructions residing in microprogram control store, an instruction dependent address should be generated and this is the task of the microprogram sequencer.

This address is sent to the microprogram control store, which gives the logic control bits of the first microinstruction. These signals, together with the timing module, control the operation of the CPU. The operation specified by one microinstruction normally takes 150/190 ns (with cache/without cache). This time is referred to as a micro cycle. When a micro cycle is completed, the next microinstruction has already been read out from the microprogram control store.

## 2.1.7 Main Arithmetic

### Refer also to Figure 2.2

From the A and B selector the arithmetic logic unit (ALU) receives the information about which A and B operand to select in the arithmetic operation. The ALU performs all the arithmetical and logical operations as specified in the instruction set. The bit slice, ALU, is completely controlled from the microprogram.

The ALU with its current registers has a two-way communication over IDB with the register file for loading and storing of the current register set.

Figure 2.2: Instruction Execution

# 2.1.8 The Register File

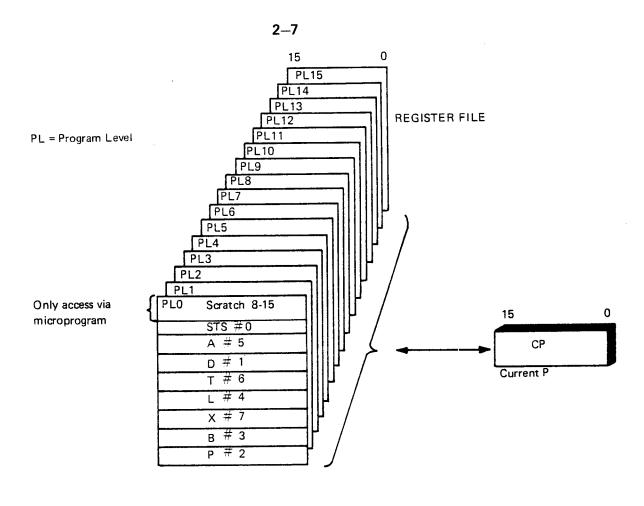

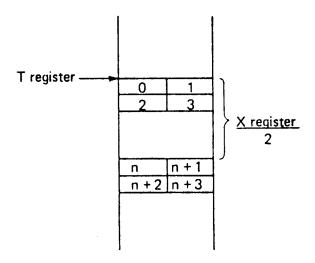

## Refer to Figure 2.3

There are 16 register sets in the ND-100, one for each of the 16 program levels. Each of the register sets consists of 8 general programmable registers and 8 scratch registers for microprogram use only. There is a total of 256 registers; these are referred to as the register file.

## The 8 general registers are:

### Status register (STS)

This register holds the indicators described in the status indicators section.

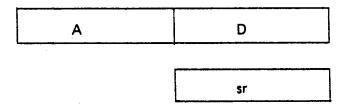

### A register

This is the main register for arithmetic and logical operations directly with operands in memory. This register is also used for input/output communication.

### D register

This register is an extension of the A register in double precision or floating point operations. It may be connected to the A register during double length shifts.

### T register

Temporary register. In floating point instructions it is used to hold the exponent part. It is also used with the IOXT instruction to hold the device address.

### L register

Link register. The return address after a subroutine jump is contained in this register.

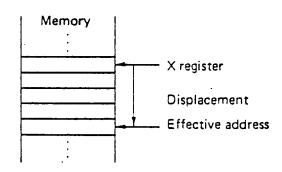

#### X register

Index register. In connection with indirect addressing it causes post indexing.

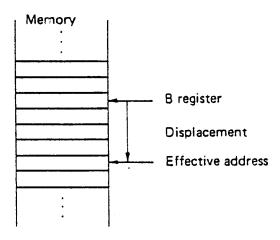

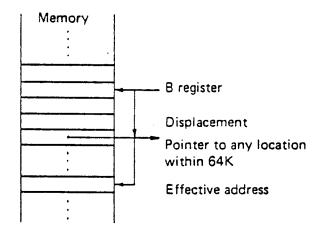

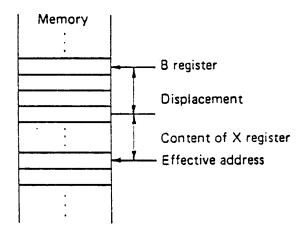

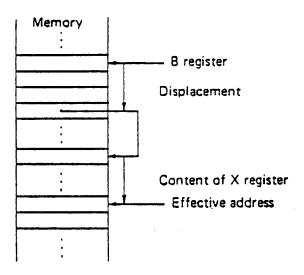

### B register

Base register or second index register. In connection with indirect addressing, it causes preindexing.

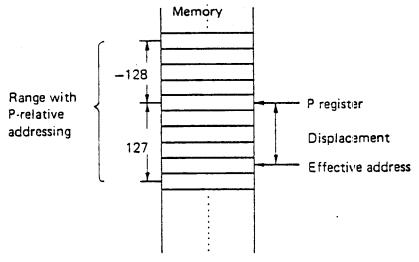

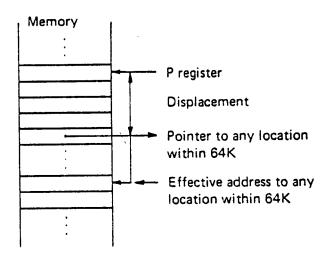

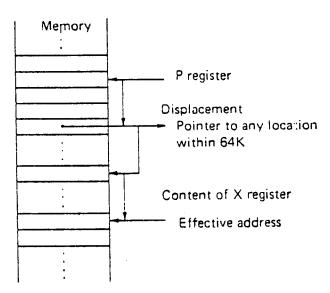

## P register

Program counter, address of current instruction. This register is controlled automatically in the normal sequencing or branching mode. But it is also fully program controlled and its contents may be transferred to or from other registers.

ND-06.014.02

Figure 2.3: Register File

The current register set is held in the ALU and under level change this register set is stored in the register file. The register set for the new level is loaded to the ALU. Any registers or levels can be read or written by specifying register and level information.

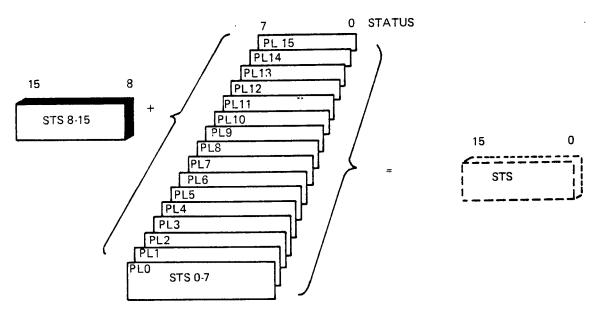

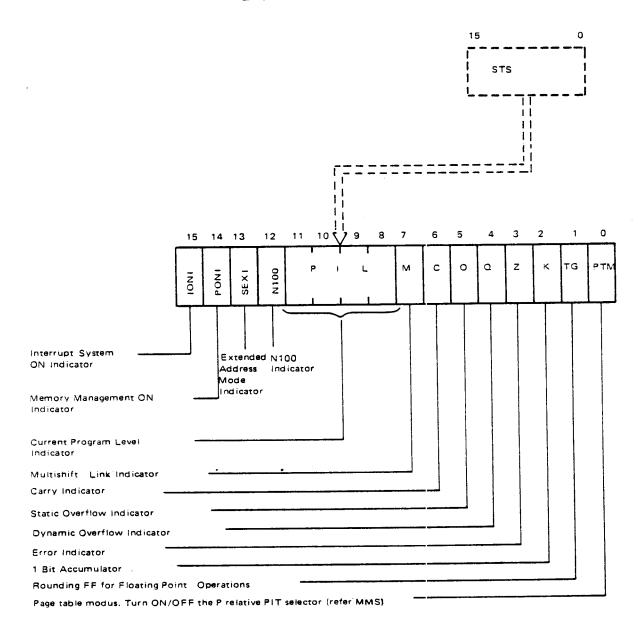

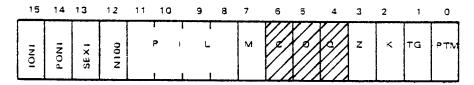

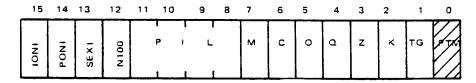

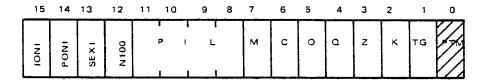

## 2.1.9 Status Indicators

Eight indicators are accessible by programs. These 8 indicators are:

- M Multishift link indicator. This indicator is used as temporary storage for discarded bits in shift instructions in order to ease the shifting of multiple precision words.

- C Carry indicator. The carry indicator is dynamic.

- O Static overflow indicator. This indicator remains set after an overflow condition until it is reset by program.

- Q Dynamic overflow indicator.

- Z Error indicator. This indicator is static and remains set until it is reset by program. The Z indicator may be internally connected to an interrupt level such that an error message routine may be triggered.

- K One bit accumulator. This indicator is used by the BOP (bit operations), instructions operating on one bit data.

- TG Rounding indicator for floating point operations.

- PTM Page table modus. Enables use of the alternate page table.

These 8 indicators are fully program controlled either by means of the BOP instruction or by the TRA or TRR instructions where all indicators may be transferred to and from the A register. Refer to Figure 2.4.

Figure 2.4: Status Register Assignment

The upper part (8 bits) is common for all program levels. This part gives us the following information:

| IONI | Interrupt system ON indicator.                                                                                           |  |  |

|------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| PONI | Memory management ON indicator.                                                                                          |  |  |

| SEXI | Extended indicator to show that MMS is in 24 bits extended addressing mode instead of the usual 19 bits addressing mode. |  |  |

| N100 | N100 indicator to tell the operating system that this is a ND-100 machine.                                               |  |  |

| PIL  | Current program level indicator.                                                                                         |  |  |

## 2.2 THE INTERRUPT SYSTEM

## 2.2.1 General

The ND-100 interrupt system is designed to simplify programming and to allow high efficiency multiprogramming.

This is achieved by use of a complete set of registers and status indicators for each program level.

There are 16 program levels in ND-100 and therefore 16 sets of registers and status indicators. Each set consists of A, D, T, L, X and B registers, program counter and each of the status indicators O, Q, Z, C, M, K, PTM and TG. There are also 9 registers that are only accessible from microprogram.

The context switching from one program level to another is completely automatic and requires only 5.0  $\mu$ s; including the saving and unsaving of all registers and indicators.

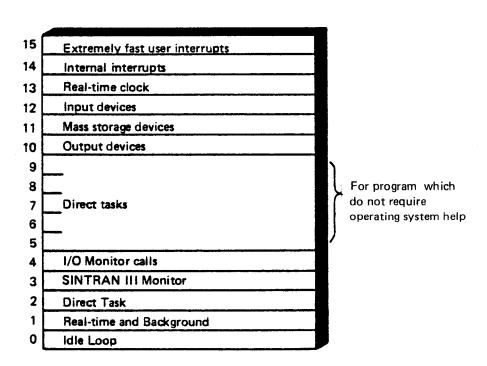

The arrangement of the 16 program levels is as follows.

Figure 2.5: Level Assignments

The priority increases, program level 15 having the highest priority, program level 0, the lowest.

All program levels may be activated by software. In addition, the levels 10, 11, 12 and 13 may be activated by 512 external I/O interrupts. An IDENT instruction is used to identify the interrupting device. Program level 14 is used by the internal interrupt system, which monitors error conditions or traps in the CPU. Program level 15 may only have one I/O interrupt source.

Program level 15 is not used by standard ND equipment or software, but is available for users who need an immediate access to the CPU.

A change from a lower to a higher program level is caused by an interrupt request. A change from a higher program level to a lower takes place when the program on the higher program level gives up its priority.

For both internal hardware status interrupts and external interrupts there is an automatic priority identification mechanism which provides fast interrupt source detection.

# 2.2.2 Functional Description

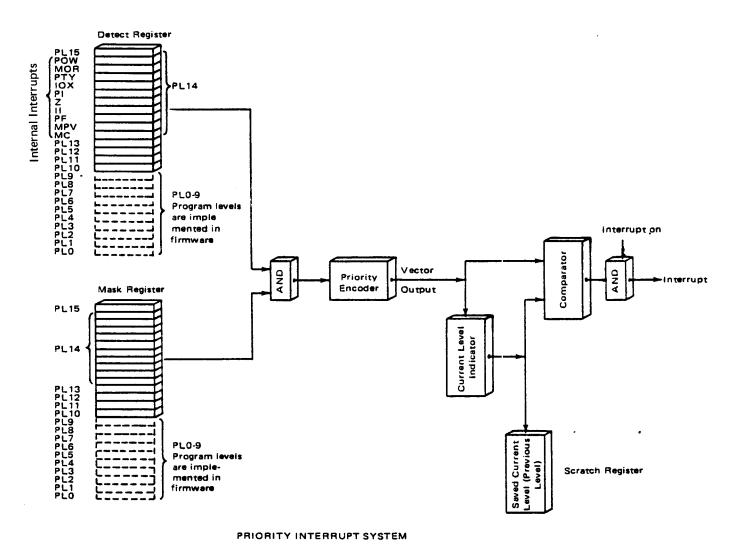

Figure 2.6 shows the functional operation for the complete priority interrupt system.

There is one bit for each level in a detect register with 10 sources to cause a program level 14 interrupt, i.e., an internal interrupt. The detect register for program levels 0-9 are implemented in firmware which means that the microprogram takes care of the detection of interrupts on these levels.

The mask register is used to enable/disable the different program levels and conditions which may cause an internal interrupt. Program levels 0-9 are also taken care of by the microprogram.

When an interrupt comes, these two registers are ANDed together via an AND gate and the priority encoder gives a level value corresponding to the highest bit set in both the detect and mask registers.

This level indicator is compared with the current level to check if the new level is higher than the current one. If this is true, and the interrupt system is on, an interrupt will be generated.

The implementation of the ND-100 interrupt system is based on two registers: the detect register and the mask register. In both the detect and mask registers each interrupt level is assigned a bit position.

Figure 2.6: Priority Interrupt System

# 2.2.3 The External Interrupt System

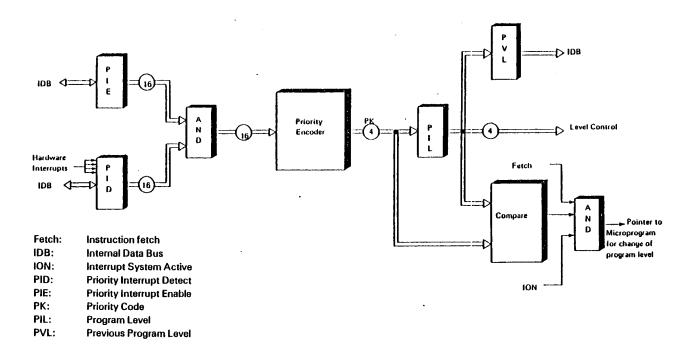

Figure 2.7 gives a block diagram presentation of the external interrupt system.

The program level to run is controlled from the two 16 bit registers:

PIE Priority Interrupt Enable

PID Priority Interrupt Detect

Each bit in the two registers is associated with the corresponding program level. The PIE register is controlled by program only. The PID register is controlled both by program and hardware interrupts. At any time, the highest program level which has its corresponding bits set in both PIE and PID is running.

The actual mechanism for this is as follows.

The current program level is PIL (0 - 15). The 4 bit PIL register controls which register set (context block) to use.

The PIL number is constantly compared to a 4 bit code, PK. PK always contains the number of the highest program level which has its corresponding bits set in both PIE and PID. Whenever PK is unlike PIL, an automatic change of context block will take place through a short microprogram sequence.

The CPU will not ask for the next machine instruction but enter a microprogram that will change the program level to the PK. However, before the level change takes place, the program counter will be saved. The level change can be illustrated as follows:

- 1. The interrupt system is temporarily blocked to prevent false interrupts.

- 2. The program counter (CP) is copied to the saved program counter (P) on the current level.

- 3. The PIL (program level) register is copied into the PVL (previous program level) register.

- 4. The PK (new level priority code) register is copied into the PIL (program level) register. (The CPU has, at this moment, changed level.)

- 5. The P (saved program counter) on the new level is copied to the CP (current program counter).

- 6. A fetch is issued, i.e., the first machine instruction on the new level is asked for.

This complete sequence requires only 5.0  $\mu$ s from the completion of the instruction currently working when the interrupt took place, until the first instruction is started on the new level with its new set of registers and status.

External interrupts may set PID bits 15, 13, 12, 11, 10, and internal hardware status may set PID bit 14, because all internal interrupts are connected to this level.

Figure 2.7: External Interrup System

# 2.2.4 The Internal Interrupt System

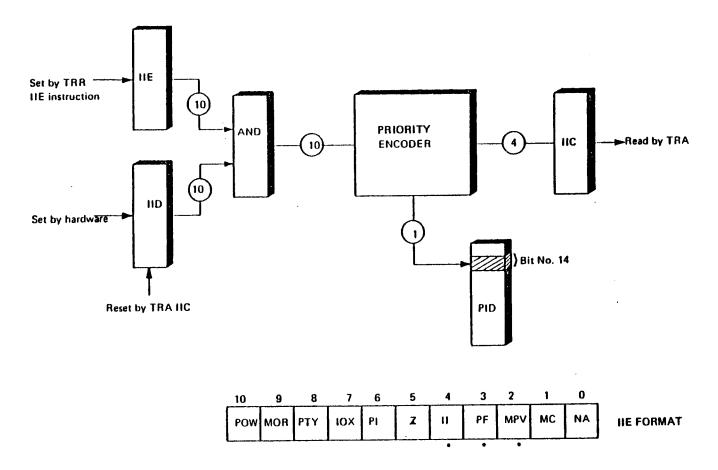

The functional operation of the internal interrupt system is basically the same as the external one. Refer to Figure 2.8.

<sup>\*</sup>Interrupts any micro-instruction.

IIC: Internal Interrupt Code

IID: Internal Interrupt Detect

IIE: Internal Interrupt Enable

TRR HE: Transfers the Content of the A-Register Into the IIE Register TRA IIC: Transfers the Content of the IIC Register into the A-Register.

Figure 2.8: Internal Interrupt System, Block Diagram

# 2.2.4.1 The IIC and IIE Registers

As previously mentioned, the internal interrupt system is connected to level 14. Any internal interrupt condition will force the CPU to level 14. On this level the operating system will read the IIC — Internal Interrupt Code register. This register will hold a code between  $0 - 12_8$  which will identify the internal source for the interrupt.

Internal hardware status interrupts are individually enabled by an 11 bit register called IIE, Internal Interrupt Enable. IIE is set by the TRR IIE instruction. See Figure 2.8.

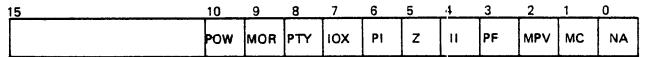

The internal hardware status interrupts are assigned to the IIE register in the following way:

The internal conditions which may cause internal interrupts and their associated vectors, the internal interrupt codes, are listed below:

|     | Bit No.: | IIC Code: | Cause                                                                  |

|-----|----------|-----------|------------------------------------------------------------------------|

| n/a | 0        | 0         | Not assigned                                                           |

| MC  | 1        | 1         | Monitor call                                                           |

| PV  | 2        | 2         | Protect Violation. Page number is found in the Paging Status Register. |

| PF  | 3        | 3         | Page fault.<br>Page not in memory.                                     |

| II  | 4        | 4         | Illegal instruction. Not implemented instruction.                      |

| Z   | 5        | 5         | Error indicator.<br>The Z indicator is set.                            |

| PI  | 6        | 6         | Privileged instruction                                                 |

| IOX | 7        | 7         | IOX error.<br>No answer from external device.                          |

| PTY | 8        | 10        | Memory parity error                                                    |

| MOR | 9        | 11        | Memory out of range Addressing non-existent memory.                    |

| POW | 10       | 12        | Power fail interrupt                                                   |

|     | 11 - 15  |           | Not assigned                                                           |

# 2.2.4.2 Internal Hardware Status Interrupts

### Monitor Call Interrupt

One of the internal interrupt sources is the monitor call instruction named MON. The monitor call instruction differs from the other internal interrupt sources in that the monitor call code or number is found in the T register on level 14.

The MON instruction may have up to 3778 different codes (8 lower bits in the MON instruction) and the T<sub>14</sub> register will be equal to this code with sign extention (bit 7 is sign).

Information to operating systems designers regarding the ND-100 MON-instruction

If a MON-instruction is executed in the last word of a page and the prefetching of the first instruction in the next page gives a page-fault interrupt, then the page-fault interrupt will be reported when a TRA IIC-instruction is executed.

The handling of this page-fault interrupt will clear all traces of the executed MON-instruction. The T-register on level 14 will be loaded with the monitor-call number before the page-fault interrupt occured, but an internal interrupt with IIC-code equal to 1 will never occur.

To avoid this behaviour, make the interrupt handler on level 14 check if a monitor-call number has been written into the T-register on level 14 before level 14 was entered. If the T-register has been changed in this way, the monitor-call handler should be entered regardless of the contents of the IIC. The page fault will occur later, when execution of the instruction after the MON is attempted.

#### Programming example:

% Last part of a level 14 handler

LDA (1000

% Any number not possible

**COPY SA DT**

% as monitor-call number

WAIT

% Give up priority

% Reactivated by internal interrupt

SKP IF DA EQL ST

JMP MONCT

% T is changed

TRA IIC

% Check other internal interrupts

MONCT, TRA IIC

% Necessary to unlock IIC

TRA PGS

% Necessary to unlock PGS

% Ordinary monitor-call handler

### Protect Violation Interrupt

A protect violation has occurred. Two types of violations are possible:

Memory protect violation.

This means that an illegal reference (read, write, fetch or indirect) has been attempted.

Ring violation.

This means that a program attempted to access an area with higher ring status.

Details regarding this interrupt are found in the paging status register.

#### Page Fault Interrupt

The program attempted to reference a page that is presently not in memory. Information regarding page number, etc. is found in the Paging Status register.

### Illegal Instruction Interrupt

Attempted execution of an instruction that is not implemented causes this interrupt.

#### Error Indicator Interrupt

The Z indicator in the STS register has been set. This may be caused by several instructions:

- FDV with 0.0 (FDV = divide floating accumulator).

- EXR of an EXR instruction (EXR = execute register).

- DNZ overflow (DNZ = denormalize).

- RDIV overflow (RDIV = integer inter register divide).

- Programmed setting of Z (BSET = bit set, MST = masked set or TRR = transfer to register).

The instructions are described in further detail in Section 3.

Note: Level 14 must always reset the Z indicator on the offending level, otherwise, a new interrupt will occur when the level is reentered.

### Privileged Instruction Interrupt

Attempted execution of a privileged instruction causes this interrupt. The privileged instructions are listed below.

ION, IOF, PON, POF, PION, PIOF, WAIT, IOX, IOXT, IDENT, TRA, TRR, MCL, MST, LRB, SRB, IRR, IRW, SEX, REX, DEPO, EXAM, LWCS, OPCOM.

These instructions are described in further detail in Section 3.3.

### IOX Error Interrupt

The addressed input/output device does not return a BDRY (Bus Data Ready) signal. This may be due to a malfunctioning or missing device or no device answering to an IDENT instruction.

#### Memory Parity Error Interrupt

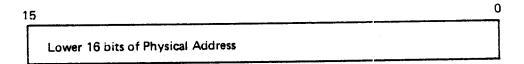

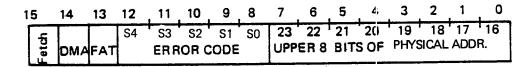

A memory parity error has occurred. The least significant 16 bits of the failing address can be read from the PEA register using the TRA PEA instruction. PEA = Parity Error Address.

Further information may be read from the PES register (Parity Error Status).

### Memory Out of Range Interrupt

This interrupt occurs when the program addresses nonexisting memory. The least significant 16 bits of the referenced address can be read from the PEA register.

Further information may be read from the PES register.

#### Power Fail Interrupt

This interrupt is triggered by the power sense unit. It is possible for this interrupt to occur simultaneously with some other internal interrupt. In this case, the power fail interrupt has priority.

# 2.2.4.3 Reset of the IIC Register

In order to optimize the processing of internal hardware status interrupts, the instruction TRA IIC will return the contents of IIC to the A register, bits 0-3, with bits 4 - 15 zero.

The instruction TRA IIC will automatically reset IIC.

Note that if the interrupt is caused by the error indicator Z, the Z indicator on that program level must be cleared by program control from program level 14. (Otherwise, another interrupt will occur.)

# 2.2.5 Programming Control of the Interrupt System

# 2.2.5.1 Programming the PID and PIE Registers

PID = Priority Interrupt Detect.

PIE = Priority Interrupt Enable.

The programming control of the interrupt system is as follows:

PID and PIE may be read to the A register with the instructions

TRA PID and TRA PIE.

Three instructions are available for the setting of these registers.

#### 1. TRR PID and TRR PIE

The TRR instruction will copy the A register into the specified register.

#### 2. MST PID and MST PIE

The MST, masked set, instruction will set the bits in the specified register to one where the corresponding bits in the A register are ones. (The A register is used as a mask for selection of which bit to set.)

#### 3. MCL PID and MCL PIE

The MCL, masked clear, instruction will reset to zero the bits in the specified register where the corresponding bits in the A register are ones.

All program levels may be activated by program, by setting the appropriate bits in PIE and PID.

In addition to TRA, TRR, MCL and MST, the PID register is also controlled in the following ways:

## 2.2.5.2 The WAIT, ION and IOF Instruction

The resetting of PID bits is also controlled by the WAIT instruction, which will reset PID on the current program level. (The WAIT instruction is also called "Give up Priority".)

For example, a program on program level 14, which issues a WAIT instruction, will cause PID bit 14 to be zeroed. This will cause a new program level to be entered and PK becomes different from PIL (PIL = 14, PK < 14).

The interrupt system is also controlled by the two instructions:

ION — Turn on interrupt system

IOF - Turn off interrupt system

When power is turned on, the power up sequence will reset IIE, PIE and PIL, and the register set on program level zero will be used.

The ION instruction will continue operation at the highest program level at the time ION is executed. If a condition for change of program levels exists, the ION instruction will be the last instruction executed at the old program level and the P register on the old program level will point to the instruction after ION.

The IOF instruction will turn off the mechanisms for changing of program level, and PIL will remain unchanged.

IOF and ION may also be used to disable the interrupt system for short periods, for example, in order to prevent software timing problems.

# 2.2.5.3 The Previous Level Register, PVL

In some cases after being forced to level  $14_{10}$  it may be useful to know which level was the last one.

This might be the case when a MPV (Memory Protect Violation) has occurred. In this case one wishes to find the value of the SP (Saved Program) counter on the offending level and/or the offending instruction.

The PVL register holds the previous level information, and this could be read by the TRA PVL instruction.

# 2.2.5.4 Vectored Interrupts and the IDENT Instructions

In ND-100 there may be up to 2048 vectored interrupts. Usually, each physical input/output unit will have its own unique interrupt response code and priority.

These vectored interrupts must be connected to the four program levels 13, 12, 11 and 10.

The standard way of using these levels is as follows:

Level 13: Real-time clock Level 12: Input devices

Level 11: Mass storage devices

Level 10: Output devices

The vectored interrupts are connected to the corresponding bits in the PID register.

When a vectored interrupt occurs, an IDENT instruction is used to identify the interrupt, since several devices may have interrupts on the same level. The instruction has the following format:

### IDENT cprogram level>

When an IDENT instruction is executed, a hardware search on the indicated level is performed. The first interrupting device found will respond with its identification code and reset its interrupt condition.

The CPU will use the identification code (vector) as a branch address to the driver for the interrupting device.

If more than one device on the same level generates interrupts, the device interface located closest to the CPU has highest priority. If there is more than one device connected to the module, an internal priority on the module will determine which is to be treated first.

## Programming Example:

| LEV13, | WAIT  |       | % | Give up priority             |

|--------|-------|-------|---|------------------------------|

|        | SAA   | 0     | % | Set content of A-reg. to $0$ |

|        | IDENT | PL13  | % | Identify device on level 13  |

|        | RADD  | SA DP | % | Computed GO TO               |

|        | JMP   | ERR13 | % | Code 0, error                |

|        | JMP   | DRIV1 | % | Code 1                       |

|        | JMP   | DRIV2 | % | Code 2                       |

|        | _     |       |   |                              |

|        | _     |       |   |                              |

|        | JMP   | DRIVN | % | Code N                       |

|        |       |       |   |                              |

# 2.2.6 Initializing of the interrupt System

Before use of the interrupt system it must be initialized. After switching power on, IIE, PIE and PIL will be zero. The registers on level zero will be in use. The interrupt initialization must include the following:

- 1. Enabling of the desired program levels by proper mask setting in PIE (Priority Interrupt Enable).

- Enabling of the desired internal interrupt sources by proper mask setting in IIE — Internal Interrupt Enable register.

- 3. The P, saved program counters, on the levels to be used must be initialized, i.e., they must all point to the program to be executed on the different levels.

- 4. If the Z (error) indicator is enabled for interrupt (IIE bit number 5), care should be taken that this indicator is cleared in the status register (bit number 3) for all levels being initialized.

- 5. The IIC (Internal Interrupt Code) register, the PES (Parity Error Status) register and the PEA (Parity Error Address) register might be blocked after power up.

By performing a TRA instruction for IIC and PES, all three registers will be unblocked and ready for use.

6. The interrupt system is turned ON.

#### Example:

| LDA             | (76032 | % Enable for interrupts on level               |

|-----------------|--------|------------------------------------------------|

| TRR             | PIE    | % 1, 3, 4, 10, 11, 12, 13, and 14              |

| LDA             | (3736  | % Enable for all internal                      |

| TRR             | IIE    | % Interrupt sources except for the Z indicator |

| LDA             | (P1    | % The saved program counters                   |

| IRW             | 10 DP  | % on the enabled levels                        |

| LDA             | (P3    | % start value                                  |

| IRW             | 30 DP  | %                                              |

| etc. for each P |        |                                                |

| in use          |        |                                                |

| TRA             | IIC    | % Unlock IIC                                   |

| TRA             | PEA    | % Unlock PEA and PES                           |

| ION             |        | % Turn on interrupt system                     |

| JMP             | START  | % Go to main program                           |

### 2.3 THE MEMORY MANAGEMENT SYSTEM

## 2.3.1 General

The Memory Management System is designed to extend the ND-100 physical address space, and to provide a sophisticated memory and privileged instruction protection system. This system may be used for several purposes, such as:

- Dynamic memory allocation (paging).

- Program relocation.

- Expanding the maximum physical address space size to 16 M words.

- Memory protection of each individual page.

- Privileged instructions and ring structured program protection.

The Memory Management System includes two major subsystems:

- The paging system.

- The memory protection system.

The Paging System can work in two modes:

- Normal mode. A 16 bit virtual address is mapped into a 19 bit physical address. This extends the physical address space from 64 K to 512 K words. Four page tables of 64 entries each are used. This mode is compatible with the NORD-10/S.

- Extended mode. A 16 bit virtual address is mapped into a 24 bit physical address. This extends the physical address space from 64 K to 16 M words.

Four page tables of 64 entries each are used.

For each mode the four page tables are located in high speed registers, directly connected to the internal data bus (IDB). This reduces paging overhead to practically zero. The page size is 1024 words.

The Memory Protection System may be divided into two subsystems:

- The page protection system.

- The ring protection system.

The page protection system protects each page from read, write or instruction fetch accesses or any combination of these.

The ring protection system places each page on one of four priority rings. A page of memory that is placed on one specific ring may not be accessed by a program that resides in a page on a ring of lower priority. This system is used to protect system programs from user programs, the operating system from its subsystems, and the system kernel from the operating system.

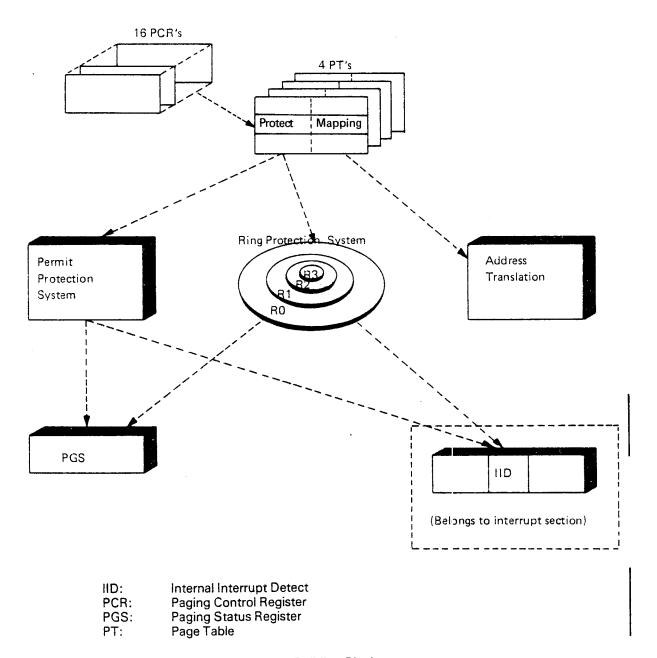

# 2.3.2 Memory Management Architecture

Memory Management consists of:

- 4 page tables.

- 16 paging control registers.

- A paging status register.

- A permit protection system.

- A ring protection system.

The page size is fixed to 1K words, thus each page table will map the full 64K virtual address space of the ND-100.

Figure 2.9: Memory Mangement Building Blocks

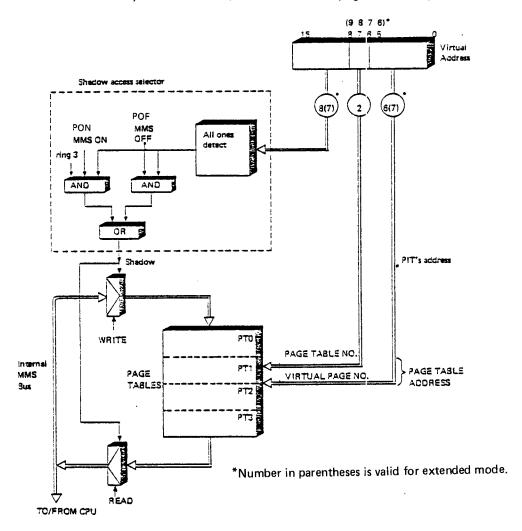

# 2.3.3 The Paging System

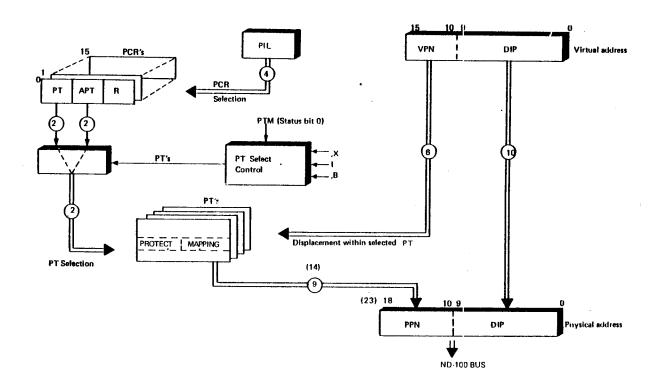

Number in parenthesis is valid for extended mode.

The Paging System is an automatic address interpretation system which maps a 16 bit virtual address, as seen from the program, into a 19 (24) bit physical address. This implies that the maximum memory size may be extended from 64K words to 512K (16 M) words. The system also allows programs to be written for 64K virtual memory with only parts of the program residing in physical memory at a given time, the rest being kept on mass storage.

The Paging System divides the memory into memory blocks or pages of 1024 words or 1K words. The pointers to these pages are found in the page tables. In ND-100, there are four page tables, each consisting of 64 entries, and each covering a full 64K address space. The tables are kept in high speed registers with a 32 bit word length.

ND-100 uses 1K words per page. This implies that in order to map 64K words of virtual address space, 64 Page Table (PT) entries are required.

To address any location within a 1K address space, 10 address bits are required. These bits are the displacement within a page (DIP), and are transferred directly to the ND-100 bus. The most significant part of the virtual address (bits 10 - 15) are used as an address selecting one of 64 entries in PT. This address is referred to as Virtual Page Number (VPN).

The program level (PL) determines which paging control register (PCR) to use. The selected PCR determines which page index table to select, and VPN addresses an entry in the selected PT.

When a memory request is performed, the content of the 32 bits PT is looked up. 7 bits are used for protection, and are discussed later. 9 (14) bits are called Physical Page Number (PPN), and are transferred to the ND-100 bus. PPN can have values from 0 - 512 (16384). This makes it possible to access 512 (16384) pages. Since one page = 1024 words, it is possible to access 512 (16 384) x 1024 512 K (16 M) words.

Prior to program start, the operating system will set the PPN to the proper value in the PT. The address translation is therefore under control of the operating system.

Figure 2.10: Virtual to Physical Address Mapping

Addressing mode bits from the Memory Reference Instruction

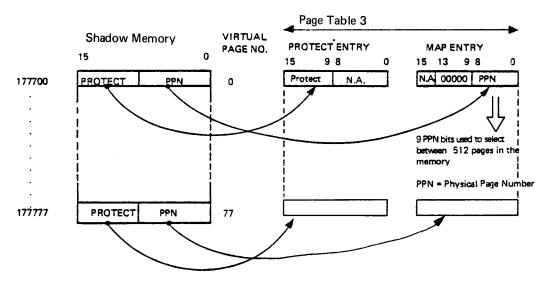

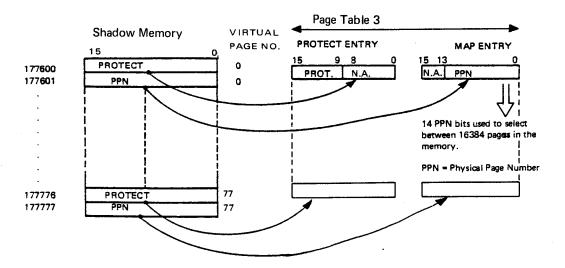

# 2.3.4 The Shadow Memory

The shadow memory is a number of reserved memory addresses. These memory addresses are used to access the page tables in the same way as the rest of the memory.

These reserved addresses are called shadow memory because it lies in the shadow of the main memory and is inaccessible for users on rings 0, 1 and 2. For ring 3 users or when paging is off however, main memory lies in the shadow and is inaccessible. Figure 2.11 shows the shadow memory layout.

The topmost locations in the 64 K virtual address space are reserved for page table access. In normal mode 1 x 64 x 4 = 256 locations are needed and in extended mode 2 x 64 x 4 = 512 locations are needed. The following octal addresses are hence reserved:

Figure 2.11: Shadow Memory Layout.

In normal mode only 16 of each page table entry's 32 bits are used. Therefore only one shadow memory word is read/written to fill one page table entry.

In extended mode 21 of the 32 page table entry's bits are used. This means that two shadow memory words are read/written to fill one page table entry.

Figure 2.12: Shadow Memory Addressing.

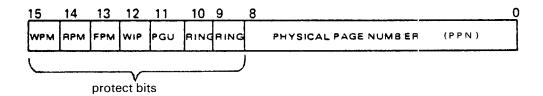

# 2.3.5 The Page Tables

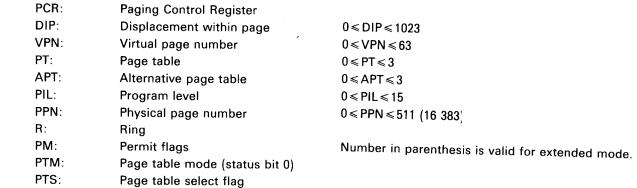

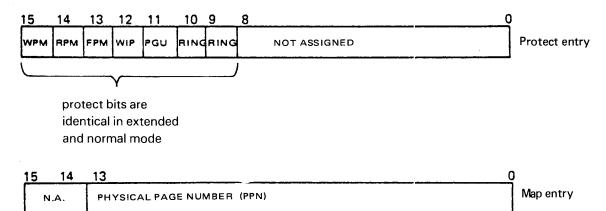

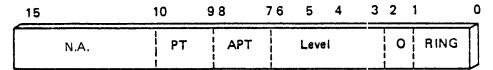

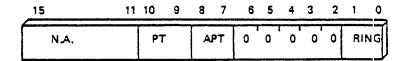

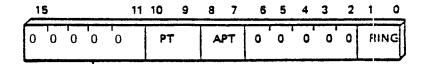

In normal mode the map part requires 9 bits and the protect part requires 7 bits. Together the map and protect parts require 16 bits, which is the PT's 16 bit word length. The 9 PPN bits (Physical Page Number) in the map entry shown in figure 2.13 are used to select one of 512 pages in the memory.

Figure 2.13: Reading Page Table 3 Entries as seen from Program in Extended

Mode

In extended mode the map part requires 14 bits and the protect part requires 7 bits. Together the map and protect parts make 21 bits, which extend the PT's word length. Therefore we have to use two shadow memory locations for housing the map and protect parts. The 14 PPN bits in the map entry shown in figure 2.14 are used to select one of 16 384 pages in the memory.

Figure 2.14: Reading Page Table 3 Entries as seen from Program in Extended Mode

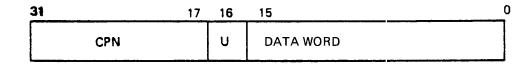

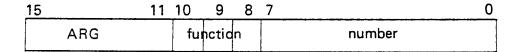

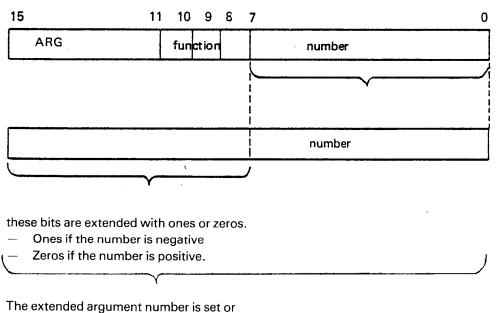

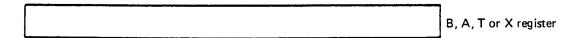

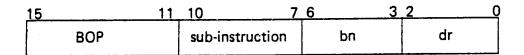

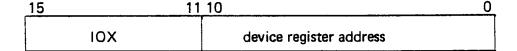

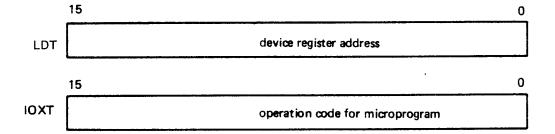

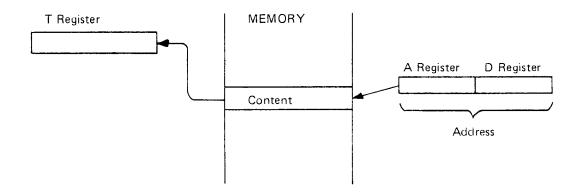

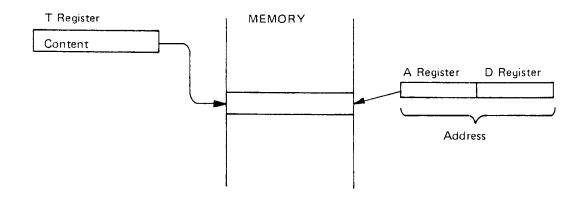

The page table format: