**DIGITAL ELECTRONICS**

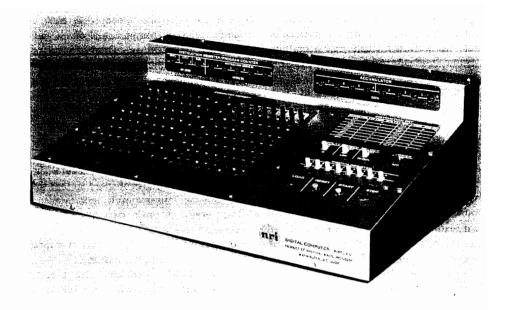

THE MODEL 832 DIGITAL COMPUTER

REFERENCE MANUAL

10KX

Na 139-OM-701(501)

# THE MODEL 832 DIGITAL COMPUTER

REFERENCE MANUAL 10KX

## INDEX OF SECTIONS

| 1. Introduction                           | Pages 1 - 3   |

|-------------------------------------------|---------------|

| 2. Computer Operation                     | Pages 4 - 10  |

| 3. Word Formats                           | Pages 11 - 12 |

| 4. The Instruction Set                    | Pages 13 - 17 |

| 5. Displays and Controls                  | Pages 18 - 22 |

| 6. Programming and Operating the Computer | Pages 23 - 28 |

| 7. Logic Circuitry Analysis               | Pages 29 - 44 |

| 8. Appendix                               | Pages 45 - 57 |

The Model 832 is a small digital computer designed for training purposes. It fills the gap between those training devices designated as logic trainers for teaching digital logic and computer circuitry and the more complex and harder to program minicomputers. It was designed to minimize circuitry and simplify operation but at the same time maintain all of the major features of a real digital computer. Those using it in a training program can quickly and easily learn the fundamentals of digital computers including organization, operation and programming. Let's look at the major features of the Model 832.

The Model 832 was designed especially for training. The architecture, logic, and instruction set of the Model 832 were designed to optimize the computer's use as a training device. Its physical arrangement also serves this purpose. The large front panel contains two easy to read register displays as well as the memory

switches that permit rapid access to onehalf of the computer's memory so that programs and data can be quickly changed without the need for costly input/output devices. A minimum of controls are carefully placed to permit ease of operation.

The Model 832 uses modern SSI and MSI TTL integrated circuits. The use of 7400 TTL integrated circuits makes the Model 832 a reliable, low-cost digital computer with a minimum amount of hardware. The student works with the latest and most popular integrated circuits in use in digital equipment today.

The Model 832 allows the student to study detailed circuit operation of the digital computer at the gate level. The student can demonstrate all of the basic logical concepts and most widely used digital circuitry. At the same time the computer design permits the student to work at a higher level; he learns to write programs to implement popular

NATIONAL RADIO INSTITUTE, WASHINGTON, D.C. 20016

1979 EDITION

algorithms for solving typical problems. The student can easily program the computer to perform virtually any operation. Many advanced programming concepts can be demonstrated.

The Model 832 was designed to teach digital computer fundamentals. The best way to learn computer organization and operation is to study a particular digital computer thoroughly in order to learn its operation and to become intimately familiar with its instruction set so that useful programs can be written. The Model 832 is small enough that anyone can readily learn its operation and master its instruction set to demonstrate all of the most important programming fundamentals. Regardless of which type of computer you eventually work with, you will demonstrate all of the important digital computer concepts with the Model 832.

#### GENERAL SPECIFICATIONS

Memory. Maximum memory size 32 8-bit binary words. Sixteen 8-bit words of memory are available in the programmable read-only switch/diode matrix memory. Another sixteen 8-bit words of memory are available in the form of a bipolar semiconductor read/write random access memory. The first sixteen 8-bit words of memory are represented by front panel switches so that program and data changes can be quickly and easily made without the need for costly input/ output devices. This one feature alone makes the Model 832 computer one of the most valuable computer training devices ever built.

Control. Stored program, fully synchronous operation. There are two basic computer modes, instruction fetch and instruction execute.

Addressing. The Model 832 uses a single address format and direct addressing of memory. Other forms of addressing, such as indirect, indexed, and relative, can be demonstrated through programming.

Clock. Both low and high speed clock pulses are available. The high speed clock runs at approximately 250 kHz. The slow clock runs at approximately 2 Hz. The slow speed clock operation executes the program at a low rate of speed so that the student can observe each operation and logic event. A single step mode is also available so that the student operator can step the program a clock pulse at a time with a front panel push button.

Instructions. There are fifteen basic instructions, seven memory reference instructions, and eight generic or literal instructions. These include load/store, arithmetic/logic, jump/skip, shifts, and register transfers.

Input/Output. The input is via front panel binary switches; the output is by two 8-bit binary light displays.

**Programming.** Programming is strictly by machine language using hexadecimal notation.

Circuitry. Seventy-four type 7400 TTL integrated circuits, both the SSI and MSI type, are used to implement the Model 832. All integrated circuits are installed in sockets. This makes the IC's easy to replace should one ever become defective and permits demonstrations of trouble-shooting. All sockets and circuitry are mounted on highly reliable, double-sided G-10 printed circuit boards.

Basic Word Size, 8 bits.

Arithmetic. Binary representation of numbers with 2's complement representation of negative numbers. All processing is done serially. However, there are numerous internal parallel data transfers.

Size. The Model 832 is 22 inches wide, 7 inches high, and 14 inches deep.

Color. Blue cabinet, front panel of brushed aluminum with red trim and white lettering.

Cabinet. Made from heavy sturdy steel with an aluminum front panel.

Total Weight. 16 pounds.

Power Source. 95 - 125 VAC, 50/60 Hz. 25 watts.

2

# **Computer Operation**

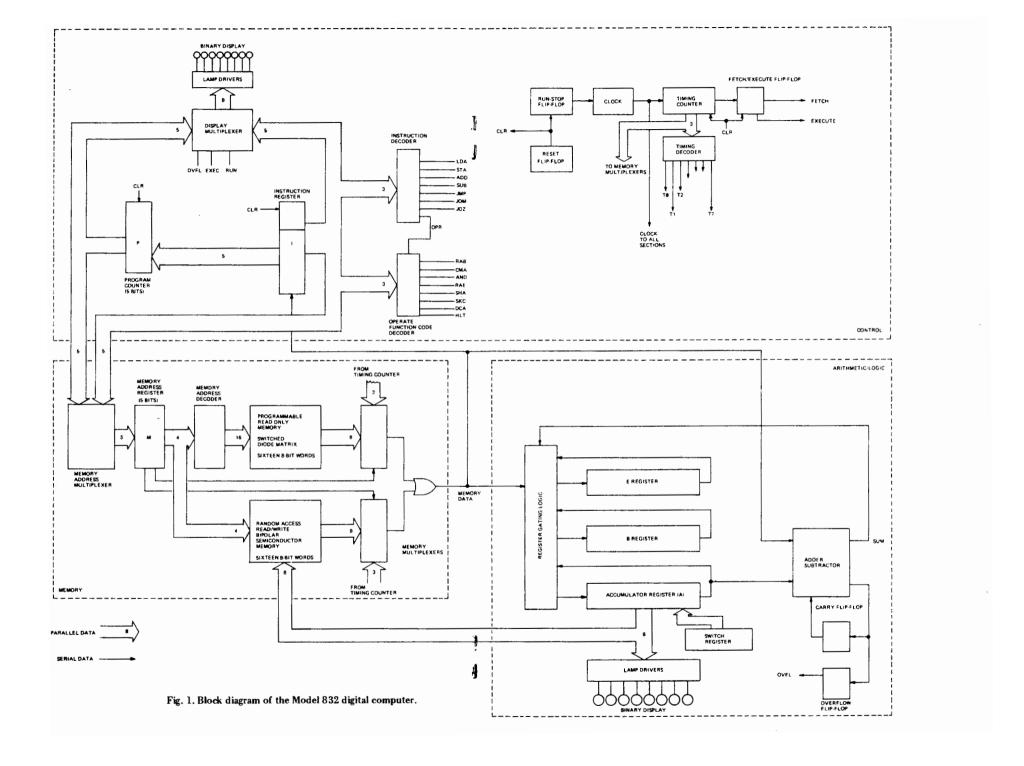

Fig. 1 (center fold) shows a complete block diagram of the Model 832. In this section we will analyze the basic operation of the computer using this diagram. You will also study the basic overall operating concepts of the machine.

The Model 832, like any digital computer, operates on a stored program concept. A series of instructions forming a program to produce some useful calculation or operation is stored in the computer's memory. The computer sequentially fetches these instructions from memory one at a time, analyzes them, and then carries out the operations specified by the instructions. The step-by-step sequence of instructions causes the desired operations and calculations specified by the program to take place.

#### REGISTERS

The various registers used in carrying out the operations specified by the instructions form the very heart of any digital computer. The Model 832 contains six operating registers. Let's define them before we continue with a detailed block diagram analysis.

A Register. The A register is the accumulator or main operating register in the computer. All of the instructions in the computer refer to operations that take place on data stored in the accumulator. The accumulator is the basic arithmetic logic register in the machine. It is eight bits in length. Its content is displayed continuously on the eight right-hand display lamps.

B Register. The B register is an auxiliary 8-bit register used to store intermediate results of program calculations. It is generally used to exchange data with the accumulator. A rotate A and B instruction causes the data in the accumulator to be transferred to the B register and the data in the B register to be transferred to the accumulator. In performing the logical AND instruction, the contents of the A and B registers are ANDed together with the result appearing in the accumulator.

E Register. This is another 8-bit auxiliary register which is used to store intermediate results in calculations. The contents of the accumulator can be shifted into the E register while the contents of the E register are shifted into the accumulator. This is done with a rotate A and E instruction.

In some versions of the Model 832 digital computer, the bipolar semi-conductor read/write memory is an option. When this memory is not contained within the computer, the E register is wired as a read/write portion of the memory and simulates one memory location.

I Register. This 8-bit register is the instruction register. It holds the instruction word during the execution of that instruction. The I register is loaded serially from the memory. Its contents are then decoded to determine the operation to be performed. The I register contents can be displayed by the eight left-hand display lamps via a display multiplexer. During jump instructions (conditional or unconditional branches in the program) the five address bits of the

instruction register are transferred to the program counter to tell the computer where to fetch the next instruction.

M Register. The M register is the memory address register. It is five bits in length and holds the address of the word to be fetched from memory. The word, of course, may be either an instruction word or a data word. The memory address register is loaded from the program counter during instruction fetch operations. Its contents are decoded and the desired instruction is loaded serially into the I register. During the execute phase of the operation, the M register is loaded from the 5-bit address portion of the instruction register.

P Register. The P register is the program counter. This 5-bit counter contains the address of the next instruction in sequence to be executed. It is normally incremented once for each fetch/execute phase. Its content is fed to the memory address register during fetch operations to determine the location of the instruction to be fetched and executed. The program counter is loaded from the instruction register during conditional or unconditional jump instructions to alter the sequence of the program. The output of the program counter is fed to a display multiplexer where its contents may be observed on the left-hand binary lamp display.

#### **BLOCK DIAGRAM ANALYSIS**

As shown in Fig. 1, the Model 832 digital computer is divided into three basic sections, the memory, the control section, and the arithmetic/logic section. The memory stores the program and the data. The control section sequentially examines the instructions of the program stored in memory and generates the

control signals that carry out the specified operations. The arithmetic/logic unit manipulates the data according to the control signals generated by the control section to carry out the functions specified.

Memory. The memory in the Model 832 digital computer consists of a maximum of 32 8-bit memory locations where data and instruction words can be stored. The first half of the memory is the programmable read-only memory that is a switched diode matrix making up a total of sixteen 8-bit words. For each bit position there is a switch and a diode in the matrix. The 128 switches are on the left side of the front panel of the computer grouped as sixteen 8-bit words. The memory is programmed by setting the switches. Either data or instructions may be stored this way.

Data can be read out of the memory only. Data cannot be written into the memory under the control of the computer with a store instruction. However, the memory is fully programmable by setting the front panel switches.

The switched diode matrix programmable read-only memory is used in the Model 832 because of its convenience in programming the computer, particularly for training purposes. To keep the cost of the computer low, no input/output devices are used. Therefore, to get data into the memory quickly and conveniently without an input device, the memory was designed to provide rapid data entry and changes.

In addition, the contents of the memory can be readily observed by visually noting the positions of the switches. Because this portion of the memory is so easy and quick to change, many different programs can be entered and run in a short time.

Another advantage of the switched diode matrix programmable read-only memory is its nonvolatile characteristic. Since all the data is stored as mechanical switch settings, turning off the power does not destroy the contents of the memory.

Despite the small size of the programmable read-only memory, an amazing number of programming and computer fundamentals can be demonstrated with just sixteen words. There are very few basic computer concepts that cannot be demonstrated.

The more sophisticated programming experiments require additional memory space, however. For this purpose, sixteen additional 8-bit words of memory are used in the Model 832. This portion of memory is made up of a random access, read/write bipolar semiconductor memory. It consists of a total of 128 TTL flip-flops, one for storing each of the bits in the sixteen 8-bit words. These flip-flops are grouped by words and are addressable. Data can be read from the memory and easily written into the memory under program control with a store instruction.

The bipolar semiconductor memory is volatile, so whenever computer power is removed, all of the flip-flops storing the data will be disabled. When power is reapplied, the states of the flip-flops will come up in some random manner, thereby destroying any program previously stored there. For that reason, care should be taken not to remove power if you wish to retain the contents of the semiconductor memory.

Now refer to the memory section in Fig. 1. The programmable read-only memory is shown as a block, as is the bipolar semiconductor memory. The circuitry used to address a single word in

either portion of the memory consists of a memory address multiplexer, the memory address register, and a memory address decoder. The memory address multiplexer accepts two parallel 5-bit words, one from the program counter and the other from the address section of the instruction register. The multiplexer causes either of these two 5-bit words to be stored in the memory address register.

During the fetch phase, when an instruction is to be taken from memory and analyzed the memory address multiplexer causes the output of the 5-bit program counter to be transferred to the memory address register. At this time the five input lines from the instruction register are inhibited. During the execute phase of the computer operation, when the instruction is carried out, the memory address multiplexer inhibits the program counter inputs and causes the five address bits from the instruction register to be stored in the memory address register. This is true for all memory reference instructions where an instruction specifies an operation on some data word stored in memory. The five bits from the address section of the instruction register designate the location of that operand.

The 5-bit address word stored in the memory address register specifies one of the 32 total memory words. These five bits from the memory address register are applied to a memory address decoder and directly to the bipolar semiconductor memory. The memory address decoder looks at the four least significant bits of the memory address register and selects one of sixteen words in the programmable read-only memory. These four bits from the M register are also applied to the bipolar semiconductor memory. The decoding for all sixteen words in this memory is contained within the integrated

circuit memory itself. The four bits then select one of the sixteen words in the bipolar semiconductor memory.

As you can see, two words in the memory have been addressed by the four bits in the memory address register, one in the programmable read-only memory and the other in the bipolar semiconductor memory. However, we want only one word to be read out. The two words addressed in the two halves of the memory are read out in parallel and are applied to memory multiplexers. These multiplexers are enabled by the fifth bit in the memory address register. Only one of the two multiplexers will be enabled. If the desired word is stored in the programmable read-only memory, then the associated memory multiplexer will be enabled. The multiplexer associated with the bipolar semiconductor memory will be inhibited.

The purpose of the memory multiplexers is to produce a parallel-to-serial data conversion. The outputs of the programmable read-only memory and the bipolar semiconductor memory are eight parallel bits. The multiplexers scan these eight bits one at a time, causing the data at the output to be in serial form. The outputs of the two multiplexers feed an OR gate whose output is the serial memory data.

It is not possible to store data under program or instruction control in the read-only memory. However, data can be stored in the bipolar semiconductor memory. This is done with a Store Accumulator instruction. The eight output bits from the accumulator are applied directly to the bipolar semiconductor memory. When a Store Accumulator instruction is executed, the contents of the accumulator are transferred in parallel and stored in the location addressed.

The Control Section. The control section of the computer is the unit that sequentially examines the instructions of the program stored in memory. It interprets their meaning and generates the necessary control signals to have the arithmetic logic unit carry them out. In Fig. 1 you can see that the control section consists of the program counter, the instruction register, the instruction decoders as well as the clock, the timing counter, the timing decoder and the fetch/execute, run/stop and reset flipflops. A display multiplexer permits the contents of both the program counter and the instruction register to be displayed.

There are two distinct phases of operation of the computer, the fetch phase and the execute phase. In the fetch phase, the 5-bit address portion of the program counter is transferred to the memory address register. Then the instruction word stored in memory is read out and loaded serially into the instruction register. After this happens the computer goes into the execute phase where the arithmetic logic unit carries out the function specified by the instruction. During this time, the 5-bit address portion of the instruction word in the instruction register is transferred to the memory address register where the operand to be used by the instruction is addressed and read out serially.

Once the execute phase has been completed, the computer again goes into the fetch phase where the next instruction in sequence is read out and executed. This procedure continues until all of the instructions in the program have been executed and a halt instruction is recognized.

The basic source of timing and control in the computer is the clock oscillator. It

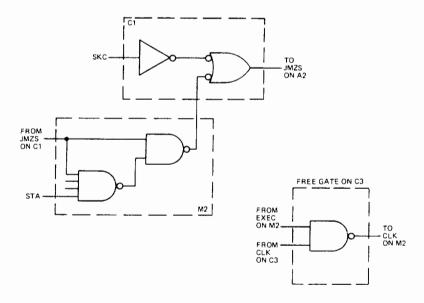

generates high frequency rectangular pulses that are used to control all sections of the computer. These clock pulses cause all of the counters to count and registers to shift at the appropriate times. The clock is controlled by a run/stop flip-flop. When the flip-flop is reset, it stops the clock so that no pulses are produced. When this flip-flop is set, it is in the run state and allows the clock to generate pulses.

The run/stop flip-flop is in turn controlled by a clear (CLR) signal generated by the reset flip-flop. The reset flip-flop is operated by a front panel push button which is used to reset and clear this flip-flop as well as the program counter, instruction register, accumulator, and fetch/execute flip-flop in the computer. The run/stop flip-flop is also controlled by the halt signal. Whenever a halt instruction is decoded, it causes the run/stop flip-flop to be reset, thereby stopping the clock and terminating the program.

The clock output pulses feed a 3-bit binary timing counter. This 3-bit ripple counter drives the fetch/execute flip-flop. This flip-flop determines the phase of operation of the computer. When it is reset, the computer is in the fetch state. When this flip-flop is set, the computer is in the execute state. The output of the timing counter causes the fetch/execute flip-flop to toggle alternately between the fetch and execute states. The timing counter counts eight pulses and then causes the fetch/execute flip-flop to be complemented. For example, if this flipflop is initially in the reset or fetch state, it will become set after eight clock pulses have occurred. After the second eight clock pulses have occurred, the flip-flop will again toggle from the execute to the fetch state.

The reason for counting by eight is because the word length used in the computer is eight bits. It takes eight clock pulses to cause the contents of an 8-bit register to be shifted in or shifted out. Therefore, all operations in the computer can take place during eight clock pulses. It takes eight clock pulses to load the instruction register with the 8-bit instruction word stored in memory. It takes an additional eight clock pulses to cause an arithmetic or logic operation to take place on the contents of the 8-bit accumulator.

In operating the Model 832 digital computer, the reset button on the front panel is pressed first to make sure the clock is stopped. This operation also clears the program counter, the instruction register, the accumulator register, the timing counter, and resets the fetch/ execute flip-flop to the fetch state. The computer is now ready to run. When the start button is depressed it automatically sets the run/stop flip-flop, allowing the clock to operate. During this fetch phase the contents of the program counter (00000) are transferred through the memory address multiplexer to the M register. This means that the computer automatically looks for the first instruction at memory location 016 in the programmable read-only memory. The first instruction word of any program should be stored there.

The instruction stored in memory location  $0_{16}$  is read out serially and stored in the instruction register. It takes eight clock pulses for this operation to occur. At the end of eight clock pulses the timing counter toggles the fetch/execute flip-flop. This puts the computer in the execute state. The five address bits in the instruction word are transferred through the memory address multiplexer to the M

register. Here the memory word referred to by the previous instruction is read out.

For example, suppose that a Load Accumulator instruction is detected. The address specified by the instruction word is fed to the memory where the contents of the specified memory location are read out serially and transferred into the accumulator register. It takes a total of eight clock pulses for this to happen. Once these eight clock pulses have occurred the data word will be in the accumulator and the timing counter will recycle, resetting the fetch/execute flip-flop to the fetch phase.

During the execute phase, the program counter is incremented to 0001. This automatically causes the program counter to contain the address of the next instruction in sequence to be fetched. When the fetch phase occurs, the program counter contents are again transferred to the M register where the next instruction of the program in sequence is read out and stored in the instruction register.

The instruction register is monitored by the instruction decoder. This decoder looks at the op code (three most significant bits) of the instruction word. It produces eight output states, only one of which is enabled at a time. The output line enabled determines which instruction is to be executed.

If the operate (OPR) instruction is specified by the op code, it enables the operate function code decoder. This is another decoder that monitors the three least significant bits of the address portion of the word in the instruction register. Only one of the eight output lines of this decoder will be enabled. The output line enabled will define which of the eight possible operate functions will be executed.

The output control lines from the instruction and function decoders are combined in logic gates along with timing pulses generated by the timing decoder. The timing decoder monitors the three flip-flops in the timing counter. Eight output signals are generated by the timing decoder. The outputs of the timing decoder designated TØ, T1, T2 and T7 are the ones used to generate most of the control signals.

The Arithmetic/Logic Section. The arithmetic/logic unit (ALU) of the Model 832 digital computer is that section which carries out the operations specified by the instructions. Most of the instructions specify some arithmetic or logic operation. These arithmetic or logic operations will be carried out on the data contained in the accumulator, the B register, the E register and from data words in memory specified by the instruction. The various operations are performed by the register gating logic and the arithmetic/logic unit.

As an example of the operation of the ALU, consider the arithmetic operations of add and subtract. When an add operation is selected, the contents of the accumulator will be added to the word stored in the memory location specified by the instruction word. These two words are added serially, a bit at a time, in the arithmetic unit and the sum is stored back in the accumulator. When a subtract operation is specified, the contents of the memory location specified by the instruction are subtracted from the contents of the accumulator. Again the operation is performed serially, a bit at a time, and the difference is stored back in the accumulator. The carry flip-flop is used to store any carry condition that arises. so that the carry may be added to the next bit position.

The register gating logic block shown in Fig. 1 permits a wide range of data transfers between registers. Data may be exchanged between the accumulator and the B register or the accumulator and the E register. The logical AND operation also takes place between the A and B registers when it is executed.

The overflow flip-flop determines a specific overflow condition in the accumulator. Should a carry output be generated by the most significant bits of

the word in the accumulator and memory during an add operation, an overflow condition is indicated. This may or may not be a genuine overflow or error condition, depending upon the data in the register and the operation being carried out. However, the overflow indication is given so that it can be detected should the operator require this detection. The overflow is displayed on the 8-bit lamp display shared with the 5-bit program counter.

## **Word Formats**

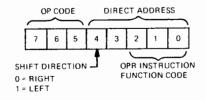

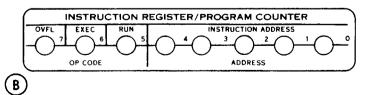

Figs. 2 and 3 show the instruction and data word formats used in the Model 832 digital computer. Both are eight bits in length.

#### INSTRUCTION WORD FORMAT

Fig. 2 shows the instruction word format. The 8-bit word is divided into two sections, the op code and the direct address. The bit positions are numbered Ø through 7 from right to left. Bits 7 through 5 (7:5) are used to define the instruction op code. This permits a total of eight basic instructions for the computer. Seven of these instructions are memory reference instructions in that the operation they specify calls for an operand from some location in memory. That location in memory is identified by the address portion of the instruction word which is made up of bits 4 through Ø (4:0). These five bits permit us to define a maximum of  $2^5 = 32$  memory locations. All memory locations are addressed directly. There is no immediate, indirect, indexed or literal addressing in the Model 832. However, some of these modes of addressing can be demonstrated through programming.

The eighth instruction defined by the op code is the operate (OPR) instruction. This instruction defines operations that

Fig. 2. Instruction word format.

do not require addressing a location in the memory for an operand. These include logic operations, shifts, skips and register transfers. Whenever the OPR instruction is selected, the bits of the address portion of the instruction word are used to further define the exact function to be carried out. Bits 2 through  $\emptyset$  (2: $\emptyset$ ) can specify eight functions. Bit 3 is not used. Bit 4 defines the direction of the shift operation specified by the function code. A binary 0 represents a right shift and a binary 1 represents a left shift.

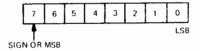

#### DATA WORD FORMAT

Fig. 3 shows the data word format for the Model 832. As with the instruction word, the data word bits are numbered 7 through Ø from left to right. In the Model 832 digital computer, the data may be either binary bit patterns or numbers representing a specific magnitude. In either case, the pure binary code is used.

Fig. 3. Data word format.

When the data word defines a number, there are several ways in which these numbers can be represented. These are positive integers, signed integers or signed fractional numbers. Table I shows how numbers are represented in each of these three number systems. In each case the largest and smallest numbers possible in each scheme are indicated. The decimal,

| NUMBER REPRESENTATION SYSTEM | DECIMAL                | OCTAL | HEX | BINARY    |

|------------------------------|------------------------|-------|-----|-----------|

| Positive Integer             |                        |       |     |           |

| Largest Number               | +255                   | 377   | FF  | 11111111  |

| Smallest Number              | 0                      | 000   | 00  | 00000000  |

| Signed Fractional            |                        |       |     |           |

| (2's Complement)             |                        |       |     |           |

| Largest Positive Number      | +127/128<br>(.9921875) | 177   | 7F  | 0.1111111 |

| Smallest Negative Number     | -128/128<br>(-1.0)     | 200   | 80  | 1.0000000 |

| Signed Integer               |                        |       | į   |           |

| (2's Complement)             |                        |       |     |           |

| Largest Positive Number      | +127                   | 177   | 7F  | 01111111. |

| Smallest Negative Number     | -128                   | 200   | 80  | 10000000. |

Table I. Number representation in the Model 832.

octal, and hexadecimal binary representations for each are given for convenience.

In the positive integer number representation system there are no fractional or negative numbers. The smallest number represented is 0, the largest is 255. As you recall, the largest number that can be represented by a binary code is equal to  $2^n - 1$ , where n is the number of bits. This gives us  $2^8 - 1 = 256 - 1 = 255$ . For many of the calculations and demonstrations in the Model 832 this number representation is the most convenient to use.

In the signed fractional number representation system, also known as the 2's complement system, the binary point is assumed to be between bits 6 and 7 of the data word. This means that bit 7 is used as a sign bit where a binary 0 equals a positive sign and a binary 1 represents a negative sign. The remaining bits are used to define the magnitude of the number.

With the binary point to the left of the seven bit number, all of the numbers will be fractional. The largest positive number, then, is +127/128 or in decimal form .9921875. The smallest negative number is -128/128 or -1. This means that all of the numbers represented by the data word in this system are between +1 and -1. A wide range of numbers can be represented by using this system to scale the numbers to represent other numbers smaller or larger than the fractional value.

In the signed integer number representation the 2's complement representation of numbers is also used. Here the binary point is assumed to be to the right of the number. This permits us to represent the range of numbers between  $\pm 127$  and  $\pm 128$ . Since bit 7 is used as the sign bit, this leaves a total of 7 data bits. The maximum that can be represented with the 7 bits is  $2^7 - 1 = 128 - 1 = 127$ .

## The Instruction Set

There are 15 basic instructions that the Model 832 digital computer can execute. The 3-bit op code in the instruction word defines eight instructions, seven of which are memory reference instructions. The eighth is a generic instruction that further defines eight functions or operations that do not require memory reference. In this section we completely define the instruction set for the Model 832 digital computer.

# MEMORY REFERENCE INSTRUCTIONS

# Load Accumulator (LDA) Op Code 000

The load accumulator instruction is used to transfer the contents of the memory location specified by the 5-bit address in the instruction word into the accumulator (A) register. When this instruction is executed, the contents of the designated memory location will be transferred serially into the accumulator register.

## Store Accumulator (STA) Op Code 00I

The store accumulator instruction causes the contents of the accumulator register to be stored in the memory location designated by the 5-bit address in the instruction word. Because of the nature of the memory of the Model 832, the STA instruction has no effect when addresses 00000 through 01111 are used. The first 16 words of memory defined by these addresses are read-only memory

locations. They are programmable in that they can be set to the desired contents with the front panel programming switches. However, vou cannot automatically write into these locations from the computer itself. For that reason when an STA instruction specifies an address in this range, nothing will take place. However, it is possible to write data into the last 16 words of memory, addresses 10000 through 11111, with the STA instruction. When this instruction is executed, the contents of the accumulator will be transferred in parallel to the bipolar semiconductor memory and stored in the designated location.

In some versions of the Model 832 computer, the semiconductor memory is an optional feature. For those models of the computer without this memory, the E register within the computer is wired to act as a single memory location into which data can be written. This single register acts as a memory location that is addressed with bit 4 of the instruction word. When this bit is a binary 1 and the STA instruction is specified, data will be transferred from the accumulator to the E register in serial form for storage. Any address between 10000 and 11111 will cause the contents of the accumulator to be stored in the E register. When the optional memory is available, the E register is not used for this purpose.

## Add (ADD) Op Code 010

The ADD instruction causes the contents of the accumulator (A) to be added to the number stored in the memory

location designated by the address portion of the instruction word. The sum will be stored back in the accumulator. The number previously stored in the accumulator will be lost. The addition process takes place serially, a bit at a time. The addition process is strictly algebraic in nature and it may be in any of the three formats that were designated earlier.

## Subtract (SUB) Op Code 011

The SUB operation causes the contents of the specified memory location to be subtracted from the contents of the accumulator. The difference will appear in the accumulator. The number stored there previously, the minuend, is lost. The operation is carried out serially, a bit at a time.

## Unconditional Jump (JMP) Op Code 100

This instruction is an unconditional jump or branch instruction that causes the computer to execute instructions out of their normal sequence. When the JMP instruction is executed, it causes the address designated by the jump instruction to be transferred to the program counter. This means that the next instruction to be executed will be that instruction that is contained within the memory location specified by the jump instruction.

## Jump-On-Minus (JOM) Op Code 101

This instruction causes the sequence of executing instructions in the computer to be changed if the accumulator contains a

negative number. The computer circuitry monitors bit 7 of the accumulator and interprets it as a sign bit. If it is a binary 0 the number is considered to be positive. If bit 7 is a binary 1, the number is negative (minus). When the JOM instruction is executed, the circuitry looks at bit 7 of the accumulator. If it is a binary 0 then no change will take place. The computer will continue to execute the instructions of the program in normal sequence one after another. However, if bit 7 is a binary 1, the 5-bit address specified by the JOM instruction will be transferred to the program counter so that the next instruction to be executed in sequence will be taken from that address.

## Jump-On-Zero (JOZ) Op Code 110

This conditional jump instruction causes the computer to execute instructions out of sequence if the number in the accumulator is zero. All eight bits of the accumulator are monitored by the circuitry and when all are binary 0's, a logic signal is generated to indicate this condition. When the JOZ instruction is executed, the circuitry looks at this zero indication signal. If it is a binary 0, indicating that the accumulator is not zero, then the computer will continue to execute instructions in the normal sequence. If the zero indication signal is a binary 1, it tells the logic circuitry that the content of the accumulator is zero. The address of the next instruction executed will come from the address specified by the JOZ instruction. This address is transferred from the instruction register to the program counter. Instructions following this will be in sequence starting from that address.

# Operate (OPR) Op Code 111

The OPR instruction is a generic instruction not requiring reference to a memory location. For this reason the bits of the instruction word normally used to designate an address are used to form a function code that specifies a specific operation to take place. There are eight operations that can take place with the OPR instruction. These are defined by a 3-bit function code, bits 2 through  $\emptyset$  (2: $\emptyset$ ) in the instruction word format. These eight operations are defined next.

#### OPERATE INSTRUCTIONS

## Rotate A and B (RAB) Function Code 000

When this instruction is executed, the contents of the accumulator (A) register will be exchanged or rotated with that of the B register. The contents of the accumulator will be shifted out serially into the B register while the contents of the B register are shifted into the accumulator. This instruction is specifically designed for the Model 832 digital computer to conserve memory space. It permits the storage of intermediate results during calculations without reference to a memory location. The contents of the accumulator can be saved in the B register with this instruction and then later recalled by again executing the instruction.

## Complement Accumulator (CMA) Function Code 100

Executing this instruction causes the l's complement of the contents of the accumulator to appear in the accumu-

lator. The binary number in the accumulator is shifted out a bit at a time, inverted, and then shifted back into the accumulator. When this instruction is executed the number in the accumulator is lost but its complement appears in the accumulator where all 1's have been changed to 0's and all 0's have been changed to 1's. The 2's complement version of a number in the accumulator can be produced by executing the CMA instruction and then by adding one with an add instruction.

## Logical AND (AND) Function Code 010

Executing this instruction causes the contents of the A register to be logically ANDed with the contents of the B register with the result appearing back in the accumulator. The original contents of the accumulator are lost, but the original contents of the B register are recirculated and saved. Executing this instruction produces the pure logical AND operation a bit at a time in serial form. This instruction can be used for masking and editing operations on data words.

## Rotate A and E (RAE) Function Code 110

Executing this instruction causes the contents of the accumulator (A) register to be rotated or exchanged with the contents of the E register. This instruction is similar to the RAB instruction except, of course, the E register is used instead of the B register. When this instruction is executed, the contents of the accumulator are shifted out serially into the E register are shifted serially into the accumulator. This instruction is valid

only on computers containing the optional semiconductor memory expansion. On those computers without the semiconductor memory, this instruction causes binary 0 to be shifted into the accumulator. Thus, for these models the RAE instruction could be called clear accumulator (CAC).

# Shift Accumulator (SHA) Function Code 001

The SHA instruction causes the contents of the accumulator to be shifted one bit position either to the right or to the left, depending upon the state of bit 4 in the instruction word. If this bit is a binary 1, the shift is to the left. If this bit is a binary 0, the shift is to the right. The bits shifted out of the accumulator to the right or to the left are lost. Binary zeros are shifted into the register in either right or left shifts. This is a logical rather than an arithmetic shift where all bits of the accumulator are shifted, including the sign bit.

## Skip-on-Condition (SKC) Function Code 101

The Skip-on-Condition instruction causes the next instruction in sequence in the program to be skipped and the following instruction executed if a specified condition is met. The condition monitored in the Model 832 digital computer can be wired to sense practically any logical condition in the computer. It can be used to skip on accumulator Ø, accumulator minus, overflow, or any other logical condition that can be monitored. By using an external signal, the program sequence can be controlled by outside events. If the specified condition is met, the next instruction after the skip is passed over and the following

instruction is executed. This is done by incrementing the program counter by one so that the next instruction in sequence can be skipped automatically. If the condition is not met, the normal program sequence will take place and the next instruction in sequence will be executed.

## Decrement Accumulator (DCA) Function Code 011

This instruction causes the contents of the accumulator to be decremented by one. In other words, one is subtracted from the contents of the accumulator when this instruction is performed. This instruction permits down counting operations in the accumulator.

# Halt (HLT) Function Code 111

Executing the halt instruction causes the computer to stop. When this instruction is executed, clock pulses are inhibited at the end of the execute phase to prevent further operation.

This basic instruction set for the Model 832 has been selected to make maximum use of the simple architecture of the computer. The various instructions have been selected to optimize computer operation with a small number of memory locations. Despite the small memory size, the flexible instruction set permits a fantastic variety of programs to be run.

This built-in flexibility also permits the instruction set to be modified to optimize the use of the computer for some particular application. Depending upon the application, it is possible to eliminate those instructions rarely used and replace them with other instructions of more value to the application. For example, the additional rotate register E may not be

needed, in which case the RAE instruction can be eliminated. In its place a clear accumulator or increment accumulator instruction may be substituted. Another example is to eliminate the subtract instruction and modify the logic so that the AND instruction is made into a memory reference instruction. Since sub-

tract operations can be performed with the add instruction by manipulating the data properly, in some applications it may be more desirable to have the AND instruction as a memory reference. In this case, it frees the 010 function code and permits other generic instructions to be added.

# **Displays and Controls**

All of your communications with the Model 832 digital computer will be via the displays and controls. The various switches and push buttons provide the input data and the control signals to the computer. The display lamps provide the outputs. In this section you will learn to use each of the controls and interpret the displays. Pay particular attention to this section, as proper operation of this computer is fully dependent upon your knowledge and understanding of the displays and controls.

#### **DISPLAYS**

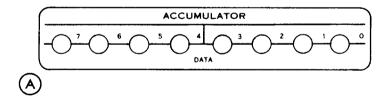

The Model 832 digital computer has two incandescent binary light displays. Fig. 4A is the display which appears on the right of the computer. Fig. 4B appears on the left of the computer. Both are eight bits in length. They permit the computer operator to observe practically all of the most important logic states in the machine during its operation. Like any other binary light display, an off

lamp indicates a binary 0 and an *on* lamp indicates a binary 1.

The 8-bit display on the right monitors the contents of the accumulator register. The bits are labeled  $\emptyset$  through 7. The data in the accumulator can be either a binary number or simply a bit pattern. For binary numbers bit  $\emptyset$  is the least significant bit position. Bit 7 represents the sign bit in 1's and 2's complement representation of negative numbers.

This display is fixed and will always monitor the accumulator contents. Notice that the display is divided into two 4-bit groups for convenience in viewing the contents of the accumulator as a hexadecimal number. For example, if the content of the accumulator is 0101 1100, this number would be represented by the hexadecimal digits 5C. Refer to the Appendix for hexadecimal conversion tables.

The left-hand display on the computer front panel permits the operator to monitor a wide range of program states.

Fig. 4. Model 832 displays.

The part of the computer monitored by this display is determined by the display switch. With the switch in the down or IR position, the display monitors the instruction register. Notice that the labeling on the display divides it into upper and lower halves with the lower half marked according to the instruction word format. Bits 7 through 5 (7:5) of the instruction word represent the 3-bit op code. Bits 4 through  $\emptyset$  (4: $\emptyset$ ) designate the address referred to by the op code. These five bits represent the direct address referenced by the seven memory reference instructions.

For the operate (OPR) instruction bits 2 through  $\emptyset$  (2: $\emptyset$ ) represent the function code. Bit 4 designates the direction of shift operations when the operate instruction is being used. The instruction repetoire table on the front panel of the computer below the accumulator display gives complete details.

When the display switch is in the up or PC position, the left-hand display monitors the program counter which contains the instruction address or the address of the next instruction in sequence to be executed. Bit positions 4 through  $\emptyset$  (4: $\emptyset$ ) contain this 5-bit address. The remaining three bits, 5, 6, and 7, monitor three operating conditions in the computer. Bit 5 monitors the RUN state of the machine. When automatic operation is selected by the front panel switches, the run light will be on while the clock is generating clock pulses. When the computer is reset or is caused to halt due to the execution of a halt instruction, the RUN lamp will be off.

The bit 6 position is the execute (EXEC) state which tells the operator when the computer is in the execute phase. During the Fetch state the EXEC lamp will be off. During the EXEC phase the bit 6 lamp will be on.

Bit 7 monitors the overflow state of the arithmetic section of the computer. During any arithmetic operation involving additions and subtractions, if there is a carry out of the bit 7 position in the accumulator, the overflow lamp will light. There are numerous ways of determining whether a true overflow condition exists when this lamp lights. The interpretation is up to the operator depending upon the data word format he is using. The OVFL indication simply shows a carry out of the bit 7 position and it may be interpreted as desired.

There are several special features about the displays which you should understand. First, whenever the computer is in the reset state all of the lamps in both displays will be off.

Whenever power is applied to the computer, the flip-flops in the registers monitored by the displays can come up in any random state. Therefore, the displays will show this random state. By depressing the reset push button, the displays can be cleared.

The displays do not change when the clock in the computer is not running. When the clock is running at low speed, where clock pulses are approximately two pulses per second, you can observe the data changing in the registers by watching the lights flash on the display. The slow clock speed is slow enough to permit you to readily monitor the changes in the display for each clock pulse. However, when the computer is running at high speed on the fast clock, the display lamps will all be on and will glow dimly.

#### **CONTROLS**

The control switches and push buttons on the front panel of the Model 832 digital computer are for the most part

19

self-explanatory. In this section we describe the exact function of each of these controls. See Fig. 5.

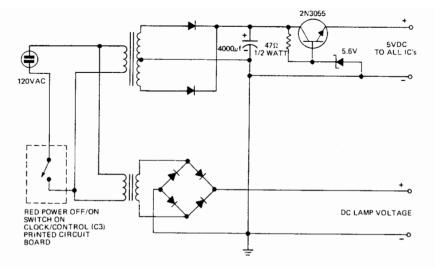

Power. The power switch is a red control used for applying 120 VAC to the computer power supply. No power is applied to the computer with the switch in the down or off position. With the switch in the up or on position, the power supply is enabled.

Clock. This two-position white switch selects either the automatic or single step modes of clock operation. With the switch in the up or AUTO position, clock pulses will be supplied to the computer circuitry by the main systems clock. With the switch in the down position the computer is in the single step mode. Clock pulses are applied to the computer by the single step manual push button located in the lower right-hand corner of the computer panel.

Speed. This white switch selects either a low or high frequency clock. It is effective only in the AUTO clock mode. With the switch in the down position, a low frequency clock is selected. The low speed clock frequency is approximately two pulses per second. With the speed switch in the up position the high frequency clock is selected. This clock runs at approximately 250 kHz.

Display. This white switch selects the circuitry displayed by the left-hand display on the computer panel. With the switch in the down or IR position, the left-hand 8-bit display shows the contents of the instruction register. With the switch in the up or PC position the display monitors the program counter as well as the states of the overflow, fetch/execute, and run/stop flip-flops.

Switch Register. These eight white switches form a switch storage register from which data can be entered directly into the accumulator. By setting these switches to a desired number, this number may be loaded into the accumulator by depressing the LOAD push button. The bit switches are labeled  $\emptyset$  through 7 from right to left in accordance with the accumulator numbering where the right-hand switch is the least significant bit. A switch in the down position represents a binary 0 and a switch in the up position represents a binary 1.

Load. This black push button causes the contents of the switch register to be loaded into the accumulator. The moment this switch is depressed, the accumulator contents will be equal to that of the switch register. The accumulator display will show the result.

Reset. This red push button resets the instruction register, program counter, accumulator register, run/stop flip-flop and the timing counter in the computer. This button is a complete systems reset. This is the normal beginning state for the computer operation. This reset button control is completely asynchronous in that any time that it is depressed, it will cause the clock to stop and all registers to be reset regardless of the current state of operation.

Start. This red push button sets the run/stop flip-flop and causes clock pulses to be generated. If the computer is running, pressing the Start push button will reset the run/stop flip-flop, allowing you to halt the computer. Operating the Start push button once more will allow the program to continue.

Step. This black push button generates a single clock pulse each time it is depressed. This button functions only when the clock switch is in the step mode. This step control permits the operator to generate clock pulses at any desired manual rate. This convenience

permits the operator to sequence the program a clock pulse at a time so that he can view the results of each and every clock pulse change.

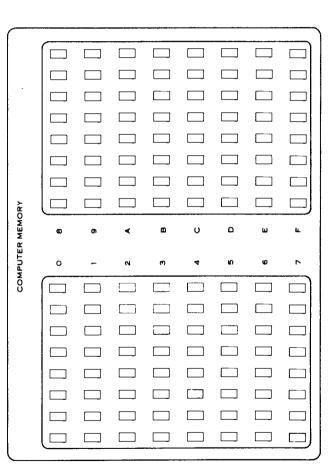

Computer Memory. The 128 switches on the left-hand side of the computer front panel are not really controls in the normal sense. These switches make up one-half of the computer memory of the Model 832. The switches are grouped as sixteen 8-bit words numbered Ø through 9, A through F in hexadecimal form.

These are the hexadecimal addresses for these words of the memory. A switch in a down position represents a binary 0 and a switch in the up position represents a binary 1. These switches may be set to store instructions and data in the computer memory. Normally the computer, after it has been reset, will fetch the first instruction from memory location 0. For this reason the first instruction to be executed should be located in memory location 0.

# Programming and Operating The Computer

The Model 832 digital computer, like any digital computer, must be properly programmed before it can perform any useful function. All standard digital computer programming techniques are fully applicable to the Model 832, as long as the programmer confines himself to the given instruction set. Knowing the instruction set and basic computer programming fundamentals you can program virtually any problem that will fit within the memory. The problem to be solved or function to be performed is analyzed and broken into a number of simple steps. Each of these steps is then implemented with an instruction or group of instructions. The instructions are then written in sequence to form a complete program. The program is entered into memory and the computer is operated to produce the final result. In this section we are going to give you several suggestions which will be quite useful when you begin programming and operating the Model 832 digital computer.

#### **PROGRAMMING**

Programming fundamentals are covered completely in experimental manuals 10K and 11K. The experiments outlined in these manuals permit you to demonstrate all of the most important programming fundamentals on the Model 832 digital computer. You should immediately learn or review the programming fundamentals outlined in these manuals. Once you have performed the programming experiments in these manuals you will be completely

familiar with the use of the Model 832. You will then want to try your hand at programming a variety of problems on the computer.

The Model 832 is programmed in machine language. That is, as the programmer you will enter the binary data representing each instruction and data word by manipulating the switch register and memory switches. However, in writing programs for the Model 832 we recommend the use of hexadecimal notation. Once you are intimately familiar with the hex system you can readily convert between binary and hex numbers. We recommend that you memorize the binary and hexadecimal equivalents for all 4-bit combinations. A table outlining the conversion equivalents is given in the Appendix. You should write the programs in hexadecimal notation and then you will have no difficulty in converting them into their equivalent binary numbers when you enter the program into the computer.

Programming the Model 832 is most easily accomplished by using a programming coding form similar to that shown in Table II. The left-hand column lists the memory address of each location in the memory. This address is given in hexadecimal notation.

Memory addresses Ø through 9 and A through F are the memory locations in the programmable read-only memory, accessible only by the front panel switches. Memory locations 1Ø through 1F are the sixteen locations in the bipolar semiconductor memory.

| MEMORY<br>LOCATION | CONTENTS | HEX<br>CONTENTS | COMMENTS     |

|--------------------|----------|-----------------|--------------|

| 0                  | LDA 6    | 06              | 42           |

| 1                  | ADD C    | 4C              | 42 + 27 = 69 |

| 2                  | SUB 1E   | 7E              | 69 - 35 = 34 |

| 3                  | STA 12   | 32              |              |

| 4                  | HLT      | E7              |              |

| 5                  |          |                 |              |

| 6                  | 42       | 2A              |              |

| 7                  |          |                 |              |

| 8                  |          |                 |              |

| 9                  |          |                 |              |

| A                  |          |                 |              |

| В                  |          |                 |              |

| C                  | 27       | 1B              |              |

| D                  |          |                 |              |

| E ,                |          |                 |              |

| F                  |          |                 |              |

| 10                 |          |                 |              |

| 11                 |          |                 |              |

| 12                 | (34)     | 22              | RESULT       |

| 13                 |          |                 |              |

| 14                 |          |                 |              |

| 15                 |          |                 |              |

| 16                 |          |                 |              |

| 17                 |          |                 |              |

| 18                 |          |                 |              |

| 19                 |          |                 |              |

| 1 A                |          |                 |              |

| 1B                 |          |                 |              |

| 1C                 |          |                 |              |

| 1D                 |          | ,               |              |

| 1E                 | 35       | 23              |              |

| 1F                 |          |                 |              |

Table II. Recommended program coding format,

Adjacent to the memory address is another column designated Contents. This column describes the instruction or data word stored in each location. In this column is written the mnemonic for each instruction in the program along with the hexadecimal memory address referred to by those memory reference instructions used and the decimal value of data numbers to be used.

The next column to the right gives the 2-digit hex value of each instruction and data word. You can use the decimal-to-hex conversion chart in the Appendix to help you arrive at the values here. Then using this column and mentally converting to binary, you enter the program into memory.

The right-hand column in the programming form is a Comments column. It permits you to make specific notations about the operation taking place at each instruction step.

To illustrate the operation and programming of the computer, an example problem is shown in Table II. As you recall, the Model 832 always looks for the first instruction to be executed in memory location  $\emptyset$ . Here the computer first interprets the LDA 6 instruction. This tells the computer to load the accumulator with the contents of memory location 6. As you can see in Table II, location 6 contains the number 42.

Once the content of memory location 6 is loaded into the accumulator, the next instruction is executed. There is an ADD C instruction in memory location 1. It tells the computer to add the contents of memory location C to the contents of the accumulator and store the result back in the accumulator. The content of memory location C is the number 27. This instruction will cause 27 to be added to the number 42 now in the accumulator

with the result, 69, being stored back in the accumulator. Note that the Comments column in Table II indicates this for reference.

The next instruction in sequence is then executed. This is an SUB 1E instruction in memory location 2. This causes the contents of memory location 1E, which is the number 35, to be subtracted from the contents of the accumulator, 69. The difference, 34, will appear in the accumulator.

The next instruction in sequence, stored in memory location 3, is then executed. This is an STA 12 instruction. It tells the computer to store the contents of the accumulator in memory location 12. Therefore, the contents of the accumulator, 34, designated in parenthesis, are stored in memory location 12. The next instruction, memory location 4, is then executed. This is an HLT or halt instruction so the computer operation stops. The final result of the calculation (the number 34) is still in the accumulator and will be displayed on the accumulator lamps.

It is a good idea to use the format shown in Table II to program each one of the problems you wish to solve. By writing a neat program in this form you will have complete documentation for every problem that you solve.

There are many common operations that you may wish to perform on the Model 832 digital computer which are not fully implemented by the instruction set. Typical of these are multiply and divide operations or logic operations such as the OR function. These functions can be readily performed but must be done by program subroutine. Several of the most popular subroutines are given in the Appendix. Other methods for performing these operations can be implemented, but

the ones given in the Appendix are recommended because they use the least number of memory locations, thereby saving as much space as possible for other instructions.

#### OPERATING THE COMPUTER

Once you have written the program you will enter it into the computer memory and cause the computer to execute that program. In this section we will show you exactly how to do this.

Loading the Memory. Loading the programmable read-only memory is extremely simple. This is only a matter of setting the switches to the proper binary bit positions as they correspond to the hexadecimal contents of the words in your program. Simply refer to the hexadecimal Contents column of the program coding form, translate it into the equivalent binary numbers and set the switches on the appropriate memory word. If the program is short enough to be contained within sixteen words, the entire program can be stored in the switch memory. If the program requires more than sixteen locations or if store-into-memory operations are required, then it will be necessary to load the semiconductor read/write memory. If the program is long enough and requires using the semiconductor memory, the semiconductor memory should be loaded first. This is done by using a simple programmed subroutine set into the memory switches. Once you have entered all of the required data into the semiconductor memory using this program, the remaining part of the program can be set into the switch memory as described earlier.

The procedure for loading the semiconductor memory is to write a simple program that will cause the desired data

to be loaded into a specific memory location. This is done by first loading the accumulator with the instruction or data word to be stored in a specific memory location. This is done by setting the switch register on the front panel to the desired number and depressing the LOAD push button. This will cause the contents of the accumulator to be the same as that of the switch register. Then in memory location Ø you will store an STA instruction that will cause the contents of the accumulator to be stored in a memory location designated by the five address bits in that STA instruction word. The five address bits of the STA instruction word are set to a memory location in the 10000 to 11111 range as desired. In memory location I a halt instruction is written. Once the accumulator has been loaded with the appropriate word and the address portion of the STA instruction set into the location where the word is to be stored, the Start button is depressed. This will cause the computer to execute the program and store the word in the accumulator and the desired memory location and then halt automatically. The computer should be in the high speed automatic clock mode for this purpose. Once the word has been loaded, the Reset button is depressed to clear the accumulator and again ensure that the computer will execute the instruction stored in memory location Ø when the Start button is depressed.

The next word to be loaded is set into the switch register and then loaded into the accumulator with the Load push button. The desired address is entered into the STA instruction by the front panel switches from memory location 0. The Start button is then depressed to cause the program to execute the store instruction and place the desired word in

the designated memory location. This procedure is repeated until all of the necessary memory locations are loaded. Then the remaining part of the programming operation can be completed by setting the memory switches to the desired positions.

Once you have loaded the semiconductor memory you may wish to check the contents to be sure that you have made no mistakes. Again this can be done by writing a simple subroutine that will cause each memory location in the semiconductor memory to be displayed on the accumulator lamps one at a time. By using the slow speed clock mode for this operation, you can readily observe the contents in each memory location of the semiconductor memory and check it against the programming coding sheet.

The simple subroutine shown will perform this operation.

| 0 | LDA 1Ø |

|---|--------|

| 1 | LDA 11 |

| 2 | LDA 12 |

| 3 | LDA 13 |

| 4 | LDA 14 |

| 5 | LDA 15 |

| 6 | LDA 16 |

| 7 | LDA 17 |

| 8 | LDA 18 |

| 9 | LDA 19 |

| Α | LDA 1A |

| В | LDA 1B |

| C | LDA 1C |

| D | LDA 1D |

| E | LDA 1E |

| F | LDA 1F |

You can program this subroutine into the programmable read-only memory. Then depress the Reset button to clear the machine. Put the computer in the automatic operate mode on low speed. Then

depress the Start button. The contents of each of the memory locations 10 through 1F will be displayed one at a time during the fetch phase. Since there is no HLT instruction, you will have to press the Reset button to stop the computer.

As the binary content of each memory location is displayed, you can mentally convert it into hexadecimal notation and compare it to the hexadecimal contents designated by the program.

It is important to remember that the semiconductor memory is a volatile memory and all memory data will be lost if computer power is removed. If you wish to retain a program, simply leave the computer power on. The computer draws very little power, and therefore can be left on indefinitely. No damage will occur with continuous operation.

Operating the Computer. Operation of the computer is simply a matter of depressing the Reset button and then the Start push button. This will cause the program to be executed instantaneously if the high speed automatic clock mode is selected. By selecting the low speed clock in the automatic mode, you can watch the program being executed. You can see each instruction word loaded into the instruction register and the contents of the accumulator as each instruction is carried out. By following your programming coding sheet as the computer is operating, you can see how each instruction is loaded and executed.

To execute the program yourself, a clock pulse at a time so that you can stop at any given point, you should select the step mode of operation. As you depress the Step push button, one clock pulse will be generated. Remember that it takes eight clock pulses to cause any given computer operation to take place. You can count the number of clock

pulses as you depress the button. In starting the program you will initially depress the Reset button to clear the machine. Then you depress the Step push button eight times. This causes the first instruction to be fetched and loaded into the instruction register. The next eight clock pulses cause the instruction to be executed. You should remember that all operations take place with eight clock pulses and it is convenient for you to count these clock pulses as you watch each instruction being fetched and executed. If you do not count the clock pulses in 8-bit groups, you can end up at some intermediate point where the results being displayed on the lamps are essentially meaningless.

There are several useful tips that you may wish to use in programming and operating the Model 832. First of all, most programs that you will write will start with the LDA instruction. The reason for this is that it is necessary to initially load the accumulator with data in order to perform the necessary operations on that data. The first instruction in your program, therefore, will almost always be an LDA instruction. However, in order to conserve memory space it is a

good idea to eliminate as many instructions for your program as possible. The LDA instruction can generally be eliminated by using the switch register and Load push button. Before you start the program, you load the accumulator with the necessary data to be used simply by entering it into the switch register and depressing the Load push button. This eliminates the initial LDA instruction and permits the first instruction in your program to be some other operation.

Remember, if you use this procedure, it may still be necessary to provide a storage location for the word you are placing in the accumulator manually, especially if this word is referred to elsewhere in the program. If it is not, then you save an additional memory location. Efficient use of memory is good programming practice and practically a necessity with the Model 832.

Of course, you may wish to start the program at some memory location other than memory location  $\emptyset$ . In such a case, simply load a jump (JMP) instruction in memory location  $\emptyset$  that will cause the computer to branch to the first instruction of the program anywhere in memory.

# Logic Circuitry Analysis

All of the logic circuitry for the Model 832 digital computer is contained on ten printed circuit boards. The circuitry in the Model 832 is made up predominantly of TTL SSI and MSI integrated circuits. Several DTL integrated circuits and discrete component circuits are also used. In this section we are going to analyze in detail the circuitry contained on each of the ten printed circuit boards in the computer. The operation of the power supply will also be discussed.

The computer circuitry is divided into four basic groups: the memory, control,

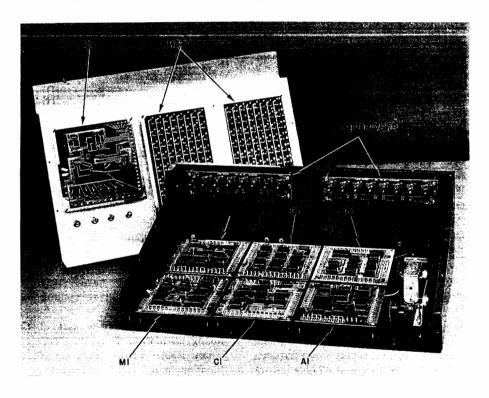

arithmetic, and power supply. The computer memory and associated circuitry is contained on three circuit boards labeled M1, M2, and M3. The control circuitry is contained on three circuit boards labeled C1, C2, and C3. The arithmetic circuitry is contained on two printed circuit boards labeled A1 and A2. The remaining two boards are lamp drivers. The power supply circuitry is wired to terminal strips on the bottom plate of the computer cabinet. Fig. 6 shows the position of each of these circuit boards in the computer.

Fig. 6. Circuit board identification inside the computer.

29

Except for the lamp driver boards and the power supplies, the circuitry for each printed circuit board is contained on a large separate logic diagram. Refer to these as each board is discussed. A complete list of signal names and their meanings appears in the Appendix. Refer to this for further clarification of each as it is referred to in the text.

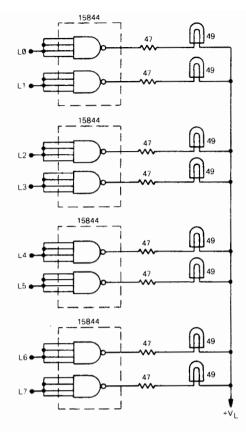

#### THE LAMP DRIVERS

There are two lamp driver printed circuit boards in the Model 832 computer. Each contains eight incandescent lamps and the associated driver circuitry. Fig. 7 shows the circuitry contained on each board. The lamp is a type 49 incandescent lamp rated at 2 volts at 60 ma. It has a bayonet base and mounts in the socket on the printed circuit board. The lamps are easily removed for replacement.

Each lamp is driven by a DTL lamp driver. These lamp drivers are contained within a type 15844 integrated circuit. This is a dual 4-input NAND gate with open collector output. The inputs are all tied together to form a single input. Whenever this input is a binary 1, the output transistor in the DTL gate is turned on. This supplies current to the lamp. Whenever the input is a binary 0, the output transistor is cut off and the lamp is out. There are two such lamp drivers in each of the four integrated circuits on the printed circuit board. The integrated circuits are powered by the +5 volt supply in the computer. The lamps themselves are supplied by a separate lamp driver power supply which furnishes approximately 5 volts. A 47-ohm resistor in series with each lamp drops the voltage for the lamps to about 2 volts.

Fig. 7. Lamp driver circuits.

#### THE M1 CIRCUIT BOARD

Refer to the large separate diagram outlining the circuitry on the M1 circuit board. This board contains the memory address register, the memory address decoder for the programmable read-only memory, and the timing counter and distributor.

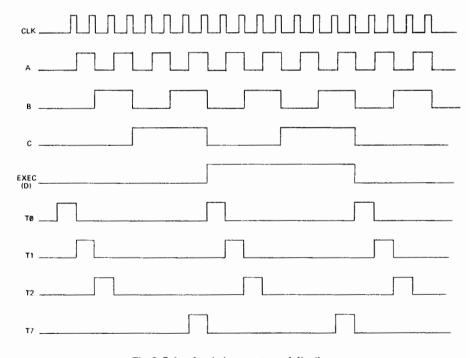

The timing counter is part of the timing distributor. This is a three-stage binary ripple counter made up of J-K flip-flops in 1C5 and 1C6. Outputs A, B, and C are applied to a type 7442 decoder, 1C7. This decoder monitors the counter

output and generates a series of eight output pulses designated TØ through T7. The outputs of the decoder are active low, meaning that the enabled output line is low while all others are high. The complement signals are made available by inverting them with the gates in IC8. Notice that only the timing signals TØ, T1, T2, and T7 are used.

The output of the C flip-flop in the timing counter drives another flip-flop designated as the fetch/execute flip-flop. This flip-flop, designated D, determines the operate state of the computer and is toggled once every eight clock pulses. Clock pulses are applied to the A flip-flop in the timing counter. Fig. 8 shows the waveforms for the timing counter, timing distributor and associated circuitry.

The memory address register is made up of IC3 and IC4. IC4 is a 7475 quad-latch. This is a 4-bit register made with type D flip-flops. IC3 is a 7400 IC connected as a type D flip-flop. Together the two IC's form a 5-bit storage register. This register holds the address of the word in memory to be addressed. The output of IC3 designated MA4 is the most significant output bit.

The M register receives its input data on lines ADRØ through ADR4. Data is loaded into the register during the TØ time interval produced by the timing distributor. Note the connection between the TØ output of IC8 and IC3 and IC4. During TØ time, the data appearing on the ADRØ through ADR4 lines is strobed into the register.

Fig. 8. Pulses for timing counter and distributor.

The four least significant bits in the M register are designated MAØ through MA3. These are applied to two 7442 IC's, IC1 and IC2. These decoder IC's look at the 4-bit address and cause one of the sixteen memory word select lines to go low. These output lines are labeled WØF through WFØ and are used to select one of the sixteen switch-diode matrix memory locations on the M3 circuit board. All of these output lines are high except for the selected one which is low. Notice that the MAØ through MA3 lines are also made available externally. These are used to address a word in the bipolar semiconductor memory as well.

#### THE M2 CIRCUIT BOARD

Refer to the large separate diagram for the M2 circuit board. You will need to refer to the diagram for the M1 circuit board as well while discussing the circuitry on the M2 board. The M2 board consists of two memory data multiplexers, IC9 and IC14. These are used to convert parallel data into serial data. Also on this board are the two bipolar semiconductor memory IC's. Each contains 64 flip-flops arranged as sixteen 4-bit words. Combining the two gives us a total of sixteen 8-bit words. Also on the M2 circuit board is the E register, an 8-bit shift register, IC11, and the associated circuitry. This register is used as an addressable memory location in those models of the 832 computer not containing the bipolar semiconductor memory. In those models that do contain the semiconductor memory, the E register is used as an auxiliary storage register that can be accessed by an RAE instruction.

The memory data multiplexer, 1C9, looks at the 8-bit parallel output of the switch-diode matrix memory. Whenever MA4 is a binary 0, this multiplexer is