## OB68K1A

MC68000 SINGLE BOARD COMPUTER USER'S MANUAL

### 0B68K1A

### MC68000 SINGLE BOARD COMPUTER

USFR'S MANUAL

The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, Omnibyte reserves the right to make changes to any products herein to improve reliability, function, or design. Omnibyte does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

The technical information contained herein is provided for reference, evaluation and repair purposes only and is copyrighted. It may not be copied or duplicated in part or in whole for any purpose without the express written permission of Omnibyte Corporation.

VERSAbug & MACSbug are trademarks of Motorola, Inc.

MULTIBUS is a trademark of Intel Corporation

OB68K1 & OB68K1A are trademarks of Omnibyte Corporation

### **TABLE OF CONTENTS**

|       | H                                    | <b>a</b> g | e     |

|-------|--------------------------------------|------------|-------|

| 1.0   | Introduction / Installation          | •          | 4     |

| 1.1   | Introduction                         |            | 4     |

| 1.2   | Unpacking Instructions               | •          | 4     |

| 1.3   | Inspection                           |            | 4     |

| 1.4   | Compatibility With Multibus Products |            | 4     |

| 1.5   | Factory Standard Configuration       |            | 5-6   |

| 2.0   | Overview of the Computer Board       |            | 7     |

| 2.1   | Summary of Features                  |            | 7     |

| 2.2   | Power Requirements                   |            | 7     |

| 3.0   | General Description of OB68K1A       |            | 9     |

| 3.1   | Serial Interface                     | . <b>.</b> | 9     |

| 3.2   | Timer                                |            | 9     |

| 3.3   | Parallel Interface                   |            | 9     |

| 3.4   | Bus Arbitration                      |            | 9     |

| 3.5   | On-board Memory                      | . <b>.</b> | 10    |

| 3.5.1 | On-board Read Only Memory            |            | 10    |

| 3.5.2 | On-board Dynamic RAM                 |            | 10-11 |

| 3.6   | Address Decoding and Memory Mapping  |            | 11    |

| 3.6.1 | ROM Address Selection (SW-3)         |            | 12    |

| 3.6.2 | RAM Address Selection (SW-1)         |            | 12    |

| 3.6.3 | I/O Base Address Selection (SW-2)    |            | 12    |

| 3.6.4 | External RAM Access Address (SW-4)   |            | 12-13 |

| 3.6.5 | Operational Considerations           |            | 13    |

| 3.6.6 | Undecoded Addresses                  |            | 13    |

| 3.7   | Transfer Acknowledge and Bus Errors  |            | 13-14 |

| 3.8   | Function Codes                       |            | 14    |

| 3.9   | Clocks                               |            | 14    |

| 3.9.1 | Processor Clock                      |            | 15    |

| 3.9.2 | Baud Rate Clock                      |            | 15    |

| 3.9.3 | Bus Clock and Constant Clock         |            | 15    |

| 3.9.4 | The E Clock                          |            | 15    |

| 3.10  | Interrupts                           |            | 15    |

| 3.11  | Status Indicators                    |            | 16    |

| 2 12  | Single-Step Mode                     |            | 16    |

| 3.13    | Restart Vector Accessing                     | 16    |

|---------|----------------------------------------------|-------|

| 3.14    | Front Panel Connector                        | 16    |

| 4.0     | User Definable Options                       | 17    |

| 4.1     | Serial Port Configuration (K25, K26)         | 19    |

| 4.1.1   | Transparent Mode (K10)                       | 19    |

| 4.1.2   | Baud Rate Selection (K18, K19)               | 21    |

| 4.1.2.1 | Manual Baud Rate Selection                   | 21    |

| 4.1.2.2 | Software Baud Rate Selection                 | 22    |

| 4.2     | Bus Error Jumper (K6)                        | 23    |

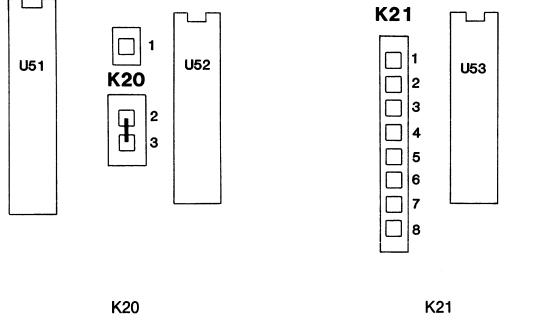

| 4.3     | DTACK Select (K20, K21)                      | 24    |

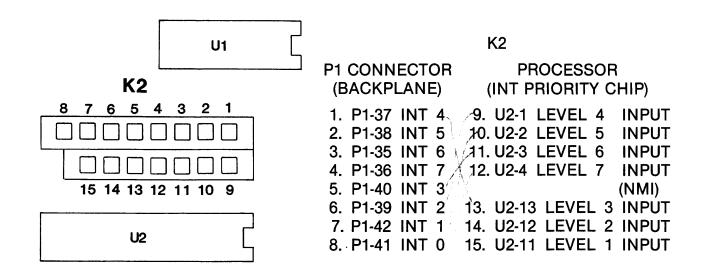

| 4.4     | Interrupt Priority (K2)                      | 26    |

| 4.5     | CCLK and BCLK (K14, K4)                      | 27    |

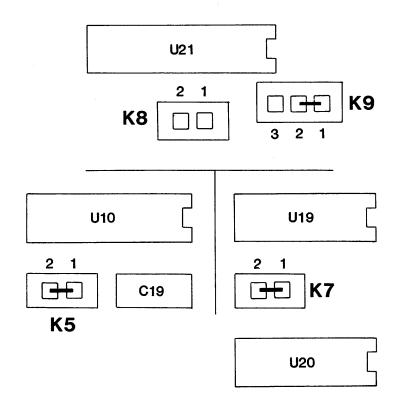

| 4.6     | Bus Arbitration (K5, K7, K8, K9)             | 27    |

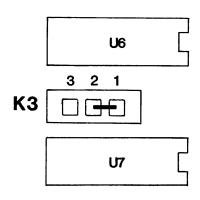

| 4.7     | Initialize (K3)                              | 29    |

| 4.8     | ROM Socket Configuration (K22)               | 29    |

| 4.8.1   | ROM Size Jumper Configuration                | 30    |

| 4.9     | Timer (K16, K17)                             | 33    |

| 4.10    | External RAM Access (K12, K27)               | 34    |

| 4.11    | Watchdog Timer for External RAM Access (K23) | 35    |

| 4.12    | Optional Front Panel (K1)                    | 35    |

| 4.13    | Miscellaneous Jumper Identification          | 37    |

| 4.14    | System Configuration                         | 42    |

| 5.0     | Connector Pinouts                            | 42    |

| 5.1     | Multibus P1 and P2 Connectors                | 42    |

| 5.2     | PIA and ACIA Connectors                      | 45    |

| 5.3     | Compatible Cable End Connectors              | 47    |

| 6.0     | Memory Decoding                              | 48    |

| 6.1     | Memory Maps                                  | 48    |

| 6.2     | I/O Address Assignments                      | 53    |

| 6.3     | Motorola MEX68KDM Compatibilty               | 55    |

| 6.4     | OB68K1/OB68K1A Compatibility/Enhancements    | 55-56 |

| 6.5     | 68000 Memory Organization                    | 56    |

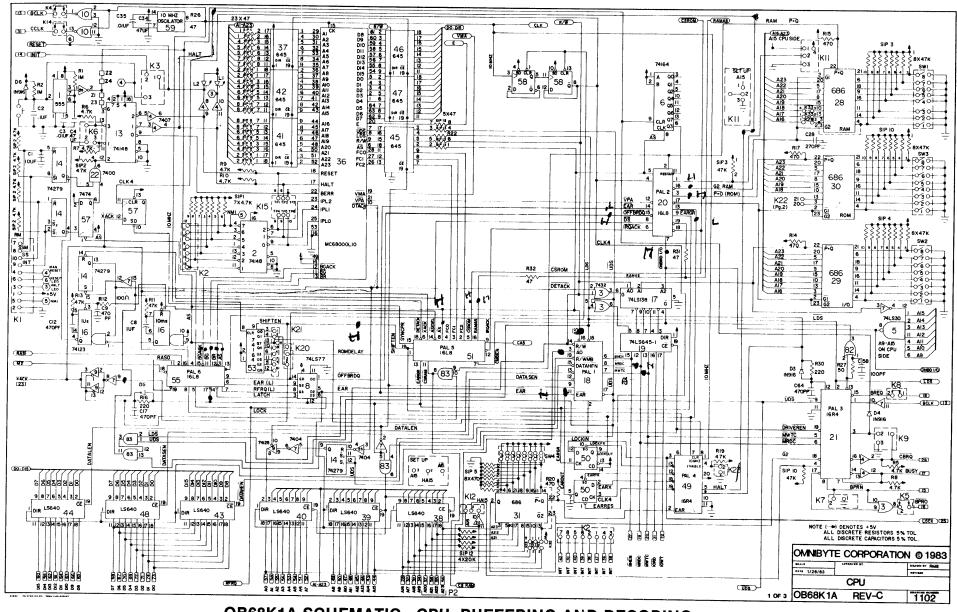

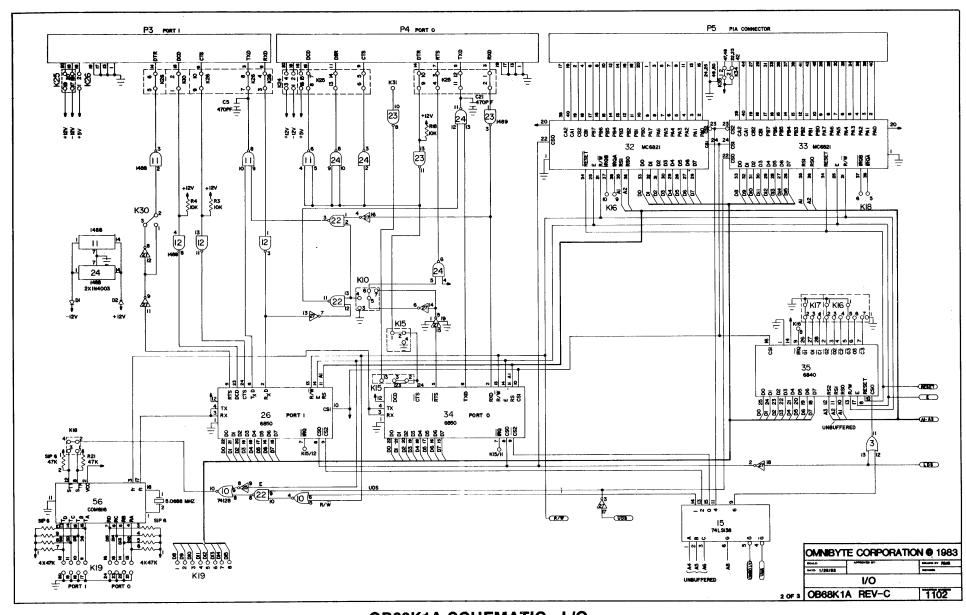

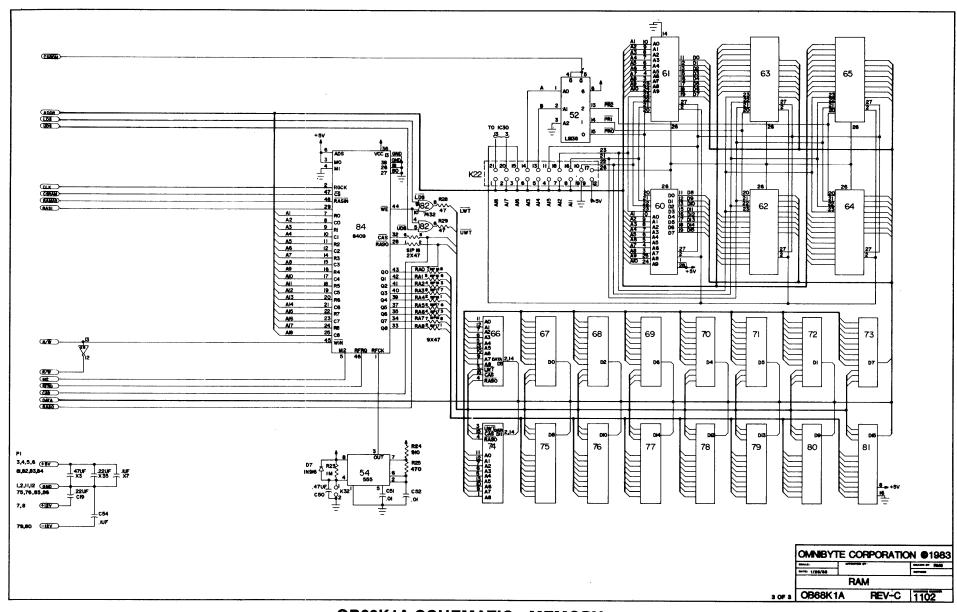

| 6.6     | OB68K1A Schematic Diagrams                   | 58    |

| 7.0     | Terminal Monitor Programs                    | 65    |

| 8.0     | Warranty Information                         | 66    |

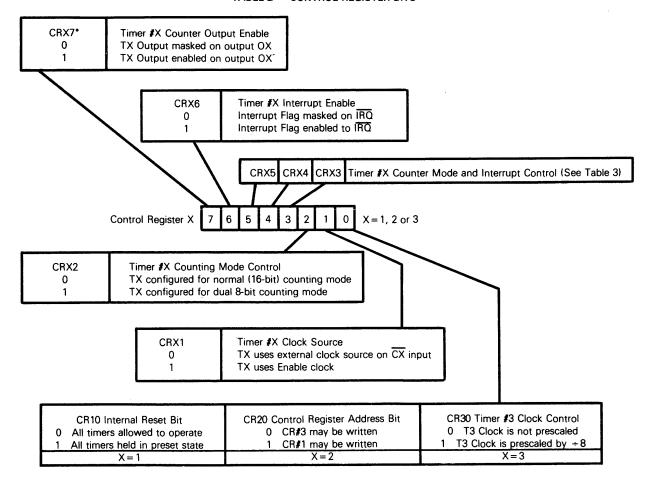

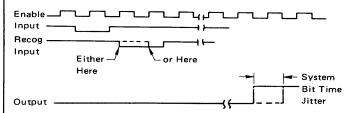

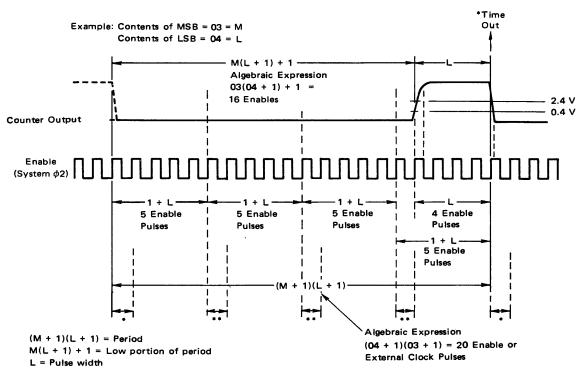

| 9.0     | Ordering Information                         | 67    |

| 10.0    | Appendix (DATA SHEETS)                       | 67    |

|         |                                              |       |

### LIST OF FIGURES AND TABLES

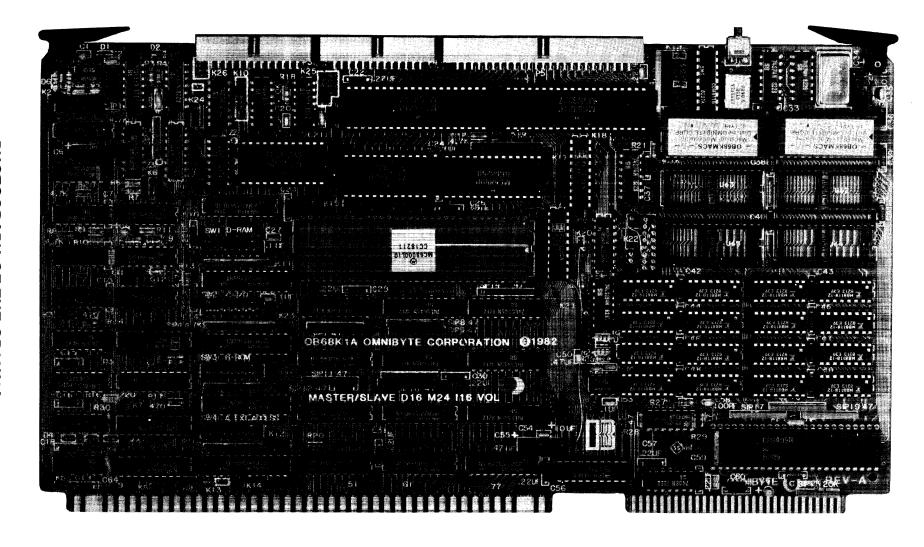

| Figure 1.0     | Photograph of the OB68K1A 1                     |

|----------------|-------------------------------------------------|

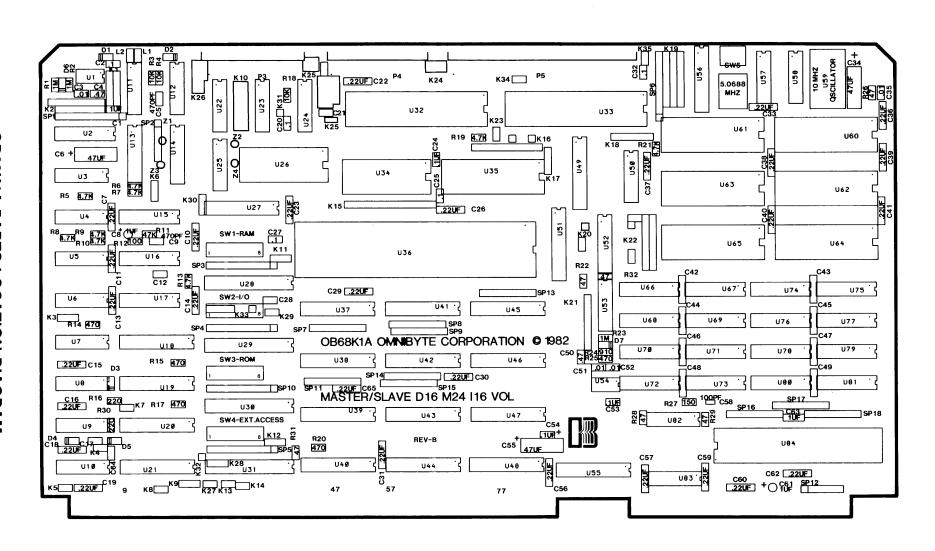

| Figure 1.1     | OB68K1A Parts Location Diagram 2                |

| Table 1.5      | Factory Jumper Configuration 5                  |

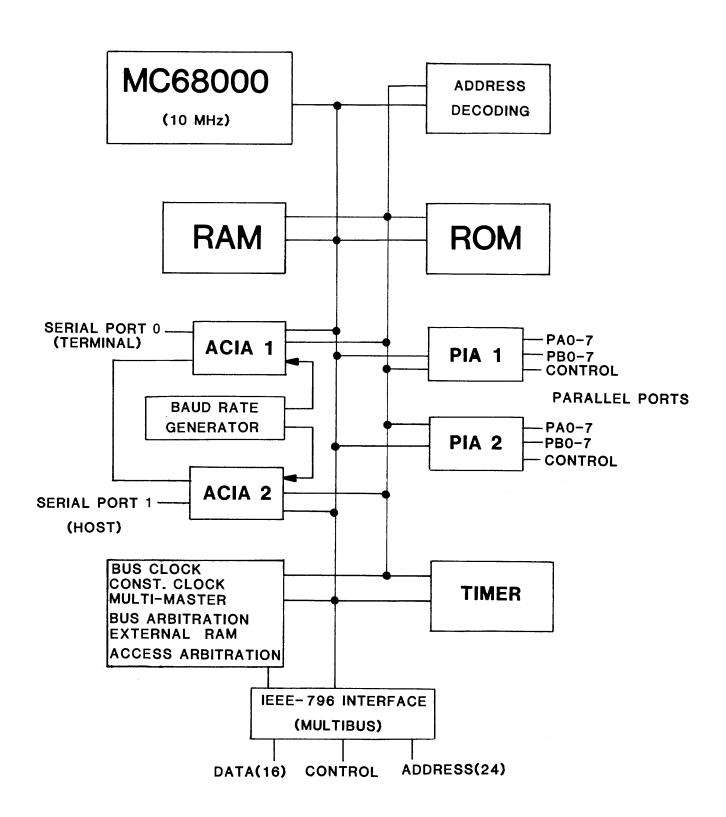

| Figure 2.0     | Block Diagram                                   |

| Table 4.0      | Jumper Options                                  |

| Figure 4.0     | Location of Jumper Options                      |

| Figure 4.1     | Serial Port Jumper Options                      |

| Figure 4.1.1   | Tranparent/Indep. Mode Jumper Location          |

| Figure 4.1.2   | Serial Port Baud Rate Jumpers                   |

| Table 4.1.2.1  | Baud Rate Selection                             |

| Table 4.3      | ROM DTACK delays                                |

| Figure 4.3     | ROM DTACK delay Jumpers                         |

| Figure 4.4     | Interrupt Jumpers                               |

| Figure 4.6     | Bus Arbitration Jumper Configuration            |

| Figure 4.7     | Reset Jumper Configuration                      |

| Figure 4.8.1   | ROM Size Jumper Configuration and Location      |

| Figure 4.8.2   | ROM Configuration Plug Layouts                  |

| Figure 4.8.3   | ROM Socket Configuration 32                     |

| Figure 4.8.4   | ROM Chip Pinout Configuration                   |

| Figure 4.9     | Timer Option Pin Identification and Location    |

| Figure 4.10    | External RAM Access Size Jumpers                |

| Figure 4.12(A) | Optional Front Panel - Connector                |

| Figure 4.12(B) | Optional Front Panel - Circuit                  |

| Figure 4.13    | Miscellaneous Jumper Locations                  |

| Table 5.1.1    | IEEE-796 P1 Connector Pinout                    |

| Table 5.1.2    | IEEE-796 P2 Connector Pinout                    |

| Table 5.2.1    | PIA Connector Pinout                            |

| Table 5.2.2    | ACIA Port 0 Connector Pinout                    |

| Table 5.2.3    | ACIA Port 1 Connector Pinout                    |

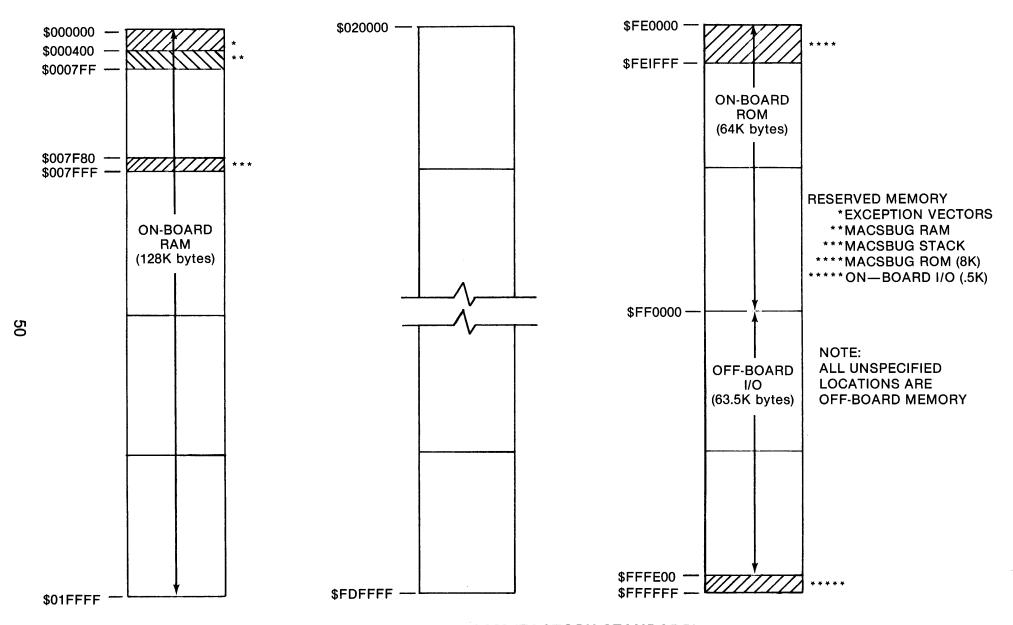

| Figure 6.1.1   | Memory Map (Factory Standard) 32K Version       |

| Figure 6.1.2   | Memory Map (Factory Standard) 128K Version 50   |

| Figure 6.1.3   | Memory Map Option (MAP 0) 32K Version 51        |

| Figure 6.1.4   | Memory Map Option (MAP 0) 128K Version          |

| Table 6.2      | Onboard I/O Address Assignments 54              |

| Figure 6.6(A)  | OB68K1A Schematic - CPU, Decoding and Buffers59 |

| Figure 6.6(B)  | OB68K1A Schematic - I/O                         |

| Figure 6.6(C)  | OB68K1A Schematic - Memory 61                   |

| Table 6.6      | OB68K1A Parts List 62-64                        |

|                |                                                 |

# OB68K1A PARTS LOCATION DIAGRAM FIGURE 1.1

### 1.0 INTRODUCTION / INSTALLATION

The OMNIBYTE OB68K1A 68000 Single Board Computer has been carefully designed to fulfill a variety of processing applications ranging from extremely small one board dedicated instruments to extremely large multi-processing systems utilizing several processor boards with shared memory and I/O. Figure 1.0 is a photograph of this board and Figure 1.1 is the parts location diagram.

### 1.1 Introduction

This chapter provides the unpacking, inspection and configuration instructions for the OB68K1A Single Board Computer.

### 1.2 Unpacking Instructions

IF THE SHIPPING CARTON IS DAMAGED UPON RECEIPT, REQUEST THAT CARRIER'S AGENT BE PRESENT WHILE THE ITEMS ARE BEING UNPACKED AND INSPECTED.

Unpack the OB68K1A Single Board Computer from its shipping carton. Save the packing material for storing and reshipping the items in case this becomes necessary.

### 1.3 Inspection

The OB68K1A Single Board Computer should be inspected upon receipt for broken, damaged, or missing parts, and for physical damage to the printed circuit board or connectors.

### 1.4 Compatibility with Multibus Products

The OB68K1A Single Board Computer has been carefully designed to meet the most current IEEE 796 bus specifications. It is advised that you become familiar with these specifications and how they compare with the original and current Multibus specifications. The OB68K1A implements full address and bus arbitration for single and multi-processor systems and has been designed for compatibility with existing Multibus products. Omnibyte assumes no liability for non-compatibility of certain products which do not meet published IEEE 796 specifications.

### 1.5 Factory Standard Configuration

The OB68K1A Single Board Computer may be used in several configurations. Prior to inserting the OB68K1A in a system, care should be taken to install the proper jumper options where necessary for your system configuration. Refer to Figure 4.0 for physical locations of these jumpers on the OB68K1A. Included below is factory standard configuration information.

The OB68K1A is shipped in a configuration that allows it to be operated in a single master system without modification. Factory standard jumper configurations are given in Table 1.5. All cut trace options are as shown on the OB68K1A electrical schematic (See Figure 6.6). Standard jumper connections are indicated by dashed lines on the schematic.

| JUMPER GROUP | CONFIGURATION    | FUNCTION                             |

|--------------|------------------|--------------------------------------|

| K3           | K3-1 TO K3-2     | INIT line driven by OB68K1A          |

| K4           | Installed        | BCLK driven by OB68K1A               |

| K5           | Installed        | Serial Prioritization Enabled        |

| K6           | K6-2 TO K6-3     | BERR enabled                         |

| K7           | Installed        | BPRN grounded                        |

| K8           | Removed          | BREQ for serial arbitration          |

| K9           | K9-2 TO K9-1     | CBRQ connected to Multibus           |

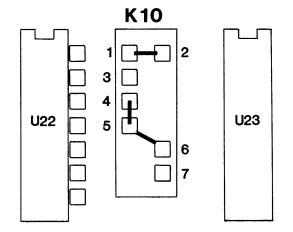

| K10          | K10-5 TO K10-6   | Normal RTS (Circuit Board Traces)    |

|              | K10-4 TO K10-5   | Serial Port transparent mode enabled |

| K11(32K)     | K11-1 TO K11-2   | Onboard RAM begins on 32K            |

| ,            |                  | boundaries (with K29 installed)      |

| K11(128K)    | K11-2 TO K11-3   | Onboard RAM begins on 128K           |

|              |                  | boundaries (with K29 removed)        |

| K12(32K)     | K12-2 TO K12-3   | External access RAM address begins   |

|              |                  | at 32K boundary (with K27 installed) |

| K12(128K)    | Removed          | External access RAM address begins   |

|              |                  | at 128K boundary (with K27 removed)  |

| K14          | Installed        | CCLK driven by OB68K1A               |

| K18          | Removed          | Hardware selected Baud Rate          |

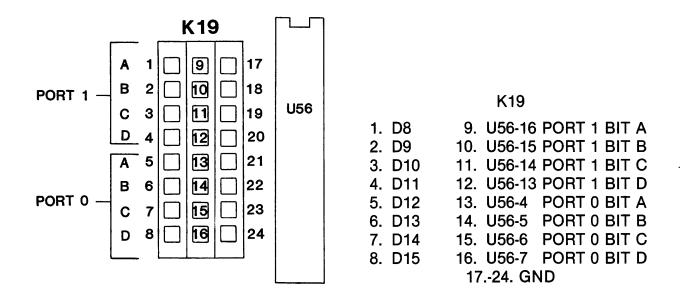

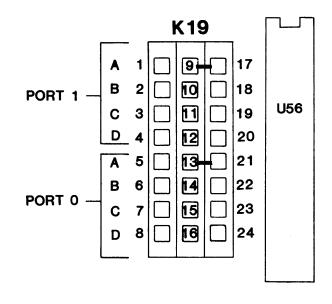

| K19          | K19-13 TO K19-21 | Serial Port 0 Baud rate set to 9600  |

| K19          | K19-9 TO K19-17  | Serial Port 1 Baud rate set to 9600  |

| K20          | K20-2 TO K20-3   | ROM DTACK set for 4 wait states      |

| K22          | Installed        | 2764 PROM type                       |

| K23          | Removed          | External access watchdog timer       |

|              |                  | enabled                              |

| K27(32K)     | Installed        | External Access RAM begins at        |

|              |                  | 64K boundary (with K12 removed)      |

| K27(128K)    | Removed          | External Access RAM begins at        |

| , ,          |                  | 128K boundary (with K12 removed)     |

| K29(32K)     | Installed        | Onboard RAM begins at 64K            |

|              |                  | boundary (with K11 removed)          |

| K29(128K)    | Removed          | Onboard RAM begins at 128K           |

|              |                  | boundary (with K11 removed)          |

| L            | L                |                                      |

FACTORY STANDARD JUMPER CONFIGURATION TABLE 1.5

The OB68K1A is configured at the factory to operate in the following way;

### a) BUS

The Bus Clock (BCLK), Constant Clock (CCLK) and Reset line (INIT) are driven off the board. On-board power-on reset enabled and the bus error jumper (K6) is installed so that bus error exception processing will be executed, if a bus error is encountered.

### b) INTERRUPTS

No interrupts are connected.

### c) RAM

On-board RAM begins at \$00000 (HEX). Contiguous RAM continues to \$007FFF (HEX) in the 32K version and to \$01FFFF (HEX) in the 128K version.

### d) ROM

All on-board ROM sockets are configured for 2764-type (8Kx8) 5 volt only EPROM and the memory map is configured to MAP 1 (for 2764). ROM address begins at \$FEOOOO (HEX) and continues to \$FEFFFF (HEX). The ROM DTACK is factory preset for 350 ns (access time) ROM chips.

### e) ON-BOARD SERIAL I/O PORTS

On-board I/O begins at address \$FFFEOO (HEX). See table 6.2 for specific device address assignments. Serial Port 0 is configured as a modem for direct connection to a RS232C terminal. Serial Port 1 is configured as a terminal for direct connection to a RS232C modem or another computer. The baud rates are set to 9600 BPS at the factory for testing.

### f) OFF-BOARD I/O

Off-board I/O begins at address \$FFOOOO (HEX) and continues to \$FFFDFF.

### g) TRANSPARENT MODE

Transparent mode is enabled.

Please note that the above is the configuration of the OB68K1A as shipped from the factory and it does not include setting-up the board in a different configuration if desired before power-up. A detailed list of the factory installed jumper configurations is given in Table 1.5. Factory standard configuration is compatible with Omnibyte's optional PROM based terminal monitor routines that provide the functionality of Motorola's MACSbug/VERSAbug/VMEbug/TUTOR programs.

### 2.0 OVERVIEW OF THE COMPUTER BOARD

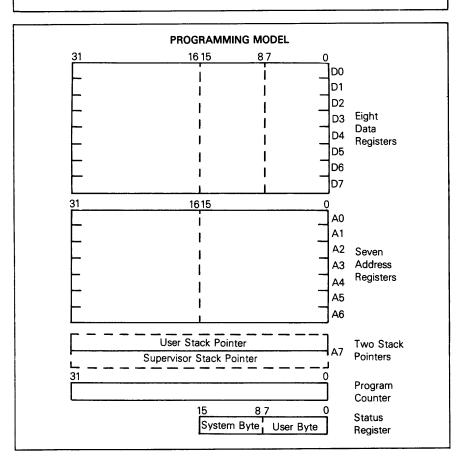

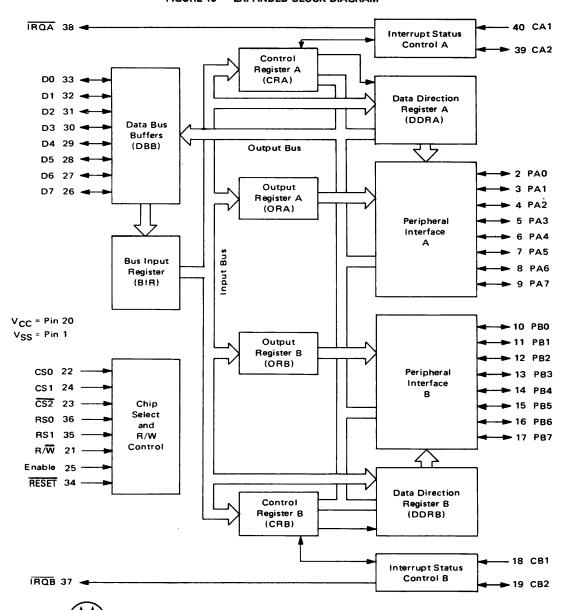

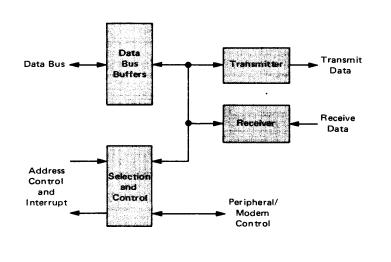

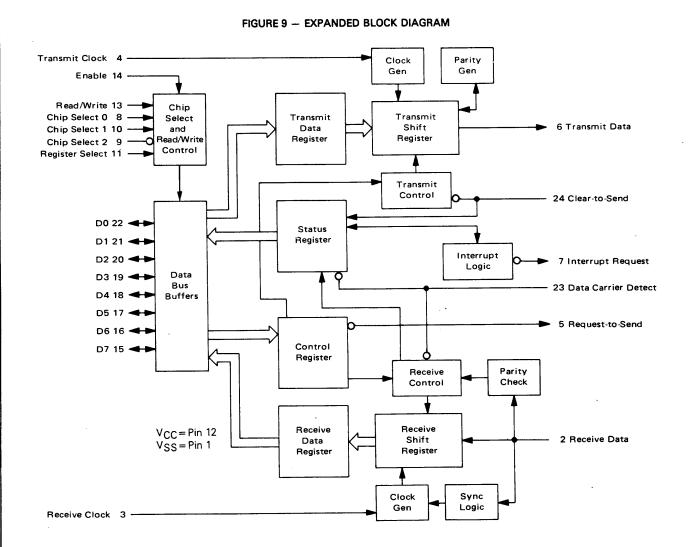

This section describes the major features of the OB68K1A. A block diagram of this single board computer is shown in Figure 2.0.

### 2.1 Summary of Features

The OB68K1A computer board provides the following features:

- a. 10MHz processor & clock

- b. IEEE 796 (Multibus) Compatible (MASTER D16 M24 I16 VOL/SLAVE M24 D16)

- c. Single step circuitry

- d. Dual Ported on-board RAM (32K byte or 128K byte)

- e. Zero wait states for on-board RAM accesses

- f. LSI Hardware memory refresh circuit

- g. On-board ROM (up to 192K bytes)

- h. Two asynchronous serial ports (RS232C)

- i. Hardware or software programmable baud rate generator

- j. Two programmable 16-bit parallel I/O ports

- k. Three 16-bit programmable timers

- I. 16 Megabyte (24-bit) direct memory addressing

- m. Independently Switch Selectable RAM, ROM, EXT. RAM ACCESS, and I/O base addresses

- n. Multi-Master bus arbitration

- o. Motorola MEX68KDM software compatibility

### 2.2 Power Requirements

The computer receives its power through the Multibus motherboard. Typical power requirements are as follows:

32K VERSION 128 K VERSION

|                   | •=      |         |

|-------------------|---------|---------|

| +5V — ± 5%        | @ 3.0A  | @ 3.25A |

| $+ 12V - \pm 5\%$ | @ 0.05A | @ 0.05A |

| $-12V - \pm 5\%$  | @ 0.05A | @ 0.05A |

Note: Single 5 volt operation is possible with the OB68K1A if the RS232C ports are not used.

### 3.0 GENERAL DESCRIPTION OF OB68K1A

The OB68K1A is designed to be both simple and flexible to use. Only general purpose memory and I/O are included on the board. Special purpose facilities such as disk controllers can be added as additional Multibus boards to configure larger systems.

### 3.1 Serial Interface

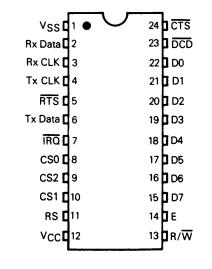

The two asynchronous serial ports are implemented using MC6850 Asynchronous Communication Interface Adapter (ACIA) chips. The baud rates are individually selectable for standard frequencies between 50 and 19,200 baud. The baud rate selection for each port may be determined either by hardware jumpers or by software setting. Both ports are factory configured to transmit and receive without handshake lines although jumper options are provided for the normal CTS, RTS, and DCD interface signals. All signals are received and transmitted through RS232C compatible buffers. The interface is made through individual, standard 26 pin header connectors.

### 3.2 Timer

A three channel 16-bit timer (MC6840) is available on the board. This timer is intended primarily for processor housekeeping. No connector is provided for input or output signals to or from the timer — the clock, gate and output pins for each timer are terminated on wire wrap posts near the chip. For normal applications the timer counts the processor "E" clock, a 1 MHz signal generated by the 68000.

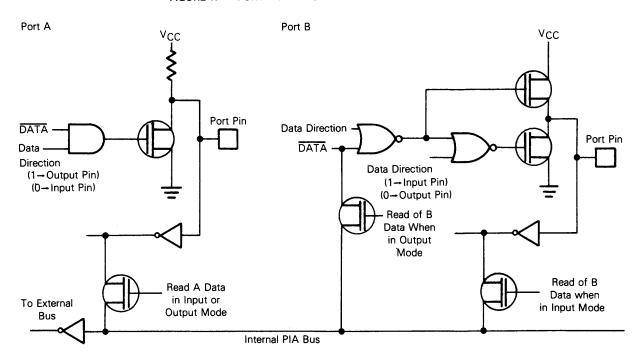

### 3.3 Parallel Interface

Two MC6821 Peripheral Interface Adapters (PIA) are provided on the OB68K1A. All the interface lines are brought out on a standard 50 pin header connector. Five volt power is also brought to this connector. The two 8-bit PIA's are configured to straddle the 16-bit data bus so that 16-bit data may be transferred using the A ports or B ports of both PIA's. Byte operations are supported on both PIA's.

### 3.4 Bus Arbitration

The bus arbitration circuit allows this computer to share the Multibus with other processors or master controllers. RAM memory that resides on this board may be made available to other masters on the Multibus. The address of the Multibus port of the onboard RAM is independently selected.

### 3.5 On-Board Memory

### 3.5.1 On-Board Read Only Memory

The six memory sockets contained on the board are organized as three pairs of byte-wide memories. A minimum of 64K bytes of memory space is always allocated for on-board ROM. However, for ROMs of less than 64K bits each, the total ROM memory space will not be utilized. *Only EPROM's that are pin compatible with the pinout shown in Figure 4.8.4 can be utilized on the OB68K1A.* Some compatible memories are 2716, 2732, 2764, 27128 and 27256 5 volt only, 24/28 pin EPROM's containing 2K, 4K, 8K, 16K and 32 K bytes respectively. Each socket pair is selected with its base address and range within the allocated space arranged so that the PROM sockets form a contiguous block of memory. All three socket pairs occupy the same amount of memory. A small prewired PC plug is inserted in the location provided to configure the board for various sizes of ROM memories. Note that 28-PIN sockets are used for all ROMs to allow for a larger base of usable ROM chips. The base address of the ROM is selected as a single memory block using switch SW-3. Note that although various ROM sizes can be accommodated, all ROM sockets are configured for the same ROM size. Also see section 3.6.1.

### 3.5.2 On-Board Dynamic RAM

The OB68K1A has sixteen dynamic RAM chips. If configured for 16Kx1 parts, a total of 32K bytes are available. If configured for 64Kx1 parts, a total of 128K bytes are available. The board is offered with either the 16K or 64K parts. The RAM is selected as a block by the main address decoding circuit and may be addressed either in the byte or word mode.

The on-board dynamic RAM chips are accessed and refreshed using an LSI DRAM controller, the DP8409. This 48-pin bipolar circuit generates the Row Address Strobes (RAS), Column Address Strobes (CAS), drives the multiplexed address lines, and performs the necessary refresh cycles. Under normal operation the RAM controller receives the processor address strobes and becomes selected when the asserted address falls within the RAM memory space. A 555 clock generates a 15 us pulse train to provide the basic refresh timing. The controller monitors both the Address Strobe and its Chip Select inputs. When a refresh cycle is needed the controller waits for an Address Strobe to occur with no Chip Select — an indication that the processor is accessing other memory or I/O. The controller will then perform a "hidden" refresh cycle, that is, a refresh cycle that does not take time away from the processor. If, during the 15 us period of the refresh clock, the RAM is accessed on all Address Strobes, the controller will request the use of the bus, cause the processor to relinquish the bus and the RAM controller will then perform a forced refresh cycle.

The duration of forced refresh cycle is about 500 ns. Under most conditions the refresh overhead of the OB68K1A will be very low. Note that because the entire RAM refresh task is implemented in hardware no processor code-execution cycles are wasted to perform RAM refresh by software.

When the processor performs a Multibus cycle, the duration of the cycle will depend on the availability of the bus and the response time of the addressed device. During these offboard cycles, no address strobes are applied to the RAM controller and forced refreshes are then implemented when needed. The XACK signal output by the OB68K1A signals the external master that data from the onboard RAM has been placed on the Multibus or the data to be written has been stored. Shortly thereafter the external master should terminate the cycle by removing the read or write command. If the cycle is not terminated after several microseconds, data in the dynamic RAM could be lost. A timeout circuit is included on the OB68K1A that interrupts the external access so a refresh can occur. The offboard master is not required to wait for the completion of an instruction. The LOCK feature of Multibus is implemented so an offboard master may do a test-and-set operation to the onboard RAM. Also see sections 3.6.2 and 3.6.4.

### 3.6 Address Decoding and Memory Mapping

The OB68K1A has been designed so that the memory mapping is switch selectable by the user. No fusible link devices are needed to change the memory map. Four separate address decoders are included on the board to individually select the base address of onboard RAM, onboard ROM, I/O and the Multibus access to the onboard RAM. For each of these four blocks, the base address is selected by the setting of an 8-bit DIP switch. The dip switches have been socketed so that dip jumpers can be used to fix addressing for production purposes, these dip jumpers are available through OMNIBYTE. See section 9.0 for ordering information. The switch setting is compared with the upper address lines to determine when the various blocks are being selected (SWITCH BIT 1 = L.S.B., SWITCH BIT 0 = M.S.B.; ON = 0, OFF = 1). Much of the random logic associated with address decoding and strobe timing has been consolidated into Programmable Array Logic (PAL)\* chips. These circuits are programmed at the factory and cannot be changed by the user.

<sup>\*</sup> PAL is a trademark of Monolithic Memories, Inc.

### 3.6.1 ROM Address Selection (SW-3)

The 8-bit DIP switch (SW-3) is used to select the base address of the onboard ROM. Address lines A16-23 are compared with the switch setting resulting in a minimum ROM block size of 64K bytes. The minimum block size will accommodate memories through 8K bytes per chip. For larger ROM chips, larger memory block sizes of 128K and 256K bytes may be selected by removing A16 and A17 from the comparator inputs, respectively. All the necessary connections are made by inserting pre-wired plugs in the location provided. Various jumper models are available from the factory. Note that within the ROM block, there are addresses for which no memory exists. For example, using 8K byte PROMs, the six sockets provided will occupy 48K of the minimum 64K byte block size. The remainder of this block is not accessable and cannot be assigned to other memory or devices.

### 3.6.2 RAM Address Selection (SW-1)

The 8-bit DIP switch (SW-1) is used to select the base address of the onboard RAM. Jumpers and cut traces at A15 and A16 are factory configured for either 32K or 128K RAM. For 32K RAM switch SW-1 selects base addresses on the lower 32K block of 64K byte boundary. For 128K RAM switch (SW-1) selects base address on 128K byte blocks. For 128K RAM, BIT 1 of SW-1 is a "don't care" bit, since pins 13 and 14 on U28 are tied together and the cut trace option at A16 is opened.

### 3.6.3 I/O Base Address Selection (SW-2)

Because the 68000 accesses I/O the same as memory, a 64K byte block of memory space is decoded and assigned to the I/O space defined in the IEEE 796 bus specification. No options exist on the board to change the size of the I/O address space, but the base address may be located at any 64K byte boundary within the available 16 megabyte address range. The onboard I/O devices occupy the uppermost 512 bytes of the I/O space; all other addresses within the block default to offboard I/O. Table 6.2 gives the addresses of the onboard I/O devices.

### 3.6.4 EXTERNAL RAM Access Address (SW-4)

A separate 8-bit DIP switch and comparator are used to determine the base address of the onboard RAM when that RAM is accessed by another Multibus master. The RAM is then accessed at independently selected addresses chosen to satisfy requirements of both the offboard master and the OB68K1A. Address line A15 can be used to gate the comparator in order to decode a 32K byte block size and jumper options allow the block size to be increased. Notice that it is possible to limit the amount of memory that can be accessed from offboard.

A 128K byte OB68K1A may allow offboard masters to access 32K, 64K or all 128K bytes of its onboard RAM. This feature allows portions of the onboard RAM to be protected from other offboard masters. Although limiting blocks of RAM from offboard access is possible, this option has not been implemented by the factory and should be selected by the user if desired. Also note that in addition to the jumper and cut trace option on A16, pins 13 and 14 on U31 have been jumpered and bit 1 of SW-4 is a "don't care" bit. (See Section 3.6.2).

### 3.6.5 Operational Considerations

When the user is setting the base address switches of the OB68K1A care must be exercised to avoid overlap of the onboard memory spaces of RAM ROM, and I/O. The offboard access to the dual-ported RAM may arbitrarily overlap any or all of the onboard RAM, ROM, or I/O space.

In systems that use multiple OB68K1A computers, the onboard base address selections may be the same for all boards.

The external access to the OB68K1A dual-ported RAM appears as a simple RAM board to an external Multibus Master. Therefore, the base address of the external access (SW 4) must be selected to avoid overlap of the dual-ported memory space with any other memory space on the Multibus. External access spaces of Multiple OB68K1A boards must not overlap. The OB68K1A is protected from accessing its own RAM via the Multibus by negating onboard access while performing offboard accesses.

### 3.6.6 Undecoded Addresses

The OB68K1A is designed so that all memory accesses default to offboard Multibus accesses unless the address that is asserted falls within the onboard RAM, ROM or onboard I/O space.

### 3.7 Transfer Acknowledge and Bus Errors

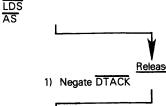

The 68000's data transfers are asynchronous — A Data Transfer ACKnowledge (DTACK) signal is required to complete an access. For Multibus cycles this signal is provided naturally by the Multibus Transfer ACKnowledge (XACK). For onboard ROM cycles, a DTACK generator is provided to terminate the cycle a fixed time after an on-board memory access is started. The delay time is selectable to match the access time of the on-board ROM memory chips. (See Section 4.3).

The DTACK signal for onboard RAM access cycles is also provided by the ROM DTACK generator and has also been optimzed for the RAM. The OB68K1A must generate an XACK signal when other Multibus masters access the onboard RAM. This signal serves to terminate the bus cycle for the offboard master. A tap on the ROM DTACK generator is used to generate this signal at a delayed time that has been optimized for the offboard RAM access time and no user adjustment is permitted.

When the OB68K1A accesses external Multibus memory or I/O, the cycle is terminated by the XACK signal returned by the board that was addressed.

In the event that unimplemented off-board memory is accessed, no DTACK will be generated. An on-board "watchdog" timer is included to detect a lack of response, and a pulse is generated that may be jumpered to the 68000 Bus Error input pin. A signal asserted on this pin will initiate bus error exception processing and a user-supplied routine is executed to allow the system to analyze the report or recover from this condition.

Notice that the 68000 itself will patiently wait forever, if desired, for a DTACK response to come. No restriction is placed on the speed of response of the addressed memory or device. The watchdog timer delay is user determined and its implementation is optional. It is included to keep the system from hanging up if no response is received.

Conditions that will cause a bus error are:

- a) Access to off-board memory addresses that have no responding memory (not plugged in, or not working).

- b) Access to off-board I/O addresses that have no responsing device (not plugged in, or not working).

An access to an on-board memory address will not cause a bus error even if a memory chip is not installed. On-board I/O uses the 68000 synchronous transfer capability and no DTACK is required.

### 3.8 Function Codes

The 68000 processor outputs three function code bits, FC0, FC1, and FC2 that allow external circuitry to know the internal operating mode of the processor. The state of these outputs indicates whether the processor is in the supervisor or user state, whether the present access is a program or data reference, or if the processor is responding to an interrupt. The standard configuration of the OB68K1A makes use of various function code values only to recognize interrupt acknowledge cycles.

### 3.9 Clocks

Four clocks are generated on-board.

### 3.9.1 Processor Clock

A 10 MHz crystal oscillator provides the processor clock. It connects directly to the 68000 clock input pin. The 10 MHz clock is also used as the time base for the DTACK generator.

### 3.9.2 Baud Rate Clock

A 5.0688 MHz crystal and a COM8116 comprise the baud rate generator. This baud rate selection can be done by setting four jumpers for each serial port, or by storing the baud rate setting in the COM8116 chip under software control. These jumper options allow the processor to dynamically control the baud rate of either one or both serial ports.

### 3.9.3 Bus Clock and Constant Clock

The 10 MHz processor clock may be used as the Multibus BCLK and CCLK. Because **only one card in a Multibus system can assert these signals**, jumpers are provided to remove these clocks from the bus. With these jumpers removed, the card uses the BCLK and CCLK generated by another master in the Multibus bin.

### 3.9.4 The E Clock

The 68000 outputs an E clock that is one-tenth the processor clock frequency. Synchronous transfers to the on-board Motorola peripherals are made using this 1MHz clock. Accordingly, it is connected to the enable input of the PIA, ACIA and timer chips. This frequency is used by the timer chip when it is configured to count the E clock.

### 3.10 Interrupts

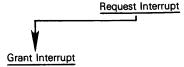

The 68000 provides for seven levels of prioritized auto-vectored interrupts. A 74148 priority encoder is included for inputting low active interrupts. The output of the 74148 directly connects to the IPL0, IPL1, IPL2 inputs of the processor. Interrupts outputs from the on-board peripherals and the Multibus interrupt lines must be connected to the priority encoder by the user. Wire wrap pins are provided for each interrupt source.

The 68000 feature of reading an interrupt vector number from the interrupting device has not been implemented on this board.

### 3.11 Status Indicators

Two LED indicator lights are included to show when the processor is in the reset mode (YELLOW) and when the processor is halted (RED).

### 312 Single-Step Mode

Circuitry is included on the OB68K1A to implement single step and halt operations. These functions are activated by an external momentary contact switch (for single stepping the processor) and an SPST switch to select the Single Step or Run mode. A 10-pin header on the board may be used to connect these switches. Additional signals included on this header are a Reset input, a Non-Maskable Interrupt input and connections to LED drivers for Halt and Reset indicators. This group of signals may be connected to a front panel if desired.

### 3.13 Restart Vector Accessing

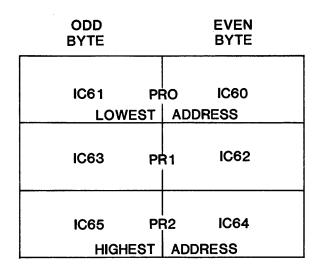

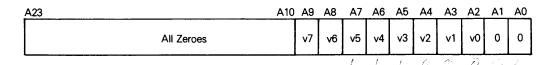

When a power-on or manual reset of the procesor occurs, the processor begins operation by accessing memory location zero in Supervisory Program space to load the restart vector and the Supervisor stack pointer. These two vectors must be stored in PROM because the contents of RAM are unknown at restart time. The OB68K1A causes the first four memory accesses following a restart to be unconditionally directed to the location 0 through 7 of the first ROM socket pair (IC60 and IC61). The access to these PROM locations is independent of the switch-selected location of ROM in the address map of the OB68K1A. For proper operation, after restart some memory must exist at location \$000000 in order to have memory at the addresses where the processor expects to find exception vectors. This may be either RAM or PROM and, can be in offboard memory. In any case, ROM chips must be present in the first two ROM sockets, to supply the initial program counter and stack pointer values at restart.

### 3.14 Front Panel Connector

The OB68K1A has a provision for connecting a front panel board that includes RESET, SINGLE-STEP, and RUN-STOP switches, HALT and RESET LEDS and a Software Abort button that asserts NMI, the level 7 interrupt. An optional front panel box and interconnecting cable is available. See Section 9.0 for ordering information.

### **4.0 USER DEFINABLE OPTIONS**

This section describes the jumpers and options included on the board. Table 4.0 is a summary of all the user definable jumpers. The location of the jumpers are shown in Figure 4.0.

| ILIMPER NO    | NO. OF PINS                     | FUNCTION                                         |

|---------------|---------------------------------|--------------------------------------------------|

| JOINT LIT NO. | 110. 01 11110                   | 1 011011011                                      |

| K1            | 10                              | Front Panel Connector                            |

| K2            | 10<br>15                        |                                                  |

| 1             |                                 | Interrupt Jumpers                                |

| K3            | S o                             | INIT Jumpers<br>BCLK to Multibus                 |

| K4            | 2                               |                                                  |

| K5            | 3<br>2<br>3<br>2<br>2<br>3<br>7 | BPRO to Multibus                                 |

| K6            | 3                               | BERR Enable                                      |

| K7            | 2                               | BPRN Enable                                      |

| K8            | 2                               | BREQ for parallel Arbitration                    |

| K9            | 3                               | CBRQ Enable/Disable                              |

| K10           | 7                               | Serial Port Transparent/Independent Mode         |

|               |                                 | Enable                                           |

| K11           | 3<br>3<br>2<br>2                | Onboard RAM Size Select                          |

| K12           | 3                               | Ext. RAM access, Upper/Lower 32K select          |

| K13           | 2                               | Future RAM Enhancement                           |

| K14           |                                 | CCLK to Multibus                                 |

| K15           | 13                              | ACIA IRQ, Handshake Configuration; Test points   |

| K16           | 10                              | Timer 2 & 3, CLK, Gate, Output; Timer IRQ, PIA 0 |

|               |                                 | IRQ's                                            |

| K17           | 4                               | Timer 1; CLK, gate, output                       |

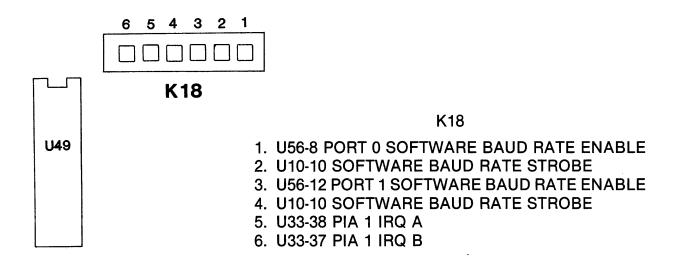

| K18           | 6                               | SW Baud Rate strobe; PIA 1, IRQ                  |

| K19           | 24                              | Hardware/Software Baud Rate Jumpers              |

| K20           | 3                               | ROM Delay (Jumper to K21)                        |

| K21           | 8                               | ROM DTACK Delay Select 100ns/tap                 |

| K22           | 21                              | Rom Socket Sizing                                |

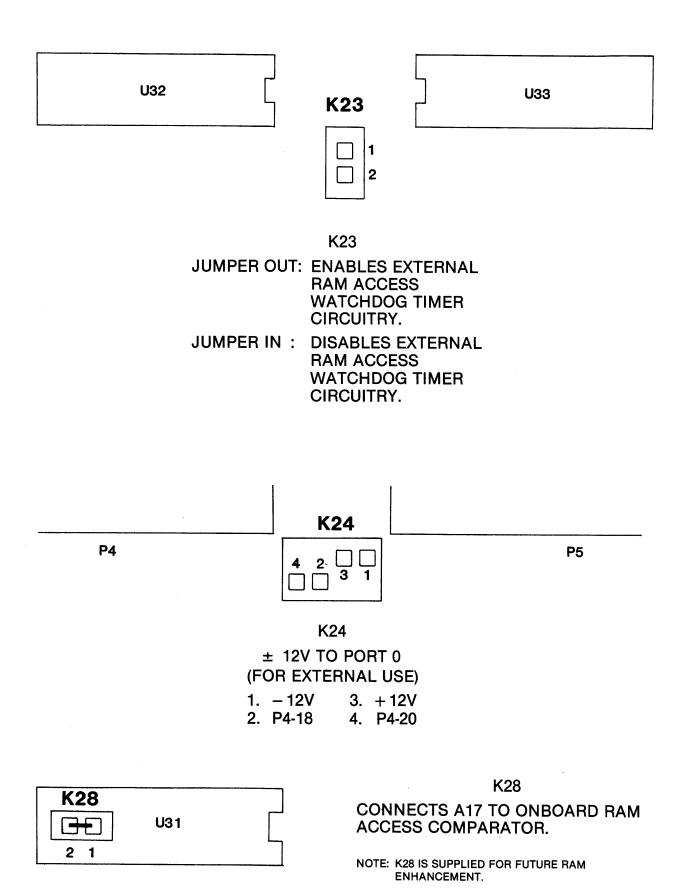

| K23           | 2                               | External access watchdog timer enable            |

| K24           | 4                               | ± 12V TO Port 0 (For External Circuitry)         |

| K25           | 20                              | Port 0 ACIA Configuration                        |

| K26           | 10                              | Port 1 ACIA Configuration                        |

| K27           | 2                               | A16 64/128K EXT. RAM Access Limit                |

| K28           | 2                               | Future RAM Enhancement                           |

| K29           | 2                               | A16 Onboard RAM Size                             |

| K30           | 3                               | DTR Normal/Invert (Port 1)                       |

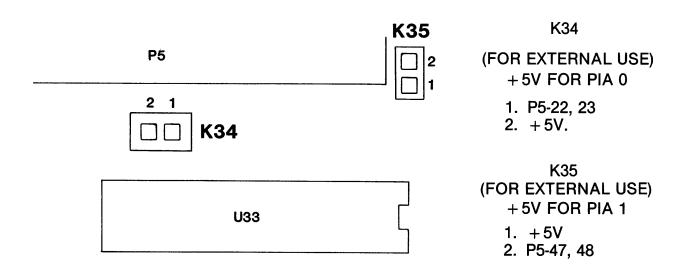

| K31           | 1                               | Spare RS232 Receiver Buffer Output               |

| K33           | 4                               | Future RAM Enhancement                           |

| K34           | 2                               | 5V for PIA 0                                     |

| K35           | 2                               | 5V for PIA 1                                     |

|               |                                 |                                                  |

JUMPER OPTIONS TABLE 4.0

### + C34 10 MHZ U59 OSCILLATOR US6 .22UF C22 P4 US8 K34 P5 K24 5.0688 470PF C5 □ MHZ U23 **U22** U32 U33 U24 U61 R21 12 950 R19 4.7K U60 K 18 U26 ٥<u>\*</u> U35 U34 LK17 U3 U63 U62 U27 .22UF C26 U15 · 2 150 R8 R9 8.78 8.78 R10 8.78 C27 .1 K11 U\$2 K22 U65 U64 U36 U5 R22 \_\_\_ C12 C43 47 47 U28 U66 U67' C29 .22UF U74 U75 ]SP13 SW2-1/0 U17 · c \_\_\_C28 K21 U41 - 5 U37 U45 R14 470 U68 OB68K1A OMNIBYTE CORPORATION © 1982 U69 U76 U77 C47 U7 U18 U29 U79 U71 U78 C50 SW3-ROM U42 U46 R15 470 \_22UF C15 D3 C49 C48 SP14 \_\_\_\_\_\_C30 UBB U01 U72 U73 \_\_\_SP10 R27 150 100PF C58 SP17 (1UE) C53 K7 R17 470 U3**0** 3645 10F U43 U47 SP18 SW4-EXT.ACCESS U82 U9 U2**0** K12 🖫 108+ R20 470 REV-B C55 U84 250 250 250 C57 C59 U4**Ø** U44 U48 **U55** C62 \_22UF 57 ne2.ι .22UF C 19 47 77

# OB68K1A LOCATION OF JUMPER OPTIONS FIGURE 4.0

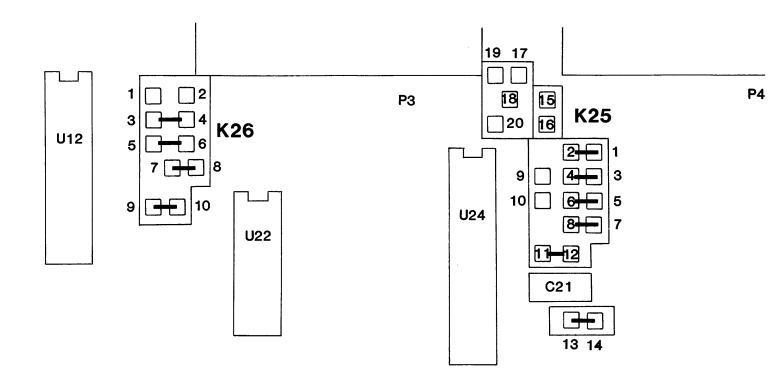

### 4.1 Serial Port Configuration (K25, K26)

The serial I/O is implemented using (2) MC6850 ACIA chips. When these are connected using ribbon cable and compatible 26 pin Berg type headers and 25 pin "D" connectors, the pinout of the "D" connector for port 0 is the same as an RS232C modem. The pinout for port 1 is the same as an RS232C terminal. That is, port 0 will plug directly onto an RS232C terminal and port 1 will plug directly onto an RS232C modem or host computer. The pinouts of these connectors are shown in Section 5.

Port 0 ACIA has both CTS and DCD tied together and connected via an RS232C buffer to DTR on the connector. A pull up resistor is provided to automatically enable the ACIA if DTR is not driven by the terminal used. Cut trace options are provided to allow the user to reconfigure the port and implement handshaking if desired.

Port 1 ACIA has handshaking implemented with CTS and DCD. Both of these signals are provided with pull up resistors to enable the ACIA if CTS and/or DCD are not driven by the device being used. Cut trace options are provided to allow the user to reconfigure the port. See Figure 4.1 for the location of these points.

Both ports have jumper options to provide +5V, +12V and -12V power to the user's device. This could be used to provide power for an in-line RS232C to 20MA current loop converter. The factory configuration of Ports 0 and 1 are identical to the Motorola MEX68KDM design module's serial ports including the implementation of the "Transparent" mode of operation. TX and RX clock are connected together on each ACIA. Each port has independent baud rate selection.

### 4.1.1 Transparent Mode (K10)

The transparent mode enables communication between the devices connected to the two serial ports, such that the board appears "transparent" and for all practical purposes is not in the circuit. The transparent mode is enabled by a command in the terminal monitor program, MACbug or VERSAbug via the RTS output of the Port 0 ACIA. For successful operation of this mode, the user should take note of several points. The device connected to Port 0 must be data terminal equipment (DTE), factory configured for an RS232 terminal; the device connected to Port 1 must be data communication equipment (DCE), factory configured for an RS232 modem or host. The devices connected to the ports must have the same baud rate. Jumpers at jumper group K10 enables/disables the transparent mode, the factory configuration is K10-4 to K10-5 transparent mode enabled. If the user should want to reconfigure the serial ports, the transparent mode may be an undesirable mode in which to run, therefore, jumper option K10-3 to K10-4 has been provided to disable the transparent mode and configures the serial ports for independent operation.

### K26 **PORT 1 JUMPERS**

- 1. +5V

- 6. P3-14(DTR)

- 2. P3-16

- 7. U11-8

- 3. U12-1

- 8. P3-3 (TXD)

- 4. P3-5(RXD)

- 9. U12-13

- 5. U11-3

- 10. P3-9 (CTS)

Note: P3 is PORT 1 Connector

### K25 PORT 0 JUMPERS

- 1. P4-3(RXD)

- 11. U24-11

- 2. U23-1

- 12. P4-5 (TXD)

- 3. P4-7 (RTS)

- 13. U24-8

- 4. U24-6

- 14. P4-11 (DSR)

- 5. P4-9 (CTS)

- 15. P4-16

- 6. U24-3

- 16. +5V

- 7. P4-15 (DCD)

- 17. 12V

- 8. U11-6

- 18. P3-18

- 9. U23-13

- 19. + 12V 20. P3-20

- 10. P4-14 (DTR)

- Note: P4 is PORT 0 Connector

K10

- 1. U12-4

- 2. P3-15 (DCD)

- 3. GND

- 4. U22-13

- 5. U27-6

- 6. U24-5

- 7. U27-5

### **OPTIONS**

4-5 TRANSPARENT MODE ENABLED

- 3-4 TRANSPARENT MODE DISABLED

- 5-6 NORMAL RTS

- 6-7 INVERTED RTS

- 1-2 DCD TO PORT 1

NOTE: CHIPS U12 AND U23 ARE RS232 RECEIVERS CHIPS U11 AND U24 ARE RS232 DRIVERS

### TRANSPARENT / INDEP. MODE JUMPER LOCATION FIGURE 4.1.1

### 4.1.2 Baud Rate Selection (K18, K19)

Jumper group K19 selects the serial baud rate for both Port 0 and Port 1. K19 is a group of 24 pins arranged in three columns as shown in Figure 4.1.2. The center row of pins connect to the baud-rate-setting pins of the COM8116 baud rate generator. The baud rate may be set manually or by software.

### 4.1.2.1 Manual Baud Rate Setting

The center row of pins in jumper group K19 are pulled up so that if a particular pin is not jumpered to ground, it will be pulled to a logic 1. To select a logic zero, a pin must be jumpered to ground by connecting to the corresponding pin in the right hand column. The baud rates corresponding to the possible values of the D, C, B, and A signals are given in table 4.1.2.1.

### 4.1.2.2 Software Baud Rate Setting

If the four pins corresponding to the DCBA inputs to the baud rate generator are jumpered to the pins in the left hand column of K19, the baud rate of the serial port may be written by the processor. To enable the Store Strobe for Port 1 and Port 0 install jumpers K18-3 to K18-4 and K18-1 to K18-2 respectively. Note that the baud rate selection for the two ports are completely independent so that any combination of manual or software baud rate selection is allowed. To set the baud rate under program control, the desired value is simply written to the baud rate generator address, see Table 6.2 for this address. For example, storing a value of \$E5 will set Port 0 for 9600 baud (DCBA = 1110) and Port 1 for 300 baud (DCBA = 0101). If one Port is selected for manual baudrate, the corresponding bits of the byte written to the baudrate address become "don't cares".

| DCBA | BAUD RATE |

|------|-----------|

| 0000 | 50        |

| 0001 | 75        |

| 0010 | 110       |

| 0011 | 134.5     |

| 0100 | 150       |

| 0101 | 300       |

| 0110 | 600       |

| 0111 | 1200      |

| 1000 | 1800      |

| 1001 | 2000      |

| 1010 | 2400      |

| 1011 | 3600      |

| 1100 | 4800      |

| 1101 | 7200      |

| 1110 | 9600      |

| 1111 | 19200     |

EXAMPLE ABOVE ILLUSTRATES HARDWARE BAUD RATE OF 9600 FOR BOTH PORTS (FACTORY STANDARD).

INSTALLED JUMPERS = 0 REMOVED JUMPERS = 1

### BAUD RATE SELECTION TABLE 4.1.2.1

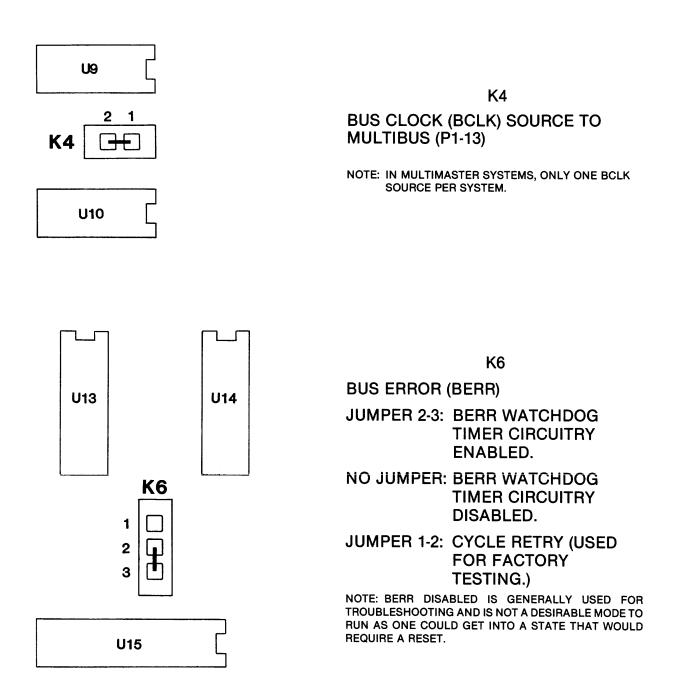

### 4.2 Bus Error Jumper (K6)

Jumper K6 connects the output of the watchdog timer to an encoder that operates the BERR and HALT lines of the 68000. When K6-2 to K6-3 is installed, BERR enabled, and DTACK is not received from an addressed device, a bus error is generated and the processor will begin bus error exception processing. With no jumper installed, the address and data lines will be static and can be examined at leisure. K6-1 and K6-2 will cause the processor to repeatedly rerun the cycle until DTACK is received. This is a useful mode for debugging off board system problems. Note that this feature is possible because the hardware refresh circuitry continues to operate even though the processor is stopped. See Figures 4.0 and 4.13 for location of jumper K6.

### 4.3 DTACK Select (K20,K21)

The DTACK generator for the ROM consists of a 74164 shift register that is held in its cleared state until either LDS or UDS is asserted. Logic ones are clocked through the shift register by the 10MHz (processor) oscillator, and DTACK timing is selected by choosing the stage of the shift register connected to the DTACK input pin. DTACK is factory set for 350ns ROM chips. If faster ROM is used, the DTACK jumper can be moved to provide a shorter DTACK delay. Each jumper represents an increment of 100ns., K21-1 being the shortest and K21-5 being the longest DTACK delay. (See Figure 4.3) Notice that the DTACK timer is active only for on-board ROM access. For off-board accesses DTACK is derived from the Multibus XACK signal. For on-board RAM accesses DTACK is derived from the RAM controller circuitry. Normal onboard RAM access will incur no wait states. See Table 4.3 below. Jumper K20-3 is the ROM delay input pin. This pin may be connected to various delayed outputs of the DTACK generator via the K21 jumper group. For convenience, K21-2 is routed to K20-2 to become the factory standard ROM DTACK delay. A jumper connecting K20-2 and K20-3 provides a ROM DTACK to operate with 350ns ROMS. For other ROM speeds K20-3 may be connected to other DTACK generator outputs at K21 according to the delay time given in Table 4.3. If 150ns or faster ROMS are used, no wait states are required. For zero wait state operation for ROM memory accesses, connect K20-3 to K20-1.

| Jumper<br>K20-3<br>Connect to | Maximum<br>ROM<br>ACCESS TIME | No. of<br>Wait States |

|-------------------------------|-------------------------------|-----------------------|

| K20-1                         | 155                           | 0                     |

| K21-1                         | 255                           | 2                     |

| K20-2/K21-2                   | 355                           | 4                     |

| K21-3                         | 455                           | 6                     |

| K21-4                         | 555                           | ·8                    |

| K21-8                         | 655                           | 10                    |

| K21-7                         | 755                           | 12                    |

| K21-6                         | 855                           | 14                    |

| K21-5                         | 955                           | 16                    |

### ROM DTACK DELAYS TABLE 4.3

| 1. U51-19 0 ROM WAIT STATES TAP | 1. U53-3 2 ROM WAIT STATES TAP   |

|---------------------------------|----------------------------------|

| 2. U53-4 4 ROM WAIT STATES TAP  | 2. U53-4 4 ROM WAIT STATES TAP   |

| 3. U51-1 ROM DTACK INPUT        | 3. U53-5 6 ROM WAIT STATES TAP   |

|                                 | 4. U53-6 8 ROM WAIT STATES TAP   |

|                                 | 5. U53-13 16 ROM WAIT STATES TAP |

| 2-3 FACTORY STANDARD            | 6. U53-12 14 ROM WAIT STATES TAP |

|                                 | 7. U53-11 12 ROM WAIT STATES TAP |

|                                 | 8. U53-10 10 ROM WAIT STATES TAP |

### ROM DTACK DELAY JUMPERS FIGURE 4.3

### 4.4 Interrupt Priority (K2)

Interrupts for on-board peripheral chips are terminated on wire wrap posts so that the user may select the interrupts to be used and the priority level of each interrupt. The following interrupts from the onboard peripheral chips are available:

| INTERRUPT SOURCE | JUMPER PIN NO. |

|------------------|----------------|

| Port 0 ACIA      | K15-11         |

| Port 1 ACIA      | K15-12         |

| Timer IRQ        | K16-8          |

| PIA 0 IRQ A      | K16-9          |

| PIA 0 IRQ B      | K16-10         |

| PIA 1 IRQ A      | K18-5          |

| PIA 1 IRQ B      | K18-6          |

Because Motorola IRQ lines are open drain connections, the interrupt requests from several chips may be wire 0Red to occupy a single priority level.

The Multibus interrupt lines (8) are brought to on-board wire wrap posts. These may also be wire 0Red and connected to the priority encoder inputs. Both the Multibus interrupts and the inputs to the priority encoder are located in jumper group K2. See Figure 4.4.

Priority encoder input seven is the highest priority; one is the lowest. Interrupt requests are not latched on-board. These interrupt requests must be held active until serviced when they are reset by the processor during execution of the interrupt service routine as indicated by the IEEE-796 specification.

### 4.5 CCLK and BCLK (K14, K4)

Jumpers K14 and K4 connect the on-board 10 MHz oscillator to the Multibus CCLK and BCLK lines, respectively. For a single processor system these jumpers should be left in place. For multi-processor systems, only one master should drive the Multibus clock lines. Removing these jumpers will remove the CCLK and BCLK signals from the bus. See Figures 4.0 and 4.13 for location of K14 and K4.

### **4.6 Bus Arbitration (K5, K7, K8, K9)**

Four jumpers are associated with the bus priority logic. K5 connects the output of the bus arbitration logic to the Multibus BPRO\* signal. The trace at K7 connects the BPRN\* line to ground. In a system with a single bus master, K7 should be in place. In a Multibus system using serial priority, BPRN\* is driven by the BPRO\* signal from the master with the next highest priority. For serial operation, K5 should be installed and K7 should be installed for single master or highest priority board in a multimaster configuration.

Common Bus Request (CBRQ) is a signal that alerts a Multibus Master that another Master needs to use the bus. As shown in Figure 4.6, if K9 is jumpered to connect K9-1 to K9-2, CBRQ will be implemented by the bus arbitration circuitry. In this mode, the OB68K1A will retain ownership of the bus until it is forced to arbitrate with a higher priority user or until a lower priority user asserts CBRQ. If another Multibus is not capable of asserting CBRQ the OB68K1A, will relinquish the bus upon the negation of BPRN and completion of the present bus cycle. This allows the OB68K1A to maintain increased offboard throughput using its CBRQ feature. If K9-2 and K9-3 are connected, the OB68K1A will relinquish the bus between each cycle.

When parallel arbitration is used the OB68K1A requests the use of the bus by asserting BREQ. For this mode of arbitration, K8 should be installed. K8 should be removed for serial arbitration.

<sup>\*</sup> indicates low active

**K**5

**K8**

1. P1-16 (BPRO)

2. U3-8

1. P1-1 (BREQ) 2. U21-15

JUMPER IN: SERIAL MULTIMASTER

**PRIORITIZATION**

JUMPER IN: PARALLEL ARBITRATION

**JUMPER OUT:**

JUMPER OUT: SERIAL ARBITRATION

PARALLEL MULTIMASTER **PRIORITIZATION**

K7

K9

1. GND

2. P1-15 (BPRN)

1. P1-29 (CBRQ)

2. U21-3

3. GND

JUMPER IN: SINGLE MASTER

OR

HIGHEST PRIORITY

**BOARD IN MULTIMASTER**

SYSTEM WITH SERIAL

ARBITRATION

JUMPER OUT: ALL OTHER

CONFIGURATIONS

1-2: BOARD MAINTAINS BUS CONTROL UNTIL ANOTHER

MASTER REQUEST BUS

2-3: BOARD RELEASES BUS CONTROL AFTER EACH TRANSFER

### **BUS ARBITRATION JUMPER CONFIGURATION** FIGURE 4.6

### 4.7 Initialize (K3)

The master in a single master system should drive the Multibus INIT line. For this type of operation K3-1 should be connected to K3-2 (See Figure 4.7). Both the power-on reset and software generated resets will drive the Multibus INIT line (Factory Standard).

For a Multi-Master system, it may be desirable for INIT to be an input to the OB68K1A board. This is done by connecting K3-2 to K3-3 so that the INIT signal will trigger the onboard reset generator.

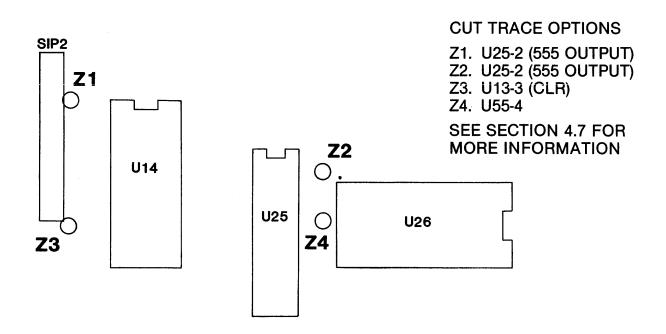

For some applications it may be necessary for the OB68K1A to be reset directly by the INIT signal in order to synchronize the restart sequence of multiple processors. To use INIT directly, cut the two traces Z1-Z3 and Z2-Z4. Connect Pin K3-2 to both Z3 and Z4. (See Figure 4.13). This modification disables the onboard reset generator and the RESET push button will not be operative. The Master driving INIT must meet the power-on timing requirements of the 68000 processor in order to insure a valid restart sequence.

### **K**3

- 1: U4-8 RESET OUTPUT

- 2. P1-14 INIT

- 3. U1-2 RESET GENERATOR INPUT

- 1-2: PROCESSOR AND ONBOARD INIT CIRCUITRY DRIVE MULTIBUS INIT.

- 2-3: MULTIBUS INIT TRIGGERS ONBOARD INIT CIRCUITRY.

### RESET JUMPER CONFIGURATION FIGURE 4.7

### 4.8 ROM Socket Configuration (K22)

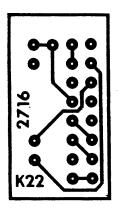

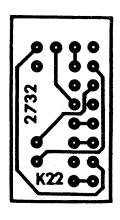

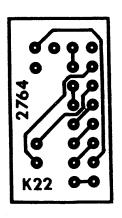

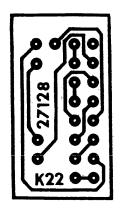

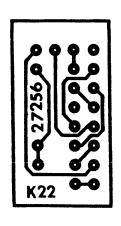

Jumper area K22 configures the ROM sockets for the ROM size that is chosen. Rather than wire wrapping this group of pins, a small configurator board is plugged in to make all the connections simultaneously. The OB68K1A is shipped with a configurator for 8K (2764's) byte PROMs, but other configuration boards are available from the factory.

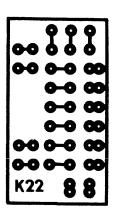

### 4.8.1 ROM Size Jumper Configuration

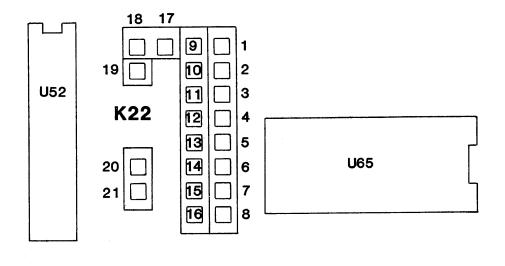

Figure 4.8.1 shows the jumper group K22 and identifies each of the pins. The user may choose to wire wrap K22 to field modify the size or type of ROM used on the OB68K1A.

Normally the user will use the factory supplied configuration plug to interconnect the K22 jumper pins. If a different PROM type is to be used, the user may reconnect K22 as shown in Figure 4.8.2. This figure shows the printed circuit artwork for the factory supplied plugs. The user may choose to fabricate plugs or purchase them from Omnibyte. The ROM sockets used on the OB68K1A have 28 pins. This is to provide for operation with certain types of 32K and 64K ROM chips. For operating with the 24 pin devices, ROM's MUST be installed with the unused pins on the right side of the socket (left justified). See Figure 4.8.3 for ROM socket configuration and Figure 4.8.4 for compatible chip pinout configuration. See section 9.0 for ordering information.

|         | NZZ                  |                   |         |

|---------|----------------------|-------------------|---------|

| 1. A 18 | 9. GND               | 17. ROM PIN 26    | - A!3   |

| 2. A 17 | 10. ROM PIN 22       | 18. ROM PIN 23    |         |

| 3. A 16 | 11. ROM PIN 27       | 19. GND           |         |

| 4. A 15 | 12. +5V              | 20. U30-3 - A/6   | 5193 -3 |

| 5. A 14 | 13. U52-2            | 21. U30-13 - 🦮 17 |         |

| 6. A 13 | 14. U52-1            |                   |         |

| 7. A 12 | 15. ROM PIN 2 - A 12 |                   |         |

| 8. A 11 | 16. ROM PIN 21       |                   |         |

K22

NOTE: SEE FIGURE 4.8.2 FOR FACTORY CONFIGURATION

OBK1A/K22-2732

OBK1A/K22-2764 (FACTORY STANDARD)

OBK1A/K22-27128

OBK1A/K22-27256

OBK1A/K22-UD (USER DEFINABLE)

### ROM CONFIGURATION PLUGS LAYOUTS FIGURE 4.8.2

# ROM SOCKET CONFIGURATION FIGURE 4.8.3

|                                              | Vpp                                                 |                                    |                                                    |                                              |                                               | PIN                                                      | 27256                                                               | 27128                                                                  | 2764                                                                | 2732                                                | 2716                                                  |

|----------------------------------------------|-----------------------------------------------------|------------------------------------|----------------------------------------------------|----------------------------------------------|-----------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------|

| A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 | A12<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 | Vpp A12 A7 A6 A5 A4 A3 A2 A1 A0 00 | A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0<br>C0 | A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 | 1 — 2 — 3 — 4 — 5 — 6 — 7 — 8 — 9 — 10 — 11 — | 28<br>27<br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>19 | Vcc<br>A14<br>A13<br>A8<br>A9<br>A11<br>OE<br>A10<br>CE<br>O7<br>O6 | Vcc<br>PGM<br>A1.3<br>A8<br>A9<br>A1.1<br>OE<br>A1.0<br>CE<br>O7<br>O6 | Vcc<br>PCM<br>N/C<br>A8<br>A9<br>A11<br>OE<br>A10<br>CE<br>07<br>O6 | Vcc<br>A8<br>A9<br>A11<br>OE/Vpp<br>A10<br>CE<br>O7 | Vcc<br>A8<br>A9<br>Vpp<br>OE<br>A10<br>CE<br>O7<br>O6 |

|                                              | 01                                                  | 01                                 | 01<br>02                                           | 01<br>02                                     | 12 <b></b>                                    | —17<br>—16                                               | 05<br>04                                                            | 05<br>04                                                               | 05<br>04                                                            | 05<br>04                                            | 05<br>04                                              |

| 02                                           | 02                                                  | O2<br>Gnd                          | O2<br>Gnd                                          | O2<br>Gnd                                    | 13-<br>14-                                    | -16<br>-15                                               | 04<br>03                                                            | 04<br>03                                                               | 04<br>03                                                            | 04<br>03                                            | 04<br>03                                              |

|          | PIN NAMES     |

|----------|---------------|

| A0 - A12 | ADDRESS LINES |

| 00-07    | DATE LINES    |

| CE       | CHIP ENABLE   |

| ŌE       | OUTPUT ENABLE |

| PGM      | PROGRAM       |

# ROM CHIP PINOUT CONFIGURATION FIGURE 4.8.4

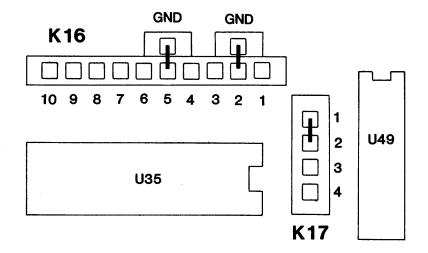

### 4.9 Timer (K16, K17)

The timer (MC6840) has a clock, a gate and an output for each of its three timing channels. All nine of these signals are terminated on wire wrap pins in jumper groups K16 and K17. To operate the MC6840 timer channels, the gate signals must be low.

A trace on the board connects each of the three gate signals to ground. A trace must be cut for the appropriate channel if the gate is to be operated from an active source.

To use the timer as a programmable interrupt generator for the CPU, no external clock or gate connections are needed. The MC6840 may use the 1 MHz "E" clock as a time base. The timer IRQ is usually connected to a selected priority interrupt level. See Figure 4.9 for the PTM jumper pad locations.

K16

- 1. GND

- 2. U35-2 GATE 2

- 3. U35-3 OUTPUT 2

- 4. U35-4 CLOCK 2

- 5. U35-5 GATE 3

- 6. U35-6 OUTPUT 3

- 7. U35-7 CLOCK 3

- 8. U35-9 TIMER IRQ

- U32-38 PIA 0 IRQ A

- 10. U32-37 PIA 1 IRQ B

K17

- 1. GND

- 2. U35-26 GATE 1

- 3. U35-27 OUTPUT 1

- 4. U35-28 CLOCK 1

TIMER OPTION PIN IDENTIFICATION AND LOCATION FIGURE 4.9

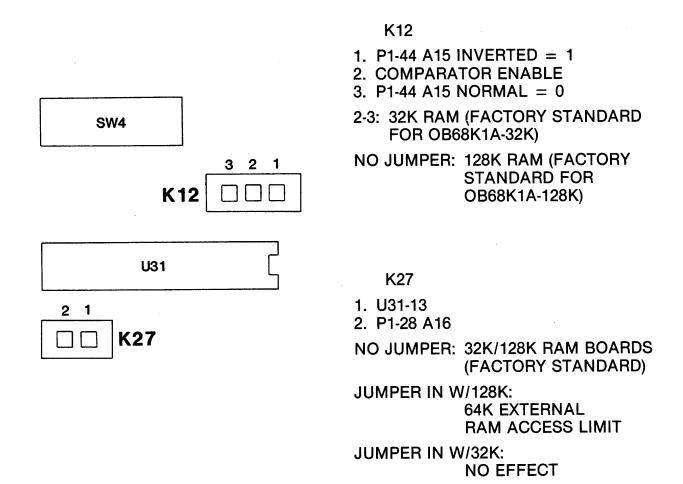

## 4.10 External RAM Access (K12, K27)

Switch SW4 is used to set the base address of the dual-port RAM for offboard access. Each OB68K1A is set to allow offboard access to the full onboard RAM. For the 128K version, the offboard access can be limited to 64K bytes by installing jumper K27. The external access can be further restricted to a 32K block of memory using jumper K12. The upper or lower half of the switch selected 64K base address is chosen by connecting K12-1 to K12-2 or K12-2 to K12-3 respectively. Jumper K12 provides the same function for 32K versions of the OB68K1A so that the external access can be made to appear at any 32K byte boundary. Address lines A19-A23 have been pulled to logic 0 to accommodate systems that do not implement the full 16M-byte address. Please note that the 128K RAM starts on 128K byte boundaries even if, a lesser amount is made accessible to offboard access, ie. upper or lower 64K byte blocks.

NOTE: WITH THE 128K BOARD K27 IS NOT JUMPERED AND PINS 13 AND 14 ON U31 (ADDRESS COMPARATOR) ARE TIED TOGETHER. THIS MAKES POSITION 1 ON SWITCH 4 A DON'T CARE BIT AND REDUCES POSSIBLE ERRORS.

## 4.11 Watchdog Timer for External RAM Access (K23)

In the case of a malfunction of an external Master, an external RAM access could fail to terminate a command even after the XACK was generated. If this condition would persist for many microseconds, the contents of the onboard RAM could be destroyed. Logic is included in the dual port arbitration circuitry to negate the external request to the onboard RAM after 2.5 micro seconds. Once the access is terminated by the arbitration circuitry the board is allowed to resume normal processing; ie a processor cycle or RAM refresh. The external RAM access, if still present, is treated as a new request by the arbitration circuit and this cycle is repeated. The board is shipped with the watchdog timer enabled, but this feature may be defeated by installing jumper K23. See Figure 4.13.

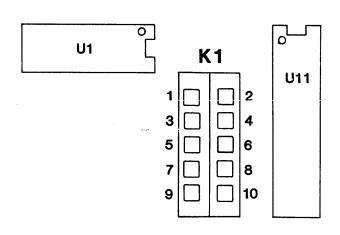

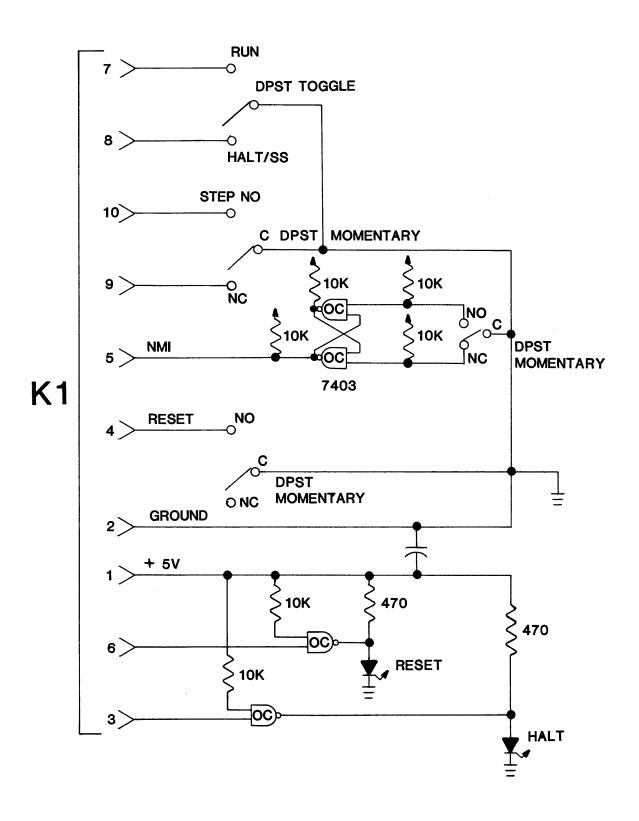

## 4.12 Optional Front Panel (K1)

Jumper group K1 is provided as a means of connecting a front panel to the OB68K1A. Using the K1 signals, a front panel can be implemented that includes a RUN/HALT switch, RESET, SINGLE STEP and NMI pushbuttons. The required external circuitry is shown in Figure 4.12 (B). The NMI (non-maskable interrupt) may be used as a software abort button. This front panel requires only one quad 2-input NAND gate. Power for the front panel is included in the K1 jumper group.

The front panel circuit of Figure 4.12 (B) is available as an option from Omnibyte. This is a small box with a 5-foot interconnecting cable terminated in a connector that plugs into jumper group K1. The ordering information is given in Section 9.0.

K1

- 1. +5V

- 2. GND

- 3. HALT LED

- 4. MANUAL RESET

- 5. NMI INPUT

- 6. RESET LED

- 7. RUN

- 8. HALT/SS MODE

- 9. SINGLE STEP PUSH BUTTON N.C.

- 10. SINGLE STEP PUSH BUTTON N.O.

## 4.13 Miscellaneous Jumper Identification

Several jumper options have been included on the OB68K1A for flexibility and future enhancement. Although these jumpers are not normally changed by the user, they are documented in Figure 4.13 for completeness. The Figure serves to define the physical location of specific jumper pins that appear on the OB68K1A electrical schematic diagram. Those jumper groups not documented elsewhere in the text are included in Figure 4.13.

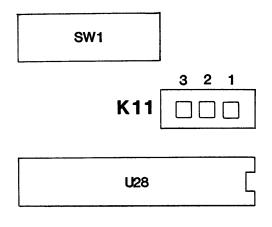

K11

**ONBOARD RAM SIZE**

1-2 32K RAM 2-3 128K RAM

NOTE: FACTORY CONFIGURED, GENERALLY NOT CHANGED BY USER, JUMPER MUST BE IN PLACE TO ACCESS RAM.

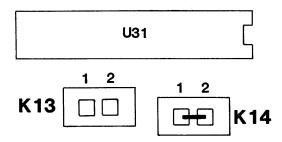

K13

JUMPER IN: CONNECTS A18 TO ADDRESS COMPARATOR FOR ONBOARD RAM.

NOTE: K13 IS SUPPLIED FOR FUTURE ONBOARD RAM ENHANCEMENT.

K14

CONSTANT CLOCK (CCLK) TO MULTIBUS (P1-31)

NOTE: IN MULTIMASTER SYSTEMS, ONLY ONE CCLK SOURCE IS PERMITEED.

**U36**

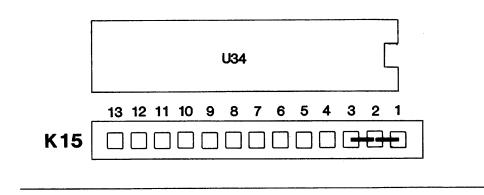

#### K15

- 1. U23-11 (DTR)

- 2. U34-24 (CTS)

- 3. U34-23 (DCD)

- 4. GND

- 5. TEST POINT 2 (TP2) HALT

- 6. TEST POINT 1 (TP1) RESET

- 7. TEST POINT 3 (TP3) BERR

- 8. TEST POINT 4 (TP4) IPL 2

- 9. TEST POINT 5 (TP5) IPL 1

- 10. TEST POINT 6 (TP6) IPL 0

- 11. U34-7 PORT 0 IRQ

- 12. U26-7 PORT 1 IRQ

- 13. SPARE RS232 RECEIVER BUFFER INPUT (OUTPUT ON K31; TTL)

NOTE: K-15 - 1,2,3 CONNECTION MADE VIA CIRCUIT BOARD TRACES.

MISCELLANEOUS JUMPERS LOCATIONS - CONT. FIGURE 4.13

# MISCELLANEOUS JUMPERS LOCATIONS - CONT. FIGURE 4.13

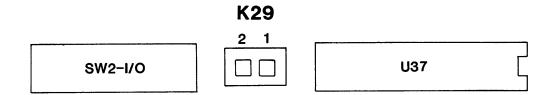

K29

CONNECTS A16 TO ONBOARD RAM ADDRESS COMPARATOR

JUMPER IN: 32K RAM JUMPER OUT: 128K RAM

NOTE: ON 128K RAM BOARDS PINS 3 AND 4 ON U28 ARE TIED TOGETHER, THUS MAKING POSITION 1 ON SWITCH 1 A DON'T CARE BIT AND REDUCES POSSIBLE ERRORS.

| K30         |     | K30                                                                            |

|-------------|-----|--------------------------------------------------------------------------------|

| 1<br>2<br>3 | U27 | INVERTS SIGN OF DTR ON PORT 1<br>2-3 NORMAL (FACTORY STANDARD)<br>1-3 INVERTED |

|             | U23 | K31<br>SPARE RS232 RECEIVER BUFFER<br>OUTPUT (INPUT ON K15-13; TTL)            |

MISCELLANEOUS JUMPERS LOCATIONS - CONT. FIGURE 4.13

CONNECTS

CONNECTS A17 (1-2) AND A18 (3-4) TO ONBOARD RAM ADDRESS COMPARATOR.

K33

NOTE: K33 IS SUPPLIED FOR FUTURE ONBOARD RAM ENHANCEMENT.

MISCELLANEOUS JUMPERS OPTIONS - CONT. FIGURE 4.13

## 4.14 System Configuration

OB68K1A boards that have been ordered in conjunction with, the OB68K/SYS Development System or, the three board Functional Board Pack, have been modified from the standard factory configuration stated earlier in this manual.

Port 1 has been reconfigured as Data Communications Equipment (DCE), so that a terminal can be connected to Port 1. + 12V has also been brought out to the Port 1 connector and a TI810\* printer can be connected to the Port 1. Several interrupts have also been connected. Listed below are details of the modifications:

| Port 1 | Modific | ations |

|--------|---------|--------|

|--------|---------|--------|

| Jumper Group K26 |      |         |                    |

|------------------|------|---------|--------------------|

| cut              | 3-4  | connect | 3-8                |

| cut              | 5-6  | connect | 4-7                |

| cut              | 7-8  | connect | 6-9                |

| cut              | 9-10 |         |                    |

| Jumper Group K10 |      |         |                    |

| cut              | 1-2  | connect | K10-2 to<br>K25-19 |

| P3 connector     |      |         |                    |

| Pin 11 to Pin 15 |      | connect |                    |

#### **INTERRUPTS**

| wire-wrap                | Multibus INT 3 to Level 3                             |

|--------------------------|-------------------------------------------------------|

| wire-wrap                | INT input<br>Port 0 IRQ to Level 16 INT               |

| •                        | input                                                 |

| wire-wrap                | Port 1 IRQ to Level 5 INT input                       |

| wire-wrap                | Timer IRQ to Level 14 INT input                       |

| jumper with              | Isolates INT 0 from                                   |

| IN916-anode<br>toward D6 | circuitry of 555 during power-on RESET                |

|                          | wire-wrap wire-wrap wire-wrap jumper with IN916-anode |

#### **5.0 CONNECTOR PINOUTS**

#### 5.1 Multibus P1 and P2 Connectors

P1 and P2 are the Multibus connectors and are pinned according to the IEEE 796 specification. See Tables 5.1.1 & 5.1.2 respectively for the pin assignments.

<sup>\*</sup>TI810 is a trademark of Texas Instruments

|                                   |                                              | (Cor                                                 | nponent Side)                                                               |                                              |                                                 | (Circuit Side)                                                                                         |

|-----------------------------------|----------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------|

|                                   | Pin                                          | Mnemonic                                             | Description                                                                 | Pin                                          | Mnemonic                                        | Description                                                                                            |

| Power<br>Supplies                 | 1<br>3<br>5<br>7<br>9<br>11                  | GND<br>+ 5V<br>+ 5V<br>+ 12V<br>GND                  | Signal GND<br>+ 5Vdc<br>+ 5Vdc<br>+ 12Vdc<br>Reserved, bussed<br>Signal GND | 2<br>4<br>6<br>8<br>10<br>12                 | GND<br>+ 5V<br>+ 5V<br>+ 12V<br>GND             | Signal GND<br>+ 5Vdc<br>+ 5Vdc<br>+ 12Vdc<br>Reserved, bussed<br>Signal GND                            |

| Bus<br>Controls                   | 15<br>17<br>19<br>21                         | BCLK* BPRN* BUSY* MRDC* IORC* XACK*                  | Bus Clock Bus Pri. In Bus Busy Mem Read Cmd I/O Read Cmd XFER Acknowledge   |                                              | BPRO*<br>BREQ*<br>MWTC*<br>IOWC*                | Initialize<br>Bus Pri. Out<br>Bus Request<br>Mem Write Cmd<br>I/O Write Cmd<br>Inhibit 1 (disable RAM) |

| Bus<br>Controls<br>and<br>Address | 25<br>27<br>29<br>31<br>33                   | LOCK* BHEN* CBRQ*  CCLK* INTA*                       | Lock Byte High Enable Common Bus Request Constant Clk Intr Acknowledge      | 28<br>30<br>32                               | INH2*<br>ADR16*<br>ADR17*<br>ADR18*<br>ADR19*   | Inhibit 2 (disable PROM or ROM)  Address  Bus                                                          |

| Interrupts                        | 37                                           | INT6*<br>INT4*<br>INT2*<br>INT0*                     | Parallel<br>Interrupt<br>Requests                                           | 40                                           | INT7*<br>INT5*<br>INT3*<br>INT1*                | Parallel<br>Interrupt<br>Requests                                                                      |

| Address                           | 43<br>45<br>47<br>49<br>51<br>53<br>55<br>57 | ADR12*<br>ADR10*<br>ADR8*<br>ADR6*<br>ADR4*<br>ADR2* | Address<br>Bus                                                              | 44<br>46<br>48<br>50<br>52<br>54<br>56<br>58 |                                                 | Address<br>Bus                                                                                         |

| Data                              | 63<br>65<br>67<br>69<br>71                   | DATC*<br>DATA*<br>DAT8*<br>DAT6*<br>DAT4*<br>DAT2*   | Data<br>Bus                                                                 | 64<br>66<br>68<br>70<br>72                   | DATF* DATD* DATB* DAT9* DAT7* DAT5* DAT3* DAT1* | Data<br>Bus                                                                                            |

| Power<br>Supplies                 | 75<br>77<br>79<br>81<br>83<br>85             | – 12V<br>+ 5V                                        | Signal GND Reserved, bussed - 12Vdc + 5Vdc + 5Vdc Signal GND                | 76<br>78<br>80<br>82<br>84<br>86             | – 12V                                           | Signal GND Reserved, bussed - 12Vdc + 5Vdc + 5Vdc Signal GND                                           |

All Reserved pins are reserved for future use and should not be used if upwards compatibility is desired.

# IEEE 796 P1 CONNECTOR PINOUT TABLE 5.1.1

|         |     | (        | Component Side)      |     | (Circuit Side) |                      |  |

|---------|-----|----------|----------------------|-----|----------------|----------------------|--|

|         | Pin | Mnemonic | Description          | Pin | Mnemonic       | Description          |  |

|         | 1   |          | Reserved, Not Bussed | 2   |                | Reserved, Not Bussed |  |

|         | 3   |          | Reserved, Not Bussed | 4   |                | Reserved, Not Bussed |  |

|         | 5   |          | Reserved, Not Bussed | 6   |                | Reserved, Not Bussed |  |

|         | 7   |          | Reserved, Not Bussed | 8   |                | Reserved, Not Bussed |  |

|         | 9   |          | Reserved, Not Bussed | 10  |                | Reserved, Not Bussed |  |

|         | 11  |          | Reserved, Not Bussed | 12  |                | Reserved, Not Bussed |  |

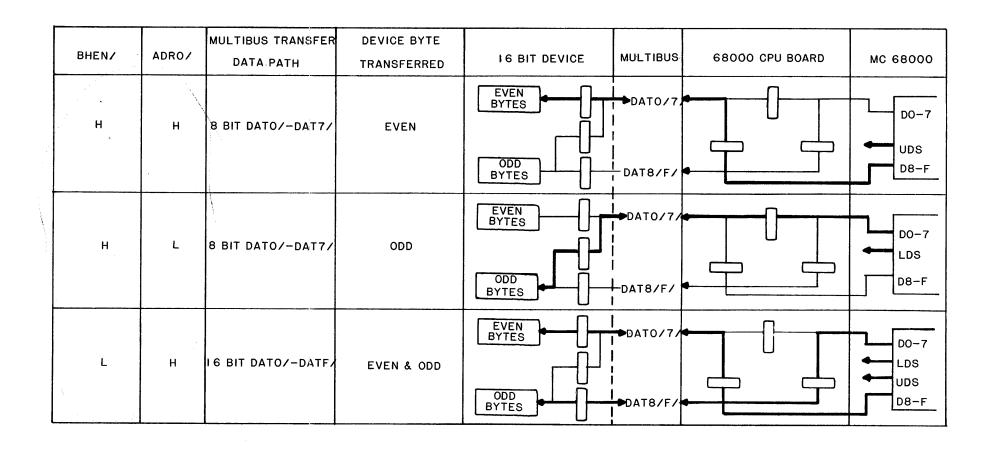

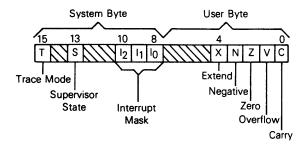

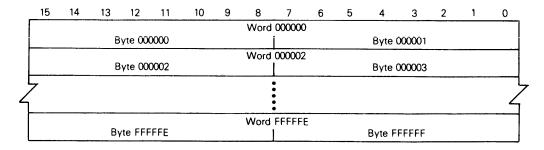

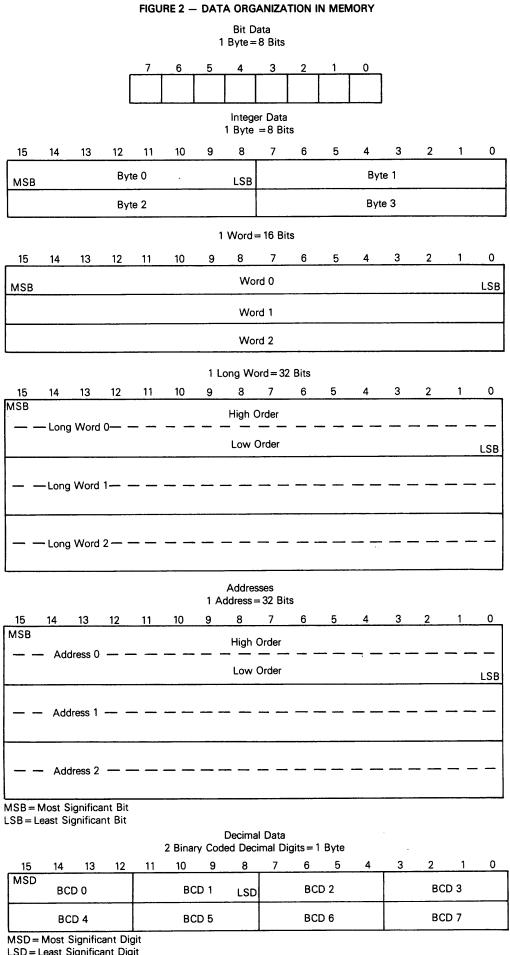

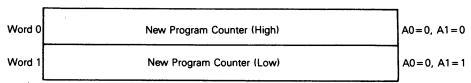

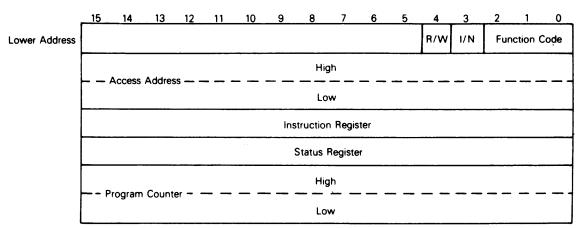

|         | 13  |          | Reserved, Not Bussed | 14  |                | Reserved, Not Bussed |  |