An Introduction to

# **PB440 MICROPROGRAMMING**

pb Packard Bell Computer

An Introduction to

# **PB440 MICROPROGRAMMING**

## FOREWORD

This Microprogramming Manual is the first in a series of technical and application reference manuals on the Packard Bell PB440 Computer. Others to be made available include programming manuals on command sets, a Fortran Programming Manual and technical manuals on peripheral equipment.

Although this present manual covers microprogramming procedures in some detail, few PB440 users will wish to program their machine at that level. However, a study of microprogramming techniques will be helpful in disclosing many of the more significant details of the PB440 hardware. To facilitate use of the PB440, representative command lists covering engineering scientific computation and realtime systems computing and control will be provided with the machine.

### REVISION NOTICE

This manual is a revised edition of "An Introduction to the PB440 Computer," dated November 1962. All information in this revised edition supersedes the information contained in the November 1962 edition.

# **TABLE OF CONTENTS**

| Page                                    |

|-----------------------------------------|

| GENERAL DESCRIPTION 5                   |

| THE INSTRUCTION REPERTOIRE 5            |

| DESIGNING AN INSTRUCTION SET 6          |

| THE PB440'S INTERNAL SEQUENCE 7         |

| THE REGISTERS 7                         |

| THE MICRO-STEPS 10                      |

| MEMORY ACCESS OPERATIONS 10             |

| LOGICAL WORD OPERATIONS 12              |

| SHIFTING OPERATIONS                     |

| MULTIPLICATION AND DIVISION 18          |

| TRANSFER OF CONTROL 20                  |

| TEST OPERATIONS                         |

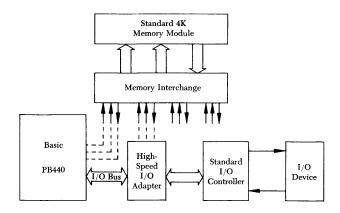

| INPUT-OUTPUT SYSTEM 24                  |

| SUMMARY OF OPERATION CODES              |

| PB440 CHARACTER CODES                   |

| GLOSSARY                                |

|                                         |

|                                         |

| ILLUSTRATIONS                           |

| Page                                    |

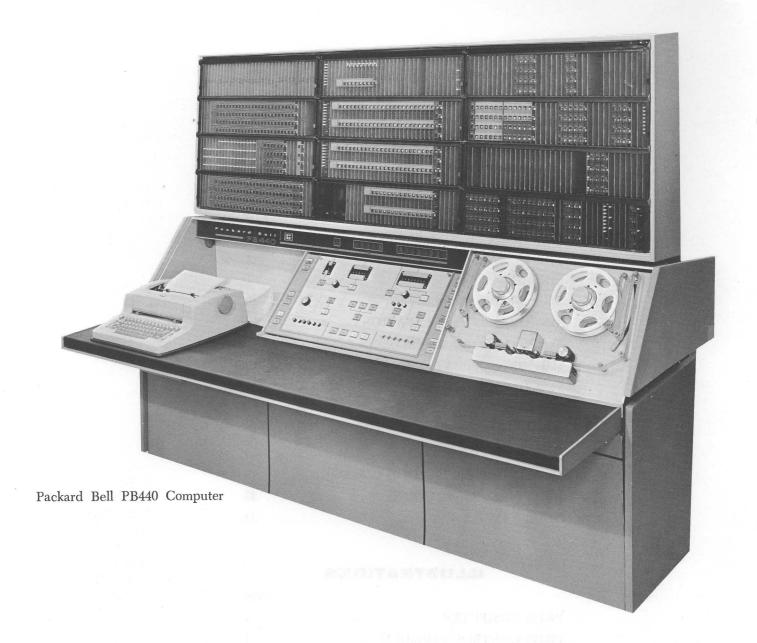

| PB440 COMPUTER 4                        |

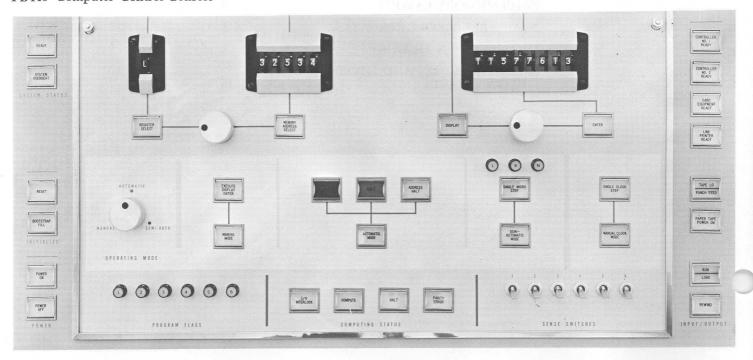

| PB440 CONTROL CONSOLE 4                 |

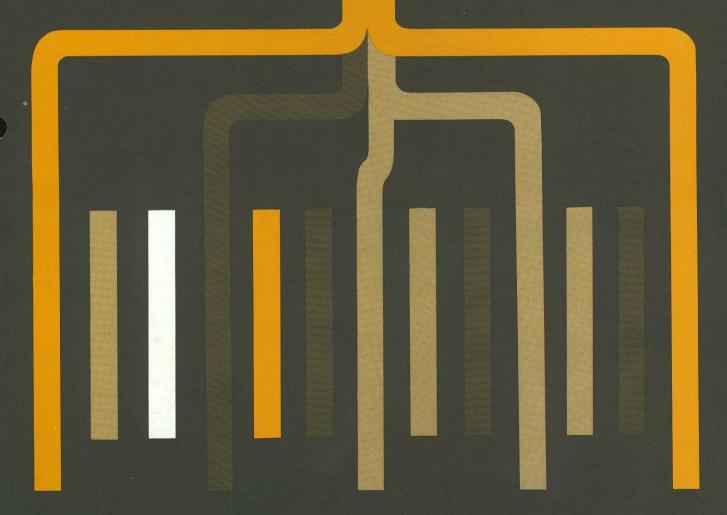

| PB440 MEMORY LAYOUT 5                   |

| AVAILABLE REGISTERS 8                   |

| MICRO-STEP IN MEMORY 9                  |

| MULTIPLICATION AND DIVISION FLOW CHARTS |

PB440 Computer Control Console

#### **GENERAL DESCRIPTION**

The PB440 Computer is a core-memory computer whose basic operations can be performed at the clock rate of the computer. The programmer has complete control over the specific operation performed during nearly every clock pulse; in this sense the computer is said to be micro-programmed. Sequences of basic operations can be stored in memory and executed much like a conventional subroutine, so that operations normally considered to be "commands" on a conventional computer can be described in terms of their elementary operations, and can be changed at will. In this sense the computer is said to be of the stored-logic type.

Two separate types of core memory are provided, although the memory is addressed as a single homogeneous block. Main memory, comprising the bulk of the storage capacity of the machine, consists of magnetic cores from which one word of information can be obtained in 2 microseconds. The memory cycle time is 5 microseconds. Fast memory, designed to hold the sequences of elementary steps which define an "instruction", consists of a set of BIAX cores, from which a word can be obtained in less than 1 microsecond. Since these cores are read non-destructively, the term "cycle time" does not apply to fast memory. The word length of both memories is 24 binary digits (bits). (Internal parity checking is provided automatically, and utilizes an additional bit in each word for this purpose. This bit is not available for programming purposes.)

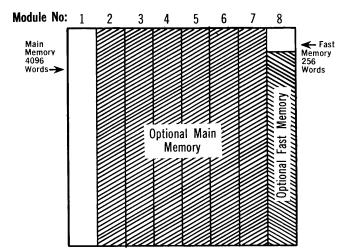

The basic machine contains 4096 words of main memory and 256 words of fast memory (see Figure 1). Main memory can be expanded to a maximum of 28,672 words, and fast memory can be expanded (in 256 word blocks) to 4096 words for a maximum of 32,768 words of directly addressable memory.

The input-output equipment planned for the basic computer consists of a photo electric paper-tape reader capable of reading 500 characters per second, a paper-tape punch capable of punching at a rate of 110 characters per second, and an electric typewriter which can print 16 characters per second. Additional input-output equipment, consisting of IBM-compatible card and magnetic tape devices, is available at extra cost. A high-speed line printer will also be available as optional equipment.

#### THE INSTRUCTION REPERTOIRE

The PB440 does not have a set of instructions in the same sense that conventional computers have. Instead, its basic design provides the programmer with the option of describing, in terms of elementary operations, a sequence of steps which define an instruction. Nearly every clock pulse is available to the programmer for

Figure 1. PB440 Overall Memory Layout

Each module can contain 4096 words, 24 bits in length.

Main memory access time:  $2\mu$ sec Main memory cycle time:  $5\mu$ sec Fast memory access time:  $<1\mu$ sec

#### **Memory Addressing Scheme**

| Module No.                  | Octal Addresses | Decimal Addresses |

|-----------------------------|-----------------|-------------------|

| 1                           | 00000 to 07777  | 00000 to 04095    |

| 2                           | 10000 to 17777  | 04096 to 08191    |

| 3                           | 20000 to 27777  | 08192 to 12287    |

| 4                           | 30000 to 37777  | 12288 to 16383    |

| 5                           | 40000 to 47777  | 16384 to 20479    |

| 6                           | 50000 to 57777  | 20480 to 24575    |

| 7                           | 60000 to 67777  | 24576 to 28671    |

| 8                           | 70000 to 77777  | 28672 to 32767    |

| 1st Block of<br>Fast Memory | 70000 to 70377  | 28672 to 28927    |

this purpose. A complete sequence of elementary steps which describe an operation (instruction) in the conventional sense is called a *microutine*. To avoid confusion we will refer to the instruction described in this way as a "macro-instruction". A complete instruction set consists of a control sequence (to determine which of the various macro-instructions is indicated) and a set of microutines, each of which defines a macro-instruction. This instruction set is normally stored in fast memory, although micro-steps can be executed from main memory (at a slower rate) if so desired, or if there is not enough room in fast memory to contain them all.

There are, of course, many different ways in which one could describe the individual logic steps which constitute a conventional computer instruction. The logic designer usually describes them with a set of Boolean equations, each equation consisting of many terms of differing meanings. He uses the same technique to describe the "control" section of the computer. Since, to a large extent at least, the design of the macroinstructions for the PB440 computer has been left to the programmer, a method of description was chosen which is already familiar to him; that is, in terms of a sequential series of elementary steps which he calls a program. It should be emphasized that there is a very real difference between a microutine, which describes a macro-instruction, and a computer program, which consists of a series of macro-instructions designed to solve a problem, even though the methods used to obtain the two are very much alike.

## **DESIGNING AN INSTRUCTION SET**

The enormous advantage of being able to choose an instruction set to suit a particular problem is probably obvious to anyone who has written a program for a digital computer. The programmer can, in a very real sense, design the computer to fit his problem. The resulting program which he can write will be far shorter and more efficient than if he were restricted to an instruction set not of his own choosing, and he need not have a group of instructions available which he finds he cannot use. As an example, by designing an instruction set to execute a program written originally in the FOR-TRAN language and compiled automatically, it was found that the resulting program (generated by the compiler) would be about half as long as one generated from the same source program on a more conventional computer. This saving, in terms of the length of the program, is effected by having available instructions designed to concisely describe operations available in the FORTRAN source language. In the same way, the compiler itself can be made compact and efficient by writing it in an instruction set which can describe, in a very few instructions, the manipulations which a compiler must perform to translate a source program into a machine language program.

It should be recognized that not all programmers will want to be bothered with the problems of computer design every time they write a program. They need not be. Packard Bell recognizes its responsibility in this regard, and will provide several complete instruction sets with the computer upon delivery, in addition to the FORTRAN system now under construction. Assembly routines and other "utility" routines will be provided which are compatible with each of the instruction sets, and provision will be made for the programmer who may want to augment an instruction set with a few instructions of his own design.

The design of an instruction set may be conveniently divided into three parts:

- A macro-instruction format is chosen, usually with an eye toward rapid interpretation. This format need not be restricted to a word length of 24 bits, nor to single address instructions. The instructions need not refer to an "accumulator" unless this is useful, and more than one "accumulator" may be referenced if desired. Conventional or unconventional indexing may be described. Any other useful features, such as indirect addressing, relativeindirect addressing, or whatever special functions are needed, can be included.

- 2. The control sequence is described. It must be capable of distinguishing between the macroinstruction formats chosen (if there were more than one) and will normally provide operations common to most, or all, of the instructions such as indexing and indirect addressing. It will normally obtain the parameters, if any, needed for the execution of the instruction.

- 3. The microutines, each of which defines the execution of an instruction, are written. These may be of any length and complexity desired, and may call on, or transfer control to, other microutines. Astute design of the microutines can shorten the whole instruction set considerably, and provide many useful combinations not normally found on conventional computers. As an example, assume we need a fixed-point add instruction, and we also require an instruction which stores the content of an "accumulator" into memory. Very little is required to provide an additional instruction which performs both of these functions in sequence. This new instruction becomes "add the content of memory to the accumulator, and store the result back in the same place in memory". The new instruction can make use of the other two microutines already present, at little cost in space or in execution time, and provides the facility for increasing the value of a "counter" in memory. For example, using only two instructions:

CLA 1 Clear and add "1" to the accumulator

ADS CNTR Add "CNTR" and store the

sum in "CNTR"

It should be remembered that the amount of time required to interpret the macro-instruction should be kept as short as possible, since this amount of time must be added to the execution time of each macro-instruction, no matter how fast that execution may be. It is an "overhead" which must be included when considering

the overall execution speed of any particular instruction set.

This "overhead" time can be minimized in two ways. Many of the micro-steps available to the programmer are designed to make interpretation easy and fast, and the programmer should become familiar with them before he attempts to design an instruction set. He should also choose the individual macro-instructions with care so that as few of them as possible are needed to do his job.

## THE PB440'S INTERNAL SEQUENCE

The registers available in the PB440 Computer are shown in Figure 2. For the moment, we need consider only the registers labeled "P" and "E".

The individual micro-steps are stored in memory in pairs (see Fig. 3) and are executed in sequence from left to right. The "P" register functions as a micro-pair location counter, and normally contains the address of the next micro-pair to be executed. It is automatically incremented by 1 each time a micro-pair is obtained from memory for execution.

The "E" register holds the pair of micro-steps being executed, and may be thought of as the micro-level command register. If we examine the automatic sequence of operations, beginning at the moment the micro-pair is inserted into the "E" register for execution, we would observe the following operations:

- 1. The "P" register is incremented by 1.

- The left-hand micro-step is examined by the computer logic and the indicated micro-step operation is performed.

- 3. At the same time, the right-hand micro-step is examined to see if it involves a memory reference, or indicates the "P" register is to be changed. For the moment, assume it does not.

- Following execution of the left-hand micro-step the right-hand micro-step is examined and executed as before.

- During the execution of the right-hand micro-step, the next micro-pair is inserted into the "E" register and the cycle repeats.

Normal timing for this execution sequence, assuming the next pair is located in fast memory, is 2 clock pulses. To a first approximation one can say that execution proceeds at a rate of 1 micro-step per clock pulse. When the right-hand micro-step changes the content of the "P" register, however, the proper micro-pair cannot be obtained from memory until this operation is completed. This condition requires that the computer wait for one additional clock pulse, so that 3 clock pulses are required to execute the micro-pair.

The memory-bus structure allows either fast or main memory to be referenced during any clock pulse, but not both at the same time. Therefore, if the right-hand micro-step is one which references either main or fast memory, the next micro-pair cannot be obtained at the same time, and the computer must wait for 1 additional clock pulse after the memory access. There is no compounding of waiting periods for both changing "P" and accessing memory in a right-hand micro-step.

Since transfer of control is effected by altering the content of the "P" register (which is addressable), actual control transfer will not occur until after execution of the right-half micro-step. In general, then, it can be seen that contol transfer micro-steps and memory reference micro-steps should be kept in the left-half of the pair wherever possible.

One restriction is inherent in the micro-pair structure. Since the "P" register contains the location of each *pair*, it is possible to transfer control only to a left-half microstep. While this restriction might indicate that many "no-op" micro-steps would be required, programmer ingenuity can keep them to a minimum.

One consequence of the micro-pair structure should be mentioned. Conditional-test micro-steps exhibit a different response according to whether they are located in the left- or the right-hand side of a micro-pair. If the conditional test micro-step is located in the left-half of a micro-pair and if the condition being tested is met, the right-hand micro-step is executed as written. If the condition is not met, the right-hand micro-step is not executed. However, if the conditional-test micro-step is in the right-half position, the next complete micro-pair will be executed as written if the condition is met, or it will be skipped if the condition is not met.

## THE REGISTERS

The working registers are shown in diagram form in Figure 2. All of the registers shown are directly addressable with the exception of E, the micro-pair command register. The dotted lines indicate portions of a register which are not actually present in hardware; reference to such a region has the same effect as if the register contained all zeroes in those bit positions. The Q register is all empty; it may be considered as a register permanently containing zeroes.

The working registers consist of the A, B, C, and D registers of 24 bits each, the N register consisting of 8 bits, the L register (15 bits in length), three carry toggles, 6 "program flags" (which are addressable 1 bit registers), and a parity toggle. Not shown in Figure 2 are those elements which are available on the computer console (6 sense-switch toggles, address switches representing a 15 bit address, and another set of switches representing a full 24 bit word). These elements can be referenced by the programmer (as can various input-

|               |                            |                      | Reg.<br>Name     | Reg.<br>Numbe | er Use                                                               |

|---------------|----------------------------|----------------------|------------------|---------------|----------------------------------------------------------------------|

| 0 1 2 3 4 5 6 | 7 8 9 10 11 12 13 14 15 16 | 17 18 19 20 21 22 23 | A                | 1             | Arithmetic Register                                                  |

|               |                            |                      | В                | 2             | Arithmetic Register                                                  |

|               |                            |                      | С                | 3             | Arithmetic Register                                                  |

|               |                            |                      | D                |               | Arithmetic Register and Macro-Instruction<br>Interpretation Register |

|               | 9                          | 23                   | L                |               | Macro-Program Location Counter or General<br>Address Register        |

|               | 9                          | 23                   | Р                | 7             | Logic Level Location Counter                                         |

| [1            | 8                          |                      | N                | 6             | Repeat Count Register or Exponent Register                           |

|               |                            |                      | Q                | 0             | Phantom Register                                                     |

| 0             | 11 12                      | 23                   | E                | _             | Micro-Pair Command Register (Not Addressable)                        |

| 01            | 9                          |                      | CARRY<br>TOGGLES |               | Indicate Carry from Bit Positions 0, 1, and 9                        |

|               |                            |                      | PROGRAM<br>Flags |               | Boolean (1 Bit) Registers                                            |

|               |                            |                      | PARITY<br>TOGGLE |               | Indicates parity of the last memory access microstep                 |

Figure 2. PB440 Register Configuration

| LEFT MICRO     | RIGHT MICRO       | Micro-steps are stored in pairs. Each micro-step occupies 12 bit positions.                                                                                                                 |

|----------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OP MOD         |                   | For some micro-steps the right-hand 6-bit field is treated as a unit, and is called the modifier field.                                                                                     |

| OP R1 R2       |                   | For other micro-steps the modifier field is used in two parts, R1 and R2. Each of these can address one register.                                                                           |

|                |                   | ATS FOR INSTRUCTION<br>ON AND ARITHMETIC                                                                                                                                                    |

| S MAGNITUE     | DE                | One data-word format consists of the sign position (bit 0) and magnitude (bit positions 1-23).                                                                                              |

| S EXPONENT FRA | CTION (MOST SIG.) | Floating-point data require two words. The sign position of the most significant word indicates the sign of the complete word. The other sign position is a second The other sign position. |

| S EXPONENT FRACTION (MOST SIG.) | Floating-point data require two words. The sign position of the most significant word indicates the sign of the complete word. The other sign position is unused. The exponent field (8 bits) is |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S FRACTION (LEAST SIGNIFICANT)  | always positive; excess—128 exponent convention is used to allow both positive and negative exponents.                                                                                           |

| MACRO-OP | Х    | ADDRESS | The D register allows special formats. One possible format for macro-instructions consists of                                                                           |

|----------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1       | MODE | C2      | an op-code, 7 index registers and an address. Special fields (like C1 and C2) can be used to address memory, and the bits of the mode field can be tested individually. |

| LOGICAL WORD | Many micro-steps operate on the full 24-bit word, called a logical word. |

|--------------|--------------------------------------------------------------------------|

|              | word, called a logical word.                                             |

Figure 3. PB440 Word Formats

output elements and devices) but are not considered in detail in this discussion of the registers.

In general, it is expected that most arithmetic and logical operations will be performed utilizing the A, B, C, and D registers. It is expected that the L register will be used as a macro-instruction location counter, though it should be emphasized that the design in no way restricts the use of any register (except, of course, for "P" and "E") to any particular function. Several micro-step operations reference specific registers, but, for the most part, the programmer is free to decide the function of the registers for himself.

The carry toggles are set by certain micro-steps automatically, and are designed to indicate carry-out from bit positions 0, 1, and 9. That is, a carry toggle is made true (or "1") if carry-out occurs from its bit position, or made false if no carry-out occurs. They may be set and tested individually as well. The 6 program flags may be set and tested at the discretion of the programmer, and their content, as well as the content of any other register, may be displayed on the console. The parity toggle contains the parity of the last executed memory access micro-step, and it may be referenced by the programmer.

The N register serves as a repeat counter for those micro-steps which are of a repetitive nature, such as multiplication, division, and shifting operations. It may also be used for other purposes when desired.

Figure 3 shows various word formats in diagram form. Various fields in the word have been labeled so that they may be referred to during the description of the individual micro-steps. It will be noted that the N register is located so that it can hold the "exponent" field of a floating-point format word. Also, the "fraction" portion of a floating-point format word consists of 15 bits and can also contain an address for reference to the memory system of the computer.

Several micro-steps reference only the D register which can be used to good effect as a macro-instruction command register. Any register may be shifted, but the N register should be shifted only after careful consideration of the net effect.

#### THE MICRO-STEPS

Figure 3 shows two possible formats for a micro-step. While many micro-steps utilize both the R1 and R2 fields to designate one of the registers, not all of them do so, and these 3 bit fields may have special meaning for certain of the micro-steps. In some cases the full 6 bit field, exclusive of the operation field, is used as a unit and reference to the register (or registers) is implied by the operation field.

In general, where the R1 and R2 fields are used to designate two registers, both fields may designate the same register. In some cases it is not meaningful to do this since no change results, but it is always permitted. For convenience, the individual micro-steps have been grouped in the descriptions below.

## **Memory Access Operations**

Memory accesses may refer to either main memory or to fast memory. "Load" micro-steps retrieve a full 24 bit word from memory, and "Store" operations place the full 24 bit word into the designated memory cell. Where a register is less than 24 bits in length the "missing" portion will always store zeroes into memory in those bit positions.

When main memory is referenced for a load operation, 2 clock pulses are required to read the content of the memory cell into the designated register. Following the main memory access, 3 clock pulses are required to establish (or re-establish) the content of the memory cell. This time may be used for useful computing, and is referred to as "shadow time". Should a reference to main memory be made during this three clock-pulse interval, the computer will wait until the previous cycle is completed.

When main memory is referenced for a store operation, the computer is immediately ready for useful computing. However the full memory cycle time must elapse before another memory reference can be made. Therefore since the store operation requires a single clock pulse, the "shadow time" is 4 clock pulses, and if another main memory reference is made during this time the computer will wait until the previous cycle is completed. It is the programmer's responsibility to utilize the "shadow time" effectively if he can. Since fast memory read-out is non-destructive, no "shadow time" results from a fast memory access. The amount of time lost in storing into fast memory (no computing is possible until such an operation is completed) is 8 microseconds. This operation should probably be avoided if maximum speed is desired.

Each individual module of main memory has its own read-write circuitry, so that reference to module 2 may, if desired, be made during the "shadow time" resulting from a reference to module 1, with no penalty in execution speed.

In the micro-steps described below, the R1 field designates a register which contains an address. The low order 15 bits of this register (bit positions 9-23) are used as the address; the high-order bits are ignored. The carry toggles are not affected unless specifically stated in the description. The parity toggle is set to 1 if the

number of 1's in the word is even, or to 0 if the number of 1's is odd.

Description

Mnemonic

Meaning

| LDM R1 R2 | Load from<br>Memory                    | The content of the memory cell, designated by the address in register R1, replaces the content of the register designated by R2.                                                                                                                                                                                                                                                                                                                                                          |

|-----------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STM R1 R2 | Store into<br>Memory                   | The content of the register designated by R2 is stored into the memory cell designated by the address in R1. The content of R1 and R2 remains unchanged.                                                                                                                                                                                                                                                                                                                                  |

| LDI R1 R2 | Load (from<br>memory) and<br>Increment | The content of the addressed memory cell replaces the content of the register designated by R2. Simultaneously, the address in register R1 is incremented by 1 in bit position 23. This latter operation does not change the setting of the carry toggles. When R1 and R2 designate the same register the content of the addressed memory cell and the incremented value of the designated register are combined (logical or), and the logical sum replaces the content of that register. |

| STI R1 R2 | Store and increment                    | The content of the register designated by R2 is stored into the                                                                                                                                                                                                                                                                                                                                                                                                                           |

The content of the register designated by R2 is stored into the addressed memory cell. Simultaneously, the address in R1 is incremented by 1 in bit position 23. This latter operation does not change the setting of the carry toggles. If R1 and R2 designate the same register, the memory cell will contain its own address and R1 will contain the logical sum of the address and its incremented value at the end of the operation.

It is clear that the above micro-steps can refer to any memory cell in the computer, but an address for that cell must be present in one of the registers. (Designating Q or N by the R1 field can refer only to main memory location 00000. This should probably be avoided.) Since many common operations involve the requirement that the content of some register be stored temporarily, a group of 8 cells in main memory has been designated as "working storage". These may be referred to directly, without the requirement that an address be provided. The following two micro-steps

reference these cells. The R1 field designates which one of the 8 cells is to be used, and *does not* designate a register.

| Mnemonic  | Meaning    | Description                        |

|-----------|------------|------------------------------------|

| LDW R1 R2 | Load from  | The content of the working         |

|           | Working    | storage cell designated by R1 re-  |

|           | Storage    | places the content of the register |

|           |            | designated by R2. The content      |

|           |            | of the designated memory cell      |

|           |            | remains unchanged.                 |

| STW R1 R2 | Store into | The content of the register des-   |

|           | Working    | ignated by R2 is stored into the   |

|           | Storage    | designated working storage cell.   |

|           |            | The content of the register desig- |

|           |            | nated by R2 remains unchanged.     |

# LDS and STS-Load Special and Store Special

In addition to the above, two special micro-steps have been provided which reference certain fixed locations in memory. In these micro-steps the R1 field is used as a control field to designate which one of eight possible load or store operations is desired. In all of the operations, the effective address of the cell is constructed from a designated field of the D register.

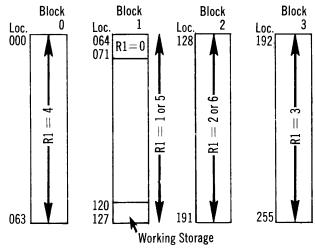

The first portion of main memory is divided into blocks of 64 words each, numbered, for reference, blocks 0-3. Seven of the 8 possible configurations of R1 reference this portion of memory while the eighth configuration references fast memory according to the following scheme:

| R1 | Portion of D Used        | Memory Block Referenced                                                       |

|----|--------------------------|-------------------------------------------------------------------------------|

| 0  | Bits 6-8<br>(mode-field) | Block 1, cells 00-07<br>(Locations 64-71)                                     |

| 1  | Bits 18-23               | Block 1, cells 00-63<br>(Locations 64-127)                                    |

| 2  | Bits 18-23               | Block 2, cells 00-63<br>(Locations 128-191)                                   |

| 3  | Bits 18-23               | Block 3, cells <b>00-63</b><br>(Locations 192-255)                            |

| 4  | Bits 0-5                 | Block 0, cells 00-63<br>(Locations 00-63)                                     |

| 5  | Bits 0-5                 | Block 1, cells 00-63<br>(Locations 64-127)                                    |

| 6  | Bits 0-5                 | Block 2, cells 00-63<br>(Locations 128-191)                                   |

| 7  | Bits 0-5                 | Fast memory cells 28864 to 28927 (last 64 cells in 1st module of fast memory) |

The portions of main memory referenced by R1 configurations 0-6 may be visualized by the following representation of memory module 1:

#### **MEMORY MODULE 1**

(MAIN MEMORY)

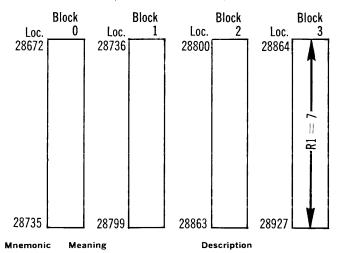

The portion of fast memory referenced by R1 configuration 7 may be visualized by the following representation of memory module 8:

#### **MEMORY MODULE 8**

(FAST MEMORY)

LDS R1 R2 Load Special

An address is constructed from the content of portions of the D register, as designated by R1. The content of the addressed cell replaces the content of the register designated by R2.

STS R1 R2 Store Special

An address is constructed from the content of portions of the D register, as designated by R1. The content of the register designated by R2 is stored in the addressed memory cell. The content of the register designated by R2 remains unchanged.

Several useful operations can be performed simply and easily by means of these micro-steps. For example, any arbitrary 6-bit character code can be converted into any other code by having available a table of the replacement code, arranged in the proper order, in memory. When one character of the alien code is obtained it is placed in the D register, say in bit positions 18-23. A single micro-step, e.g., "LDS 3 D" will replace the character with one chosen from the table in memory block 3. Another extremely important operation involves branching to one of 64 possible microutines on the basis of a macro-instruction operation code. If this code is located in, say, positions 0-5 of the D register, and a table of microutine starting locations is located in memory block 0, then execution of the micro-step "LDS 4 P" will cause the desired branch of control. If a faster branch is desired, in which fast memory is used for the "jump table" (located in the last 64 words of the first 256-word block of fast memory) the micro-step "LDS 7 P" will effect the control transfer.

It should be clear that memory location assignments for macro-instructions must take into account those main memory locations actually used by the instruction set, including working storage. It is expected that normal operation will involve using the first 64 words of main memory (Block 0) as a "jump table" for rapid macro-instruction interpretation, and that Block 1 will be used for index registers and, possibly, Block 1, 2, or 3 to replace the character set obtained from input devices with one more amenable to programming use.

#### **Logical Word Operations**

A rather complete set of operations is provided for the manipulation of a 24-bit word, called a logic word. In all of the following operations all 24 bit positions take part in the operation; where registers of less than 24 bits in length are involved, the "missing" portions take place as if they contained zeroes. In all of these micro-steps R1 and R2 designate registers, and in all cases the result of the operation appears in the register designated by R2. The carry toggles are not affected unless specifically stated in the description.

| Mnemonic  | Meaning      | Description                        |

|-----------|--------------|------------------------------------|

| CPL R1 R2 | Copy Logical | The content of the register des-   |

|           |              | ignated by R1 replaces the con-    |

|           |              | tent of the register designated by |

|           |              | R2. The content of register R1     |

|           |              | remains unchanged. If both R1      |

|           |              | and R2 designate the same reg-     |

|           |              | ister, no change is observed.      |

| CCL R1 R2 | Conv         | The content of the register des    |

CCL R1 R2 Copy The content of the register des-Complement ignated by R1 is complemented Logical (1's complement) and this result

| Mnemonic                     | Meaning                          | Description                                                                                                                                                                                                                          | Mnemonic                                         | Meaning                                                | Description                                                                                                                                                                                                                                    |

|------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                                  | replaces the content of the register designated by R2. The content of register R1 remains unchanged unless it is the same register that is designated by R2.                                                                         |                                                  |                                                        | designated words, and the result<br>replaces the content of the regis-<br>ter designated by R2. The result<br>has a 1 in any bit position where<br>one word had a 1 and the other<br>did not; in bit positions where                           |

| CIL R1 R2                    | Copy and<br>Increment<br>Logical | A 1 at bit position 23 is added<br>to the content of the register des-<br>ignated by R1, and this result<br>replaces the content of the regis-<br>ter R2. All three carry toggles are<br>set by this operation; they will be         |                                                  |                                                        | both words contained a 1, or both contained a 0, the result is 0. Note that if R1 and R2 designate the same register, the result is an all-zero register.                                                                                      |

|                              |                                  | set to 0 if no carry-out passes<br>their bit position, and will be set<br>to 1 if such a carry is present.<br>Register R1 remains unchanged<br>unless it is also designated by R2.                                                   | ADL R1 R2                                        | Add Logical                                            | The arithmetic sum of the two designated registers replaces the content of the register designated by R2. All three carry toggles are set by this operation. Register R1 remains unchanged unless it is                                        |

| CDL R1 R2                    | Copy and<br>Decrement<br>Logical | An internally generated word, consisting of 24 1's, is added to the content of the register designated by R1. This result replaces the content of register R2. The net effect is the same as if a 1 at                               |                                                  |                                                        | the same register designated by R2. In this case the result is identical with that obtained by shifting the content of the register left 1 position.                                                                                           |

|                              |                                  | bit position 23 had been subtracted from the content of R1. The carry toggles are <i>not</i> set by this operation, and register R1 remains unchanged unless it is also designated by R2.                                            | ALC R1 R2                                        | Add Logical<br>for Carry                               | The three carry toggles are set<br>by this operation, based on<br>whether or not a carry-out would<br>occur at their bit position if the<br>contents of the two designated<br>registers were added together<br>arithmetically. The contents of |

| EXC R1 R2                    | Exchange                         | The contents of the two regis-<br>ters designated are exchanged. It<br>doesn't matter which of the two                                                                                                                               |                                                  |                                                        | the registers designated by R1 and R2 remain unchanged.                                                                                                                                                                                        |

|                              |                                  | is designated by R1 and which by R2; the result is the same. If R1 and R2 designate the same register, no change is observed.                                                                                                        | SLS R1 R2<br>or<br>SL6 R1 R2                     | Shift Left<br>Six                                      | The content of the register designated by R1 is shifted left 6 bit positions, end-around, and the result replaces the content of the                                                                                                           |

| AND R1 R2<br>or<br>EXT R1 R2 | And<br>Extract                   | The logical product of the con-<br>tents of the two registers replaces<br>the content of the register desig-                                                                                                                         |                                                  |                                                        | register designated by R2. The content of register R1 remains unchanged unless it is also desig-                                                                                                                                               |

| LXI KI KZ                    | LATIACT                          | nated by R2. The result has a 1 only in those bit positions where                                                                                                                                                                    | Partial-V                                        | Word Ope                                               | nated by R2. rations                                                                                                                                                                                                                           |

|                              |                                  | both words contained a 1. The content of R1 is unchanged.                                                                                                                                                                            |                                                  |                                                        | -steps reference certain portions of operate only on that portion. The                                                                                                                                                                         |

| LOR R1 R2                    | Logical Or                       | The logical sum of the contents of the two registers replaces the content of the register designated by R2. The result has a 1 in any bit position where either of the words contained a 1. The content of register R1 is unchanged. | remainder<br>tion. As<br>designates<br>nates the | of the word<br>with the loss one of the<br>other, with | d remains unchanged by the opera- gic word format micro-steps, R1 addressable registers and R2 desig- a the result appearing in R2. The affected unless the description so                                                                     |

| XOR R1 R2                    | Exclusive Or                     | The logical operation "exclusive or" is performed on the two                                                                                                                                                                         | CPS R1 R2                                        | Copy Sign                                              | The sign position (bit 0) of the register designated by R1 re-                                                                                                                                                                                 |

|                              |                                  |                                                                                                                                                                                                                                      |                                                  |                                                        |                                                                                                                                                                                                                                                |

Mnemonic Meaning Description

places the sign position of the register designated by R2. The remainder of register R2 remains unchanged. Register R1 is not affected by this operation. If R1 and R2 designate the same register no change is observed.

CCS R1 R2 Copy

Sign

The sign position of register R1 Complement is copied into the sign position of R2 in complemented form. If the sign of register R1 were positive (contained a zero) then the sign position of register R2 will be negative (will contain a 1) after the operation. If R1 and R2 designate the same register, the net effect is to change the sign of that register.

ADS R1 R2 Add Signs

The sign position of register R1 is added to the sign position of register R2, the result replacing the sign of register R2. Carry toggle 0 will be set by this operation. It will be on (will contain a 1) if the sign of both designated registers contained a 1, and will contain a zero (be set off) otherwise. The sign of register R1 is unchanged unless it is also designated by R2.

These three micro-steps give the programmer complete control over the sign positions of registers "A", "B", "C", and "D", the only registers whose sign position is actually present. Reference may be made to the other registers, particularly in the R1 field of the micro-step, where this might be useful. Remembering that any "missing" portion of a register may be thought of as containing zeroes, the micro-step "CPS N A" will set the sign of the "A" register positive. Similarly, "CCS L B" will set the sign of "B" negative. The sign position of a register may be "preserved" (in carry toggle 0) by the micro-step "ADS C C". The result of this operation will leave the sign of the "C" register zero, and carry toggle 0 will be on only if the original content of the sign position was a 1 (was negative).

It should also be noted that, "ADS A D" will leave the sign of the "D" register in a state which indicates whether it was the same as the sign of the "A" register or not. If the signs of "A" and "D" were both positive, or were both negative, the D register sign will be positive following the operation. It will be negative otherwise. This operation corresponds to the logical operation of "exclusive or", applied only to the sign positions of the two registers. The micro-step "CCS B B" will, of course, reverse the sign of the "B" register.

Mnemonic Meaning Description

CPM R1 R2 Copy

Magnitude

The magnitude field (bits 1-23) of the register designed by R1 replaces the same field of the register designated by R2. The sign position of the R2 register remains unchanged. If both R1 and R2 designate the same register, no change is observed.

CCM R1 R2 Copy

Magnitude

The magnitude field of the reg-Complement ister designated by R1 is complemented (1's complement) and this result replaces the same field of the register designated by R2.

ADM R1 R2 Add Magnitude

The magnitude field of the register designated by R1 is added to the magnitude field of the register designated by R2. This result replaces the magnitude field of the R2 register. The sign position of the R2 register is not affected. Carry toggles 1 and 9 are both set by this operation, but carry toggle 0 is not affected. If R1 and R2 designate the same register, the result will be the same as a magnitude left-shift of 1, with carry toggle 1 indicating the value of the bit "shifted off".

AMK R1 R2 Add Magnitude with Carry-in

The magnitude field of the register designated by R1 is added to the magnitude field of the register designated by R2, and, at the same time, the content of carry toggle 1 is added into bit position 23 of the sum. Carry toggles 1 and 9 are set by this operation, but carry toggle 0 is not affected.

The micro-steps described above allow the computer to perform arithmetic computations using data words arranged in a "sign-and-magnitude" format, providing the sign of the sum is determined separately and is inserted into the sign position of the proper register. Double-precision addition in this format is particularly easy providing the format does not require that the sign position of the least significant word be used. For example, if the "A" and "B" registers contain one doubleprecision data word and the "C" and "D" registers contain the other, the micro-sequence

# ADM D B AMK C A

places the double-precision sum in the A and B registers. In the case of differing signs, the programmer must expand this sequence to perform the complement operation on the proper words, and to establish the sign of the result.

Certain of the micro-operations have been chosen to allow rapid manipulation of double-precision data words in a particular format; this format is shown in Figure 3 and is designated the "floating-point format". It should not be assumed that the format shown is the only possible one which can be implemented on the computer; it is one whose execution times will be particularly short. The micro-steps described below reference the "exponent" and "fraction" fields of the floatingpoint format. It should be noted that the "fraction" field of 15 bits is also a convenient field for an address in a macro-instruction word, and the micro-steps dealing with this field can also be used to single out the address field when it corresponds.

Description

of the register designated by R2.

Mnemonic

Meaning

| CPX R1 R2 | Copy<br>Exponent                  | The exponent field of the register designated by R1 replaces the exponent field of the register designated by R2. Bit 0 and the bit field 9-23 of the R2 register are not affected by this operation. The exponent field in any register may be set to zero selectively if the R1 field references a register whose exponent field is not present (is permanently zero). |

|-----------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCX R1 R2 | Copy<br>Complement<br>Exponent    | The exponent field of the register designated by R1 is complemented (1's complement) and the result replaces the exponent field of the register designated by R2. If R1 references a register whose exponent field is permanently zero, and R2 designates a full 24-bit register, the exponent field in the latter register is set to all 1's.                           |

| CIX R1 R2 | Copy and<br>Increment<br>Exponent | A 1 at bit position 8 is added<br>to the exponent field of the reg-<br>ister designated by R1, and the<br>result replaces the exponent field                                                                                                                                                                                                                             |

**Mnemonic** Meaning Description Carry toggle 1 is set by this operation, and will contain a 1 only if the original exponent field of the R1 register contained all 1's. Carry toggles 0 and 9 are not affected by this operation. ADX R1 R2 Add The exponent field of the reg-**Exponents**

CPF R1 R2

AFK R1 R2

Add

Carry-in

Copy

Fraction

ister designated by R1 is added to the exponent field of the register designated by R2, and the sum replaces the exponent field of the R2 register. Carry toggle 1 is set by this operation; the other carry toggles are not affected.

The fraction field (bits 9-23) of the register designated by R1 replaces the fraction field of the register designated by R2. Bits 0-8 of the R2 register are not affected by this operation. The fraction field in any register may be set to zero if the R1 field references a register whose fraction field is not present.

CCF R1 R2 Copy The fraction field of the regis-Complement ter designated by R1 is comple-Fraction mented (1's complement) and the result replaces the fraction field of the register designated by R2. If R1 references a register whose fraction field is permanently zero, the fraction field in the register referenced by R2 is set to all 1's.

ADF R1 R2 Add The fraction field (bits 9-23) of the register designated by R1 Fraction is added to the fraction field of the register designated by R2, and the result replaces the fraction field of the R2 register. Carry toggle 9 is set by this operation; the other carry toggles are not affected.

The fraction field of the regis-Fraction with ter designated by R1 is added to the fraction field of the register designated by R2, and, at the same time, the content of carry toggle 1 is added into bit position 23 of the sum. Carry toggle 9 is set by this operation; the other carry toggles remain unchanged. Mnemonic Meaning Description

The resulting sum replaces the fraction field of the R2 register; bit positions 0-8 of the R2 register remain unchanged.

An additional micro-step, which might be included in this group, is the one designated "SFR—Shift Floating Right". Since it is somewhat specialized, and involves the use of the N register for repeat-counting, its description will be deferred until the discussion of the other shift operations.

# CLN and CLD—Copy Literal to N and Copy Literal to D

Several "copy" operations of a specialized nature are possible utilizing micro-steps of this type. Some of these are described under "Transfer of Control", since this is the effect obtained. Another two micro-steps provide the same function, but reference different registers.

The term "Literal" is used in these micro-steps to designate that the operand is contained in the modifier field of the micro-step.

| Mnemonic | Meaning                | Description                                                                                                                                                                                                                                                              |

|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLN M    | Copy Literal<br>to N   | The Modifier field of this micro-step, treated as a single 6-bit                                                                                                                                                                                                         |

| or       |                        | unit, is copied into bit positions                                                                                                                                                                                                                                       |

| LRC M    | Load Repeat<br>Counter | 3-8 of the N register. Bit positions 1 and 2 of the N register are set to zero by this operation. This micro-step provides a simple way of initializing the "N" register for repeated operations such as multiplication, division, and the various shifting micro-steps. |

| CLD M    | Copy Literal<br>to D   | The modifier field of this micro-step, treated as a single 6-bit unit, is copied into bit positions 18-23 of the "D" register. Bit positions 0-17 are set to zero by this operation.                                                                                     |

# CFS and CTS—Copy from Special and Copy to Special

This pair of micro-steps is provided primarily for the purpose of program interrupt operation. They allow the programmer to record into the designated register the contents of the various toggles for storage into main memory, and provide the facility of retrieving this information after the interrupt operation is complete and restoring the original state of the toggles. Included as well is the facility for setting special (optional) registers connected with high-speed input-output devices. It is

also possible to set an information pattern into any class of toggle, or into all three classes together.

In these micro-steps, the R1 field designates the class, or classes, of device which is to be referenced, according to the following table:

| R1 | Items Referenced                      |

|----|---------------------------------------|

| 4  | All Carry Toggles                     |

| 5  | All Interrupt Masks                   |

| 6  | All Program Flags                     |

| 7  | All Toggles (Items 4, 5, and 6 Above) |

The R2 field is used to designate a register which either receives the information from the various items, or provides the information for setting the items referenced by the R1 field. By convention, the various classes of toggles are copied to or from the following register bit positions:

- 1. Carry toggles 0, 1, and 9 correspond to register bit positions 9-11.

- The interrupt masks correspond to register bit positions 14-17.

- 3. The program flags correspond to register bit positions 18-23.

| 10115 10 20.          |                                 |                                                                                                                                                                                                                                                                                                                            |

|-----------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic<br>CFS R1 R2 | Meaning<br>Copy from<br>Special | The information contained in the item, or items, designated by R1 is copied into the register designated by R2. If the information does not occupy the complete                                                                                                                                                            |

|                       |                                 | register, the "unused" portions of<br>the register are set to zero. Where<br>toggles are designated by R1, if<br>the toggle is in the <i>on</i> , or <i>true</i> ,<br>state, the register bit position cor-<br>responding will be set to 1. If the<br>toggle is off (false state) the bit<br>position will be set to zero. |

| CTS R1 R2             | Copy to<br>Special              | The information contained in<br>the register designated by R2 is<br>copied into the item, or items,<br>designated by R1, where such an<br>operation is possible.                                                                                                                                                           |

# **Shifting Operations**

All shifting operations are performed in a repeated fashion (with the exception of the "SLS—Shift Left 6" micro-step) and utilize the "N" register for counting purposes. Execution proceeds at a rate of 1 clock pulse per bit shifted (a shift of either zero or 1 position requires 1 clock pulse). For the direct-shift micro-steps, the programmer must initialize the "N" register prior to

execution of the shift micro-step. A count may be copied into the "N" register from some other register; it may be loaded from memory, or may be inserted by means of the "LRC—Load Repeat Count" micro-step. Execution of the direct-shift micro-steps will repeat until the "N" register is "counted down" to zero. The carry toggles are not affected by these micro-steps.

# SSL and SDL—Shift Single Length and Shift Double Length

These two micro-steps utilize the R1 field to designate the type of shifting operation desired. To simplify discussion, the three bit positions of the R1 field are called bits A, B, and C. In these two micro-steps they are given the following meanings:

| Bit          | Value | Description                                                         |

|--------------|-------|---------------------------------------------------------------------|

| A            | 0     | Shift Left                                                          |

| A            | 1     | Shift Right                                                         |

| В            | 0     | Closed (End-Around) Shift                                           |

| В            | 1     | Open Shift                                                          |

| С            | 0     | Magnitude Shift (sign position does not take part in the operation) |

| $\mathbf{C}$ | 1     | Logical Shift (sign position is shifted)                            |

When an "open" shift is indicated, the vacated positions of the register are set to zero, and the bits "shifted off" are lost. The "N" register will always contain zeroes after the execution of a direct-shift operation.

| Mnemonic  | Meaning                | Description                                                                                                                                                                                                                                                                                                                                             |

|-----------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSL R1 R2 | Shift Single<br>Length | The content of the "N" register is examined. If it is initially zero, no operation takes place. If it is non-zero, the content of the register designated by R2 is shifted one bit position in the manner specified by R1, and the content of the "N" register is decremented by 1. This process is repeated until the "N" register is reduced to zero. |

|           |                        |                                                                                                                                                                                                                                                                                                                                                         |

SDL R1 R2 Shift Double Length

The coupled contents of the "A" and "B" registers, treated as a single double-length register, are shifted in the manner designated by R1. The R2 field of this micro-step is not used. The "N" register is decremented by 1 for each bit position shifted. The operation is repeated until the "N" register is reduced to zero.

## SFR—Shift Floating Right

This micro-step is provided to facilitate certain floating-point operations:

| Mnemonic  | Meaning        | Description                        |

|-----------|----------------|------------------------------------|

| SFR R1 R2 | Shift Floating | The contents of the fraction       |

|           | Right          | field of the "A" register and the  |

|           |                | magnitude field of the "B" regis-  |

|           |                | ter are treated as a single, ex-   |

|           |                | tended-length register and are     |

|           |                | shifted right until the content of |

|           |                | the "N" register is reduced to     |

|           |                | zero. Zeroes fill the vacated por- |

|           |                | tion of the "A" register, and bits |

|           |                | shifted beyond position 23 of the  |

|           |                | "B" register are lost. The R1 and  |

|           |                | R2 fields are not used. The sign   |

|           |                | and exponent fields of the "A"     |

|           |                | register and the sign position of  |

|           |                | the "B" register are unaffected.   |

#### SLC—Shift Left and Count

Although designed primarily as an aid to manipulations involving normalized floating-point numbers, this micro-step can be utilized for various types of logical operations as well. The magnitude field of the "B" register, and designated portions of the "A" register, are treated as a single extended-length register for this operation. The R1 field of the micro-step serves two functions: It designates which portions of the "A" register are to be involved in the shifting operation, and also indicates which bit position, or positions, are to be examined for termination of the shifting process. The R2 field is not used.

The shifting operation is always a left shift, and is repeated until one of the bit positions designated for examination contains a 1. There are circumstances in which this operation will not terminate, and it is the programmer's responsibility to see that they do not occur. For each bit position shifted the "N" register is decremented by 1, but the "N" register is not examined by the process; it terminates only when one of the designated bit positions of the "A" register is non-zero.

The effect obtained from the various possible configurations of the R1 field can best be seen by reference to a table. The letters "S", "X", and "F" are used to designate the sign field, the exponent field, and the fraction field respectively. Where more than one letter appears it indicates that the designated fields take part in the shift; absence of a letter or letters indicates that the fields do not take part in the operation. The R1 field is shown in binary format.

| R1        | Portion of<br>"A" Shifted | Bit Positions of "A" Examined      |

|-----------|---------------------------|------------------------------------|

| 000       | F                         | None. This will not terminate      |

| 001       | $\mathbf{F}$              | Position 9 only                    |

| 010       | XF                        | Position 1 only                    |

| 011       | XF                        | Positions 1 and 9                  |

| 100       | SXF                       | Position 0 only                    |

| 101       | SXF                       | Positions 0 and 9                  |

| 110       | SXF                       | Positions 0 and 1                  |

| 111       | SXF                       | Positions 0, 1 and 9               |

| Mnemonic  | Meaning                   | Description                        |

| SLC R1 R2 | Shift Left                | The coupled contents of the        |

|           | and Count                 | magnitude field of the "B" regis-  |

| or        |                           | ter and designated portions of the |

| FLC R1 R2 | Float Left                | "A" register are treated as a sin- |

|           | and Count                 | gle extended-length register and   |

|           |                           | are shifted left until one (or     |

|           |                           | more) of the bit positions of "A"  |

|           |                           | designated for examination con-    |

|           |                           | tains a 1. The content of "N" is   |

decremented by 1 for each bit

position shifted. The sign position

of "B" and portions of "A" not

designated for shifting remain

unchanged. Vacated portions of

"B" are set to zero.

# **Multiplication and Division**

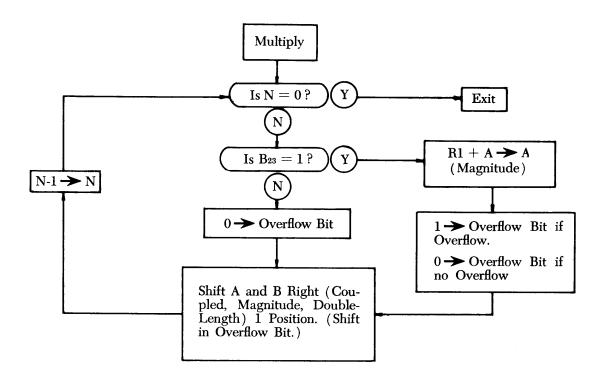

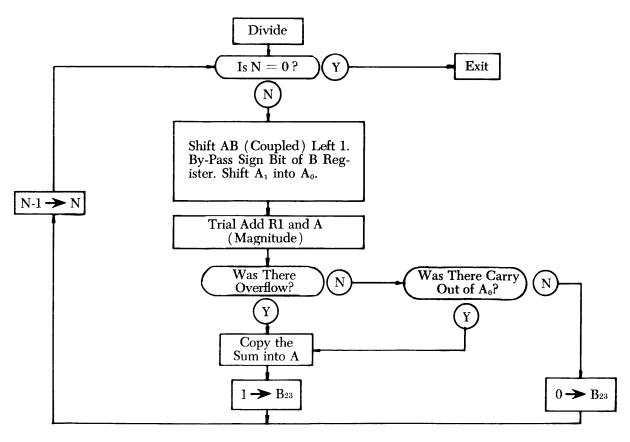

Two micro-step operations are provided which can greatly simplify the arithmetic operations of multiplication and division; in many cases they are sufficient in themselves to provide this function. They are both repeated micro-steps, and the programmer must specify, by establishing the proper count in the "N" register, how many times they are to be repeated. The multiplication operation (MPS—Multiply Step) requires 1 clock time per step of its execution, while divide step (DVS) requires 2. The operation of each is perhaps best explained by means of a flow chart (Figure 4). The conditions which must be established by the programmer prior to the execution of MPS are as follows:

- 1. The multiplier is loaded into the "B" register.

- 2. The multiplicand is loaded into the register designated by R1 (normally the "C" or "D" register).

- 3. The repeat count is loaded into the "N" register.

- 4. If the result is to be a simple double-length product the "A" register must be set to zero. If it is not zero, its content will be added into the least significant bit positions of the double-length product.

Assuming the "N" register contains "23" at the start of the operation, indicating that the multiply step operation is to be executed 23 times, the results will be as follows:

- 1. The "A" register will contain the most significant bits of the product in bit positions 1-23. Bit position 0 of the "A" register does not take part in the operation and remains unaffected.

- 2. The "B" register will contain the least significant half of the double-length product in bit positions 1-23. Bit position 0 of the "B" register does not take part in the operation and is unaffected.

- 3. The "N" register will contain all zeroes.

- 4. The contents of all the other registers (except, perhaps, "P") remain unaltered.

This multiplication algorithm has many advantages which may not be obvious from casual inspection. First of all, the sign of the product can be established in the single micro-step "ADS". For integer multiplication (where the least significant bit is located in bit position 23) the multiplicand is loaded into the "B" register, "A" is set to zero (if no addition is to take place) and the "MPS" micro-step is executed 23 times. The integer product will appear in the "B" register, and overflow will be indicated by a non-zero "A" register. In this case, the sign of the product would be established in the "B" register, either before or after the operation.

Again, dealing with integers, a repeated multiply step operation can give the result B = BC + A, where the letters designate the registers involved, and the "=" sign indicates that the result appears in "B". As before, a non-zero "A" register indicates overflow.

The divide-step algorithm, shown in flow chart form in Figure 4, has similar advantages. Prior to execution of the DVS operation the programmer must establish the following conditions:

- 1. The most significant half of the dividend must be in the "A" register in bit positions 1-23. The sign bit of "A" is unimportant, but will be destroyed in the process.

- 2. The least significant half of the double-length dividend must be in the "B" register, bit positions 1-23. The sign position of the "B" register does not take part in the operation, and may contain the pre-established sign of the quotient if desired.

- 3. The divisor, in 2's complement form, must be in bit positions 1-23 of the "C" or "D" register. The sign position of that register must contain a 1.

- 4. The repeat count must be in the "N" register.

Assuming the "N" register contains "23" at the start of the operation, indicating that the divide step opera-

Figure 4. Multiply and Divide Operations

tion is to be executed 23 times, the results will be as follows:

- 1. The quotient will appear in the "B" register in bits 1-23.

- 2. The remainder will appear in the "A" register, in bit positions 1-23. The sign of the "A" register will, in general, not mean anything; this can best be seen from the flow chart.

- 3. The "N" register will contain all zeroes.

- 4. The other registers (except, perhaps, "P") will be unchanged.

No automatic provision is made to detect a divideoverflow condition. This problem is left as an exercise for the programmer.

While it is, in theory, possible to designate some register other than "C" or "D" in using both MPS and DVS, this should be done with caution; in particular, designating "N" as the multiplicand will result in the multiplicand being decremented by one after each iteration. The two micro-steps use the same format as the others, except that the R2 field *must* designate the "A" register. Neither micro-step affects the carry toggles.

Mnemonic Meaning

MPS R1 A Multiply

Step

Description

The content of the register designated by R1 is multiplied by the content of the "B" register, and the double-length product appears in the magnitude fields of "A" and "B". The "N" register must initially contain the number of multiplication iterations desired. The sign positions of the "A" and "B" registers are not affected. The prior content of the "A" register is added into the least significant bit positions of the double-length product. The "N" register will contain all zeroes.

DVS R1 A Divide Step

The content of the coupled "A" and "B" registers, treated as containing (in their magnitude fields) a double-length dividend, is divided by the content of the register designated by R1. This latter register must contain the divisor in 2's complement form, and the "N" register must initially contain the number of divide iterations desired. Following execution, the quotient replaces the magnitude field of the "B" reg-

Mnemonic Meaning

Description

ister, and the remainder replaces the magnitude field of the "A" register. The sign of the "B" register is unaffected, but the sign of the "A" register is destroyed. The "N" register will contain all zeroes.