# TRANSAC S-2000 SYSTEM DESCRIPTION

January 1958

PHILCO CORPORATION

GOVERNMENT AND INDUSTRIAL DIVISION

Philadelphia, Penna.

### TRANSAC S-2000 SYSTEM DESCRIPTION

### TABLE OF CONTENTS

|    |     |                                               | Page |

|----|-----|-----------------------------------------------|------|

| 1. | INT | RODUCTION                                     | 1    |

| 2. | TRA | ANSAC S-2000 SYSTEM                           | 3    |

| 3. | CON | MPUTING AND CONTROL UNIT                      | 6    |

|    | 3.1 | Arithmetic Operation                          | 6    |

|    | 3.2 | Speed of Arithmetic Operation                 | 6    |

|    | 3.3 | Programming Operations                        | 9    |

|    | 3.4 | Addressing and Index Registers                | 10   |

|    | 3.5 | Computer Instructions                         | 10   |

| 4. | MAC | GNETIC CORE STORAGE UNIT                      | 19   |

|    | 4.1 | Expanding the Magnetic Core Storage           | 19   |

|    | 4.2 | Magnetic Core Storage Control                 | 19   |

| 5. | ON- | LINE INPUT-OUTPUT EQUIPMENT                   | 20   |

|    | 5.1 | Magnetic Tape System                          | 20   |

|    | 5.2 | Magnetic Drum Unit                            | 31   |

|    | 5.3 | On-Line Punch Card System                     | 34   |

|    | 5.4 | The Paper Tape System                         | 35   |

|    | 5.5 | Console Typewriter                            | 38   |

| 6. | OFF | -LINE INPUT-OUTPUT EQUIPMENT                  | 39   |

|    | 6.1 | High Speed Printer                            | 39   |

|    | 6.2 | Card to Magnetic Tape - Magnetic Tape to Card |      |

|    |     | Converter                                     | 45   |

| 7. | PHY | SICAL DESCRIPTION                             | 49   |

|    | 7.1 | Circuit Construction                          | 49   |

|    | 7.2 | Modular Frame                                 | 54   |

|    | 7.3 | Computer                                      | 54   |

|    | 7.4 | Magnetic Core Storage Unit                    | 57   |

|    | 7.5 | Paper Tape Unit                               | 59   |

|    | 7.6 | Magnetic Tape Units                           | 64   |

|    | 7.7 | Magnetic Drum Storage Unit                    | 65   |

|    | 7.8 | High Speed Printer                            | 65   |

|    | 7.9 | Punch Card System                             | 67   |

#### APPENDICES

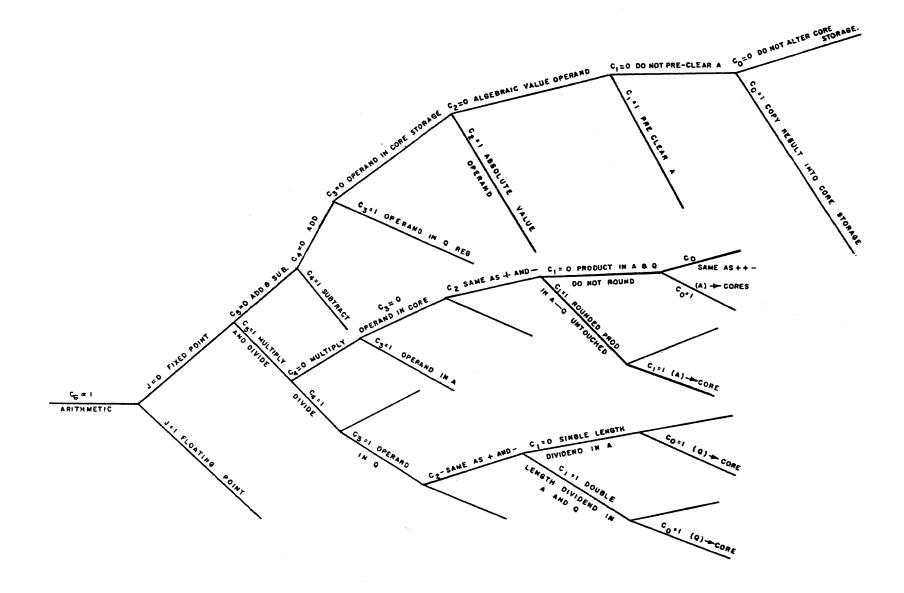

- A. TRANSAC S-2000 Command Code Construction

- B. Use of Index Registers in the TRANSAC S-2000

- C. TRANSAC S-2000 Word Construction and Usage

- D. TRANSAC S-2000 Product Line List and Unit Designation Code

### LIST OF ILLUSTRATIONS

| Figure No. |                                                                    | Page |

|------------|--------------------------------------------------------------------|------|

| 1.         | Typical Transac S-2000 System Layout (on Line Equipment)           | 5    |

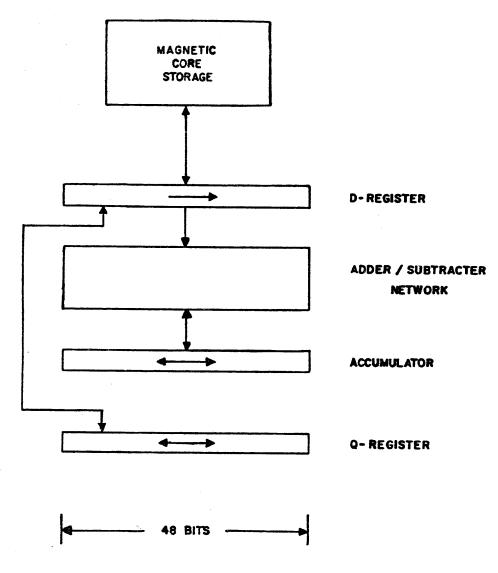

| 2.         | Block Diagram of Fixed Point Arithmetic Section                    | 7    |

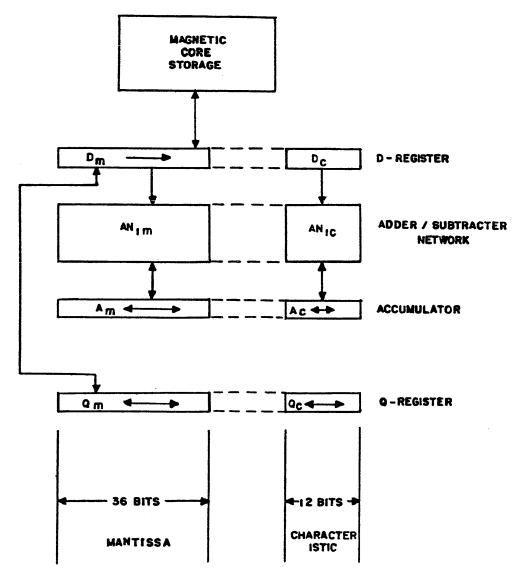

| 3.         | Block Diagram of Floating Point Arithmetic Section                 | 8    |

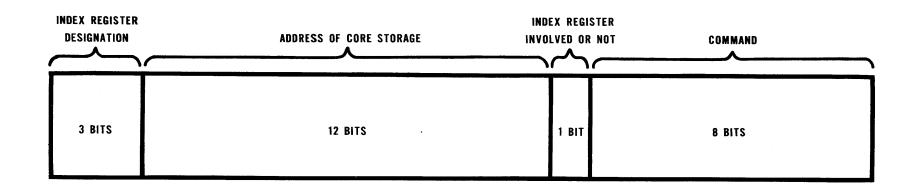

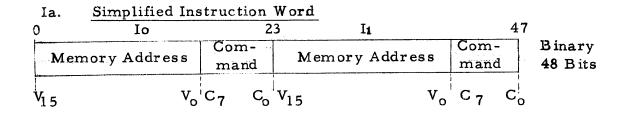

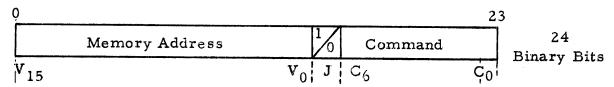

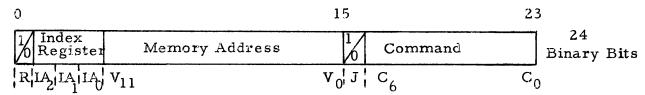

| 4.         | Computer Instruction Word Format                                   | 11   |

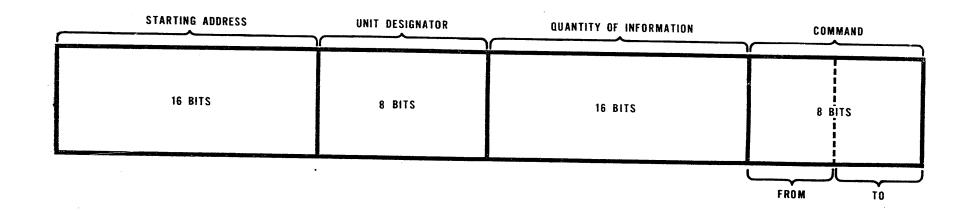

| 5.         | System Instruction Format                                          | 21   |

| 6.         | Magnetic Core Storage Connected to the System                      | 22   |

| 7.         | Magnetic Tape Format                                               | 23   |

| 8.         | Magnetic Tape Control Unit                                         | 29   |

| 9.         | Arrangement of Magnetic Tape Control Units for Multiple Sequencing | 30   |

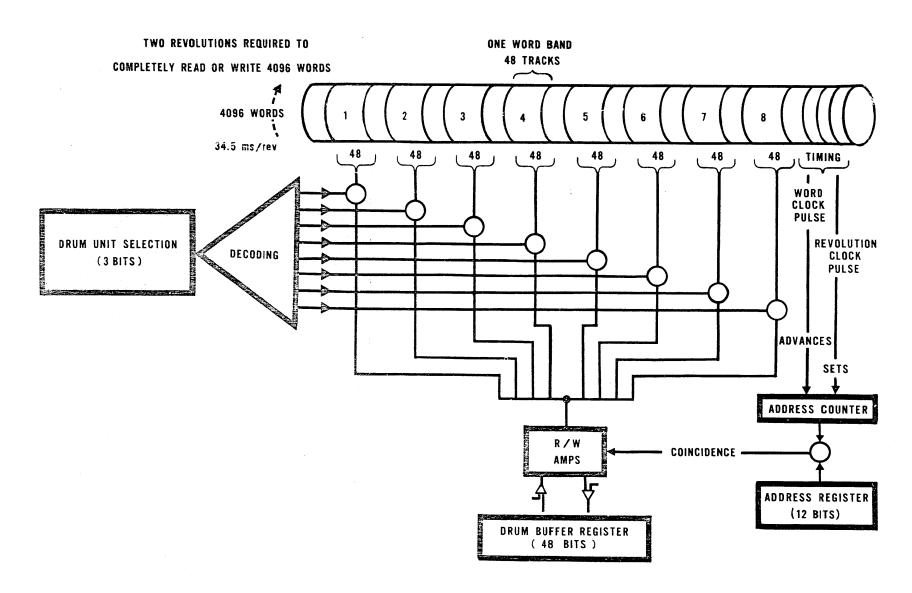

| 10.        | Magnetic Drum Unit - Block Diagram                                 | 33   |

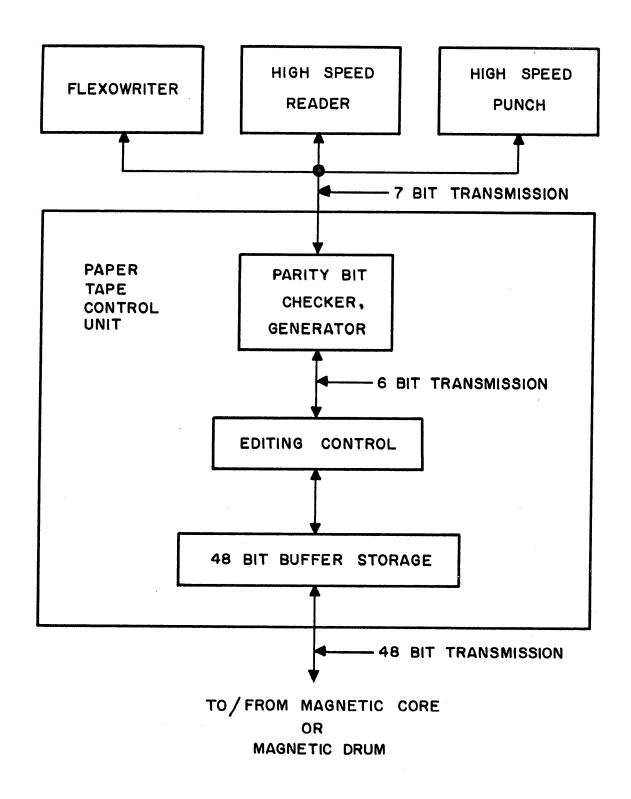

| 11         | Paper Tape Control Unit                                            | 36   |

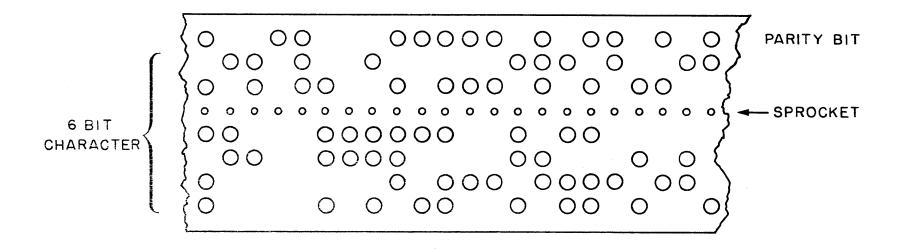

| 12         | Paper Tape Format                                                  | 37   |

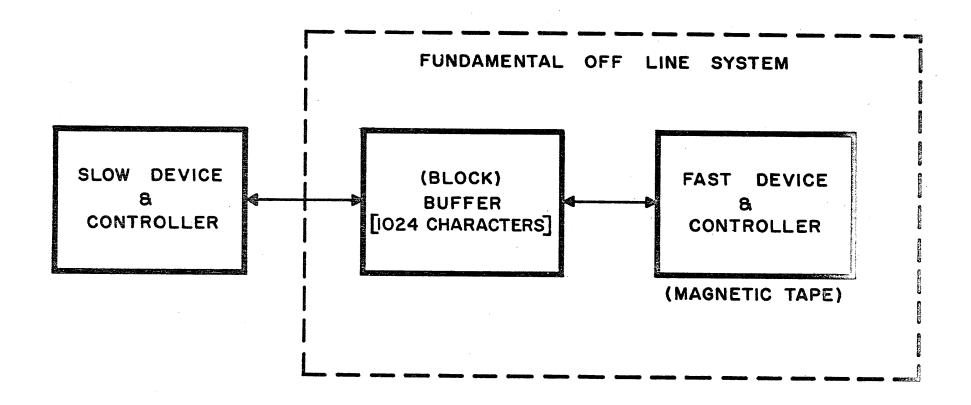

| 13.        | Block Diagram of Generalized Off-Line System                       | 40   |

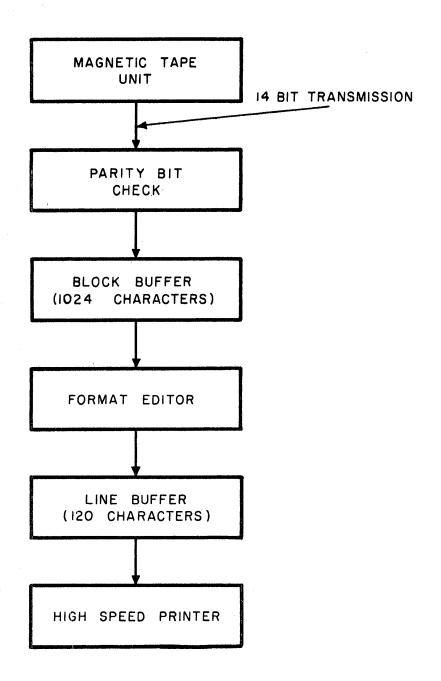

| 14.        | Block Diagram of High Speed Printer System                         | 41   |

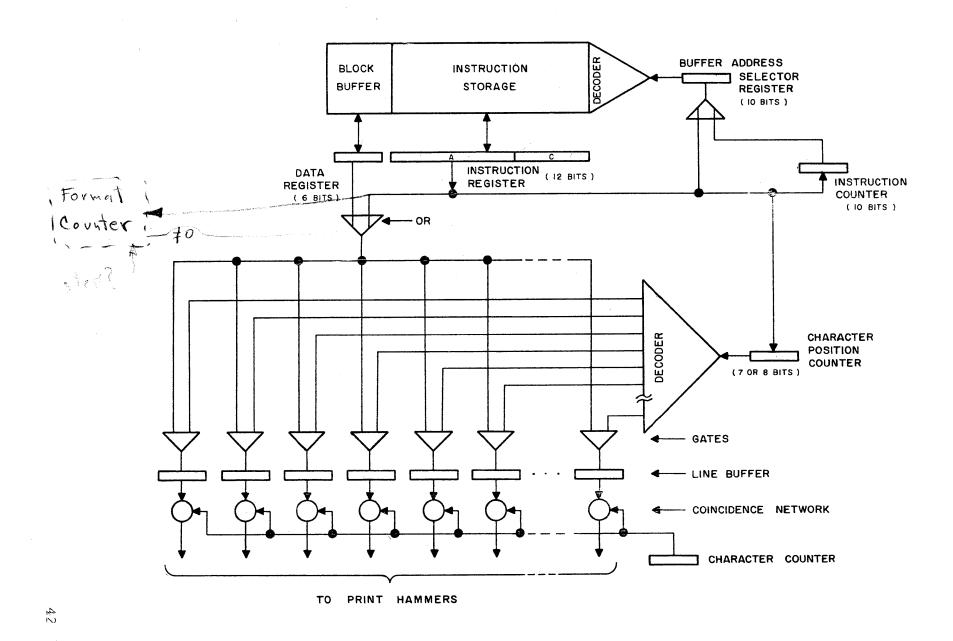

| 15.        | Block Diagram of Format Editor                                     | 42   |

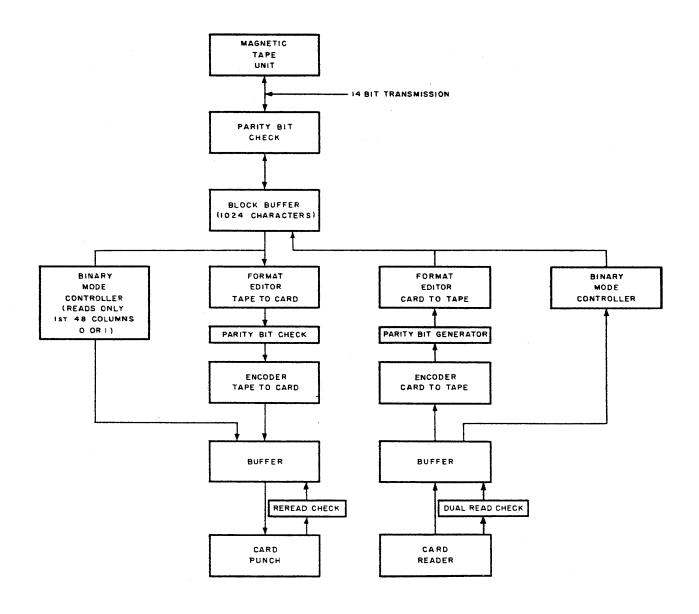

| 16.        | Block Diagram of High Speed Card Conversion System                 | 46   |

# LIST OF ILLUSTRATIONS (Cont'd)

| Figure No. | •                                              | Page |

|------------|------------------------------------------------|------|

| 17.        | Table of Sizes, Weights and Power Requirements | 50   |

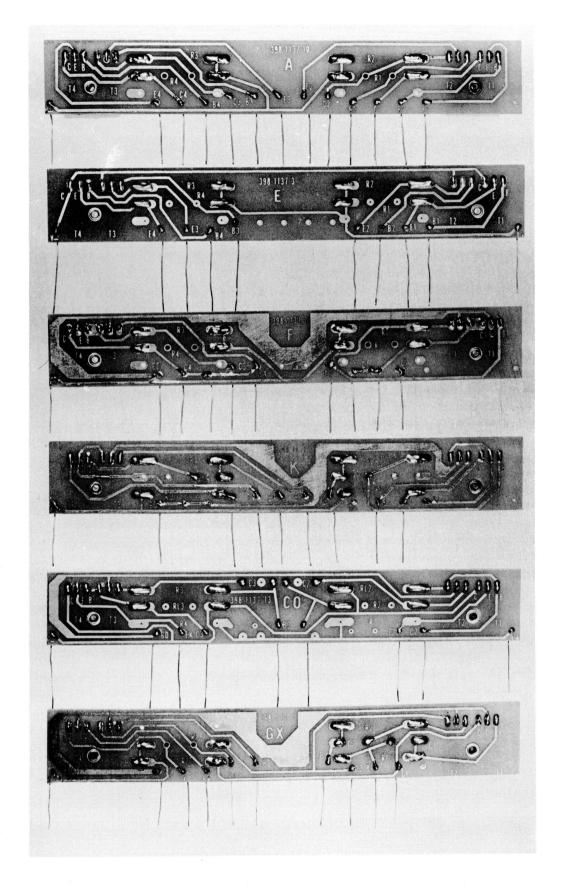

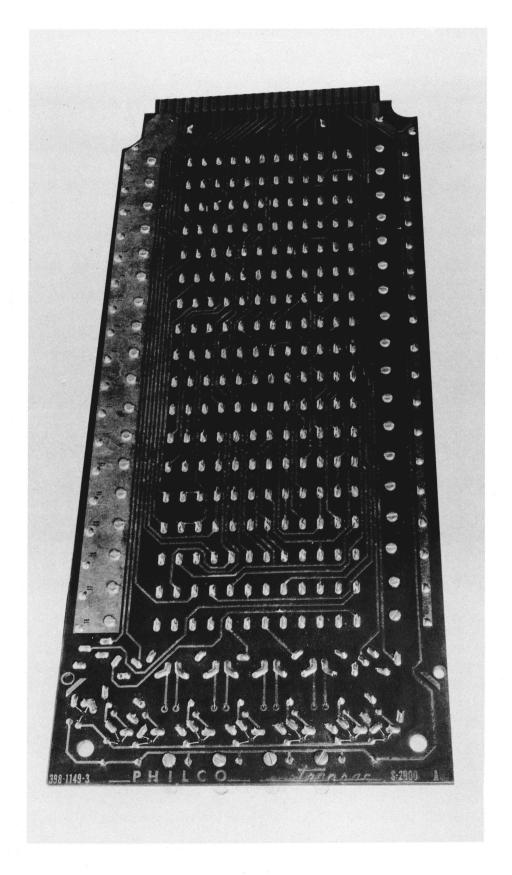

| 18.        | Typical Computer Module Circuit Cards          | 51   |

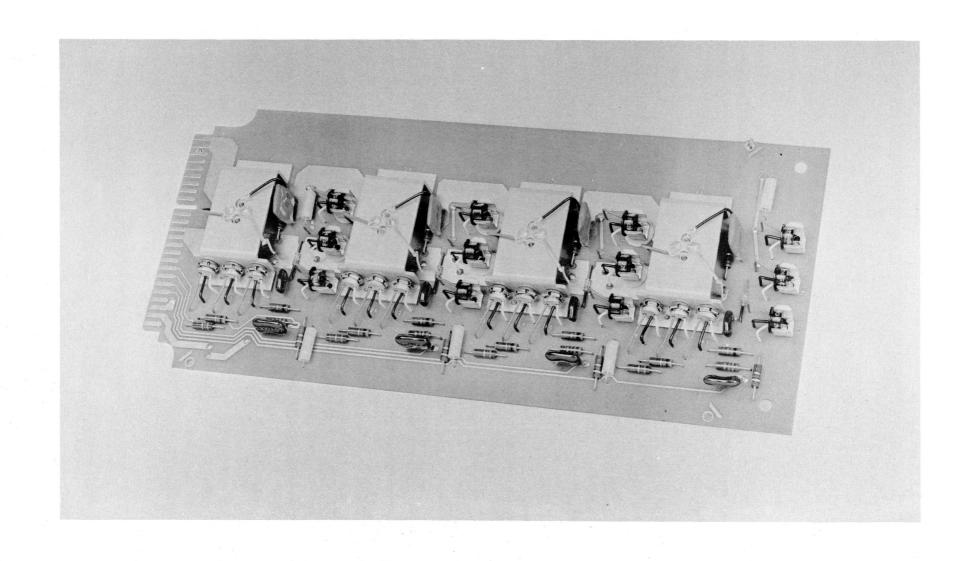

| 19.        | Computer Chassis Card                          | 52   |

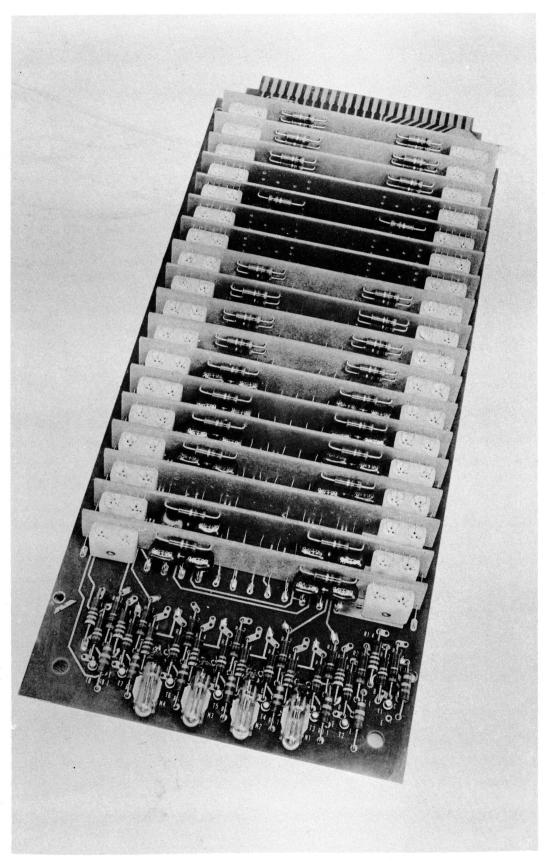

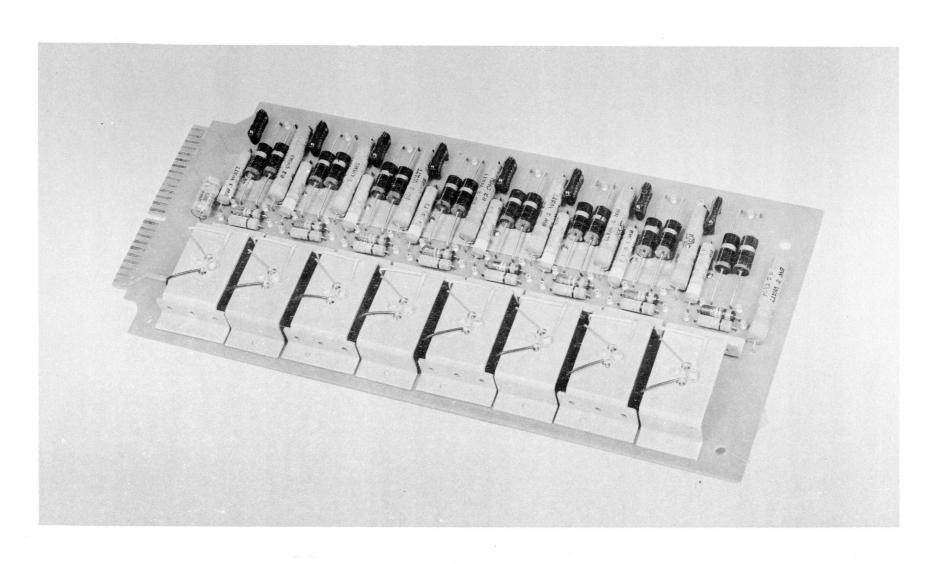

| 20.        | Arithmetic, Register Chassis Card              | 53   |

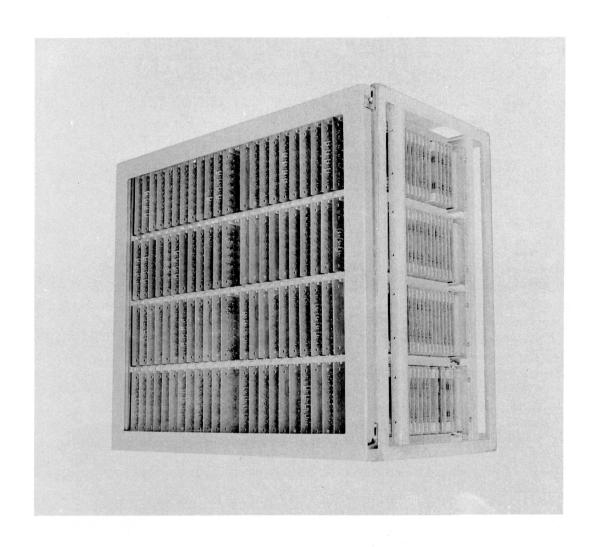

| 21.        | Basic Modular Frame - Card End                 | 55   |

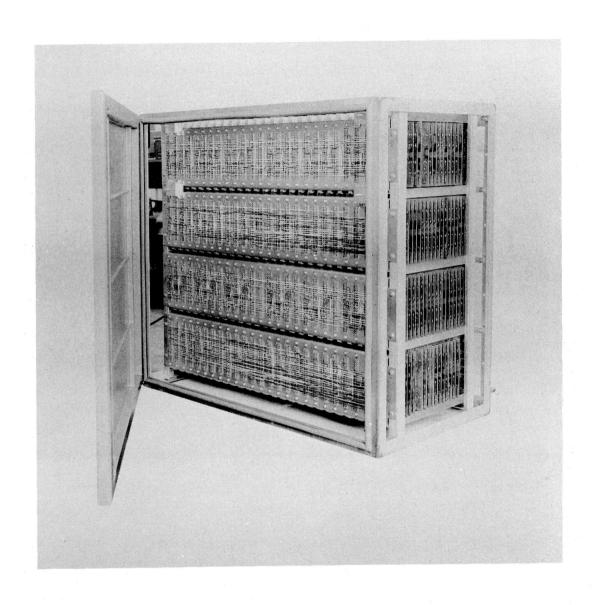

| 22.        | Basic Modular Frame - Wiring End               | 56   |

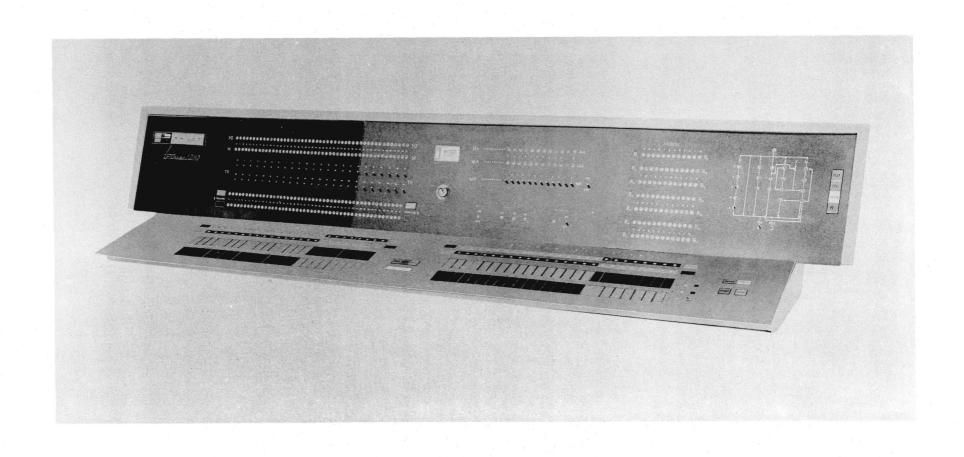

| 23.        | Computer Control Panel                         | 58   |

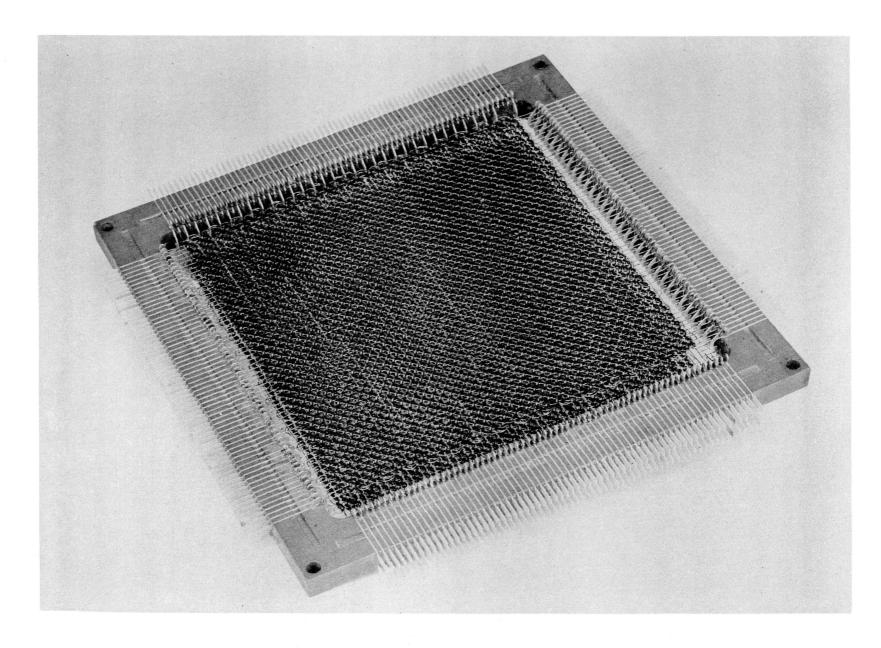

| 24.        | Magnetic Core Plane                            | 60   |

| 25.        | Inhibit Drive Chassis Card                     | 61   |

| 26.        | Read/Write Driver Output Card                  | 62   |

| 27.        | Paper Tape Unit                                | 63   |

| 28.        | Hi-Speed Printer Chassis                       | 66   |

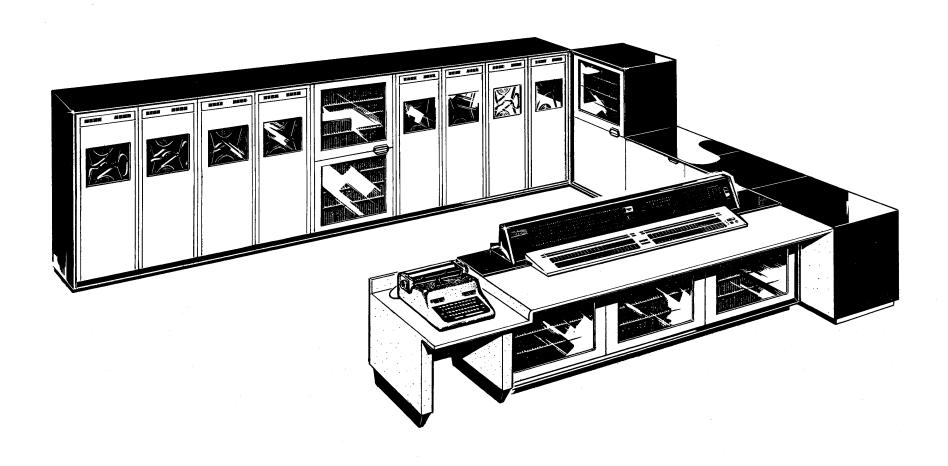

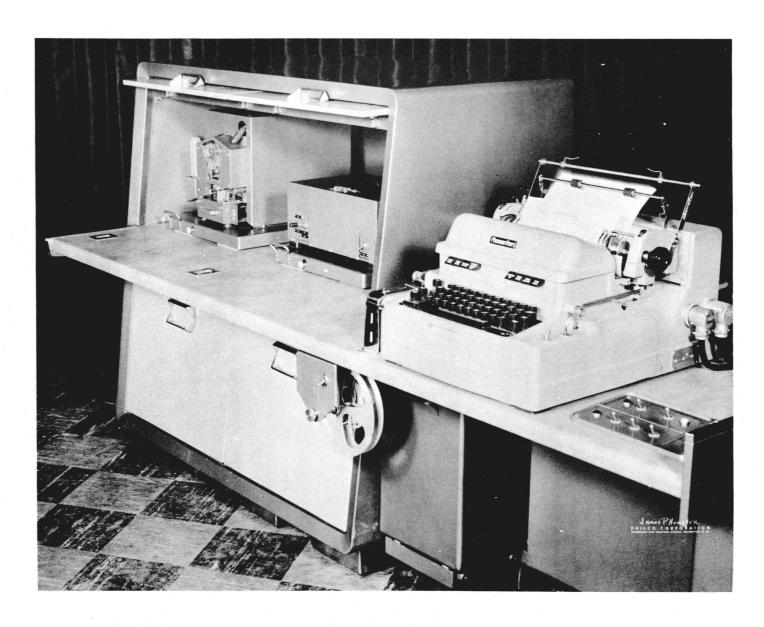

S-2000 Computer System Installation

#### TRANSAC S-2000

#### SYSTEM DESCRIPTION

#### 1. INTRODUCTION

The TRANSAC S-2000 System is Philco's answer to the challenge of the modern world for more advanced digital computing and data processing systems. It embodies new exclusive concepts. The S-2000 is designed for optimum utilization of transistor characteristics. It is not a transistorized version of a vacuum tube system.

#### 1.1 Advanced System Design

The TRANSAC S-2000 solves business, scientific and control problems. Its speed of operation keeps pace with the data processing requirements of today and tomorrow. Its unique features of expansibility permit a basic installation to be increased in capacity to accommodate more complex or demanding problems at any time after installation without redesigning the existing system.

### 1.2 Reliability

The reliability achievements of the S-2000 are made possible by the Philco Surface-Barrier Transistor, the active electronic element in the S-2000. The 90% life expectancy of these transistors is well over 200,000 hours. Such transistors are 100 times more reliable than either diodes or vacuum tubes.

### 1.3 High-Speed Operation

The use of asynchronous parallel transistor logic results in an equivalent clock rate of 10 megacycles. The average time required to add two 15 decimal digit numbers is less than 1 microsecond.

### 1.4 Multiple Sequencing

The rate of data handling is further increased by processing as many as four magnetic tape units simultaneously. A system using this technique is capable of processing up to 360,000 binary coded decimal (alpha numeric) characters per second.

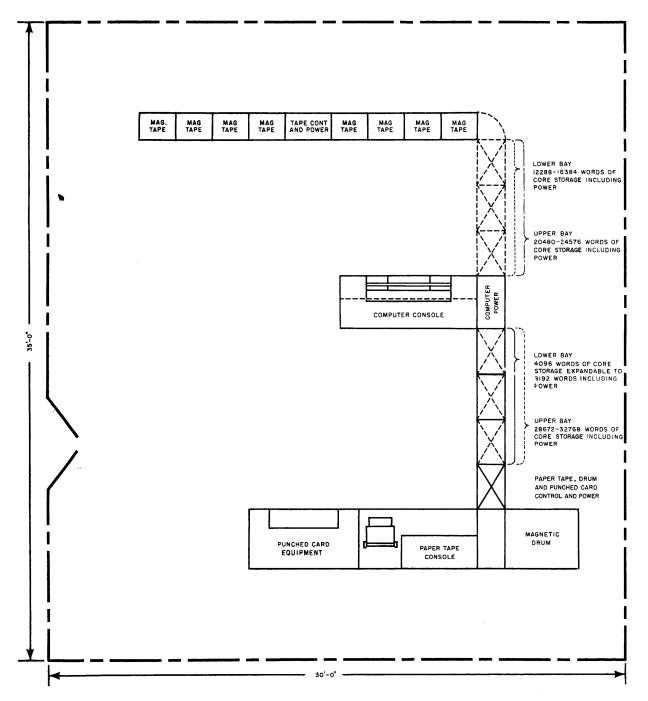

#### 1.5 Compactness

A typical large-scale S-2000 occupies only 600 square feet including working and access area or about 1/4 of the floor area required by equivalent vacuum tube systems.

#### 1.6 Economy

This S-2000 Computer requires less than 2 kilowatts of power; or about 1/10 the power required by a vacuum tube computer. There is no need for costly air conditioning or costly power distribution systems.

#### 1.7 Versatility

The programmer may choose from 64 arithmetic, 16 transfer of data, 14 shift, 16 transfer of control, and 16 special instructions. The instructions have been carefully designed to produce ease in programming and efficiency in the use of Compilers.

#### 1.8 Simplicity

Electrical and mechanical modular design results in simplicity of fabrication and maintenance. All logical functions are performed by two Philco developed circuits; common emitter and common collector type switches.

#### 1.9 Ease of Servicing

The reliability of Surface Barrier transistor reduces the frequency of component replacement. Fullest use is made of automatic diagnostic techniques for rapid preventive maintenance. Modular assemblies are easily accessible for quick replacement.

#### 1.10 Human Engineering

Controls are designed and positioned to minimize operator fatigue. Color styling increases operator efficiency.

#### 2. TRANSAC S-2000 SYSTEM

A TRANSAC S-2000 installation consists of:

#### 2.1 Computing and Control Unit MF-2000

Optional Features:

- (a) Floating point and/or fixed point arithmetic FP-20

- (b) Variable number of index registers; 4 to 16 index registers in groups of 4 (IR-2004, 8, 12, 16)

### 2.2 Magnetic Core Storage Unit MC-2001 to 16

4096 Word by 48 Bit capacity per Unit. Expansible up to 8 Units. (32,768 Words)

### 2.3 On-Line Input-Output Optional Equipment

#### 2.3.1 Magnetic Tape System

- (a) Magnetic Tape Units (up to 256) TT-2150

- (b) Magnetic Tape Control Unit TC-2150

- (c) Magnetic Tape Sequencing Unit TS-2150

#### 2.3.2 Magnetic Drum System

- (a) Magnetic Drum MD-2032

- (b) Magnetic Drum DC-2032

#### 2.3.3. On-Line Punch Card System PC-2801

- (a) Card Reader

- (b) Card Punch

- (c) Card Controller

#### 2.3.4 On-Line Paper Tape Console

- (a) High Speed Paper Tape Reader

- (b) High Speed Paper Tape Punch

- (c) Flexowriter

#### 2.3.5 Console Typewriter CT-2000

# 2.4 Off-Line Input-Output Optional Equipment

- 2.4.1 High Speed Printer CPS-2912

- 2.4.2 Card to Magnetic Tape Magnetic Tape to Card Converter CPC-2802

These devices are described in detail in the following sections. A typical S-2000 installation is illustrated in Figure 1.

TYPICAL TRANSAC S-2000 SYSTEM LAYOUT (ON LINE EQUIPMENT)

FIG. I

### 3. COMPUTING AND CONTROL UNIT MF-2000

The Computing and Control Unit performs the arithmetic and programming operations for the system.

### 3.1 Arithmetic Operations

Binary arithmetic is performed with a parallel logic. Negative numbers are represented in the two's complement form. Numbers are handled in an algebraic sense. For fixed point arithmetic, numbers are normalized such that they are in magnitude less than unity and equal to or greater than -1. The register arrangement for fixed point arithmetic is illustrated in Figure 2. Each register has a capacity of 48 bits. The far left bit designates the sign, and the remaining 47 bits contain the magnitude of the number.

Floating point numbers consist of a mantissa (magnitude) and the characteristic (exponent), where both are represented in the two's complement form. The mantissa is normalized such that in absolute value it is less than unity but greater than one-half. The register arrangement for floating point arithmetic is illustrated in Figure 3. There are 36 bits allotted to the mantissa and 12 bits allotted to the characteristic.

In either case, the operations performed in the arithmetic section include:

- 1. Addition: Contents of A-Register added to contents of D-Register, with sum stored in the A-Register.

- 2. Subtraction: Contents of D-Register subtracted from contents of A-Register, with difference stored in the A-Register.

- 3. Multiplication: Contents of the D-Register multiplied by the contents of the Q-Register, with the product stored in the A and Q-Registers.

- 4. Division: Contents of the A-Register divided by the contents of the D-Register, with the quotient stored in the Q-Register and the remainder stored in the A-Register.

#### 3.2 Speed of Arithmetic Operations

Some of the arithmetic instructions obtain operands from the magnetic core storage and others use operands stored in the registers of the arithmetic section. The speed of operation is determined by the access time of the magnetic core storage and the switching speed of the arithmetic instructions. The following tables illustrate some of the arithmetic speeds.

BLOCK DIAGRAM OF FIXED POINT ARITHMETIC SECTION FIG. 2

BLOCK DIAGRAM OF FLOATING POINT ARITHMETIC SECTION FIG. 3

#### Operands Initially in Arithmetic Registers

| Operation      |                  | Fix | ed Point  | Floa | ating Point |

|----------------|------------------|-----|-----------|------|-------------|

| Addition/and   | Av.              | 1.0 | μsec      | 8    | μsec        |

| Subtraction    | Min.             | 0.5 | $\mu$ sec | 0.5  | μsec        |

|                | Max.             | 5.1 | μsec      | 19   | μsec        |

| Multiplication | Av .             | 28  | μsec      | 22   | μsec        |

| and Division   | Min.             | 19  | μsec      | 15   | $\mu$ sec   |

|                | $\mathbf{Max}$ . | 245 | $\mu$ sec | 140  | μsec        |

#### Operands Transferred from Magnetic Core Storage

| Operation      |      | Fixed Point |      | Floating Point |                    |

|----------------|------|-------------|------|----------------|--------------------|

| Addition and   | Av.  | 12          | μsec | 20             | μsec               |

| Subtraction    | Min. | 12          | μsec | 13             | μsec               |

|                | Max. | 12          | μsec | 41             | μsec               |

| Multiplication | Av.  | 33          | μsec | 27             | μsec               |

| and Division   | Min. | 24          | μsec | 20             | $\mu \mathtt{sec}$ |

|                | Max. | 250         | μsec | 145            | μsec               |

#### Result Replaces Operand in Magnetic Core Storage

| Operation      |      | Fixed Point        | Floating Point |

|----------------|------|--------------------|----------------|

| Addition and   | Av.  | 13 $\mu$ sec       | 20 μsec        |

| Subtraction    | Min. | $12.5 \mu sec$     | 13 $\mu$ sec   |

|                | Max. | 17 $\mu$ sec       | 31 µsec        |

| Multiplication | Av.  | $40~\mu 	ext{sec}$ | 34 μsec        |

| and Division   | Min. | 31 $\mu$ sec       | 27 μsec        |

|                | Max. | 257 $\mu$ sec      | 152 $\mu$ sec  |

#### 3.3 Programming Operations

Programming instructions are read from the magnetic core storage and stored in the PR-Register for interpretation and execution. The PR-Register has a capacity of 48 binary bits. An instruction word requires 24 binary bits, which includes the command, and address information. Single address instructions are used. The PR-Register therefore contains two instructions, side by side. The left-hand instruction is executed first except for the case where only the right-hand instruction is to be executed.

The instructions of the program are sequenced by a Program Address Register (PA).

#### 3.4 Addressing and Index Registers

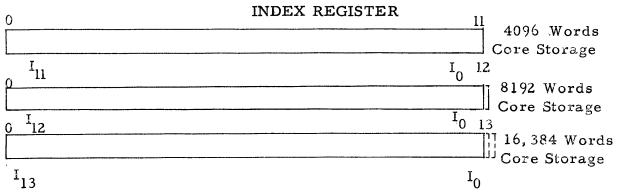

The format for an instruction word is illustrated in Figure 4. Eight bits determine the command (function of the instruction), one bit designates whether index registers are used or not, fifteen bits are used to address the magnetic core storage and designate which index register is involved. When the word capacity of the magnetic core storage is 4096 and 8 index registers are used, twelve bits address the magnetic core storage and 3 bits designate which index register is involved. When index registers are involved, the contents of the designated index register is added to the 12-bit address portion of the instruction to address the magnetic core storage.

When 8192 words of magnetic core storage are used in the system, the same instruction word format is used except that 13 bits instead of 12 bits are necessary to address the magnetic core storage. In this case, if index registers are not involved, 13 bits are taken from the addressing portion of the instruction. If an index register is involved, 12 bits of the address portion of the instruction are added to a 13-bit index register to perform the addressing.

Besides address modification, the index registers are used for counting, address placement or substitution, or accumulating.

#### 3.5 Computer Instructions

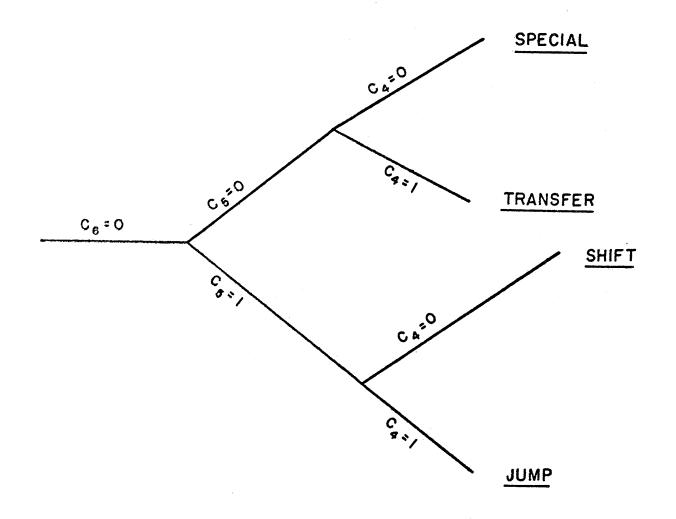

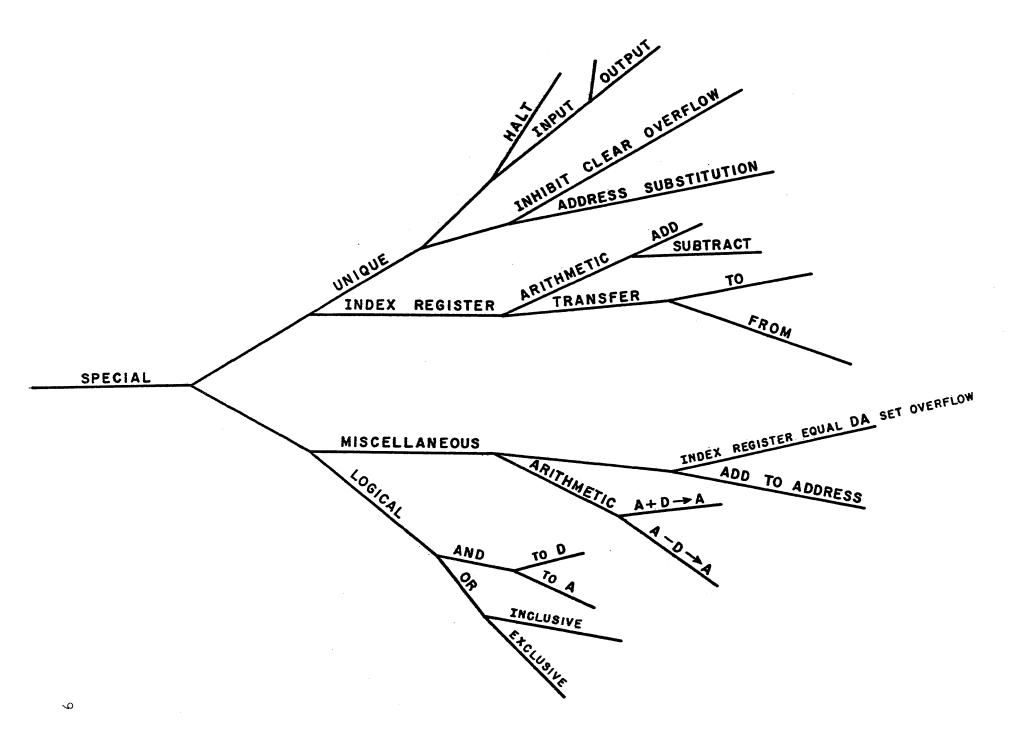

Computer instructions are subdivided into five groups:

- 1. Arithmetic,

- 2. Transfer of data,

- 3. Shift.

- 4. Transfer of control (jump),

- 5. Special.

To describe the instructions in detail, a symbolism is adopted, which is explained as follows:

- A. refers to the A-Register

- D refers to the D-Register

- Q refers to the Q-Register

- V refers to the magnetic core storage.

- signifies 'absolute value of'.

- () signifies 'contents of'.

# COMPUTER INSTRUCTION WORD FORMAT

FIG 4

→ signifies 'place in'.

d<sub>j</sub> designates the j<sup>th</sup> bit of D, where j=0 for the sign position, and j= -1 through -47 for the remaining positions to the right of the sign.

#### 3.5.1 Arithmetic Instructions

There are a total of 32 addition and subtraction instructions which may be summarized as follows:

(A)

$$\pm [(V) \text{ or } (Q)] \longrightarrow [A \text{ or } A \text{ and } V]$$

$$0 \quad \pm \quad \boxed{(V) \text{ or } (Q)} \quad \longrightarrow \quad \boxed{A \text{ or } A \text{ and } V}$$

(A)

$$\pm \begin{bmatrix} 1 & (V) & 1 & \text{or} & 1 & (Q) & 1 \end{bmatrix} \rightarrow \begin{bmatrix} A & \text{or} & A & \text{and} & V \end{bmatrix}$$

$$0 = \begin{bmatrix} 1 & (V) & 1 & \text{or} & 1 & (Q) & 1 \end{bmatrix} \rightarrow \begin{bmatrix} A & \text{or} & A & \text{and} & V \end{bmatrix}$$

There are a total of 16 multiplication instructions which may be summarized as follows:

(Q)

$$X \cap (V)$$

or  $(A) \longrightarrow AQ$  or  $AQ$  and  $(A) \longrightarrow V$ ,

(Q) X  $\begin{bmatrix} 1 & (V) & 1 & or & 1 & (A) & 1 \end{bmatrix} \rightarrow AQ$  or AQ and  $(A) \rightarrow V$ , where A contains the more significant half of the product without round off, and Q contains the lesser significant half of the product.

(Q)

$$X [V)$$

or  $(A) \longrightarrow A$  or A and V,

(Q) X  $\boxed{1}$  (V) 1 or 1 (A)  $\boxed{1} \longrightarrow A$  or A and V, where A contains the more significant half of the product with round off. The multiplier is left in the Q-Register.

There are a total of 16 division instructions which may be summarized as follows:

$$[(AQ) \text{ or } (A)] \div [(Q) \text{ or } (V)] \longrightarrow Q \text{ or } Q \text{ and } V$$

$[(AQ) \text{ or } (A)] \div [1(Q)1 \text{ or } 1(V)1] \rightarrow Q \text{ or } Q \text{ and } V,$  where the remainder is stored in the A-Register.

The overflow flip-flop is normally set to zero before an arithmetic operation. In the event the arithmetic operation should obtain a result which overflows the capacity of the register, the overflow flip-flop is set to unity. As will be seen later, the overflow flip-flop may be used for control purposes.

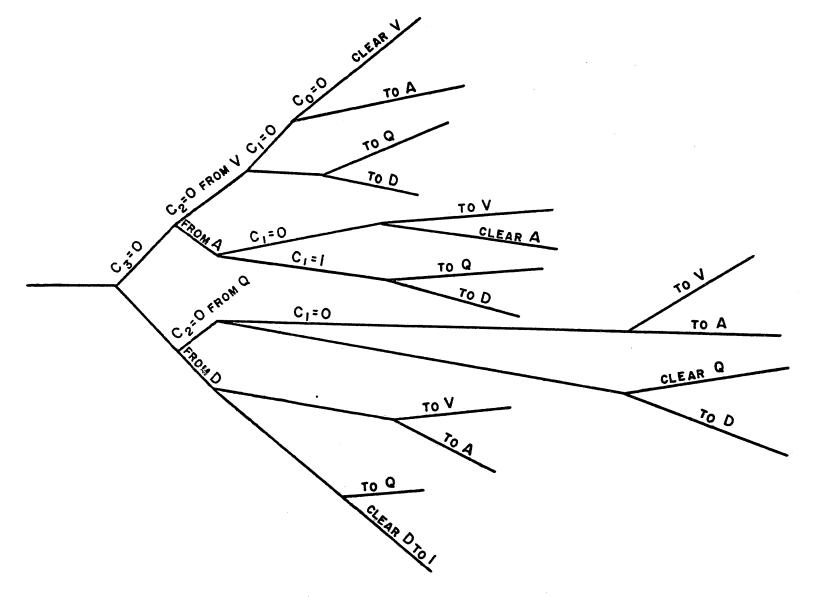

#### 3.5.2 Transfer of Data Instructions

The transfer of data instructions include:

$$(V) \longrightarrow A$$

or Q or D

$$0 \longrightarrow V$$

$$(A) \longrightarrow Q$$

or D or V

$$0 \longrightarrow A$$

$$(Q) \longrightarrow D$$

or V or A

$$0 \longrightarrow Q$$

$$\begin{array}{cccc} \text{(D)} \longrightarrow \text{V} & \text{or A or Q} \\ \text{all l's} \longrightarrow & \text{D} \end{array}$$

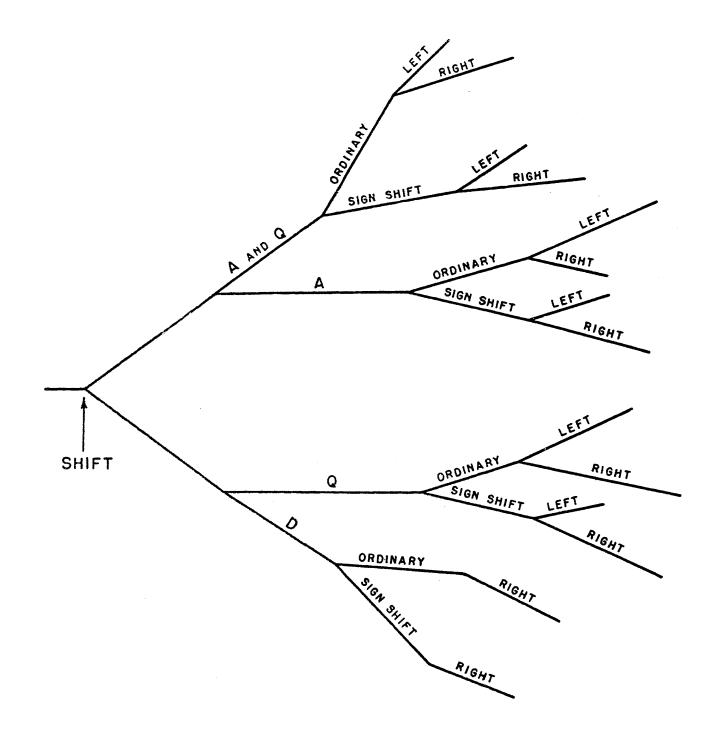

#### 3.5.3 Shift Instructions

There are a total of 14 shift instuctions which are summarized as follows:

1. A and Q ordinary shift left out

$$a_0 \leftarrow a_{-1} \cdots \leftarrow a_{-47} \leftarrow q_0 \leftarrow q_{-1} \cdots \leftarrow q_{-47} \leftarrow q_0 \leftarrow q_$$

2. A and Q ordinary shift right

$$0 \rightarrow a_0 + a_1 \rightarrow \dots \rightarrow a_{-47} \rightarrow q_0 \rightarrow q_{-1} \rightarrow \dots \rightarrow q_{-47} \rightarrow \text{out}$$

3. A and Q sign shift left out

$$a_0 = a_{-1} + \cdots + a_{-47} + q_0 + q_{-1} + \cdots + q_{-47} + 0$$

4. A and Q sign shift right

$$a_0 \rightarrow a_0 \rightarrow a_{-1} \rightarrow \cdots \rightarrow a_{-47} \xrightarrow{q_0} q_{-1} \rightarrow \cdots \rightarrow q_{-47} \rightarrow \text{out}$$

5, 6 A, Q ordinary shift left out

$$-a_0 - a_{-1} - \cdots - a_{-47} - 0$$

7,8 A, Q ordinary shift right

$$0 \rightarrow a_0 \rightarrow a_{-1} \rightarrow \cdots \rightarrow a_{-47} \rightarrow \text{out}$$

9, 10 A, Q sign shift left out

$$a_0$$

$a_{-1} \leftarrow \cdots \leftarrow a_{-47} \leftarrow 0$

11, 12A, Q sign shift right

$$a_0 \rightarrow a_0 \rightarrow a_{-1} \rightarrow \cdots \rightarrow a_{-47} \rightarrow \text{out}$$

13. D ordinary shift right

$$0 \longrightarrow d_0 \longrightarrow d_{-1} \longrightarrow \cdots \longrightarrow d_{-47} \longrightarrow out$$

14. D sign shift right

$$0 \xrightarrow{d_0 - d_{-1}} \cdots \xrightarrow{d_{-47}} out$$

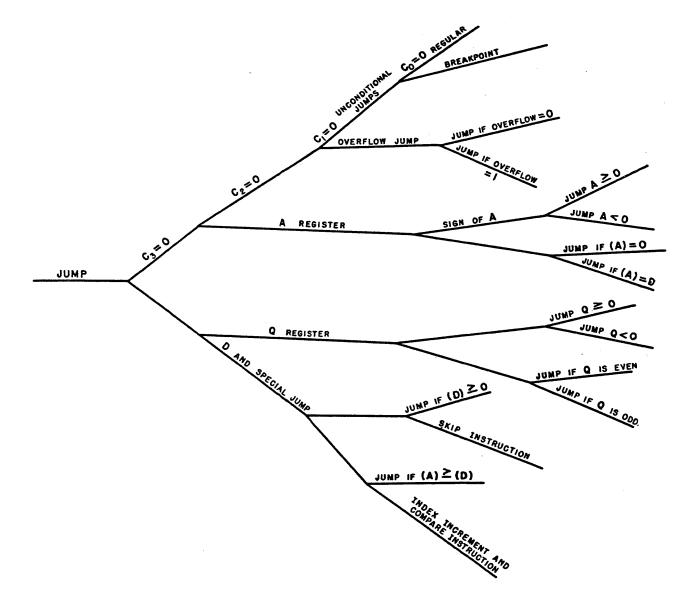

### 3. 5. 4 Transfer of Control (Jump) Instructions

The program is sequenced by the program address counter. However, the programmer can interrupt the sequence by inserting a jump instruction which decides whether to continue the sequence or to select another instruction from the core storage. The decision is based on certain conditions that exist in the computer. The instruction the program jumps to may be either the left or right half of a word read from the core storage. Jump instructions can be classified into three types: unconditional, conditional, and preparatory. The jump instructions are as follows:

- An unconditional jump instruction transfers

(V) PA, and designates whether the left or right instruction is to be performed next.

- 2. An unconditional breakpoint jump (identical to the unconditional jump) is used when the "breakpoint" switch is OFF. When the breakpoint switch is ON, the unconditional breakpoint jump halts the computer. Then, upon depressing the ADVANCE button on the front panel of the console, an unconditional jump is performed.

- 3. There are 13 conditional jumps; the decision to jump depends on whether:

- (a) Overflow flip-flop = 0 (no overflow)

- (b) Overflow flip-flop = 1 (overflow)

- (c) Number in A-Register is positive

- (d) Number in A-Register is negative

- (e) Number in A-Register equals zero

- (f) Contents of A-Register equal to contents of D-Register

- (g) Contents of A-Register greater than or equal to contents of D-Register.

In the following jump instructions involving the Q-Register, the contents of the Q-Register are shifted in a circular fashion in the direction of sensing, after the sensing is performed, regardless of the jump decision. An example of the circular shift can be illustrated as follows:

$$q_{-47} \leftarrow q_0 \leftarrow q_{-1} \cdots \leftarrow q_{-47} \leftarrow q_0$$

Hence, the Q jumps are decided by:

- (h) The number in the Q-Register is even, q-47 = 0, circular shift right

- (i) The number in the Q-Register is odd, q-47 = 1, circular shift right

- (j) The number in the Q-Register is positive,  $q_0 = 0$ , circular shift left

- (k) The number in the Q-Register is negative,  $q_0 = 1$ , circular shift left.

A conditional jump which involves the D-Register and the decision to jump is based on whether:

The number in the D-Register is positive, do = 0.

The remaining conditional jump involves a special application of index registers. The programmer first places a control number in the D-Register. For this purpose, the D-Register is divided into parts called the left and right half, such that either half may be associated with an index register or a memory address. The instruction then decides to jump depending on whether the contents of the specified index register increased by one is not equal to the left half of the D-Register. This jump instruction differs from the others in that the right half of the D-Register contains the address of the instruction control is transferred to, instead of the address portion of the instruction itself.

Similar to the jump instructions are two skip instructions. The first says to skip the next consecutive instruction and execute the following one provided,

$$(A) \geq (X_i),$$

Otherwise continue with the next consecutive instruction. (A) is the contents of the address portion of the skip instruction, and  $X_i$  is control information from some external source. Which  $X_i$  is selected is determined from the three bits which normally select index registers. The second says to skip the next instruction unless an input/output fault has occurred. The specific fault being examined may be specified by the address portion of the skip instruction.

### 3.5.3 Special Instructions

The special instructions include:

- A. Unique control functions

- B. Index Register control

- C. Special arithmetic instructions

- D. Logical operations

The unique control functions include:

- 1. Halt: This instruction stops the controls of the Computer.

- 2. Breakpoint Halt: This instruction stops the controls provided the breakpoint halt switch is ON; otherwise, it is a dummy instruction.

- 3. Input/Output: This instruction only indicates that a system instruction which involves input/output devices, exists in the D-Register and is to be performed.

- 4. Inhibit clearing of overflow flip-flop. Otherwise when an arithmetic instruction is performed, the overflow flip-flop is first cleared to ZERO, and then set to ONE in the event that an overflow occurred in the arithmetic instruction. By using this instruction, a subroutine can be sampled (instead of a single instruction) for overflow.

5. Address Substitution: Transfer the contents of the program address counter to the address portion of the word contained in core storage location V. Storage location V usually contains a jump instruction which implies that the program address counter includes information concerning whether the left or right instruction is involved. Further, because of the manner in which index registers are used, special consideration is given to the number of bits transferred.

The Index Register control instructions include:

- Add the contents of the address portion of the D-Register to the specified index register.

(Left or right portion is specified by the command).

- 7. Subtract the contents of the address portion of the D-Register from the specified index register.

- 8. Transfer the contents of the index register to the address portion of the D-Register. Because of the manner in which the index register is employed, special consideration is given to the number of bits transferred. The bit of the D-Register, which in an instruction sense determines whether an index register is involved, makes the decision.

- 9. Transfer the contents of the address portion of the D-Register to the specified index register. A similar situation exists for this instruction as in the preceding one.

- 10. If the contents of the specified index register are equal to the contents of the indicated half of the D-Register, set the overflow flip-flop to unity.

The special arithmetic instructions include:

- Increase the address portion of the word in memory location (V) by one.

(Left or right is specified by the command.)

- 12. (A)  $\pm$  (D)  $\longrightarrow$  A

The logical operations include:

- 13. Logical Product to D. Take the bit by bit logical conjunction of (D) and (V), and leave in the D-Register.

- 14. Logical Product to A. Same as 13 above except that (D)→A after the logical product is formed.

- 15. Logical Sum. Take the bit by bit (inclusive or) of (D) and (V), and leave in V.

- 16. Add without carry. Take the bit by bit logical (exclusive or ) of (V) and (A) and leave in A and V.

## 3.5.6 Speeds of Non-Arithmetic Instructions

The non-arithmetic instructions may be said to include:

- of instruction access time and magnetic core access time. The magnetic core access time is 5 microseconds for reading and 7 microseconds for writing. The nature of the magnetic core storage demands that a write cycle must follow a read cycle in order to retain information in the storage. Therefore, the access time of the magnetic core storage is 12 microseconds. Since two instructions are obtained in a 48-bit word from the magnetic core storage, the access time for instructions is 6 microseconds.

- 2. Shift instructions require less than 1/2 microsecond per bit shifted.

- 3. Jump instructions require less than 1/2 microsecond each exclusive of access times.

#### 4. MAGNETIC CORE STORAGE UNIT

The high-speed storage of the TRANSAC S-2000 is a coincident current magnetic core device. Transistor circuits are used. The magnetic core device is designed in groups of 4096 words where each word contains 48 bits. The system is capable of using up to 8 such units.

### 4, 1 Expanding the Magnetic Core Storage

To expand the magnetic core storage from one unit to several requires the addressing registers of the program portion of the computer to be expanded accordingly. This includes the -

- 1. Memory Address Register (MA)

- 2. Program Address Register (PA)

- 3. Index Registers (RI)

These registers are packaged in a manner as to permit expansion by inserting additional printed circuit chassis, which are identical to those present. No rewiring is necessary.

### 4.2 Magnetic Core Storage Control

The MA register is connected to the selection network of the core storage. To operate the storage the address is set in MA and either Read or Write control is activated. Information read from or written into the storage passes through either the D-register or PR-register, depending on the situation. To transfer data from the D-register to the storage requires first a Read cycle, which clears the storage location, followed by a Write cycle, which transfers the contents of the D-register to the cores. To transfer data from the cores to the D-register requires a Read cycle to transfer the data, and a Write cycle to restore the data in the cores. The Write cycle does not have to immediately follow the Read cycle, hence the Write cycle is held up during the replace type arithmetic operation.

The time required for the Read cycle is 5 microseconds, and for the Write cycle is 7 microseconds.

#### 5. ON-LINE INPUT/OUTPUT EQUIPMENT

Data transmission between the input/output devices and the magnetic core storage is controlled by a set of system instructions which are distinct from the computer instructions. The system instruction format, which uses a 48-bit word length, is illustrated in Figure 5. A system instruction is transferred from the core storage to the D-Register, and the next consecutive computer instruction is the Special Instruction which says that an input/output device is involved. The contents of the D-Register are then interpreted by the input/output controllers. If the core storage is involved with instruction, the starting address of the core storage is contained in the address portion of the special computer instruction.

The system instructions are listed in Table I. An appropriate selection of those on-line input/output devices may be made to complete a data processing system.

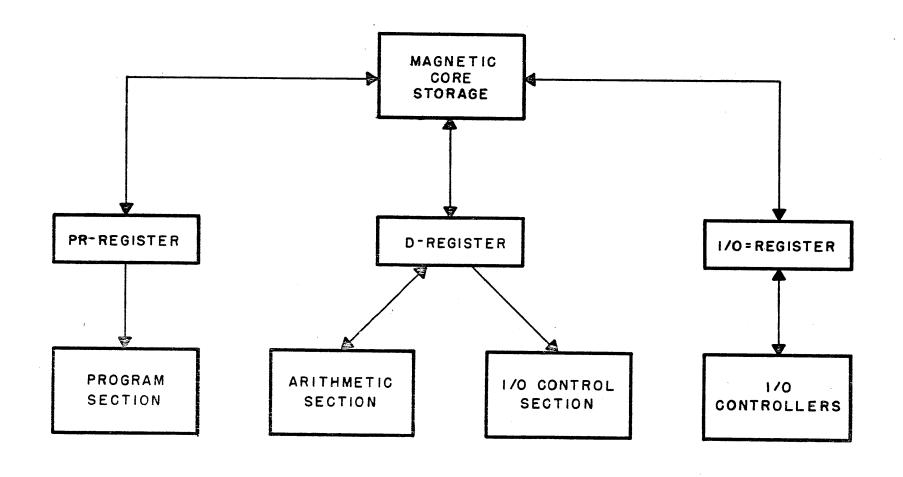

Since control information is obtained from the Magnetic Core Storage and stored in the D-Register, an Input/Output register is employed to transmit data between the Magnetic Core Storage and the Input/Output control units. The manner in which the Magnetic Core Storage device is connected to the system is illustrated by Figure 6.

#### 5.1 Magnetic Tape System

The magnetic tape system consists of:

- A. Magnetic Tape Units (1 to 256)

- B. Magnetic Tape Control Unit (1 to 4 per system)

- C. Magnetic Tape Sequencing Unit (one needed when more than one Magnetic Tape Control Unit is used for concurrent operations).

#### 5.1.1 Magnetic Tape Unit

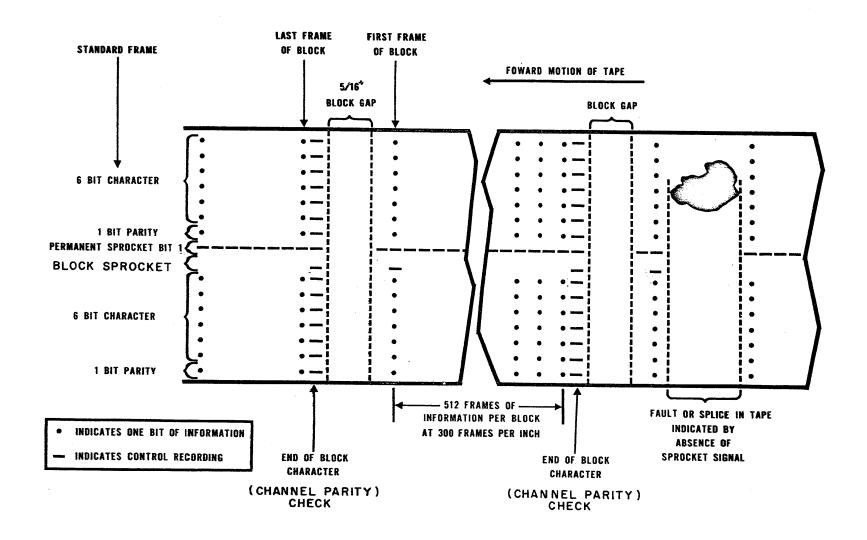

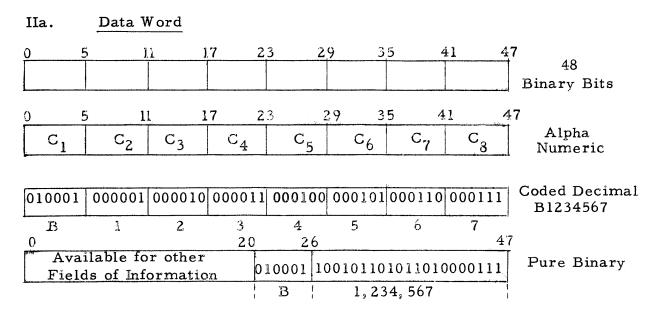

The magnetic tape format is illustrated in Figure 7. Two six-bit groups, each with a parity bit are recorded side by side on 1" mylar tape. The information may be stored on the tape in either 6-bit coded decimal form (alpha numeric data) or in pure binary notation. Storing numerical data in pure binary increases the information density on the tapes; thereby, increasing the effective information transfer rate by a ratio of 3 to 5. The information on the tape is partitioned into fixed blocks where each block has a capacity of 1024 characters. The blocks are separated by the block gap, which is adequate for stopping the tape between blocks without

SYSTEM INSTRUCTION FORMAT

FIG 5

22

Figure 6. Magnetic Core Storage Connected to the System

MAGNETIC TAPE FORMAT FIG.7

loss of information. The sprocket channel, which is physically located down the center of the tape, is a permanent recording permitting any faults in the tape to be skipped.

Vacuum controlled servos for the magnetic tape units are used.

The TRANSAC tape unit has the following performance characteristics:

#### Tape Unit Operating Specifications

| 1.  | Tape Speed             | 150 inches/sec.                            |

|-----|------------------------|--------------------------------------------|

| 2.  | Rewind Speed           | 250 inches/sec.                            |

| 3.  | Start Time             | 3 milliseconds                             |

| 4.  | Stop Time              | 3 milliseconds                             |

| 5.  |                        |                                            |

|     | Reversing Time         | 6 milliseconds                             |

| 6.  | Inter-record Gap       | 5/16 of an inch                            |

| 7.  | Stop-Start Cycles Rate | 0 to 120 cps                               |

| 8.  | No. of tracks          | 16                                         |

| 9.  | Tape Width             | l inch                                     |

| 10. | Tape Thickness         | l mil mylar base                           |

| 11. | Recording Density      | 300 bits/inch                              |

| 12. | Type of Recording      | NR Z                                       |

| 13. | Reel Size; Type        | 10 1/2 inch Precision                      |

|     |                        | NARTB Reels Machined                       |

|     |                        | From Magnesium Alloy                       |

| 14. | Tape Length            | Up to 3600 feet.                           |

| 15. | Type of Threading      | Leader                                     |

| 16. | Reel Change Time       | Less than 1/2 minute                       |

| 17. | End of Tape Sensing    | Sensing of Conduct Coating on back of tape |

| 18. | Program Restrictions   | None                                       |

| 19. | Write Lock Out         | Ring must be inserted in Tape Reel to per- |

|     |                        | mit writing on Tape. Tape Reels cannot be  |

|     |                        | stored in container until ring is removed. |

| 20. | Fail Safe Feature      | Automatic stopping of tape in case of      |

| ·   |                        |                                            |

|     |                        |                                            |

- A. Vacuum loss

- B. Tape break

- C. Power failure

- 21. Dust Control

- 22. Reel Door Interlock

- 23. Local Controls and Displays

Cabinet Pressurized

Opening door Lock Out

Remote Contact.

- A. Start Key

- B. Ready Light

# 23. Local Controls and

Displays (cont'd)

- C. Select Light

- D. Reset Key

- E. Read Only Light

- F. Load-Rewind Key

- G. Address Selector Key Changes

Unit Address

- 24. Remote Command

- A. Stop

- B. Forward

- C. Reverse

- D. Rewind

- E. Rewind and Lock Out

### 5.1.2 Magnetic Tape Control Unit

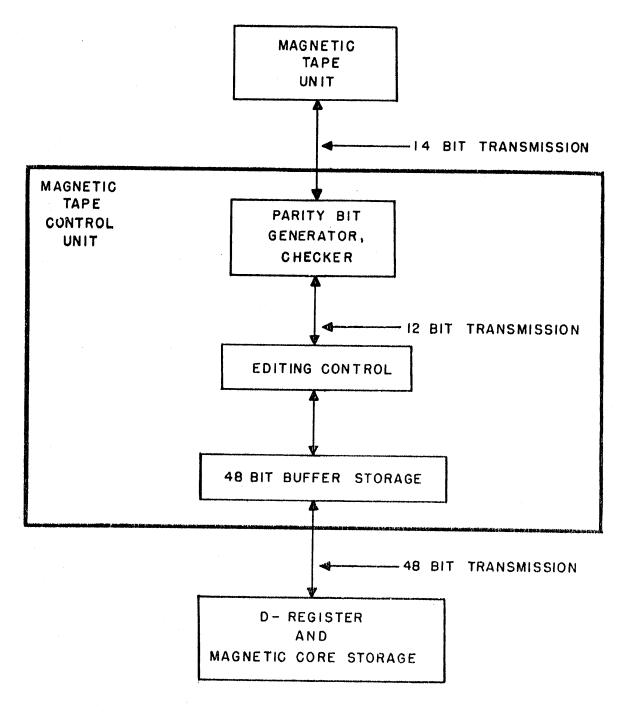

The Magnetic Tape Control Unit is illustrated by the block diagram of Figure 8.

When transmitting data from magnetic tape to magnetic core, the Parity Bit Generator, Checker, checks for odd parity. The Editing Control distributes four double characters to the 48-bit Buffer Storage.

The timing signals which actually control the flow of information originate from the sprocket channel on the tape. During the processing of a block of tape information, a counter is operated which checks whether 1024 characters have been processed.

The Block Sprocket indicates the beginning and end of a block such that abnormal gaps (for tape faults) are not confused as block gaps. The End of Block character contains odd parity check information for the block for 14 channels.

# 5.1.3 Magnetic Tape Multiple Sequencing

With the tape speed used, words of 48 bits are processed 90 microseconds apart. The magnetic core storage having an access time of 12 microseconds permits several magnetic tape units to be processed concurrently. Also this permits computer operations to be performed concurrently with Magnetic Tape processing. The programming control link which permits this, is a combination of the special skip instruction and jumps.

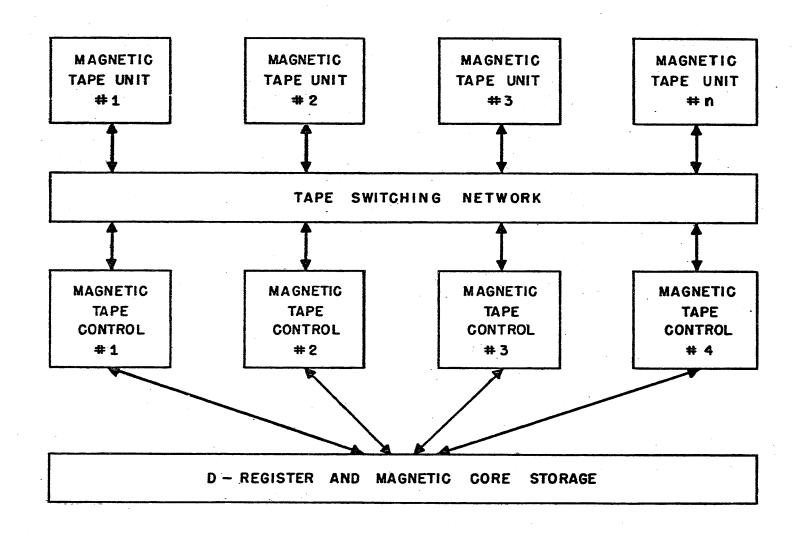

The Magnetic Tape Control Units are arranged as shown in Figure 9. The programmer selects the appropriate Tape Unit and an available Tape Control Unit is selected by the Multiple Sequencing Control.

### TABLE 1 OF SYSTEM INSTRUCTIONS

| (16 Bits)           | (8 Bits)           | (16 Bits)                | TRANSMI                               | г                                   |

|---------------------|--------------------|--------------------------|---------------------------------------|-------------------------------------|

| Starting<br>Address | Unit<br>Designator | Amount of<br>Information | (4 Bits)<br>From                      | (4 Bits)<br>To                      |

| On Drum             | Which Band on Drum | No.of Words              | Core                                  | Drum                                |

| On Drum             | Which Band on Drum | No.of Words              | Drum                                  | Core                                |

| On Drum             | Which Band on Drum | No. of Cards             | Card<br>(Reader)                      | Drum                                |

| On Drum             | Which Band on Drum | No. of Cards             | Drum                                  | Card<br>(Punch)                     |

| On Drum             | Which Band on Drum | No. of Words             | High Speed Paper Tape (Reader)        | Drum                                |

| On Drum             | Which Band on Drum | No. of Words             | Drum                                  | High Speed Paper Tape (Punch)       |

| On Drum             | Which Band on Drum | No.of Words              | Flexowriter (keyboard or tape reader) | Drum                                |

| On Drum             | Which Band on Drum | No.of Words              | Drum                                  | Flexowriter (printer or tape punch) |

# TABLE 1 (Cont'd)

| (16 Bits)           | (8 Bits)             | (16 Bits)                | TRANSMIT                           |                                                |  |

|---------------------|----------------------|--------------------------|------------------------------------|------------------------------------------------|--|

| Starting<br>Address | Unit<br>Designator   | Amount of<br>Information | (4 Bits)<br>From                   | (4 Bits) To                                    |  |

|                     | Which Tape Transport | No. of Blocks            | Magnetic Tape (Forward or Reverse) | Core                                           |  |

|                     | Which Tape Transport | No. of Blocks            | Core                               | Magnetic Tape (Forward)                        |  |

|                     | Which Tape Transport |                          |                                    | Magnetic Tape (Rewind with or without lockout) |  |

|                     | Which Tape Transport | No. of Blocks            |                                    | Magnetic Tape Space (Forward or Reverse)       |  |

| Starting<br>Block   | Which Bin            | No. of Blocks            | Core                               | Magnetic Tape Bin File                         |  |

| Starting<br>Block   | Which Bin            | No. of Blocks            | Magnetic Tape Bin File             | Core                                           |  |

|                     |                      | No. of Words             | Core                               | High Speed Paper Tape (Punch)                  |  |

|                     |                      | No. of Words             | High Speed Paper Tape<br>(Reader)  | Core                                           |  |

# TABLE 1 (Cont'd)

| (16 Bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (8 Bits)           | (16 Bits)                | TRA                                   | NSMIT                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------|---------------------------------------|-------------------------------------|

| Starting<br>Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Unit<br>Designator | Amount of<br>Information | (4 Bits)<br>From                      | (4 Bits) To                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | No. of Words             | Flexowriter (Keyboard or Tape Reader) | Core                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | No. of Words             | Core                                  | Flexowriter (Printer or Tape Punch) |

| The state of the s |                    | No. of Cards             | Card Reader                           | Core                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | No. of Cards             | Core                                  | Card Punch                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                          |                                       |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                          |                                       |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                          |                                       |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                          |                                       |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                          |                                       |                                     |

MAGNETIC TAPE CONTROL UNIT FIG.8

ARRANGEMENT OF MAGNETIC TAPE CONTROL UNITS

FOR MULTIPLE SEQUENCING

FIG.9

When computer operations take place during a Magnetic Tape operation, the demands of Magnetic Tape on the Magnetic Core Storage are given precedence. Sequencing the Magnetic Core is controlled by the Multiple Sequencing Control.

When sequencing is used, a single sequencing unit TS-2150 and up to four (4) magnetic tape control units TC-2150 must be included in the system. If it is desired to have four (4) tapes reading or writing concurrently, then four (4) controllers must be used. If three (3) tapes are all that must be run concurrently, then only three (3) tape controllers are required. The total number of tapes that can be addressed by the sequencer is 16, of which up to any four (4) can be reading or writing at any one instant.

### 5.2 Magnetic Drum Unit

The Magnetic Drum Unit consists of the Drum Storage Cylinder and the Magnetic Drum Control Circuit.

## 5.2.1 Magnetic Drum Storage Cylinder

The drum has the following characteristics:

- l. Diameter 20 inches

- 2. Length 24 inches

- 3. No. of Channels 442

- 4. Recording Return to Zero

- 5. Speed 1740 r.p.m.

The Drum Storage is subdivided along its axis into eight bands, each of which has a capacity of 4096 48-bit words. This gives a total of 32,768/48-bit words. The bits within each word are arranged in parallel, while the words are arranged serially.

With 4096 words scanned in one revolution, the words occur approximately 8 microseconds apart. Since this is not compatible with the speed of the Magnetic Core Storage, consecutive addresses on the drum are interlaced to produce a speed of 16 microseconds between words.

Since one revolution of the Drum requires 34.5 milliseconds, the average time required to locate the starting address is 17.25 milliseconds. Any number of consecutive words may be transmitted between the Magnetic Core and Magnetic Drum by one System Instruction. Hence, once the starting address on the drum is located, transmission takes place at 16 microseconds between words. This is easily accomplished by the Magnetic Core Storage because of its asynchronous timing properties between the Read and Write cycles.

## 5.2.2 Magnetic Drum Control

The Magnetic Drum and its control are illustrated by the block diagram of Figure 10. For one System Instruction only one band is operated on. Hence, only one set of Read/Write amplifiers is needed. The heads of the drum are connected to the set of Read/Write amplifiers by the switching network as shown in Figure 10. The Read/Write amplifiers are then connected by controlled gates to the 48-bit Drum Buffer.

The words on the Drum are addressed by a binary counter which is clocked by a timing channel of the drum. The counter is checked each revolution by another timing channel.

The starting address is compared to the Drum address counter such that when coincidence occurs, the operation will start.

The Magnetic Drum also communicates with the paper tape and punch card devices, when they are used in the system. Since this does not involve the Magnetic Core Storage, once these System Instructions are set up in the appropriate devices, the computer continues independently. Because of the slower speeds of paper tape and punch card equipment, transmission takes place on a revolution basis with respect to the Drum. Under this condition, the Drum has an asychronous behavior since every revolution of the Drum does not have to be involved in a continuous transmission of several words.

MAGNETIC DRUM UNIT - BLOCK DIAGRAM

F1G.10

### 5.3 On-Line Punch Card System

The on-line punch card system can read punch cards into or out of the core memory or onto or off of the Magnetic Drum. When the system is working with the Magnetic Drum the central computer is free to continue with other processing. The on-line card system reads the cards in two modes - binary form in which the card is read or punched in pure binary, first 48 columns only, and the number of cards to be read or punched is controlled by the input/output instruction. The second mode is reading or punching the cards in IBM Card Code. When the mode is selected, columns to be read or punched can be selected by a plug board and the number of cards to be read or punched is controlled by the input/output instruction. The card reader can handle 200 cards per minute and the card punch 100 cards per minute.

# 5.4 The Paper Tape System

In the On-Line system, the devices which employ a perforated paper tape medium of storage share a control unit as shown in Figure 11. The Paper Tape Control unit is similar to the Magnetic Tape Control unit except that 7-bit instead of 12-bit information is handled at one end. The Editing Control, therefore, converts 8 6-bit characters into a 48-bit word in one direction, and converts a 48-bit word into 8 6-bit characters in the other direction.

The format for paper tape is illustrated in Figure 12, where one frame contains a six-bit character, a parity bit check and a sprocket channel.

## 5.4.1 High Speed Paper Tape Reader

The High Speed Paper Tape Reader operates at a speed of 200 characters per second. Because of the photoelectric system, the characters are also read while the tape is getting up to speed, and actually can read a character while the tape is stationary. This means that information on the tape does not have to be broken up into blocks. Provisions are made to pass blank tape (leads).

In view of the high speed of the tape, wear of tape is minimized by the use of the photoelectric reading system and a friction drive arrangement for the tape feed.

If the tape is twisted or otherwise prevented from passing through the reader in the correct manner, it will slip in the mechanism without being torn. Tests have shown that a tape can be passed 10,000 times through the reader without appreciable wear, and a spliced tape passes through the machine without difficulty. The tape may be left stationary in the reading position without fear of damage by burning.

# 5.4.2 High Speed Paper Tape Punch

The High Speed Paper Tape Reader operates at a speed of 3600 characters per minute. This is a synchronous device. The Magnetic Core and Magnetic Drum have an asynchronous behavior at this speed which means that large buffers are not required. When communication is desired between a paper tape device and the Magnetic Drum, the Computer continues to operate independently, unless otherwise decided by the programmer.

Figure 11 Paper Tape ControlUnit

Figure 12. Paper Tape Format

#### 5.4.3 Flexowriter

A standard Flexowriter which consists of a keyboard, printer, Paper Tape Reader and Paper Tape Punch is used. It may be desirable to interrogate the computer during diagnostic operations, by means of the keyboard and at the same time print hard copy or punch a tape to record the activity. On the other hand, during this type of operation information may be desired from the computer which also results in typed hard copy or punched tape.

The Flexowriter printing mechanism can type a maximum of 86 different characters from 43 type bars shiftable to type from either of two characters on each bar. The Tape Reader is set to automatically operate the Flexowriter at a nominal speed of 571 characters per minute.

## 5.5 Console Typewriter

When an On-Line Paper Tape System is not included in the system an electric typewriter is connected to the console to permit the operator to interrogate the computer during diagnostic operations and to generate a hard copy of such interrogations for the record.

## 6. OFF-LINE INPUT-OUTPUT EQUIPMENT

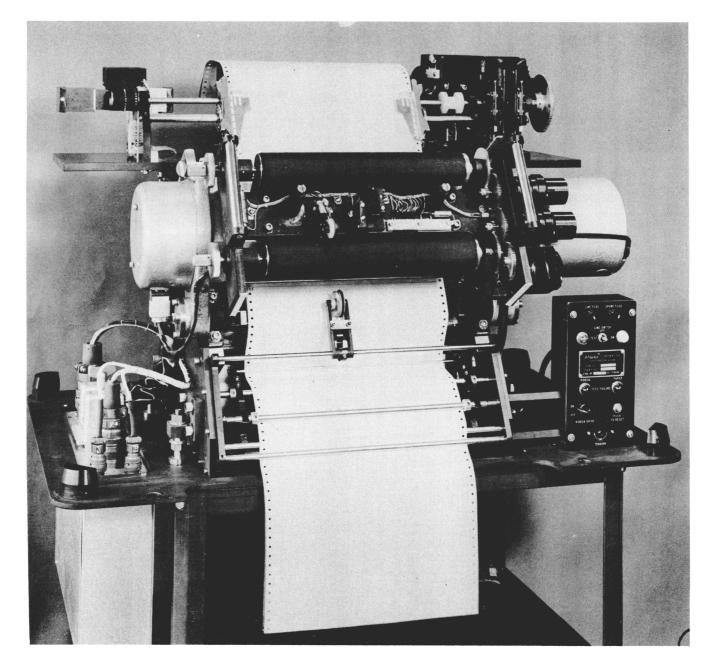

The off-line system prepares data from some external source such that it is easily processed by the on-line system. It then takes data from the on-line system and produces it in a form compatible with the application at hand. Since Magnetic Tape is the major storage medium of the on-line system, the off-line system is concerned primarily with writing information on or reading information from Magnetic Tape to some other medium. In general, this is accomplished in a manner as illustrated by Figure 13. With a fixed block length format for magnetic tape, a Block Buffer which has a capacity of 1024 characters is used. The slow device in Figure 13 may be a High Speed Printer, card equipment or some other input/output device depending on the requirements of the particular installation. Hence, the fundamental equipment necessary for most of these applications is the combination of Block Buffer, Magnetic Tape Control Unit, and the Magnetic Tape Unit.

### 6.1 High Speed Printer

The High Speed Printer system consists of a standard tape unit as described in section 5 above, a Tape Controller, a Block Buffer, Format Editor, Line Buffer and High Speed Printer as described in the block diagram of Figure 14.

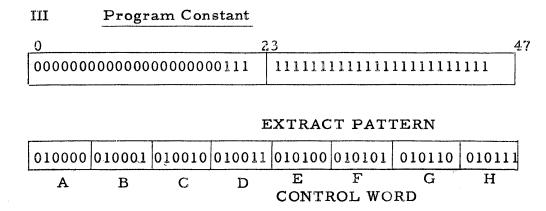

A block of magnetic tape information is read into the Block Buffer. Then the Format Editor takes control and distributes the information to the Line Buffer to be printed. The Format Editor consists of a stored program whose instructions have an address and a command. There are 10 bits allocated for the address portion and 2 bits for command; except in the case where the address portion is not used to address the Buffer, in which case 3 bits are allocated to command. The instructions are stored in the Block Buffer along with the Magnetic Tape information. The Format Editor is illustrated by the block diagram of Figure 15. The instructions include:

- 1. Advance Character Position (column) Counter number of positions indicated 7 bits of address. This command also loads a blank space code in the Line Buffer at each position skipped.

- 2. Transfer Data (addressed by A) to Line Buffer position indicated by character position counter.

Figure 13. Block Diagram of Generalized Off-Line System

Figure 14 Block Diagram of High-Speed Pointer System

Figure 15 Block Diagram of Format Editor

- 3. Transfer 6 bits of address to Line Buffer position indicated by character position counter.

- 4. Set Format Counter to (A). This is a counter which controls the number of times a loop should be performed.

- 5. Jump to instructions whose address is given by "A" if Format Counter is not equal to zero.

Instruction 4 and 5 permits placing the same information in several locations on a line or on subsequent lines.

- 6. Transfer Vertical Format Control to paper loop channel whose address is given by "A".

- 7. Printing of block is complete. Line counter should equal address "A".

- 8. Start of new field zero suppression. This command sets the zero suppression circuit so that all zeros are suppressed and in their place a blank space code is loaded into the Line Buffer up until the first significant figure is transferred.

Vertical Format Control is accomplished by a perforated 7 channel tape photo electric sensed. This permited selecting 7 different vertical formats and the loop can be varied in length to handle up to 20 inch forms.

Checks. Parity bit check of information transfers from tape to Block Buffer and Block Buffer, and Block Buffer to Line Buffer.

Firing Circuit Count.

Lines per Block Count.

Line Buffer Load Count.

This type of Format Editor gives the maximum in control. It produces the following features:

(1) Format Control is read into the instruction storage from magnetic tape. It may be contained on the leader of the tape which contains the information to be printed. Hence set up time is minimized. The Format Program can be modified by means of a pushbutton register on the Printer Control Panel.

- Several different types of reports can be made from the same data tape by altering the program. Special symbols and punctuation can be inserted by the Format Editor and, therefore, do not have to be inserted in the data tape by the central computer.

- (3) Suppresssion of zeros to the left of significant digits. For example:

25.00 instead of \$00025.00, would be printed.

- Arbitrary arrangement of characters on the printed form (4)independent of their occurrence on the magnetic tape.

- (5) No preparation necessary in the On-line System for tape to be printed.

The output of the system is printed copy on a weight paper up to and including card stock.

Two models are available, one handles 160 columns and the other 120 columns with 4 horizontal spacing of ten characters per inch. The vertical spacing is six lines per inch. The characters which can be printed are 26 alphabetic, 10 numeric, and 20 symbols. The symbols can be selected to meet specific applications. Listed here is one set of symbols available.

> = - Equal Sign # - Number Sign \* - Asterisk

\$ - Dollar Sign , - Comma

" - Quotation Marks

% - Percent Sign . - Period

; - Semicolon ? - Question Mark

& - And Sign @ - At or Per

' - Apostrophe / - Diagonal Line or Slash

( - Left Parenthesis - - Hyphen or Minus Sign

) - Right Parenthesis ¢ - Cent Sign