# TECHNICAL MANUAL

Lansac.

5-2000

PHILCO CORPORATION

COMPUTER AND AUTOMATION DEPARTMENT

4700 WISSAHICKON AVENUE

PHILADELPHIA 44, PENNSYLVANIA

#### PREFACE

The S-2000 Technical Manual is primarily intended for training and reference use by TRANSAC Field Engineers. It can be used as well by other groups desiring a detailed description of the system.

The material is arranged to facilitate study and will serve as a comprehensive technical introduction to TRANSAC S-2000. The scope of this manual excludes those areas covered by other S-2000 publications, as the Programming Manual.

Inquiries concerning this manual should be directed to

Jerome Stone

Computer and Automation Department

# TRANSAC S-2000 TECHNICAL MANUAL

# PART 1 COMPUTER LOGICAL DESCRIPTION

# TABLE OF CONTENTS

|    |      |                                                 | Page   |

|----|------|-------------------------------------------------|--------|

| 1. | ORGA | ANIZATION OF THE COMPUTER                       | 1.1-1  |

|    | 1.1  | Block Diagram, Information Storage and Control. | 1.1-1  |

|    | 1.2  | Control Organization                            | 1.2-1  |

|    | 1.3  | Control Registers                               | .1.3-1 |

|    | 1.4  | Commands                                        | 1.4-1  |

|    | 1.5  | Numbers - Control Signals                       | .r.5-1 |

| 2. | INTR | ODUCTION TO TRANSAC LOGIC                       | 2.1-1  |

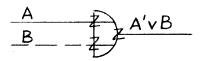

|    | 2.1  | S-2000 Symbolism, Logical Circuits              | 2.1-1  |

|    | 2. 2 | Notation for Schematic Logic                    | .2.2-1 |

| 3. | INST | RUCTION SELECTION AND PERFORMANCE               | 3.1-1  |

|    | 3.1  | Basic Program Cycle                             | 3.1-1  |

| 4. | COM  | PUTER CONSOLE AND OPERATING                     | 4.1-1  |

|    | 4.1  | Console and Operating Controls                  | 4.1-1  |

|    | 4.2  | Operational Modes                               | 4.2-1  |

| 5. | LOGI | C SECTIONS OF COMPUTER                          | 5.1-1  |

|    | 5.1  | Adder Networks                                  | 5.1-1  |

|    | 5.2  | Registers                                       | 5.2-1  |

# Table of Contents (continued)

|           |      |         |                                   | Page      |

|-----------|------|---------|-----------------------------------|-----------|

| <b>5.</b> | DETA | ILED LC | OGIC OF INSTRUCTIONS              | 6.1-1     |

|           | 6.1  | Organiz | zation of Instruction Control     | 6. 1-1    |

|           | 6.2  | Addres  | s Modification by Index Registers | 6.2-1     |

| e y       | 6.3  | Memor   | y Control and Use                 | 6.3.1-1   |

|           |      | 6.3.1   | Memory Cycle                      | 6. 3. 1-1 |

|           |      | 6.3.2   | Computer Use of Memory            | 6, 3.2-1  |

|           |      | 6.3.3   | Memory Assignment                 | 6.3.3-1   |

|           | 6.4  | Transfe | ers                               | 6.4-1     |

|           | 6.5  | Shifts  | •••••••••••                       | 6.5-1     |

|           | 6.6  | Arithm  | etic                              | 6.6-1     |

|           |      | 6.6.1   | Add Instructions                  | 6. 6. 1-1 |

|           |      | 6.6.2   | Subtract Instructions             | 6.6.2-1   |

|           |      | 6.6.3   | Multiply Instructions             | 6.6.3-1   |

|           |      | 6.6.4   | Divide Instructions               | 6.6.4-1   |

|           |      | 6.6.5   | Floating Point Numbers            | 6.6.5-1   |

|           |      | 6.6.6   | Add, Subtract, Floating Point     | 6.6.6-1   |

|           |      | 6.6.7   | Multiply, Floating Point          | 6.6.7-1   |

|           |      | 6.6.8   | Divide, Floating Point            | 6.6.8-1   |

|           |      | 6.6.9   | Inhibit Clear of Overflow         | 6.6.9-1   |

# Table of Contents (continued)

|                                                     |                                                               |                                                                                                                                                  | Page    |  |

|-----------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| 6.7                                                 | Jumps                                                         |                                                                                                                                                  | 6.7.1-1 |  |

|                                                     | 6.7.1                                                         | Jump Instructions                                                                                                                                | 6.7.1-1 |  |

|                                                     | 6.7.2                                                         | Comparison Logic for Conditional Jumps                                                                                                           | 6.7.2-1 |  |

| 6.8                                                 | Repeat                                                        |                                                                                                                                                  | 6.8.1-1 |  |

|                                                     | 6.8.1                                                         | Repeat Instruction                                                                                                                               | 6.8.1-1 |  |

|                                                     | 6.8.2                                                         | Repeat Mode                                                                                                                                      | 6.8.2-1 |  |

|                                                     | 6.8.3                                                         | Index Register Modification, Repeat Counter                                                                                                      | 6.8.3-1 |  |

|                                                     | 6.8.4                                                         | No Op (Filler)                                                                                                                                   | 6.8.4-1 |  |

| 6.9                                                 | Index F                                                       | Register Instructions                                                                                                                            | 6.9-1   |  |

| 6.10                                                |                                                               | ss Substitution and Increase, IIJ, INCA                                                                                                          | 6.10-1  |  |

| 6.11                                                | Refere                                                        | nce Change, LWD, SWD                                                                                                                             | 6.11-1  |  |

| 6.12                                                | Bit-by-bit Boolean Extract, Insert, Word Merge 6.12-1         |                                                                                                                                                  |         |  |

| 6.13                                                | _                                                             | ter Stop struction, Command Fault                                                                                                                | 6.13-1  |  |

| 6.14                                                |                                                               | e Transfers, Register, Typewriter                                                                                                                | 6.14-1  |  |

| Append:<br>Append:<br>Append:<br>Append:<br>Append: | ix II - A<br>ix III - A<br>ix IV - G<br>ix V - I<br>ix VI - I | able of Powers of 2 Alphanumeric Coding S-2000 Instructions Control Register States Definitions of Numbers I/O Commands TRANSAC S-2000 Symbolism |         |  |

# LIST OF ILLUSTRATIONS

| Figure  | Title                                    | Page                   |

|---------|------------------------------------------|------------------------|

| 1.1-1   | Block Diagram Central Computer           | 1.1-2                  |

| 1.3-1   | Flow Diagram of Computer Timing          | 1.3-8                  |

| 1.3-2   | Timing Chain                             | 1.3-11                 |

| 1.4-1   | Command Decoding                         | 1.4-6                  |

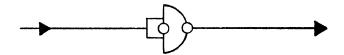

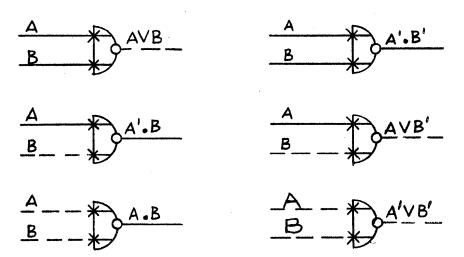

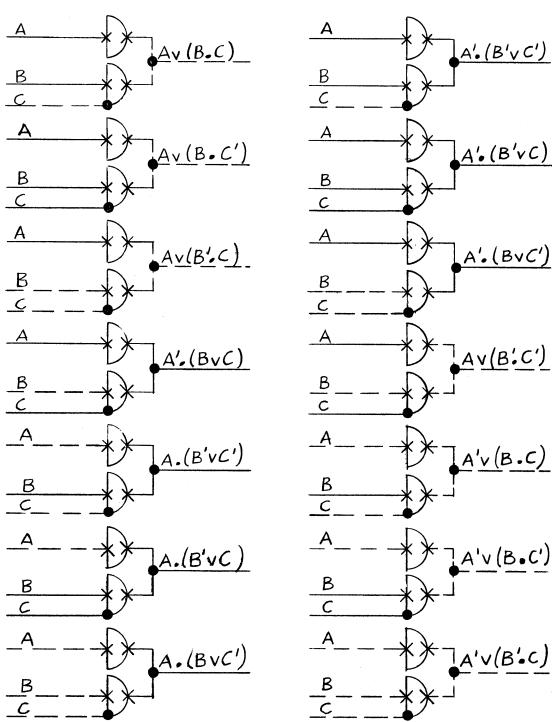

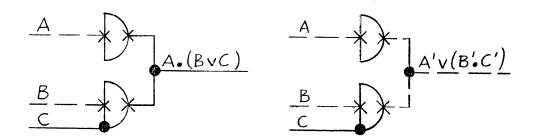

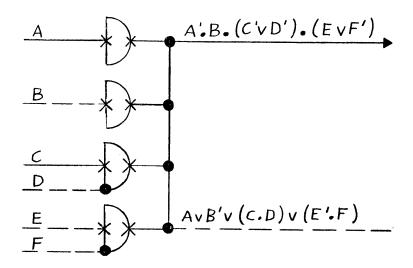

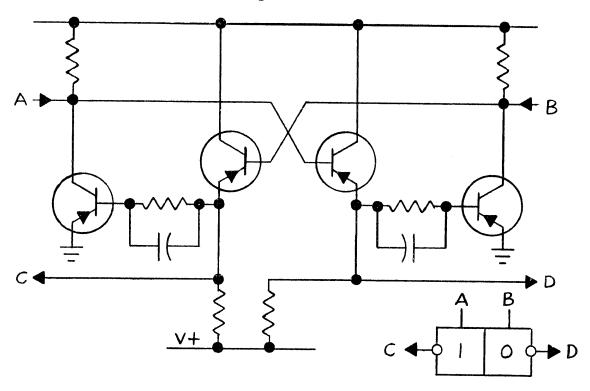

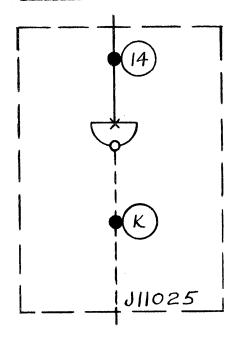

| 2.1-1   | Inverter                                 | 2.1-1                  |

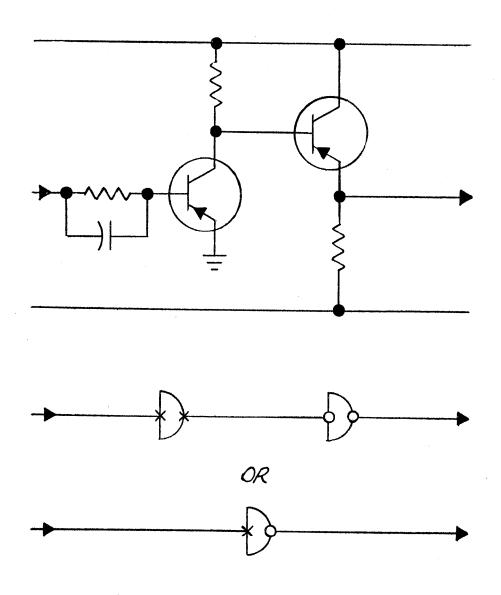

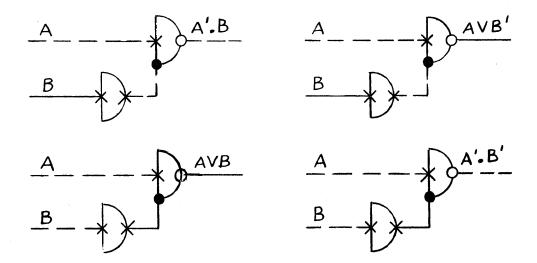

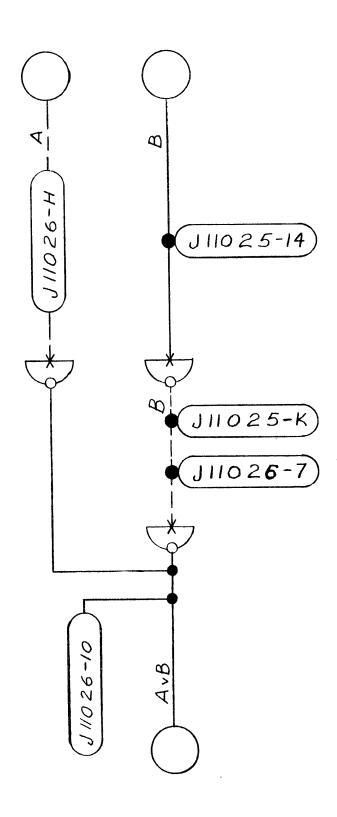

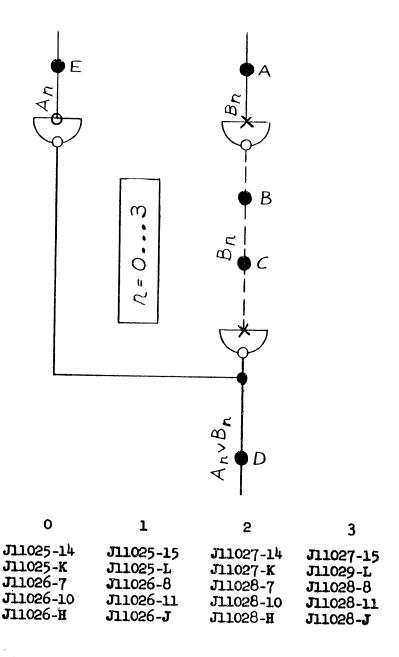

| 2.1-2   | Parallel RC Gate                         | 2.1-1                  |

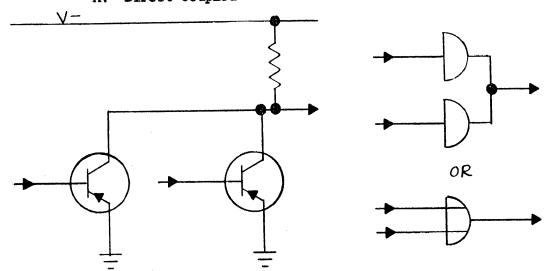

| 2.1-3   | Parallel Emitter Follower Gate           | 2.1-2                  |

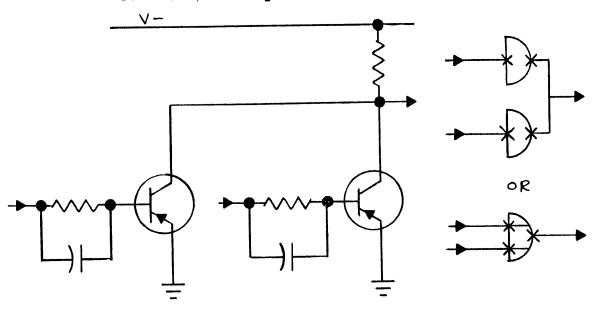

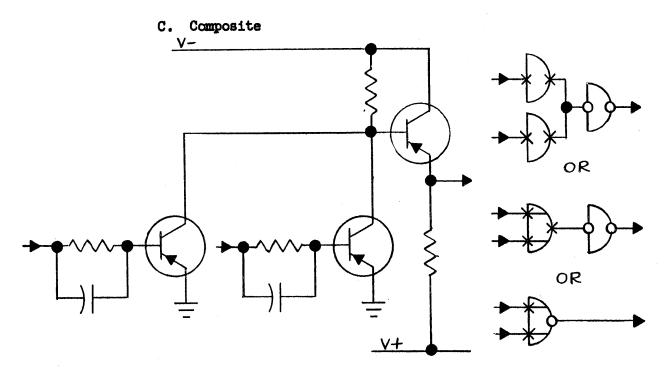

| 2.1-4   | Parallel Emitter Follower OR Gate        | 2.1-2                  |

| 2.1-5   | Series Gate                              | 2.1-3                  |

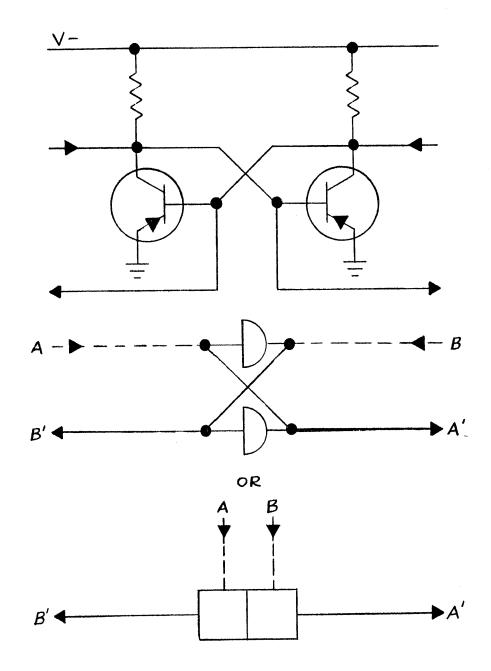

| 2.1-6   | Exclusive OR                             | 2.1-3                  |

| 2.1-7   | Exclusive OR                             | 2.1-4                  |

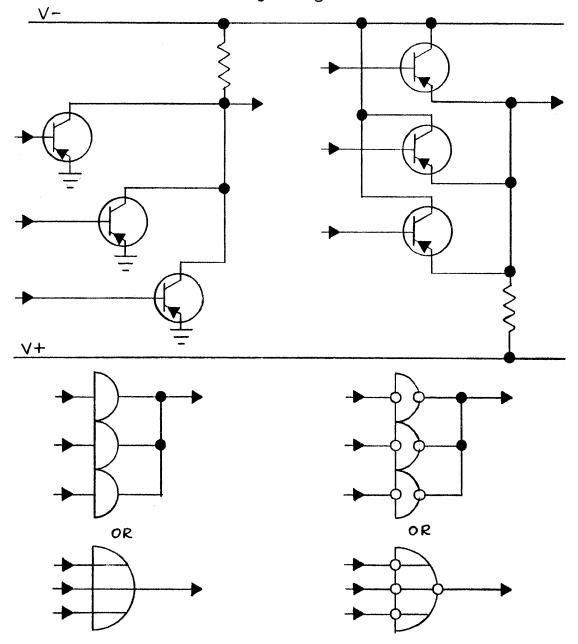

| 2.1-8   | Exclusive OR                             | 2.1-4                  |

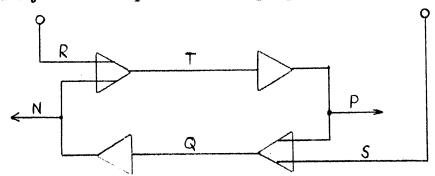

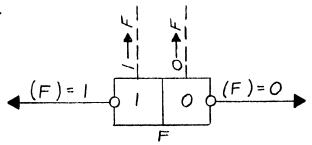

| 2.1-9   | Standard Flip-flop                       | 2.1-6                  |

| 2.1-10  | Single Shot Timing Chain                 | 2.1-6                  |

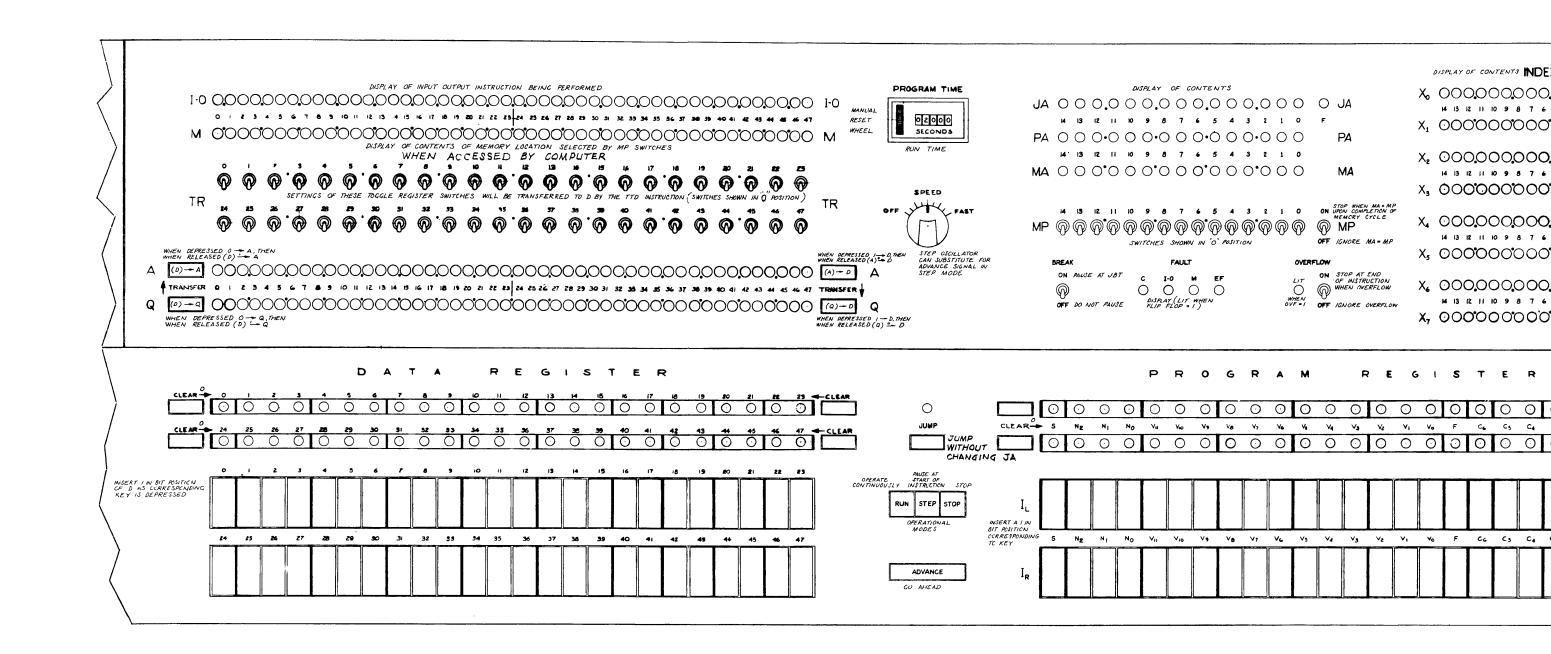

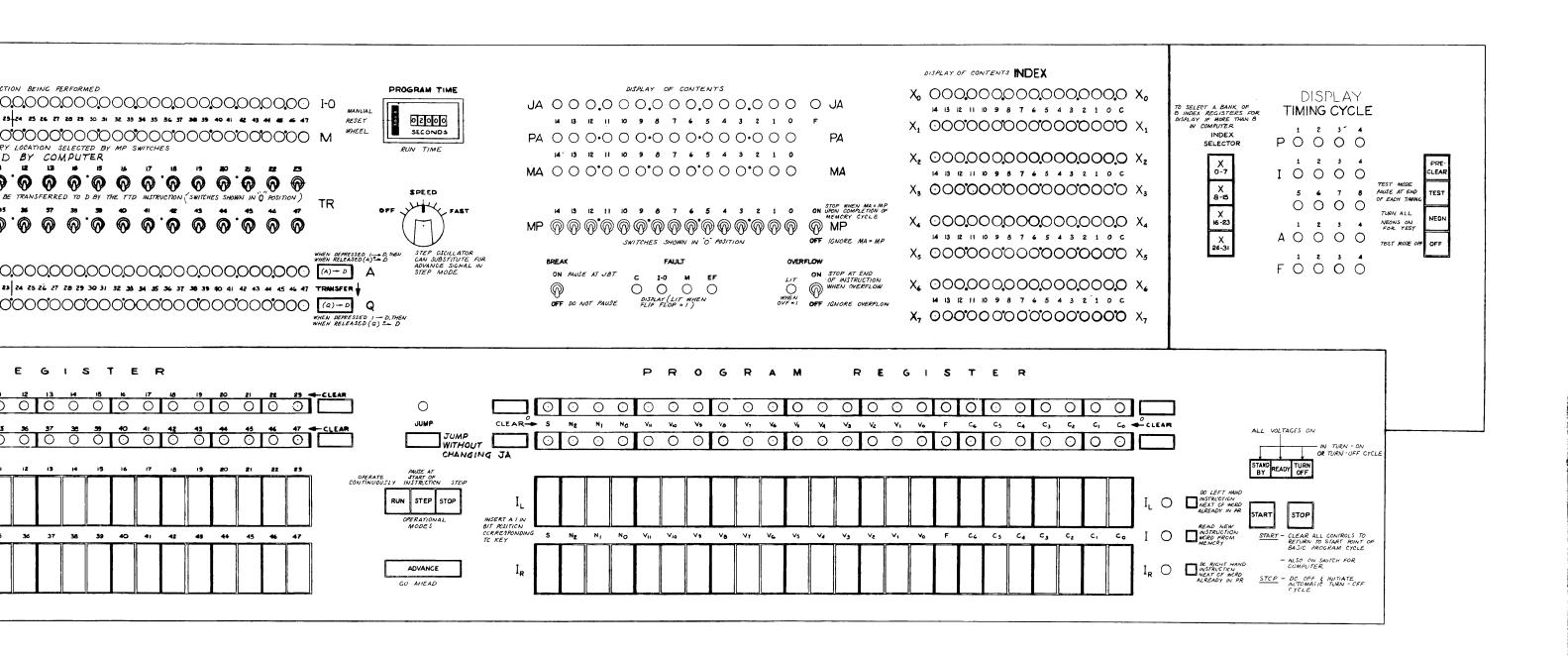

| 4.1-1   | S=2000 Console                           | 4.1-2                  |

| 4.1-2   | Console Controls Partial                 | 4.1-7                  |

| 4.2-1   | Front Panel Controls                     | 4.2-2                  |

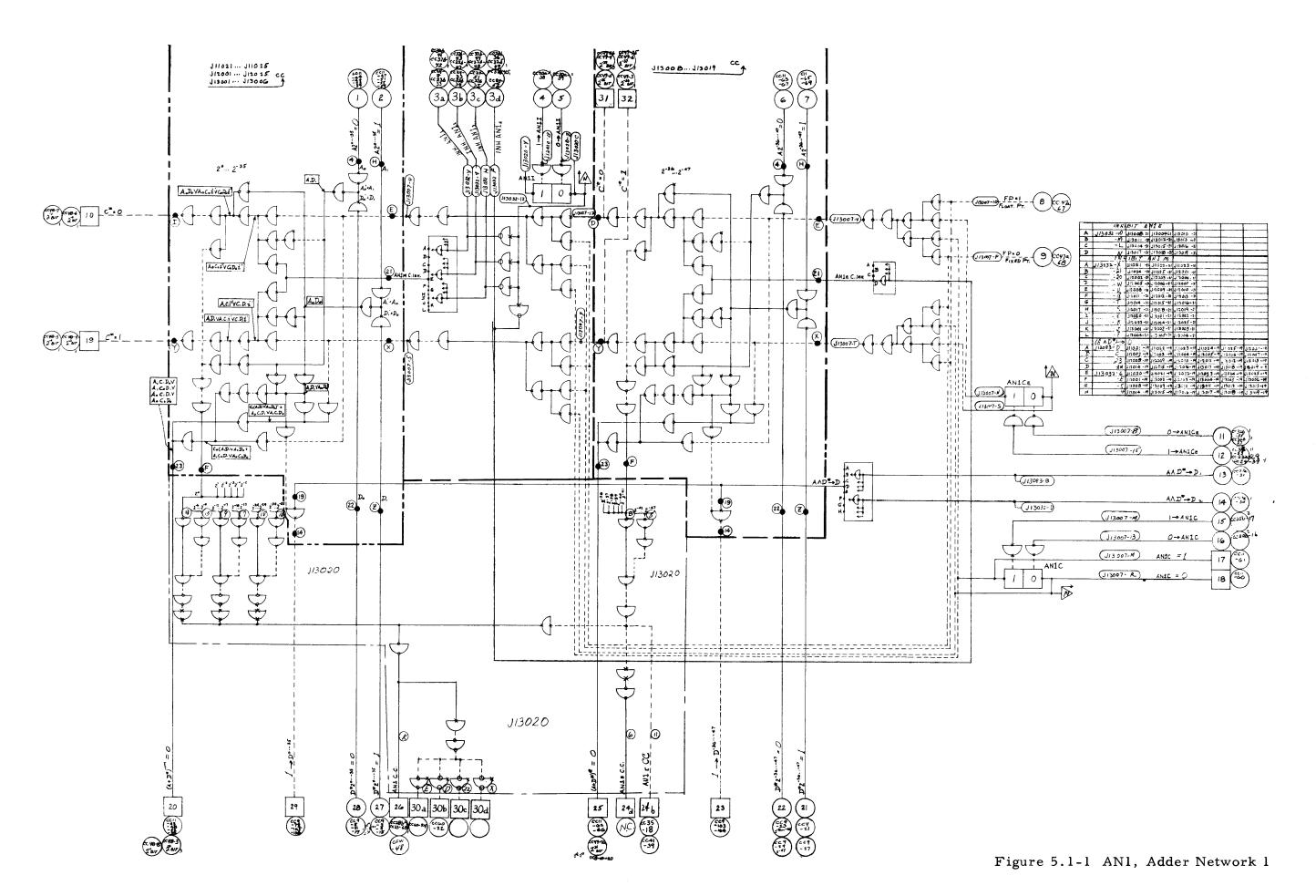

| 5.1-1   | AN1, Adder Network 1                     | 5.1-2                  |

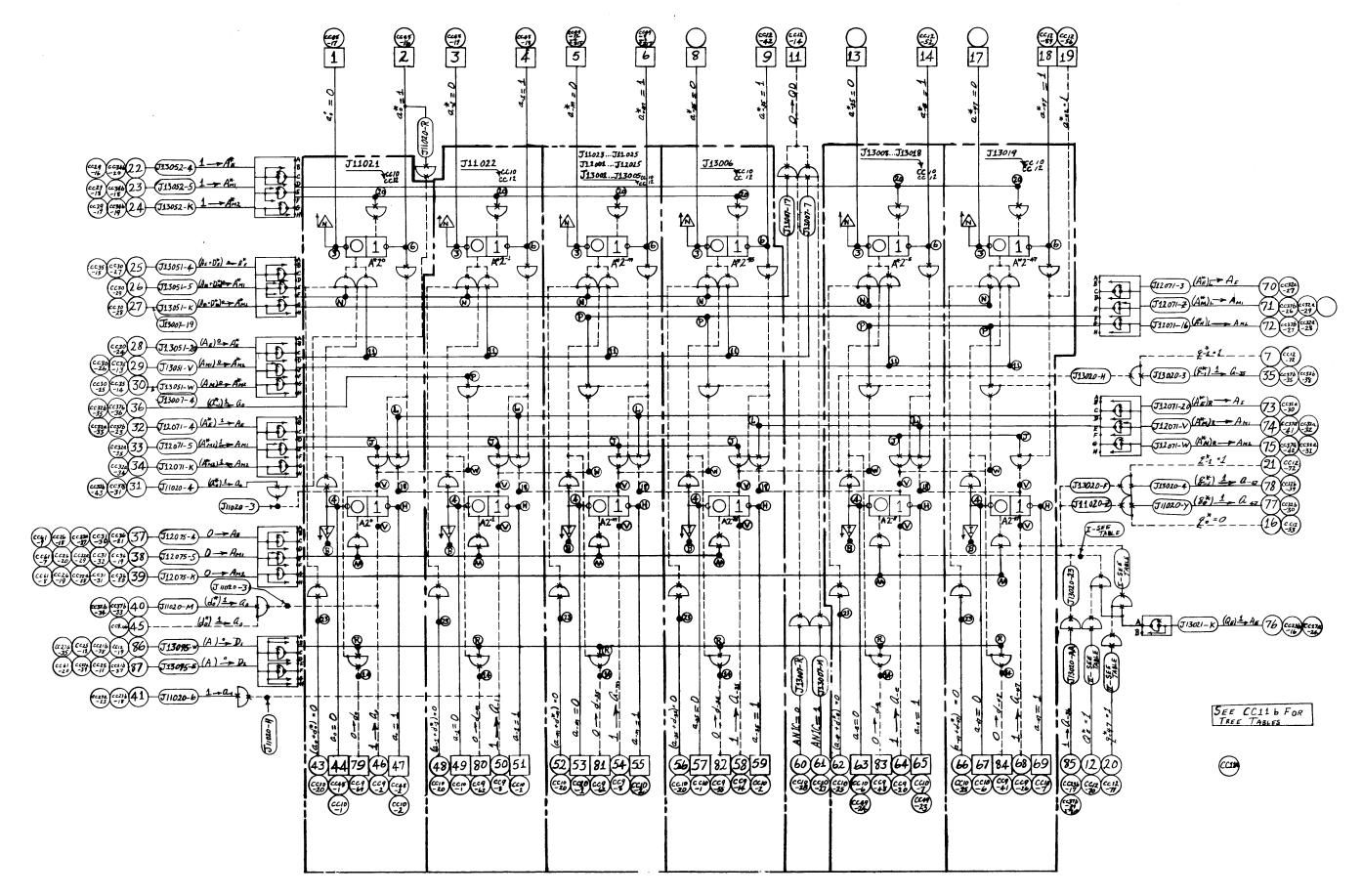

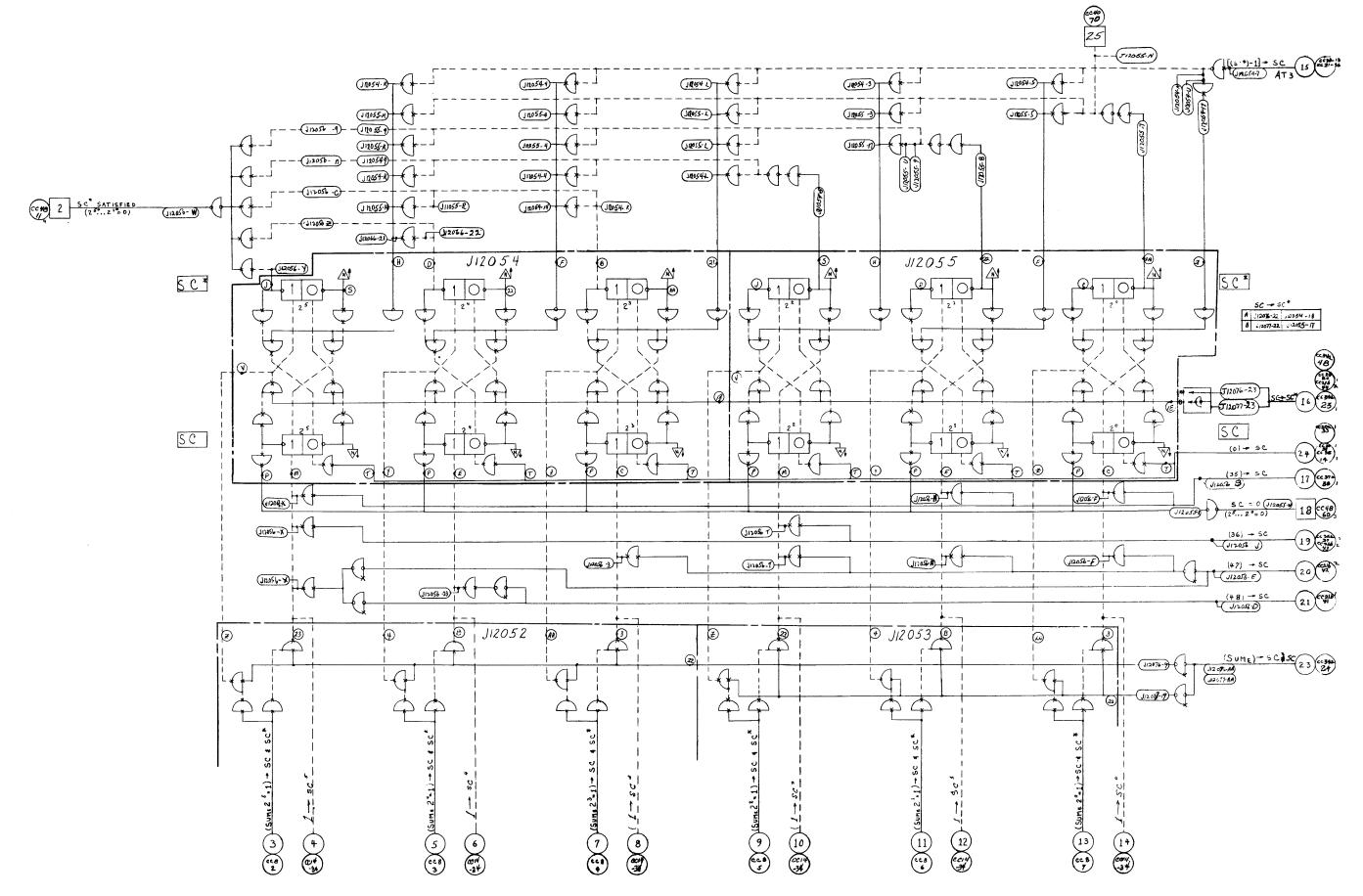

| 5.2-1   | Schematic Logic A, A* Registers          | 5.2-2                  |

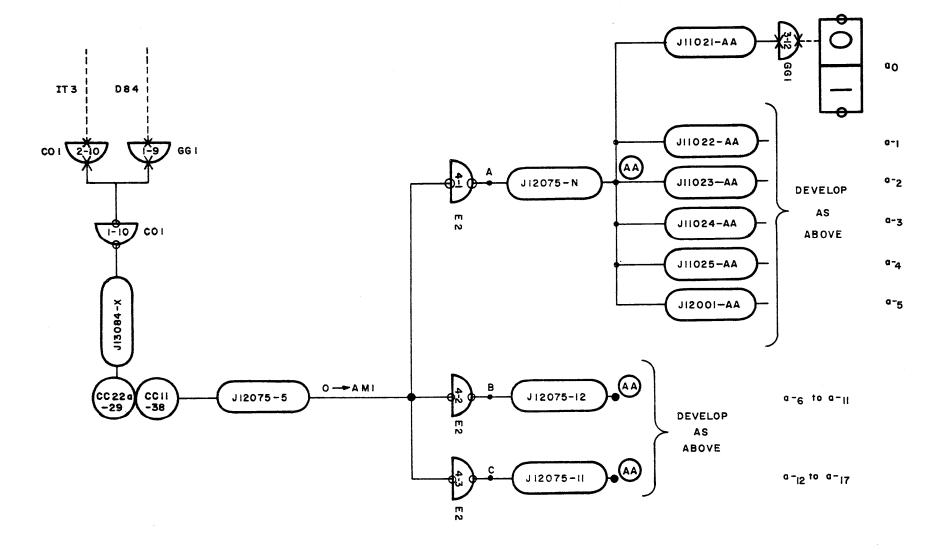

| 5.2-2   | Tree (Partial) for $O \longrightarrow A$ | 5.2-4                  |

| 6.2-1   | Address Fields                           | 6.2-1                  |

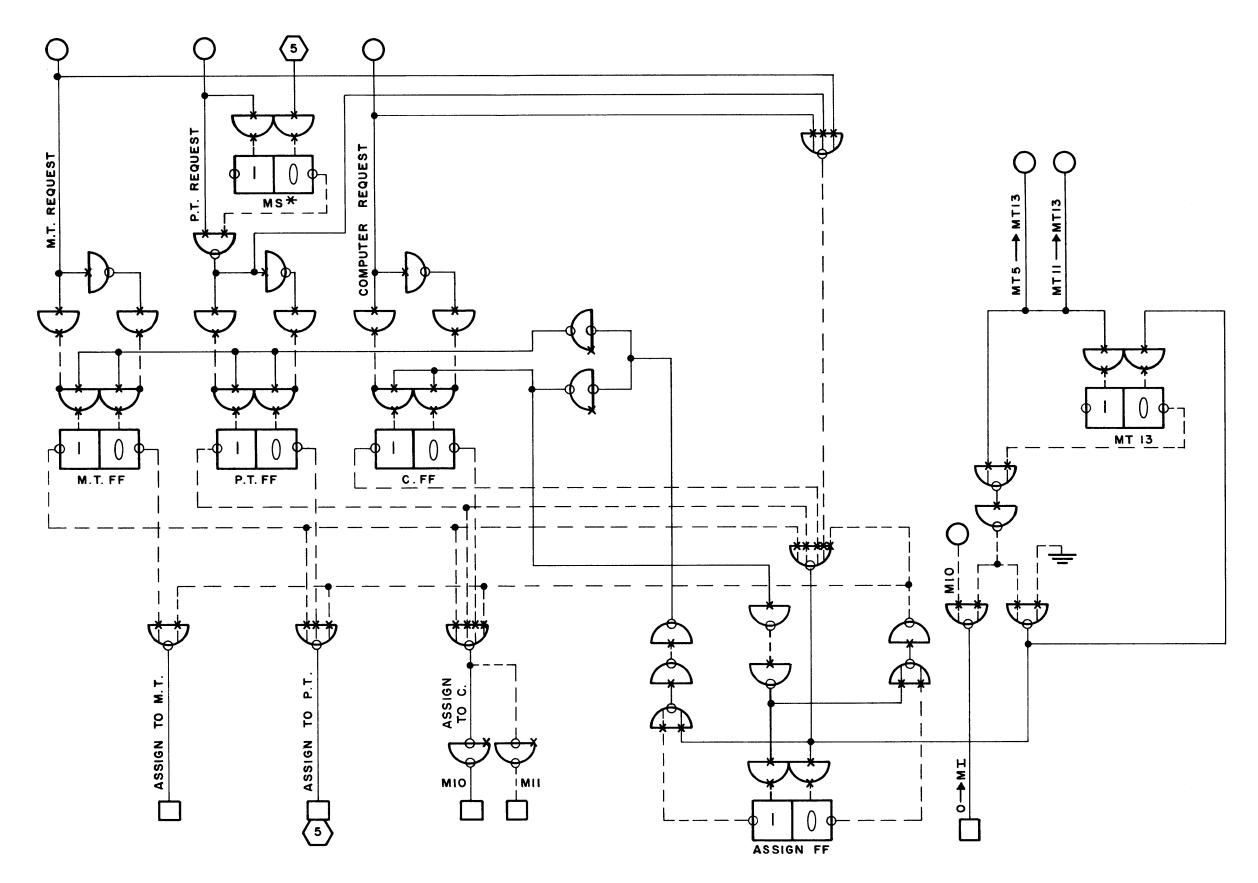

| 6.3.2-1 | Computer Use of Memory                   | 6.3.2-4                |

| 6.3.3-1 | Memory Assignment Control                | 6.3.3-3                |

| 6.5-1   | S-2000 Shifts                            | 6.5-2                  |

| 6.5-2   | Shift Counter                            | 6.5-6                  |

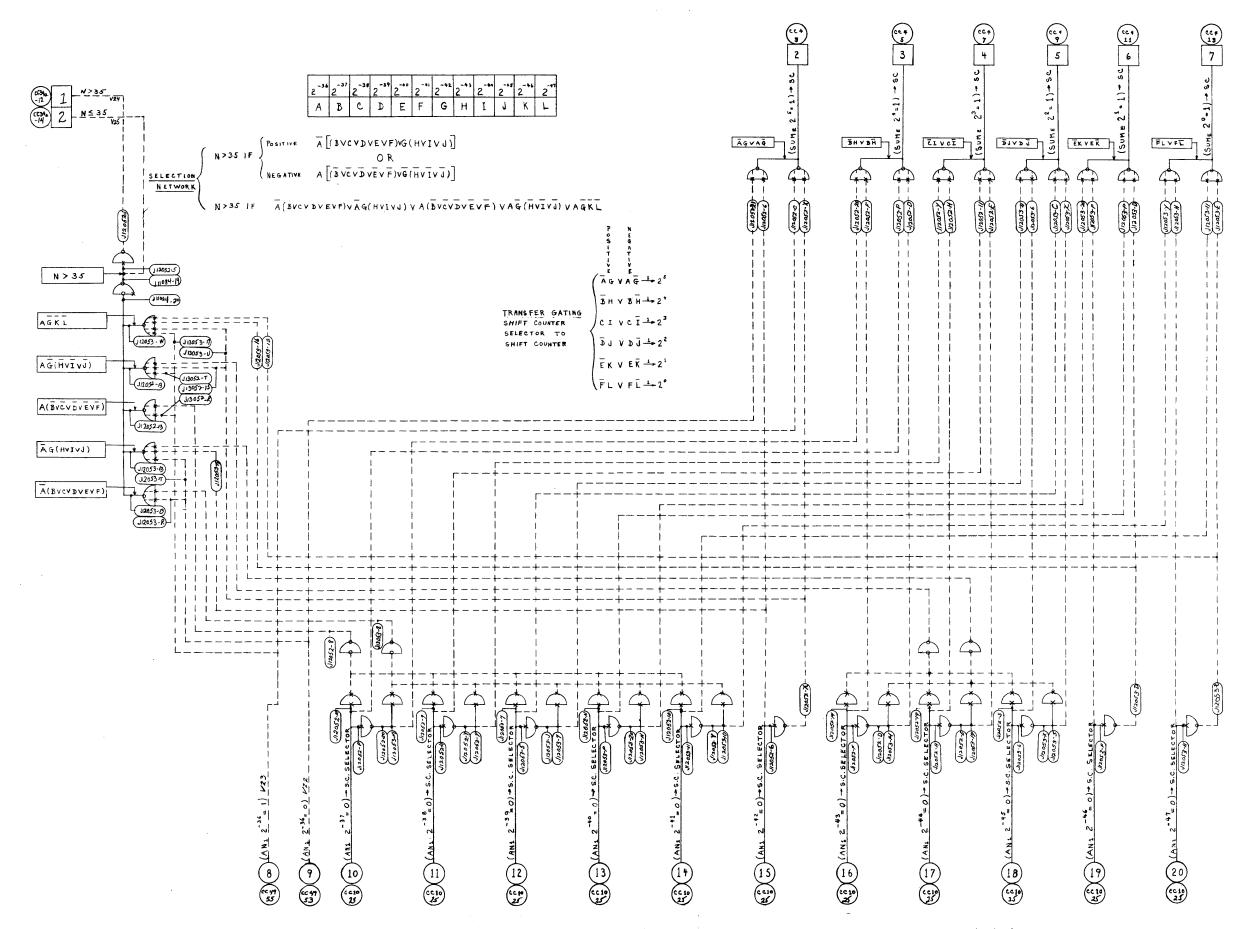

| 6.6.6-1 | Shift Counter Selector                   | 6. 6. 6 <sub>-</sub> 5 |

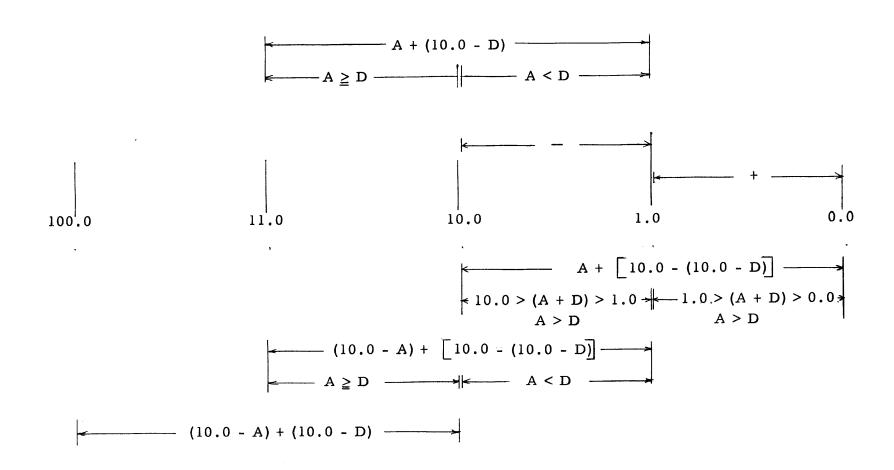

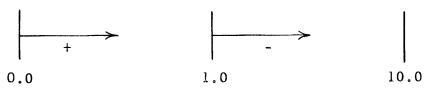

| 6.7.2-1 | Ranges of Sums, Algebraic Comparison     | 6. 7. 2-4              |

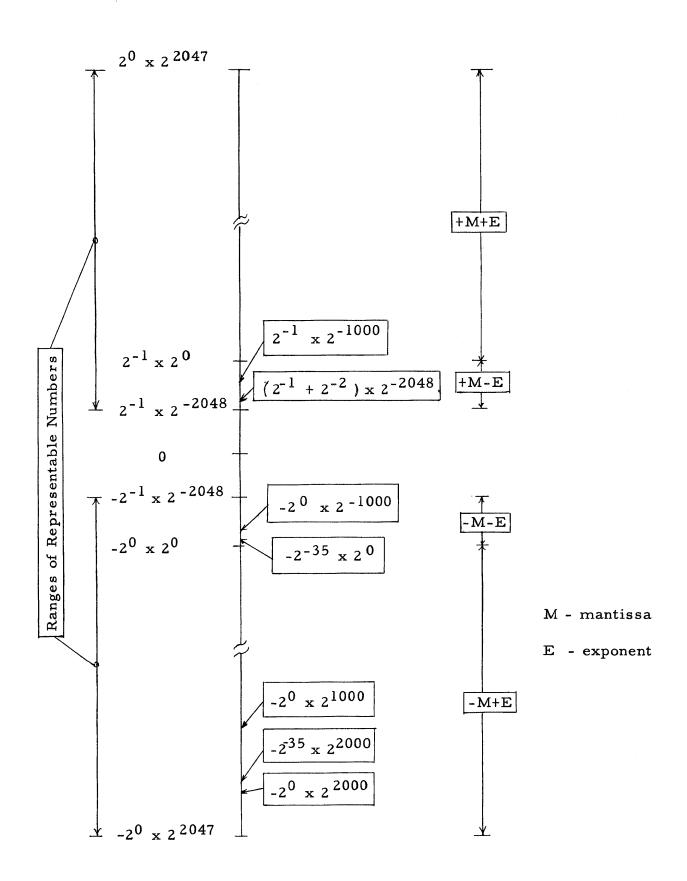

| 6.7.2-2 | Floating Point Numbers                   | 6.7.2-9                |

| 6.8.3-1 | Normal Program Control Sequencing        | 6.8.3-2                |

| 6.8.3-2 | Index/Repeat Program Control Sequencing  | 6 8 3 3                |

# LIST OF TABLES

| Table   | Title                                      | Page     |

|---------|--------------------------------------------|----------|

| 1.1-1   | Location of Arithmetic Operands            | 1.1-8    |

| 1, 3-1  | Triggers for the Timings                   | 1.3-13   |

| 5.2-1   | Tree Tables                                | 5.2-5    |

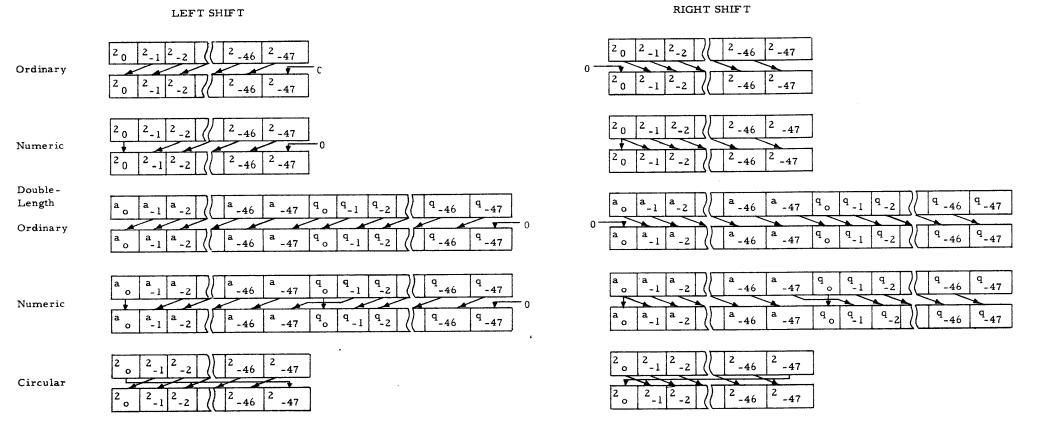

| 6.5-1   | Shift Logic of Shift Instructions          | 6.5-4    |

| 6.6.4-1 | Overflow for Fixed Point Division          | 6.6.4-7  |

| 6.6.6-1 | Exponent Comparison for Add, Subtract      | 6.6.6-3  |

| 6.6.6-2 | Arranging Smaller Floating                 | 6.6.6-11 |

| 6.6.7-1 | Cases of Floating Point Products           | 6.6.7-2  |

| 6.6.8-1 | Division Faults                            | 6.6.8-5  |

| 6.7.1-1 | Organization of Jump Instruction           | 6.7.1-4  |

| 6.7.2-1 | Algebraic Comparison, Key Bit Values       | 6.7.2-6  |

| 6.7.2-2 | F. P. Algebraic Comparison, Key Bit Values | 6.7.2-7  |

| 6.7.2-3 | JAQF Exponent Comparison                   | 6.7.2-11 |

| 6.7.2-4 | JAQF Mantissa Comparison                   | 6.7.2-13 |

| 6.8.3-1 | PI States                                  | 6.8.3-8  |

| 6.12-1  | Logic of Bit-by-Bit Boolean                | 6.12-6   |

#### 1. ORGANIZATION OF THE COMPUTER

# 1.1 Block Diagram, Information Storage and Control

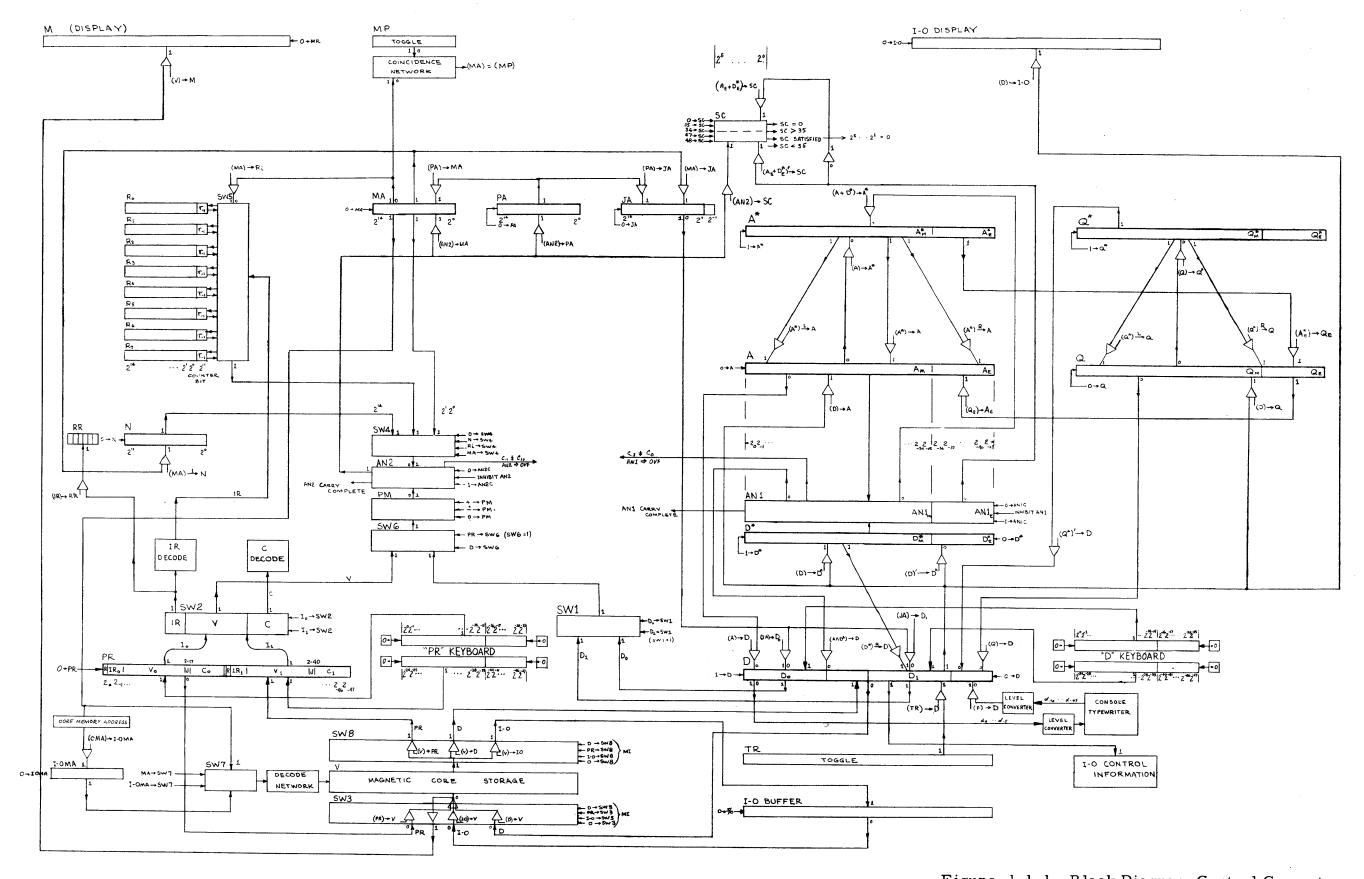

Figure 1.1-1 is a block diagram of the computer showing the major information storage registers, control and paths of information flow. The notes define some symbols which may be unfamiliar. This section describes the various units shown to give an overall view of the functions of the computer.

#### Control Information Storage

The organization of the control section of the central computer requires the following registers for storage of control information. The abbreviation follows the name of the register.

# Program Register (PR)

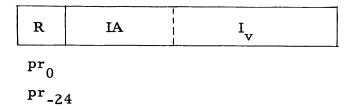

The instruction about to be, or currently being, performed is located in the Program Register. PR is a 48-bit register, storing an instruction word (two instructions). The input to PR is usually from the internally stored program in memory. Direct access into PR is also available from the console with the "PR Keyboard" manually operated switches. The left instruction location of PR (bits  $2_0$  through  $2_{-23}$ ) is identified as PR $_0$ . It contains the I $_0$  instruction. The other location, PR $_1$ , contains the I $_1$  instruction.

#### Switch 2 (SW2)

The selection of which of the pair of instructions in PR is to be operative is made by SW2. SW2 contains a flip-flop, with that name. When SW2 = 0,  $I_0$  is the operative instruction. Through SW2, the parts of the selected instruction are distributed among the various controls.

#### Switches

Functionally a switch as discussed here has two parts. The switch is a means of controlling a multitude of information signal lines that exist in a parallel computer. The control signal indicating the direction is a single line and it is usually desired to maintain the connection over a period of time.

Figure 1.1-1 Block Diagram Central Computer

The switch usually has one or more flip-flops which are set to the required state by the control signal. The flip-flop output(s) go to a large number of AND gates where they permit or inhibit the transfer of information. The selected source or destination of the information will thus be determined by the state of the flip-flops. Some switches do not use flip-flops for selection control. In this case a decode network serves as selection control.

SW2, for example, is a single flip-flop as its order of selection is twofold. The flip-flop inputs are two. Each side of the SW2 flip-flop goes to 24 gates by which means  $I_0$  or  $I_1$  is transferred from PR.

Distribution of the Parts of the Current Instruction

The command part of the instruction, C, is routed to the command decoding network. The memory address part of the instruction,  $I_{v^{\flat}}$  is routed to the Memory Address Register (MA) through the adder network, AN2 (a general purpose routing for this part of any instruction from PR to elsewhere in the control section). The index register address part of the instruction, IA, is routed to its decoding when an index register is involved in the instruction.

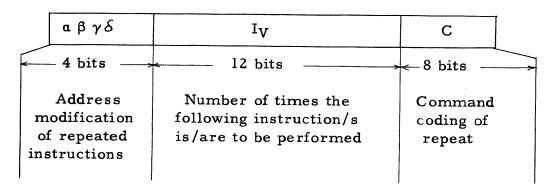

For the repeat instruction, the four leftmost bits, a  $\beta$   $\gamma$   $\delta$  (which indicate the type of repeat) are sent to the Repeat Register (RR) for control use. The I field of the repeat instruction, which indicates the number of times an instruction (or pair of instructions) is to be repeated, is sent to the Repeat Counter (N) by an indirect route via MA.

Adder Network for Control Information (AN2)

AN2 serves two basic functions. It is an adder network, one of the two in the central computer. The term, adder network, is used to signify a logical adder which has no registers, no storage capabilities. AN2 is used for addition or subtraction involving  $I_{\rm v}$  and IA parts of the instruction. (IA, in this case, is part of a memory address, rather than an index register address.

This function of AN2 requires it to be connected to many registers of the control section. These existing information transfer paths can therefore be used for transfers involving these registers without arithmetic operations with a resulting saving in circuitry. Arithmetic is avoided during such a transfer by simply gating only one, instead of two

register inputs to AN2. AN2 acts, for transfers, as a junction. Zeros are gated to the unused input.

#### AN2 Inputs

The inputs to AN2 are controlled by SW4 (Switch 4) and PM (Plus-Minus). SW4 is the means of selecting one of three sources as one input to AN2. They are N, MA, and X (selected index register). A fourth state of SW4 selects none of these; instead it gates zeros to AN2. SW4 contains two flip-flops.

PM also contains two flip-flops. It controls the other input to AN2 and can select either the number or its ones complement (for subtraction) as the quantity to be sent to AN2. If PM is "-" (one of the four states of the two flip-flops) the ones complement of the number is sent to AN2. If PM is "+", the number, uncomplemented, is transferred. If PM is "0", zeros are sent to this input.

# Address Register Size

In any individual S-2000 system the size of AN2, MA, PA, and X will be in accordance with the size of the memory in that system. As mentioned previously, X and JA each have an additional bit  $--x_c$  is the counter bit of an index register;  $ja_1$  is the half-word identification in JA.

# Index Registers (X = the selected index register)

The index registers store information which may be used to determine an effective address, in conjunction with the address part of the instruction. The effective address would be the actual one used in that particular performance of an instruction. At other times X, itself, can furnish the effective address. The index register can be incremented by 1, following each use, by means of the counter bit. When  $x_{C} = 1$  (counter bit = 1) the register contents will be so incremented.

Under the repeat mode, in addition to the above use, the index register can be "repeat modified". The index register alone furnishes the address, in this case, and following each instruction performance the register is either incremented or decremented by the contents of the "address" part of the instruction being repeated.

An S-2000 system may contain up to 32 index registers, in groups of four. Information is transferred by means of SW5. SW5 has no flip-flops bearing that name. Selection is made by the Index Register Decode network to gate information to or from X. The input is always through MA; X's output goes only to AN2 via SW4.

Incrementing or decrementing the register contents is achieved by a pass through AN2. The register has no separate counting ability.

The number into the PM gating is either from PR or the D register. SW6 controls this selection. SW6 = 1 selects PR; SW6 = 0 selects D. SW2 selects one of the two halves of PR;  $I_0$  or  $I_1$  as the input to the SW6 gating. SW1 performs a similar function for the D register. SW1 = 0 selects the  $D_0$  half; SW1 = 1 selects  $D_1$ . The D register has a connection to AN2 as it is used to handle control information (memory addresses) as well as its more common function of handling data.

Aside from the index registers, there are four other registers that store address information. MA contains the address currently used, or last used for memory access when the address was supplied by the central computer. Memory address can also be supplied by an input-output unit. In this case the I-O MA contains the current or last used address. The selection between MA and I-O MA is made at SW7.

PA (Program Address Register) stores the address of the next instruction word to be used. In the normal sequence this address is increased by one each time a new instruction word is transferred from memory. Jumps break this sequence; the address to which the program jumps is placed in PA during the execution of the jump instruction.

JA (Jump Address Register) might also be termed the "return address register". It is used to store the address of the next instruction in normal sequence that was not performed due to the program jump. This is required, as a common characteristic of programs is to leave the main part of the program, by means of a jump, to perform a sub-routine. Following the sub-routine, a return to the main program is desired. The contents of JA are the reference for the return. As JA refers to an instruction location, rather than a word location, the register contains in addition to the address, one more bit to indicate which half of the word contains the next instruction. (PA does not require this as there is a

normal sequence of performance within the instruction word,  $I_0$ ,  $I_1$ .)

An address is transferred to JA from either MA or PA. If the jump instruction is  $I_0$  the instruction word containing it was just transferred to PR from memory. Its address is still in MA where it was used to access the memory. This address is transferred to JA as well as an indication that the next instruction in normal sequence is  $I_1$  of that address.

$$(MA) \longrightarrow JA$$

$$1 \longrightarrow ja_{-1}$$

If the jump instruction were I<sub>1</sub>, the address of the next instruction in normal sequence is stored in PA.

$$(PA) \longrightarrow JA$$

$$0 \longrightarrow ja_{-1}$$

JA is connected to D so that the address may be transferred to memory. The customary procedure in a sub-routine, immediately upon entering it, is to transfer the address in JA to the address part of a jump instruction at the end of the sub-routine. Thereupon, the exit from the sub-routine will be back to the point of departure from the main program.

Normal Sequencing of Address

The incrementing of the program address for normal sequence is done as follows:

In a shift operation, for example, the register cannot simultaneously store two different things, the original number and the shifted number. The A register is one of the adder network inputs. The sum is stored in A. A cannot simultaneously store both numbers. (The adder network, ANI, is inherently incapable of storage.)

Each of these data registers is therefore double ranked. Each consists of a pair of one word registers, A and A\*, D and D\*, Q and Q\*. Addition (A) + (D)  $\longrightarrow$  A is performed by transferring D to D\*. (A) + (D\*) are the inputs to AN1. AN1 output to A\*, A is cleared; and the sum in A\* is transferred to A. Shifting of A is performed by transferring A to A\*, clearing A, transferring A\* to A through the shift gates, right or left.

Table 1.1-1 lists the functions of these registers in arithmetic operations.

Repeat Register (RR)

The repeat register is a 6-bit register storing control information for operation in the repeat mode. Its contents are:

| R a | β | γ | δ | I |

|-----|---|---|---|---|

|-----|---|---|---|---|

where:

R = 1 indicates repeat mode operation.

- I indicates whether one or a pair of instructions is being repeated. (I = 0 signifies that both instructions in the word should be performed).

- a  $\beta \gamma \delta$  specify the type of repeat (modification or not of X, and manner of modification).

Repeat Counter (N)

N is a 12-bit register, enabling the repetitive performance of an instruction up to 4095 times. N does not possess counting ability.

TABLE 1.1-1

|                | Operation         | A                 | D            | Q                 |

|----------------|-------------------|-------------------|--------------|-------------------|

| Addition       | Before operation  | Augend            | Addend       |                   |

|                | After operation   | Sum               | Addend       |                   |

| Subtraction    | on                |                   |              |                   |

|                | Before operation  | Minuend           | Subtrahend   |                   |

|                | After operation   | Difference        | Subtrahend   |                   |

| Multiplica     | ation             |                   |              |                   |

| Rounde         | ed Product        |                   |              |                   |

|                | Before operation  |                   | Multiplicand | Multiplier        |

|                | After operation   | Product           | Multiplicand | Multiplier        |

| Multiplication |                   |                   |              |                   |

| Double         | -length Product   |                   |              |                   |

|                | Before operation  |                   | Multiplicand | Multiplier        |

|                | After operation   | Major<br>Product  | Multiplicand | Minor<br>Product  |

| Division,      | Single-length     |                   |              |                   |

| dividend -     | Before operation  | Dividend          | Divisior     |                   |

| Division,      | Double-length     |                   |              |                   |

| dividend .     | -Before operation | Major<br>dividend | Divisor      | Minor<br>dividend |

| Division,      | Both size         |                   |              |                   |

| dividends      | - After operation | Remainder         | Divisor      | Quotient          |

It stores a number (in twos complement form) which indicates how many times an instruction, or pair of instructions, is to be performed. The number is incremented by use of AN2 and returned to N via MA.

# Memory Preset (MP)

Memory Preset consists of a bank of double throw toggle switches on the console provided primarily as a programming facility. The MP switch levels are continuously compared with the contents of MA and coincidence will be recognized to stop the computer, if desired.

#### Data Registers

Three registers are used to handle the data word in the computer, A, D and Q. (D is also used to handle an instruction word if part of the word is to be changed.) The nature of a parallel computer requires an additional storage media for these registers. During a shift operation, for example, a register cannot simultaneously store the original and shifted word.

Each of these registers has another 48-bit register associated with it,  $A^*$ ,  $D^*$  and  $Q^*$ , to provide the required additional storage. These are spoken of as the "star" registers ("A Star", etc.).

#### **CMA**

The Core Memory Address register stores addresses for paper tape, magnetic drum and printer access to computer memory. The separate register is required as the input-output operation time-shares the computer with many internal instructions, the latter having other addresses.

The magnetic tape control also requires an individual memory address register. This is located in its control unit, outside the computer.

#### Switch 3 and Switch 8

These switches route information to and from memory. Switch 8 (SW8) routes the read-out from memory to the desired destination, PR, D, or IOB (Input-Output Buffer). Switch 3 (SW3) connects a register for writing-in from memory, PR, D, or IOB. The M register is for display only.

#### Other Controls

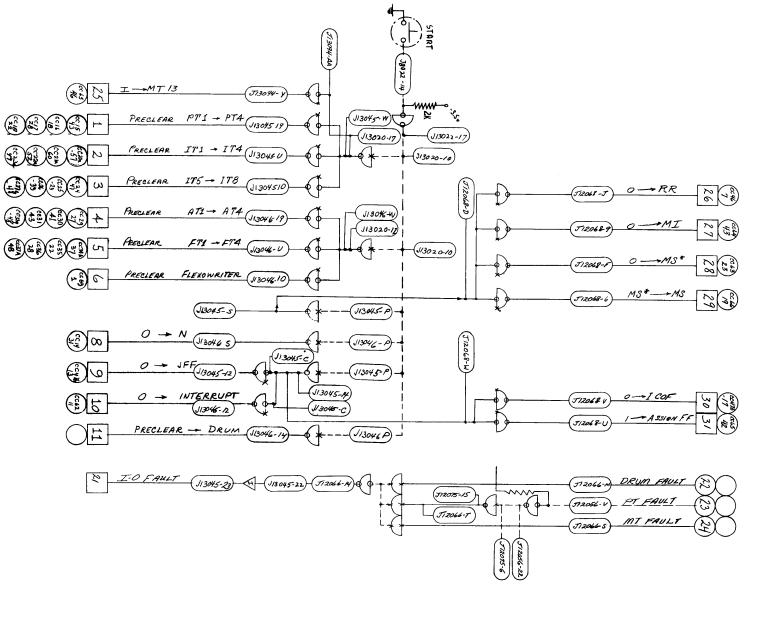

Several other controls are not illustrated. One group consists of the Fault flip-flops. When any of these are set to one, they will stop computer operation.

Command Fault (CF) Command coding in PR which is not assigned to any instruction.

Memory Fault (MF) Temperature of memory unit is not in operating range and operation is unreliable.

Exponent Fault (EF) The result of an algorithm with floating point numbers has resulted in a quantity that cannot be represented by the computer.

The STOP flip-flop, when set, will halt the computer. The flip-flop is set either by the HALT instruction (HLT) or operator intervention (STOP switch in lower center of console)

The OVERFLOW (OVF) flip-flop is set by overflow conditions. The JOF instruction requires the computer to jump if overflow. The OVERFLOW console switch in the ON position will stop the computer, otherwise.

The JUMP flip-flop (JFF) is set when a jump is to be executed. It controls the details of the execution.

# 1.2 Control Organization

The performance of an instruction, or a series of instructions forming a program, consists of a larger sequence of what may be termed as "operations.". The basic program cycle operations would consist of selecting an instruction and performing it. The instructions themselves are a sequence of operations, perhaps involving transfer of data, followed by arithmetic or non-arithmetic manipulation of the data and possibly concluding with a transfer of the result from a register to memory or another register.

Among the operations of the instructions and the program cycle there are many identities and similarities. The complexity of the computer control logic can be minimized by an organization wherein the control specifies operations. An operation can be defined as some part of an instruction or part of the program cycle. The instruction calls for the proper sequence and number of operations. Some of the operations possible within an instruction have been previously mentioned. The operations control signal lines which cause groups of tasks to be performed.

The smallest piece of logical work performed by the computer can be termed a "task". The task is a change or transfer of information. The transfer changes the condition of some information storage unit. There are two types of information, data and control.

A criterion for determining the scope of a task, in the logical design of the computer, is similar to that of determining the least common denominator in arithmetic. The scope of a task should be chosen so that it can be used for operations in many instructions.

An instruction is performed as a group of operations subdivided into groups of tasks for two basic reasons. First, the instruction usually requires several operations that cannot be simultaneously performed. These operations must be sequenced in a pre-determined fashion. The program itself, is a sequence of instructions and timing therefore enters into program control.

Secondly, due to the similarities among many instructions, the sub-division into tasks can be organized so that tasks will be identical for similar instructions. The operation is then a group of performed tasks, some simultaneously, others in a predetermined sequence.

In the broadest sense there are six groups of operations. Listing them by their control names:

Program Control

Instruction Control

Algorithm Control

Floating Point Control

Memory Cycle Control

Input-Output Control

#### Program Control

This is the group name for the operations involved in maintaining the desired sequence of instructions. These include transfer of the instruction word from memory to the program register (where it is stored for execution), selection of the proper one of the two instructions within the instruction word, establishing the location of the next instruction, index register modification.

#### Instruction Control

This group of operations consists of those preparatory to the performance of any instruction as well as those necessary prior to specific instructions. In the case of non-arithmetic instructions, this control may cover the performance of the entire instruction.

#### Algorithm Control

The group of operations for performing arithmetic.

#### Floating Point Control

The manipulation of the operands prior to, and the result subsequent to, the arithmetic operations.

#### Memory Cycle Control

The transfer of information to and/or from core storage.

#### 1.3 Control Registers

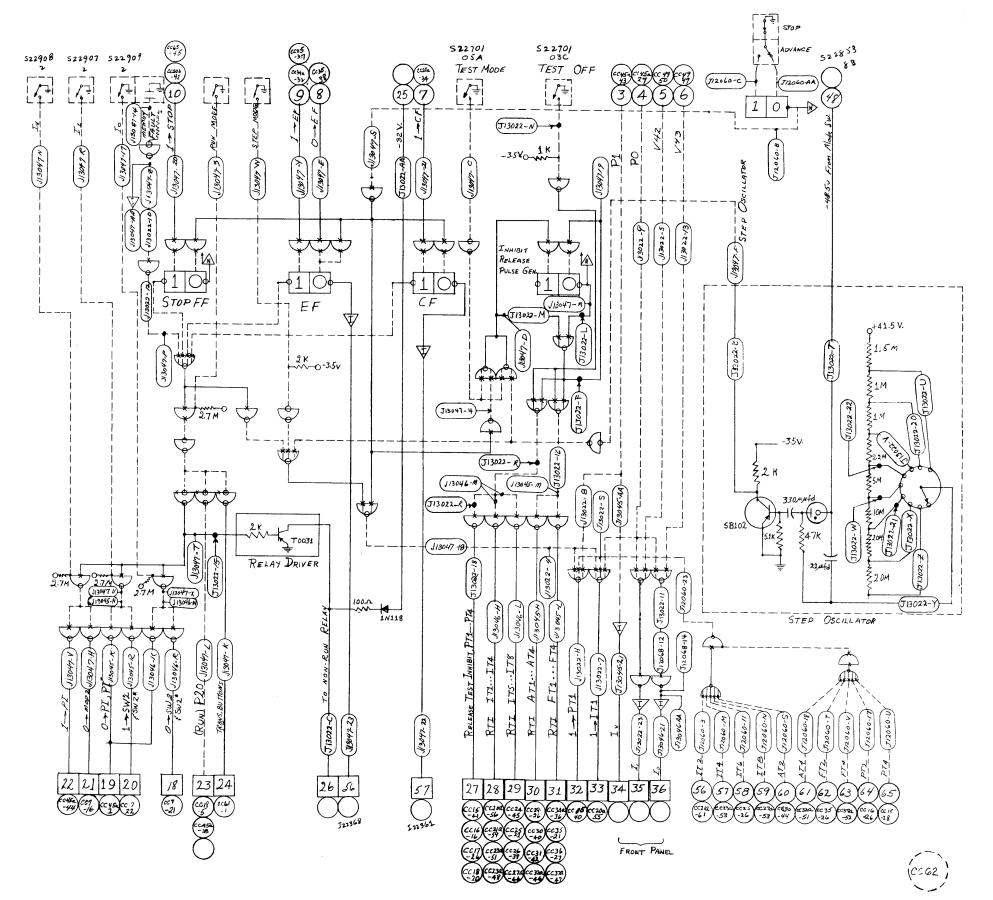

The computer is functionally divided into the first four groups of operations mentioned before. Only one control register of the four is active at a time. The last two, memory and input-output control, operate asynchronously and can be active simultaneously with the first four.

Each of the four groups of operations has a control register, consisting of the required number of flip-flops, to enable establishing the control for the activity within each operation. The control registers are identified as:

- PI Program Control Register

- II Instruction Control Register

- AI Algorithm Control Register

- FI Floating Point Control Register

Each setting of a control register controls the execution of a specific variety of that species of operation.

Control Register Functions

$\mathbf{PI}$

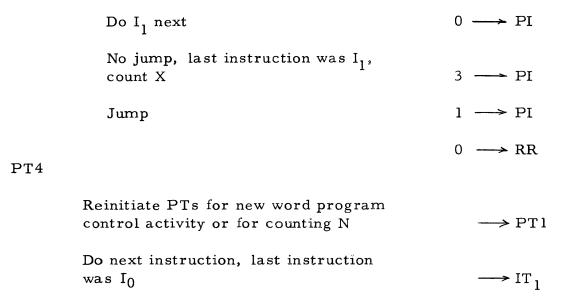

PI = 0 do next instruction

PI = 1 transfer next instruction word to PR

PI = 2 modify index register

PI = 3 count down repeat counter

ΑI

AI = 0 force add in multiplication (multiplier is minus one)

AI = 1 add or subtract

AI = 2 double-length multiplication

- AI = 3 single-length multiplication, rounded

- AI = 4 fixed point division, first cycle

- AI = 5 fixed point division, other than first cycle, or floating point division

AI = 6 Shift

AI = 7 Q Jump

FI

FI = 0 arrange first cycle (beginning of add or subtract)

FI = 1 exponent addition or subtraction (beginning of multiply or divide)

FI = 2 shift D (arrangement of D since  $D_{E} \le A_{E}$ )

FI = 3 shift A (arrangement of A since  $D_E > A_E$ )

FI = 4 normalize (following arithmetic operation)

FI = 5 correction (before algorithm if division, following if add, subtract or multiply)

FI = 6 Clear D (D<sub>E</sub> << A<sub>E</sub>)

FI = 7 clear A (A<sub>E</sub>  $<< D_E$ )

ΙI

I I = 0 control state used for most instructions

I I = 1 multiply cycle of multiply then add or subtract

instructions

#### MI Memory Control

MI = 0 memory not being used by computer

$MI = 1 (M) \longrightarrow PR \longrightarrow M$  (read and write PR)

$MI = 2 (M) \longrightarrow D$  (read D)

$MI = 3 (D) \longrightarrow M$  (write D)

$MI = 4 (M) \longrightarrow D \longrightarrow M$  (read and write D)

$MI = 5 \text{ clear M}, (D) \longrightarrow M \text{ (read 0 write D)}$

MI = 6 clear M, leave cleared (read and write 0)

MI = 7 clear M (read 0)

Note: Due to the nature of magnetic core use, the read-out from memory (sensing of information in the cores) is destructive. When the information must be maintained it is written back following the read, as in MI = 1 above.

The required sequence of operations is effected by having the instruction select the proper sequence of the control registers. Program control activity to select the next instruction to be performed, the PI operation, comes first. It is followed by the I I operation.

At the start of the I I operation, the next instruction is decoded and the sequence of operations arranged. Many instructions are completely performed in the I I operation. Arithmetic requires AI and possibly FI operations. The sequencing was predetermined by the logical design of the computer. The decoding of the command selects the control lines.

The various phases, or sequences within the operations are called "timings". The timings are the sequencing control for groups of tasks within the operation. These are consecutively numbered.

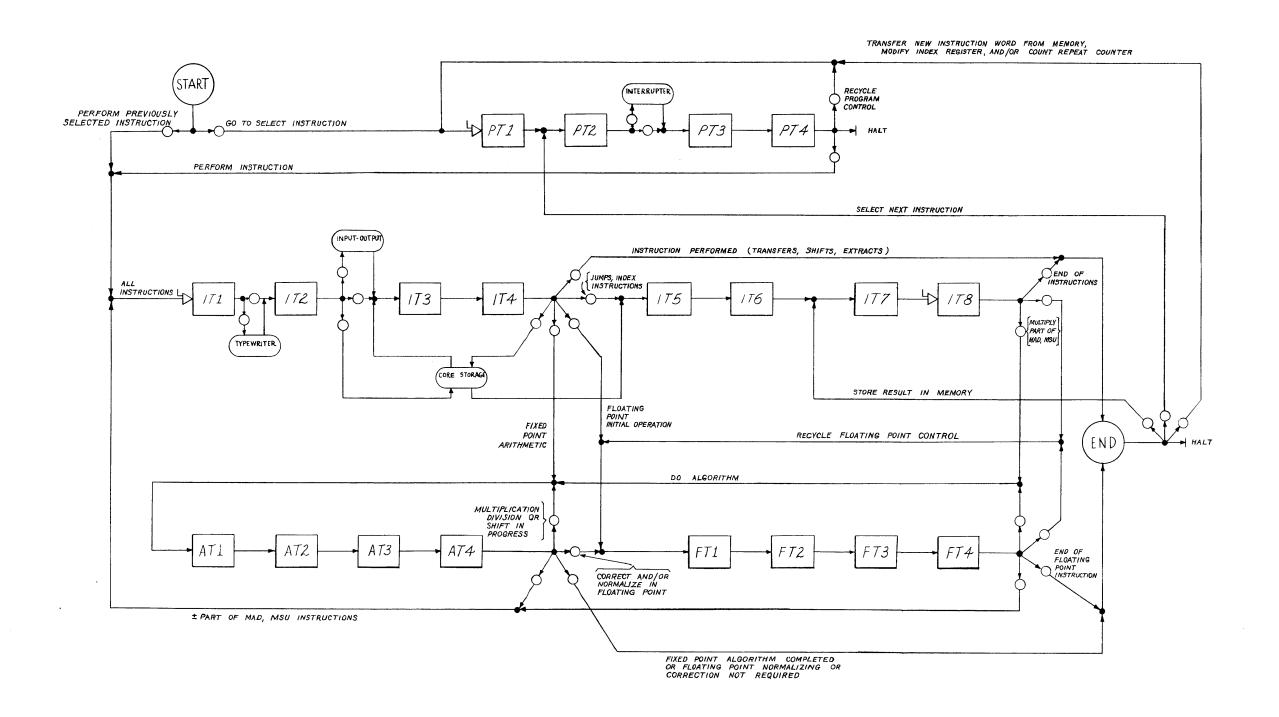

PTI through PT4 ITI through IT8 ATI through AT4 FTI through FT4 The progression of control through the timings for an operation is a function of the operation being performed. Some instructions require activity in all timings of a control, others do not. However, many similar sequences can be established. Generally, an operation is a sequence of four timings or a multiple thereof.

This can be illustrated by the general case. The purpose of the operation is to obtain new information (data or control) that is the resultant of the combination, or effect, of existing information. The operation can be symbolized as:

$$(X)$$

and  $(Y) \longrightarrow Z$

where registers X and Y are the inputs to the processing network and Z is the register receiving the output of the network. This could represent an addition, for example. Usually the storage of the result in Z is temporary. It is transferred to another register for further use (in this case, back to X).

In the S-2000, information transfers are done in two steps. The receiving register is first cleared so that all the bits (binary digits) have the same value. The register may be cleared to all zeros or all ones dependent upon the operation. Then all bits having the opposite binary value are transferred to the register. By initially clearing the register to a known condition, the following transfer of information is a direct, simple process involving a minimum of logic.

The required tasks of this illustration would be as follows (where tasks listed horizontally can be simultaneously performed):

# clear X clear Y 1. $\longrightarrow$ X $\longrightarrow$ Y clear Z 2. $[(X) \text{ and } (Y)] \longrightarrow$ Z 3. clear X 4. $(Z) \longrightarrow$ X

Usually one of the existing pieces of information has been transferred to X in some prior operation and Y is automatically cleared by program control at, say, the beginning of an instruction. This reduces the process to a four-step sequence, as numbered above, and is a reason for a module of four timings being used in the computer.

The timings are performed by using a group of flip-flops, one for each timing. For each control register, the timing flip-flops are interrelated to form a timing chain so that each is active only in its turn. The timing flip-flop outputs activate the gates to perform the selected tasks in proper sequence.

The performance of a simple, fixed point add instruction,  $(A) + (V) \longrightarrow A$ , can illustrate the sequence of control registers and their timings. The instruction is in the Program Register (PR) and has been selected as we start by entering the II operation at IT1.

In IT1, the following occurs (simultaneously):

- 1. A general clearing of controls preparatory to each instruction.

- 2. Prepare for transfer of the address of the operand in memory from PR, where the current instruction is stored, to the Memory Address Register (MA) where the address will be stored for decoding to select the desired memory location.

- 3. Clear MA

- 4. Clear the D register as it will receive the operand transferred from memory.

- 5. Go to IT2.

#### In IT2:

- 1. Transfer the address from PR to MA.

- Set the algorithm control register to the state required for add, 1 → Al. (AI = 1 indicates the operation is add or subtract). This is a preparatory

task, solely. AI will not take control until its timings have been initiated.

- 3. Set the memory control register to the state required for the transfer of the operand, 4 —— MI. The destructive nature of the memory read-out requires the information to be rewritten, following the transfer to D. The transfer to D will start at this time.

- 4. IT2 will remain on until the transfer, (V) → D is completed, at which time the computer goes to IT3.

- 5. The memory timings continue, in parallel with the computer timings, to transfer (D) V.

#### In IT3:

- 1. Clear the D\* register which is the input to the adder for one operand. (D and D\* are separate one-word registers).

- 2. Go to IT4.

#### In IT4:

- 1. Transfer (D)  $\longrightarrow$  D\*

- 2. Go to AT1.

#### In AT1:

- 1. Clear the A\* register which will receive the output of the adder.

- 2. A and D\* registers are always connected to the adder inputs. The addition occurs during this timing.

- 3. Upon completion of the addition go to AT2.

#### In AT2:

- 1. Store knowledge of overflow if it occurred.

- 2. Connect the adder output to A\* (in effect transfer the sum to A\*).

- 3. Go to AT3.

#### In AT3:

- 1. Clear A.

- 2. Go to AT4.

#### In AT4:

- 1. Transfer the sum,  $(A*) \longrightarrow A$

- 2. Go to "End". The instruction is completed and a program control decision is necessary to determine what follows this instruction.

Other instructions will go through a difference sequence of controls and timings due to the differences in operations. Floating point addition would require activity performed during FT's under FI control, in addition to the above described operations for fixed point addition. Transfer instructions are completely performed under II control from IT1 to IT4. It will be noted that during the add instruction the transfer of the operand from memory to D was done during an IT. A jump instruction would also be performed under II control, IT1 through IT8.

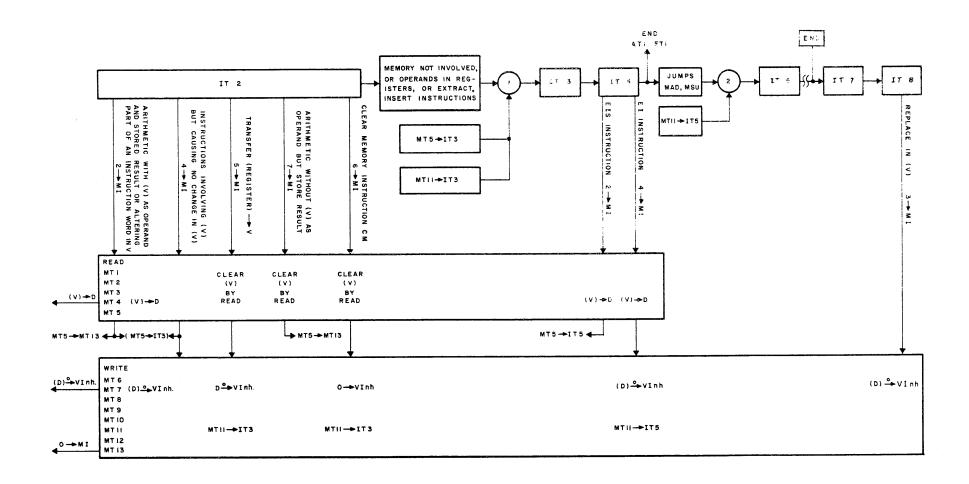

Figure 1.3-1 surveys the flow of control for the instructions.

# Program Activity for Repeat and Index Register

An interesting use of control is that done with certain operations relating to index register modification (counting or repeat modification of the index register) or relating to the repeat mode control. These operations will be the last ones to be performed in an instruction and will therefore be followed by program control activity.

Figure 1.3-1 Flow Diagram of Computer Timing

In some cases the result of these operations will determine what type of program control action shall follow. For example, the result of one of these operations will determine whether or not the final performance of a repeated instruction was just done. If not, it is performed again. If its final performance was done, repeat is terminated and the succeeding instruction word must be obtained.

The nature of these operations lend themselves to performance under the program control. This also falls in with the general scheme of starting the basic program cycle with PI operations. At the end of the instruction performance, control is returned to PI. If further operations are required, they will be performed under control of PI, during the timings of PT. Following this the PT's may be reinitiated, and this time sequence will be for the program control of the next instruction.

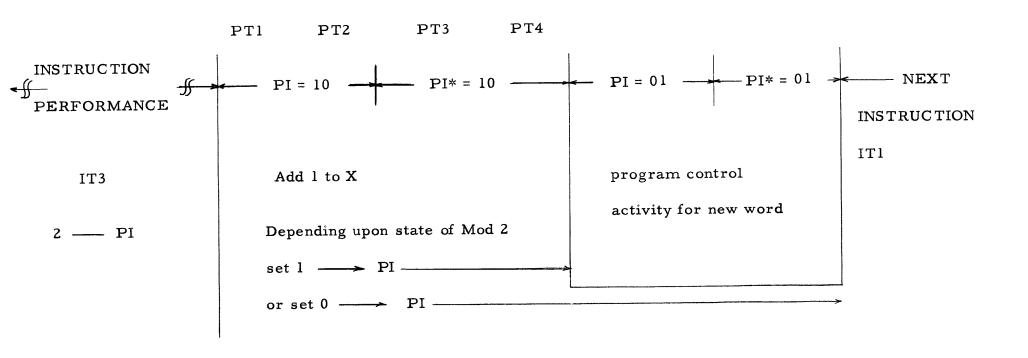

# Double Rank Control Registers

As PI may possibly be set to a different state during a set of PTs to control the next set of PT's immediately following, it is necessary to make PI a double rank register (PI and PI\*). PI controls during PTl and PT2, PI\* controls during PT3 and PT4. PI can be changed to its new setting while PI\* controls. The setting of PI is transferred to PI\* in PT1.

Every control register with a recycling control in the sense that one set of its timings may immediately succeed another of its sets is double ranked. These registers are AI, FI and PI.

The characteristics of the activities during a timing should be noted. All are done in parallel. Most are accomplished simultaneously. The completion of addition is an example of one task that may take a longer time. The time required to complete an addition is variable and a function of the data. The computer does not allot a fixed time interval for a timing but proceeds from one timing to the next as soon as all tasks of a timing that are necessary for the next timing have been completed. Where the time required for a task is variable, it waits for a signal to indicate completion. If all task completion times of a timing never vary, the computer proceeds as rapidly as possible (the limiting factor is the switching time of the circuits) from one timing to the next. In this manner, the computer is operating as fast as data and circuitry permit, for each operation, rather than at a constant rate for all operations determined by the slowest possible variable case.

#### Timing Chain

The requirements for the organization of the timing chain are fourfold:

- 1. The proper sequence should be established.

- 2. No more than one timing should be active in any interval.

- 3. If the computer has been operating in parallel with memory it must wait, if necessary, before activating a timing requiring the memory contents.

- 4. A timing which acts upon a register that has been subject to a change of contents should not become active until the situation has stabilized.

To achieve these purposes requires a system of interlocks. A timing is active only under two types of conditions. Its associated timing flip-flop is set to one and several additional signals are permissive. These signals comprise the interlocks.

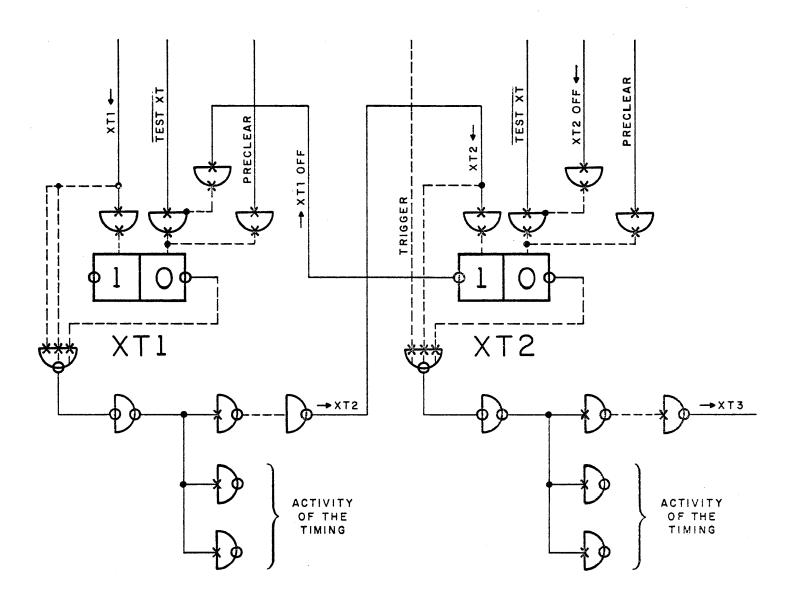

For example, one of the requirements for any timing to be active is the existence of the zero state of the previously active timing flip-flop (See Figure 1.3-2).

The proper sequence is assured by not turning a timing flip-flop off until the next timing flip-flop has turned on (set to one). Thus the set-to-one signal will continue until the flip-flop is set.

The third and fourth requirements are met by the third input of the three-input AND gate that activates the timing. This third input has been named the "trigger". Table 1.3-1 shows which timings require a trigger. MO, the PTI trigger, signifies the completion of the memory operation of the previous instruction. MO  $\equiv$  MI = 000; the memory control register has been reset to zero (or no memory operation was started at the end of the previous instruction). AN2CC (AN2 Carry Complete) indicates the stabilization of that adder network following a change of contents of a register that is an input to AN2. The D numbers that are used as triggers also incorporate the carry complete signal and note the exceptions, the instructions that need not

Figure 1.3-2 Timing Chain

await the carry complete signal. D67 is AN2CC or a jump instruction. D103 is AN1CC or instructions that need not await it. D117 is AN2CC or certain index register instructions. AN1ECC is the carry complete signal for the exponent part of AN1 in floating point number usage.

Referring to Figure 1.3-2, the "TEST XT" signal is usually negative and is changed only for engineering tests of the computer. "Preclear" is part of a manual console control to restore program control to its starting point.

In Table 1.3-1, the AT4 off signal seems to present the paradox of the flip-flop attempting to set and reset simultaneously. This is not the case as the Off signal originates after the passage of the AT4 signal through several transistors with the attendant circuit delay. IT4, IT8, AT4, FT4, and PT4 are the possible end of the timing chain for their respective control registers. It is for this reason they are turned off in the manner indicated by Table 1.3-1.

Table 1.3-1

| Timing | Trigger<br>(if any) | Signal to<br>Turn Timing<br>Off |

|--------|---------------------|---------------------------------|

| PTl    | МО                  | PT2 = 1                         |

| PT2    | AN2CC               | PT3 = 1                         |

| PT3    |                     | PT4 = 1                         |

| PT4    | AN2CC               | PT4 : MO                        |

| ITl    |                     | IT2 = 1                         |

| IT2    | D67                 | IT3 = 1                         |

| IT3    |                     | IT4 = 1                         |

| IT4    | AN2CC               | ''IT4''                         |

| IT5    | D103                | IT6 = 1                         |

| IT6    |                     | IT7 = 1                         |

| IT7    | D103                | IT8 = 1                         |

| IT8    | D117                | ''1T8''                         |

| ATl    |                     | AT2 = 1                         |

| AT2    | D48                 | AT3 = 1                         |

| АТ3    |                     | AT4 = 1                         |

| АТ4    |                     | ''AT4''                         |

| FT1    | D49                 | FT2 = 1                         |

| FT2    | ANIECC              | FT3 = 1                         |

| FT3    |                     | FT4 = 1                         |

| FT4    |                     | → END                           |

#### 1.4 Commands

The rightmost eight bits of the instruction are assigned to the coding of the command part of the instruction. They are identified as:

Bit Position

Identification J C<sub>6</sub> C<sub>5</sub> C<sub>4</sub> C<sub>3</sub> C<sub>2</sub> C<sub>1</sub> C<sub>0</sub>

The scheme for command coding follows that of the computer control organization. Since many operations are the same in instructions, as far as is feasible specific meanings are given to each bit of the command coding. A binary bit will tend to specify whether or not a possible operation shall be performed. Two bits may be grouped to select one of four possible variations in an operation. This scheme cannot be used for every command coding due to the differences among the wide variety of TRANSAC instructions. However it is used extensively.

For example, C<sub>6</sub> is used to indicate whether or not an arithmetic instruction is involved:

$C_6 = 1$  arithmetic instruction

$C_6 = 0$  non-arithmetic instruction

The coding for arithmetic instructions follows. "X" is used to indicate that the value of the bit position is not significant. This is termed "bar coding". The value of bar coding is that it serves to indicate how to decode the command into individual control signal lines.

$$\mathsf{J} \quad \mathsf{C}_6 \; \mathsf{C}_5 \; \mathsf{C}_4 \; \mathsf{C}_3 \; \mathsf{C}_2 \; \mathsf{C}_1 \; \mathsf{C}_0 \\$$

X 1 X X X X X X Arithmetic with  $C_5$  and  $C_4$  indicating type of arithmetic operation.

X 1 0 0 X X X X Add

X 1 0 1 X X X X Subtract

X 1 1 0 X X X X Multiply

X l l l X X X X Divide (also some special instructions)

```

C<sub>3</sub> indicates location of second

operand (location of other operand

not variable)

X

X

0

0

\mathbf{X} \quad \mathbf{X} \quad \mathbf{X}

operand in memory

X

X

0

1

X

X

X

operand in register

X

1

\mathbf{X}

X

X

X

X

Use algebraic value of second

operand

X

\mathbf{X}

X

X

1

X

X

Use absolute value of second

operand (in add, subtract or multiply).

X

1

0

X

\mathbf{X}

\mathbf{X}

0

X

Do not preclear A

X

1

0

X

\mathbf{X}

\mathbf{X}

1

X

Preclear A

X

1

1

X

X

\mathbf{x}

X

Double length product or dividend

X

1

X

X

X

1

\mathbf{X}

Result rounded (single length)

(except special arithmetic)

X

1

X

\mathbf{X}

X

X

X

0

Do not store result in M

) except

) special

X

X

X

\mathbf{X}

\mathbf{X}

\mathbf{X}

1

Store result in M

) arithmetic

0

1

\mathbf{X}

\mathbf{X}

X

\mathbf{X}

X

X

Fixed point arithmetic

\mathbf{X} \cdot \mathbf{X}

X

X

X

X

Floating point arithmetic

Shift Instructions

1

001

XXXX

C<sub>3</sub>C<sub>2</sub>

code the register involved:

A and Q registers

0

1

A register

1

0

Q register

```

C<sub>1</sub> codes the type of information in the word that is to be shifted.

1

D register

```

C<sub>1</sub> = 1 means treat the leftmost bit (2<sub>0</sub>) as the sign bit and the remainder as an admissible number. Shifting right is equivalent to dividing this number by 2; shifting left is equivalent to multiplying by 2.

```

C<sub>1</sub> = 0 means treat the word as some quantity.

No sign is involved and all bits are treated alike.

Co codes the direction of the shift.

```

C_0 = 0 means shift left.

```

```

C<sub>0</sub> = 1 means shift right.

(The D register can only shift right. C<sub>0</sub> = 0 causes a circular right shift in D.)

```

Jump Instructions X

```

X 010 XXXX

```

C<sub>3</sub> C<sub>2</sub> broadly defines the areas involved or types of jump instructions.

```

defines a special group of jumps. (C<sub>3</sub> through C<sub>0</sub> incl.)

0000 unconditional jump

0001 jump if (A) = 0

0010 jump if OVF = 0 (overflow flip-flop is zero)

0011 jump if OVF = 1

```

#### 01XX defines the A jumps

```

0100 jump if A is positive (A \ge 0)

0101 jump if A is negative (A < 0)

0110 jump if (A) = (Q)

0111 jump if (A) = (D)

```

# 10XX defines the Q jumps

jump if Q is positive (Q is also circular shifted left one place whether or not the control jumps.)

jump if Q is negative. (Q is circular shifted left one place, as well)

jump if Q is even (2 = 0)

-47

(Q is also circularly shifted right one place whether or not the control jumps).

jump if Q is odd (Q is circular shifted right, one place, as well

11XX refers to D and magnitude jumps

| 1100 | jump if D is positive                            |

|------|--------------------------------------------------|

| 1101 | jump if (A) $\geq$ (Q) in floating point sense   |

| 1110 | jump if $(A) \ge (Q)$ in the algebraic sense     |

| 1111 | jump if (A) $\geq$ (D) in the alphanumeric sense |

In addition there is a group of six miscellaneous or special arithmetic instructions. The groups can be identified by the bar coding: X 111 1XXX.

00X Multiply and add or subtract

01X Logical product and add or subtract

10X Add or subtract D

where  $C_0 = 0$  means add  $C_0 = 1$  means subract

#### Non-Arithmetic Instructions

The non-arithmetic instructions are divided into five groups by the use of  $C_4$   $C_5$  and J.

| 000 | XXXX              | special instructions             |

|-----|-------------------|----------------------------------|

| 001 | XXXX              | transfers of data                |

| 001 | XXXX              | shifts                           |

| 010 | XXXX              | jumps                            |

| 011 | XXXX              | index register instructions      |

|     | 001<br>001<br>010 | 001 XXXX<br>001 XXXX<br>010 XXXX |

#### Transfers of Data 0 001 XXXX

Transfers of data are among four possible locations, indicating

a two-bit coding to indentify the location.

| 00 | location is memory     |

|----|------------------------|

| 01 | location is A register |

| 10 | location is Q register |

| 11 | location is D register |

$C_3$   $C_2$  identify the sending location;  $C_1$   $C_0$  identify the receiving location. If  $C_3$   $C_2$  is the same as  $C_1$   $C_0$  the register is cleared to zero. Otherwise the sending location is unaltered by the transfer.

The varieties of index register and special instructions are not suited for description by means of bar coding.

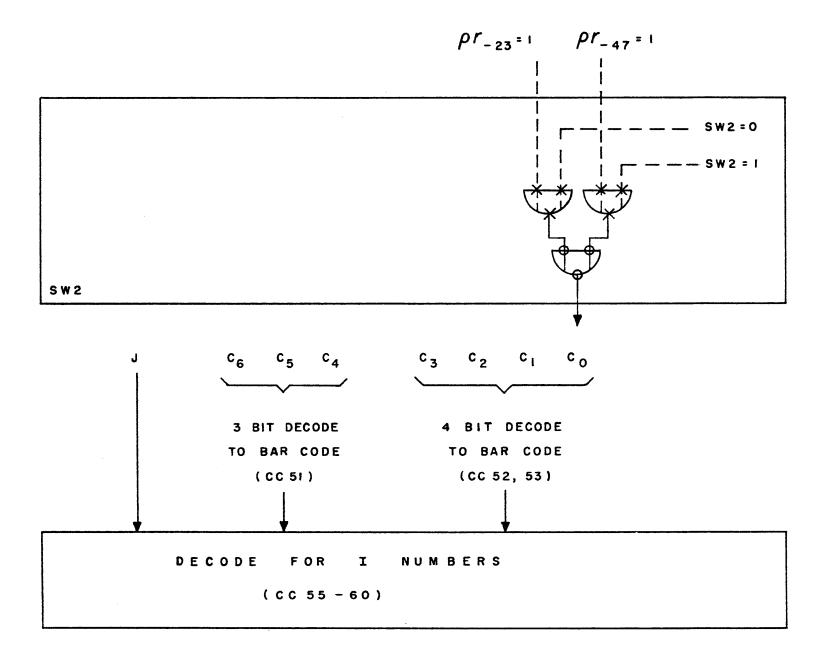

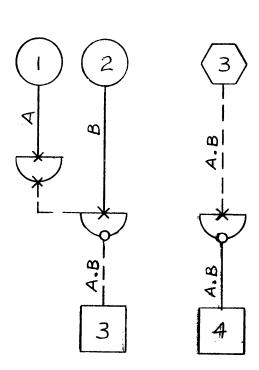

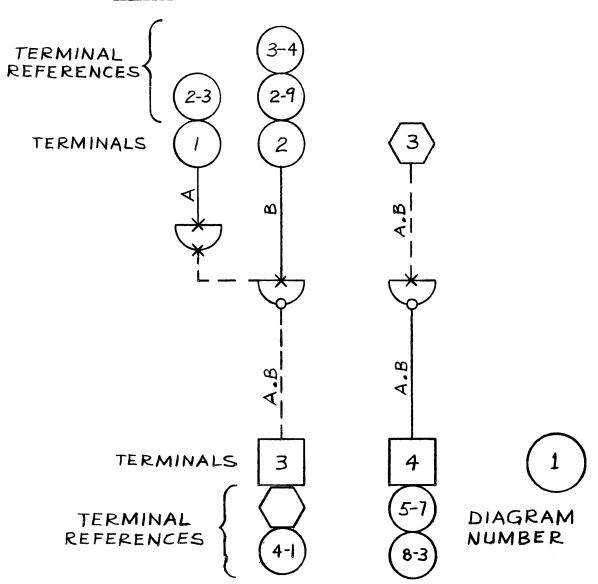

### Command Decoding

When the command bits of the instruction are decoded the bar codes are used, to a large extent, to determine the meaning of the decode outputs. The outputs are control signal lines and are called "I" numbers. Each is identified by the letter "I" followed by a number. The following is representative of the types of I numbers.

| 11          | 010 | 0001 | jump if A = 0 (a specific instruction)          |

|-------------|-----|------|-------------------------------------------------|

| <b>I</b> 15 | 010 |      | jump instructions (a type)                      |

| 139         | 1XX | 0XX0 | arithmetic instruction with (V) as one operand  |

|             |     |      | and result not stored (one variety of a type of |

|             |     |      | instruction).                                   |

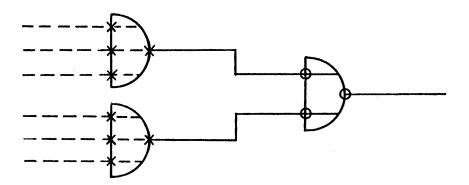

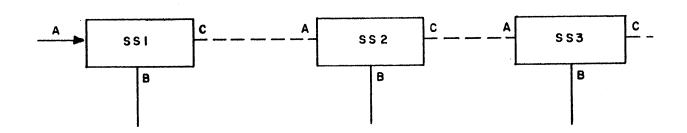

Decoding is done by sub-dividing the 8-bit command code into three groups as shown in Figure 1,4-1. Generally, the 3-bit and 4-bit decode results in bar codes which are combined to produce the "I number" control signal lines.

#### Translations

As an aid in translating between the machine command coding and English or the mnemonic code, the 8-bit code is converted to a quaternary type of code (quaternary number system having the numbers, 0 through 3). Reading from left to right, each pair of binary digits is converted to one quaternary number. Tables give the instruction and mnemonic code for each 4-digit quaternary number thus obtained. (See Appendix).

Figure 1.4-1 Command Decoding

# 1.5 Numbers - Control Signals

The problem of naming the hundreds of control signals in the computer is an appreciable one. The command part of the instruction, for example, is decoded to derive 138 control signals as the resultants of many combinations of the eight bit coding. If these signals were given descriptive names, the language on the schematic would tend to obscure the circuitry.

Abbreviations are used, instead. The signals are classified functionally. Each function is assigned a representative letter and the signals within the group are numbered consecutively. These abbreviated names are called "numbers".

The groups are decribed below. The numbers are listed in the appendix.

- A Numbers AI amd AI\* signals. These will define the various choices of activity during algorithm operations. Other signals used to derive A numbers are some FI settings, SC = Sat., SC \neq Sat. (Shift Counter not Satisfied).

- F Numbers Control signals for floating point operations derived from FI settings, the instructions and the data words being manipulated.

- I Numbers Signals derived from the command and occasionally data. Some I numbers represent the common tasks of several instructions to control their performance.

- J Numbers Jump activities derived from the command coding, the data words and their comparison.

- M and DM Numbers Signals derived from MI settings and other memory control signals.

- P Numbers Program Control signals from PI, PI\* settings, RR, and other operating controls.

- R Numbers Repeat mode control signals.

S Numbers - Skip control signals.

- V Numbers Variables is the name given to activities dependent upon the data word, such as the sign of the word, overflow; or the settings of other program controls which vary periodically.

- D Numbers When combinations of the above numbers are OR gated together, the resultant is called a "decision" and given a D Number. The D Number control signal will cause the specific tasks to be executed.

In effect then, the size and complexity of the computer requires three levels of control signals to instigate activities. There are activities done on the basis of the instruction, those that require several additional conditions to be done and those requiring many conditions to be performed.

## 2. INTRODUCTION TO TRANSAC LOGIC

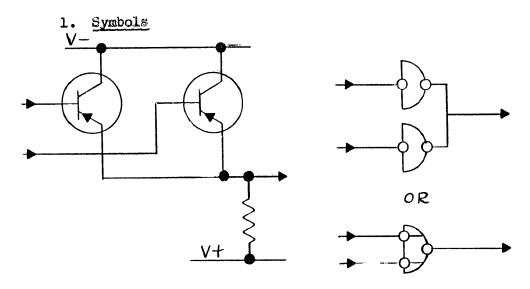

# 2.1 S-2000 Symbolism, Logical Circuits

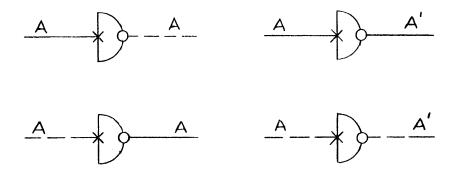

A description of the symbolism used in the notation of the S-2000 logic and standard logical elements is attached as an Appendix for convenient reference. A familiarity with this material is assumed for the remainder of this section.

## S-2000 Logical Circuits

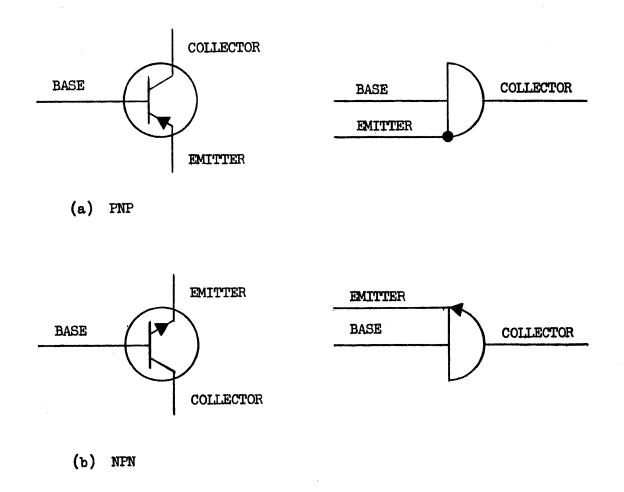

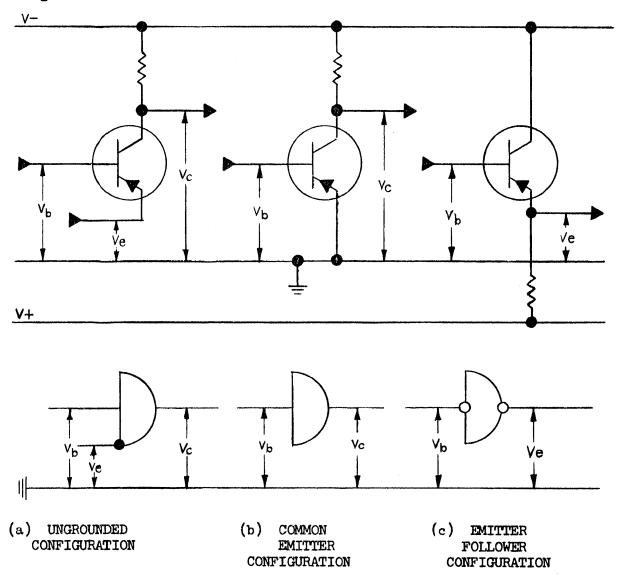

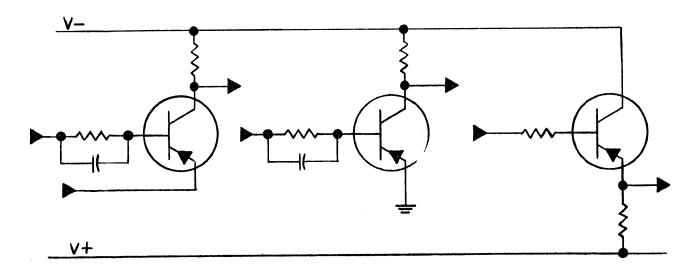

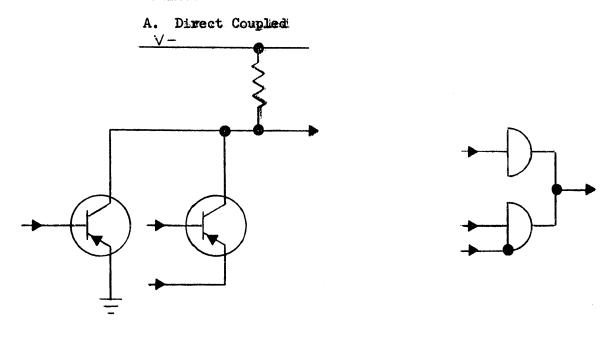

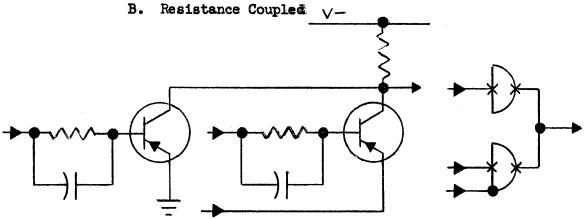

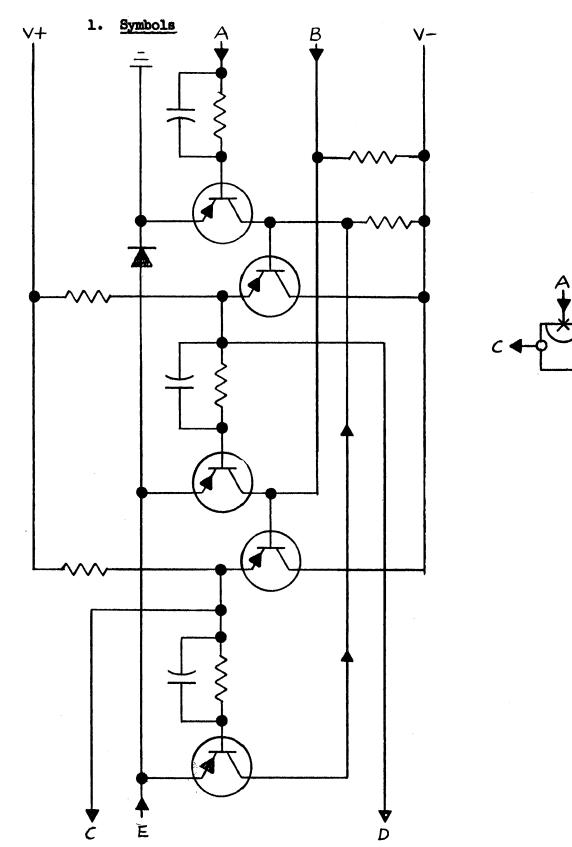

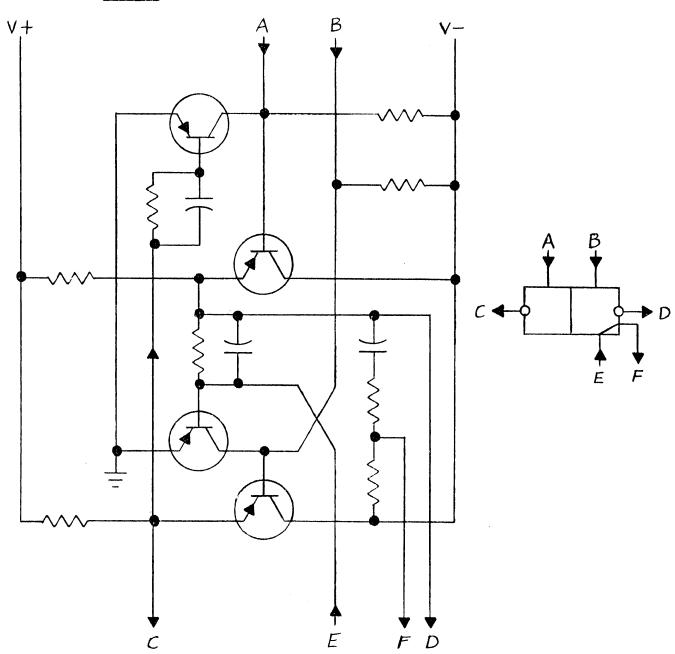

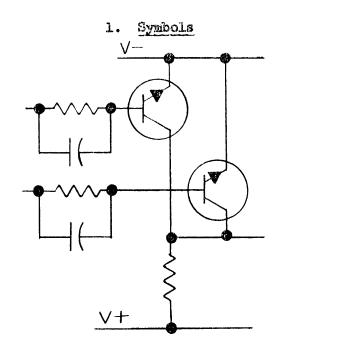

The basic logic circuits are formed by use of the standard transistor configurations.

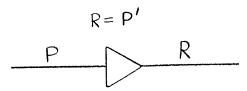

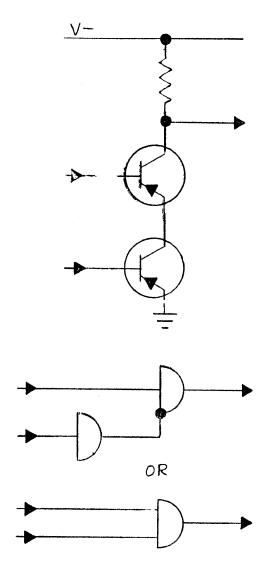

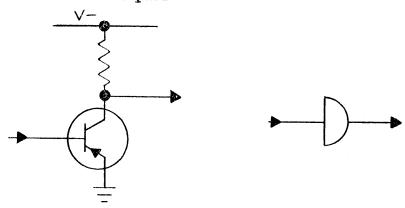

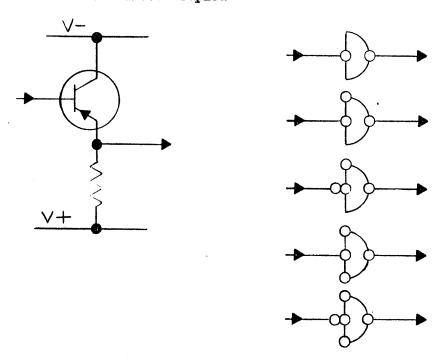

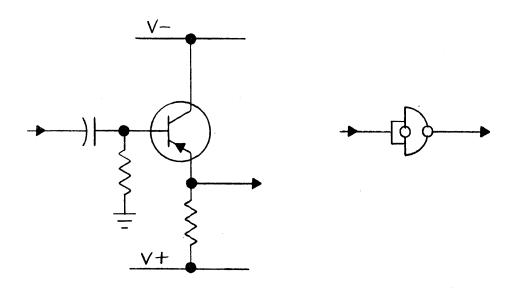

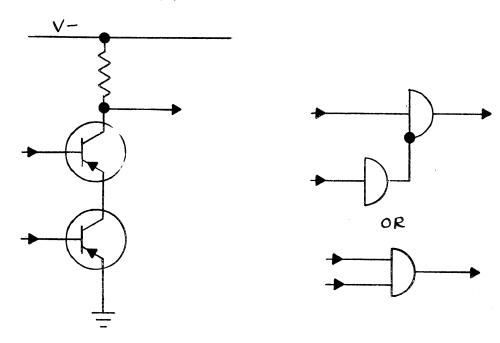

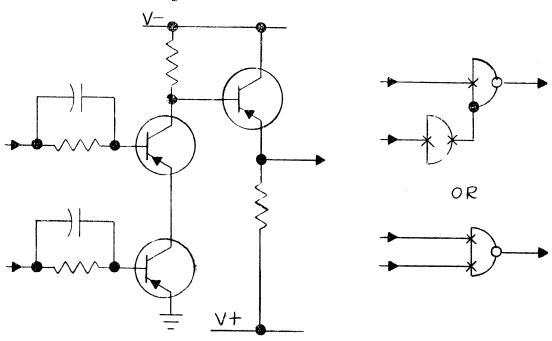

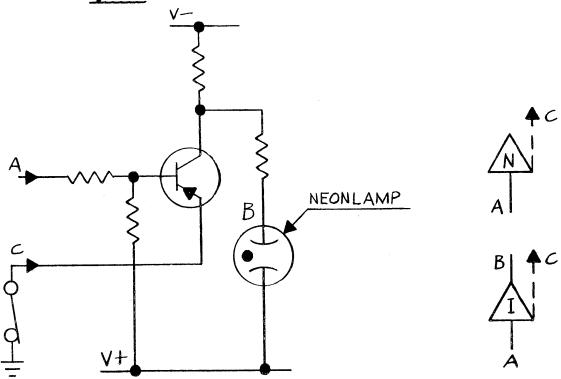

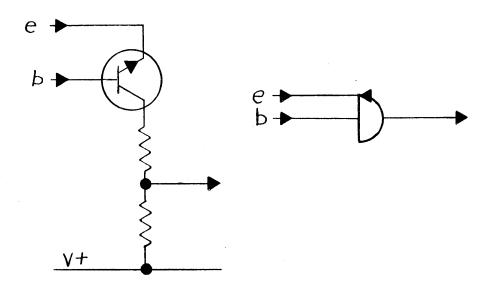

Inversion (negation) is achieved with the common emitter (usually followed by an emitter follower for design reasons). See Figure 2.1-1.

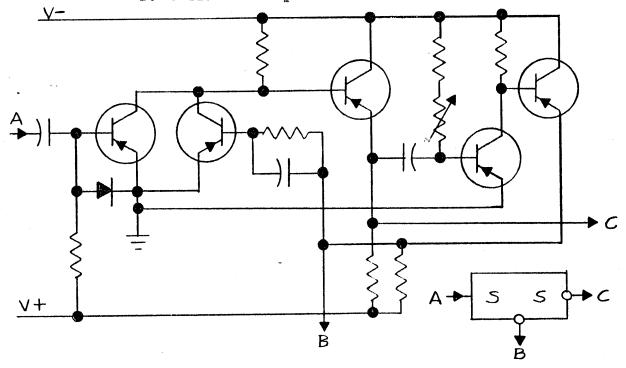

Inverter Figure 2.1-1

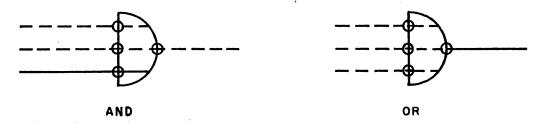

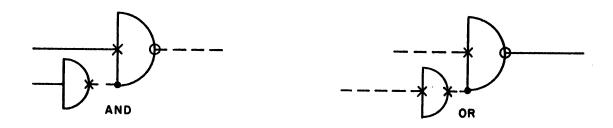

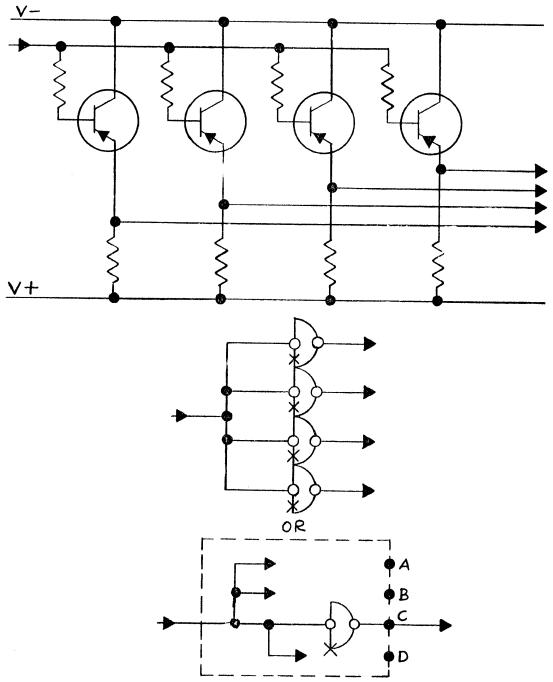

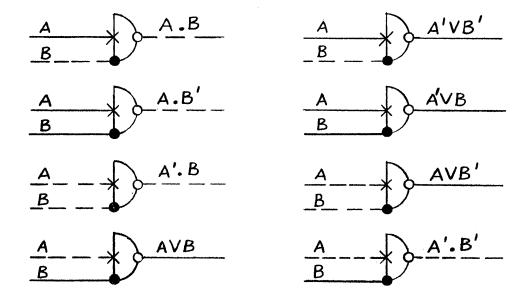

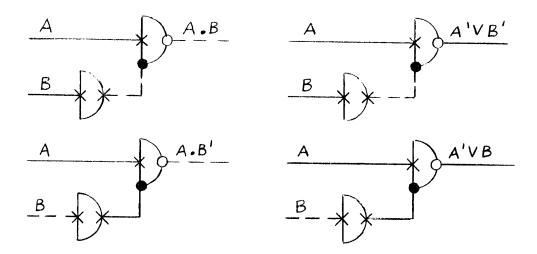

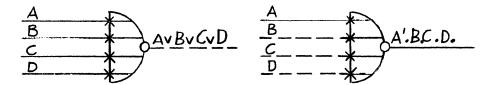

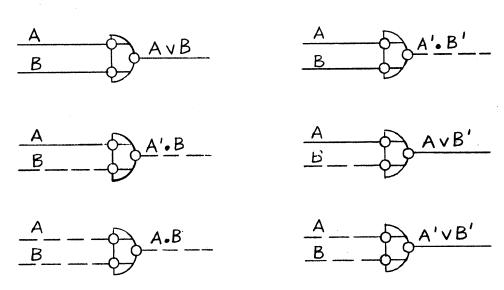

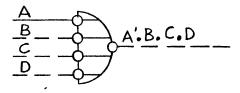

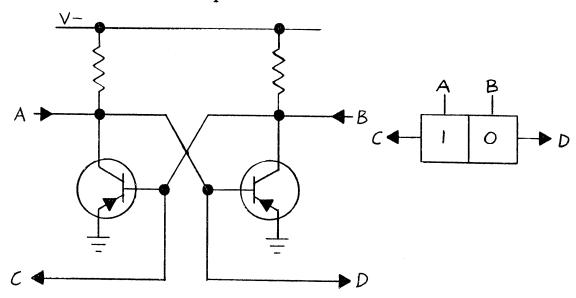

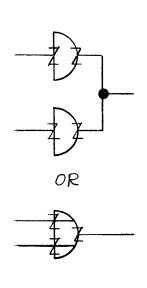

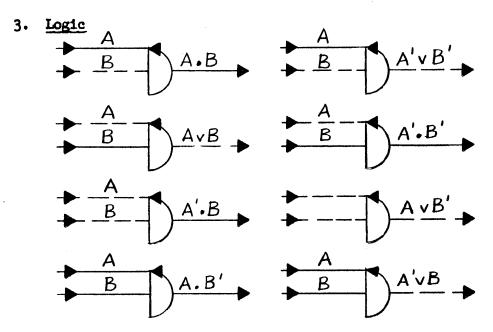

AND and OR circuits are formed by the use of either series (high) gates or parallel (wide) gates. Either gate can serve either the AND or the OR function.

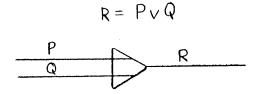

Parallel RC Gate Figure 2.1-2

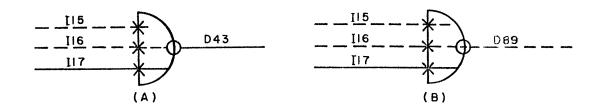

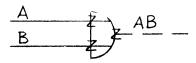

The 3-wide gate of Figure 2.1-2 can be used as an AND gate (A): I15 · I16 ·  $\overline{117} \implies D43$  (The overscore denotes the inverse value, spoken of as NOT I17)

The gate can also be used for an OR function (B):

$$\overline{115}$$

v  $\overline{116}$  v  $\overline{117}$   $\Rightarrow$  D89

(In our usage the term, OR, implies inclusive OR unless qualified.)

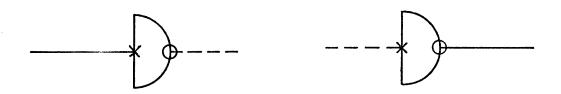

The logical function of the parallel gate can usually be determined by the polarity of the active output as shown in the schematic logic adjacent to the output signal name. An active negative polarity (solid line) for the parallel gate output indicates the AND function. All input lines must be positive to result in a negative output.

A positive active output polarity (dashed line) of the parallel gate indicates the OR function. Any combination of negative inputs will produce a positive output.

Figure 2.1-3 shows a parallel emitter follower configuration.

Parallel Emitter Follower Gate Figure 2.1-3

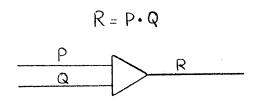

This configuration is customarily used for the OR function as illustrated in Figure 2.1-4.

Parallel Emitter Follower OR Gate Figure 2.1-4

For the OR function the active output polarity is negative. The parallel emitter follower is occasionally used as an AND gate, active output polarity positive.

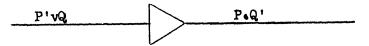

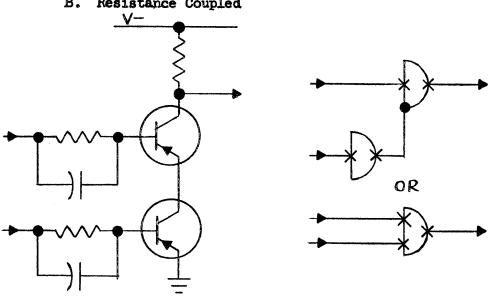

The series (high) gate can also serve either logical function. See Figure 2.1-5.

Series Gate Figure 2.1-5

The series gate usually serves as an AND gate.

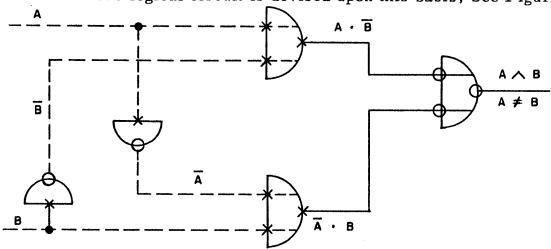

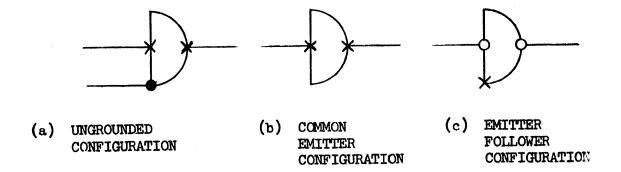

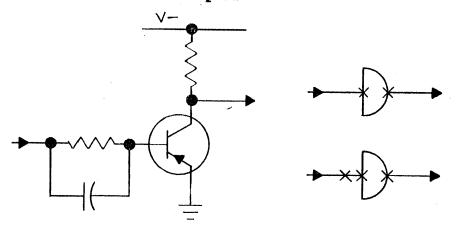

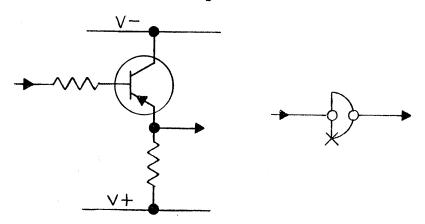

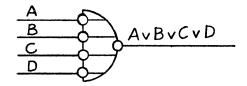

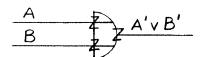

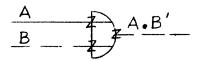

The Exclusive OR logical circuit may be better visualized by redefining Exclusive OR. It signifies inequality between two binary quantities:

$$A \wedge B \equiv A \neq B$$

The logical circuit is devised upon this basis, See Figure 2.1-6.

Exclusive OR

Figure 2.1-6

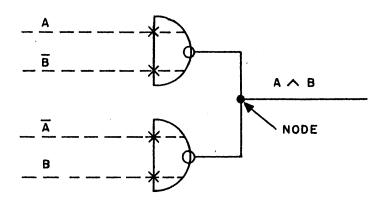

The right half of Figure 2.1-6 may also be drawn as in Figure 2.1-7. The junction of the emitter follower bases is sometimes called a "node".

Exclusive OR Figure 2.1-7

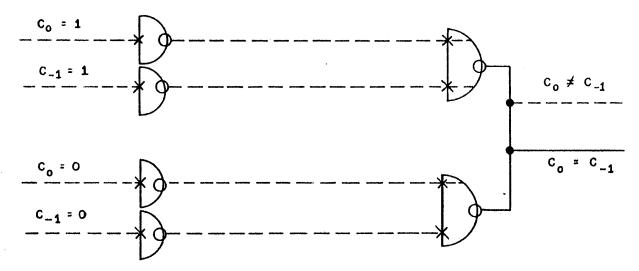

The customary use of the Exclusive OR is as part of a network for the comparison of two binary quantities. Figure 2.1-8 can be used to determine inequality or equality.

Figure 2.1-8

$$C_o \neq C_{-1} \equiv (C_o = 0 \cdot C_{-1} = 1) \cdot (C_o = 1 \cdot C_{-1} = 0)$$

The v symbol is customarily used, rather than  $\wedge$ , when the two terms are mutually exclusive, as the "V" in this example:

$$C_0 = C_{-1} \equiv (C_0 = 0 \cdot C_{-1} = 0) v (C_0 = 1 \cdot C_{-1} = 1)$$

Both outputs are not necessarily derived from the same logical circuit. Figure 2.1-8 is an illustration of a method.

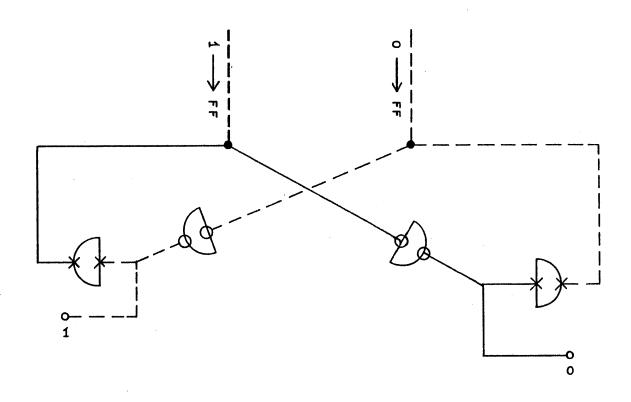

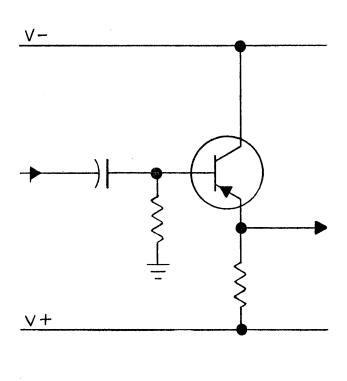

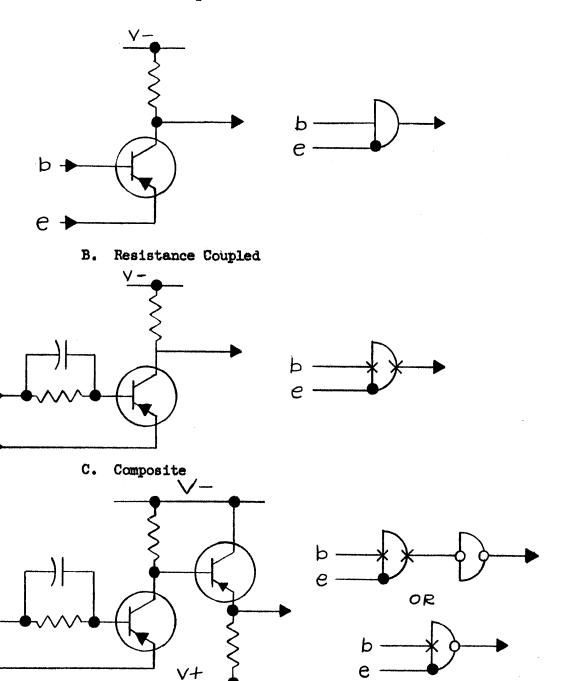

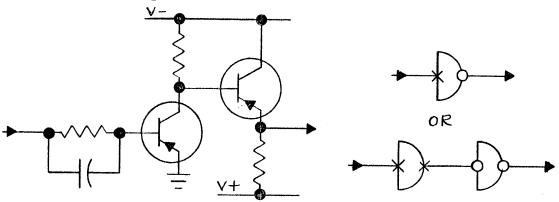

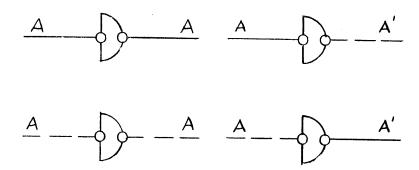

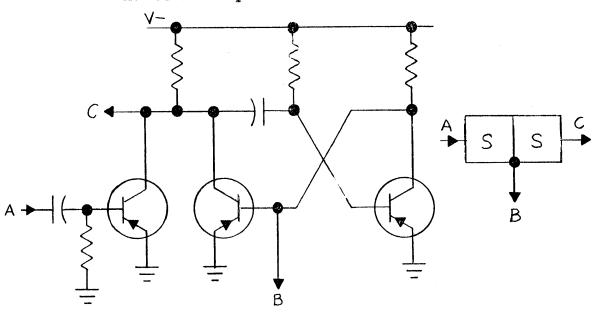

The standard RC Flip-flop is shown in Figure 2.1-9, logical circuit and symbol. The logical circuit is drawn here to emphasize the similarity to the crossover network of vacuum tube flip-flops.

The active input polarity is positive. The desired polarity of an active output line will determine from which of the two output sides the output signal is taken.

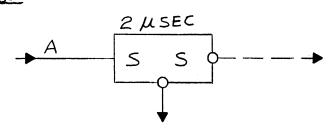

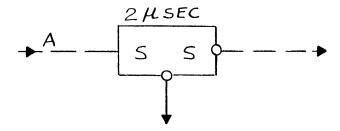

The Single Shot logical circuit is shown in Figure 2.1-10. The single shot can be triggered (changed to its unstable state) only by a negative-going signal at line A. The polarities shown for lines B and C indicate the polarities during the unstable state. The schematic logic shows a single shot timing chain in this manner.

The single shot is put to two uses, activity during its unstable state (usually the B line) and activity at the end of the unstable state (usually the C line). The A line determines when B starts to be active. The active period of B (unstable state) is of course determined by the circuit design of the single shot. C can trigger the next of a chain of single shots at the end of the unstable period. While the single shot is in its unstable state, the A line has no influence upon it. And the input that goes negative and remains negative can only trigger the single shot once. The A line must return to positive to be capable of retriggering the single shot.

The "C" output line of a single shot is normally negative. When connected as in Figure 2.1-10, the three single shots can and will operate only in sequence, each being activated by the deactivation of its predecessor. The length of the active period of the single shot is determined by the time constant of an RC network.

Standard Flip-Flop Figure 2.1-9

Single Shot Timing Chain Figure 2.1-10

# 2.2 Notation for Schematic Logic

This section describes the notation used in the schematic logic drawings of the S-2000 and this manual. The abbreviations, or symbols, used to name the registers and control devices are listed in the Glossary of Terms. An explanation of the notation method for signals follows here:

- (A) The parenthesis is used to indicate "the contents of" a storage device; in this case the contents of the A register. This distinguishes between the storage device itself, A, and its contents, (A).

- The upper case letter is used to refer to the entire register or a major portion thereof; in this case the subscript number "l" indicates the right hand half of D.

- d 1 The lower case letter indicates one bit of a data register; the subscript indicates which bit position. The positions are numbered from left to right, 0 to -47, corresponding to the negative exponent values for the binary fraction.

- AN2 In the control information registers the binary numbers stored are integers such as a memory address, number of times an instruction is to be repeated, or number of places the word is to be shifted. The bit positions of the control information registers (and their adder, AN2) are therefore numbered right to left with a superscript corresponding to the positive exponent of the binary integer. The least significant bit position of AN2 is named AN2

as compared to the naming of the least significant bit of the A register, a<sub>-47</sub>. (It was apparently considered confusing to apply the lower case letter notation to a mixture of alphabetic and numeric characters — an2<sup>o</sup> as against AN2<sup>o</sup>.

- (SW2)' The prime symbol indicates the inverse, or for a binary quantity the ones complement. In this case, the ones complement of the contents of SW2.

- 167 · V32 Logical AND symbol; when 167 and V32 are both active.

- I67 v V32 Logical inclusive OR symbol; either I67 OR V32 OR both are active.

- I67 A V32 Logical exclusive OR symbol, one OR the other but not both are active.

Control Two types of names are used. One type is an signal arbitrary or a mnemonic name such as 167, V32. Names The other type is a functional name, such as 1 — OVF (set the Overflow Flip-flop to its one state).

- Logical equations. When the signals shown at the arrow tail are active, the action listed at the arrowhead is to be performed.

D81 ·

$$\overline{D79}$$

·  $\overline{D52}$   $\Longrightarrow$  2  $\longrightarrow$  PI

When D81 and NOT D79 and NOT D52 are active, set the Program Control register to its "2" state. NOT D79 active is identical to D79 normal, logically.

- AT1 Sometime the action can only be one thing and may be therefore implied. "Go to AT1 timing" is a signal named as shown. The circumstances under which the signal is active is shown by the schematic logic drawing for the signal's origin.

- (A)

When only a certain value of information is to be transferred, it is indicated by the superscript above the arrow. This control signal permits only the binary l's in A to be transferred to corresponding bit positions in D. When prior to this action D is cleared (0

result in the transfer of a word. The converse control signal is

.

- L Transfer, shifting left one place.

- R Transfer, shifting right one place.

Data Transfer Control Signals

The distinction on the drawings between the data transfer signal lines and the control signals which permit the transfers is made in the following manner. The control signal will have a functional name describing the transfer of a register contents, or portion thereof.

d -23 = 1 The signal lines transferring the contents

will be named by bit position, due to the parallel

nature of the computer. The control signal will

go to 48 AND gates. In this instance the action

is:

$$\left[ (D) \longrightarrow Q \right] \cdot \left[ d_{-23} = 1 \right] \Longrightarrow \left[ 1 \longrightarrow q_{-23} \right]$$

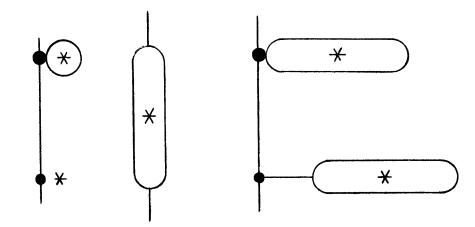

Representative Register Schematics

The computer is parallel in operation and registers contain many bits. Since the logic is identical for many of these bits, the drawing can be

representative and show the logic circuit for just one of the bits. A table accompanies the logic circuit drawing to list the connections to all of the circuits. The information signal line names will bear a subscript or superscript "x" instead of the specific bit position, for example, MA = 0 or PA = 1. When a circuit for a specific bit is different from the rest, the logic circuit for the bit is included in the drawing. Its signal lines will, of course, bear specific identification, e.g., ja\_1 = 0.

Data Registers - Subdivision of Control Signals

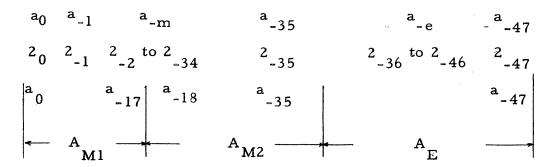

The data registers are subdivided into the mantissa and exponent sections to store floating point numbers. Furthermore, the end bits of each section have different logic circuits from the rest of the bits. The logic schematic shows 6 bits of the register (4 specific and 2 representative) and tables:

a<sub>-m</sub>(bits a<sub>-2</sub> through a<sub>-34</sub> of the mantissa)

a\_e (bits a\_36 through a\_46 of the exponent)

Examples of control signals for the register are:

$$(Q_E) \xrightarrow{1} A$$

Transfer the ones in the exponent section of Q to A.

$$q_{-1} \xrightarrow{1} a_{-47}$$

Transfer  $q_{-1}$  bit to  $a_{-47}$  if it is a one:

$(q_{-1} \xrightarrow{} a_{-47}) \cdot q_{-1} = 1 \Longrightarrow 1 \xrightarrow{} a_{-47}$ .

The parentheses is used here to simplify reading the terms of this logic.

## 3. INSTRUCTION SELECTION AND PERFORMANCE

## 3.1 Basic Program Cycle

The basic program cycle consists of the actions in selecting and performing an instruction. Unless altered by a jump instruction, the sequence of instructions performed is consecutively through the memory (by address). Each word contains two instructions, the instruction in the left half of the word ( $^2_0$  to  $^2_{-23}$  bits) is performed first.

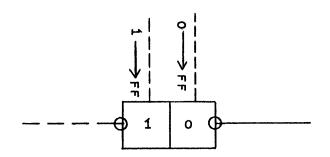

Normally, therefore, in this sequence, every other basic program cycle starts with a transfer from  $(V) \longrightarrow PR$  for a new instruction word. A control is required to specify on alternate cycles that a new instruction word is required. Another control is required to specify which half of the instruction word contains the instructions to be performed. Lastly, a control is required to alternate the first two controls between their two possible states. Flip-flops are used for these controls.

| PI =    | 01 | transfer an instruction word to PR from memory                                  |

|---------|----|---------------------------------------------------------------------------------|

| PI =    | 00 | no instruction word transfer required                                           |

| SW2 =   | 0  | perform I the instruction in PR <sub>0</sub>                                    |

| SW2 =   | 1  | perform I <sub>1</sub> , the instruction in PR <sub>1</sub>                     |

| MOD 2 = | 0  | the next instruction to be performed will be in $\ensuremath{^{\mathrm{PR}}}_0$ |

| MOD 2 = | 1  | the next instruction to be performed will be in $PR_1$                          |

SW2 as the control of the location in PR of the instruction currently being performed causes Mod 2 to alternate:

The complement of SW 2 is used since the next location is the alternate:

Mod 2's condition determines the ensuing state of PI.

$$(\text{Mod } 2 = 0) \implies (1 \longrightarrow \text{PI})$$

$$(\text{Mod } 2 = 1) \implies (0 \longrightarrow \text{PI})$$

And, at the proper time, Mod 2 will cause SW2 to alternate:

Mod 2 and PI which indicate actions to be performed following the performance of the current instruction can be switched during the performance of an instruction. SW2 must remain unchanged during the performance of an instruction as it is gating the command part of the instruction word to the command decoding network. SW2 is therefore switched between instructions.

The basic program includes timings of two control registers, PI and II. Program timings (PTs) can be considered as program cycle activities between instructions. This is the time SW2 is changed. PT2 is used as it is a timing common to both cases, transfer necessary or unnecessary from memory to PR.

All instructions go through the earlier timings of IT so it can be considered part of the basic program cycle. The complement of SW2 is transferred to Mod 2 in IT2. Following this, Mod 2's new state is transferred to PI in IT2 or IT3. The setting of PI in IT3 determines whether or not to get a new instruction word during the next set of PTs.

If the next instruction is already in PR, very little requires to be done during the PTs. To save time the computer in this case goes from "END" (a gating decision at the end of timings for AT, IT and FT) to PT2. In PT2, (Mod 2) ——SW2, to prepare to select the next instruction from PR. Then, unless the computer pauses due to a breakpoint or overflow or fault or operator intervention, it proceeds from PT4 to IT1 and the next instruction.

#### PI Time PI = 01

Three operations occur during these timings. A new instruction word is transferred from memory to PR (its address was stored in the PA register). Secondly, this address is increased by one and restored in PA to provide the next address of a normal sequence of instructions. Lastly, (Mod 2 —— SW2) to select the PR location. The activity during the four timings (PR1 to PT4) is:

PTI

- 1. Clear MA to receive address from PA 0 --- MA

- 2. Connect AN2 inputs for incrementing the address

MA ---- SW4 address will enter adder via MA

1 AN2C increment of one

0 --- PM no input from SW6

3. Clear PR for new word

$0 \longrightarrow PR$

PT2

- 1. Transfer address to MA to decode for memory access and for input to AN2 (PA) ---> MA

- 2. Start memory cycle

$1 \longrightarrow MI$

3. Prepare to select next instruction

(Mod 2) --- SW2

PT3

1. Clear PA for incremented address

$0 \longrightarrow PA$

PT4

- 1. Transfer incremented address to PA (AN2) -> PA

- 2. Proceed to next instruction unless control signals a pause —

→ ITI

#### Computer Pause

The term "pause" is used to identify the cause of the stopping of computer operation. Pause indicates the computer stopped for a reason other than a programmed stop (the Halt instruction) or machine malfunction (usually termed "hanging up"). The pause can be due to a Fault, Overflow, MA = MP, Breakpoint, operating in the STEP or TEST modes, or operator intervention by depressing the STOP switch.

It is normally desirable to have the computer pause just after completing the instruction during which a pause was signalled. When a Fault develops (Command, Memory or Exponent Fault) it is convenient to learn by the console display what instruction and what part of the program was being performed. If it were the  $I_1$  instruction, it is necessary to preserve (PR) by not reading in the next instruction word. The fault condition will therefore inhibit two signals,  $1 \longrightarrow PT1$  (avoid read-in new instruction word) and  $1 \longrightarrow TT1$  (do not go ahead to next instruction).

However, in the case of overflow, a unique situation exists due to the two jump instructions which are conditional upon overflow (JNO, JOF). In the case of JOF following an instruction whose performance generated an overflow, the computer should not pause, but proceed to jump.

This requires that program control must be always aware of the next instruction before a pause due to overflow. Therefore overflow will never stop the program cycle before PT1. The next instruction is an overflow jump. The timing logic of PT4 insures that the new word is in PR before the decision is made whether or not to pause. This situation also exists in the case of breakpoint, the JBT instruction.

STEP mode, MA = MP or operator intervention will cause the computer to pause in the same manner as a Fault, before PTl or ITl. TEST will be discussed in detail in the section on Operating Modes.

# First Basic Program Cycle

This first cycle must be manually selected. Console switches offer three choices:

# 4. COMPUTER CONSOLE AND OPERATING

# 4. l Console and Operating Controls

Figure 4.1-1 shows the S-2000 console. A brief description of each operating control and visual display is noted alongside each part of the console in this drawing.

Figure 4.1-1 S-2000 Console

### Computer ON or OFF

A single switch initiates the automatic turn-on cycle of the computer. This is the START switch at the extreme right of the console. At the end of the turn-on cycle, the READY indication will light.

The STOP switch at the extreme right of the console will turn D. C. off and initiate the automatic turn-off cycle.

Power for the Magnetic Core Stack Heaters is independent of the computer on-off switches and can be discontinued only at the main circuit breaker.