# ELECTRONIC DATA PROCESSING SYSTEMS

# PHILCO 2000 INPUT-OUTPUT SYSTEMS

# PHILCO 2000 INPUT-OUTPUT SYSTEMS

**July 1962**

## PHILCO CORPORATION

A SUBSIDIARY OF Ford Motor Company,

Computer Division • 3900 Welsh Road Willow Grove, Pennsylvania

#### **PREFACE**

A functional description of the operation of Input-Output Systems and Units of the Philco 2000 Electronic Data Processing System is contained in this manual. Where applicable, simplified block diagrams and flowcharts are also included.

This manual, TM-16A, is a minor revision of TM-16. All changes and corrections issued for TM-16 have been incorporated into this revision.

To permit incorporation of descriptions of new equipment as they become available, this manual has been published in loose-leaf form with each section individually numbered.

## TABLE OF CONTENTS

| Chapter |                                                                                                                                                                                                                      | Page                                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| I       | INTRODUCTION TO THE PHILCO 2000 INPUT-OUTPUT SECTION                                                                                                                                                                 | INT-1                                                       |

|         | ELEMENTS OF THE INPUT-OUTPUT SECTION  Buffer Units  Philco 1000 Computer Series  Recording Systems  Real-Time System  Digital Information Recorder  Accounting Clock System  Disc File System  Input-Output Channels | INT-1<br>INT-3<br>INT-3<br>INT-3<br>INT-3<br>INT-4<br>INT-4 |

|         | INITIATING INPUT-OUTPUT TRANSMISSIONS                                                                                                                                                                                | INT-4<br>INT-5<br>INT-6<br>INT-7                            |

|         | GENERAL OPERATION OF THE INPUT-OUTPUT SECTION                                                                                                                                                                        | INT-7                                                       |

|         | PHILCO 2000 CODE COMBINATIONS                                                                                                                                                                                        | INT-10                                                      |

| п       | MAGNETIC TAPE                                                                                                                                                                                                        | MT-1                                                        |

|         | INTRODUCTION                                                                                                                                                                                                         | MT-1                                                        |

|         | DATA FORMAT                                                                                                                                                                                                          |                                                             |

|         | ACCEPTANCE OF MAGNETIC TAPE ORDERS                                                                                                                                                                                   | MT-4                                                        |

|         | TAPE OPERATION                                                                                                                                                                                                       | MT-5<br>MT-7                                                |

| ш       | INPUT-OUTPUT PROCESSOR                                                                                                                                                                                               | IOP-1                                                       |

|         | INTRODUCTION                                                                                                                                                                                                         | IOP-1                                                       |

|         | MAJOR SECTIONS OF THE IOP                                                                                                                                                                                            | 10P-2                                                       |

| Chapte: | r                                                                                                               | Page   |

|---------|-----------------------------------------------------------------------------------------------------------------|--------|

|         | DATA FLOW                                                                                                       | IOP-   |

|         | Input Operations                                                                                                | IOP-   |

|         | Output Operations                                                                                               | IOP-   |

|         | Action of the Multiplexer                                                                                       | IOP-6  |

|         |                                                                                                                 |        |

|         | IOP ACCEPTANCE OF INPUT-OUTPUT ORDERS                                                                           | IOP-6  |

|         | Magnetic Tape and UBC Input-Output Orders                                                                       | IOP-   |

|         | Order Acceptance Procedures                                                                                     | IOP-   |

|         | TRANSFER OF PARAMETERS, CLASS A MAGNETIC TAPE                                                                   |        |

|         | AND UBC ORDERS                                                                                                  | IOP-10 |

|         | CHECKING FEATURES                                                                                               | TOD 11 |

|         | Assembler Availability Register                                                                                 | IOP-11 |

|         | Unit Availability Register                                                                                      | IOP-11 |

|         | Assembler Counter Register                                                                                      | IOP-11 |

|         | Assembler Fault Degister                                                                                        | IOP-11 |

|         | Assembler Fault Register                                                                                        | IOP-12 |

|         | OPERATING MODES OF MAGNETIC TAPE READ AND                                                                       |        |

|         | WRITE ORDERS                                                                                                    | IOP-12 |

|         | Error Cycles                                                                                                    | IOP-12 |

|         | Tape Position Following Error Conditions                                                                        | IOP-14 |

|         | CHADACTEDISTICS OF MITE IOD                                                                                     |        |

|         | CHARACTERISTICS OF THE IOP                                                                                      | IOP-15 |

|         | Operating Characteristics                                                                                       | IOP-15 |

|         | Physical Characteristics                                                                                        | IOP-15 |

| IV      | UNIVERSAL BUFFER-CONTROLLER                                                                                     | UBC-1  |

|         | INTRODUCTION                                                                                                    | UBC-1  |

|         |                                                                                                                 | ODC 1  |

|         | CONTROL AND DATA SELECT CHARACTERS                                                                              | UBC-1  |

|         | Absolute and Conditional Stop Characters                                                                        | UBC-1  |

|         | Data Select Code                                                                                                | UBC-1  |

|         | Absolute and Conditional Stop Codes                                                                             | UBC-2  |

|         | ORDER ACCEPTANCE                                                                                                |        |

|         |                                                                                                                 | UBC-2  |

|         |                                                                                                                 | UBC-2  |

|         | Off-Line Orders                                                                                                 | UBC-3  |

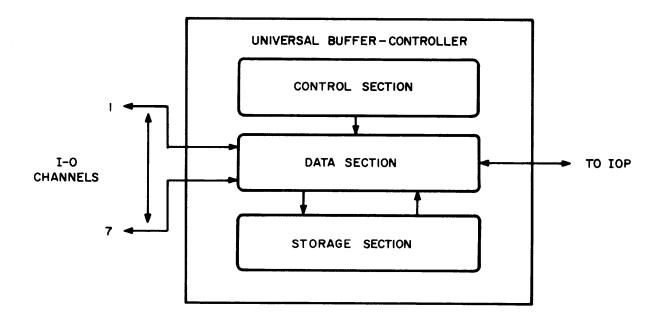

|         | MAJOR SECTIONS OF THE UBC                                                                                       | UBC-3  |

|         | DATA FLOW                                                                                                       | TIDA 4 |

|         | Loading Cycle During Magnetic Tape or IOP Operations                                                            | UBC-4  |

|         | Loading Cycle During Magnetic Tape or 10P Operations<br>Loading Cycle During Operations Involving Intermediate- | UBC-5  |

|         | Speed Devices                                                                                                   | UBC-5  |

|         |                                                                                                                 |        |

| Chapter |                                                                                                                   | Page   |

|---------|-------------------------------------------------------------------------------------------------------------------|--------|

|         | Unloading Cycle During Magnetic Tape and IOP Operations Unloading Cycle During Operations Involving Intermediate- | UBC-6  |

|         | Speed Devices                                                                                                     | UBC-6  |

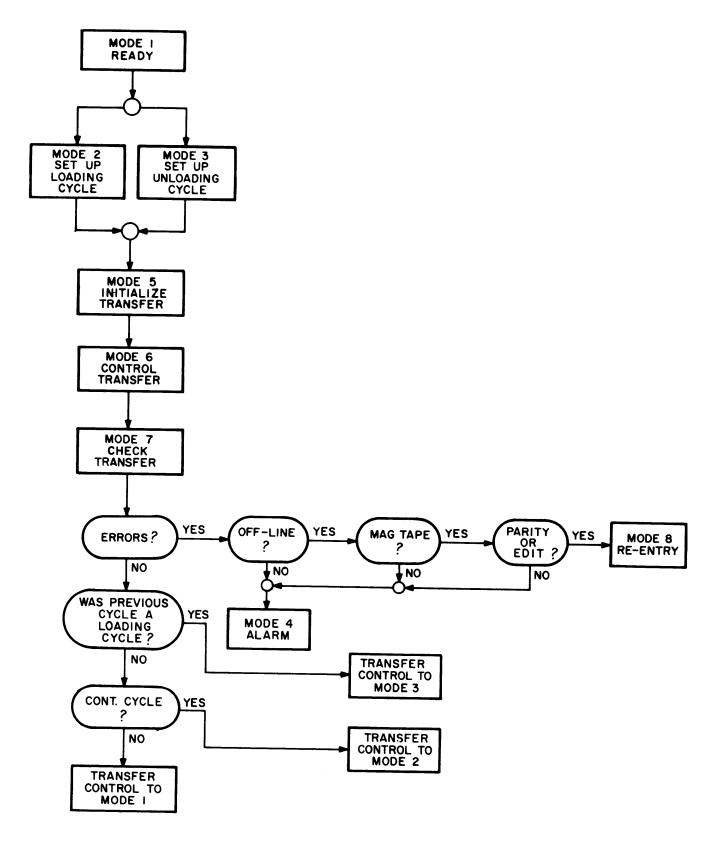

|         | OPERATING MODES OF THE UBC                                                                                        | UBC-7  |

|         | Mode 1, Ready                                                                                                     |        |

|         |                                                                                                                   | UBC-7  |

|         | Mode 4, Alarm                                                                                                     | OBC-8  |

|         | Mode 5, Initialize Transfer                                                                                       | OBC-8  |

|         | Mode 6, Control Transfer                                                                                          | OBC-8  |

|         | Mode 7, Check Transfer                                                                                            | 6-090  |

|         | Mode 8, Re-entry                                                                                                  | OBC-10 |

|         | Buffer Storage Accessing                                                                                          | OBC-10 |

|         | CHECKING FEATURES                                                                                                 | UBC-10 |

|         | CHARACTERISTICS OF THE UBC                                                                                        | UBC-10 |

|         | Operating Characteristics                                                                                         | UBC-10 |

|         | Physical Characteristics                                                                                          | UBC-11 |

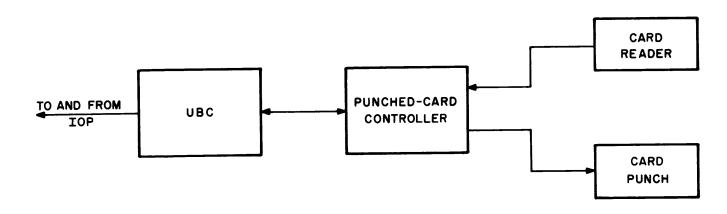

| v       | PUNCHED-CARD SYSTEM                                                                                               | PC-1   |

|         | INTRODUCTION                                                                                                      | PC-1   |

|         | CARD FORMAT                                                                                                       | PC-1   |

|         | DATA FORMAT                                                                                                       | PC-1   |

|         | FORMAT CONTROL                                                                                                    | PC-2   |

|         | FORMAT CONTROL                                                                                                    | PC-3   |

|         | Control Characters                                                                                                | PC-3   |

|         |                                                                                                                   |        |

|         | THE PUNCHED-CARD CONTROLLER                                                                                       | PC-4   |

|         | ACCEPTANCE OF PUNCHED-CARD ORDERS                                                                                 | PC-5   |

|         | ACCEPT EX-CARD CONTROL                                                                                            | PC-5   |

|         | CHECKING FEATURES                                                                                                 | PC-5   |

|         | Parity Fault Indications                                                                                          | PC-6   |

|         | Edit Fault Indication                                                                                             | PC-6   |

|         | Mechanical Fault Indications                                                                                      | PC-6   |

|         | CHARACTERISTICS OF THE PUNCHED-CARD SYSTEM                                                                        | PC-7   |

| Chapte | r                                                                                 | Pag                     |

|--------|-----------------------------------------------------------------------------------|-------------------------|

| VI     | PAPER TAPE SYSTEMS                                                                | PT-                     |

|        | INTRODUCTION                                                                      | PT-                     |

|        | DATA FORMAT                                                                       | <b>PT-</b> :            |

|        | PAPER TAPE SYSTEM, MODEL 240  I-O Order Acceptance, Model 240  Control Characters | PT-:<br>PT-:<br>PT-:    |

|        | Data Flow, Model 240                                                              | PT-4                    |

|        | Data Flow During the Punching Operation                                           | PT-5<br>PT-6<br>PT-7    |

|        | THE ACCOUNTING CLOCK SYSTEM                                                       | PT-7                    |

|        | System Tie-In                                                                     | PT-8                    |

|        | Checking Features                                                                 | PT-8                    |

|        | PAPER TAPE SYSTEM, MODEL 241                                                      | PT-9<br>PT-10           |

|        | Order Acceptance Operating Controls Data Flow                                     | PT-10<br>PT-11<br>PT-11 |

|        | Reading and Punching Eight-Channel Tape                                           | PT-11<br>PT-12<br>PT-13 |

|        | Summary of Operating Characteristics, Model 241                                   | PT-14                   |

|        | OPERATING CHARACTERISTICS OF PAPER TAPE SYSTEMS                                   | PT-14                   |

|        | PHYSICAL CHARACTERISTICS OF PAPER TAPE                                            | PT-14                   |

| VII    | THE PRINTING SYSTEM                                                               | PR-1                    |

|        | INTRODUCTION                                                                      | <b>P</b> R-1            |

|        | CONTROL CHARACTERS                                                                | PR-1                    |

|        | End-Of-Line Character                                                             | PR-1                    |

|        | Space Character                                                                   | PR-1<br>PR-1            |

|        | DATA FORMAT                                                                       | PR-1                    |

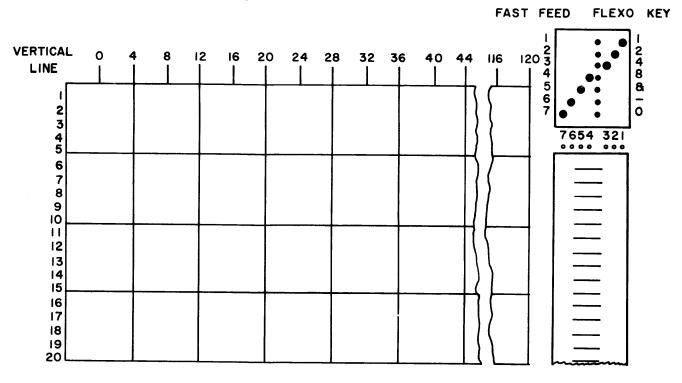

|        | Vertical Format                                                                   | PR-2                    |

|        | Horizontal Format                                                                 | PR-3                    |

|        |                                                                                   |                         |

| Chapter |                                                   | Page          |

|---------|---------------------------------------------------|---------------|

|         | HIGH-SPEED PRINTER LAYOUT SHEET                   | PR-4          |

|         | ORDER ACCEPTANCE                                  | PR-6          |

|         | DATA FLOW                                         | PR-6          |

|         | PRINTING CYCLE                                    | PR-7          |

|         | OPERATING MODES                                   | PR-7          |

|         | Write All Mode                                    | PR-8          |

|         | Test Mode                                         | PR-9          |

|         | CHECKING FEATURES                                 | PR-9          |

|         | Parity Error Conditions                           | PR-9<br>PR-9  |

|         | Mechanical Faults                                 | PR-9<br>PR-10 |

|         | OPERATING CONTROLS                                | PR-10         |

|         |                                                   | FIC-10        |

|         | CHARACTERISTICS OF THE HIGH-SPEED PRINTING SYSTEM | PR-10         |

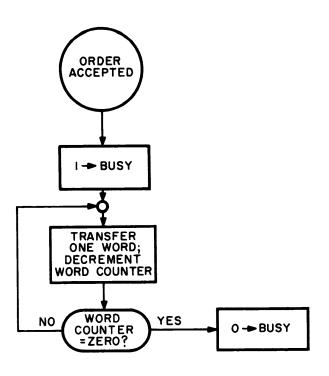

| VIII    | MAGNETIC DRUM SYSTEM                              | DR-1          |

|         | INTRODUCTION                                      | DR-1          |

|         | DATA FORMAT                                       | DR-1          |

|         | ORDER ACCEPTANCE                                  | DR-2          |

|         | DRUM OPERATION                                    | DR-3          |

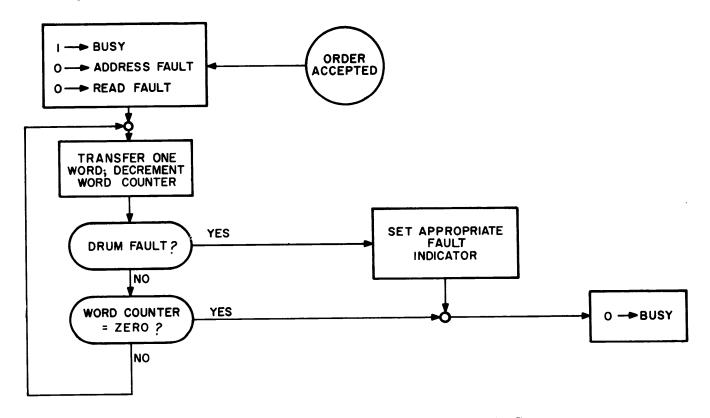

|         | Reading Operation                                 | DR-4          |

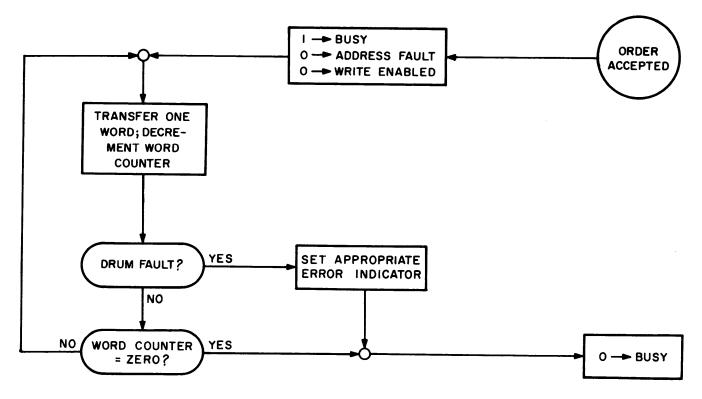

|         | Writing Operation                                 | DR-5          |

|         | Band Switching                                    | DR-6          |

|         | CHECKING FEATURES                                 | DR-6          |

|         | WRITE DISABLE                                     | DR-6          |

|         | OPERATING CHARACTERISTICS                         | DR-7          |

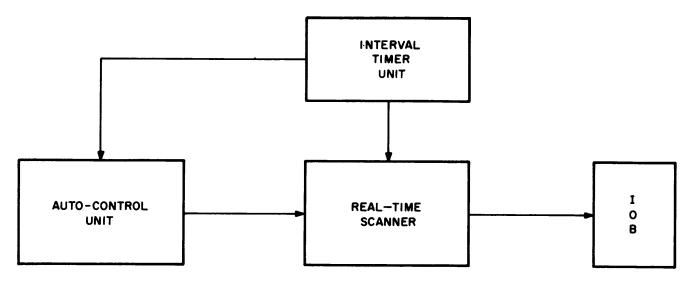

| IX      | THE REAL-TIME SYSTEM                              | RT-1          |

|         | INTRODUCTION                                      | RT-1          |

|         | SYSTEM TIE-IN                                     | RT-1          |

|         | FUNCTIONAL DESCRIPTION OF THE REAL-TIME SCANNER   | RT-1          |

| Chapter |                                                                                                                                              | Page                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

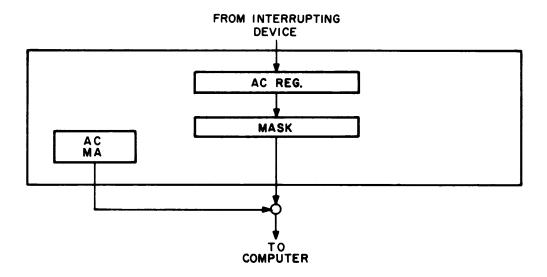

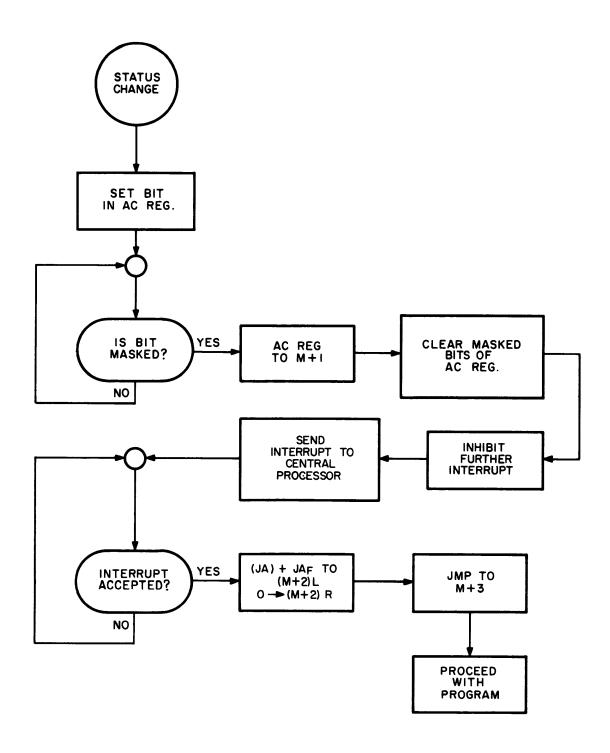

|         | FUNCTIONAL DESCRIPTION OF THE AUTO-CONTROL UNIT.  Major Components of the Auto-Control Unit                                                  | RT-2<br>RT-3<br>RT-3<br>RT-4 |

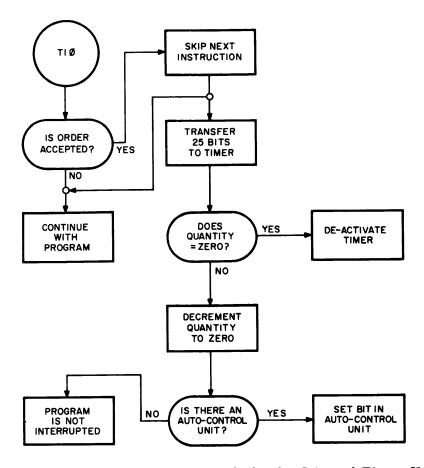

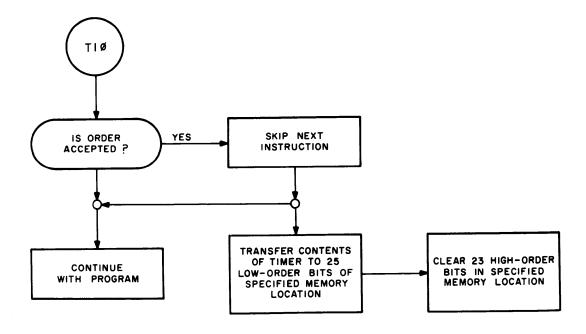

|         | FUNCTIONAL DESCRIPTION OF THE TIMER                                                                                                          | RT-6                         |

| x       | DESCRIPTION OF INPUT-OUTPUT ORDERS AND INSTRUCTIONS                                                                                          | TAC-                         |

|         | INTRODUCTION                                                                                                                                 | TAC-1                        |

|         | Coding Input-Output Orders                                                                                                                   | TAC-1<br>TAC-1<br>TAC-3      |

|         | DESCRIPTION OF INPUT-OUTPUT ORDERS  Magnetic Tape Orders  UBC Input-Output Orders  Paper Tape Orders  Magnetic Drum Orders  Real-Time Orders | TAC-4<br>FAC-14<br>FAC-19    |

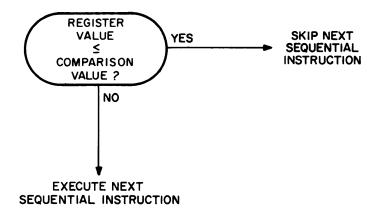

|         | SKIP INSTRUCTIONS AND RELATED INPUT-OUTPUT REGISTERS                                                                                         | TAC-23<br>TAC-24<br>TAC-24   |

|         | INTRODUCTION TO INPUT-OUTPUT MACRO-INSTRUCTIONS T Coding Procedure                                                                           | TAC-32<br>TAC-33             |

# LIST OF ILLUSTRATIONS

| Figure |                                                                                      | Page   |

|--------|--------------------------------------------------------------------------------------|--------|

| INT-1  | Simplified Block Diagram of the Philco 2000 Input-Output Section                     | INT-2  |

| INT-2  | Breakdown of D Register Showing Parameters of I-O Order                              | INT-5  |

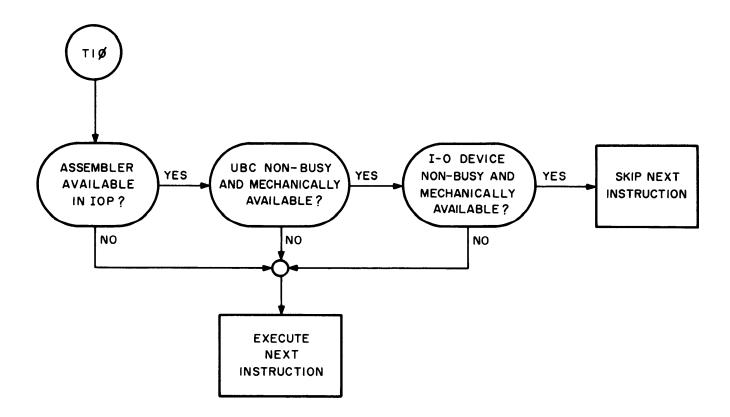

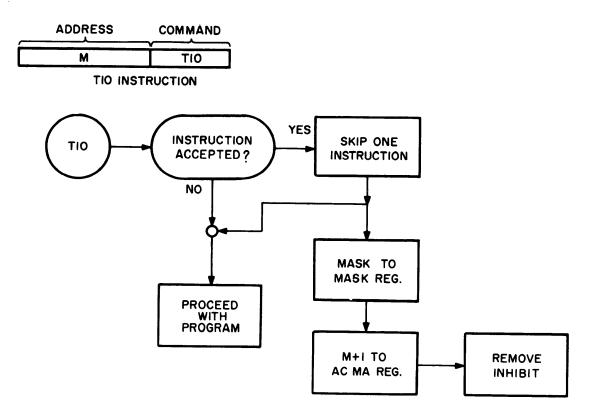

| INT-3  | Flowchart of the Operations Performed Following the Execution of the TIO Instruction | INT-6  |

| INT-4  | General Operation of the Input-Output System                                         | INT-9  |

| INT-5  | Philco 2000 Code Combinations                                                        | INT-11 |

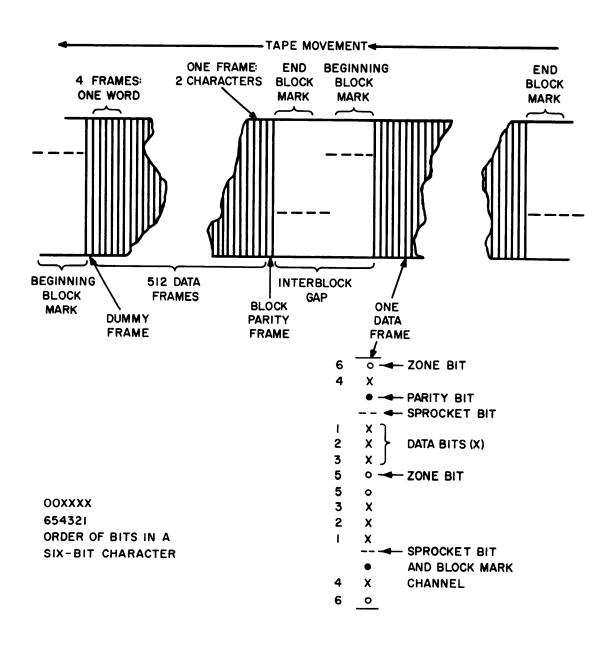

| MT-1   | Arrangement of Data on Magnetic Tape                                                 | MT-1   |

| MT-2   | Magnetic Tape Format                                                                 | MT-2   |

| MT-3   | Arrangement of Characters on Tape                                                    | MT-6   |

| IOP-1  | Major Sections of IOP                                                                | IOP-1  |

| IOP-2  | Operation of the IOP During Input Order                                              | IOP-3  |

| IOP-3  | Operation of the IOP During Output Order                                             | IOP-3  |

| IOP-4  | Data Flow in Assembler During Input Order                                            | IOP-4  |

| IOP-5  | Data Flow in Assembler During Output Order                                           | IOP-5  |

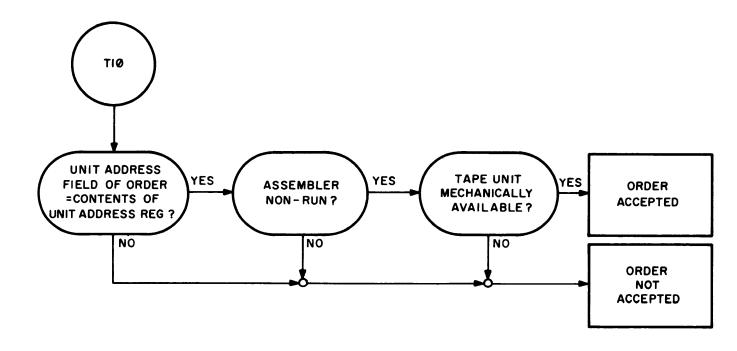

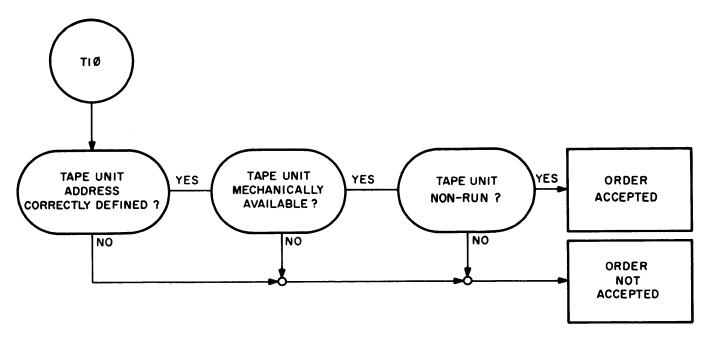

| IOP-6  | Flowchart of Class A and UBC Order Acceptance                                        | IOP-8  |

| IOP-7  | Flowchart of Class B Magnetic Tape Order Acceptance                                  | IOP-9  |

| IOP-8  | Flowchart of Class C Magnetic Tape Order Acceptance                                  | IOP-9  |

| IOP-9  | Flowchart of Class D Magnetic Tape Order Acceptance                                  | IOP-10 |

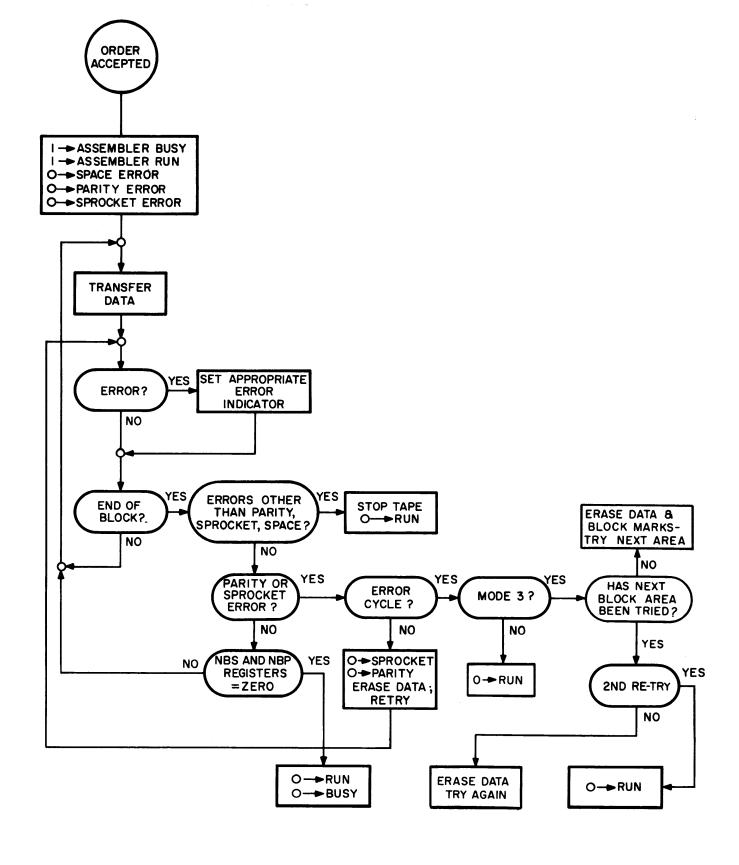

| IOP-10 | Action of IOP Following Magnetic Tape Parity or Sprocket Errors                      | IOP-13 |

| IOP-11 | Simplified Diagram of Block Areas on Magnetic Tape                                   | IOP-14 |

| UBC-1  | Flowchart of On-Line UBC Order (Core to I-O Device)                                  | UBC-2  |

| UBC-2  | Major Sections of the UBC                                                            | UBC-4  |

| UBC-3  | Flowchart of UBC Operation Modes                                                     | UBC-8  |

| PC-1   | Tie-In of Punched-Card System with 2000 System                                       | PC-1   |

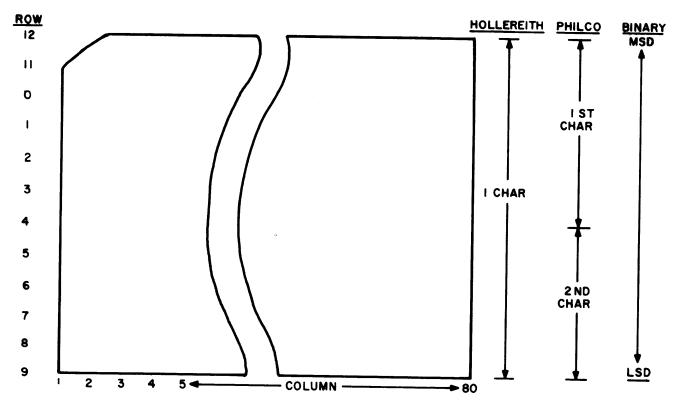

| PC-2   | Punched-Card Format                                                                  | PC-2   |

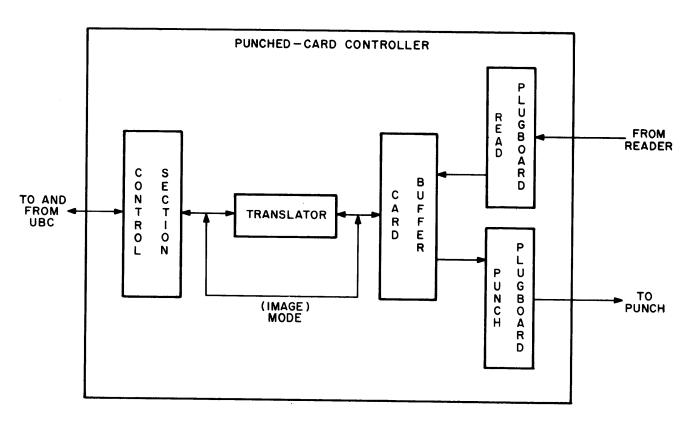

| PC-3   | Principal Components of Punched-Card Controller                                      | PC-4   |

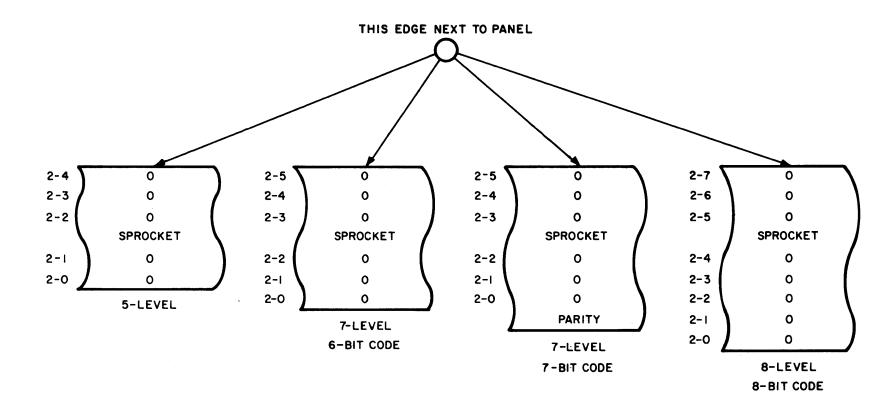

| PT-1   | Data Format on Paper Tape                                                            | PT-2   |

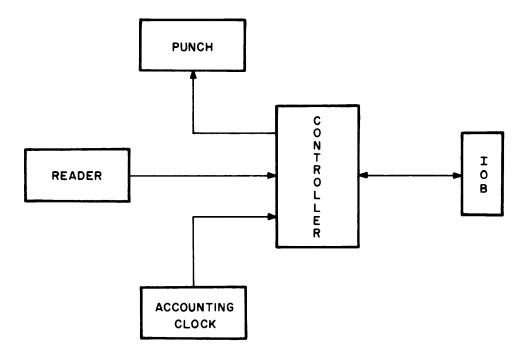

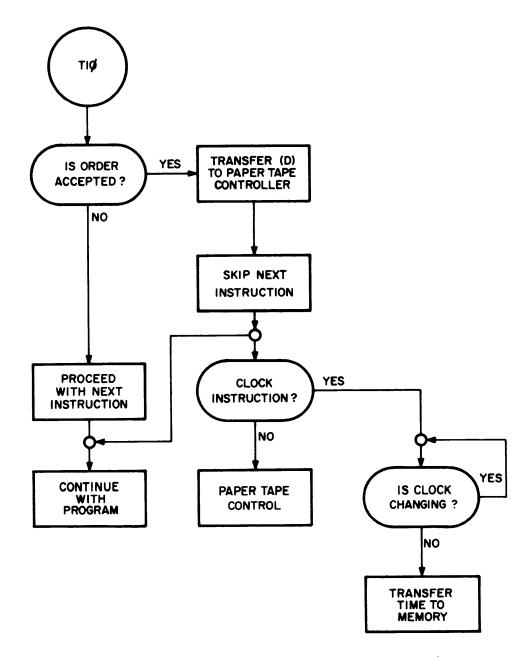

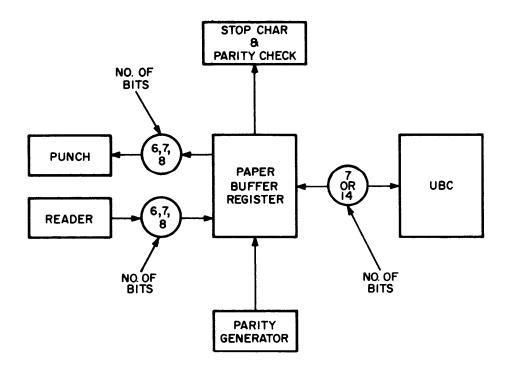

| PT-2   | Tie-In of Major Components of Paper Tape System, Model 240, Simplified Block Diagram | PT-3   |

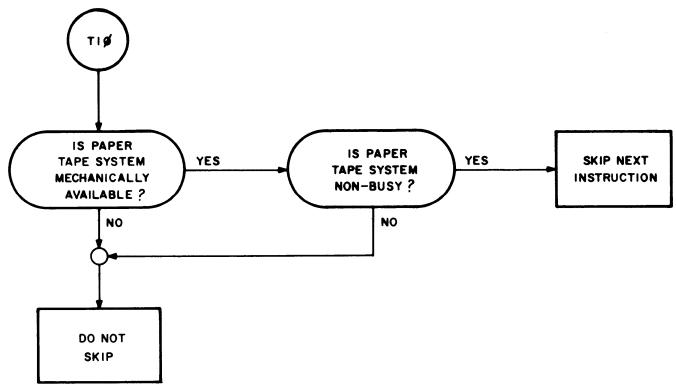

| PT-3   | Flowchart of Paper Tape System, Model 240, Order Acceptance Procedure                | PT-4   |

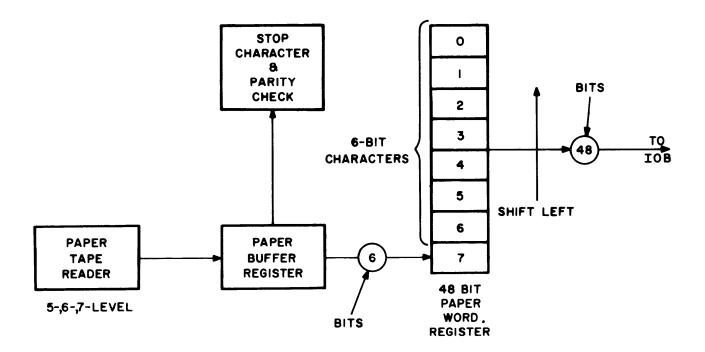

| PT-4   | Data Flow During Paper Tape System, Model 240, Reading Operation                     | PT-5   |

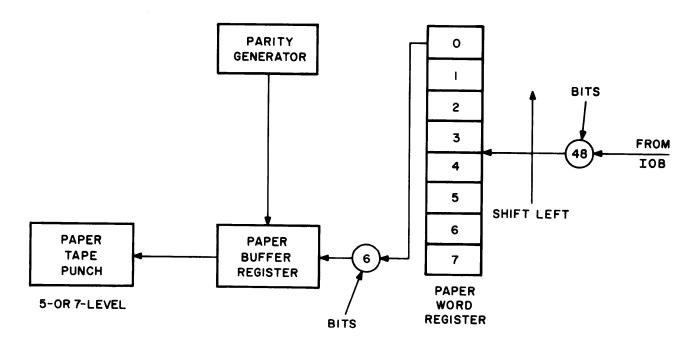

| PT-5   | Data Flow During Paper Tape System, Model 240, Punching Operation                    | PT-6   |

# LIST OF ILLUSTRATIONS (Cont'd.)

| Figure |                                                                                              | Page   |

|--------|----------------------------------------------------------------------------------------------|--------|

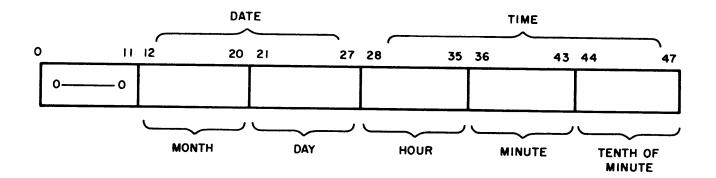

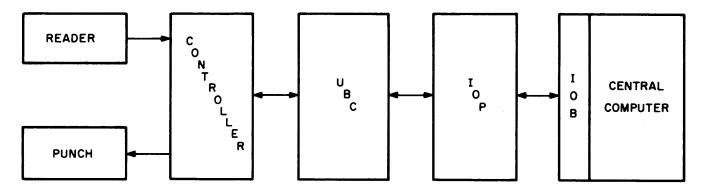

| PT-6   | Format of Accounting Clock Word                                                              | PT-8   |

| PT-7   | Accounting Clock System Input-Output Order                                                   | PT-8   |

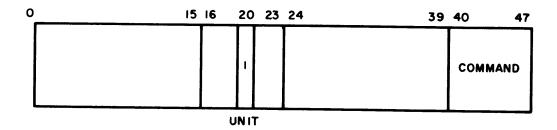

| PT-8   | Flow Chart Outlining Action of Clock Order                                                   | PT-9   |

| PT-9   | Paper Tape System, Model 241, Tie-In With Central Computer                                   | PT-10  |

| PT-10  | Data Flow During Reading Operation, Paper Tape System, Model 241                             | PT-12  |

| PT-11  | Format of One Word in Memory Following a Reading Operation of Eight-Level Tape               | PT-13  |

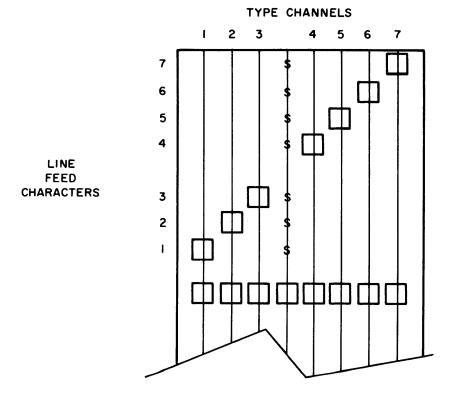

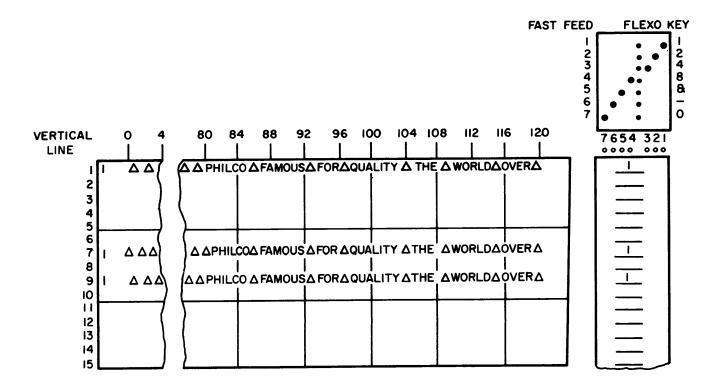

| PR-1   | Vertical Format Tape Loop                                                                    | PR-2   |

| PR-2   | High-Speed Printer Layout                                                                    | PR-4   |

| PR-3   | Use of Printer Layout Sheet                                                                  | PR-5   |

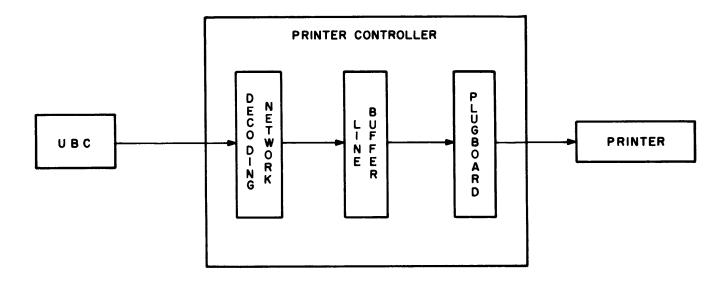

| PR-4   | Data Flow During A Printing Operation                                                        | PR-7   |

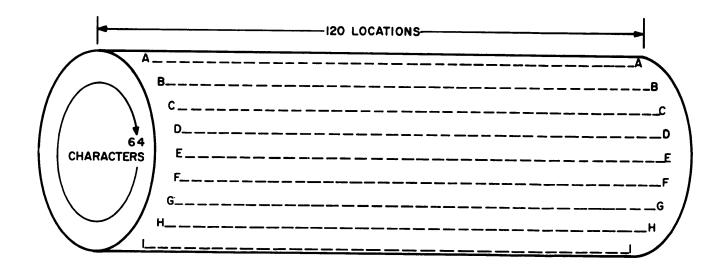

| PR-5   | Print Roll of High-Speed Printer                                                             | PR-8   |

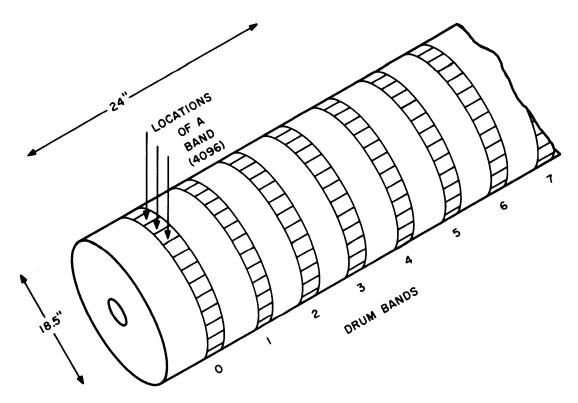

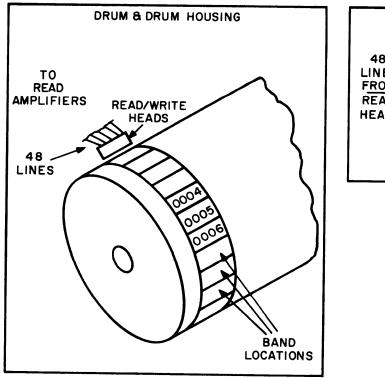

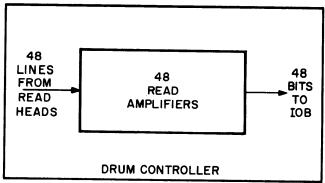

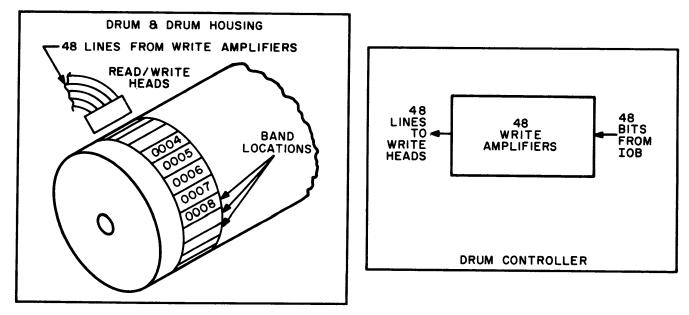

| DR-1   | Simplified Drawing of Drum Showing Drum Bands and Data Locations of These Bands              | DR-1   |

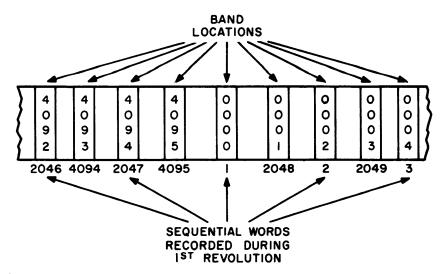

| DR-2   | Section of Drum Band Showing Band Locations and Sequential Words Recorded in These Locations | DR-2   |

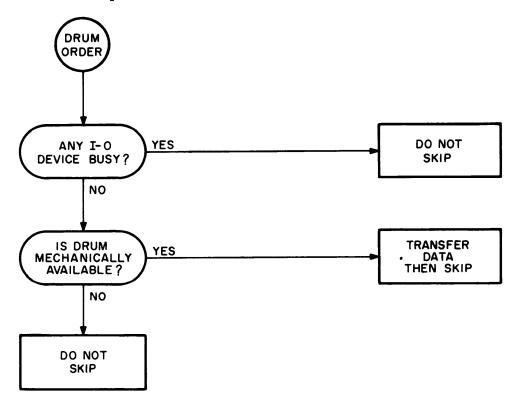

| DR-3   | Flowchart of Drum Order Acceptance Procedure                                                 | DR-3   |

| DR-4   | Data Flow During Reading Operation                                                           | DR-4   |

| DR-5   | Data Flow During Writing Operation                                                           | DR-5   |

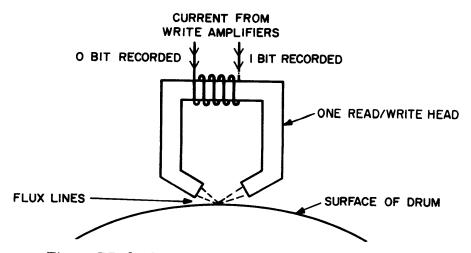

| DR-6   | Writing Method for 1 and 0 Bits                                                              | DR-5   |

| RT-1   | Real-Time System, Simplified Block Diagram                                                   | RT-2   |

| RT-2   | Registers of Auto-Control Unit                                                               | RT-3   |

| RT-3   | Setup of Auto-Control Unit                                                                   | RT-4   |

| RT-4   | Auto-Control Operation                                                                       | RT-5   |

| RT-5   | Flowchart of Output Order for Interval Timer Unit                                            | RT-7   |

| RT-6   | Flowchart of Input Order for Interval Timer Unit                                             | RT-7   |

| TAC-1  | Input-Output Orders                                                                          | TAC-2  |

|        | Flowchart of TIO Instruction                                                                 | TAC-5  |

| TAC-3  | Flowchart of Magnetic Tape Read Order                                                        | TAC-7  |

| TAC-4  | Flowchart of Magnetic Tape Write Order                                                       | TAC-8  |

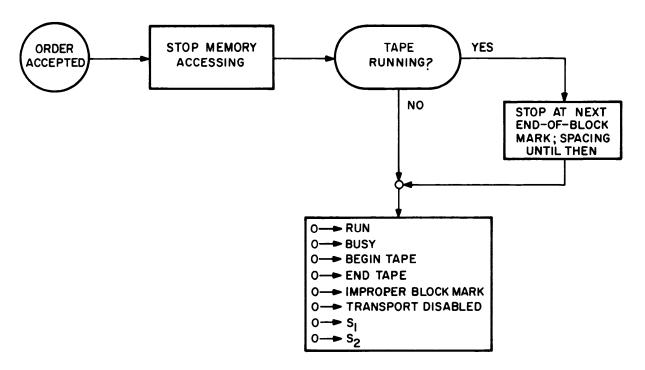

|        | Flowchart of Magnetic Tape Stop Order                                                        | TAC-9  |

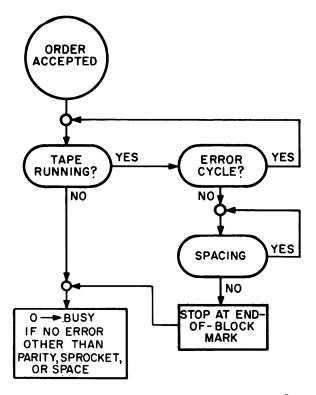

|        | Flowchart of Magnetic Tape Release Order                                                     | TAC-10 |

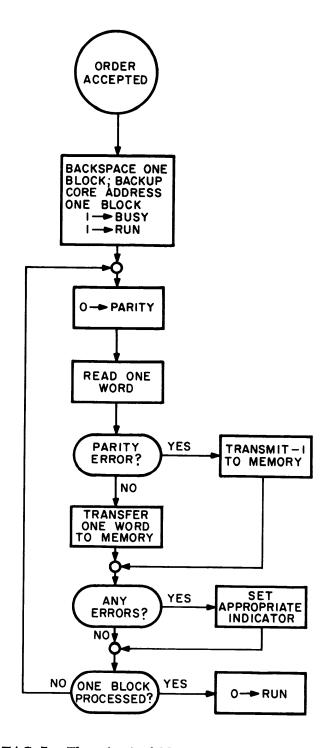

|        | Flowchart of Magnetic Tape -1 Read Order                                                     | TAC-11 |

# LIST OF ILLUSTRATIONS (Cont'd.)

| Figure |                                                                                         | Page   |

|--------|-----------------------------------------------------------------------------------------|--------|

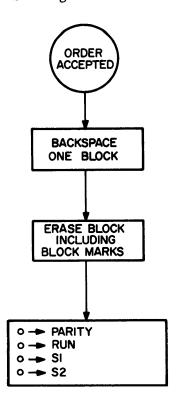

| TAC-8  | Flowchart of Magnetic Tape Erase Order                                                  | TAC-12 |

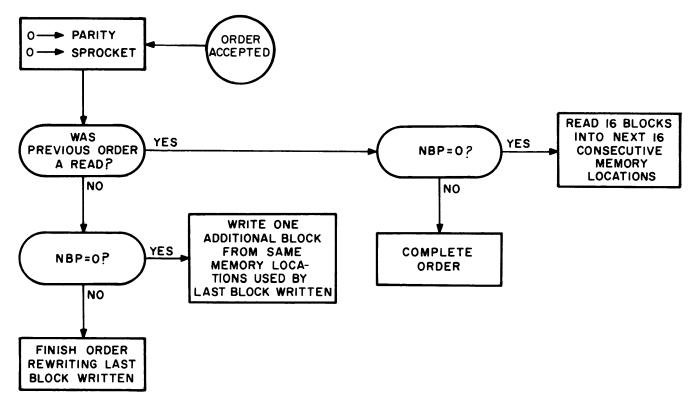

| TAC-9  | Flowchart of Magnetic Tape Resume Order                                                 | TAC-14 |

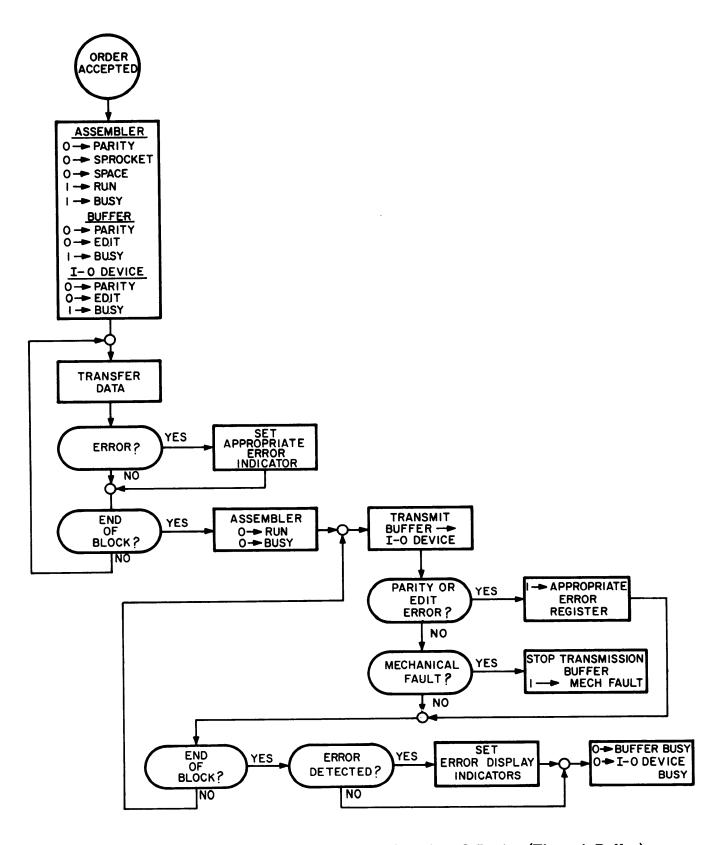

| TAC-10 | Flowchart of I-O Order, Core to I-O Device (Through Buffer)                             | TAC-16 |

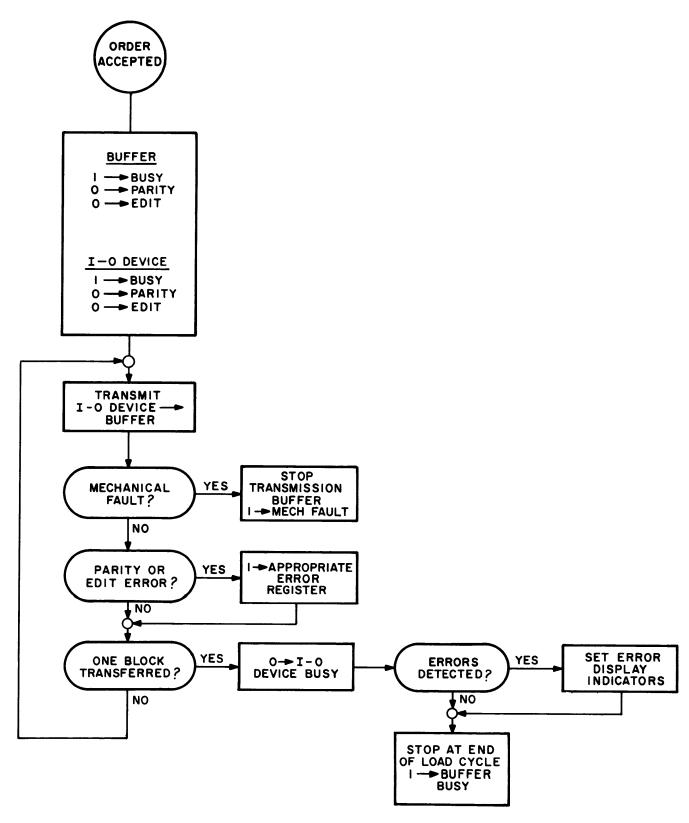

| TAC-11 | Flowchart of I-O Order, I-O Device to Buffer (One-line Push Button on Buffer Depressed) | TAC-17 |

| TAC-12 | Flowchart of On-Line I-O Order, Buffer to Core                                          | TAC-18 |

|        | Flowchart of I-O Order, Paper Tape to Core (Not Through IOP)                            |        |

|        |                                                                                         | TAC-20 |

| TAC-14 | Flowchart of I-O Order, Core to Paper Tape (Not Through IOP)                            | TAC-21 |

| TAC-15 | Flowchart of I-O Order, Drum to Core                                                    | TAC-21 |

| TAC-16 | Flowchart of I-O Order, Core to Drum                                                    | TAC-22 |

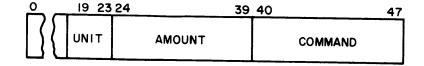

| TAC-17 | Flowchart of Skip Instructions                                                          | TAC-23 |

| TAC-18 | Format of SKC and SKF Instructions                                                      | TAC-24 |

| TAC-19 | Relation Between Assembler Counter and CQ Field of SKCA                                 | TAC-27 |

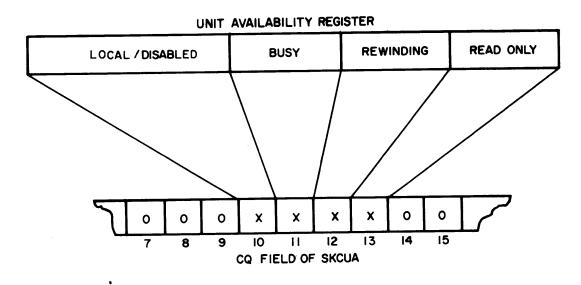

| TAC-20 | Relation Between Unit Availability Register and CQ Field of SKCUA                       | TAC-28 |

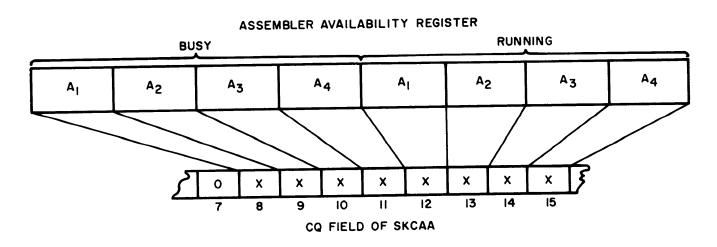

| TAC-21 | Relation Between Assembler Availability Register and CQ Field of                        |        |

|        | SKCAA                                                                                   | TAC-28 |

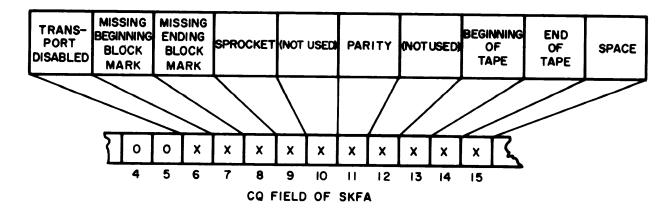

| TAC-22 | Relation Between Assembler Fault Register and CQ Field of SKFA                          | TAC-29 |

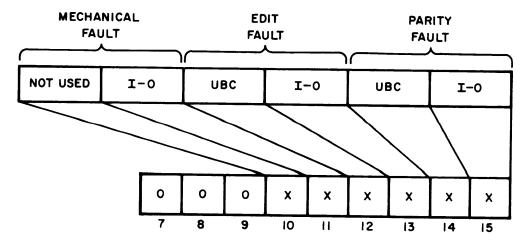

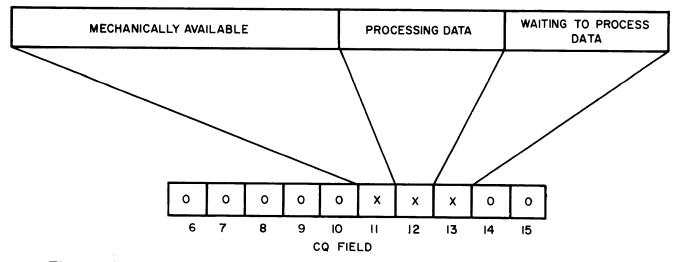

| TAC-23 | Relation Between Buffer-Controller Register and CQ Field of SKFB                        | TAC-29 |

| TAC-24 | Relation Between Paper Tape Transmission Register and CQ Field of                       |        |

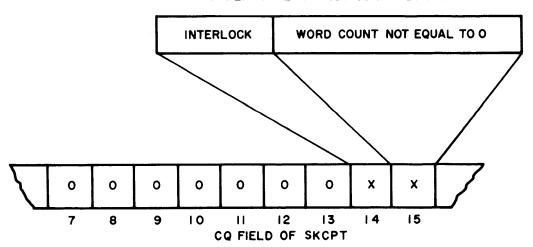

|        | SKCPT                                                                                   | TAC-30 |

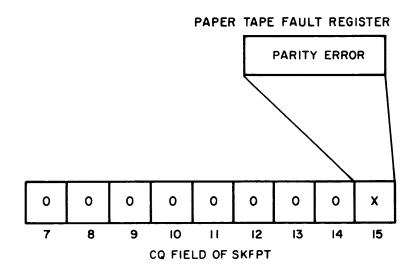

| TAC-25 | Relation Between Paper Tape Fault Register and CQ Field of SKFPT                        | TAC-31 |

| TAC-26 | Relation Between Drum Fault Register and CQ Field of SKFD                               | TAC-31 |

| TAC-27 | Relation Between Real-Time System and CQ Field of Real-Time Skip                        |        |

|        | Instructions                                                                            | TAC-32 |

#### LIST OF TABLES

| Table |                                                   | Page   |

|-------|---------------------------------------------------|--------|

| IOP-1 | Table of Tape Position Following Error Conditions | IOP-15 |

| PT-1  | Read Mode of Operation                            | PT-15  |

| PT-2  | Punch Mode of Operation                           | PT-15  |

| TAC-1 | Table of Skip Instructions                        | TAC-35 |

# INTRODUCTION TO THE PHILCO 2000 INPUT-OUTPUT SECTION

The Input-Output Section of the Philco 2000 Electronic Data Processing System consists of a group of highly specialized data processing devices that control the transmission of all data into and out of the Central Computer. These devices are individual processing systems whose on-line operation may be initialized either by programmed instructions or by operator intervention at the computer console. With either method, once an order has been accepted by an input-output (I-O) system the Central Computer is released from the transfer operation and is free to continue with the main computer program. For example, during input operations the computer continues with the execution of the program while the I-O system assembles data into full computer words. After each word has been assembled, computer processing is interrupted only for the length of time necessary to transfer that word from the I-O system into memory.

During output operations, computer processing is interrupted only for the length of time required to transfer each full word from memory to the I-O system. The I-O system controls the processing of the word while the computer continues with the execution of the program.

#### **ELEMENTS OF THE INPUT-OUTPUT SECTION**

The Input-Output Section contains three major buffer units, five different data recording systems, a Real-Time System, a Digital Information Recorder, Disc File System and an Accounting Clock System. The I-O Section is so designed that any system or unit may be easily installed or removed, depending upon the needs of the specific installation.

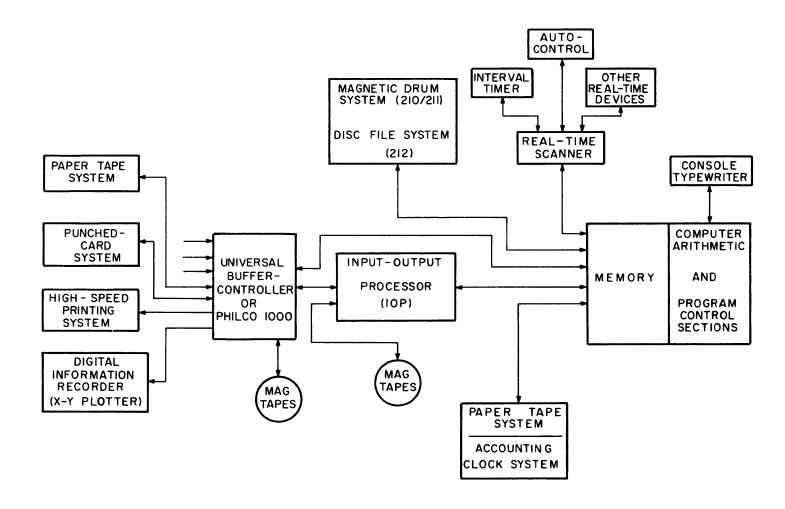

The elements of the I-O Section are illustrated in figure INT-1, and their basic function is presented on the following pages. The figure also shows the relationship between elements and their tie-in with the Central Computer.

#### BUFFER UNITS

The buffer units include an Input-Output Buffer Register (IOB), an Input-Output Processor (IOP), and a Universal Buffer-Controller (UBC).

#### The IOB

The IOB is a 48-bit register which is used to store one computer word while that word is being written into or read out of the computer memory. This register receives inputs over four different I-O channels and is physically a part of the Central Computer.

#### The IOP

The IOP is a data processing unit used to couple magnetic tape units and UBC'S to the Central Computer. The IOP accepts inputs and provides outputs over 16 channels and allows data to be transferred over any four of these channels simultaneously.

Figure INT-1. Simplified Block Diagram of the Philco 2000 Input-Output Section

#### The UBC

The UBC provides temporary storage for one block of data (128 words) during on-line operations between the Central Computer and intermediate-speed I-O systems, or during off-line data conversions between any two Philco 2000 I-O media. The I-O systems included in the intermediate speed classification are the Punched-Card and Paper Tape Systems and the High-Speed Printing System.

The UBC has eight data channels which are numbered zero through seven. Channel zero is used exclusively for transferring data to and from the IOP. Channels one and two can be used either for magnetic tape operations or for operations involving the intermediate-speed systems. Channels three through seven are used for the intermediate-speed systems only.

#### PHILCO 1000 COMPUTER SERIES

The Philco 1000 Computer Series provides stored program computers for installations requiring preformating and post-editing of data for the Philco 2000. A description of the Input-Output equipment in relation to these computers will be found in the Philco 1000 Manual.

#### RECORDING SYSTEMS

The recording systems include a Paper Tape System, a Punched-Card System, a Magnetic Drum System, a High-Speed Printing System, and a Magnetic Tape System. These systems (with the exception of the printing system, which only records data) provide the means necessary to translate stored data from an I-O medium into electrical pulses which can be used by the computer. In the reverse, they receive electrical pulses from the computer and record them onto an I-O medium. The recorded data can then be stored or used immediately in additional processing operations.

#### REAL-TIME SYSTEM

The Real-Time System couples any real-time device (radar, teletype, etc.) directly to the Central Computer memory through the IOB. This system includes an Auto-Control Unit with built-in Real-Time Scanner, and an optional Interval Timer Unit.

The Real-Time Scanner multiplexes data from as many as eight real-time devices; the Interval Timer Unit provides a time reference which can be set to facilitate the interlacing of programs; the Auto-Control Unit provides a means of interrupting the main program whenever specified conditions occur in either the Input-Output Section or in the Central Computer.

#### DIGITAL INFORMATION RECORDER

The Digital Information Recorder is a plotter capable of recording discrete points, continuous curves, letters, numerals, and symbols, based on the output of the Philco 2000. The information to be plotted may come directly from the Central Processor by way of the Universal Buffer-Controller (UBC), or from any input device, such as punched cards, paper tape, or magnetic tape connected to the UBC. Up to four recorders may be coupled to any channel of the UBC.

#### ACCOUNTING CLOCK SYSTEM

The Accounting Clock System works through the Paper Tape Controller of the Model 240 Paper Tape System, and provides a means of writing into memory at any specified point in the program the month, day, hour, minute, and tenth of a minute for accounting purposes.

#### DISC FILE SYSTEM

The Philco Disc File System provides a high-speed rapid access storage for the Philco 2000. The Disc File System is connected to the memory of the Central Processor, providing a direct flow of data between the discs and memory without interfering with other input-output operations. An order for data from the disc is transmitted and stored in the Disc File System, allowing the Central Processor to proceed immediately with previously read-in data while concurrently processing the disc order. The input or output of the disc is multiplexed with all other accesses to memory, including High-Performance tapes.

#### INPUT-OUTPUT CHANNELS

The I-O systems are coupled to the Central Computer memory through the IOB over four different I-O channels, and share memory access time with the Central Computer in a sequence established on a channel priority basis. This means that before each memory request is granted, the Central Computer scans the I-O channels in the established sequence to determine whether or not a previous request has been made from an I-O system operating over a higher priority channel. (It should be noted that the computer memory is accessed each time a word is transferred.)

The order of assigned channel priority and the I-O systems associated with each channel are as follows:

a. IOP Channel

- One IOP, and any combination of magnetic tape units and UBC'S, up to a total of 16 devices. Of the 16, a maximum of four may be UBC'S.

- b. Real-Time Channel

- Real-Time System

- c. Word-At-A-Time Channel

- One Paper Tape System and one Accounting Clock System

- d. Magnetic Drum or Disc Channel

- Magnetic Drum System (It should be noted that after memory access time is granted during a magnetic drum order, memory cannot be accessed again until the drum order is completed.)

On the Philco 212, the Disc File System is used rather than the Drum.

#### INITIATING INPUT-OUTPUT TRANSMISSIONS

The basic instruction used to initiate the processing of input-output data is the TIO instruction (Transfer Control to Input-Output). When a computer core starting address is required, that memory address is specified by the address portion of the TIO instruction. For example, if the transfer operation were to begin with memory location 1000, the TIO instruction would be written as follows:

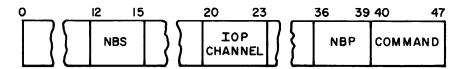

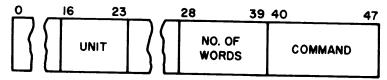

Basically, the TIO instruction transfers the contents of the D Register to an I-O system. The D Register should contain all the information necessary to perform the transfer operation. This information, which must be prepared before it is placed in the D Register, is called the input-output order. Input-output orders are 48 bits in size, as differentiated from the standard 24-bit computer instruction. As shown in figure INT-2, the D Register is apportioned as follows to contain the parameters of all I-O orders.

| STARTING ADDRESS | UNIT ADDRESS BUFFER AMOUNT OF INFORM | AMOUNT OF INFORMATION   | COA               | OMMAND |       |

|------------------|--------------------------------------|-------------------------|-------------------|--------|-------|

| OTANTINO ADDICES | OWY ADDRESS                          | CHANNEL                 | TO BE TRANSMITTED | FROM   | то    |

| 0.               | 16◆ →23                              | 24 <del>&lt; </del> ≥27 | 28                | 40-43  | 44—47 |

|                  | 725                                  | 244721                  | 207               | †<br>† |       |

Figure INT-2. Breakdown of D Register Showing Parameters of I-O Order

| BITS          | CONTENTS                                                                                                                                                            |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 through 15  | Location of information within the I-O device; the number of blocks to be spaced during magnetic tape operations                                                    |

| 16 through 23 | IOP channel to which UBC is connected, use bits 20-23; Unit number for real-time devices, use bits 19-22.                                                           |

| 24 through 27 | UBC channel to which I-O device is connected                                                                                                                        |

| 28 through 39 | Amount of information to be transferred (i.e., number of words, cards, or blocks)                                                                                   |

| 40 through 47 | Command — indicates which I-O device is being used. Determines if the order is transferring information to memory from the I-O device, or from memory to the device |

|               | Bits 40 through 43 indicate device from which data is received. Bits 44 through 47 indicate device to which data is transmitted                                     |

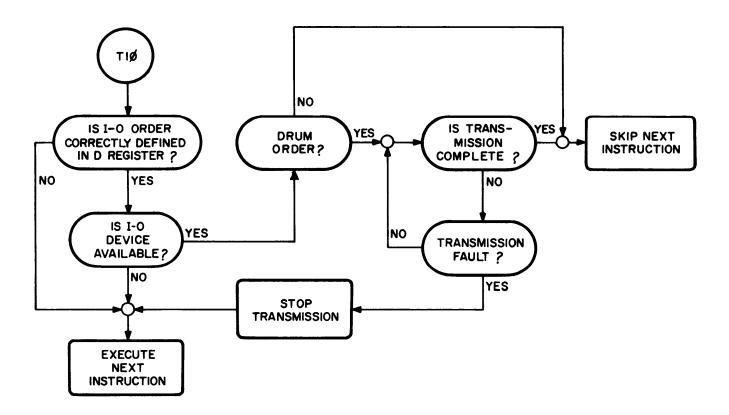

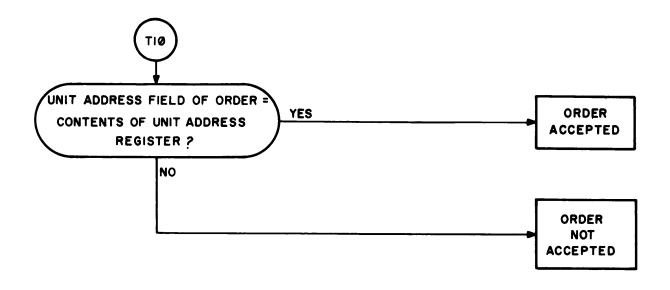

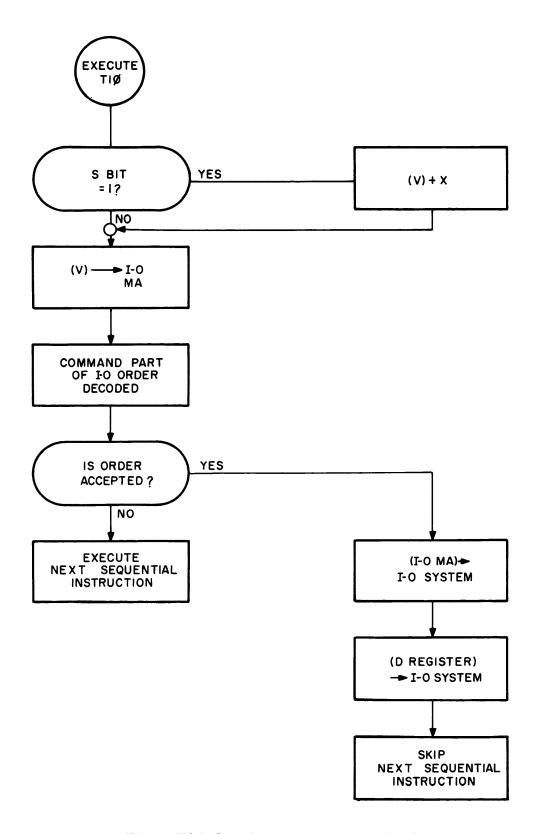

#### ACTION OF THE TIO INSTRUCTION (See figure INT-3.)

Before a TIO instruction can be executed successfully, the parameters of the I-O order must be placed in the D Register. When the TIO is executed, the I-O system designated by the command portion of the order is interrogated to determine whether or not that order can be accepted. If the order can be accepted, the next sequential instruction in the program is skipped. If the order cannot be accepted, the instruction following the TIO is

executed. Two other conditions, in addition to the status of the I-O system, affect the skipping action which follows the execution of the TIO instruction. These conditions are (1) that the command portion of the I-O order has been defined incorrectly and (2) that the I-O order is to the drum system. If the command has not been correctly defined, the next instruction in the program is executed. If the order is to the drum system, the next instruction is always skipped, either after the drum order has been completed successfully, or if it is interrupted because of an error.

Figure INT-3. Flowchart of the Operations Performed Following the Execution of the TIO Instruction.

#### SKIP INSTRUCTIONS

Included in the Philco 2000 repertoire of computer instructions are skip instructions, which permit the status of I-O systems and the progress of data transmissions through them to be checked.

In each I-O system there are one or more registers which monitor the action of that system. When the system is busy or if an error is detected during a transmission, a register reflects that condition. Essentially, skip instructions are used to check the contents of these "information" registers.

#### EXAMPLE OF I-O CODING

The following instructions illustrate how the I-O order and computer instructions could be written to initiate I-O operations:

| LOCATION | COMMAND | ADDRESS AND REMARKS |  |  |

|----------|---------|---------------------|--|--|

|          | TMD     | I-O ORDER           |  |  |

|          | TIØ     | 1000                |  |  |

|          | JMP     | DIAGNO              |  |  |

| PROCESS  | AM      | XXXX                |  |  |

|          | •       |                     |  |  |

|          | •       |                     |  |  |

|          | •       |                     |  |  |

| DIAGNO   | xxx     | xxxx                |  |  |

The TMD instruction transfers the I-O order from memory into the D Register; the TIO instruction is used to execute that order. If the order is acceptable, the jump instruction is skipped and the instruction at location PROCESS is executed. If the order is not acceptable, the jump to DIAGNO is executed. Starting at location DIAGNO, a series of skip instructions could be used to determine why the order was not accepted.

## GENERAL OPERATION OF THE INPUT-OUTPUT SECTION

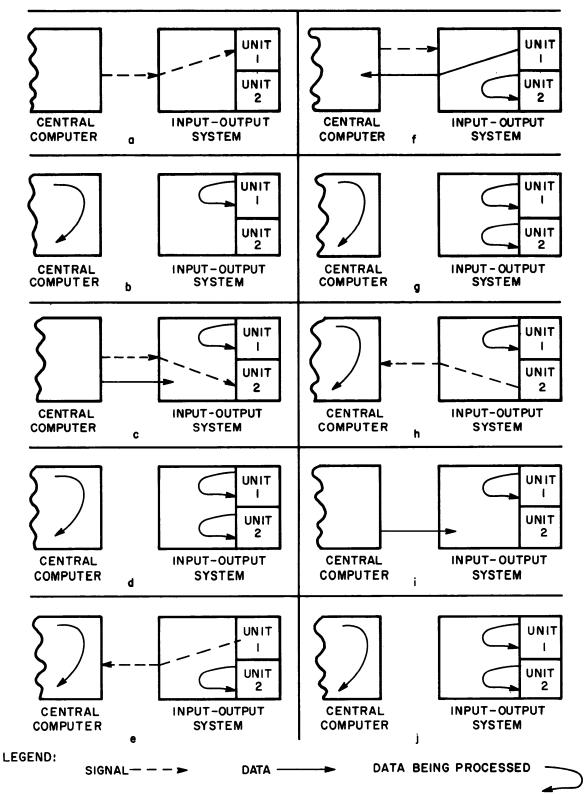

Since the I-O systems process data independently of the Central Computer operation, two different I-O systems may be used concurrently, one processing input data and the other processing output data. In actual operation, as many as nine systems may be processing data concurrently. Of the nine, some may be processing input data while the remaining systems are processing output data. Conditions may also exist where all the systems may be processing either input or output data.

Two systems are used in an illustration to describe the operation of the input-output systems with the Philco 2000 Computer. (See figure INT-4.) In the following description, Unit 1 is used for the input operation, Unit 2 is used for the output operation, and the I-O order is assumed as being accepted:

- a. During the main computer program, the parameters of the input order are transferred to the designated input-output system (Unit 1).

- b. The Central Computer continues with the main program and Unit 1 processes the input data. Processing includes assembling the information into full words, checking the accuracy of the transmission, and storing the assembled words in a register.

- c. Later in the main program, the parameters of an output operation which involves Unit 2 are transferred to that device, and the first word to be transmitted is transferred from the Central Computer to Unit 2.

- d. The Central Computer returns to the main program, and the Input-Output Section simultaneously processes both the first word of the output operation and the first word of the input operation. The processing of the output operation includes checking the transmission, altering the data format, and recording the information on the specified recording device.

- e. When Unit 1 has formed one full word, the word is stored in a register and a signal is sent to the Central Computer. This signal indicates that a word is ready to be written into memory.

- f. When the computer memory is available, the Central Computer sends a signal which indicates that the word from Unit 1 can now be written into memory.

- g. After the word from Unit 1 is written into memory, Unit 1 starts to process the next input word, and Unit 2 continues to process the first output word.

- h. When Unit 2 has completed processing one word, a signal is sent to the Central Computer which indicates that the next word can be accepted.

- i. When memory is available, the Central Computer transfers the second word of output information to Unit 2.

- j. The Central Computer then returns to the main program, and the two input-output systems continue to process data. The cycle (steps d through i) is repeated until all input-output data is processed.

Figure INT-4. General Operation of the Input-Output System

#### PHILCO 2000 CODE COMBINATIONS

A total of 64 discrete characters comprise the list of the Philco 2000 Code Combinations. These characters are shown in figure INT-5, and also on form TF17. In the figure, columns one and five contain the 64 "human language" numbers, letters, and symbols. Columns two and six contain the octal equivalent of the binary code for these characters. Columns three, four, seven, and eight list the associated Hollerith punch and Console Typewriter key.

# $\mathsf{PHILCO}_{\circledR}$ 2000 CODE COMBINATIONS

| Philco<br>Character | Octal<br>Code | Hollerith<br>Punch | Cons<br>Typew |              | Philco<br>Character | Octal<br>Code | Hollerith<br>Punch | Con:<br>Typev |        |

|---------------------|---------------|--------------------|---------------|--------------|---------------------|---------------|--------------------|---------------|--------|

|                     |               |                    | Upper         | Lower        |                     |               |                    | Upper         | Lower  |

| o                   | 00            | o ł                | 0             | ?            | l -                 | 40            | 11 1               | <u>-</u>      | ,      |

| ĭ                   | 01            | ĭ                  | 1             | <            | J                   | 41            | 11-1               | J             | زا     |

| 2                   | 02            | 2                  | 2             | 1: 1         | к                   | 42            | 11-2               | ĸ             | k      |

| 3                   | 03            | 3                  | 3             | e l          | L                   | 43            | 11-3               | L             | 1      |

| 4                   | 04            | 4                  | 4             | l 6          | М                   | 44            | 11-4               | M             | m      |

| 5                   | 05            | 5                  | 5             | @            | N                   | 45            | 11-5               | N             | n      |

| 6                   | 06            | 6                  | 6             | ΙĭΙ          | 0                   | 46            | 11-6               | 0             | 0      |

| 7                   | 07            | 7                  | 7             | >            | P                   | 47            | 11-7               | P             | Р      |

| 8                   | 10            | 8                  | 8             | •            | Q                   | 50            | 11-8               | Q             | l q    |

| 9                   | ii            | 9                  | 9             | #            | R                   | 51            | 11-9               | R             | r      |

| é e                 | 12            | 8-2 ①              | (See LC       | 5) ②         | ¬                   | 52            | 11-8-2 ①           | TAB           | TAB    |

| =                   | 13            | 8-3                | =             | l'''         | \$                  | 53            | 11-8-3             | (See LC       |        |

| :                   | 14            | 8-4                | (See LC       | 2) ②         | *                   | 54            | 11-8-4             | (See LC       |        |

| <u>.</u>            | 15            | 8-5 ①              | (See LC       |              | <                   | 55            | 11-8-5 ①           | (See LC       |        |

| -<br>&              | 16            | 8-6 ①              | &             |              | #                   | 56            | 11-8-6 <b>①</b>    | (See LC       |        |

| ī                   | 17            | 8-7                | (See LC       | '8) <b>②</b> | <u> </u>            | 57            | 11-8-7 O           | SHIFT         |        |

| +                   | 20            | 12                 | +             | *            | Δ ③                 | 60            | Blank 🐧            | SPAC          |        |

| A                   | 21            | 12-1               | Α             | a            | /                   | 61            | 0-1                | (See LC       | ;-)    |

| В                   | 22            | 12-2               | В             | ь            | S                   | 62            | 0-2                | S             | s      |

| c                   | 23            | 12-3               | С             | c            | T                   | 63            | 0-3                | Т             | t      |

| Ď                   | 24            | 12-4               | D             | d            | U                   | 64            | 0-4                | U             | u      |

| E                   | 25            | 12-5               | E             | e            | v                   | 65            | 0-5                | v             | V      |

| F                   | 26            | 12-6               | F             | f            | w                   | 66            | 0-6                | w             | w      |

| G                   | 27            | 12-7               | G             | g            | x                   | 67            | 0-7                | x             | ×      |

| н                   | 30            | 12-8               | н             | h            | Y                   | 70            | 0-8                | Y             | У      |

| Ī                   | 31            | 12-9               | I             | i            | Z                   | 71            | 0-9                | Z             | z      |

| n (3)               | 32            | 12-8-2 ①           | CAR. F        | RET.         |                     | 72            | 0-8-2 ①            | STOP          | CODE   |

|                     | 33            | 12-8-3             | 1             | 1:           | ,                   | 7.3           | 0-8-3              |               | u      |

| )                   | 34            | 12-8-4             | (See LC       | ·'%) ②       | [ ] (               | 74            | 0-8-4              | (See LC       |        |

| %                   | 35            | 12-8-5 ①           | %             | f)           | >                   | 75            | 0-8-5 ①            | (See LC       |        |

| ?                   | 36            | 12-8-6 ①           | (See LC       | (o) ②        | :                   | 76            | 0-8-6 ①            | (See LC       |        |

|                     | 37            | 12-8-7 ①           | SHIFT         |              | e (3)               | 77            | 0-8-7 ①            | DELET         | E CODE |

#### CONTROL CHARACTERS

| Character        | Console Typewriter                                                                      | High-Speed Printer | Punched-Card System                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------|

| л<br><br>е<br>!! | Carriage Return Tab Space Stop Code Delete Code Shift to upper case Shift to lower case | Space              | Null Cond. Stop ①, End of Block Blank Column ③ Abs. Stop ②, Punches 0-8-2 End of Card Punches 12-8-7 Punches 11-8-7 |

#### NOTES

- These codes can be punched on the keypunch by multiple punching.

The octal codes for these Philco Characters are illegitimate on the Console Typewriter. To type these characters from the computer, first transmit a shift to lower case (octal code 57), then transmit code for Philco character indicated in parenthesis.

- 3 These characters are printed by the Line Printer when in Write -

- All mode only.

These characters are recognized only when the second character in a block in off-line non-data select operation; otherwise second function is performed.

- (3) A switch on the Punched-Card Controller allows blank columns to be read as Philco Character 0 or  $\Delta$

PHILCO® 2000 TF (7-61)

Figure INT-5. Philco 2000 Code Combinations

#### MAGNETIC TAPE

#### INTRODUCTION

Magnetic tape provides the principal input-output medium for the Philco 2000 System, and the tape transports are the fastest commercially available tape recording devices.

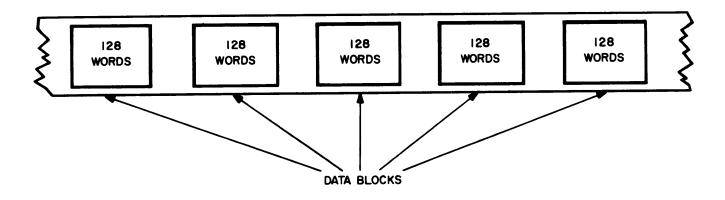

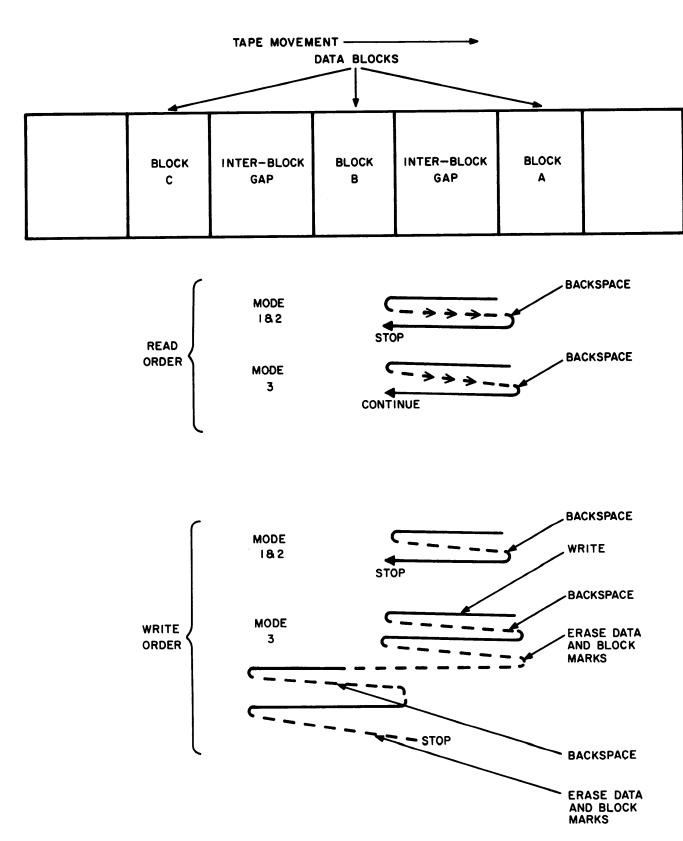

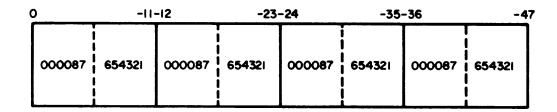

Data is recorded on magnetic tape in blocks of 128 words and may be processed either one block at a time, or in multiples thereof, to a maximum of 16 blocks per I-O order. This arrangement of data on tape is shown in figure MT-1.

Figure MT-1. Arrangement of Data on Magnetic Tape

#### DATA FORMAT (See figure MT-2)

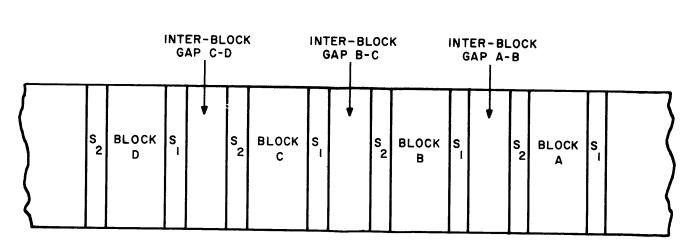

In the Philco 2000 alphanumeric code, a computer word (48 bits) is represented by eight units of six-bits each. These units are called "characters." The characters are recorded two at a time across the width of the tape, and each pair is called a "frame." In turn, the data frames are recorded in groups of 512, and each group is referred to as a "block."

In addition to the two characters in each frame, two checking bits, called 'parity' bits, are also recorded. One parity bit is recorded for each character. The value of the parity bit is chosen so that the total number of 'one' bits in the seven bits recorded for each character is always odd. Parity bits are used to check the accuracy of data transmission.

Figure MT-2. Magnetic Tape Format

Each frame is followed by two sprocket marks, one sprocket mark following each character in the frame. The sprocket marks are used to indicate tape skew and to provide a means of counting the total number of frames in a block.

The bits of each character in the frame are recorded in a particular arrangement. Starting at either side of the tape and moving toward the center, the pattern of bits for one character is as follows: 6, 4, parity, sprocket, 1, 2, 3, and 5. Six represents the most significant bit, and 1 represents the least significant bit of the six-bit Philco 2000 character.

The total number of frames in each block is 514. A block consists of 512 data frames, a channel parity frame, and a dummy frame. The channel parity frame is recorded following the last data frame. In the channel parity frame, the value of each bit is chosen so that an even number of "one" bits exists for each channel in the block. (Channels are the areas of tape on which data is recorded. One data channel covers the length of the tape, and 16 data channels cover its width.)

The dummy frame is recorded preceding the data frames. It contains all "zeros," with the exception of the parity bit recorded for each character; "ones" are recorded in these bit positions. The purpose of the dummy frame is to simplify control by providing a symmetrical format in the recording areas of the tape. With 514 frames, the first and last frames are not data frames, regardless of the direction of the tape movement.

Although there are 514 frames in each block, the total number of sprocket mark pairs recorded in each block is 515. A pair of sprocket marks is recorded preceding the dummy frame in each block to provide a means of checking tape skew when the tape is being read in the backward direction.

#### **BLOCK MARKS**

Each block is bracketed by block marks, which denote the areas on tape in which data can be recorded. The block marks which precede the block are called Beginning Block Marks (BBM's), and those which follow the block are called Ending Block Marks (EBM's).

There are 16 magnetic pulses comprising the BBM's and 17 magnetic pulses comprising the EBM's. The pulses of the BBM's are recorded preceding the sprocket mark in channel 13, and the pulses of the EBM's are recorded following the sprocket mark in channel 4. Block mark pulses are differentiated from sprocket marks in that they are recorded at twice the density of sprocket marks; that is, twice as many block mark pulses appear in the same area of tape.

Block mark pulses are also used to indicate when a tape has deteriorated beyond the point at which information can be recorded or read reliably. Usable areas of tape are identified by the presence of a minimum of eight continuous block mark pulses. If there are less than eight continuous pulses, a missing block mark condition is present. If there are more than eight but less than 12 continuous pulses, an improper block mark condition is present. Any number of continuous pulses of more than 12 is treated as a proper block mark. These block mark conditions are displayed on the control panel of the IOP.

#### INTER-BLOCK GAP

The inter-block gap is the area between two adjacent blocks, and it includes both block marks and an information free area. The information free area between block marks is used for starting and stopping the tape.

#### **ACCEPTANCE OF MAGNETIC TAPE ORDERS**

The acceptance of magnetic tape orders is controlled by the IOP, and the procedure which is followed is described in the chapter dealing with the IOP.

#### TAPE OPERATION

In the magnetic tape unit there are 16 read heads and 16 write heads. One read head and one write head are used in each of the 16 data channels of the tape. When tape is moved

in the forward direction, the tape passes under the write head first. This order is established to permit the read-back of information during a writing operation so that the accuracy of each recording may be checked.

#### WRITING ON TAPE

During a write operation, the IOP receives the data from the Central Computer memory and transfers a maximum of 16 pulses in parallel to the write heads. A pulse, when present, changes the direction of the magnetic field created by the write head and causes a "one" to be recorded.

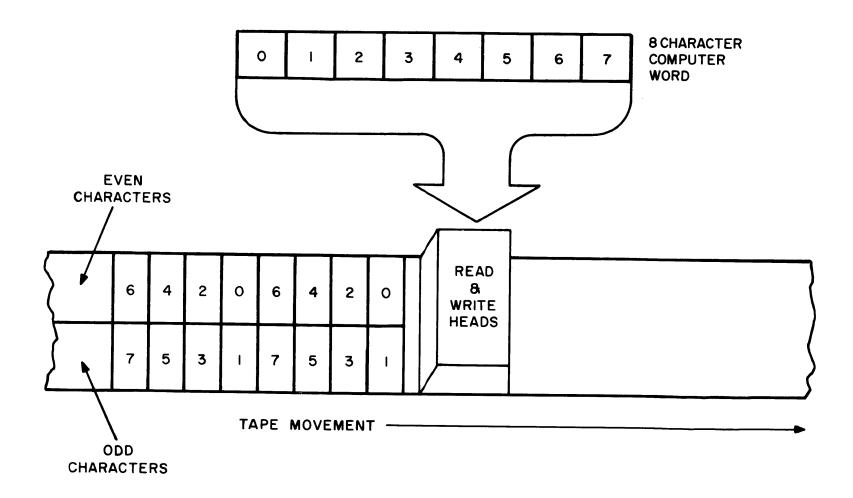

The characters of each computer word are recorded in a particular arrangement on the tape. As shown in figure MT-3, all even characters of the computer word are recorded on one side of the tape and all odd characters are recorded on the other.

#### READING TAPE

During a read operation, any change in the magnetic field on the surface of the tape passing under the read heads is interpreted as a "one." The output from the 16 read heads is transferred in parallel to the IOP. The IOP, in turn, transfers the information to the Central Computer memory.

#### WRITE ENABLE RING

The write enable ring is a safety feature which guards against the loss of data resulting from unintentional recording on or erasing of a particular tape. All tape reels are equipped with this removable ring, and without the ring, data cannot be recorded. With or without the ring, however, data can be read.

Figure MT-3. Arrangement of Characters on Tape

#### PHYSICAL CHARACTERISTICS OF TAPE

The magnetic tape has a Mylar\* base and is one inch wide and one mil thick. The beginning and end of every reel is coated with a non-plastic sensitized material (silver); when this sensitized area is detected, the tape stops automatically.

Tapes are furnished in lengths of 600, 2400, or 3600 feet per reel.

#### OPERATING CHARACTERISTICS

- a. Read/write speeds of 90,000 alphanumeric characters per second

- b. Recording density of 750 alphanumeric characters per inch

- c. Tape speed of 120 inches per second

- d. Tape rewind speed of 180 inches per second

- e. Tape capacity of 18,000 blocks per 3600 ft. reel

<sup>\*</sup>DuPont Corporation

#### INPUT-OUTPUT PROCESSOR

#### INTRODUCTION

The Input-Output Processor (IOP) is a data processing device which controls the transfer of data between the Central Computer and Magnetic Tape Units and/or Universal Buffer-Controllers (UBC's).

During an input operation, the IOP receives data two characters at a time from the input device and assembles these characters into computer words. After each word (eight characters) has been assembled, the IOP transfers that word into the computer memory.

During an output operation, the IOP breaks down the eight-character word received from the computer memory into four groups of two characters each. As the word is processed, the IOP transfers two characters at a time to the output device.

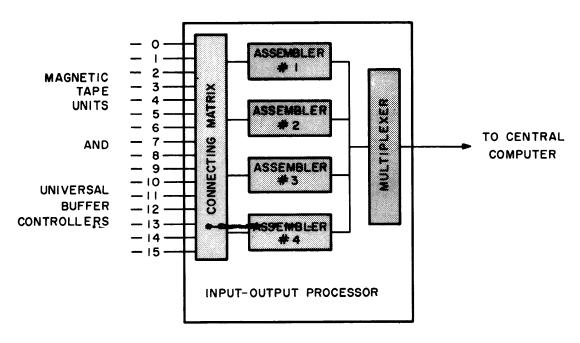

#### MAJOR SECTIONS OF THE IOP (See figure IOP-1)

Functionally, the IOP can be divided into the following three major sections:

- a. Connecting Matrix—establishes the electrical connections between the IOP and the I-O device.

- b. Assemblers—process the data being transferred. Up to four assemblers may be contained in each IOP, and all may be operating simultaneously

- c. Multiplexer—controls the operation of the assemblers.

Figure IOP-1. Major Sections of IOP

To further explain the function and relationship of these sections, their basic operation is outlined in the following paragraphs, first during an input order and then during an output order.

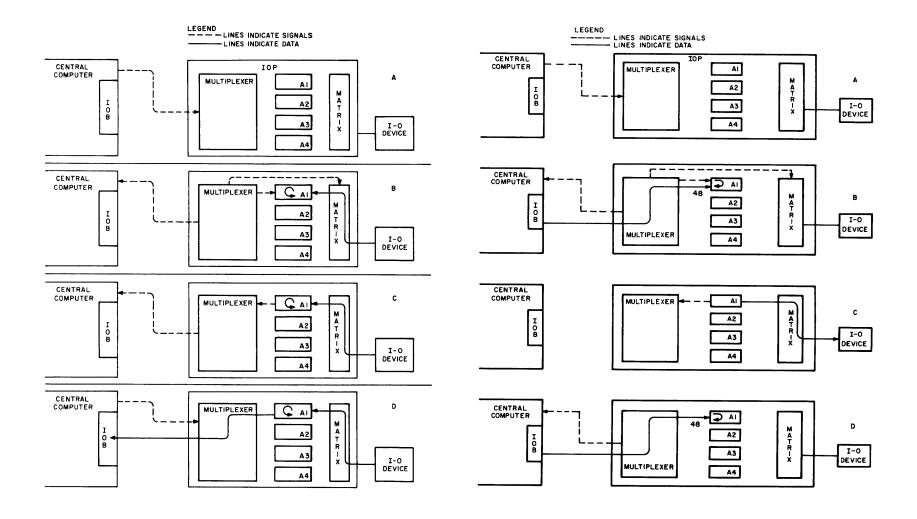

#### I-O DEVICE TO MEMORY

The function of the different sections of the IOP during an input order is described below and illustrated in figure IOP-2.

- a. The TIO instruction is decoded in the Central Computer and the I-O order is transferred to the multiplexer section of the IOP, where the order acceptance procedure is performed.

- b. If the order can be accepted, the following actions occur:

- 1. An assembler is assigned; i.e., a particular assembler is selected to process all data involved in the transmission.

- 2. The connecting matrix is "marked" (electrical connection is established between the assigned assembler and the I-O device).

- 3. A continue signal is transmitted to the Central Computer by the multiplexer, and transmission begins.

- c. When a full word (eight characters) is assembled, the assembler signals the multiplexer, and the multiplexer makes a request to the Central Computer for memory access. Meanwhile, input transmissions continue from the I-O device.

- d. The Central Computer signals the multiplexer when memory access is available, and the multiplexer allows the word to be transferred from the assembler through the IOB into memory.

#### MEMORY TO I-O DEVICE

The function of the different sections of the IOP during an output order is described below and illustrated in figure IOP-3.

- a. Similar to input order.

- b. Similar to input order.

- c. After a full word, 48 bits, has been broken down into eight six-bit characters and transferred to the I-O device by the assembler, a memory request is sent to the multiplexer by the assembler.

- d. The multiplexer sends a memory request to the Central Computer. When the request is granted, a new word is transferred from memory through the IOB into the assembler, and the assembler processing operations are repeated.

IOP-3

Figure IOP-2. Operation of the IOP During Input Order

Figure IOP-3. Operation of the IOP During Output Order

#### DATA FLOW

In the IOP, all of the data involved in a transmission must be processed, that is, manipulated and checked. For example, in transmissions from an I-O device to memory, the input data is always received two characters at a time, processed, and then presented to the computer eight characters at a time. The reverse is true during transmissions from memory to the I-O device.

This processing is performed in the assembler, and each assembler contains various data registers which are used in the processing operation. The action of these registers, which is the same for both input and output operations, is explained in the following descriptions.

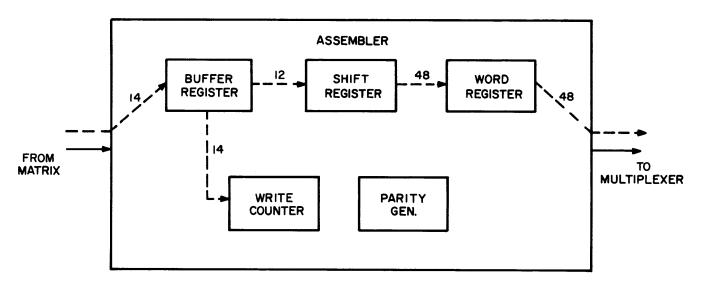

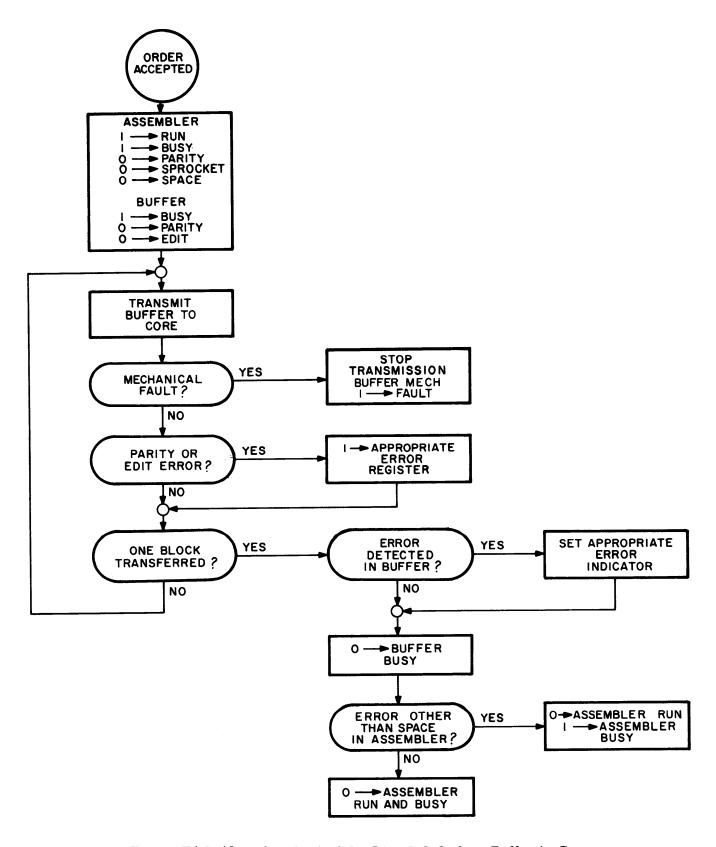

# INPUT OPERATIONS (See figure IOP-4.)

In transmissions from an I-O device to memory, two characters at a time (14 bits) are transferred from the input device through the connecting matrix to a Buffer Register in the assigned assembler. In the Buffer Register each character is checked for odd parity, and the 12 data bits are transferred to the least significant bit positions of a Shift Register. The entire 14 bits are also transferred from the Buffer Register to a Write Counter, where the bits in each transfer are counted. After the last word of the block has been transferred, even channel parity is checked.

Figure IOP-4. Data Flow in Assembler During Input Order

The 12 bits placed in the Shift Register are shifted 12 places to the left to make room for the next group of 12 bits. Data is transferred from the Buffer Register until four groups of 12 bits each have been placed in the Shift Register.

When a full word is assembled in the Shift Register, its contents are transferred in parallel to a Word Register, clearing the Shift Register for the next group of 12 bits. While the word is in the Word Register, the Shift Register continues to process data and the multiplexer requests memory access. When memory access is granted, the word is transferred from the Word Register into memory.

The processing operation continues in this manner until the amount of information specified by the NO. OF BLOCKS field of the I-O order has been transferred.

When reading in the backward direction, data flow is the same as in the forward direction except that the 12 bits are transferred from the Buffer Register to the 12 most significant bits of the Shift Register. The Shift Register is then shifted to the right to assemble a word.

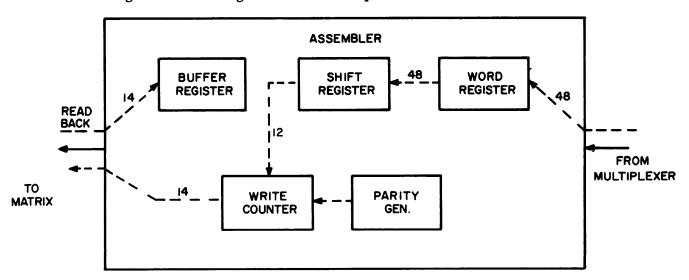

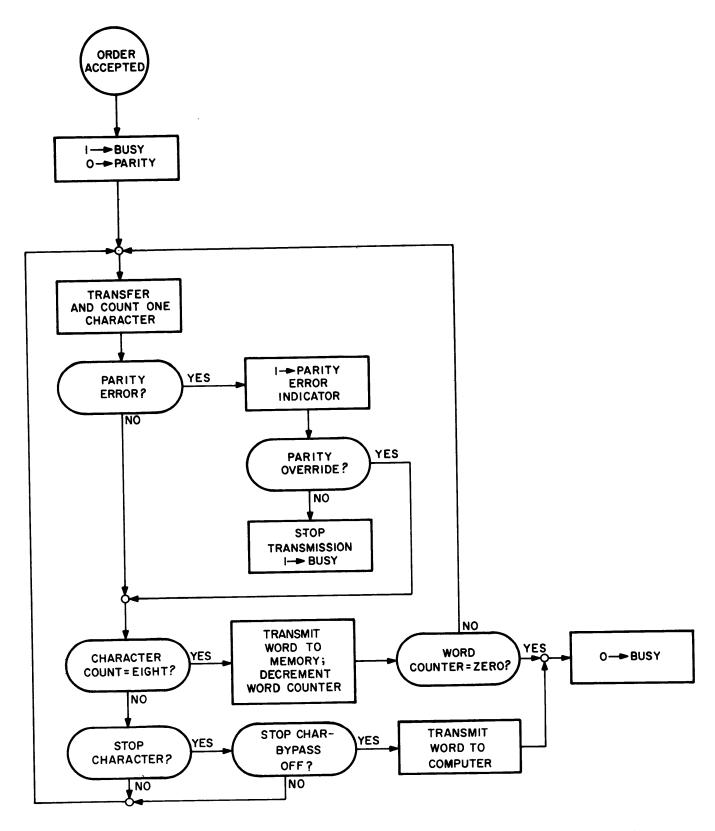

# OUTPUT OPERATIONS (See figure IOP-5.)

In transmissions from memory to an I-O device, a full 48-bit computer word is transferred from memory through a Word Register into a Shift Register. From the Shift Register, the 12 most significant bits are transferred to the Write Counter. The Shift Register then shifts 12 places to the left so that the next 12 bits may be in position to be transferred to the Write Counter. While data is in the Write Counter, character parity bits are added by a Parity Generator. After the parity bits have been added, the Write Counter transfers the 14 bits through the connecting matrix to the output device.

Figure IOP-5. Data Flow in Assembler During Output Order

After the data has been recorded by the output device, the recorded information is read back into the Buffer Register, where character parity is checked. The Buffer Register is then cleared, and no data is transferred to the Shift Register or to the Write Counter, since this would interfere with the writing process.

Following each transmission from the Write Counter, sprocket marks generated by the IOP are also transmitted. After a full block has been transferred, as indicated by the generation of 515 pairs of sprocket marks, the ending block mark pulses of that block are added by the IOP.

The processing operation continues in this manner until the amount of information specified by the NO. OF BLOCKS field of the I-O order has been transferred.

#### ACTION OF THE MULTIPLEXER

The multiplexer section of the IOP controls the selection of the particular assembler which is assigned to complete an I-O order, it also establishes access to the computer memory whenever memory is required by an assembler. When more than one assembler is operating, the multiplexer controls their sequence of transmission.

To provide the accessing function, the multiplexer monitors each assembler in sequence for a specific signal which indicates that memory is required. This monitoring action is performed continuously; however, in a four assembler system it would only require slightly more than 1 microsecond for the multiplexer to monitor all assemblers. When a signal is received from an assembler, the following operations occur, and monitoring stops until memory is accessed for that assembler.

- a. The multiplexer signals the Central Computer that access is required.

- b. At a time determined by the Central Computer, the multiplexer is signaled that memory is available. It is possible that more than one assembler will request memory before it can be made available; however, the request signal is maintained by the assembler, and the multiplexer executes requests in a prearranged sequence.

- c. When the memory request is granted by the computer, the transfer is initiated.

The Central Computer signals the multiplexer when the IOB Register contains the word being transferred.

- d. The multiplexer transfers the contents of the IOB Register into the assembler Word Register during output operations, or clears the assembler Word Register during input operations.

- e. In the computer, the contents of the IOB are placed into memory. During input operations, the word received from the assembler Word Register is now in memory. During output operations, the word originally in memory is restored.

# IOP ACCEPTANCE OF INPUT-OUTPUT ORDERS

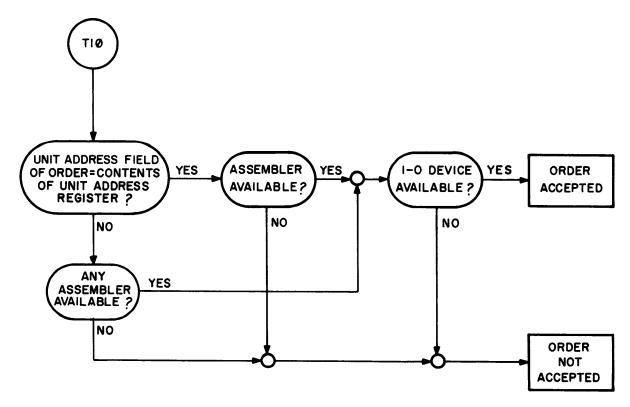

The IOP controls the acceptance procedure of all on-line orders issued to magnetic tape units and affects the acceptability of orders issued to intermediate-speed I-O devices connected on line to the UBC. Thus, not only must the I-O device be available before an order can be accepted, but certain conditions must also prevail in the IOP because all online data transmissions involving tape units and the UBC are through the IOP. The following discussion is concerned principally with the status of the IOP during the issuance of online orders; the conditions affecting the availability of I-O systems are described in the particular chapters dealing with these systems.

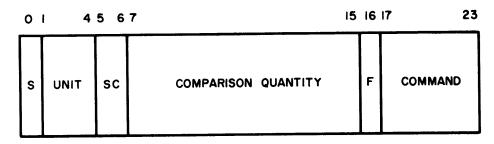

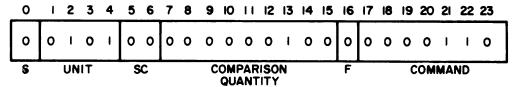

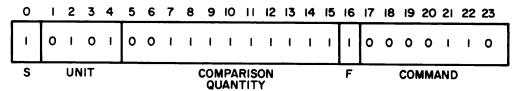

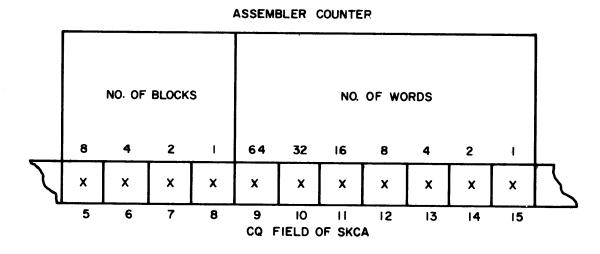

In the IOP, the acceptance of I-O orders is determined by the status of assemblers and by the contents of a certain control register, called the Unit Address Register, contained in each assembler. During data transmissions, this register contains the address of the I-O device involved in the transmission. When the transmission is completed or interrupted, the contents of the Unit Address Register are not disturbed. Instead, the address is retained until the assembler containing that register is used for another order involving a different I-O device. This fact will have significance in the discussion dealing with magnetic tape orders.

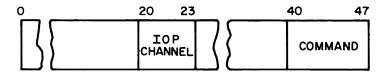

#### MAGNETIC TAPE AND UBC INPUT-OUTPUT ORDERS

There are 26 different magnetic tape orders and three different UBC orders. The 26 magnetic tape orders may be divided into nine different types, and the nine types, for convenience, may be subdivided into four classes; Class A, Class B, Class C, and Class D. The Class A orders include Read, Write, and Edit orders, which perform the original processing operations. The Class B orders include Stop and Release orders, which terminate processing orders and release assemblers. (The term "release" means to remove the electrical connection between an assembler and an I-O device; "terminate" means to interrupt a processing operation before it has been completed. When an order is terminated due to an error, the assembler is not released.) The Class C orders include Erase, Resume, and -1 Read orders, which provide for the resumption of processing orders which have been interrupted because of an error. The Class D orders include Rewind and Rewind with Lockout orders, which provide for rewinding tape.

There are two terms which are used to define the status of an assembler during the acceptance of I-O orders. These terms are Busy and Running, and are defined as follows:

- a. Busy-indicates that the assembler is connected to an I-O device.

- b. Running-indicates that the assembler is Busy and transferring data.

At the time I-O orders of each classification are executed, the status of assemblers must be as follows:

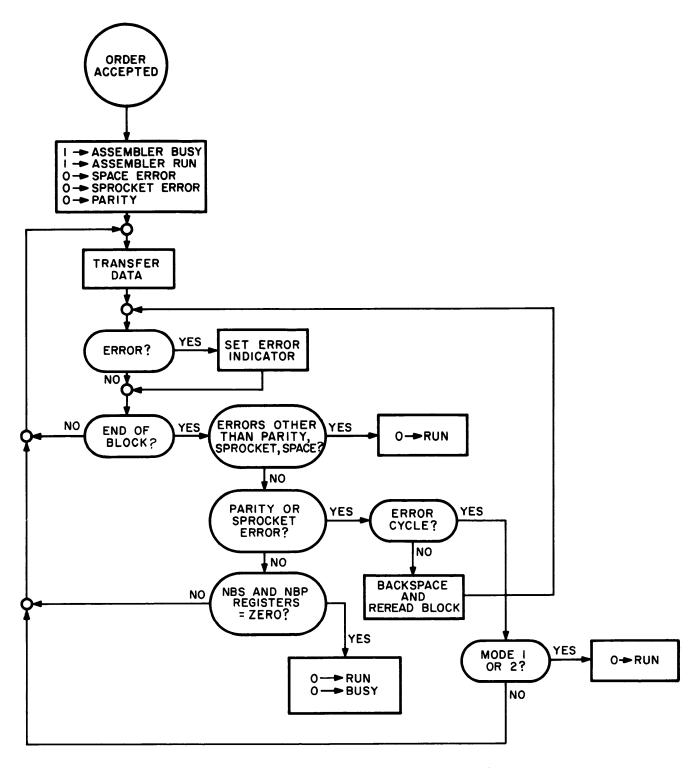

- a. Class A and UBC orders—at least one assembler must be nonbusy.