# P/25 ENGINEERING MANUAL

PLEXUS COMPUTERS INC

2230 Martin Ave Santa Clara, CA 95050 408/988-1755

Plexus Publication #5018-1A June 18, 1982

# Copyright 1982 Plexus Computers Inc, Santa Clara, CA

# All rights reserved.

No part of this manual may be reproduced in any form without written permission from the publisher.

Printed in the United States of America

#### REVISION RECORD \_\_\_\_\_

| REVISION | DATE   | DESCRIPTION                                                                                                        |

|----------|--------|--------------------------------------------------------------------------------------------------------------------|

| 1A       | 7/1/82 | Based on information from engineering<br>during system development. Includes<br>relevant information up to EN 156. |

The information in this manual is subject to change. Plexus Computers Inc assumes no responsibility for the accuracy of the information in this manual.

### TABLE OF CONTENTS

#### **PREFACE**

#### OVERVIEW

- 1. INTRODUCTION

- 2. CENTRAL PROCESSOR UNIT (CPU)

- 2.1. Processor

- 2.2. Software

- 2.3. Diagnostic Port

- 3. MEMORY MANAGEMENT UNIT (MMU)

- 3.1. Page Map RAM

- 3.2. Memory Protection

3.3. Error Detection and Correction

- 3.4. Refresh

- 4. MEMORY ARRAY

4.1. Dynamic RAM Array

- 4.2. EPROM

- 4.3. Static RAM

- 5. INPUT/OUTPUT CONTROLLER

- 5.1. Serial Ports

- 5.2. Parallel Port

- 5.3. Local Memory

- 5.4. Pseudo DMA

- 6. INTELLIGENT MASS STORAGE CONTROLLER (IMSC)

- 7. MULTIBUS BACKPLANE AND INTERFACE

- 8. POWER SUPPLY

- 9. RESET, POWER FAIL AND RESTART

- 10. STANDARD PERIPHERAL CONFIGURATION

- 10.1. Disk Drive

- 10.2. Tape Drive

- 11. SPECIFICATIONS

- 11.1. Processor Specifications

- 12. BIBLIOGRAPHY

Figure

#### PROCESSOR

- 1. Z8001A MICROPROCESSOR

1.1. Programming Information

- 1.2. Hardware Interface

- 1.3. I/O Access

1.4. Trace Mode Capability

- 1.5. Controls and Indicators

- 1.6. Circuit and Timing Analysis

- 2. MEMORY MANAGEMENT UNIT (MMU)

- 2.1. Memory Mapping

- 2.2. Memory Protection

- 2.3. MMU Circuit Analysis

- 2.4. Address Latches and Bidirectional Data Buffers2.5. Wait-State Generator

- 2.6. Status Latches and Decoder

- 2.7. Memory Access Arbitration

- 3. LOCAL PERIPHERALS

- 3.1. Introduction

- 3.2. Peripheral Interface Controller

- 3.3. Parallel Input/Output (PIO) Controller 3.4. Realtime Clock

- 3.5. Programmable Interrupt Controller (PIC)

- 3.6. Diagnostic Port

- 4. MULTIBUS INTERFACE

- 4.1. Introduction

- 4.2. Multibus Memory Access

- 4.3. Processor Board Multibus Access

- 5. LOCAL BUS ARBITER AND TIMING SEQUENCER

- 5.1. Local Bus Arbiter

- 5.2. Timing Sequencer

- 6. ERROR HANDLER6.1. Circuit Analysis

- 6.2. Error Status Registers

Figures

#### I/O CONTROLLER

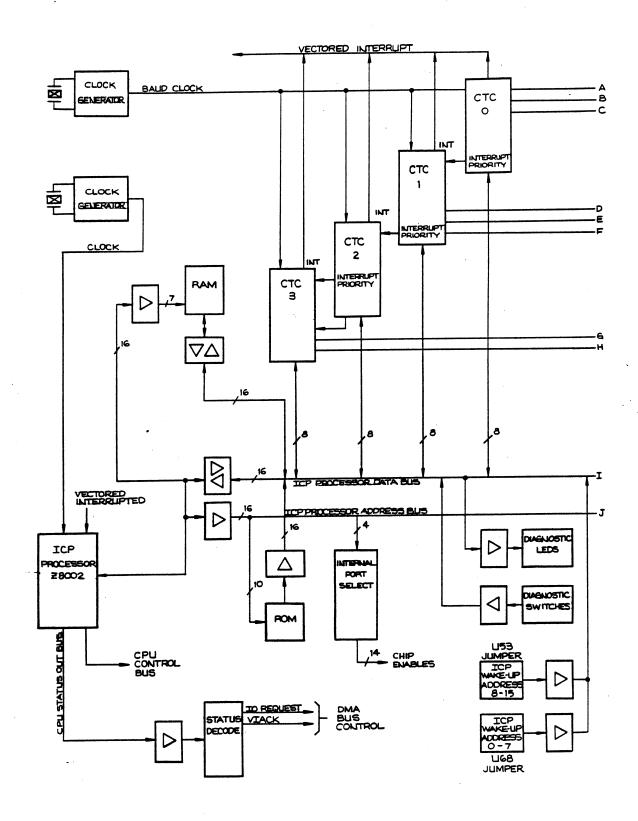

- 1. ICP OVERVIEW

- 2. PROCESSOR

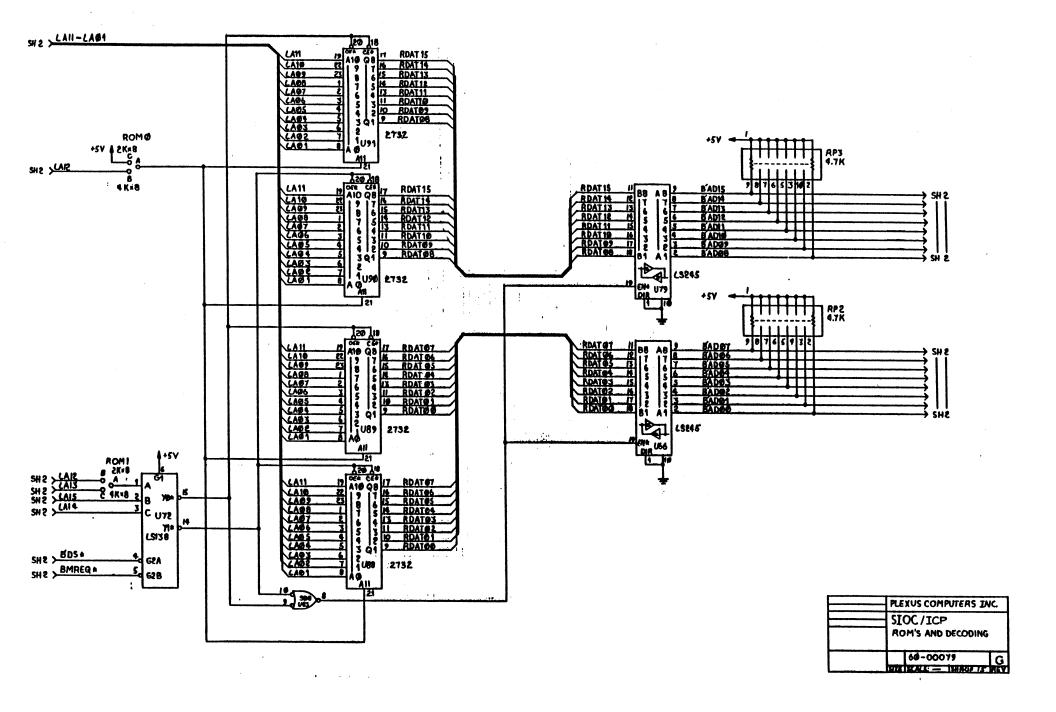

- 3. LOCAL MEMORY

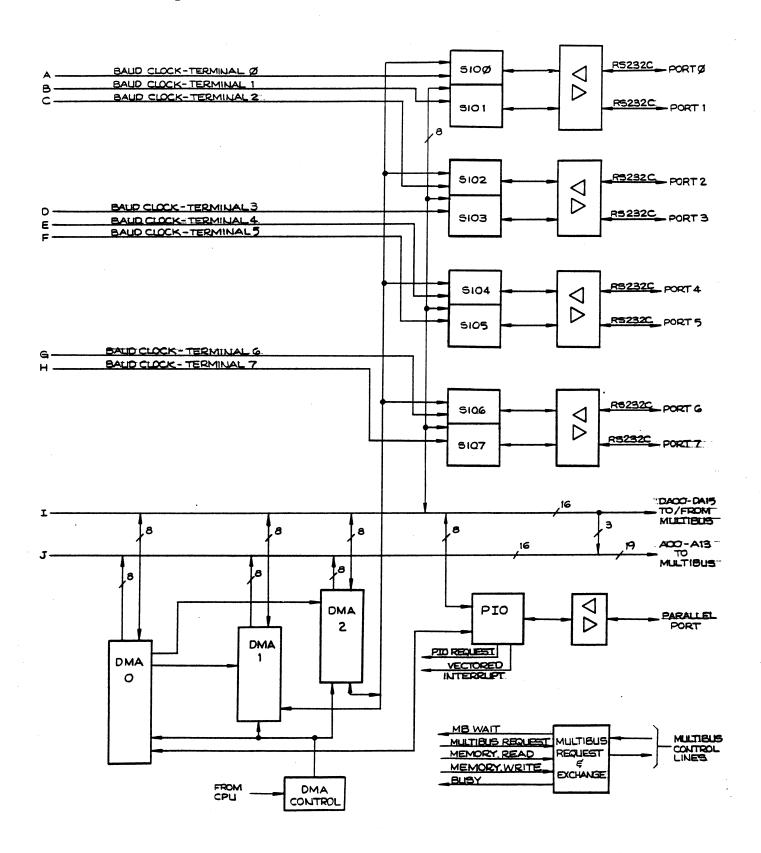

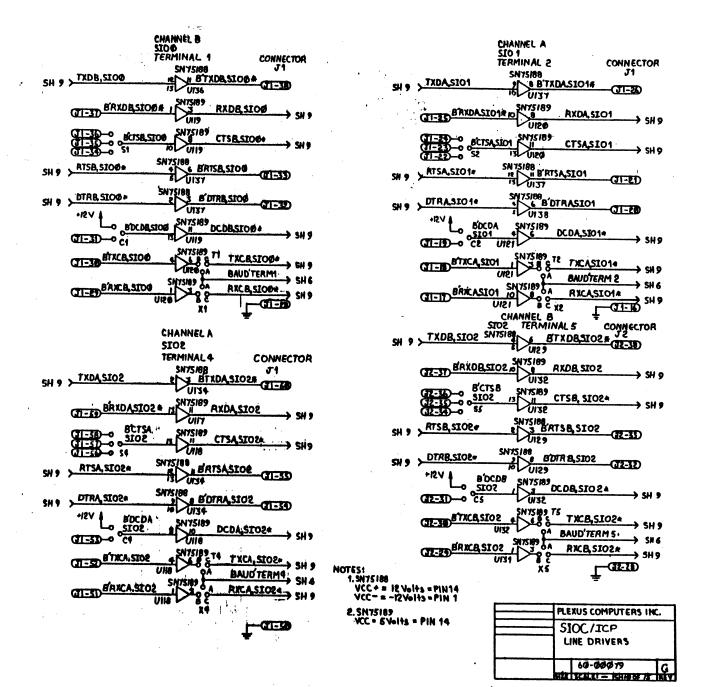

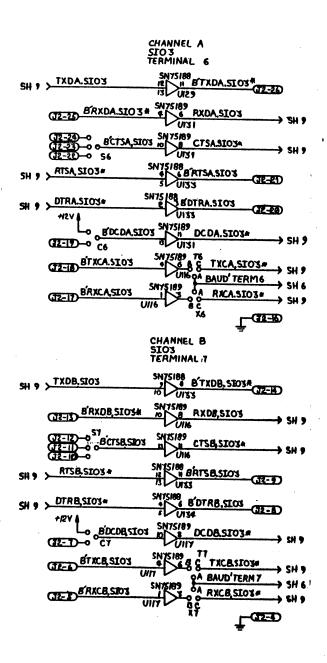

- 4. SERIAL PORTS

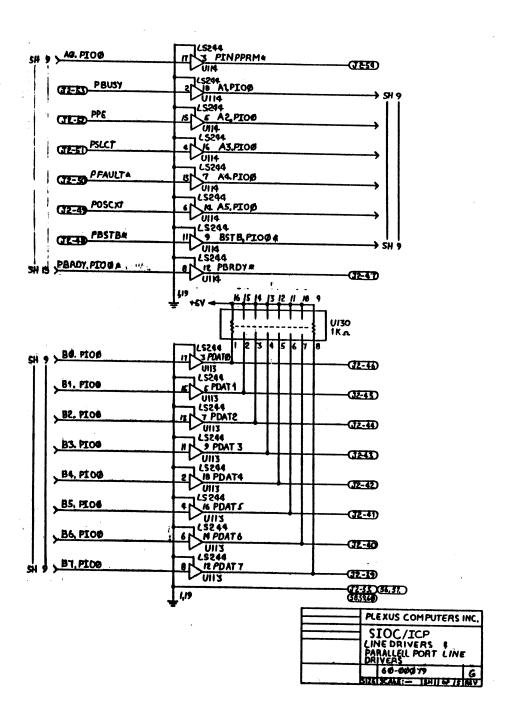

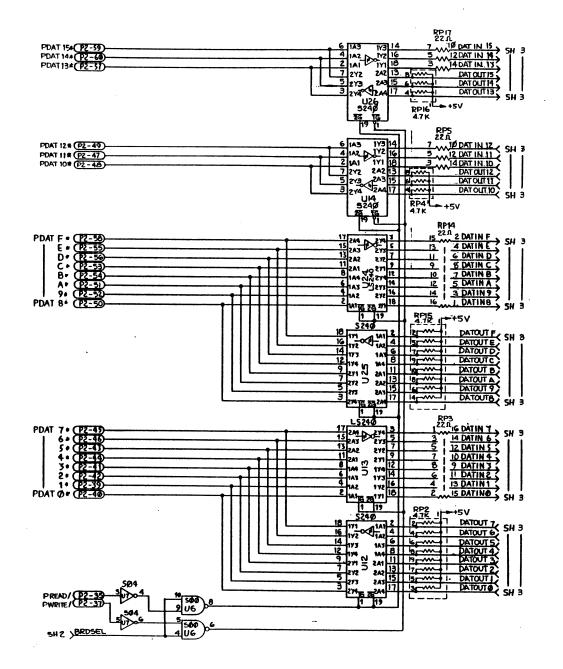

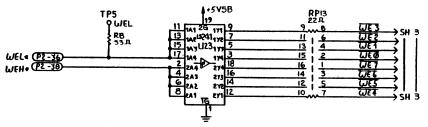

- 5. PARALLEL PORT

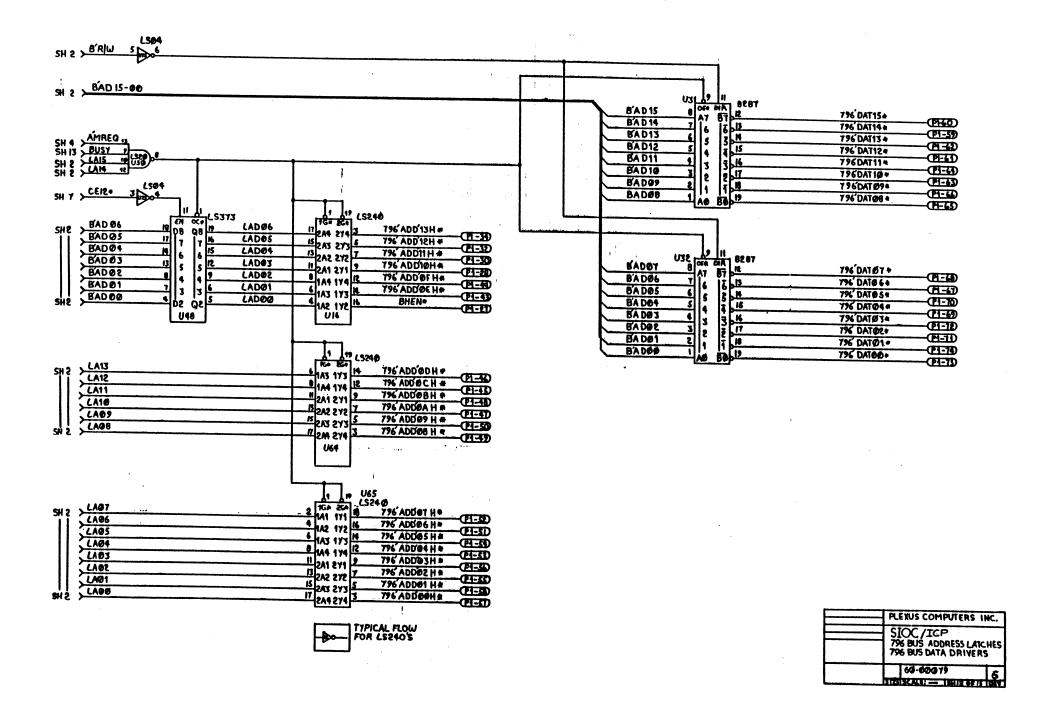

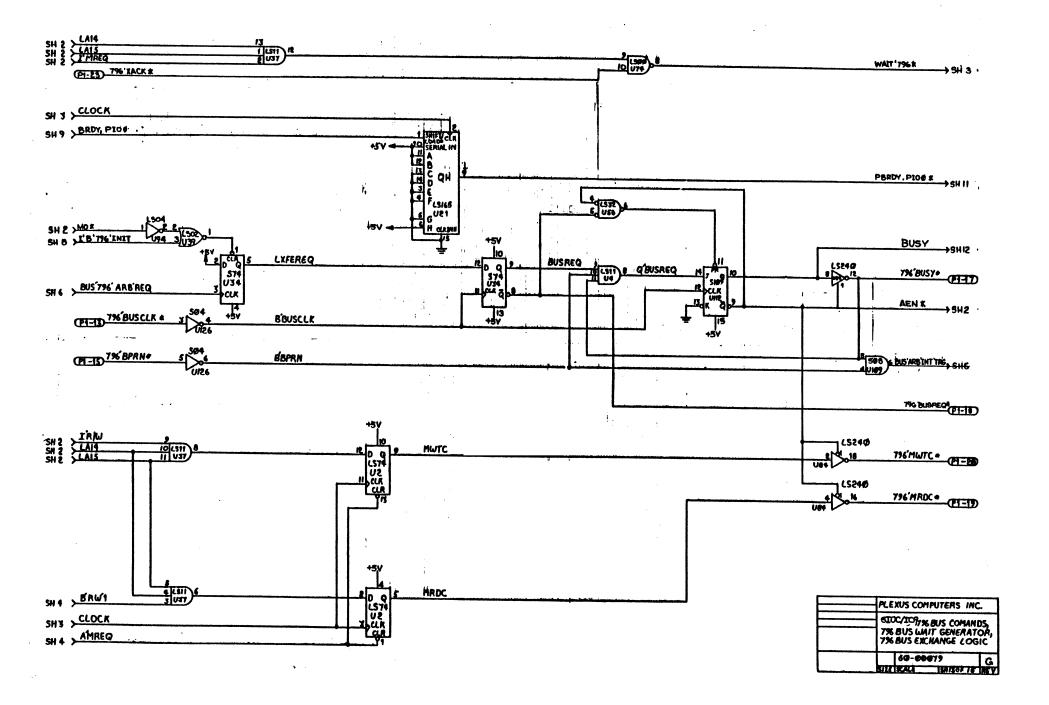

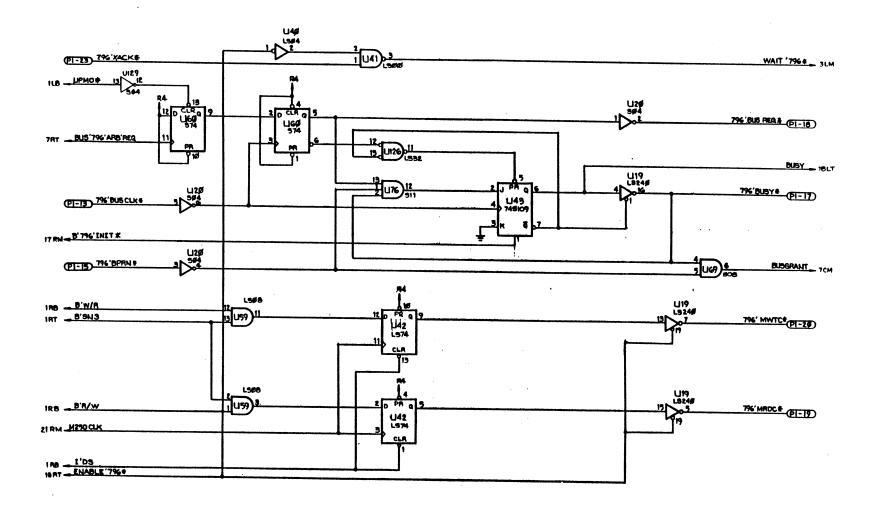

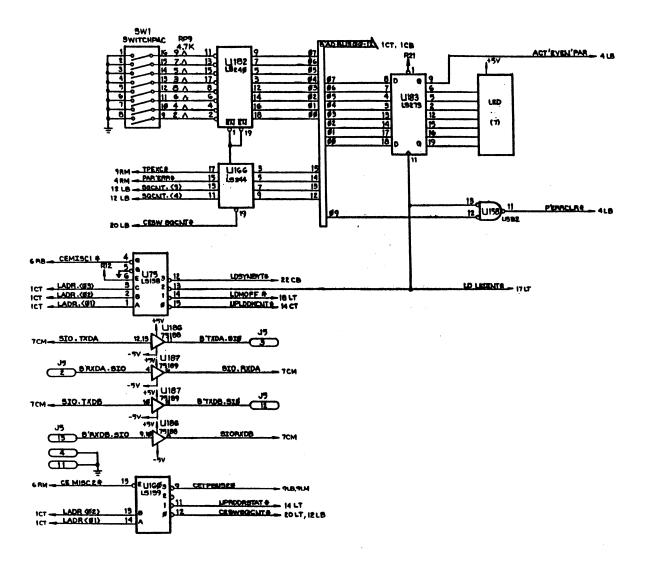

- 6. MULTIBUS ARBITER AND INTERFACE

- 7. INTERRUPTS

- 7.1. Nonmaskable Interrupts

- 7.2. Vectored Interrupts

7.3. Nonvectored Interrupts

- 7.4. Programming Information

- 8. STATUS AND CONTROL PORTS

- 9. I/O SPACE

- 10. CHANNEL ATTENTION PORT

- 10.1 Reset

- 11. PSEUDO DMA

- 12. PINS, CONNECTORS AND PINOUTS

- 12.1. Connector Pinouts

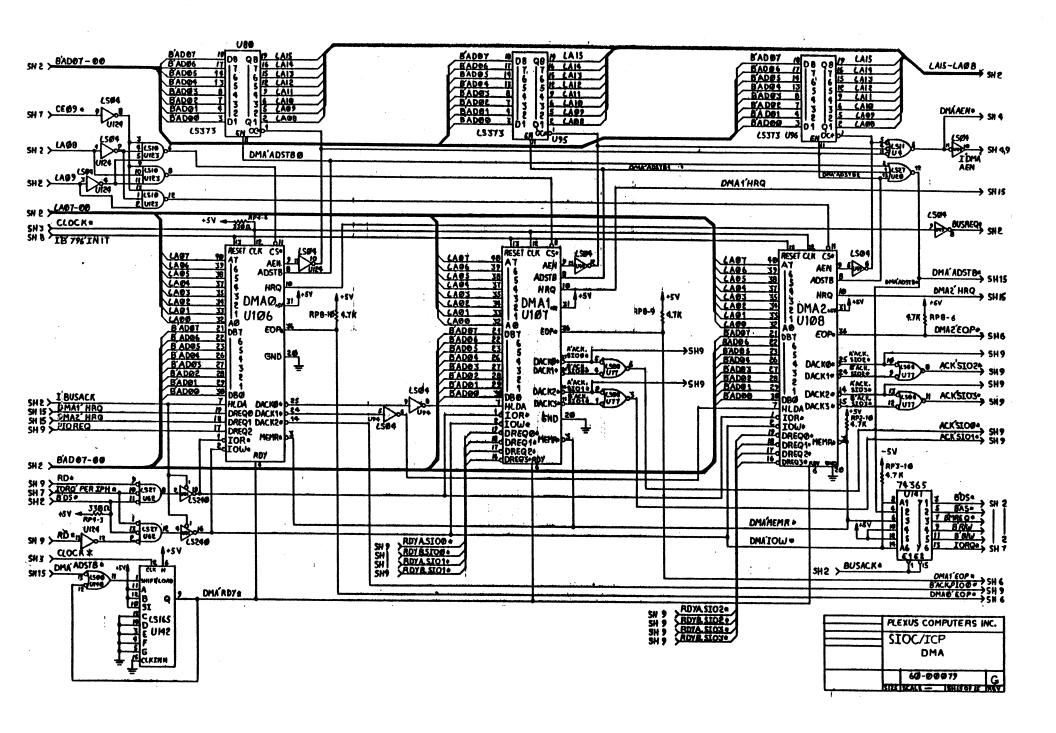

- 13. DMA OPERATION

- 14. ICP SOFTWARE CONCEPTS

- 14.1. Timing Considerations

- 14.2. Bus Arbitration

Figures

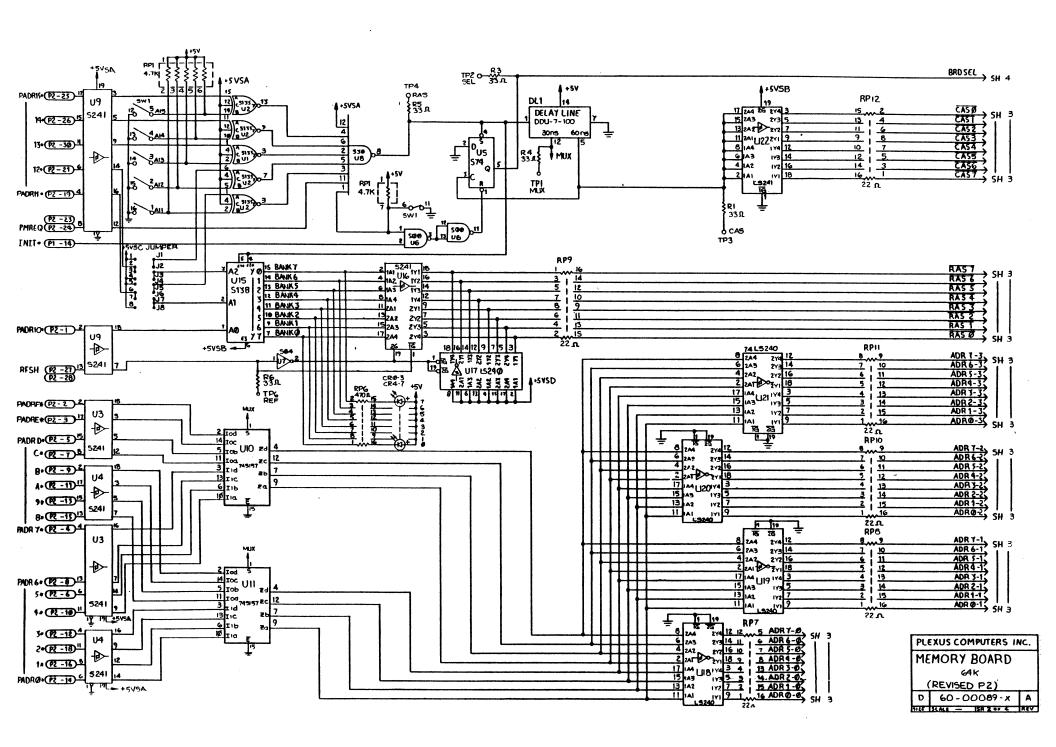

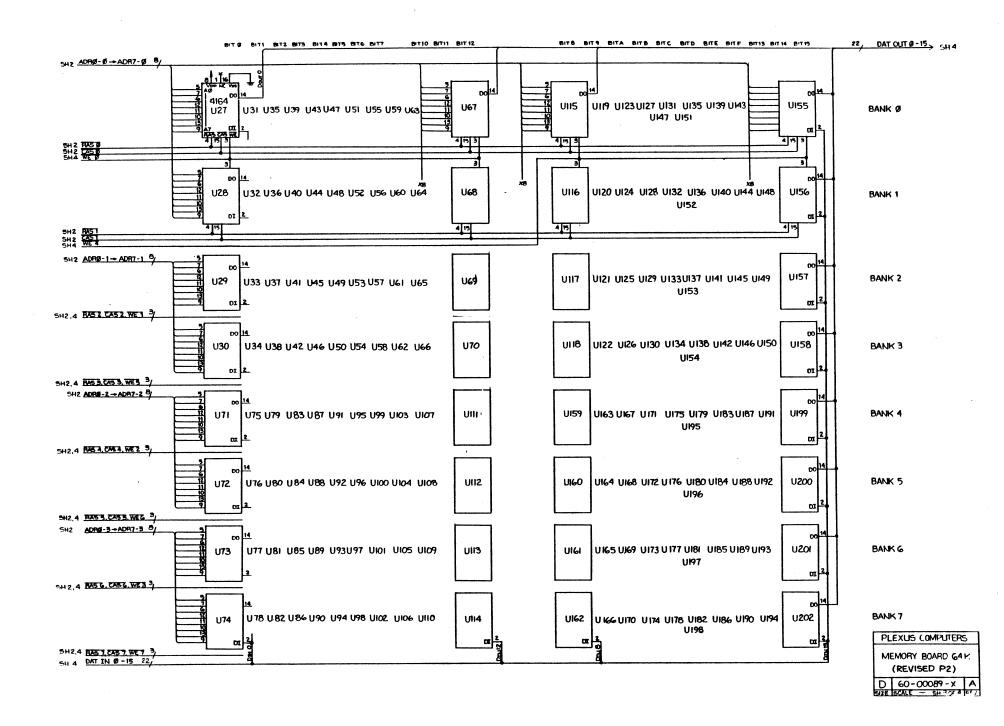

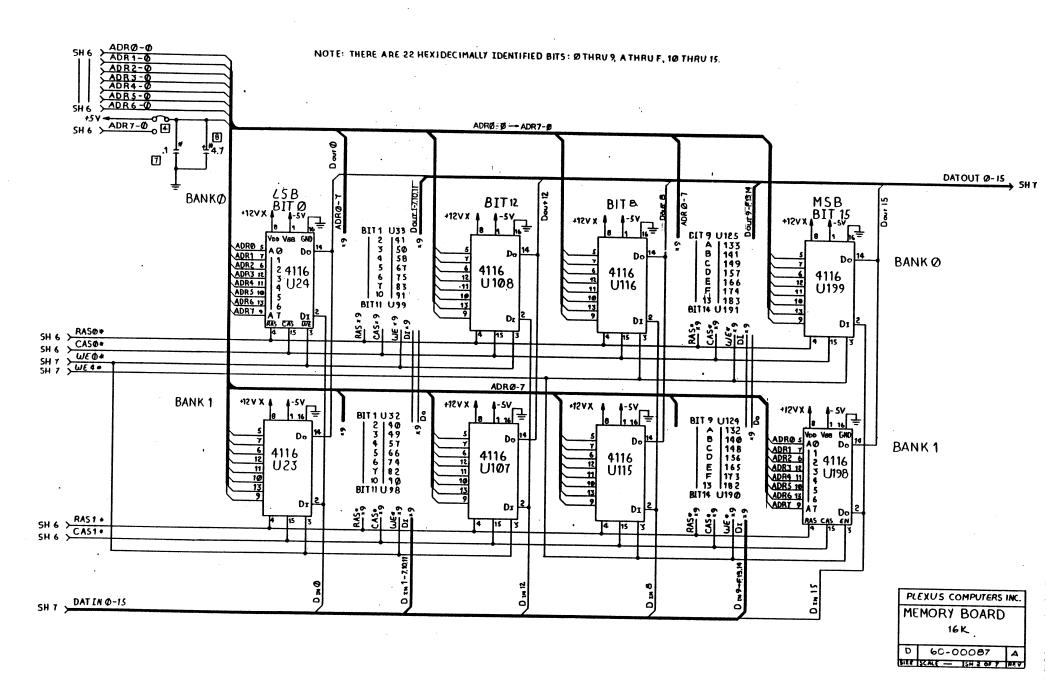

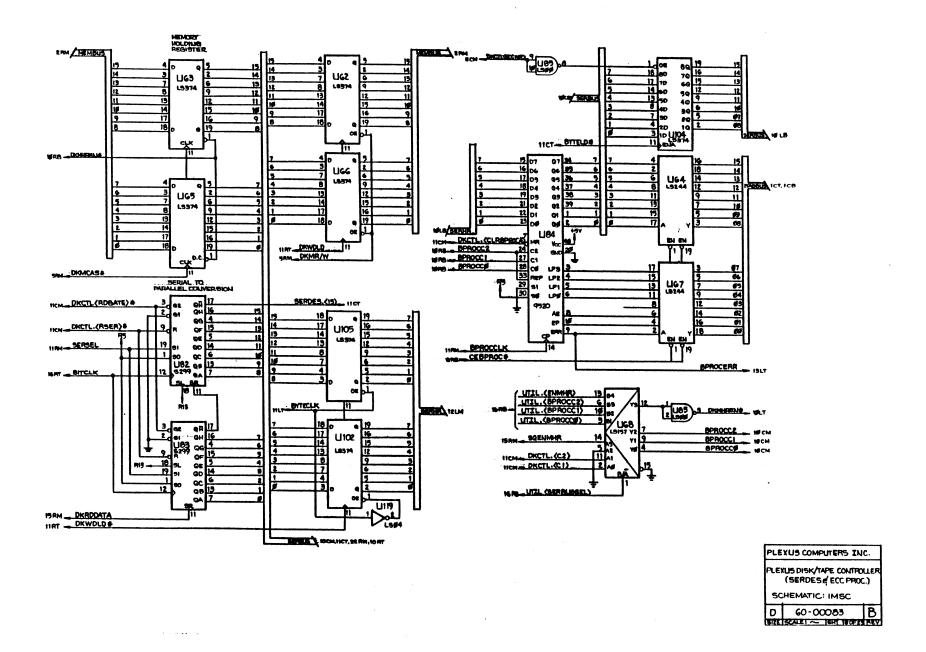

### MEMORY

- 1. INTRODUCTION

- 2. PRINCIPLES OF OPERATION

- 2.1. Physical and Logical Memory Space

- 2.2. Dual-Port Memory

2.3. Error Detection and Correction

2.4. Circuit and Timing Analysis

Figure

Schematics

#### **BACKPLANE**

- 1. MULTIBUS BACKPLANE AND INTERFACE 1.1. Multibus Interface

IEEE Proposed Microcomputer System Bus Standard (P796 Bus)

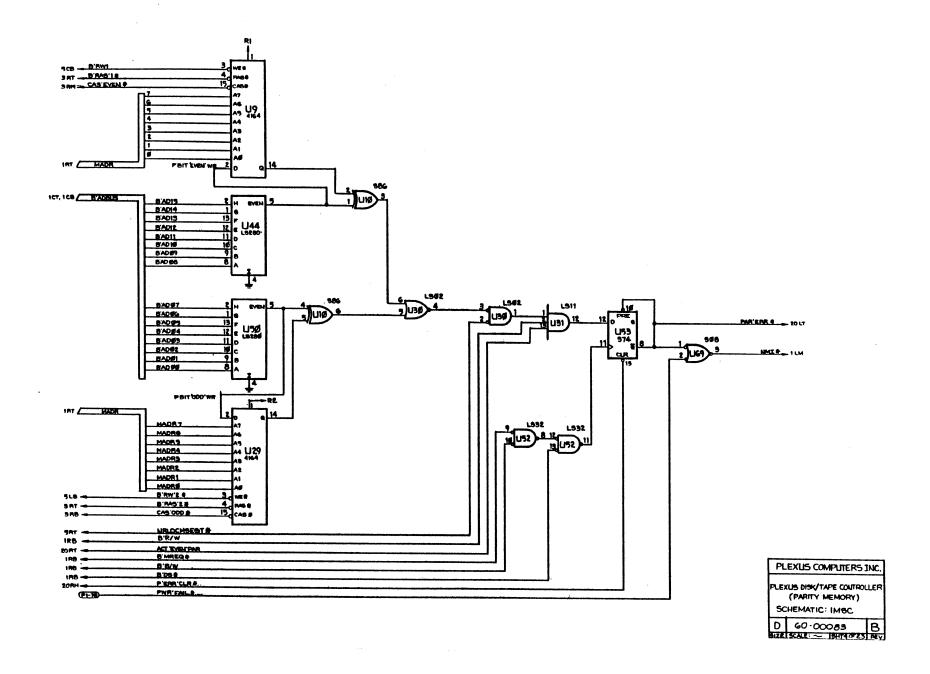

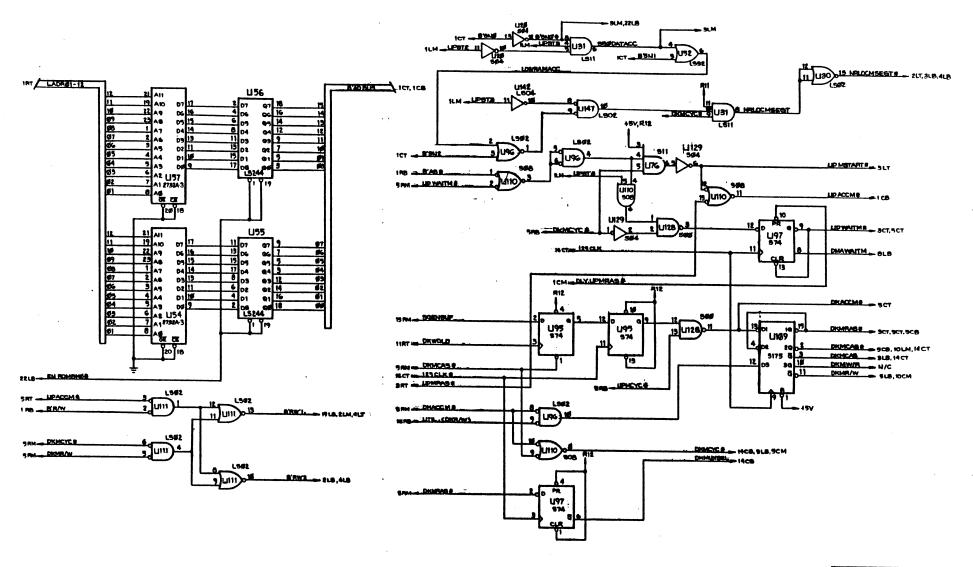

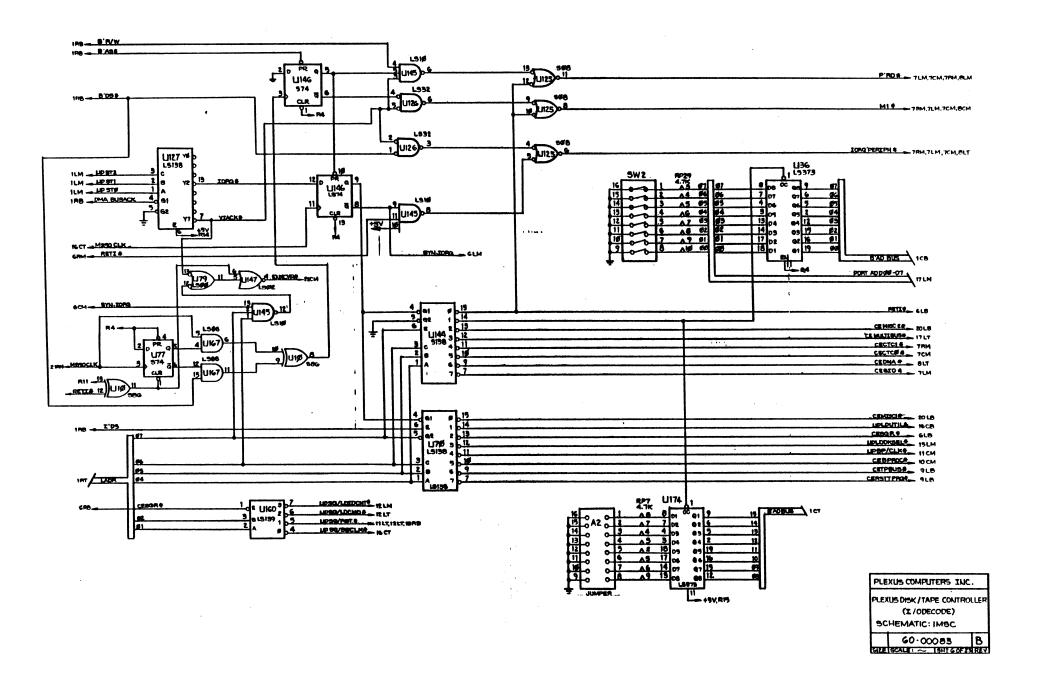

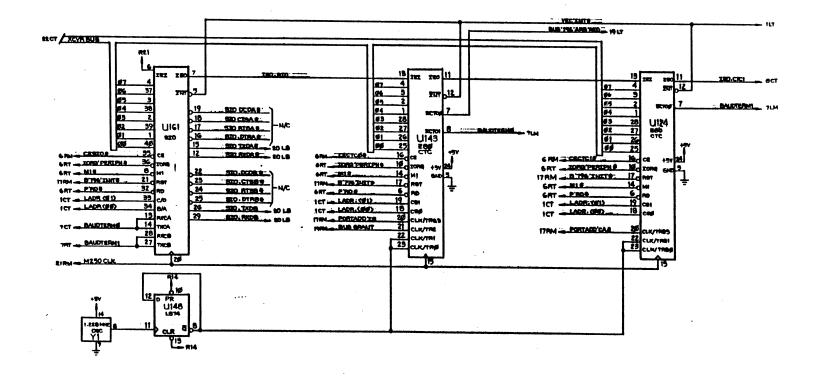

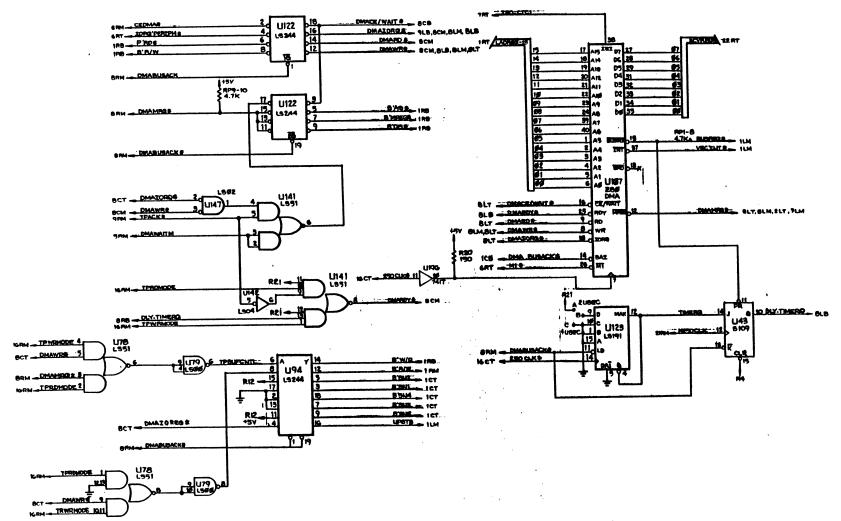

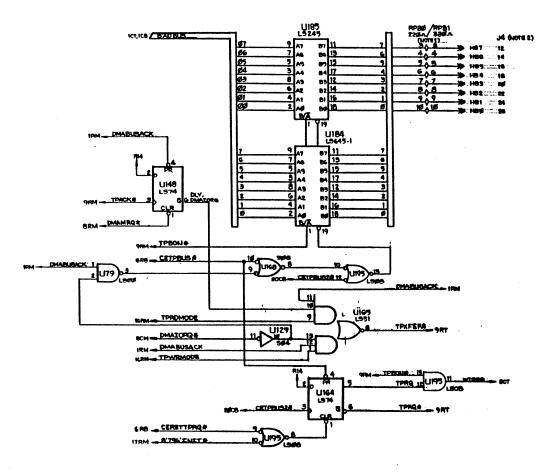

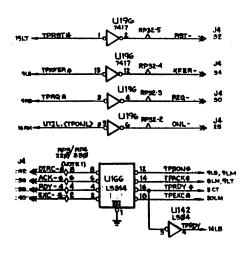

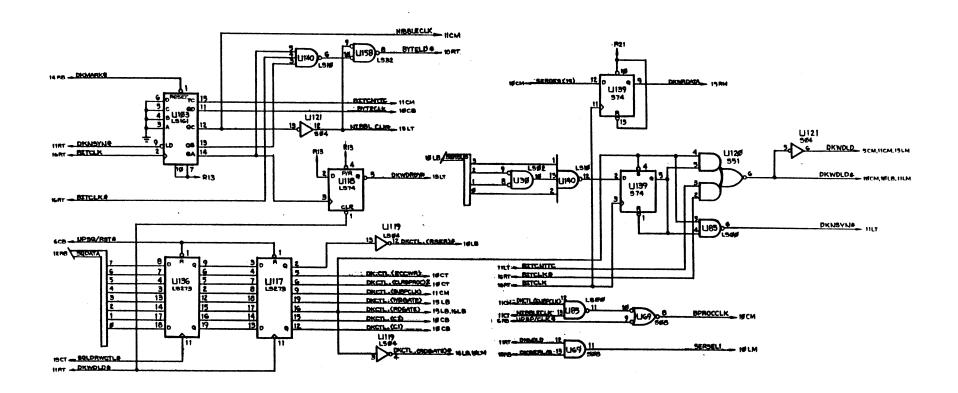

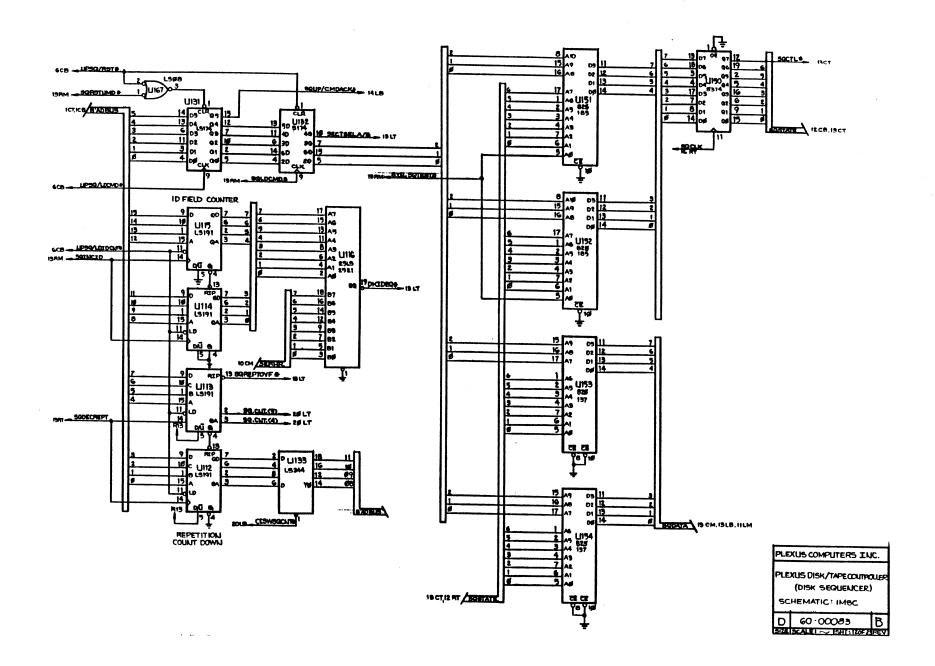

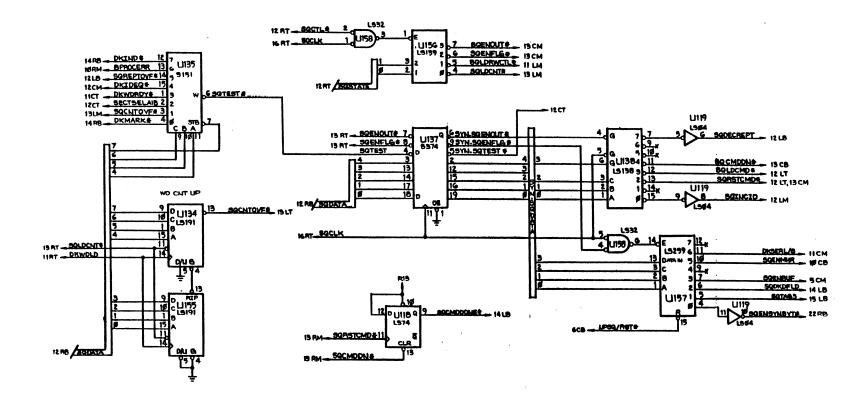

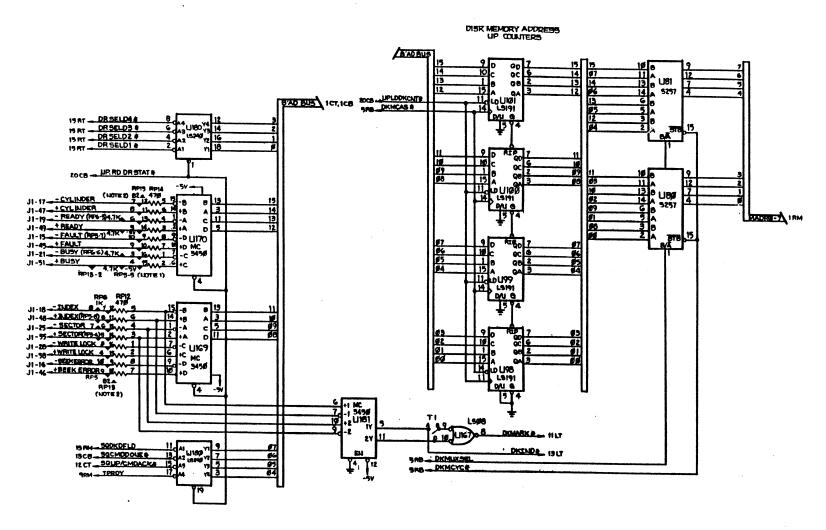

#### DISK AND TAPE CONTROLLER

- 1. IMSC OVERVIEW

- 1.1. References

- 2. PROCESSOR

- 2.1. Local Capabilities

- 2.2. Bus Structure

- 2.3. Local Ports

- 3. LOCAL MEMORY

- 3.1. Memory Organization

- 3.2. Local Dynamic RAM Access

- 3.3. Memory Arbitration 3.4. Local PROM

- 4. MULTIBUS INTERFACE

- 4.1. Bus Arbitration

- 4.2. Data Transfer4.3. Address Transfer

- 5. IMSC CONTROL

- 5.1. CPU Controlling IMSC5.2. IMSC Controlling Disk

- 5.3. ID Equate Latch

- 5.4. Serial-to-Parallel Conversion

- 5.5. Disk Interface 5.6. IMSC Controlling Tape Drive 5.7. Tape DMA

- 6. INTERRUPTS

- 6.1. Vectored Interrupts6.2. Nonvectored Interrupts

- 6.3. Nonmaskable Interupts

- 7. DMA

- 7.1. Overview

- 7.2. Disk to IMSC Transfer

- 7.3. Tape DMA

- 7.4. Local RAM to Memory Array -- Pseudo DMA

- 8. LOCAL BUS STRUCTURE

- 9. CTCs AND SIOS

- 9.1. Counter Timer Circuits

- 9.2. Serial Input/Output

- 10. ERROR HANDLING

- 10.1 Overview

- 10.2 Disk Errors

- 10.3 Tape Drive Errors

10.4 Local Memory Errors

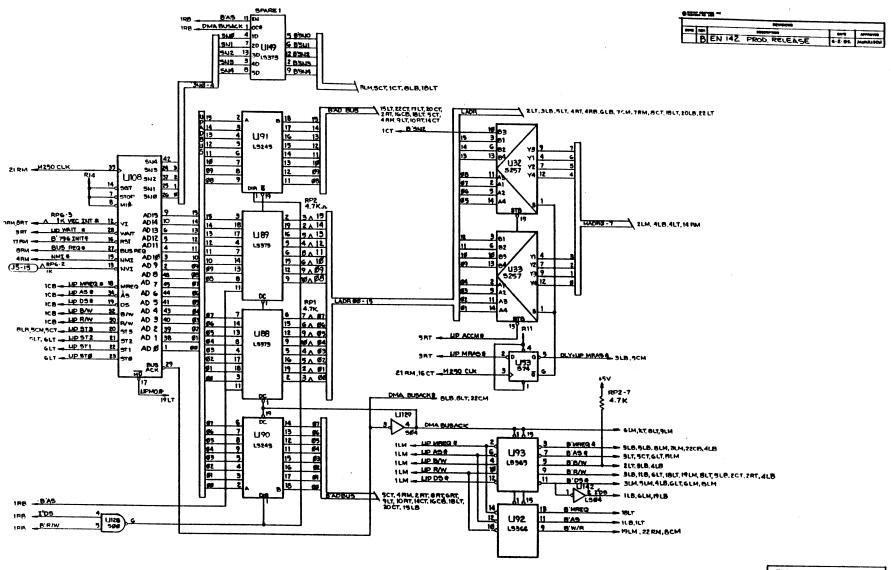

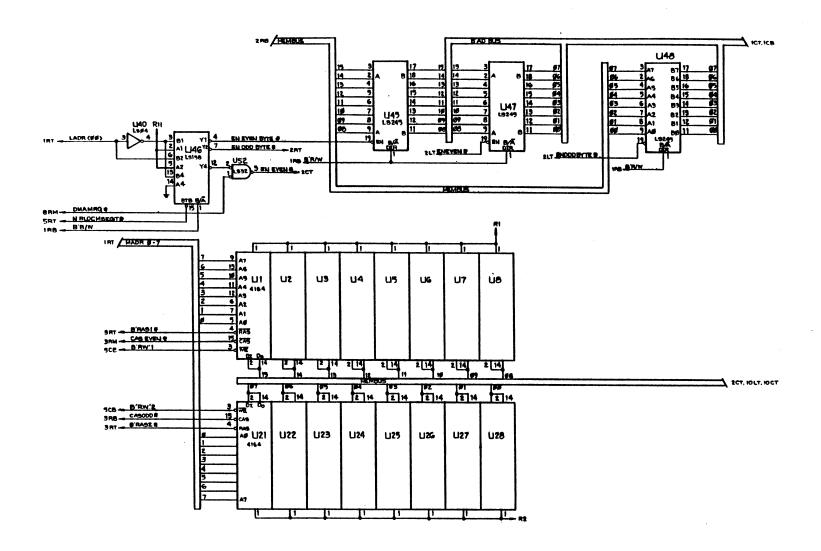

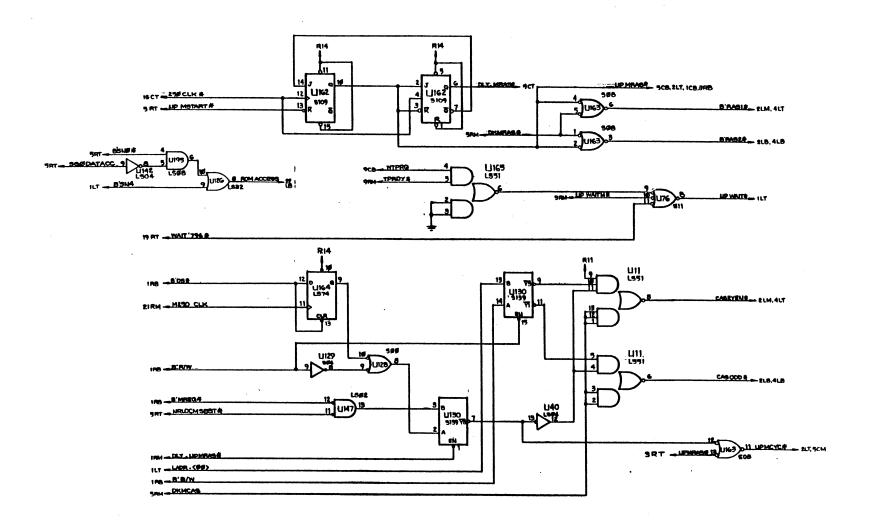

Figures

#### PREFACE

#### AUDIENCE

This P/25 Hardware Engineering Manual is intended for use by engineers and technicians who need to understand the P/25 in order to modify it, repair it or interface other equipment. It describes the P/25 down to the component level.

This is not a user's guide or a programming manual. While users and programmers might find the information useful, for day-to-day instructions, they should see the <u>Plexus P/25 User's Manual</u>. For programming information, they should see the <u>Plexus V7 UNIX Programmer's Manual--vol 1, 2A and 2B</u>.

A working knowledge of digital theory and/or computer architecture is necessary to make full use of this manual.

#### EQUIPMENT LEVEL

This manual is current as of July, 1982. It describes systems having both 4 and 5 Mhz system clocks and memory boards with 64K RAM chips. Earlier systems may have memory boards with 16K RAM chips.

#### CONTENTS

Except for the system overview, each section in this manual describes a particular P/25 PCB. Each PCB is responsible for a distinct set of system functions, so each section describes both a PCB and a set of system functions.

The sections in this manual are as follows:

System Overview -- Describes the entire system at a basic level. Read the overview first to obtain a feeling for the entire system. This will enhance understanding of any sections read later.

Processor -- Describes the Processor board, which contains the Central Processing Unit (CPU) and the Memory Management Unit (MMU). This is the controller for the entire system; each P/25 contains one and only one processor board.

Input/Output Controller -- The input/output controller is really an intelligent communication processor (ICP) that controls interaction with up to eight serial I/O ports (RS232C standard) and one parallel port (Centronics standard). Each P/25 contains one or two ICPs.

Memory -- While there is memory on every PCB in the P/25, this

section describes the system main memory (dynamic RAM) which connects to the rest of the P/25 via connector P2 from the processor board. Each P/25 contains one or two memory boards.

Backplane -- The backplane connects the components of the P/25 to each other. It consists of an industry standard Multibus (P796 Standard) and connector P2 which connects system memory to the processor. An <a href="IEEE Proposed Microcomputer System BusStandard">IEEE Proposed Microcomputer System BusStandard</a> (P796 Bus) is included in this section.

Disk and Tape Controller -- This section describes the Intelligent Mass Storage Controller (IMSC) which controls interaction with 1 to 4 SMD type disk drives and a streaming cartridge tape drive.

The figures and schematics for each section are at the end of the section.

2 Preface

## OVERVIEW

- 1. INTRODUCTION

- 2. CENTRAL PROCESSOR UNIT (CPU)

- 3. MEMORY MANAGEMENT UNIT (MMU)

- 4. MEMORY ARRAY

- 5. INPUT/OUTPUT CONTROLLER

- 6. INTELLIGENT MASS STORAGE CONTROLLER (IMSC)

- 7. MULTIBUS BACKPLANE AND INTERFACE

- 8. POWER SUPPLY

- 9. RESET, POWER FAIL AND RESTART

- 10. STANDARD PERIPHERAL CONFIGURATION

- 11. SPECIFICATIONS

- 12. BIBLIOGRAPHY

Figure

#### 1. INTRODUCTION

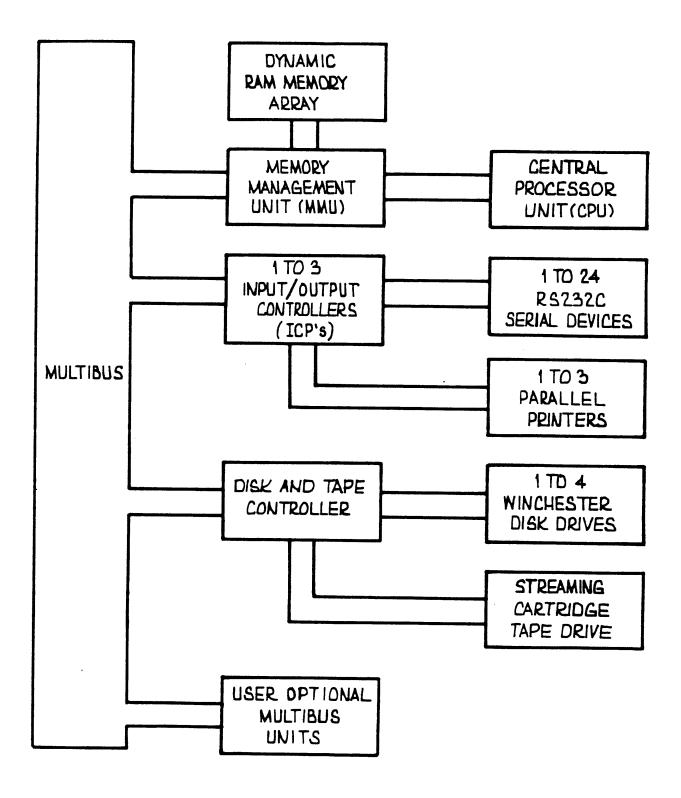

The Plexus Computers P/25 is a 16-bit multiprocessing minicomputer designed specifically to run the UNIX\* operating system. It supports 512K to 2M bytes of error-correcting memory, 16 terminals (serial ports), two parallel ports (printers), one streaming cartridge tape drive and one to four SMD-interface disk drives. The standard configuration includes a 22, 36 or 72M-byte (formatted) fixed Winchester disk drive and a 20M-byte four-track cartridge tape drive.

The P/25 uses an industry standard Multibus\*\* backplane (IEEE P796 Standard), and a storage module disk (SMD) interface. This, combined with the UNIX operating system, increases the ability of designers to rapidly integrate software and hardware to meet specific application needs.

The P/25 has from 3 to 5 asynchronous processors. The central processing unit (CPU), which executes system processes and user programs, contains a Zilog Z8001A. It is helped by at least two other processors — a disk and tape controller, and an intelligent communication processor (ICP). These peripheral controllers handle all interaction with disks, tape drives, terminals and printers independently of the CPU, using DMA to access memory. This deloads the Z8001A, leaving it free to execute instructions without handling many of the routine interrupts.

The P/25 also supports one or two user-supplied Multibus-compatible PC boards which plug into the Multibus backplane.

The standard P/25 is composed of the following major components:

Central Processor Unit

Memory Management Unit

Memory Array

Intelligent Communication Processor (ICP)

Intelligent Mass Storage Controller (IMSC)

Power Supply

Multibus Backplane

Winchester Disk Drive

Streaming Cartridge Tape Drive

Enclosure

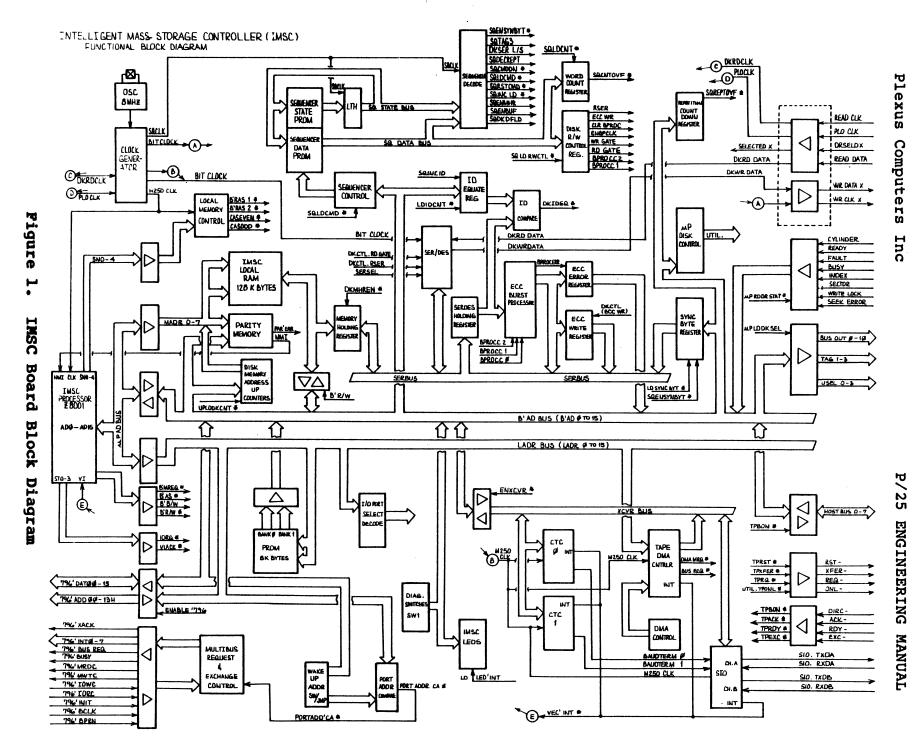

Each of the components is described in the following sections. A

<sup>\*</sup>UNIX is a trademark of Bell Laboratories. Plexus Computers Inc is licensed to distribute UNIX under authority of AT&T.

\*\* Multibus is a trademark of Intel Corporation.

block diagram (Figure 1) shows how they are interconnected.

# 2. CENTRAL PROCESSOR UNIT (CPU)

Each P/25 is equipped with one processor board, which contains the central processor unit and the memory management unit mounted on a double-height Multibus card.

#### 2.1. Processor

The CPU uses a Zilog Z8001A microprocessor which runs at 5-Mhz. The board includes latches, buffers, control lines, local peripherals and local memory to support the Z8001A. It accesses all other system boards through the Multibus (connector P1) except system memory which it accesses through connector P2.

# 2.1.1. Local Peripherals

The system CPU controls the following local peripheral devices located on the processor board:

Counter/Timer Circuit -- The CPU has access to a 4-channel Zilog Z80B counter/timer circuit. Channel 0 is connected to channel 1 and programmed to divide the system clock down to 50 hz. The output signal of channel 1 is used to generate realtime interrupts to the Z8001A. Channels 2 and 3 are uncommitted and available for general software use.

Programmable Interrupt Controller -- Interrupts to the Z8001A are controlled by a programmable interrupt controller (PIC), which receives interrupt requests from various devices and passes interrupts to the Z8001A based on priority.

Clock/Calender -- A clock/calender circuit (realtime clock) gives the CPU access to time-of-day in hours, minutes and seconds, and days, months and years. A battery powers it for up to three months after system power is removed.

#### 2.2. Software

The CPU uses four of the Z8001A address spaces. Standard I/O space communicates with ports on the Multibus. Special I/O space controls peripheral circuitry on the processor board. Memory instruction space and data space are used to access memory.

The CPU uses three of the Z8001A interrupt and trap capabilities.

Nonmaskable interrupts are used for power-fail detection. Vectored interrupts inform the Z800lA that a controller on the Multibus requires service, and a segment trap informs the Z800lA that an MMU error has occurred.

The Z8001A can be reset by asserting the Multibus INIT/ line, or it can reset itself by causing the INIT/ line to be asserted. It can also reset all Multibus controllers with the INIT/ line without resetting itself.

## 2.3. Diagnostic Port

The CPU has direct control of a diagnostic console port which attaches to connector P3.

## 3. MEMORY MANAGEMENT UNIT (MMU)

The memory management unit (MMU), located on the processor board, controls access to system memory. It receives logical memory addresses from the CPU or peripheral controllers and converts them into physical memory addresses for access to the memory array. It also handles memory protection, error detection and correction, and refresh.

#### 3.1. Page Map RAM

The MMU contains a page map RAM which, under the control of the operating system, remembers the differences between physical memory addresses and logical memory addresses. This allows different programs and processes to use the same instruction set simultaneously. The physical memory consists of 32 map sets of 32 pages, each containing space for 2K bytes.

## 3.2. Memory Protection

Each page can be assigned a read-only and an invalid status. These protect critical data from illegal instructions. Memory accesses which do not match the page status are not allowed.

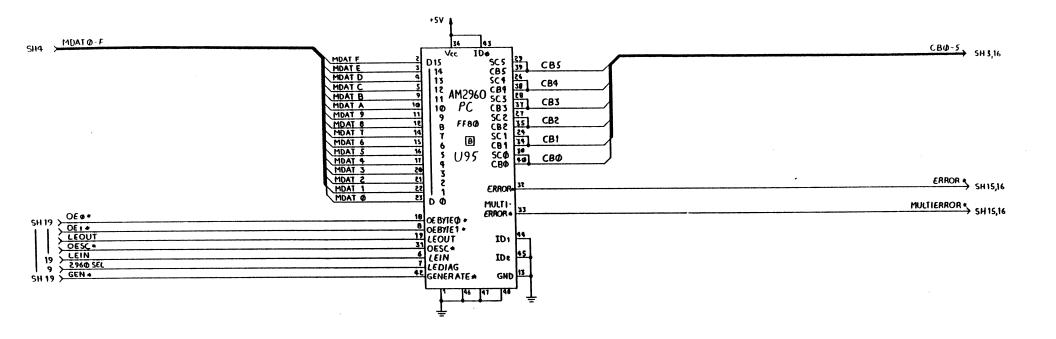

# 3.3. Error Detection and Correction

The MMU contains an AMD 2960 error detection and correction circuit which generates checkbits based on a modified hamming code. When data is stored in memory, a set of checkbits are stored with it. When the data is retrieved, a new set of checkbits are generated and compared with the old set. It they

are not identical, it attempts a correction and sends the proper signal to the CPU.

#### 3.4. Refresh

Refresh circuits for system memory are located on the processor board. It provides an 8-bit refresh address every 14.4 microseconds using a cycle-stealing technique.

#### 4. MEMORY ARRAY

The P/25 memory array consists of three types of memory: dynamic RAM, EPROM, and static RAM. The dynamic RAM is located on separate printed circuit boards, while the EPROM and static ROM are located on the processor board.

# 4.1. Dynamic RAM Array

Dynamic RAM is the major component of system memory. It occupies physical addresses from 100,000 to 300,000H when fully equipped, and is the only system memory used during normal operation.

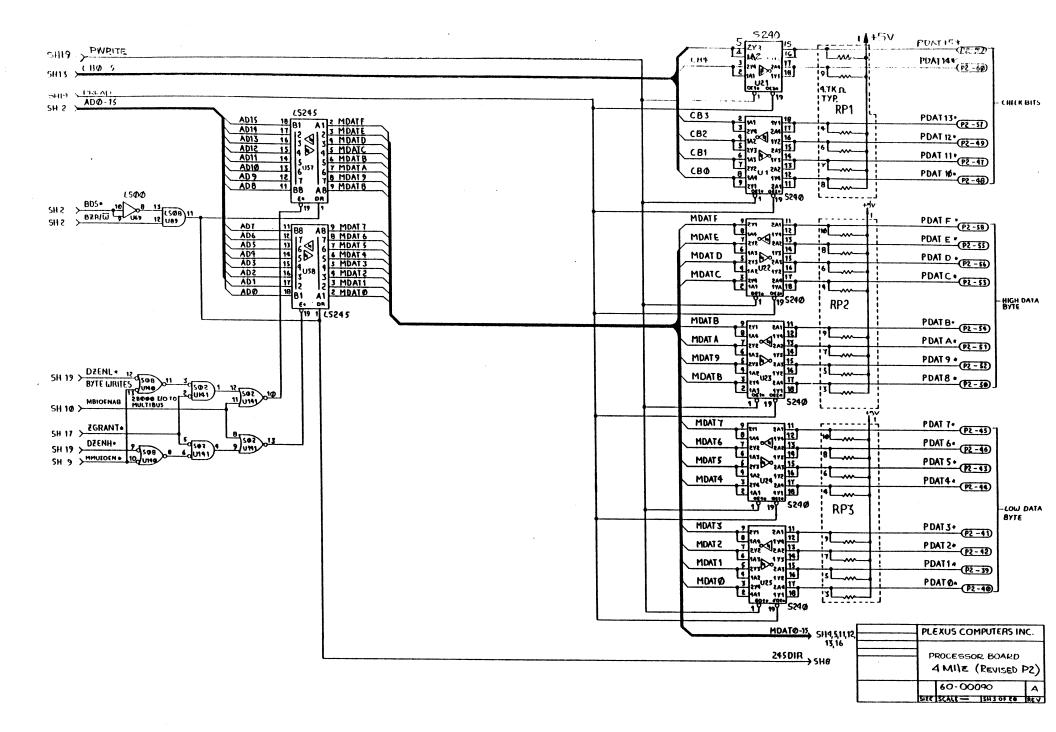

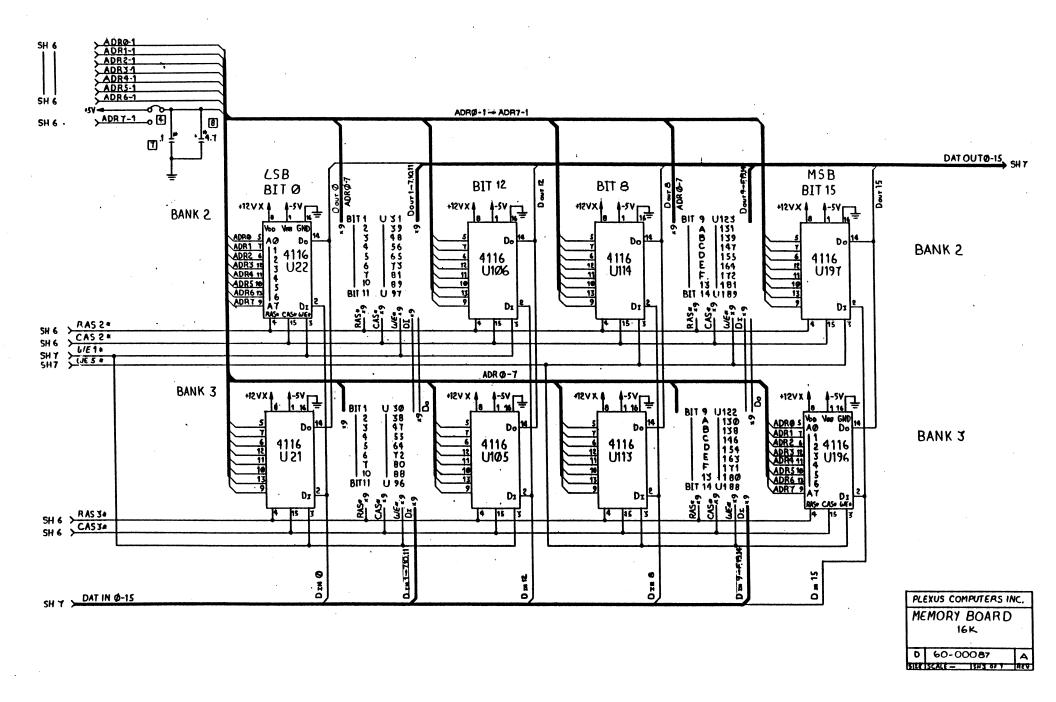

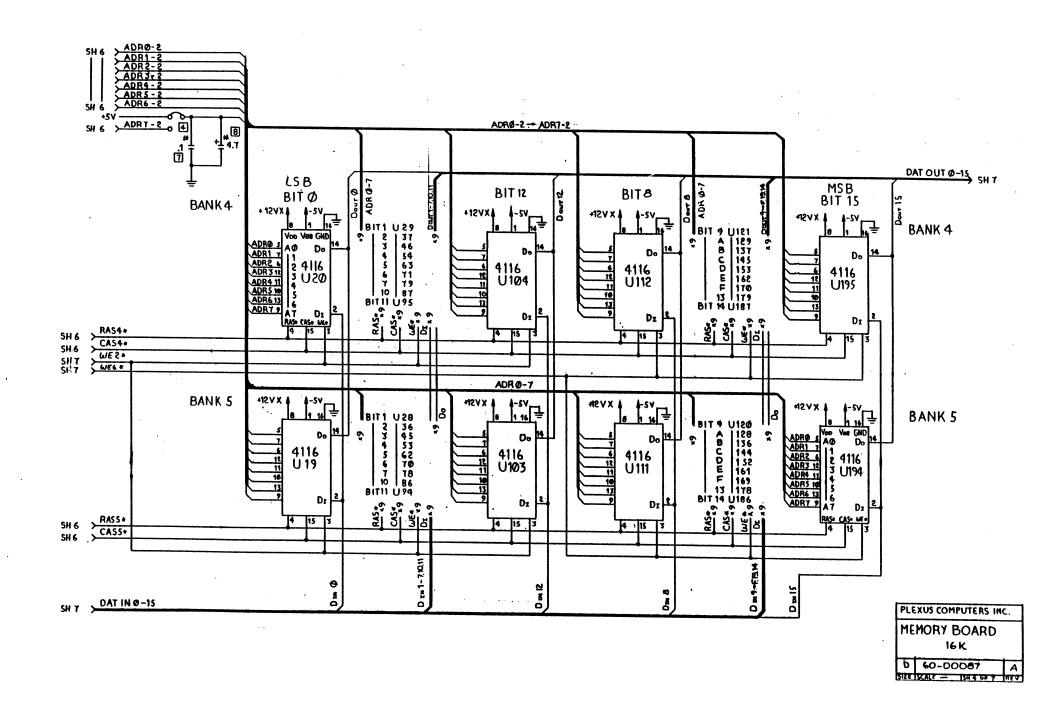

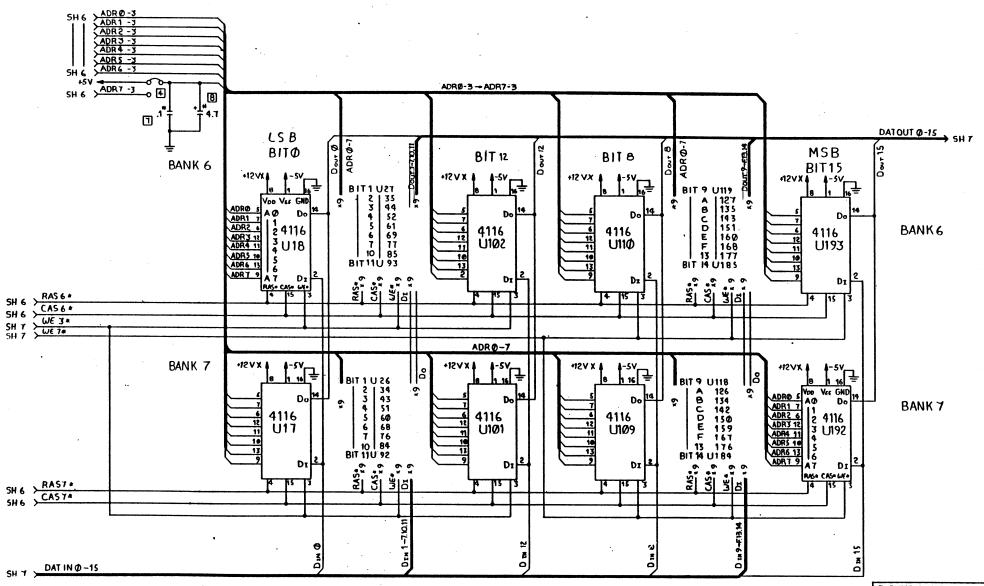

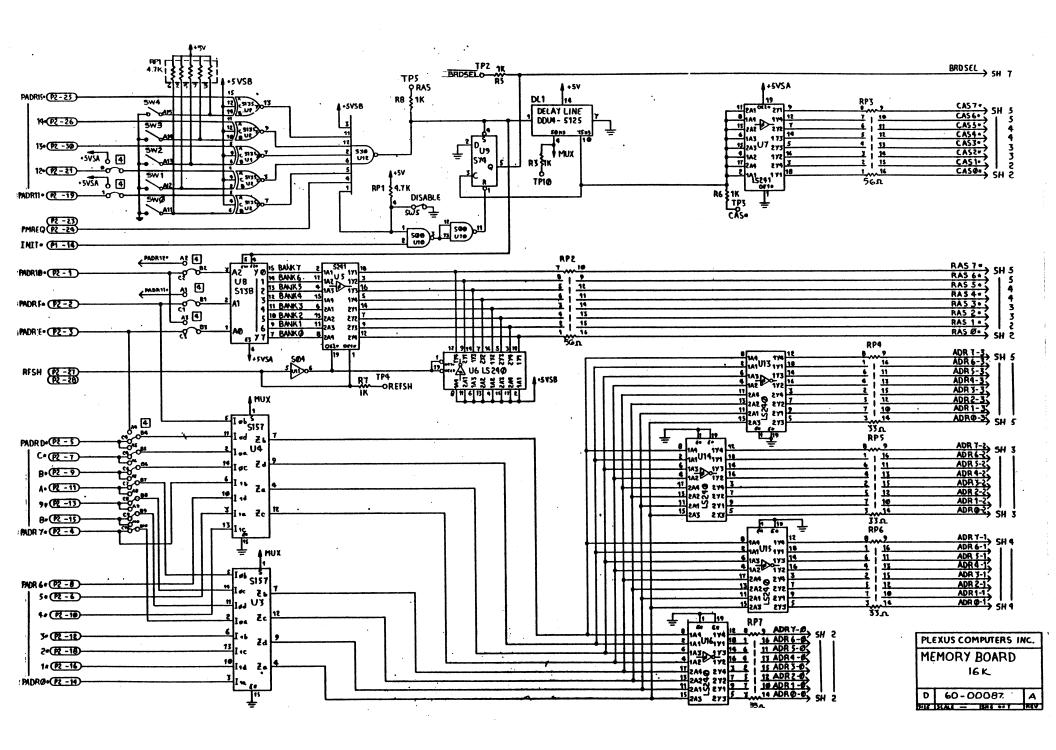

The dynamic RAM boards each contain 256K, 512K or 1024K bytes of memory arranged in 2-byte words. Each word consists of 16 bits of data and six error-correction bits. Each board also contains basic support functions for the RAM, including address decoders, buffers and RAS/CAS multiplexors. All control, address and data lines for the RAM array come from the MMU over a dedicated bus on connector P2. Although an array board occupies a slot in the Multibus backplane, it takes only power and ground from the Multibus connector.

## 4.2. EPROM

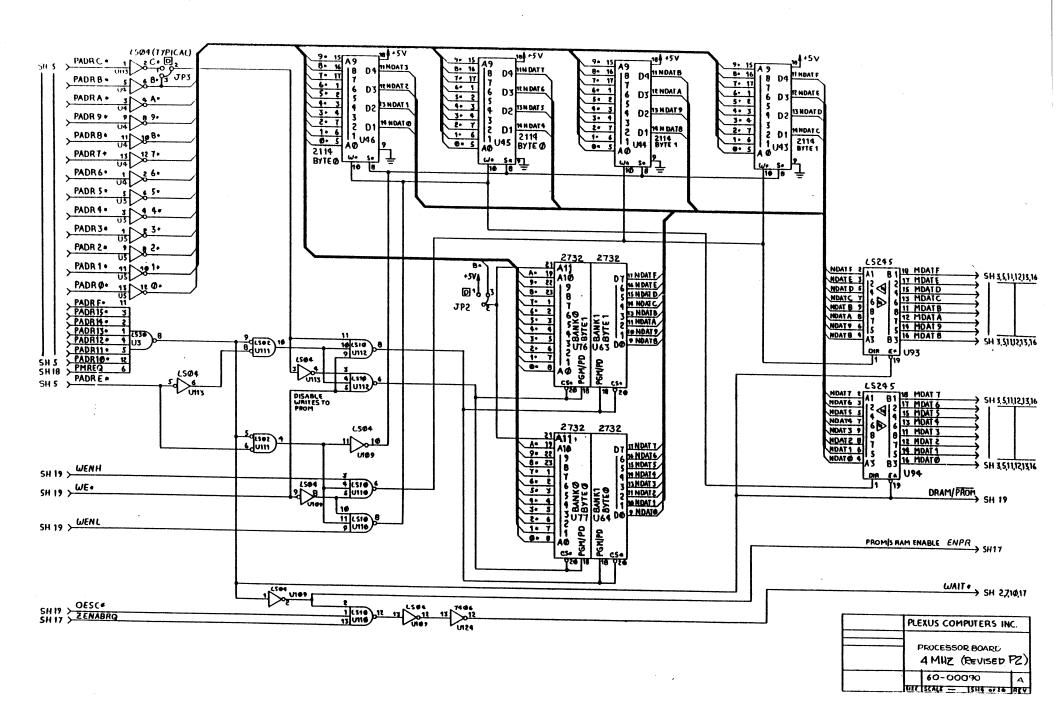

The EPROM contains the bootstrap instructions used to load the operating system. It also contains data used for factory testing and diagnostics. It occupies physical memory addresses from 0 to 3fff.

Four sockets for EPROM are located on the CPU board. The sockets accommodate either  $2K \times 8$  (2716) or  $4K \times 8$  (2732) MOS EPROMS. The minimum EPROM configuration is 2K words (two 2716 EPROMS) and the maximum is 8K words (four 2732 EPROMS). A jumper on the board is used to select the EPROM size. The access time is 450 nsec. A single wait-state is added when the CPU accesses the EPROM.

No error correction or detection is performed on accesses to EPROM.

#### 4.3. Static RAM

The CPU has lK words of static RAM which occupies addresses from 8000 to 87FE. It is implemented with four lK x 4 static RAMS (2114). The RAM is byte-addressable and is used principally for diagnostic and initialization routines.

The static RAM has a 450-nsec access time, so a single wait-state is added when the CPU accesses static RAM. No error correction or detection is performed on accesses to static RAM.

### 5. INPUT/OUTPUT CONTROLLER

The input/output controllers are intelligent communication processors (ICPs) that handle data movement between terminals and printers and system memory. They use direct memory access (DMA) to bypass the CPU, freeing it from handling I/O interrupts. Each ICP controls eight serial ports (terminals) and one parallel port (printer). Each P/25 is equipped with one or two ICPs.

The ICP is a double-height Multibus card that features a Zilog Z8002 microprocessor.

#### 5.1. Serial Ports

The eight RS232C serial ports are implemented with Z80A SIO/2 USARTS. They support baud rates from 50 to 38.4K hz by programming a Zilog CTC Counter/Timer. Each channel has its own DMA channel to move data from local memory to the transmit line. A DMA transfer is initiated by the SIO when its transfer buffer becomes empty. A rotating priority scheme ensures that the most recently serviced SIO has the lowest priority.

### 5.2. Parallel Port

The ICP has a single DMA-supported parallel port used to connect an industry-standard (Centronics-type) printer. Control logic associated with the port generates all the handshake signals necessary for the DMA to transfer data to the printer without intervention from the CPU.

### 5.3. Local Memory

Each ICP is equipped with 32K bytes of dynamic RAM, including parity bits and refresh. This is used to store operating instructions for the ICP and to buffer data between transfers.

#### 5.4. Pseudo DMA

The ICP uses pseudo DMA to move data from its local RAM to system memory. The Z8002 initiates block moves between the local RAM and a 16K section of its memory space that is mapped into main memory. This can run in the background, without monopolizing either the Multibus or the local bus.

#### 6. INTELLIGENT MASS STORAGE CONTROLLER (IMSC)

The IMSC is an intelligent disk and tape controller that contains an onboard Z8001 microprocessor. It receives commands from the CPU to move blocks of data between system memory (RAM) and the disk drives or tape drive. It has 128K bytes of local RAM which it uses to buffer entire disk tracks, thus decreasing the number of real disk accesses when two different processes require constant access to the disk. The buffers store the information from the disk and pass it to each process as if it were the only process using the disk.

The disk interface is an industry-standard SMD type. The tape drive is intelligent, performing many of the functions normally required of the tape controller. It communicates with the IMSC over eight data lines and eight control lines.

The IMSC has three distinct DMA circuits on board. A Z80 DMA chip controls the movement of data between the tape drive and the IMSC local RAM. The disk sequencer provides DMA between the disk drives and the IMSC local RAM. The IMSC processor (Z8001) uses its block move capability to move data from local RAM to or from the portion of its memory space which is mapped into the Multibus memory space. This is not a true DMA because the initiating device (the IMSC processor) stays involved.

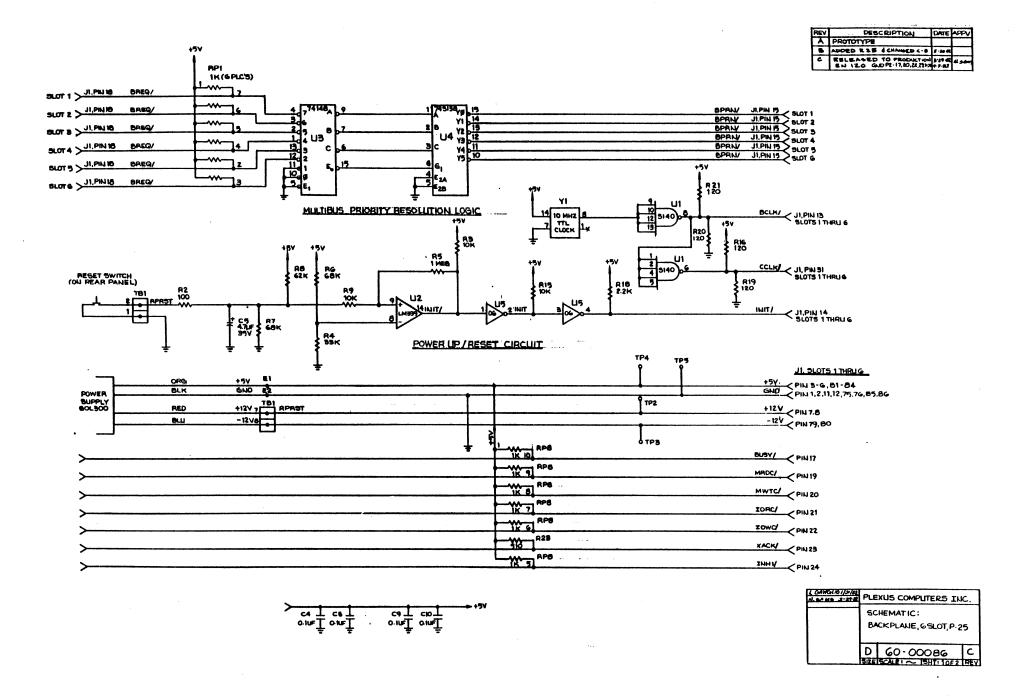

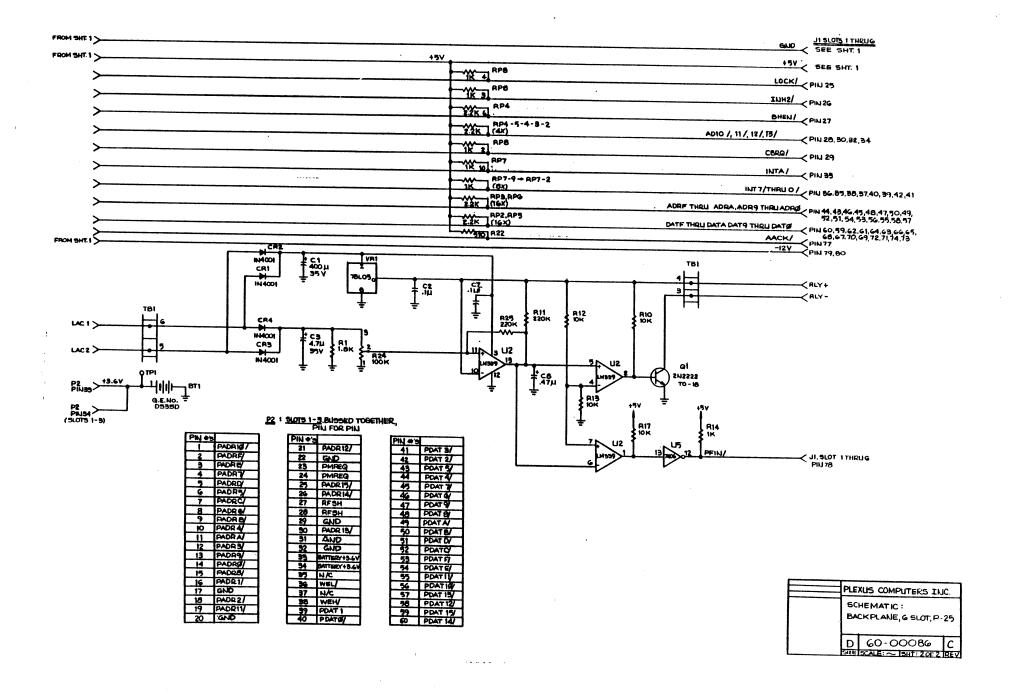

## 7. MULTIBUS BACKPLANE AND INTERFACE

Most of the circuits in the P/25 are on PC cards that plug into a Multibus backplane. The backplane has 6 slots, and can contain one or two memory array boards, three bus masters and a processor board.

The only active circuits on the Multibus backplane are bus

priority resolution circuits that arbitrate control of the Multibus, and a bus clock generator that provides the 10-Mhz signal used by bus masters to synchronize their bus arbiters.

Each standard-equipped P/25 contains one processor board, one or two intelligent communication processors (ICPs), one or two memory array boards (dynamic RAM) and a disk and tape controller board. This leaves room one or two user-selectable Multibus boards.

All PC cards except for the memory array are attached to connector Pl which is described in the <u>IEEE Proposed Microcomputer System Bus Standard (P796 Standard)</u>. The memory array boards attach to connector P2 and the diagnostic console attaches to connector P3.

In the P/25, the CPU acts like a bus master. The IMSC and the MMU (physically located on the processor board) act like bus masters or slaves. User-selectable boards may be either masters, slaves or both.

The P/25 Multibus uses a subset of the parallel arbitration technique described in the P/25 Standard,

section 2.4.2.2. Once a master is granted control of the Multibus, it maintains control by holding the BUSY/ line active. The amount of time a master is allowed to hold the Multibus has a serious effect on system performance and can be adjusted.

The bus priority out (BPRO/) and common bus request (CBRQ/) signals are not used by the P/25 standard units, but may be used by user-selectable I/O controllers.

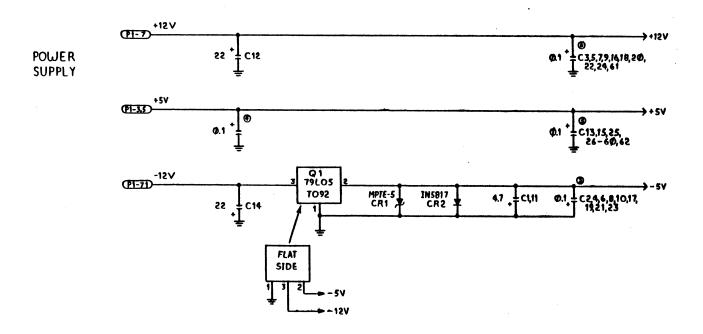

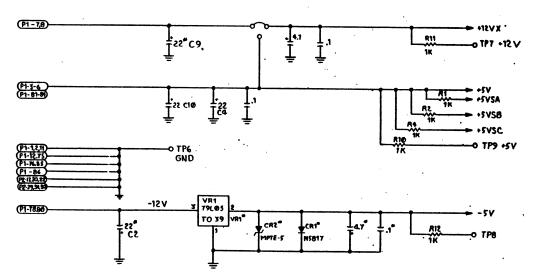

#### 8. POWER SUPPLY

The P/25 is equipped with a multiple-output, switching power supply which provides overvoltage and short-circuit protection. It supplies the following levels:

| <u>Volts</u>            |                      | Amp <u>s</u>          |

|-------------------------|----------------------|-----------------------|

| +5<br>+12<br>-12<br>+24 | at<br>at<br>at<br>at | 25<br>2.5<br>1.7<br>4 |

| <b>-</b> 5              | at                   | ī                     |

### 9. RESET, POWER FAIL AND RESTART

The entire P/25 can be reset by asserting the INIT/ line on the Multibus. This line is controlled by three sources:

- (1) front-panel reset button

- (2) a control bit that can be set by the CPU

- (3) the power supply's AC line monitoring circuitry.

The AC line monitor sends a power fail interrupt (PFIN/) to all devices on the Multibus when the line voltage drops below specification. The CPU responds to this interrupt and, after performing some housekeeping, resets the system by asserting the INIT/ line. Other processors in the system can use the PFIN/ internally.

When AC power is restored to the system, no effort is made to restart the system to its state prior to power failure because there are no provisions to save the contents of memory during the outage. Instead, when failure due to a power outage cannot be tolerated, an uninterruptible supply (UPS) for the AC line is available.

NOTE: The P/25 power supply is equipped with brownout protection, which provides uninterrupted power to the P/25 for 16 milliseconds in the event of a transient AC power failure.

When power is applied to the system, the INIT/ line is asserted for about 100 milliseconds. This assures that DC power is stable before the system is placed in operation.

### 10. STANDARD PERIPHERAL CONFIGURATION

The IMSC supports a number of industry-standard disk and tape drives, so it is possible to configure a wide variety of systems. However, the combination of a fixed Winchester disk and streaming cartridge tape drive has proven to be a very flexible and cost-effective combination, and is therefore offered as the standard.

#### 10.1. Disk Drive

The P/25 comes equipped with one of three standard 8-inch fixed Winchester disk drives. These are compared in the following table:

# Storage Capacity

Average Positioning Time (Head Positioning + Latency)

22 megabytes 38.55 milliseconds

36 megabytes 38.55 milliseconds

72 megabytes 28.3 milliseconds

Up to 3 additional disk drives may be added in a separate cabinet. The total disk capability is 336 megabytes.

(For further information on the drive, see the Plexus Winchester Disk Manual for the appropriate size disk drive.

# 10.2. Tape Drive

The P/25 comes equipped with a 20M-byte streaming cartridge tape drive. It has 8000 bpi storage density on 8 tracks, and can store 20M-bytes in 3.7 minutes.

(For further information on this drive, see the <u>Plexus Cartridge</u> <u>Tape Drive Manual</u>.

## 11. SPECIFICATIONS

The P/25 with its standard peripherals is packaged in a 19-inch wide, 24-inch deep, 10.5-inch tall tabletop cabinet which can fit in a standard 19-inch RETMA rack.

# 11.1. Processor Specifications

#### Electrical

95 - 130 volts AC @ 4a 190 - 250 volts AC @ 2a

#### Environmental

temperature: 5C to 38C (41F to 100F) relative humidity: 20% to 80% noncondensing

### 12. BIBLIOGRAPHY

- (1) Advanced Micro Devices <u>AmZ8000 Family Data Book</u> (AMD #AM-PUB098)

- "Am9512 -- Floating Point Processor"

- (2) Advanced Micro Devices <u>Bipolar Microprocessor Logic and Interface Book</u> (AMD #MLI-495)

- "Am2960 -- EDC Cascadable 16-Bit Error Detection and Correction Unit"

- (3) Intel Component Data Catalog (Intel #AFN-01300A-1)

- "8237/8237-2 -- High Performance Programmable DMA Controller"

- "8259A/8259A-2/8259A-8 -- Programmable Interrupt Controller"

- (4) OKI Semiconductor <u>MSM5832</u> -- <u>Microprocessor Real-Time</u> <u>Clock/Calendar</u>

- (5) Signetics Z661 UART Product Specification

- (6) Zilog Z8000 CPU Technical Manual (Zilog #00-2010-C)

- (7) Zilog 1981 Data Book

- "Z8420 -- Z80 PIO Parallel Input/Output Controller"

- "Z8430 -- Z80 CTC Counter/Timer Circuit"

- "Z8440 -- Z80 SIO Serial Input/Output Controller"

Figure 1. Block Diagram of the P/25

# PROCESSOR

- 1. Z8001A MICROPROCESSOR

- 2. MEMORY MANAGEMENT UNIT

- 3. LOCAL PERIPHERALS

- 4. MULTIBUS INTERFACE

- 5. LOCAL BUS ARBITER AND TIMING SEQUENCER

- 6. ERROR HANDLER

Figures

#### 1. Z8001A MICROPROCESSOR

The P/25 CPU is built around the Zilog Z8001A 16-bit microprocessor. Nearly all features of the Z8001A are used, including separate instruction and data space, user/system modes, and nonvectored and vectored interrupts.

The Z8001A in the P/25 has 16 general-purpose registers and 110 distinct instruction types. For detailed descriptions of the registers and instructions, refer to the Zilog Z8000 CPU Technical Manual.

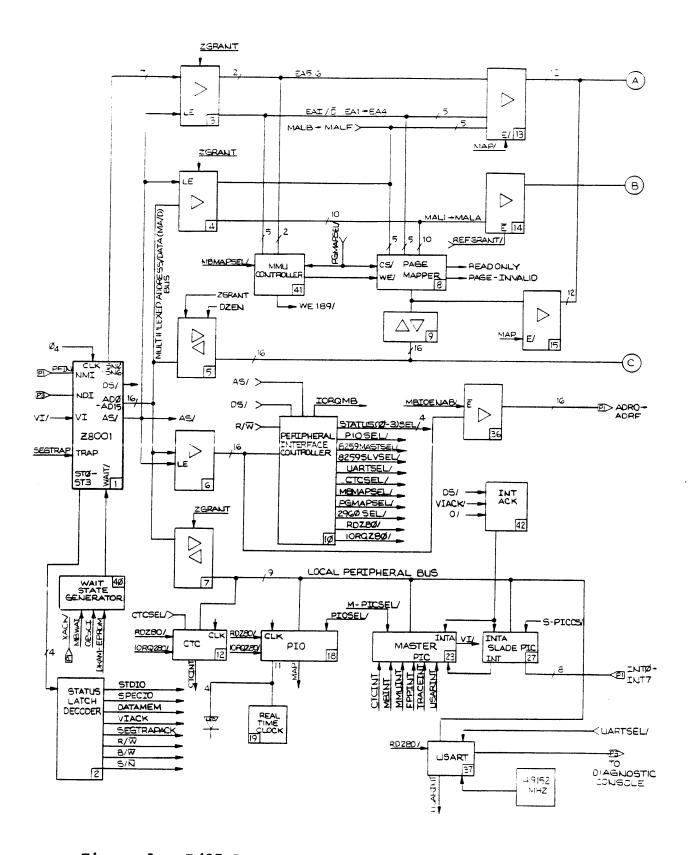

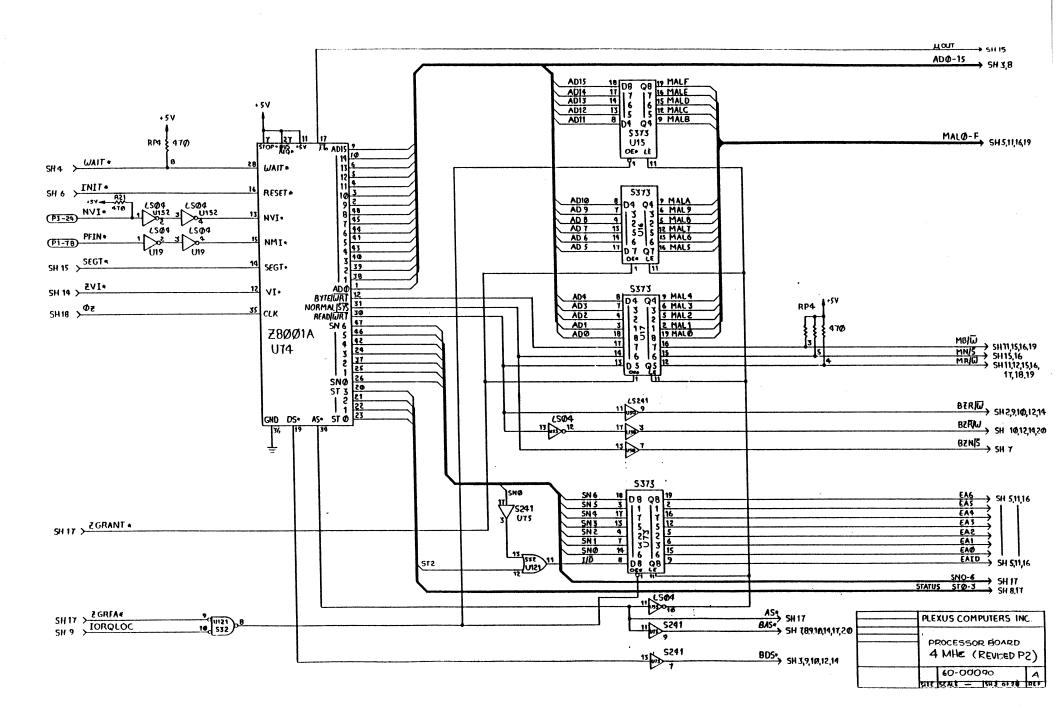

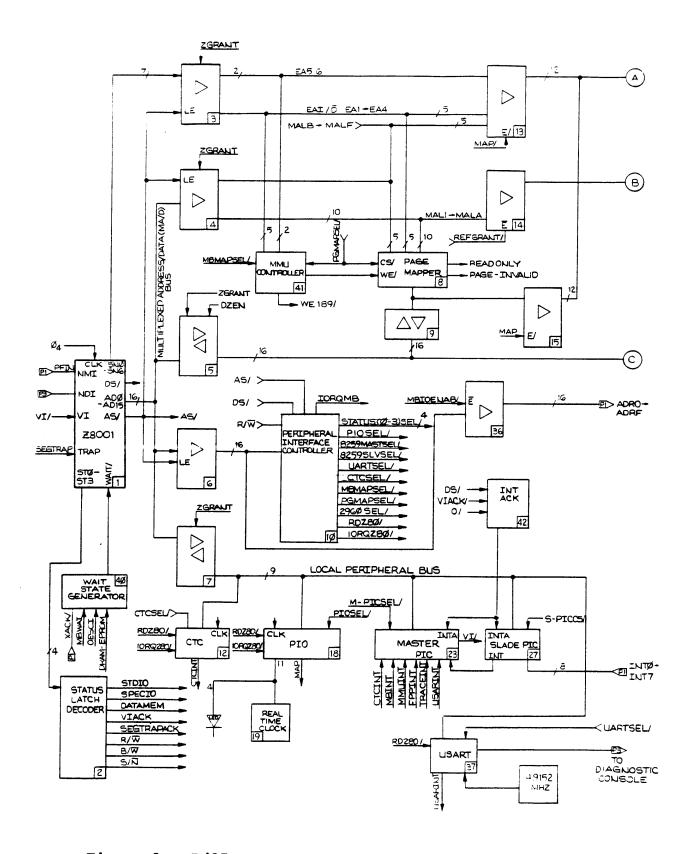

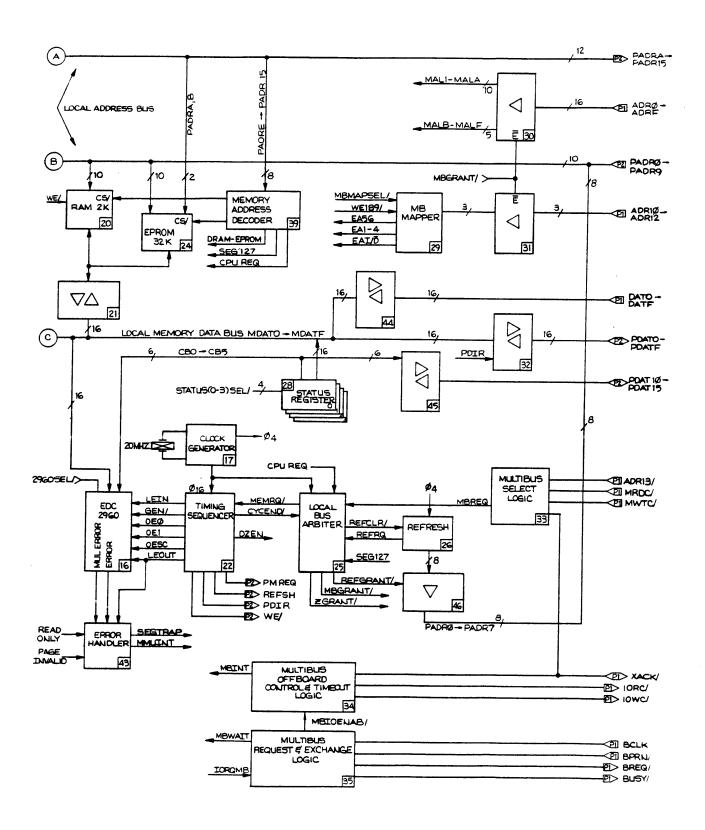

The functional blocks on the processor board are shown in Figure 1. All block references in this section are to Figure 1.

## 1.1. Programming Information

The following programming information is necessary to understand the functioning of the Z8001A CPU:

- (a) Address Spaces -- All four address spaces provided by Z800lA are used in the P/25. The normal I/O space is used to communicate with I/O ports on the Multibus. The special I/O space is used to control the peripheral circuitry on the processor board. Memory instruction and data spaces are used to access the corresponding locations in main memory.

- (b) User and System Process -- When a user process is running, the Z8001A is always operated in normal mode and unsegmented mode. But when a system process is running, the Z8001A operates in system mode and either unsegmented mode or segmented mode. Thus, user programs can only access one memory segment but system programs can access all memory segments. One segment occupies 64K bytes of address space in Z8001A.

- (c) Data Types -- The Z8001A supports manipulation of eight data types. Each data type is supported by a number of instructions which operate upon it directly. These data types are:

Bit

Binary integer

Logic value (boolean)

Address

Decimal integer

String of bytes

String of words

Stack of words

- (d) Byte and Word -- Both byte and word operations are provided, enabling the Z8001A to transfer data to an 8-bit master on the Multibus and enabling a Multibus master to access the 16-bit memory system.

- (e) Segments -- There are 128 segments available in the Z8001A memory address space providing a maximum address space of 8M bytes. In the P/25, the top segment (seg 127) is allocated to the memory mapper to reduce overhead when swapping processes. The lower segment (seg 0) is allocated to the local CPU memory (EPROM and static RAM).

#### 1.2. Hardware Interface

The following Z8001A lines control peripheral hardware functions:

- (a) Address/Data lines -- These 16 address/data lines are connected from the Z800lA to the local multiplexed address/data bus and through it to the other local buses.

- (b) Segment lines(SNO to SN6) -- In addition to their normal function, the least significant segment line (SNO) is ORed with ST2 to select either program or data address space.

- (c) WAIT/ -- This line is pulled low, extending the transaction time, when any of the following occurs:

- 1) EPROM and static RAM read or write

- 2) Multibus I/O port read or write

- 3) Byte write to dynamic RAM.

- (d) Segment Trap -- A segment trap is generated by the error handler when a memory mapping error or a EDC error output is detected.

- (e) Nonmaskable Interrupt (NMI) -- This input is connected to POWER FAIL line on the Multibus.

- (f) Nonvectored Interrupt (NVI) -- This input is reserved for diagnostics and is provided on connector P3.

- (g) Vectored Interrupt (VI) -- Two Intel 8259A interrupt

controllers (one master and one slave) provide 15 levels of interrupt.

(h) Multi-Micro (MO/) -- This Z800lA output pin controls the error detection and correction (EDC) single-bit interrupt circuits.

NOTE: The MO/ output is not used in earlier models of the processor unit.

(i) STOP/, BUSRQ/ -- Not used.

## 1.3. I/O Access

## 1.3.1. Standard I/O Space

When a standard I/O instruction is to be executed, the Z8001A requests control of the Multibus through the local bus arbiter. When control is granted, the CPU places the I/O port address on ADRO to ADR15, and asserts the proper read or write control line (IORC/ or IOWC/). The addressed multibus port executes the command and returns an acknowledge (XACK/). The Z8001A allows the command execution to complete, then releases the Multibus. The proper number of wait-states are inserted automatically when standard I/O instructions are executed.

The CPU uses only word instructions when accessing Multibus ports (BHEN/ must be low). If the port supports only byte operations, the high-order byte is undefined when the port is read and ignored when the port is written.

The CPU can maintain control of the Multibus between I/O instructions by setting bit Al of the control port PIO (7F88H) high. This causes the bus arbiter to hold the bus until the bit is reset. Until then, no other bus masters can use the bus. This is used primarily for diagnostic fault isolation and to test and set shared resource semaphores.

#### 1.3.2. Watchdog Timer

A watchdog timer forces the completion of a CPU-initiated I/O cycle if the CPU does not receive XACK/ within 20 microseconds. This prevents the system from being disabled if the CPU executes a standard I/O instruction to a nonexistent port or if the device at the port fails to return XACK/. If the timeout occurs, a vectored interrupt is sent to the CPU, which must clear the

interrupt by performing a special output (SOUT) to port 7FB3H.

# 1.3.3. Special I/O Space

The Z8001A special I/O space is used to control local (processor board) peripherals, and for diagnostic and housekeeping functions. As with the standard I/O space, only word instructions are allowed. For more information on the uses of special I/O space, see the Processor section 3, Local Peripherals.

## 1.4. Trace Mode Capability

To aid in software debugging, the CPU has trace mode capability, which generates a vectored interrupt to the Z800lA when the CPU fetches the first word of an instruction in normal mode. This is useful for single-stepping through programs. This interrupt must be reset by performing an SIO write to port 7FB2H. To shut off the trace mode, the CPU must mask off the trace mode interrupt in the interrupt controller.

### 1.5. Controls and Indicators

The processor board is equipped with four DIP switches. Three of the switches select the baud rate for the diagnostic console and the fourth selects automatic boot mode (the system re-initializes itself automatically after powerup or reset).

NOTE: The switch and LED functions are set by system software and are subject to change.

The processor board also has four LEDs (CR4 to CR7) which provide diagnostic information during powerup and system status information during normal operation. The LEDs indicate system status as follows:

- CR 4 -- ON indicates a disk access

- CR 5 -- ON indicates a tape access

- CR 6 -- Not used

- CR 7 -- ON indicates user access.

# 1.6. Circuit and Timing Analysis

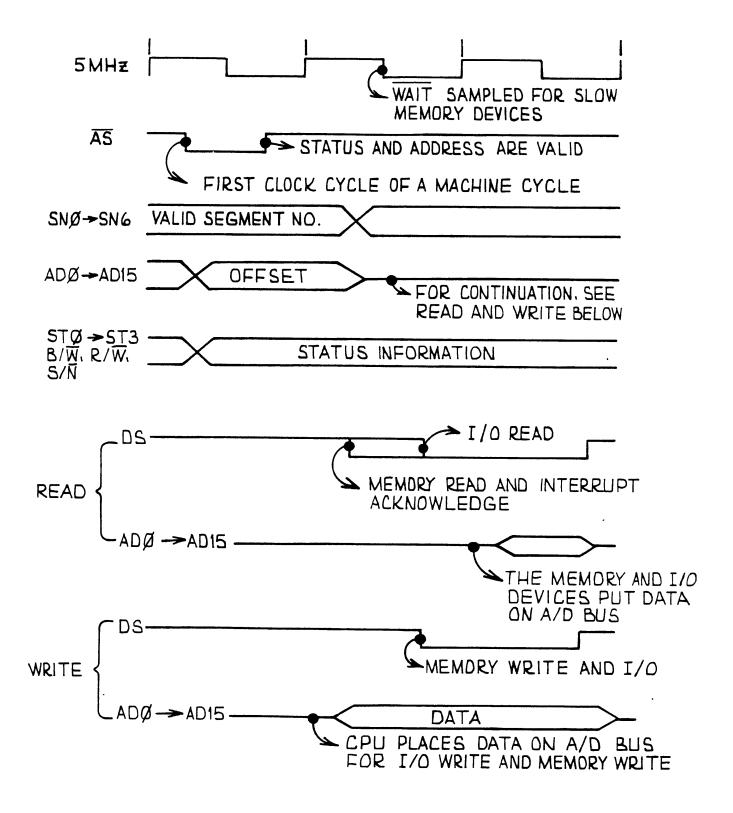

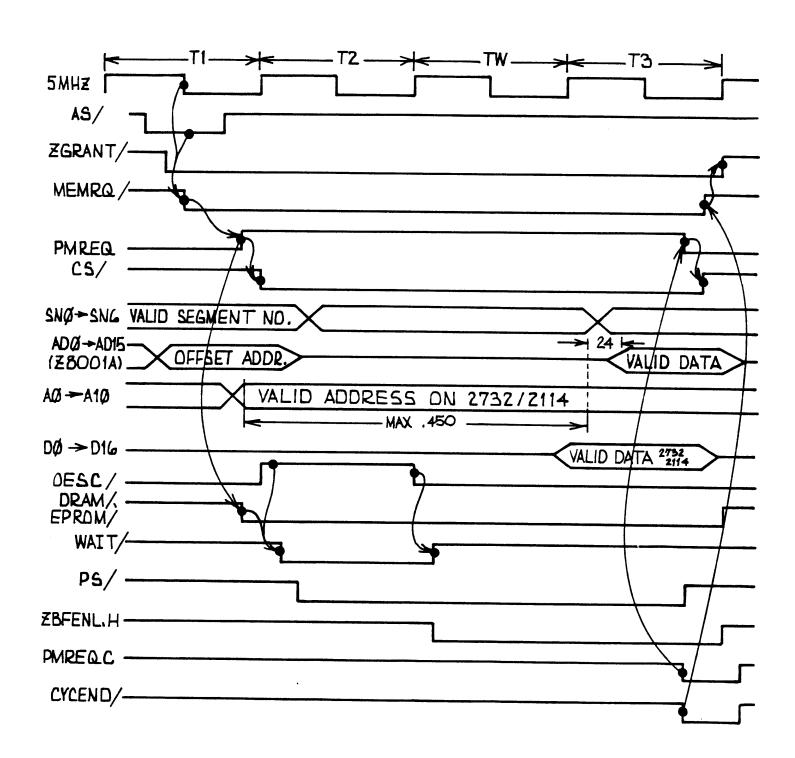

A basic timing diagram of the Z800lA for both read and write operations is shown in Figure 2.

## 2. MEMORY MANAGEMENT UNIT (MMU)

The MMU is physically located on the processor board. Its basic functions are: a) to map logical address space into the physical address space and b) to check each memory reference for consistency with the attribute bits assigned to each page.

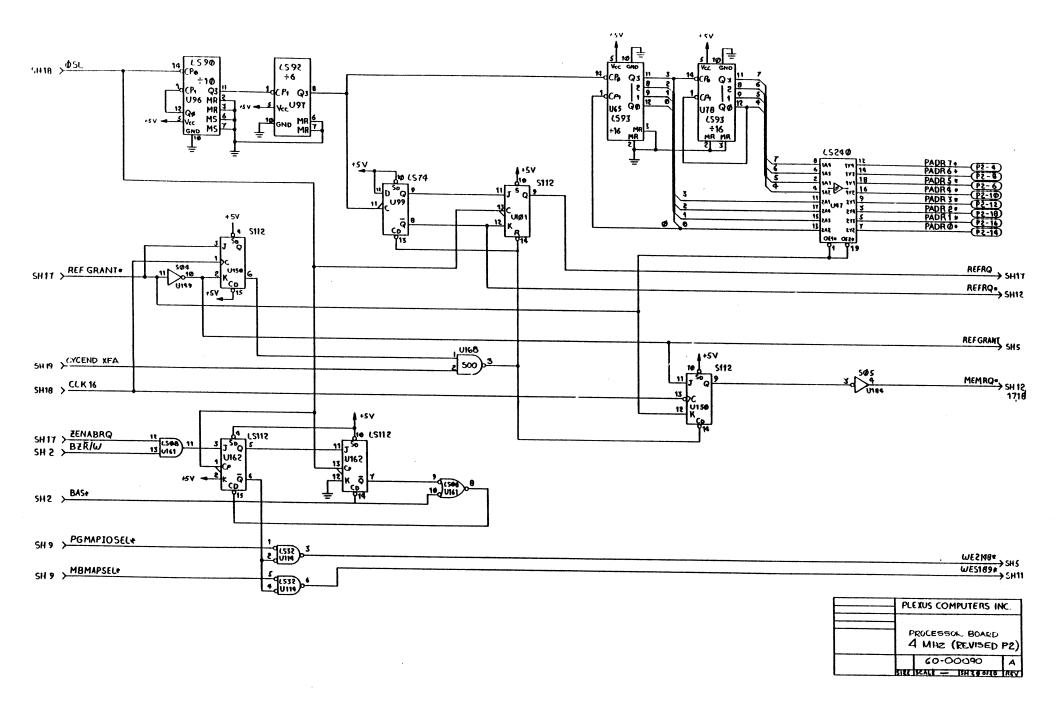

## 2.1. Memory Mapping

## 2.1.1. Address Mapping Scheme

Address mapping allows the P/25 to distinguish between logical and physical memory addresses. A physical address is an actual location in the memory array. A logical address is a location within a program whose physical address is relative to the physical address at which the program started. For example, logical address 132 in a program stored beginning at physical address 16000 is at physical address 16132.

The page mapper acts like a file clerk, placing logical files in physical locations and remembering where they are located. All programs and processes are mapped; the only direct access of physical memory occurs during powerup.

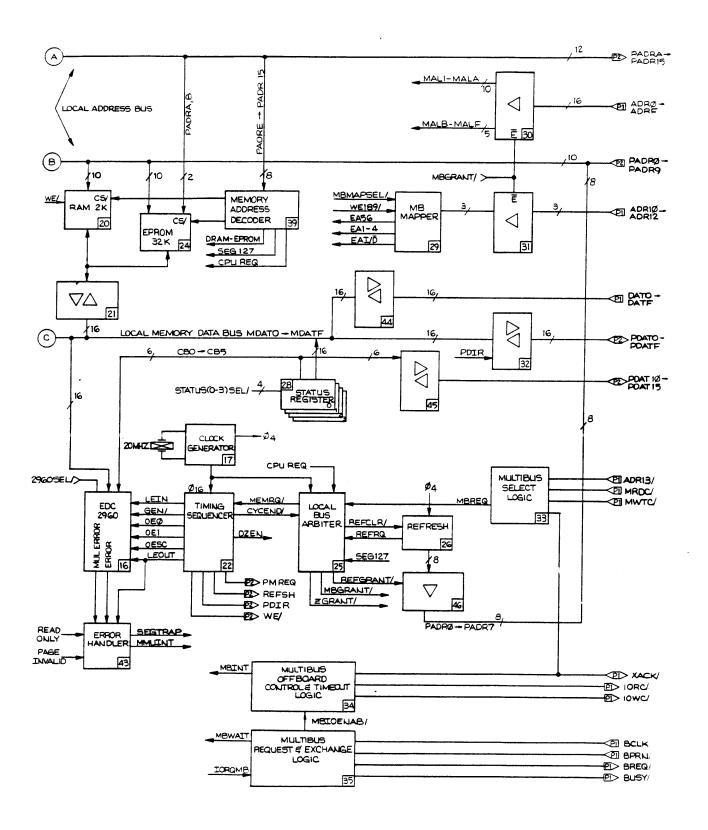

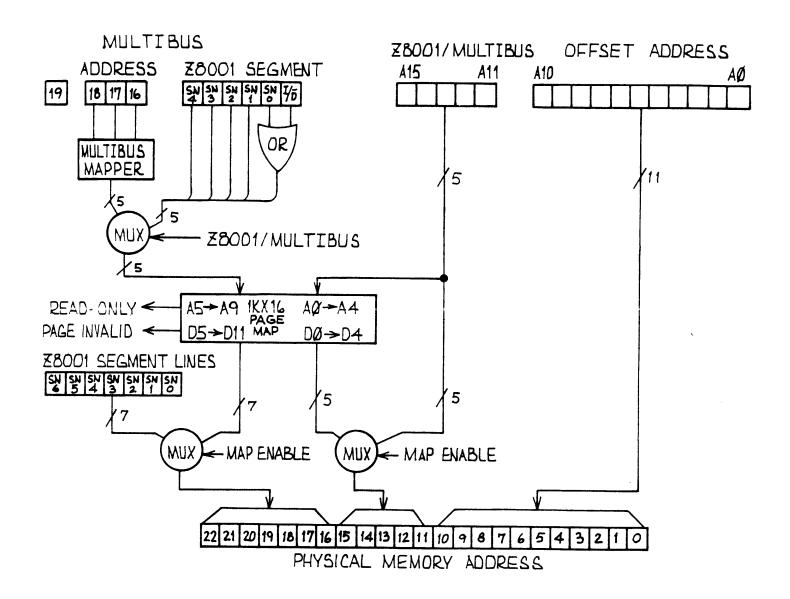

When the Z8001A is accessing memory, the lower five segment lines (SNO to SN4) and the five highest offset address lines (A15 to All) are input to the page map RAM, which produces the 12 high-order bits of the physical address. The lower five segment lines select one of 32 page maps, and the high five offset address lines select pages within the map. Each map contains from one to 32 pages, and each page contains 2K bytes of memory. The address within each page is selected by the lower 11 offset address lines (A0 to A10), which are unchanged by the page-mapping process.

The lowest segment line (SNO) is ORed with the Z8001A instruction/data line (ST2), so that while in instruction mode, only odd-numbered map sets can be accessed. This way, a program running in unsegmented mode (i.e. a system program) can access a user program but a user program cannot change a system program. This allows several user programs to use the same system program without being able to change it.

The Multibus accesses memory through the Multibus map RAM, which can select one of eight page maps. The output of the Multibus map RAM is used in place of the segment lines (and  $\mbox{I/D}$  bit) as input for the page map RAM.

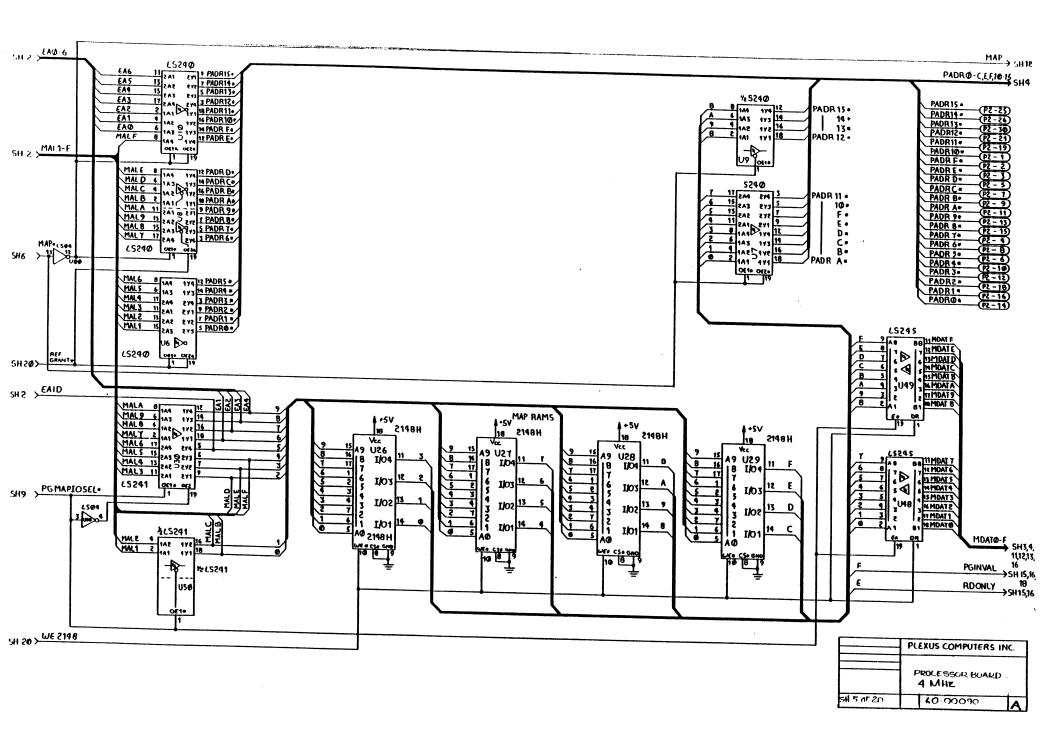

Both arrangements are shown in Figure 3.

A typical process or program requires two map sets; one pointing to instructions and one pointing to data. The minimum memory for a single program is 4K bytes and the maximum is 128K bytes (2K to 64K for instructions and 2K to 64K for data). Up to 16 processes can be resident in memory simultaneously.

Several processes can execute the same program simultaneously. When this occurs, they share the same physical instruction space but each has its own data space and its own map set. Each map points to the same instructions in physical memory and to a separate data space in physical memory.

### 2.1.2. Powerup And Reset

When the P/25 is powered-on or reset, the MMU is disabled and physical memory addresses are generated by concatenating sixteen Z800lA address lines to the seven segment lines. This is required since the Z800lA starts loading the program counter and control word from address 2 in segment 0.

# 2.1.3. Programming Information

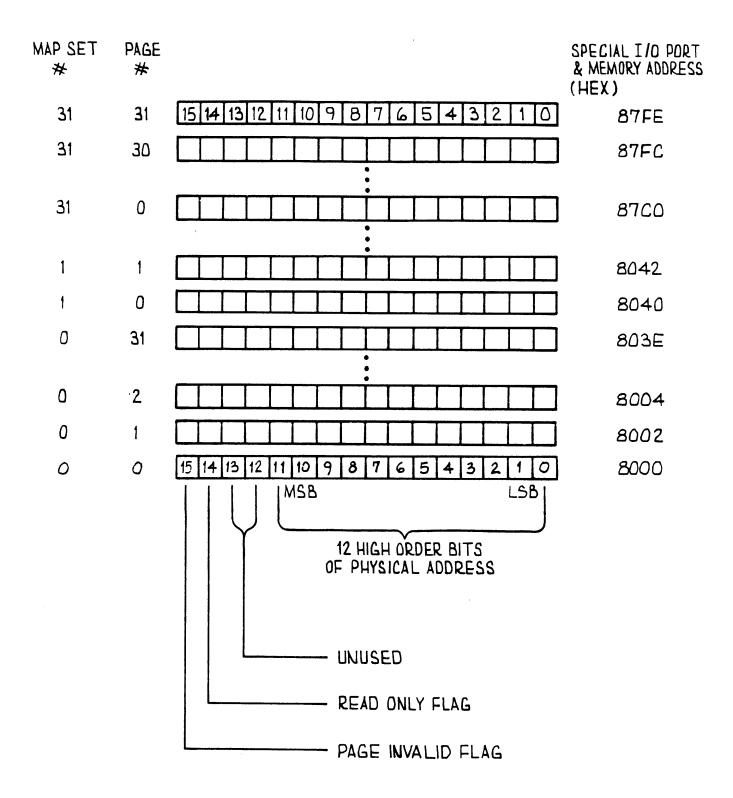

Before enabling the MMU, the Z800lA must load the page map RAM using either special I/O instruction or memory instructions. The page map appears as 1024 contiguous 16-bit ports which can be read or written using special I/O instruction. These ports are located at even addresses from 8000H to 87FEH. The same map location can also be addressed as 1024 contiguous word memory locations between 8000H and 87FEH in segment 127. Logically, these addresses can be thought of as 32 map sets each containing 32 pages, as shown in Figure 4.

Like the page map, the Multibus map must be loaded by the Z8001A before any controllers can access memory through the MMU. This map appears as eight contiguous 8-bit special I/O ports from FF88H to FF8FH. The format of the Multibus map is shown in Figure 5.

After the Multibus map has been loaded, the CPU enables the map by performing a special output to port FF90H.

The Z800lA can prevent Multibus controllers from accessing memory by writing to port FF98H. However, this is not necessary when the Z800lA is changing the page map or the Multibus map.

### 2.2. Memory Protection

The MMU checks each memory reference to ensure that it is consistent with the attribute bits assigned to the page. Each page can be assigned a read-only and an invalid status. If a page has its read-only bit set, the Z8001A or Multibus controllers cannot write to that page. The invalid bit indicates that the page is not resident in physical memory. In the event of an illegal memory reference, the action taken by the MMU depends on the current memory cycle and map attribute bits as follows:

| Z8001A=0<br>Multibus=1 | S=0<br>N= <u>1</u> | R=1<br><u>W=0</u> | Read<br>Only | Page<br>Invalid |                                               |

|------------------------|--------------------|-------------------|--------------|-----------------|-----------------------------------------------|

| 0                      | 0                  | 0                 | 0            | 1               | Generate segment<br>trap                      |

| 0                      | 0                  | 0                 | 1            | 1               | Generate segment<br>trap and inhibit<br>write |

| 0                      | 0                  | 1                 | -            | 1               | Generate segment<br>trap                      |

| 0                      | 1                  | 0                 | 1            | 0               | Generate segment<br>trap and inhibit<br>write |

| 0                      | 1                  | 0                 | 0            | 1               | Generate segment trap                         |

| 0                      | 1                  | 0                 | 1            | 1               | Generate segment<br>trap and inhibit<br>write |

| 0                      | 1                  | 1                 | -            | 1               | Generate segment trap                         |

| 1                      | 1                  | 0                 | 1            | 0               | Generate interrupt and inhibit write          |

| 1                      | 1                  | 0                 | 0            | 1               | Generate interrupt                            |

| 1                      | 1                  | 0                 | 1            | 1               | Generate interrupt and inhibit write          |

| 1                      | 1                  | 1                 | -            | 1               | Generate interrupt                            |

If the illegal reference was generated by the Z8001A, the MMU asserts the Z8001A segment trap line. If the violation was caused by a Multibus controller, the MMU sends a vectored interrupt (MMUINT) to the Z8001A. Both are handled by the error handler (block 43).

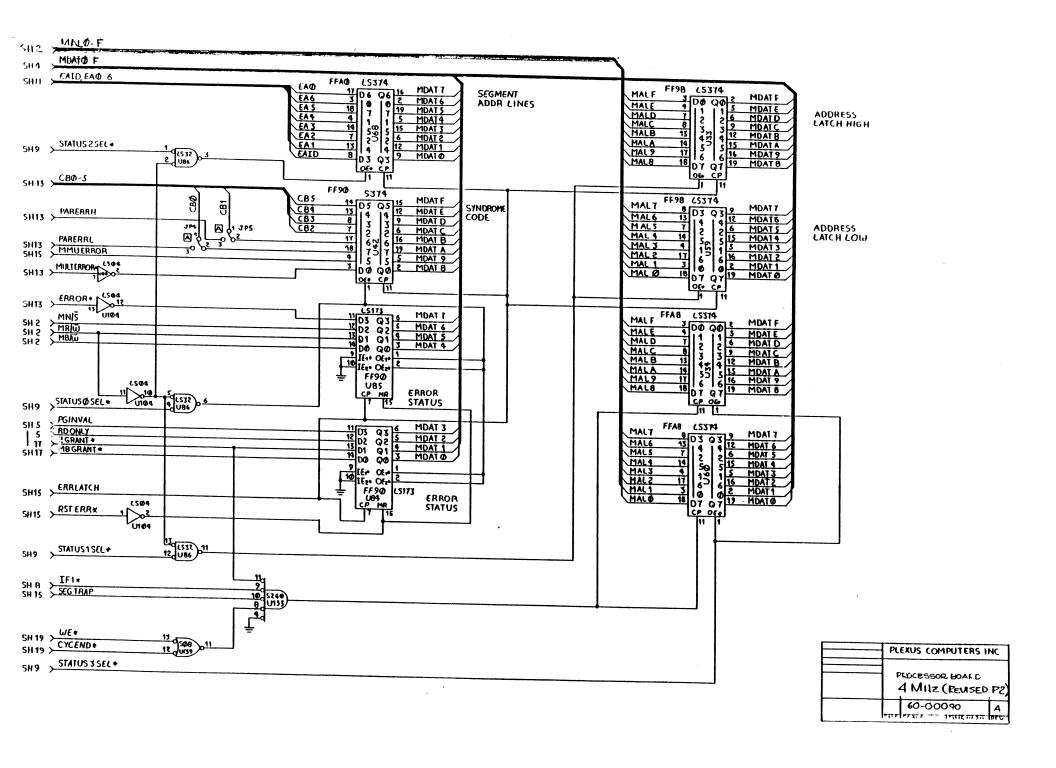

When a memory violation occurs, the following information is stored in latches that can be read by the CPU:

- (a) Address and map set numbers which caused the violation

- (b) Status information

- (c) The address of the first word of the last instruction fetched before the error occurred (Z8001A violations only).

Subsequent errors do not update these latches until the Z8001A resets the error condition by performing a write to port FFA0H. The format and address of this information is shown in Figure 11.

# 2.3. MMU Circuit Analysis

The MMU is shown in Figure 1 as blocks 3, 4, 8, 9, 13, 14, 15 and 41.

# 2.3.1. Normal Operation

The lower five segment lines and the highest five offset address lines are input to the page map RAM, where they select a page map entry. The page map RAM outputs a 12-bit physical memory address which passes through the buffer in block 15 to reside on connector P2. The offset address passes through block 14 to also reside on connector P2. During normal operation (in map mode), blocks 14 and 15 are enabled and block 13 is disabled. During reset (nonmap mode), block 13 is enabled and the physical address passes to connector P2 without changing.

NOTE: The ll-bit offset leaves block 4 with only 10 bits. The llth (low-order) bit is always a zero, which places it on a word boundary.

# 2.3.2. Loading and Reading the Page Map RAM

The page mapper is a high-speed static RAM with 55-nsec access time.

When the Z8001A wants to load or read the page map RAM, it issues a memory reference to segment 127. The memory address decoder

(block 39) generates a SEG127 signal (active high, U152 pin 10) which prevents the local bus arbiter from pulling MEMRQ/low. (A memory cycle won't be started.) Instead, the peripheral interface controller (block 10) decodes the offset address and generates the PGMAPIOSEL/signal (U166 pin 6). The static RAMs in the page mapper are selected and a read or a write operation is performed. The MMU controller is responsible for generating WE2148/ (sh 20) and CYCENDIO/ (sh 9). CYCENDIO/ signals the end of a cycle to the local bus arbiter.

When the page mapper is accessed as special I/O ports, the above sequence is the same except that the SEG127 signal stays inactive (LOW).

The Multibus mapper is a high-speed bipolar RAM inverting memory (74S189) which must be loaded with complemented (inverted) data. The Z8001A can only write to the Multibus map; the contents in the Multibus map are not readable. The MMU controller generates WE189/ (sh 20), CYCENDIO/ (sh 9) and the peripheral interface controller generates MBMAPCS/ (sh 9) to perform a Multibus map write operation.

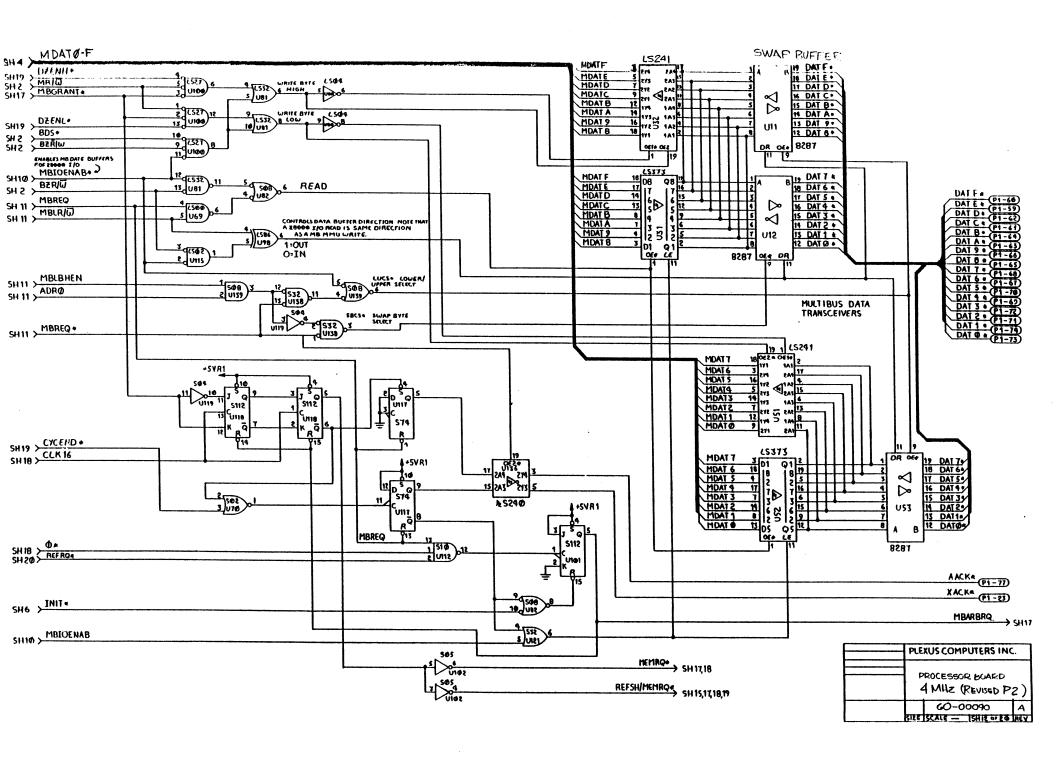

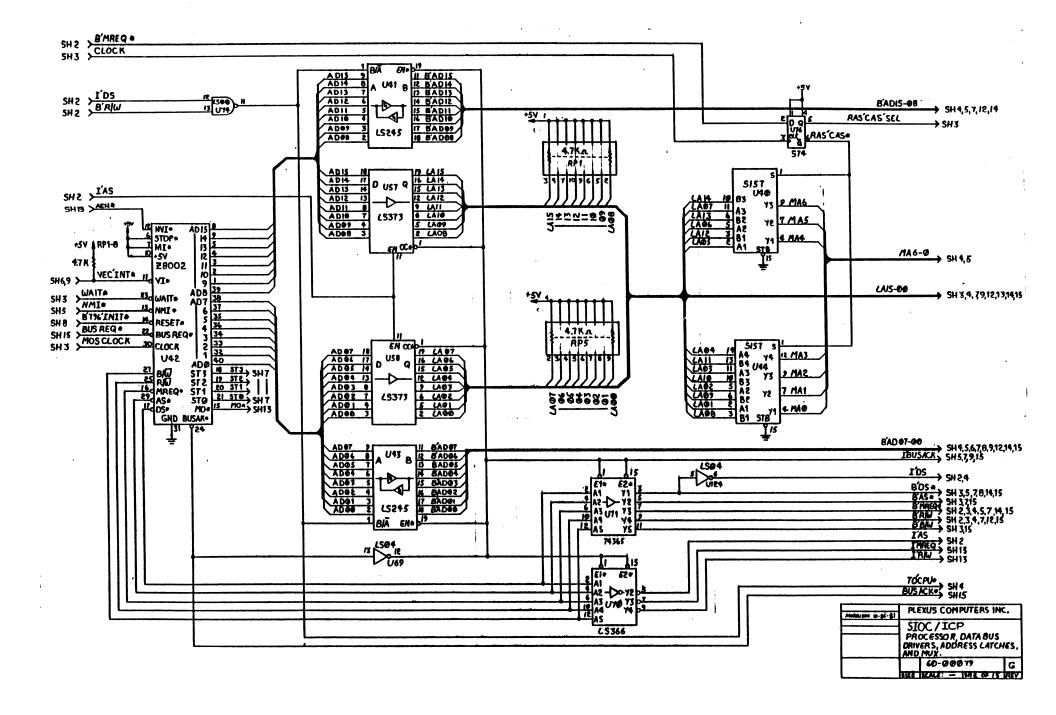

## 2.4. Address Latches and Bidirectional Data Buffers

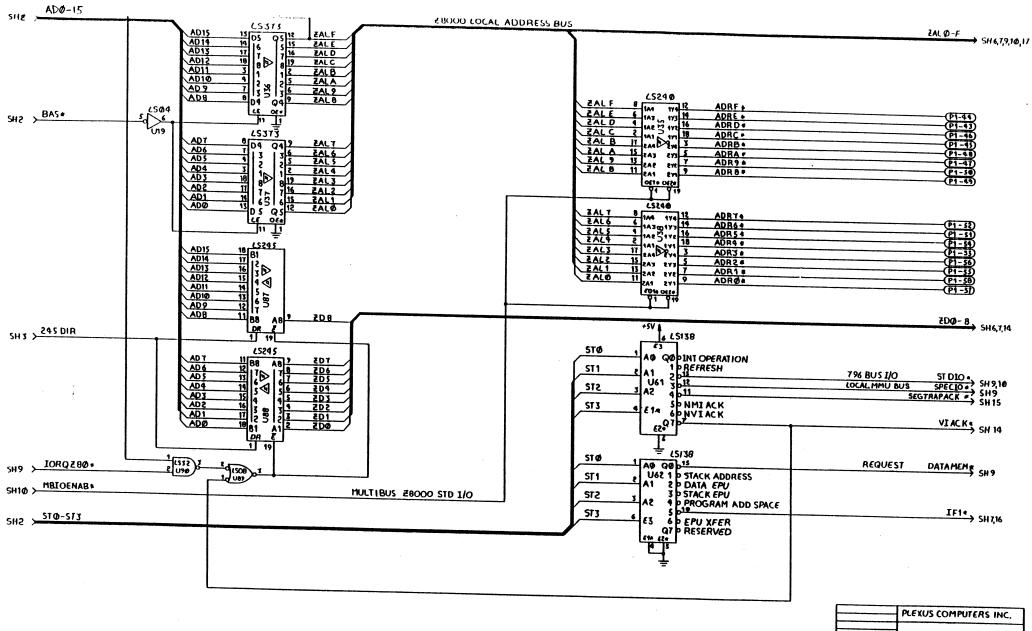

Four local buses are provided on the processor board. These are the:

- (a) Multiplexed Address/Data Bus (MA/D) -- Passes data between the Z8001A and the other local buses through the buffers in blocks 3, 4, 5 and 7.

- (b) Local Peripheral Bus -- Passes data between the peripheral devices on the processor board and the MA/D bus.

- (c) Local Address Bus -- Passes data between the MMU, local memory and system memory. These leave the board in two groups; PADR 0 to PADR 9 and PADR A to PADR 15.

- (d) Local Memory Data Bus -- Passes data between the MA/D bus (through buffer block 5), the page mapper (block 8) and the Multibus data lines (DAT 0 to DAT F) or the system memory data lines.

All address lines from the multiplexed address/data bus to the other local buses are latched at the trailing edge of AS/. Blocks 3 and 4 latch the logical segment lines and offset address lines from the Z8001A. Block 6 latches the I/O port address to select local peripherals. Block 5 contains the 16-bit bidirectional buffers between the multiplexed address/data bus and the local memory bus. These communicate between the Z8001A

and system memory (or the Multibus). Block 7 contains the data buffers to communicate with peripherals on the processor board.

### 2.5. Wait-State Generator

Whenever a Z8001A read/write cycle cannot be completed within a period of three clock cycles, the wait-state generator (block 40) pulls WAIT/ line LOW and inserts a proper number of wait-states to finish the cycle. In the Z8001A, I/O transactions are at least four clock cycles long. The wait-state is not inserted when local peripherals are being accessed. The number of wait-states inserted for different types of Z8001A cycles are listed below:

EPROM and static RAM read or write 1

Byte write to dynamic RAM 1

Multibus I/O port read or write 20 usec max

# 2.6. Status Latches and Decoder

The read-write (RW/), byte-word (BW/) and system-normal (SN/) control lines are latched by the status latch decoder (block 2). It also decodes the status lines (STO to ST3) to generate the following signals:

DATAMEM -- Data memory

STDIO -- Standard I/O

SPECIO -- Special I/O

VIACK -- Vectored interrupt acknowledge

SEGTRAPACK -- Segment trap acknowledge

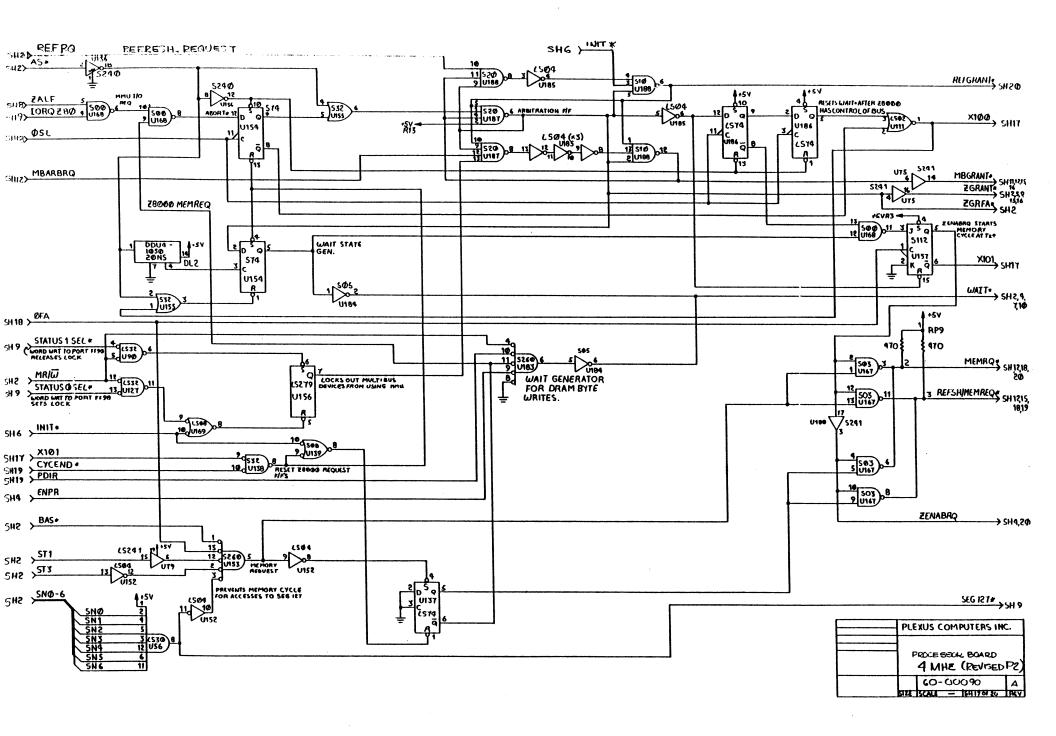

# 2.7. Memory Access Arbitration

The local bus arbiter receives requests for main memory from the CPU through the CPUREQ line (see the processor schematics, page 17, U55, pin 6), from Multibus controllers through the MBREQ line (see the schematics, page 12, U105, pin 5) and for refresh from the REFREQ line (see the schematics, page 20, U101, pin 9). On a first-come-first-served basis, the arbiter asserts the grant line (ZGRANT, MBGRANT or REFGRANT) to the winning device. When requests from two different devices are received, the arbiter interleaves the GRANT outputs in the following order: Z8001A,

refresh and Multibus.

#### 3. LOCAL PERIPHERALS

#### 3.1. Introduction

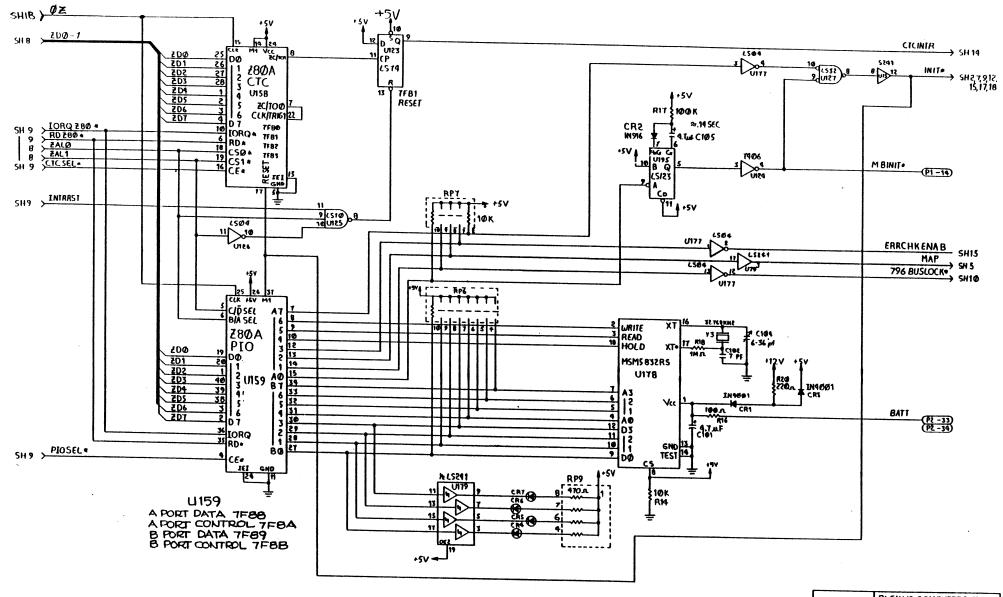

The peripherals on the processor board include a parallel input/output controller (Z80-PIO), a counter/timer circuit (Z80-CTC) a realtime clock, a master and slave programmable interrupt controller (PIC) and a diagnostic port (USART). The board also includes four LEDs and a selector switch (4 STSP DIP).

NOTE: Older processor boards (4-Mhz) are equipped with a floating-point processor. This has been replaced with software on the newer (5-Mhz) boards.

All local peripherals communicate with the Z800lA via the local peripheral bus and are addressed as ports in the Z800lA special I/O address space. The port addresses (in hexadecimal) are as follows:

PIO -- 7F88 to 7F8F

CTC -- 7F80 to 7F87

Realtime clock -- Controlled by PIO

Master PIC -- 7F90 to 7F97

Slave PIC -- 7F98 to 7F9F

USART -- 7FA0 to 7FA7

Status Switches -- 7FA8 to 7FAF

## 3.2. Peripheral Interface Controller

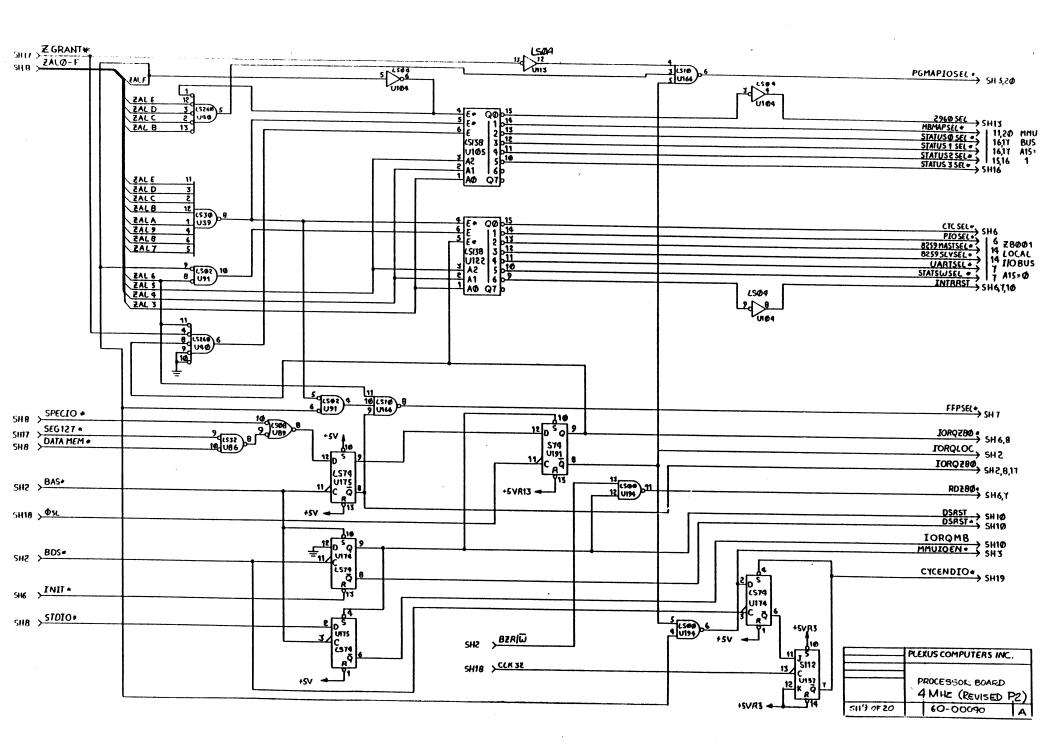

The peripheral interface controller generates chip-select signals and control logic for various peripheral devices on the processor board. It is actually a collection of chips, most of which are shown on page 9 of the processor shcematics. It appears in Figure 1 as block 10.

The peripheral interface controller reads the address/data lines (ADO to ADF) and the AS/ and DS/ signals from the Z8001A. When it sees the address of a chip under its control, it generates the proper chip-select signal (SEL), using the AS/ and DS/ to ensure proper timing.

It uses the R/W signal from the Z8001A to generate RDZ80/ which causes the CTC, PIO and USART to read when it goes low. It also generates IORQZ80/ which the CTC and PIO use for their IORQ/ inputs.

The following table shows the chip-enable signals and the devices they control:

| <u>Device</u>                                                                              | <u>Signal</u>                                                                                                    |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| CTC PIO Master PIC Slave PIC USART Status Latches Multibus Map Page Map Error Detector (ED | CTCSEL PIOSEL 8259MASTSEL 8259SLVSEL UARTSEL STATUSOSEL to STATUS3SEL and STATWSEL MBMAPSEL PGMAPIOSEL ) 2960SEL |

# 3.3. Parallel Input/Output (PIO) Controller

The Z800lA controls various local functions through the PIO chip. The PIO has three 8-bit ports. One port communicates with the Z800lA through the local peripheral bus. The other two ports (A and B) connect to the devices controlled by the PIO.

Port A is set for output only; the PIO receives instructions from the Z8001A and outputs the data it receives on Port A. Port B is programmed for input and output; the PIO receives instructions from the Z8001A and outputs them on port B, but port B also receives data and outputs it to the Z8001A. The port assignments are shown in the following table:

NOTE: Port A and B pin assignments are shown on page 6 of the processor schematics.

| PIO Port A bit | <u>I</u> /0 | Function                  | Active Level |

|----------------|-------------|---------------------------|--------------|

| 0              | 0           | Software Reset            | Low          |

| 1              | 0           | Multibus Lock             | High         |

| 2              | 0           | Enable Memory Map         | Low          |

| 3              | 0           | Enable Error Handler Trap | Low          |

| 4              | 0           | MSM5832 Hold              | High         |

| 5              | 0           | MSM5832 Head              | High         |

| 6              | 0           | MSM5832 Write             | High         |

| 7              | 0           | Z8001A Reset Protect      | Low          |

NOTE: The MSM5832 is the CMOS calender clock chip described in part 3.4. of this section.

| PIO Port B bit | <u>I</u> /0 | Function                 | Active Level |

|----------------|-------------|--------------------------|--------------|

| 0              | I/O         | MSM5832 Data 0 and LED 0 | Low          |

| 1              | I/O         | MSM5832 Data 1 and LED 1 | Low          |

| 2              | 1/0         | MSM5832 Data 2 and LED 2 | Low          |

| 3              | 1/0         | MSM5832 Data 3 and LED 3 | Low          |

| 4              | 0           | MSM5832 Address 0        | N/A          |

| 5              | 0           | MSM5832 Address 1        | N/A          |

| 6              | 0           | MSM5832 Address 2        | N/A          |

| 7              | 0           | MSM5832 Address 3        | N/A          |

Port B, bits 0 through 3 serve a double purpose: they take data from the realtime clock and output it to the Z8001A, and they take data from the Z8001A and output it to the status LEDs. When they are outputting data to the LEDs, the MSM5832 HOLD line is

activated. For more on the status LEDs, see Processor section 1.

#### 3.3.1. Programming Information

To control each PIO output port, the Z800lA must write two instructions. The command instruction determines the mode in which the port operates, and the data instruction supplies the output data. Port A is set to operate in mode 0 (output mode), and port B is set to operate in mode 3 (control mode), because it transfers data in both directions.

Each instruction goes to a unique port address within the PIO address space as follows:

| Port A | Command | 7F8A |

|--------|---------|------|

| Port A | Data    | 7F88 |

| Port B | Command | 7F8B |

| Port B | Data    | 7F89 |

See the Zilog 1981 Data Book, "Z80-PIO Product Specification" for additional information.

#### 3.3.2. I/O Bit Definition

The following PIO lines require special attention:

Port A. Bit 0 (Software Reset) -- The CPU can reset the whole system by pulling this bit low.

Port A, Bit 7 (28001A Reset Protect) -- This bit works with the above bit. If this bit is set low, a software reset clears all I/O boards on the Multibus, but not the processor board.

Port A, Bit 2 (Enable Memory Map) -- When this bit is low, the Z800lA runs in mapped mode.

Port A, bit 3 (Enable Error Handler Trap) -- When this bit is inactive (high), the circuit which generates the segment trap for memory mapping errors or EDC errors is disabled.

Port A, Bit 1 (Multibus Lock) -- After powerup or reset, Multibus controllers are not allowed to access the memory. The Multibus access is permitted only after this bit is set

(active LOW).

## 3.3.3. Counter/Timer Circuit

The CPU uses a four-channel counter-timer (Zilog Z80B CTC) to provide realtime interrupts to the Z800lA. The ZC/TOO output (channel 0) is connected to the CLK/TRG input of channel 1. The ZC/TOl output (channel 1) divides the system clock down to 50 hz. It is used to trigger a flip-flop (Ul23) which asserts the CTCINTR (active HIGH) to cause the interrupt.

The Z800lA resets the interrupts by performing a special I/O write to port 7FBl.

Each Z80-CTC channel must be programmed by the Z8001A prior to operation. It writes two 8-bit words to the desired channel over the local peripheral bus. The first word is the channel control word which sets the operating mode for the channel. The second word is the time constant (see the Zilog 1981 Data Book, "Z8430 CTC Product Specification"). The channel control word for channel 0 consists of the following:

| D0 | 1 | Identifies the control word                                   |

|----|---|---------------------------------------------------------------|

| Dl | 1 | Software reset enabled                                        |

| D2 | 1 | Time constant follows                                         |

| D3 | 0 | Timer is triggered automatically when time constant is loaded |

| D4 | 0 | Falling edge triggered                                        |

| D5 | 0 | Prescaler value = 16                                          |

| D6 | 0 | Timer mode                                                    |

| D7 | 0 | Interrupt disabled                                            |

Channel 1 is programmed the same as channel 0 except that it operates in counter mode (D6 is set to 1).

#### 3.4. Realtime Clock

A clock calendar gives the CPU access to the time of day in hours, minutes and seconds, and also to the day, month and year.

This battery-operated circuit has its own crystal oscillator and remains running even when AC power is removed. The battery is automatically charged whenever the system is operating. It powers the clock for three months between charging.

The clock calendar function is provided by a MSM5832 CMOS clock circuit. This circuit inputs its data to the PIO, which passes it to the Z8001A over the local peripheral bus. Its address, data and control lines are listed in the Processor section, part 3.2.

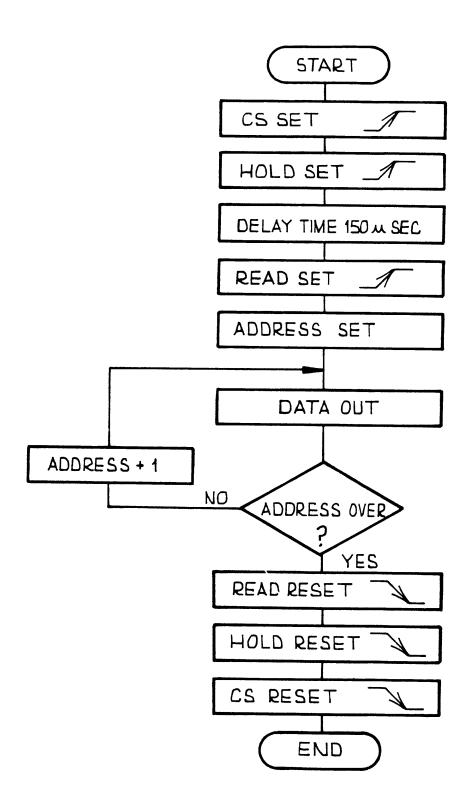

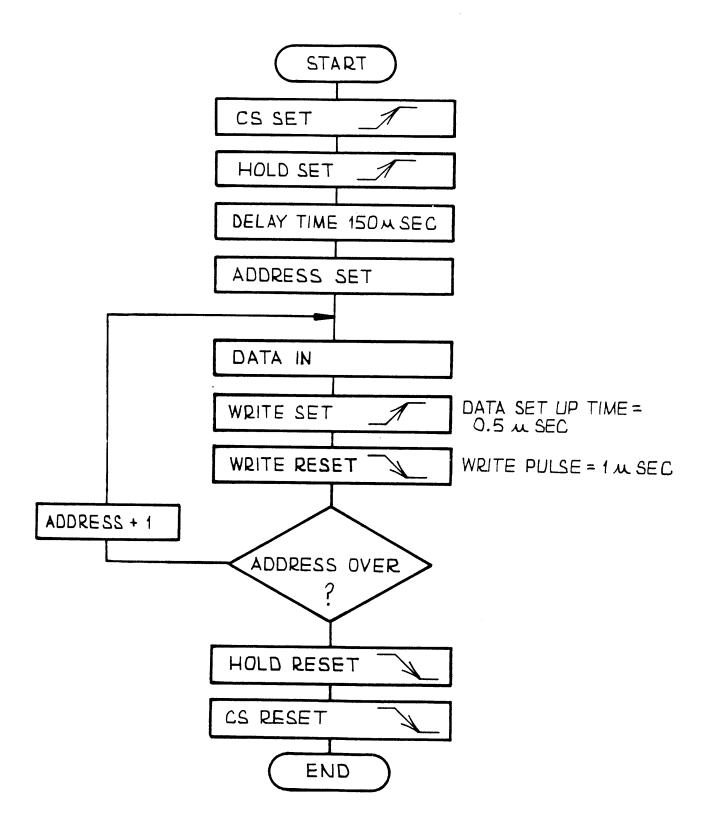

Figures 6 and 7 show the PIO/realtime clock circuit read/write timing requirements (see OKI Semiconductor MSM5832 Microprocessor Realtime Clock/Calender Product Specification).

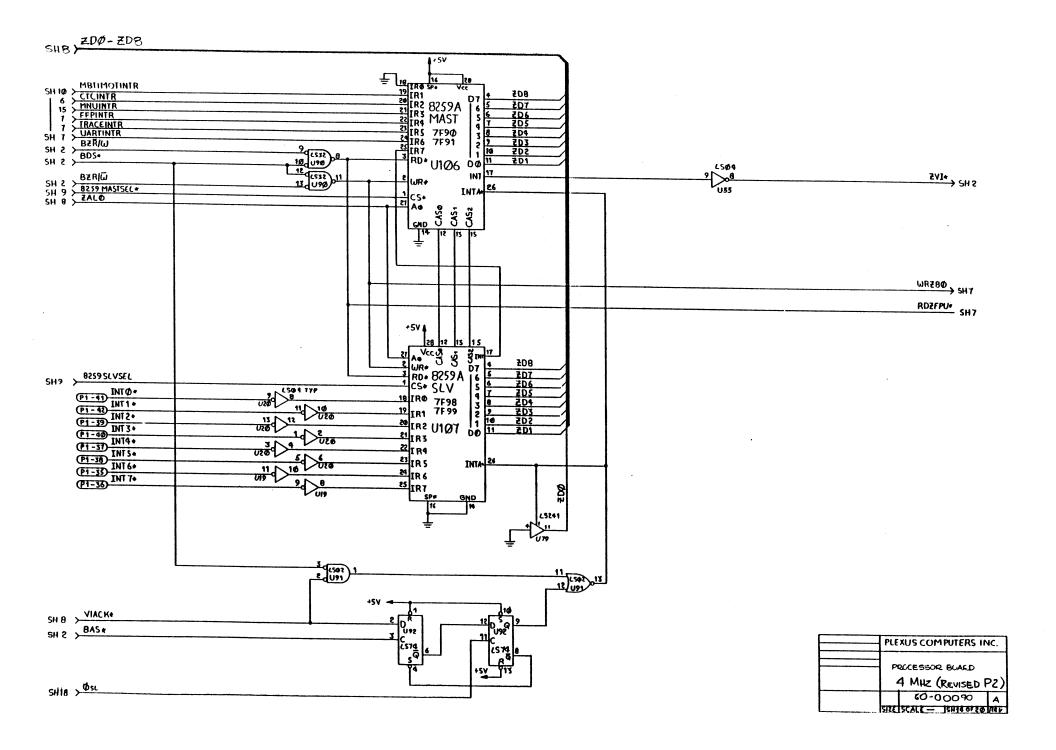

# 3.5. Programmable Interrupt Controller (PIC)

The vectored interrupt structure in the P/25 is handled by two Intel 8259A PICs. One functions as the master PIC, the other the slave PIC. The master PIC (page 14, U106) accepts interrupt requests from onboard peripherals. The slave PIC (page 14, U107) accepts interrupt requests from Multibus I/O controllers.

The basic functions of the PICs are to: a) accept interrupt requests, b) determine the priority of interrupt requests, c) assert a vectored interrupt to the Z800lA based on priority and d) provide the interrupt vector to the interrupt service routine.

In the P/25, there are 14 levels of interrupt priority, assigned as follows:

## MASTER PIC

|      | Priority | <u>Function</u>             |

|------|----------|-----------------------------|

| High | 0        | Unused                      |

|      | 1        | Multibus watchdog timer     |

|      | 2        | CTC clock                   |

|      | 3        | Multibus MMU error          |

|      | 4        | Unused*                     |

|      | 5        | Trace, normal address space |

|      | 6        | USART interrupt             |

| Low  | 7        | Cascade from slave PIC      |

<sup>\*</sup> In older (4-Mhz) systems, priority 4 is assigned to the floating point processor.

## SLAVE PIC

|      | Priority | Function                   |

|------|----------|----------------------------|

| High | 0        | Multibus interrupt (INTO/) |

|      | 1        | " (INT1/)                  |

|      | 2        | " (INT2/)                  |

|      | 3        | " (INT3/)                  |

|      | 4        | " (INT4/)                  |

|      | 5        | " (INT5/)                  |

|      | 6        | " (INT6/)                  |

| Low  | 7        | Multibus interrupt (INT7/) |

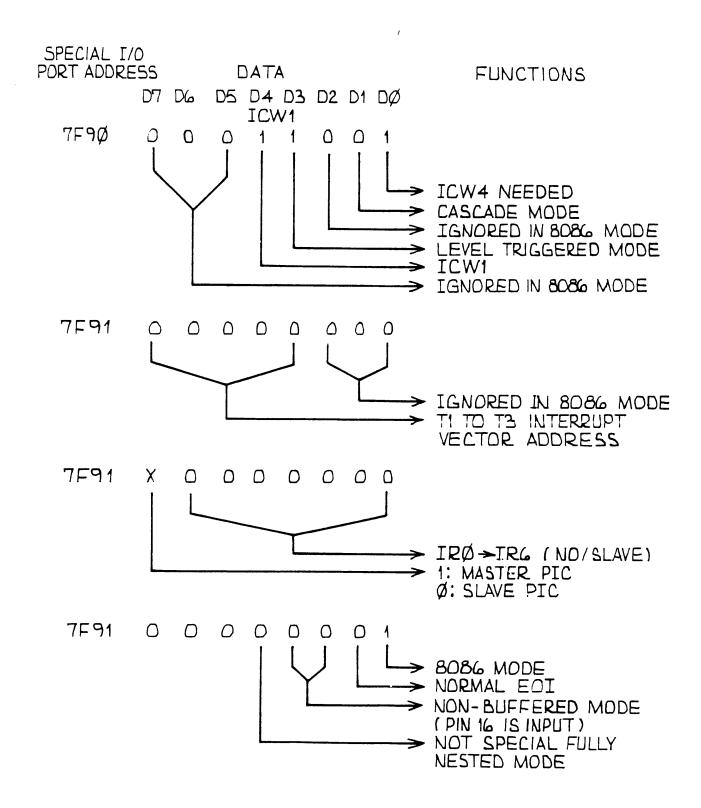

<sup>\*</sup>S3 "Programming Information" The Intel 8259A PIC requires

initialization programming before it can process interrupt requests. The initialization sequence involves two to four bytewrites to each PIC. In the P/25, the initialization command words (ICWs) are issued as shown in Figure 8 (see the Intel 8259A Programmable Interrupt Controller Product Specification).

Since the PIC is not programmed in the automatic-end-of-interrupt (AEOI) mode, each individual interrupt service routine is required to issue a nonspecific end-of-interrupt command to clear the in-service bit in the corresponding PIC.

# 3.5.1. Circuit Analysis

The vectored interrupt cycle proceeds as follows:

A local peripheral device or a Multibus master requests an interrupt by asserting an interrupt line on one of the PICs.

The PIC determines the priority of the interrupt (see interrupt priority table above).

The PIC asserts the Z8001A VI/ line.

The Z800lA waits until it reaches an interruptable point, then starts an interrupt cycle by sending the proper status to the status latch decoder (block 2), which sends VIACK/ to the interrupt acknowledge handler (block 42).

The interrupt acknowledge handler outputs the first INTA/pulse, which lasts for one clock cycle. This pulse causes the PIC to freeze the state of priority resolutions and causes the master PIC to issue an interrupt code to the slave.

The second INTA/ pulse. which is actually a copy of the DS/ signal from the Z8001A, causes the PIC to output the interrupt vector on the local peripheral bus. This is the end of the PIC's involvement.

The Z8001A reads the vector on ADO to AD8. It goes to the vector indicated and executes the instructions there.

The high five bits of the 8-bit vector are common to all eight interrupt request lines on a given PIC. They define a memory location where an interrupt instruction table is located. The lower three bits carry the code (0 to 7) for the interrupt. These bits define the table entry specific to each interrupt.

Since the Z8001A requires all vectors to be on even boundaries (bit 0 must be zero), the PIC lines are shifted one bit, so that

data line 0 from the PIC connects to data line 1 of the local peripheral bus; PIC line 7 connects to peripheral bus line 8. Data line 0 is only pulled LOW during an interrupt acknowledge cycle. This has the effect of placing the interrupt vector produced by the PIC on an even boundary. It also implies that when the PIC is read or written, the data must be shifted one bit to the left.

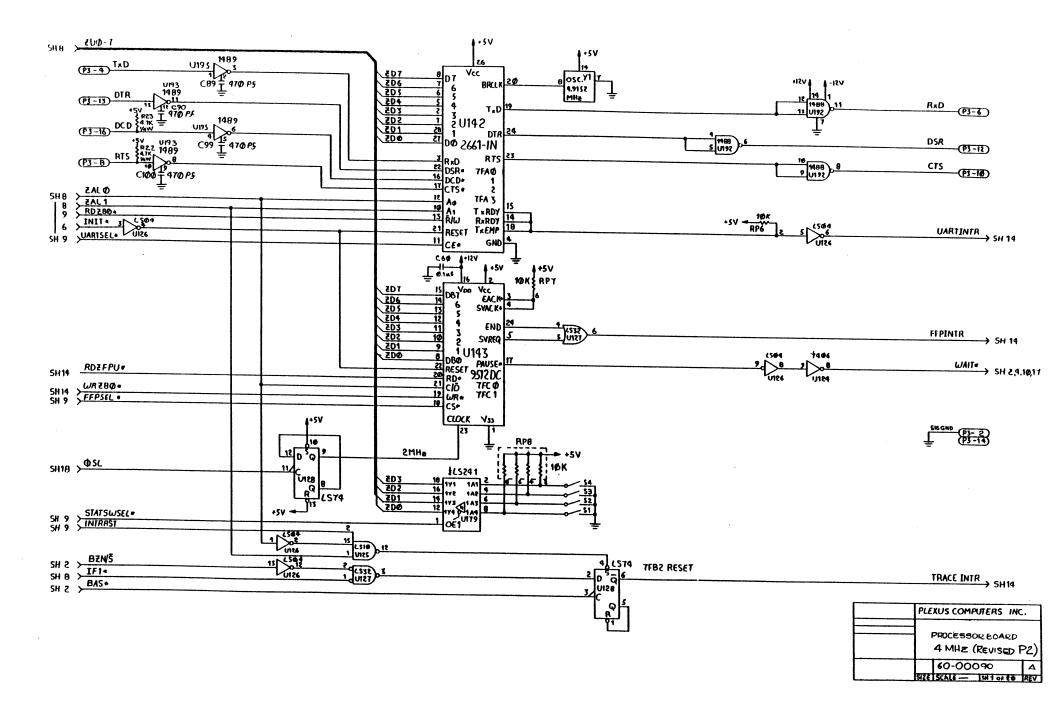

## 3.6. Diagnostic Port

The diagnostic console is supported by an industry-standard RS232C port (USART) attached to connector P3. The following table shows the EIA RS232C pins supported when a terminal is connected to P3. (If a modem is attached, the pins are identical to the ICP SIO pins -- see the Input/Output Controller section in this manual):

| RS232C Pin | I/O | <u>Name</u> | 2661 Pin | Function                              |

|------------|-----|-------------|----------|---------------------------------------|

| 2          | I   | TxD         | RxD      | Serial data from terminal             |

| 3          | 0   | RxD         | TxD      | Transmitted data from diagnostic port |

| 20*        | I   | DTR         | DSR      | General purpose input                 |

| 6          | 0   | DSR         | DTR      | General purpose output                |

| 8          | I   | DCD         | DCD      | General purpose input                 |

| 5          | 0   | CTS         | RTS      | General purpose output                |

| 4 *        | I   | RTS         | CTS      | General purpose input                 |

| 7          | -   | Ground      |          | Signal ground                         |

| 1          | _   | Ground      | -        | Protective ground                     |

<sup>\*</sup>These pins must be enabled (held high) for the UART to operate.

This connector is set up to connect directly to a terminal; data modems require a null modem cable.

The diagnostic (console) port consists of a Signetics 2661 enhanced programmable communication interface (EPCI) and RS232C

transceivers. The EPCI is a universal synchronous/asynchronous data communication controller chip which can support various communication protocols. It contains a baud rate generator which can generate 16 different baud rates between 50 and 19,200 baud. The 2661 EPCI's TxRDY (Transmitter Ready), RxRDY (Receiver Ready) and TxEMP (Transmitter Empty) interrupt lines are all ORed together to create a single vectored interrupt to the Z8001A.

The diagnostic terminal baud rate is selected by three of the switches described in the Processor section, part 1.5.

## 3.6.1. Programming Information

The port addresses assigned to the registers in the 2661 EPCI are as follows:

| Port Address | Function                                    |

|--------------|---------------------------------------------|

| 7FA0H        | Data holding register                       |

| 7FA1H        | Status register<br>SYN1/SYN2/IDLE registers |

| 7FA2H        | Mode register 1                             |

| 7FA2H        | Mode register 2                             |

| <b>7FA3H</b> | Command register                            |

#### 4. MULTIBUS INTERFACE

## 4.1. Introduction

Most P/25 system components communicate with each other over the Multibus backplane, which occupies connector Pl. The exceptions are the memory boards (dynamic RAM), which occupy connector P2. Refer to the <a href="#">IEEE Proposed Microcomputer System Bus Standard (P796 Bus)</a>) for a more complete description of the Multibus.

The processor board can act as a Multibus master or slave. As a master it can access up to 64K 16-bit ports in the standard I/O address space. As a slave, it occupies the upper half of the Multibus logical address space.

The Multibus interface can handle both byte and word transfers on the Multibus.

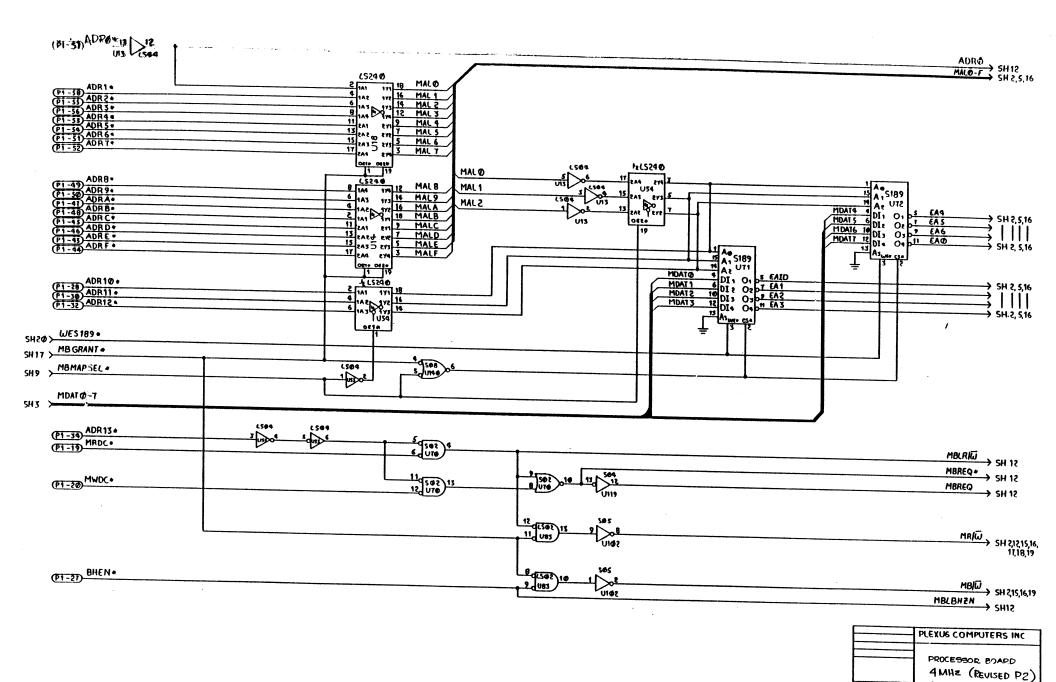

## 4.2. Multibus Memory Access

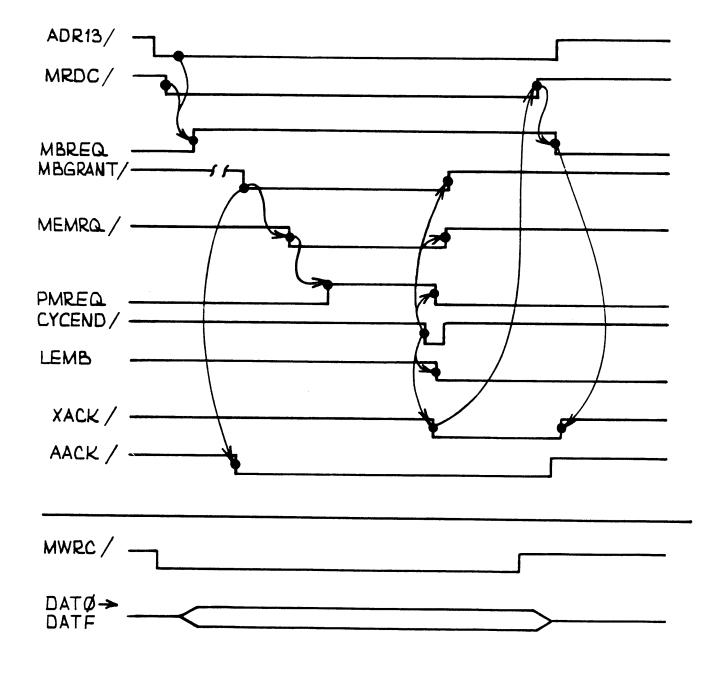

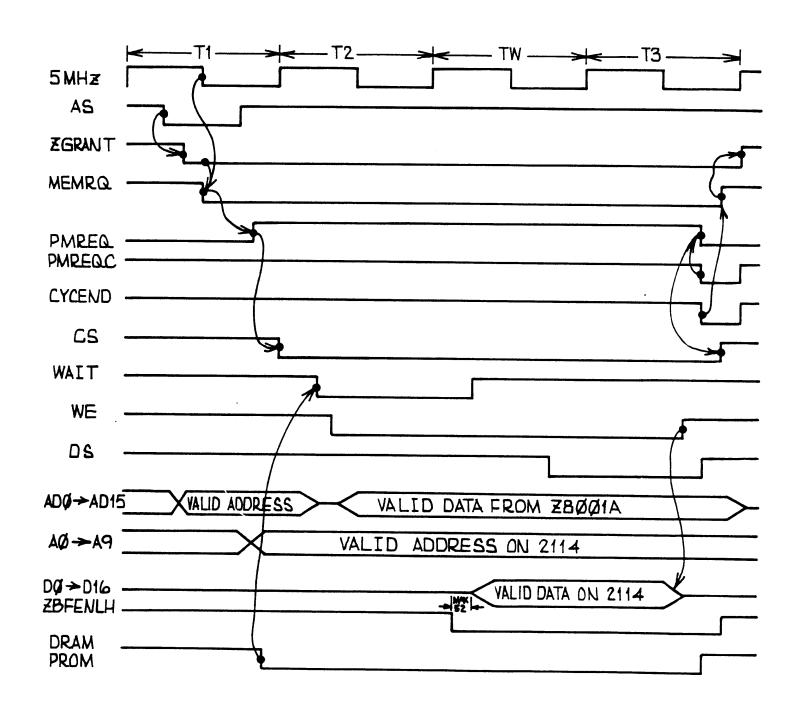

The timing diagram for the Multibus memory access is shown in Figure 9.

A Multibus memory request is recognized when both the most significant address line (ADR 13/) and the control line (MRDC/ or MWTC/) are activated by a Multibus master. Block 33 contains the logic to generate the MBREQ signal (see the processor schematics, page 12) asserts a request for local bus on the processor board. The local bus arbiter grants the request on a first-come-first-served basis by asserting MBGRANT/, which enables blocks 30 and 31. A memory cycle is started as discussed in this manual in the Memory section.

In a Multibus read cycle, data read from the memory is latched into U31 and U52 when the CYCEND/ is asserted. The processor board can start the next memory cycle or onboard I/O cycle without waiting for completion of the Multibus cycle. The XACK/ is asserted on the Multibus (sh 12, U136 pin 5). The Multibus master removes the MRDC/ or MWTC/ command. This ends a complete Multibus cycle.

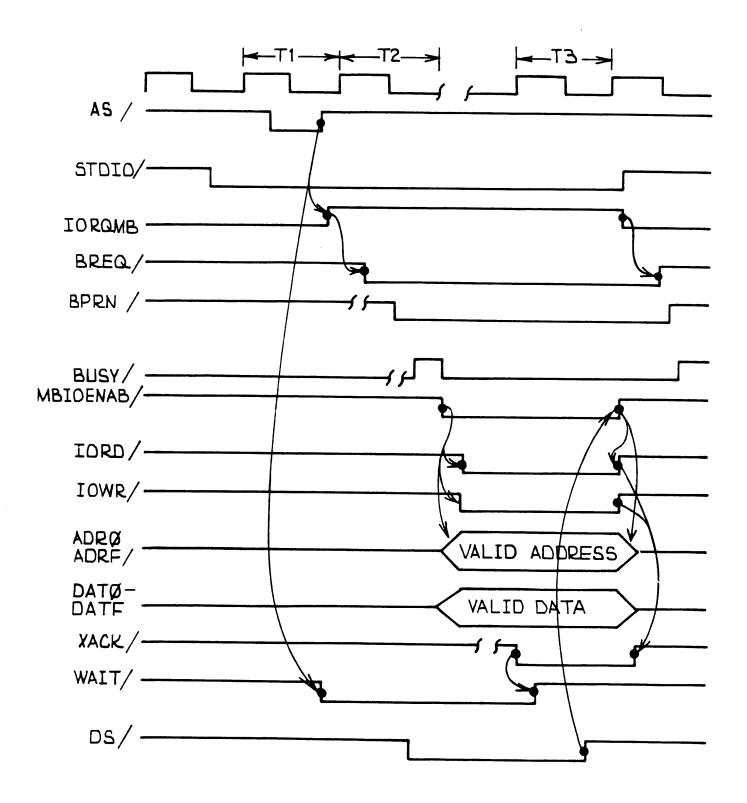

## 4.3. Processor Board Multibus Access

The timing for the processor board Multibus access is shown in Figure 10.

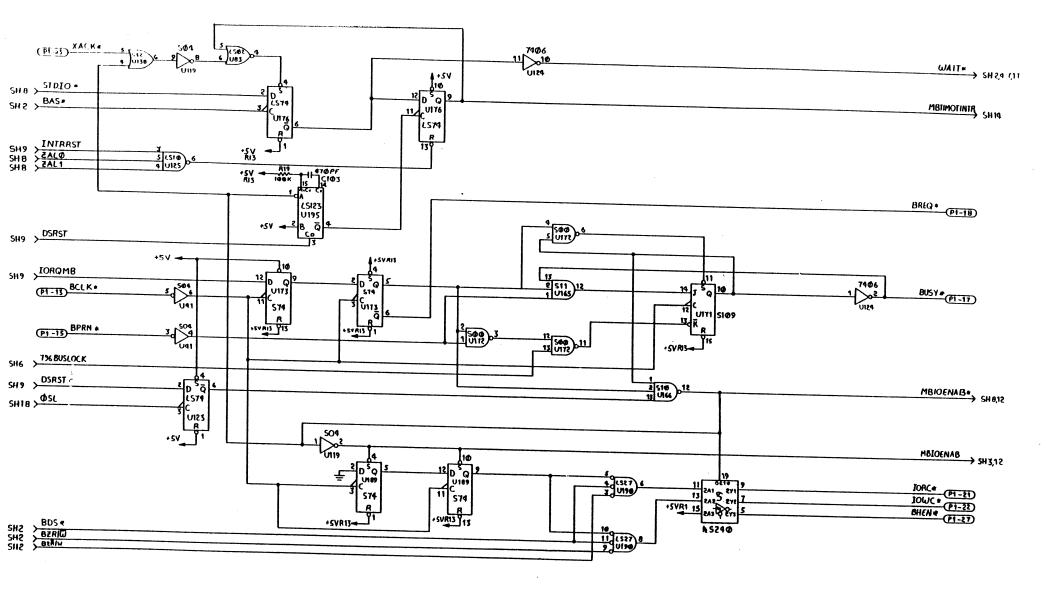

The processor board accesses the Multibus controllers as I/O

ports in the Z8001A standard I/O address space. The access starts when the IORQMB signal (page 9) goes active (HIGH). The IORQMB signal is generated at the rising edge of AS/ when a standard I/O instruction is executed. The synchronization of IORQMB and BREQ/ (Multibus signal) is achieved by flip-flop Ul73 (sh 10).

The Multibus exchange priority logic is located on the backplane. Priority is resolved in a parallel fashion whereby each slot on the backplane has a fixed Multibus access priority. This results in a location-dependent priority scheme.

If the Multibus is free (BUSY/ = high), a Multibus I/O cycle can be initiated immediately. Otherwise, the processor board waits until the current Multibus master relinquishes control of the bus (BUSY/ goes high). When this happens, J-K flip-flop Ul71 (sh 10) pulls the BUSY/ line low, locking out other Multibus masters. The MBIOENAB signal notifies the CPU that the Multibus has been granted. It also enables the data and control buffers (blocks 34 and 36) connected to the Multibus. A Multibus timer starts and the buffers output the address of the Multibus slave to be accessed.

When the slave responds by pulling the XACK/ line low, it sets a flip-flop (Ul76 -- processor schematics, page 10) which pulls the WAIT/ line high. The Z800lA leaves the wait-state and finishes the cycle.

If the slave fails to respond within 20 microseconds, the timer causes a Multibus timeout interrupt to be generated. The Z8001A leaves the wait-state and resets the interrupt by performing a write to I/O port 7FB3H. This ensures that the P/25 cannot be locked due to a failed Multibus card.

The trailing edge of DS/ from the Z800lA triggers the end of a Multibus I/O cycle. ICRQMB, BREQ/, MBIOENAB/, IORD or IOWR/, and address or data go inactive sequentially. The BUSY/ line goes high, freeing the Multibus.

## 5. LOCAL BUS ARBITER AND TIMING SEQUENCER

This section describes the processor board timing logic for the local bus arbiter and the timing sequencer.

In the P/25 processor board, the local address bus and the local memory/data bus are shared by the Z800lA, Multibus controllers and the refresh circuits. The local bus arbiter is designed to handle the sharing of the buses. It arbitrates the buses on a first-come-first-served basis for every memory access. If there is contention, the priority is assigned in the order: Z800lA, refresh and Multibus. The GRANT lines (ZGRANT/, REFGRANT/ and MBGRANT/) signal the winning device.

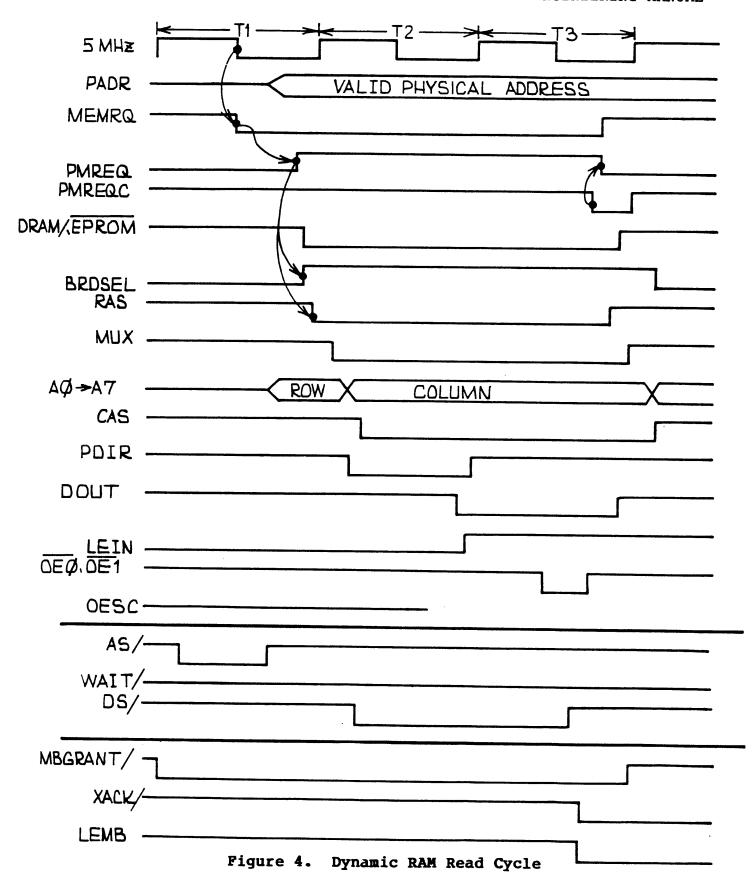

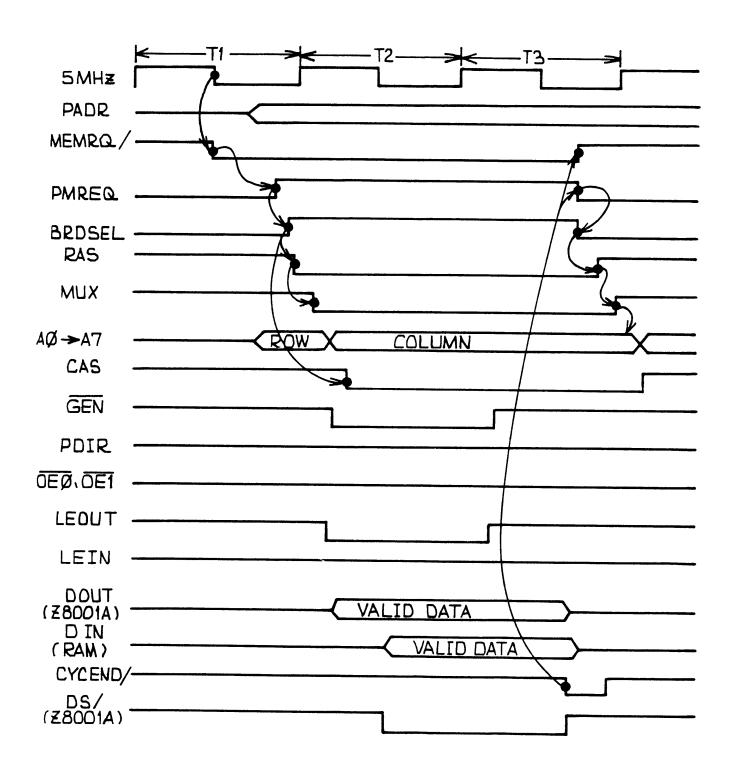

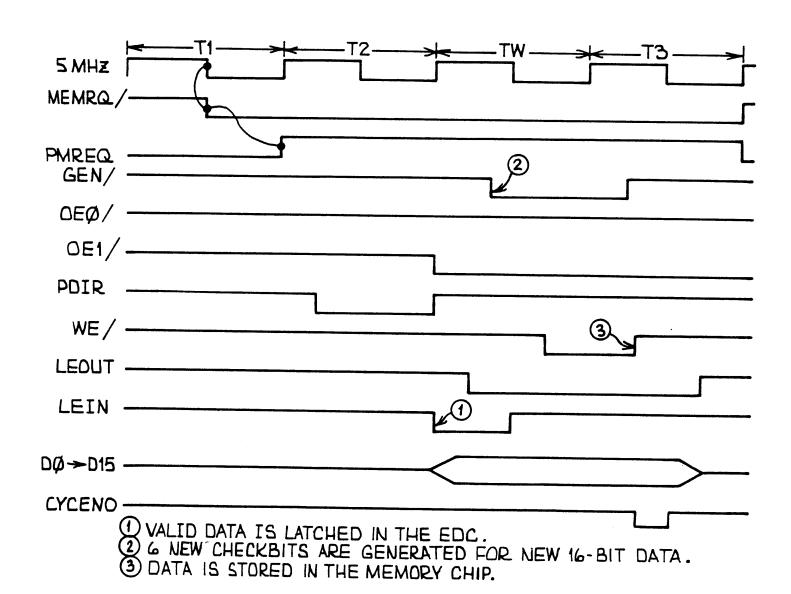

The timing sequencer is designed to generate the proper timing for the different types of memory cycles. For example, the PMREQ starts a memory cycle when a mapped physical address is valid and the LEIN controls the latching of input buffers in the EDC chip.

## 5.1. Local Bus Arbiter

As shown in the block diagram (Figure 1), the local bus arbiter receives: a) the MBREQ signal from the Multibus select logic (block 33), b) the REFRQ signal from the refresh circuits (block 26) and c) the AS/ signal from the Z8001A. The one which is granted memory access has its corresponding GRANT/ line asserted (MBGRANT/, ZGRANT/ and REFGRANT/). These control lines direct the flow of data in the processor board.

The MEMRQ/ and CYCEND/ signals are used to handle handshaking between the local bus arbiter and timing sequencer. The MEMRQ/ starts a memory cycle and CYCEND/ ends a memory cycle.

The local bus arbiter controls six different transitions from one type of memory access to another. These are:

Z8001A to Multibus

Z8001A to refresh

Multibus to Z8001A

Multibus to refresh

Refresh to Z8001A

Refresh to Multibus

The memory transition is synchronized by running the local bus

arbiter with a 20-Mhz clock.

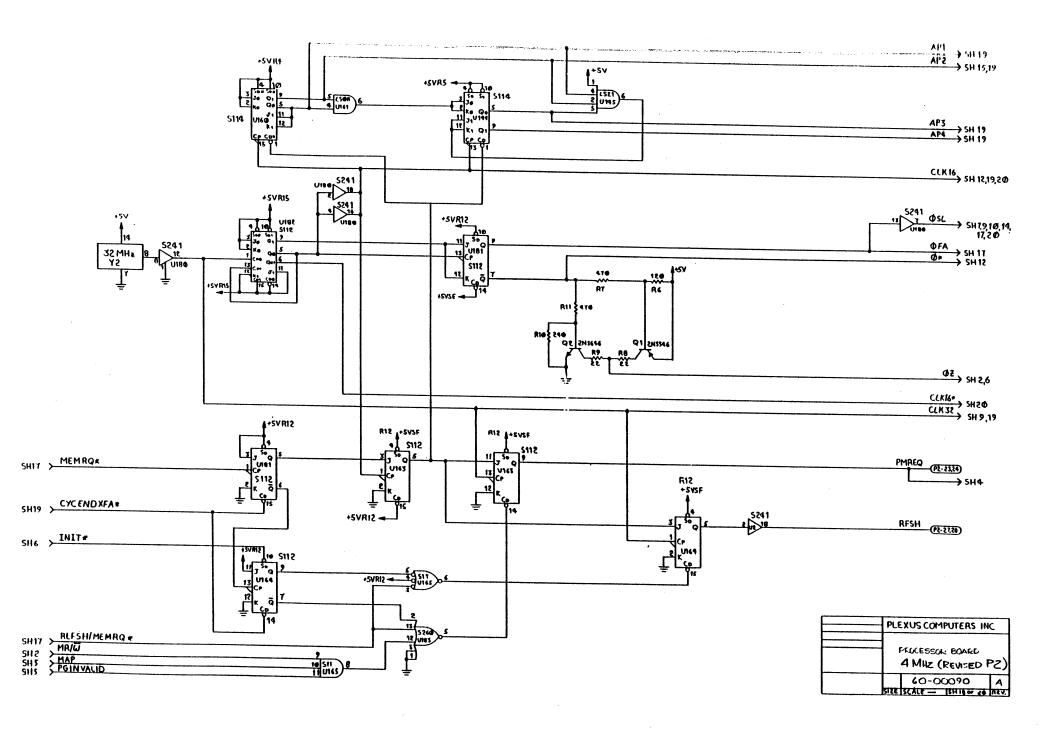

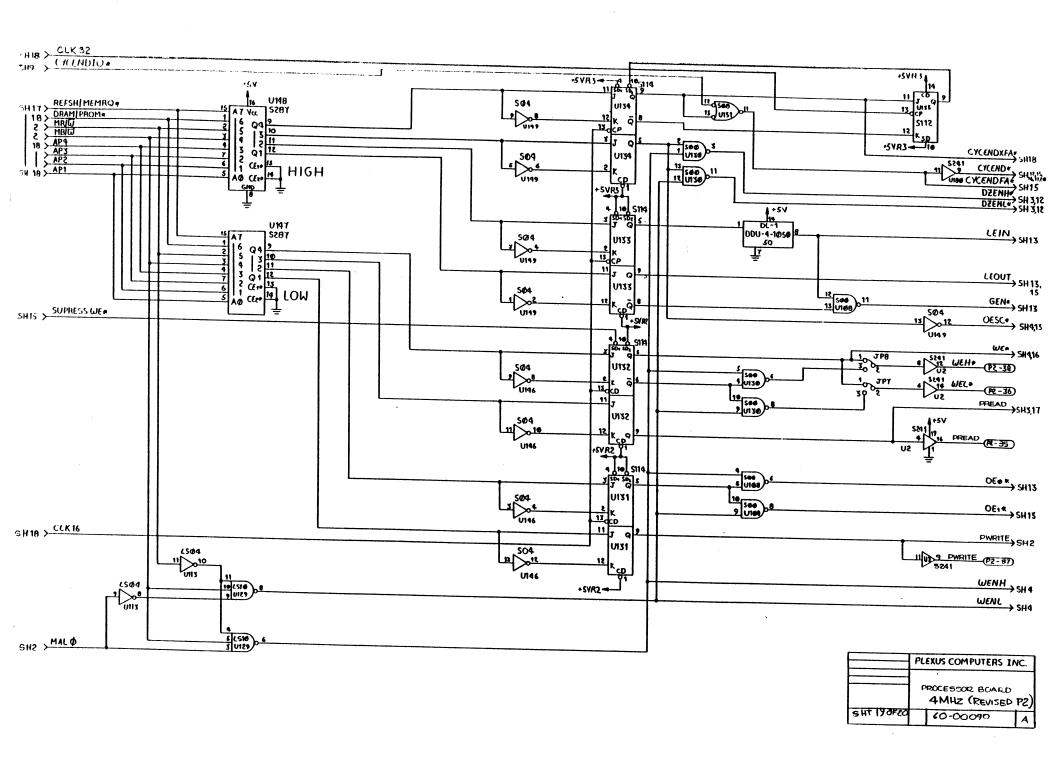

### 5.2. Timing Sequencer

The timing sequencer (block 22) is a bipolar-PROM-based state machine. Nine different types of timing programs are stored in the PROM. Only one program is executed for each type of memory access. Outputs from the timing sequencer control the timings required in a read/write cycle.

The following signals are output from the timing sequencer:

PMREQ -- Asserted when a valid mapped physical address is available.

REFSH -- Generated in a refresh cycle. Functionally equivalent to PMREQ.

PREAD -- Controls the direction of the data buffers on connector P2 for read operations.

PWRITE -- Controls the direction of data buffers on P2 for write operations.

LEIN -- Latches data into the EDC buffers.

LEOUT -- Latches data into the EDC output buffers and samples the error/ and multi-error/ lines.

WE/ -- WRITE ENABLE strobe generated in a write cycle.

OEO,1/ -- Enables output latches in the EDC chip.

OESC -- Enables output buffers of EDC chip.

GEN/ -- Active when CPU is in a memory write cycle.

DZEN -- Controls the Z8001A data buffers.

CYCEND/ -- Signals the end of a memory cycle.

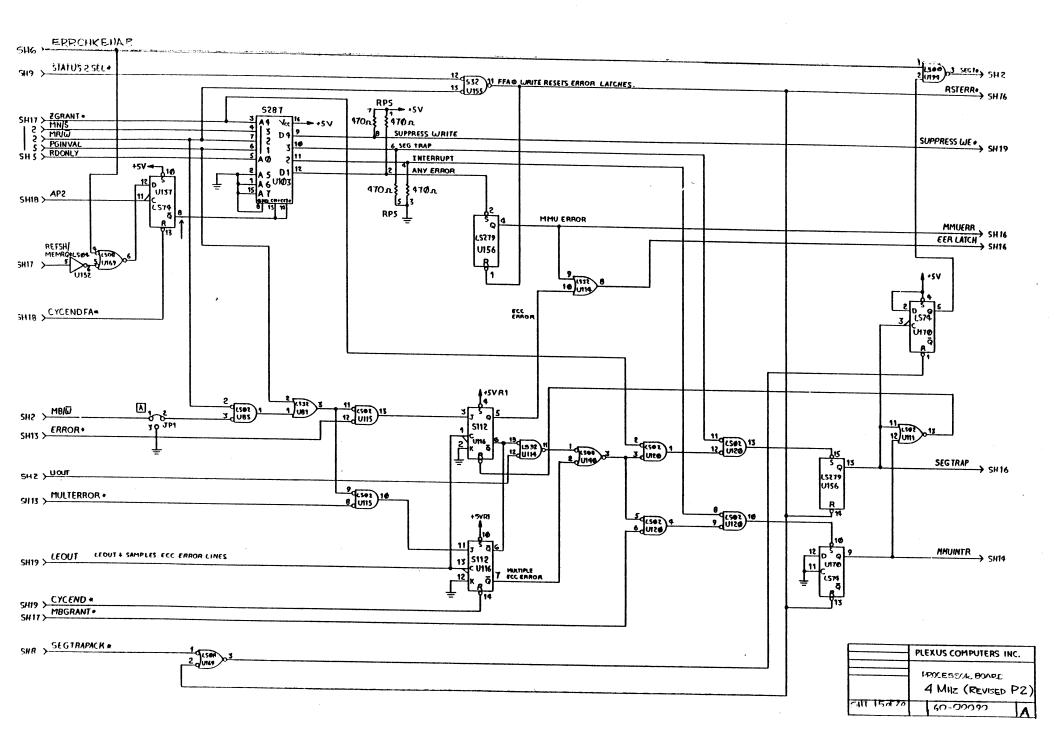

#### 6. ERROR HANDLER

The error handler (block 43) has two functions. It generates a segment trap or a vectored interrupt when errors occur and it latches relevant information about the error in the error status registers.

The P/25 detects two kinds of errors on the processor board. The first kind, a memory mapping error, occurs when a memory access violates the protection bits assigned to a page. The second kind, an EDC error, is generated by the EDC chip when the data checkbits stored in memory do not match the new checkbits generated for comparison during a read operation.

The operating environment in which a memory mapping error is generated and the action associated with the error are discussed in Processor section 2 and in Memory section 2.

## 6.1. Circuit Analysis

## 6.1.1. Memory Mapping Errors

When a memory access violates the attribute bits assigned to a page, the ERROR line is pulled low, setting flip-flop U156. If the memory access was initiated by a Multibus controller, U170 is set and MMUINT is sent to the PIC which generates a vectored interrupt. If the access was generated by the CPU, a segment trap is generated. The CPU can mask the trap by setting bit 7 of PIO port A.

If the error is caused by a write to a read-only protected page, then the write operation is suspended by asserting SUPPRESS WRITE (see the processor schematics, page 15).

#### 6.1.2. EDC Errors

When the EDC detects a single-bit error, it corrects it and activates the ERROR line to the error handler. When it detects a multiple-bit error, it activates the ERROR line and the MUL-ERROR line.

The error handler uses these inputs to generate the proper action: a) if the access was initiated by a Multibus master (other than the CPU) it sends a MMUINT to the PIC, which generates a vectored interrupt, and b) if the access was

initiated by the CPU, the error handler sends SEGTRAP to the Z800lA, which generates a segment trap.

Because the EDC corrects single-bit errors, the interrupt (or trap) serves to log the error. For multiple-bit errors, the interrupt (or trap) prevents incorrect data from being written to the requesting device.

Both error lines to the error handler are sampled at the falling edge of LEOUT signal.

When the P/25 runs in the unmapped mode, the read-only bit and page-invalid bit in the page mapper must be cleared to allow the error handler to sample the EDC ERROR/ and MULTIERROR/ outputs.

### 6.1.3. Error Recovery

Before the error handler can detect the next error, the flip-flops (U156 and U170) must be cleared with a write to special port FFA0H. This is also required to enable the error handler after powerup or reset.

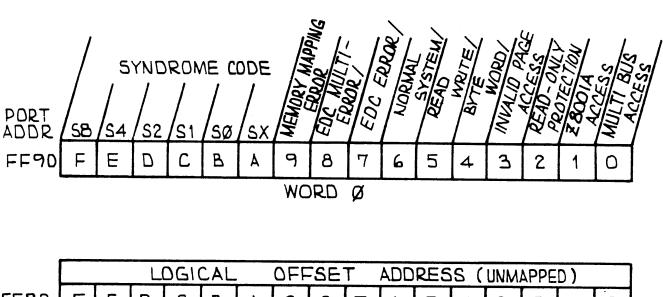

## 6.2. Error Status Registers

Error status registers located at port addresses FF90H, FF98H, FFA0H and FFA8H latch relevant status information when an error occurs. The registers latch the address of the memory location that caused the error, several status bits that describe the access, and a 6-bit syndrome code if the error was generated by the EDC. The format and data are shown in Figure 11.

Figure 1. P/25 Processor Board Block Diagram -- Part A

Figure 1. P/25 Processor Board Block Diagram -- Part B

Figure 2. Z8001A Read/Write Timing

Figure 3. P/25 Address Mapping Scheme

Figure 4. Page Mapping Layout

| HIGH ORDER 796 BUS<br>ADDRESS |     | 96 BUS | 3   | PORT ADDRESS<br>SPECIAL I/O                        |        |

|-------------------------------|-----|--------|-----|----------------------------------------------------|--------|

| A19                           | A18 | A17    | A16 |                                                    |        |

| 1                             | 1   | 1      | 1   |                                                    | ] FF8F |

| 1                             | 1   | 1      | 0   |                                                    | ] FF8E |

| 1                             | 1   | 0      | 1   |                                                    | ] FF8D |

| 1                             | 1   | 0      | ٥   | ·                                                  | ] FF8C |

| 1                             | 0   | 1      | 1   |                                                    | ] FF8B |

| 1                             | ٥   | 1      | ٥   |                                                    | ] FF8A |

| 1                             | ٥,  | 0      | 1   |                                                    | ] FF89 |

| 1                             | 0   | 0      | ٥   | 7 6 5 4 3 2 1 0<br>SNO SN6 SN5 SN4 SN3 SN2 SN1 I/C | FF88   |

Figure 5. Multibus Map Layout

Figure 6. Read Cycle For Realtime Clock

Figure 7. Write Cycle For Realtime Clock

Figure 8. ICWs For 8259A (PIC)

Figure 9. Multibus Memory Access Timing (Read/Write)

Figure 10. Processor Board Multibus Access Timing

|        | LDGICAL |   |   |   | LOGICAL OFFSET ADDRESS (UNMAPPED) |   |   |   | D ) |   |   |   |   |   |   |   |

|--------|---------|---|---|---|-----------------------------------|---|---|---|-----|---|---|---|---|---|---|---|

| FF98   | F       | E | ם | С | В                                 | А | 9 | ප | 7   | 9 | 5 | 4 | 3 | 2 | 1 | 0 |

| WORD 1 |         |   |   |   |                                   |   |   |   |     |   |   |   |   |   |   |   |

|      |        | ICAL | SEGMENT ADDR (UNMAPP |     |     |     |     | PED) |      |

|------|--------|------|----------------------|-----|-----|-----|-----|------|------|

| FFAØ | UNUSED | EAO  | EA6                  | EA5 | EA4 | EA3 | EA2 | EA1  | EA36 |

|      | WORD   | 2    |                      |     |     |     |     |      | ·    |

|      | LOG | ICAL | OF | SET | ADE | DR (L | INMA | PPEC | ) ) OF | INST | R.F | ETCH | FOR | VAL | DAC | ESS |

|------|-----|------|----|-----|-----|-------|------|------|--------|------|-----|------|-----|-----|-----|-----|

| FFAB | F   | ш    | ם  | С   | В   | Α     | ٩    | 8    | 7      | ۵    | 5   | 4    | 3   | 2   | 1   | 0   |

Figure 11. Error Status Registers

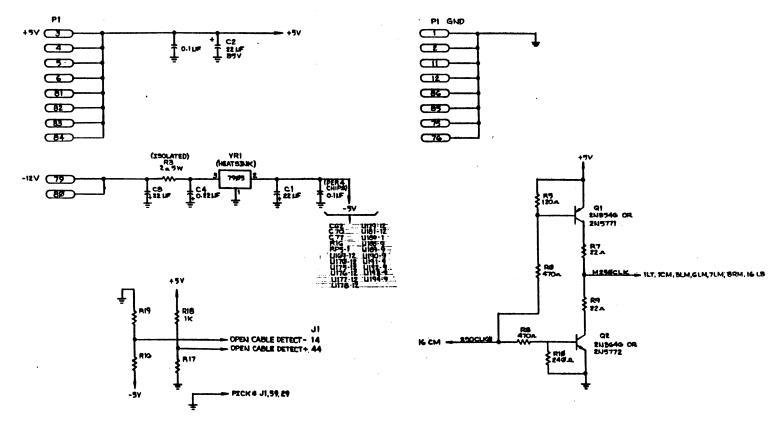

(P1-7.8) + 12V SH7 C11 1 22 UF TANT T 15WVDC MONOLITHIC C1 + 5VR1 C2-10 SS + SVR2 + SVR3 - + SVR5 + SVRIZ + 5VR13 P 12.15 P1 N.85 + SVRIS P1-86 ra11,282 (P1-19,00) - 12V SH 7 C12 NOTES:

A THE MEMORY PARITY CIRCUIT STILL EXISTS ON THE P.C.BOARD 60-00080 BUT IS NOT SHOWN IN THE SCHEMATIC, 60-00090.

1. ALL CAPACITORS ARE IN MICROFARADS \$ 20% UNLESS SPECIFIFED OTHERWISE.

2. RESISTORS ARE IN OHMS : 5% 1/4 WATT.

| Į                | REV | DESCRIPTION                                         | DATE     | APPYT |

|------------------|-----|-----------------------------------------------------|----------|-------|

|                  | C   | SWITCHED TO 32K EPROMS<br>ENGRE PROD. RELEASE EN 65 | 10-28-91 | WAM   |

|                  | D   | WIES REPLACED BY MISOLUTT BY META                   | 1-14- 92 | WAM   |

| <b>∞</b> -∞∞-∞ - | E   | C TOZ REPLACED WAS: 20PF,15 TPF                     | 1-10-82  | WAM   |

| 1                | F   | EN 103 CHG AT U 134, 150, 168                       | 42.02    | WAM   |

| ł                | F   | EN 106                                              | 4-2-02   | WM    |

| ſ                | G   | EUIIZ ADD REE, 23                                   | 4-2-02   | WM    |

|                  | LA  | EN 123 WAS: 60-00080 15:60-00090                    |          |       |

| 971. Armost 7-81 | PLEXUS COMPUTERS IN                | ζ.  |

|------------------|------------------------------------|-----|

|                  | PROCESSOR BOARD 4 MHZ (REVISED PZ) |     |

|                  | 60-00090                           | A   |

|                  | SIZE SCALE - SHE OF ZO             | REV |

PLEXUS COMPUTERS INC.

PROCESSOR BOALD

4 MHE (REVISED P2)

60-00090 A

STRE ISCALE — ISHE SP EO PRIV

PREXUS COMPUTERS INC.

PROCESSOR BOALD

4 MIZ (REVISED PZ)

SHOOF 20

60-00090

A

| PLEXUSCOMPUTERS INC.               |

|------------------------------------|

| PROCESSON BOARD 4 MHZ (REVISED P2) |

| 60-00090 A                         |

| <br>SIEE SCALE SHID OF ED MEN      |

60-00090 A

|   | PLEXUS COMPUTERS INC                |                     |     |

|---|-------------------------------------|---------------------|-----|

|   | PROCESSUR BUARD 4 MILE (REVISED PE) |                     |     |

|   |                                     | 60-00090            | Α   |

| L | SIZE                                | SCALE - SH 19 61 80 | MEV |

# INPUT/OUTPUT CONTROLLER (INTELLIGENT COMMUNICATION PROCESSOR)

- 1. ICP OVERVIEW

- 2. PROCESSOR