# OEM Service Manual

V100 Series 5.25 Inch Winchester Disk Drives

# **OEM Service Manual**

V100 Series 5.25 Inch Winchester Disk Drives

|            |                      |    |       |       |      |      |      |      |    |    |    |    | -  |    |    |

|------------|----------------------|----|-------|-------|------|------|------|------|----|----|----|----|----|----|----|

|            | SHEET REVISION TABLE |    |       |       |      |      |      |      |    |    |    |    |    |    |    |

| P/N        | 3081                 | 00 | Revis | ion L | tr A | EC 1 | 0299 |      |    |    |    |    |    |    |    |

| SHT        | i                    | ii | iii   | iv    | v    | vi   | vii  | viii | ix | 1  | 2  | 3  | 4  | 5  | 6  |

| REV<br>LTR | A                    | A  | A     | A     | A    | A    | A    | A    | Α  | Α  | A  | A  | A  | A  | A  |

| SHT        | 7                    | 8  | 9     | 10    | 11   | 12   | 13   | 14   | 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| REV<br>LTR | A                    | Α  | A     | A     | A    | A    | A    | A    | A  | Α  | A  | A  | A  | A  | Α  |

| SHT        | 22                   | 23 | 24    | 25    | 26   | 27   | 28   | 29   | 30 | 31 | 32 | 33 | 34 | 35 | 36 |

| REV<br>LTR | A                    | A  | A     | A     | A    | A    | A    | A    | A  | A  | A  | Α  | A  | A  | A  |

| SHT        | 37                   | 38 | 39    | 40    | 41   | 42   | 43   | 44   | 45 | 46 | 47 | 48 | 49 | 50 | 51 |

| REV<br>LTR | A                    | Α  | A     | A     | A    | A    | A    | A    | A  | A  | A  | A  | A  | A  | Α  |

| SHT        | 52                   | 53 | 54    | 55    | 56   | 57   | 58   | 59   | 60 | 61 | 62 | 63 | 64 | 65 | 66 |

| REV<br>LTR | A                    | A  | A     | A     | Α    | A    | A    | A    | Α  | A  | A  | A  | Α  | A  | A  |

| SHT        | 67                   | 68 | 69    | 70    | 71   | 72   | 73   | 74   | 75 | 76 | 77 | 78 | 79 | 80 | 81 |

| REV<br>LTR | A                    | A  | A     | A     | A    | A    | A    | A    | A  | Α  | A  | A  | A  | A  | A  |

| SHT        | 82                   | 83 | 84    | 85    | 86   | 87   | 88   | 89   | 90 | 91 | 92 | 93 | 94 | 95 | 96 |

| REV<br>LTR | A                    | A  | A     | A     | A    | Α    | A    | Α    | A  | A  | A  | A  | A  | A  | A  |

| SHT        | 97                   | 98 | 99    | 100   |      |      |      |      |    |    |    |    |    |    |    |

| REV<br>LTR | A                    | A  | A     | Α     |      |      |      |      |    |    |    |    |    |    |    |

## **PRIAM Sales Offices**

Headquarters: 20 West Montague Expwy., San Jose, CA 95134 (408) 946-4600, TWX 910-338-0293, FAX (408) 946-5679 Orange Co., CA (714) 662-7266; Dallas, TX (214) 690-0980 Minneapolis, MN (612) 854-3900; Boston, MA (617) 444-3973 Chicago, IL (312) 882-5760; New York (201) 938-2740 Reading U.K. 734-509621, TLX 847493 PRIAM G

## TABLE OF CONTENTS

|   |           | PAGE                                      | , |

|---|-----------|-------------------------------------------|---|

| 1 | INT       | RODUCTION                                 |   |

|   | 1.1       | GENERAL DESCRIPTION                       |   |

|   | 1.2       | SPECIFICATION SUMMARY                     | ) |

|   |           | 1.2.1 Physical Specifications             | • |

|   |           | 1.2.2 Functional Specifications 3         |   |

|   |           | 1.2.3 Reliability Specifications 4        | ŀ |

|   |           | 1.2.4 Disk Defects                        | ļ |

| 2 | FUI       | NCTIONAL CHARACTERISTICS/OVERVIEW         |   |

| _ | 2.1       | GENERAL OPERATION                         | 5 |

|   | 2.2       | READ/WRITE, SERVO AND CONTROL ELECTRONICS | 5 |

|   | 2.3       | DRIVE MECHANISM                           |   |

|   | 2.4       | AIR FILTRATION SYSTEM                     |   |

|   | 2.5       | POSITIONING MECHANISM                     |   |

|   | 2.6       | READ/WRITE HEADS AND DISKS                |   |

|   | 2.7       | SERVO SYSTEM                              | 3 |

| 3 | <b>FU</b> | NCTIONAL OPERATIONS                       |   |

|   | 3.1       | POWER SEQUENCING                          | 9 |

|   | 3.2       | DRIVE SELECTION 10                        |   |

|   | 3.3       | TRACK ACCESSING                           |   |

|   | 3.4       | HEAD SELECTION 10                         | ) |

|   | 3.5       | READ OPERATION                            |   |

|   | 3.6       | WRITE OPERATIONS                          |   |

|   | 3.7       | SYSTEM INTEGRATION CONSIDERATIONS         | 1 |

|   |           |                                           |   |

|   | TH  | <b>EORY</b> | OF OPERATION                               |    |

|---|-----|-------------|--------------------------------------------|----|

|   | 4.1 | OVER        | VIEW                                       | 12 |

|   | 4.2 |             | DISK ASSEMBLY                              |    |

|   |     | 4.2.1       | Actuator                                   |    |

|   |     | 4.2.2       | Recording Media                            |    |

|   |     | 4.2.3       | Read/Write Heads                           |    |

|   |     | 4.2.4       | Read Preamplifier/Write Driver IC          |    |

|   |     | 4.2.5       | Servo Head                                 |    |

|   |     | 4.2.6       | Servo Preamplifier IC                      |    |

|   |     | 4.2.7       | Spindle Motor                              |    |

|   |     | 4.2.8       | Air Filtration Components                  |    |

|   | 4.3 | SERVO       | <del>.</del>                               |    |

|   |     | 4.3.1       | Actuator Lock Driver                       |    |

|   |     | 4.3.2       | Clock Generator                            |    |

|   |     | 4.3.3       | Spindle Speed Control                      |    |

|   |     | 4.3.4       | Spindle Speed Checker                      |    |

|   |     | 4.3.5       | Spindle Motor Brake Relay and Relay Driver |    |

|   |     | 4.3.6       | Actuator Servo Control                     |    |

|   |     | 4.3.7       | Demodulator                                |    |

| - |     | 4.3.8       | Mode Select Switch                         |    |

|   |     | 4.3.9       | Seek Mode                                  |    |

|   |     | 4.3.10      | Velocity DAC                               |    |

|   |     | 4.3.11      | Tachometer                                 |    |

|   |     | 4.3.12      | Slope Selector                             |    |

|   |     | 4.3.13      | Current Inverter                           |    |

|   |     | 4.3.14      | On-Peak Detector                           |    |

|   |     | 4.3.15      | Power Amplifier                            |    |

|   |     | 4.3.16      | Inverter                                   |    |

|   |     | 4.3.17      | Track Follow Mode                          |    |

|   |     | 4.3.18      | Off-Track Detector                         |    |

|   |     | 4.3.19      | Seek Operation                             |    |

|   |     | 4.3.20      | Restore to Track Ø Operation               |    |

|   |     | 4.3.21      | Power On Reset                             |    |

|   | 4.4 | DATA I      | PCB                                        |    |

|   |     | 4.4.1       | Microprocessor and PLA                     |    |

|   |     | 4.4.2       | Microprocessor/PLA Control Signals         |    |

|   |     | 4.4.3       | Disk Drive Control Functions               |    |

|   |     | 4.4.4       | Input Buffers                              |    |

|   |     | 4.4.5       | Output Drivers                             |    |

|   |     | 4.4.6       | Disk Drive Data Functions                  |    |

|   |     | 4.4.7       | Read/Write Data Channel                    |    |

|   |     | 4.4.8       | Head Select and Control Logic              |    |

|   |     | 4.4.9       | Read Chain                                 |    |

|   |     | 4.4.10      | Amplifier/Signal Conditioner               |    |

|   |     |             |                                            |    |

|   |     | 4.4.11      | Differential Line Driver              | 3          |

|---|-----|-------------|---------------------------------------|------------|

|   |     | 4.4.12      | Write Chain                           | 3          |

|   |     | 4.4.13      | Line Receiver 24                      |            |

|   |     | 4.4.14      | Transition Generator                  |            |

|   |     | 4.4.15      | Write Current Source 24               | 4          |

|   |     | 4.4.16      | Write Fault Detector                  | 4          |

|   | 4.5 | <b>OPER</b> | ATIONAL SEQUENCE 24                   | 4          |

|   |     | 4.5.1       | Power On Reset                        |            |

|   |     | 4.5.2       | Motor Start 25                        |            |

|   |     | 4.5.3       | Actuator Lock                         |            |

|   |     | 4.5.4       | Servo Restore to Track 0              | 6          |

|   |     | 4.5.5       | Seek Operation                        | 6          |

|   |     | 4.5.6       | Track Format 2                        | 8          |

|   |     |             | 4.5.6.1 Gap 1 2                       | 8          |

|   |     |             | 4.5.6.2 Gap 2 2                       | 8          |

|   |     |             | 4.5.6.3 Gap 3 2                       | 9          |

|   |     |             | 4.5.6.4 Gap 4                         | 9          |

|   |     |             | 4.5.6.5 Sector Interleaving           | 9          |

|   |     | 4.5.7       | Read Operation/Head Select            | 1          |

|   |     | 4.5.8       | Write Operation/Fault Detection 3     | 3          |

|   | 4.6 | <b>ERRO</b> | R DEFINITION 3                        |            |

|   |     | 4.6.1       | Soft (Recoverable) Errors 3           | 4          |

|   |     | 4.6.2       | Hard (Non-Recoverable) Errors 3       | 4          |

|   |     | 4.6.3       | Seek (Access Position) Errors 3       | 4          |

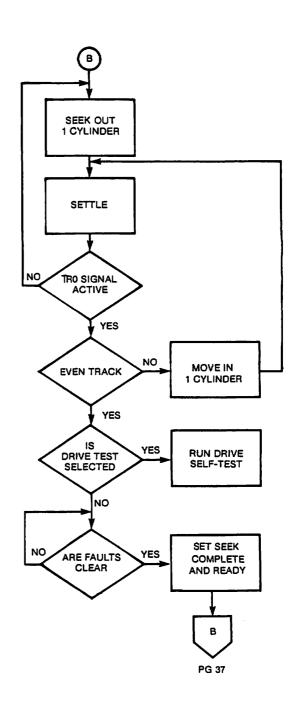

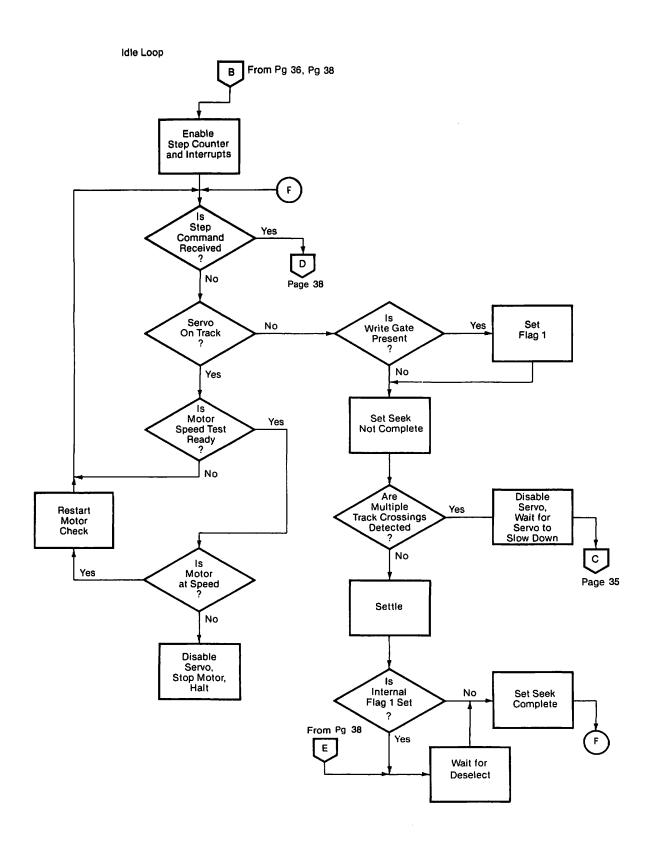

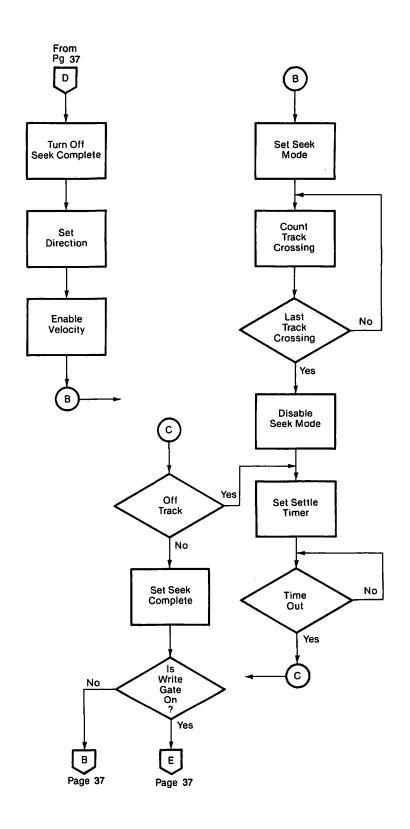

|   | 4.7 | DRIVE       | E OPERATION FLOW CHART 3              | 5          |

| 5 | EL  | ECTRI       | CAL INTERFACE                         |            |

|   | 5.1 |             | TRICAL INTERFACE OVERVIEW             | 9          |

|   | 5.2 |             | ROL INPUT LINES 4                     |            |

|   | J.2 | 5.2.1       | Write Gate 4                          | 4          |

|   |     | 5.2.2       | Head Select $2^0$ , $2^1$ , and $2^2$ | 5          |

|   |     | 5.2.3       | Direction In                          | 5          |

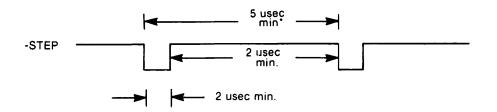

|   |     | 5.2.4       | Step 4                                | 5          |

|   |     | 5.2.5       | Drive Select 1-4                      | 16         |

|   | 5.3 |             | ROL OUTPUT LINES 4                    |            |

|   | 0.0 | 5.3.1       | Seek Complete 4                       |            |

|   |     | 5.3.2       | Track 0                               | <b>1</b> 7 |

|   |     | 5.3.3       | Write Fault 4                         |            |

|   |     | 5.3.4       | Index 4                               | 18         |

|   |     | 5.3.5       | Ready 4                               | 19         |

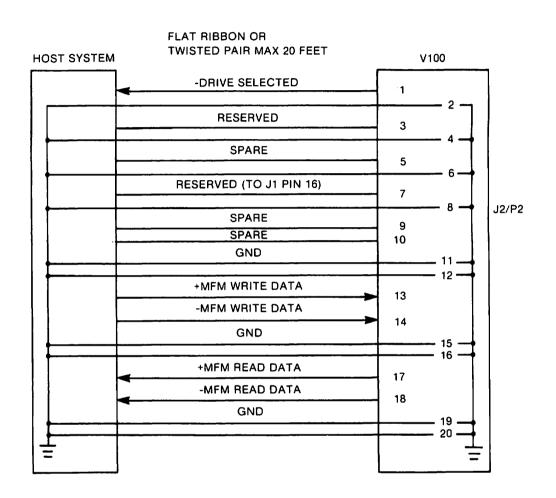

|   | 5.4 |             | TRANSFER LINES 4                      | 19         |

|   | J.7 | 5.4.1       | MFM Write Data                        | 50         |

|   |     | 5.4.2       | MFM Read Data                         |            |

|   |     | 5.4.3       | Read/Write Timing                     | 50         |

|   |     |             |                                       |            |

|    | 5.5  | DRIVE SELECTED                    |   |

|----|------|-----------------------------------|---|

|    | 5.6  | CUSTOMER OPTIONS                  |   |

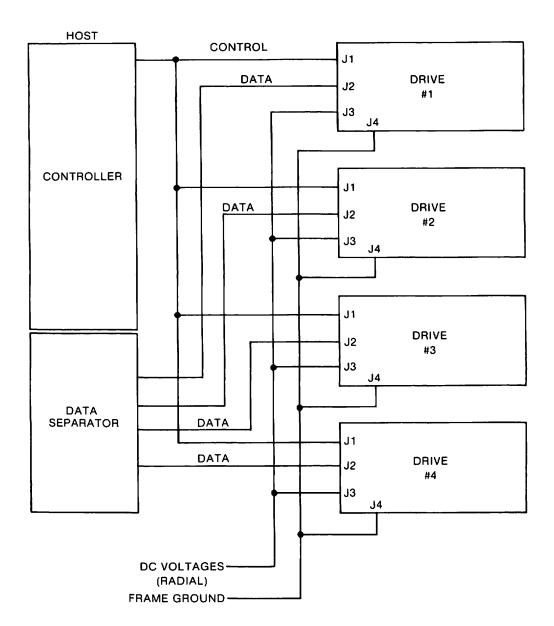

|    |      | 5.6.1 Radial and Select           |   |

|    |      | 5.6.2 Auto Access                 |   |

|    |      | 5.6.3 Power Sequencing (PS)       | 2 |

|    |      | 5.6.4 Non-Multiplexed Index (NMI) |   |

|    |      | 5.6.5 Write Protect (WP)          |   |

|    |      | 5.6.6 Radial Seek Complete (SC)   |   |

|    |      | 5.6.7 Grounding 5                 | 3 |

| 6  | PH   | YSICAL INTERFACE                  |   |

|    | 6.1  | PHYSICAL INTERFACE OVERVIEW 5     |   |

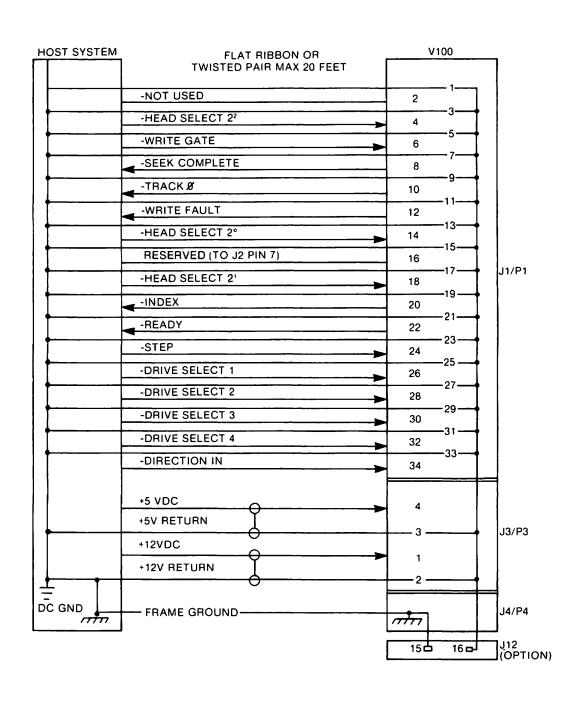

|    | 6.2  | J1/P1 CONNECTOR—CONTROL SIGNALS 5 | 5 |

|    | 6.3  | J2/P2 CONNECTOR—DATA SIGNALS 5    | 5 |

|    | 6.4  | J3/P3 CONNECTOR—DC POWER 5        |   |

|    | 6.5  | J4/P4 FRAME GROUND CONNECTOR 5    |   |

|    | 6.6  | DRIVE PHYSICAL CABLING 5          |   |

| 7  | PH   | YSICAL SPECIFICATIONS             |   |

|    | 7.1  | <b>OVERVIEW</b>                   | Q |

|    | 7.2  | MOUNTING ORIENTATION 5            |   |

|    | 7.3  | MOUNTING HOLES                    |   |

|    | 7.4  | PHYSICAL DIMENSIONS 5             |   |

|    | 7.5  | FACEPLATE 6                       |   |

|    | 7.6  | SHIPPING REQUIREMENT 6            |   |

| 8  | D A' | TA PCB BLOCK DIAGRAM 6            | 3 |

| 0  | DA   | A T CD BLOCK DIAGRAM              | 7 |

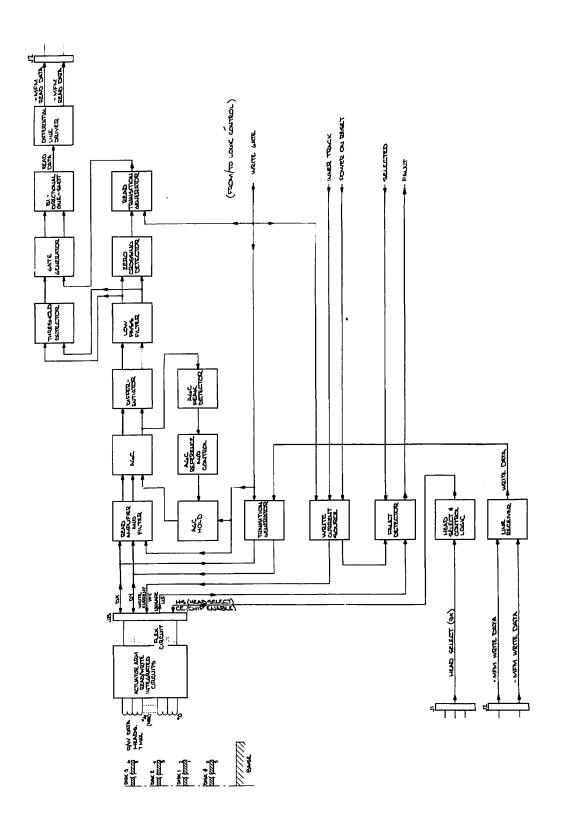

| 9  | SEI  | RVO PCB BLOCK DIAGRAM 6           | 5 |

| 10 | MA   | INTENANCE/REPAIR                  |   |

|    | 10.1 | OVERVIEW                          | ٥ |

|    | 10.1 |                                   |   |

|    | 10.2 | 10.2.1 Front Cover                |   |

|    |      | 10.2.2 Side Frames                |   |

|    |      | 10.2.3 Data PCB                   |   |

|    |      | 10.2.4 Servo PCB                  |   |

|    | 10.3 | REPAIR AND ADJUSTMENTS 7          |   |

|    | 10.0 | 10.3.1 Data PCB                   |   |

|    |      | 10.3.2 Servo PCB                  |   |

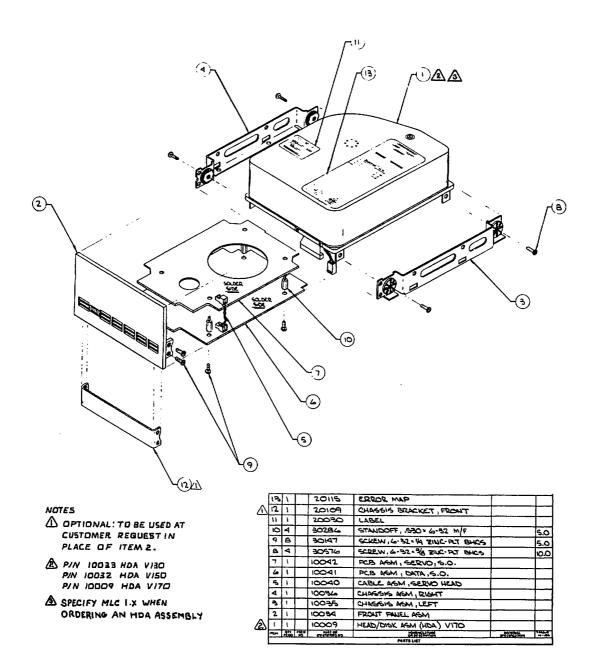

|    | 10.4 | SPARE PARTS LIST (MLC 1.X)        |   |

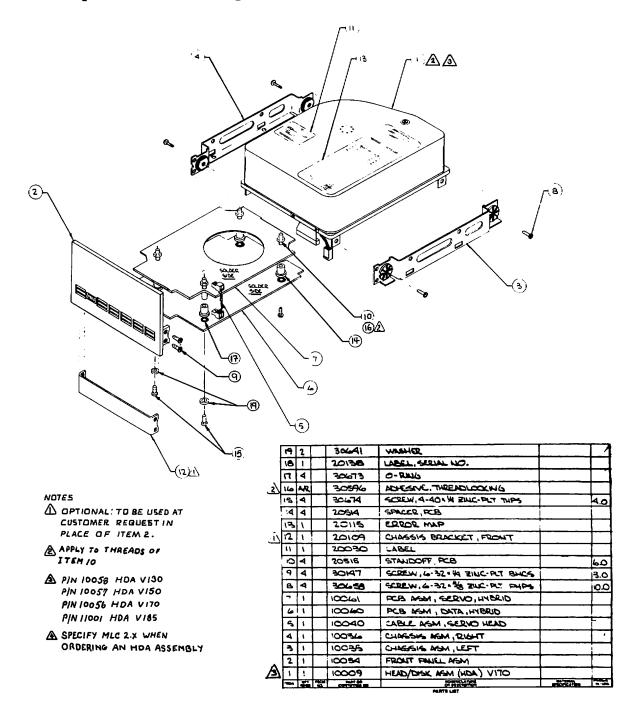

|    |      | CDADE DADTC   ICT (MI C 2 V)      |   |

| 11 V100 TEST POINTS (MLC 1.X)                |    |

|----------------------------------------------|----|

| 11.1 DATA PCB TEST POINTS                    | 74 |

| 11.2 SERVO PCB TEST POINTS                   |    |

| 12 V100 TEST POINTS (MLC 2.X)                |    |

| 12.1 DATA PCB TEST POINTS                    | 83 |

| 12.2 SERVO PCB TEST POINTS                   | 87 |

| APPENDIX A UNPACKING AND HANDLING GUIDE      |    |

| A.1 INTRODUCTION                             | 92 |

| A.2 UNPACKING THE DRIVE                      | 92 |

| A.2.1 Shipping Damage Inspection             |    |

| A.2.2 Opening the Shipping Container         | 92 |

| A.2.3 Removing Drive From Shipping Container | 92 |

| A.2.4 Inspection Procedures                  |    |

| A.3 HANDLING PROCEDURES                      | 97 |

| A.3.1 Shock and Vibration Precautions        | 97 |

| A.3.2 Automatic Head Actuator Lock           | 97 |

| A.3.3 Drive Handling Guidelines              | 97 |

| A.4 SHIPPING REQUIREMENTS                    | 98 |

| A.4.1 Automatic Head Actuator Lock           | 98 |

| A.4.2 Shipping a Stand-Alone Unit            | 98 |

| A.4.3 Shipping Drive Mounted in an Enclosure |    |

| A.4.4 Return Authorization                   |    |

| A.5 OTHER DOCUMENTATION                      |    |

| UNPACKING CHECKLIST                          |    |

|      | PA                                                              | GE   |

|------|-----------------------------------------------------------------|------|

| LIST | T OF TABLES                                                     |      |

| 5-1  | J1/P1 CONNECTOR PIN ASSIGNMENT                                  | 30   |

| 5-2  | J2/P2 CONNECTOR PIN ASSIGNMENT                                  | . 29 |

| 5-3  | P3-DC CONNECTOR PIN ASSIGNMENTS                                 | 40   |

| 6-1  | DC POWER REQUIREMENTS                                           | . 56 |

| A-1  | DC POWER REQUIREMENTS WINCHESTER DISC DRIVE HANDLING GUIDELINES | . 98 |

| LIS  | T OF FIGURES                                                    |      |

| 2-1  | AIR FILTRATION SYSTEM                                           | . 6  |

| 2-2  | READ/WRITE HEAD POSITIONING MECHANISM                           | 7    |

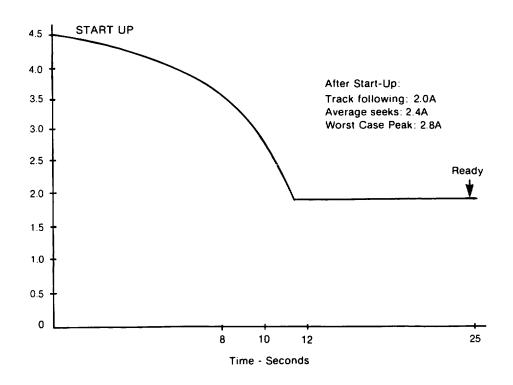

| 3-1  | POWER UP SEQUENCE                                               |      |

| 4-1  | POWER RESET                                                     |      |

| 4-2  | GENERAL SEEK TIMING                                             | . 27 |

| 4-3  | "A1" ADDRESS MARK BYTE                                          | . 29 |

| 4-4  | TYPICAL TRACK FORMAT                                            | . 30 |

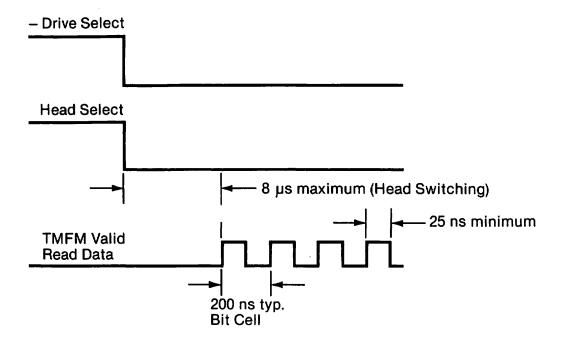

| 4-5  | TYPICAL READ TIMING                                             |      |

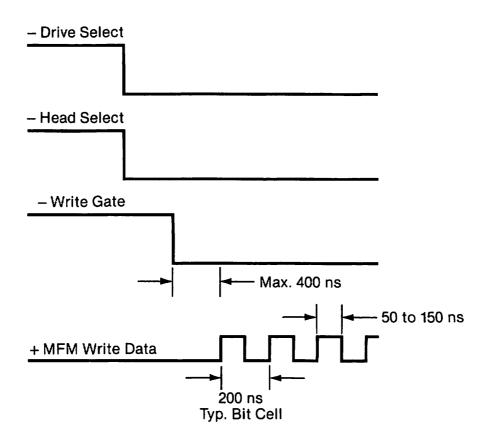

| 4-6  | WRITE DATA TIMING                                               |      |

| 5-1  | CONTROL SIGNALS                                                 |      |

| 5-2  | DATA SIGNALS                                                    |      |

| 5-3  | TYPICAL CONNECTION 4-DRIVE SYSTEM                               | . 43 |

| 5-4  | CONTROL SIGNAL DRIVER/RECEIVER COMBINATION                      |      |

| 5-5  | BUFFERED STEP                                                   | . 46 |

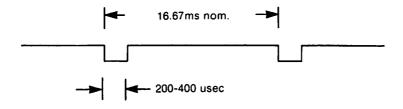

| 5-6  | INDEX TIMING                                                    |      |

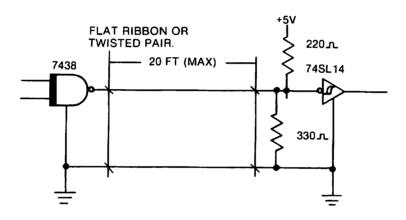

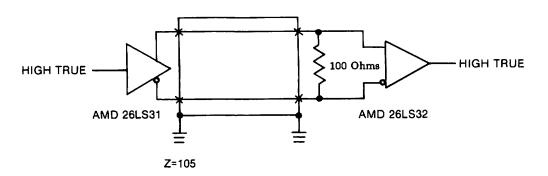

| 5-7  | DATA LINE DRIVER/RECEIVER COMBINATION                           | . 49 |

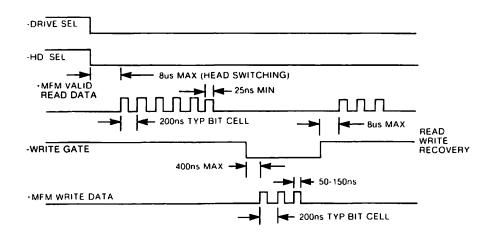

| 5-8  | READ/WRITE DATA TIMING                                          | . 50 |

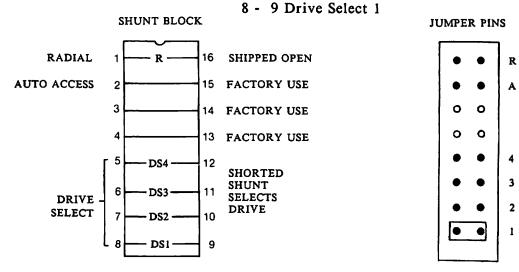

| 5-9  | OPTION SHUNT BLOCK (J6)                                         | . 51 |

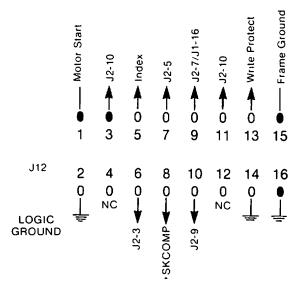

| 5-10 | PCB OPTION PADS (J12)                                           | . 53 |

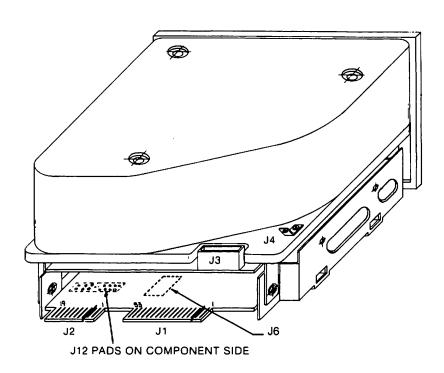

| 6-1  | INTERFACE CONNECTOR PHYSICAL LOCATIONS     | . 54 |

|------|--------------------------------------------|------|

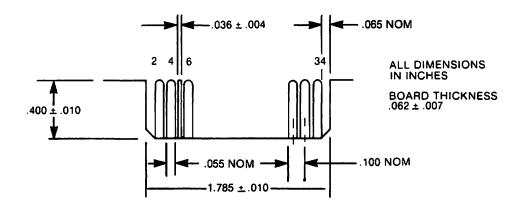

| 6-2  | J1 CONNECTOR DIMENSIONS                    | . 55 |

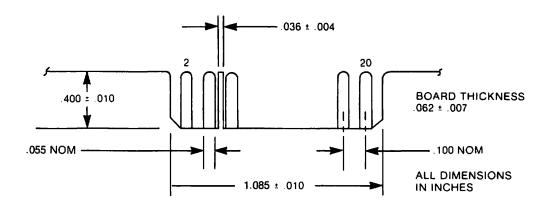

| 6-3  | J2 CONNECTOR DIMENSIONS                    |      |

| 6-4  | J3 CONNECTOR-INNER PCB SOLDER SIDE         |      |

| 6-5  | TYPICAL & MAXIMUM 12V CURRENT REQUIREMENTS |      |

| 6-6  | DRIVE INTERNAL AND EXTERNAL CABLING        | . 58 |

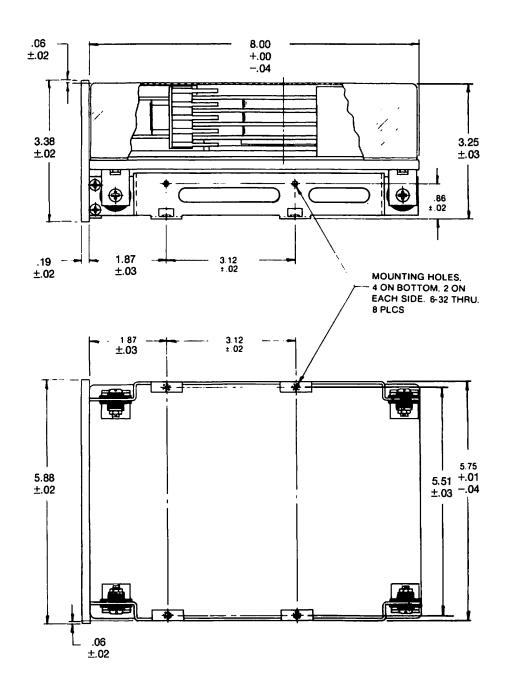

| 7-1  | MOUNTING PHYSICAL DIMENSIONS               | . 60 |

| 7-2  | OVERALL PHYSICAL DIMENSIONS                | . 61 |

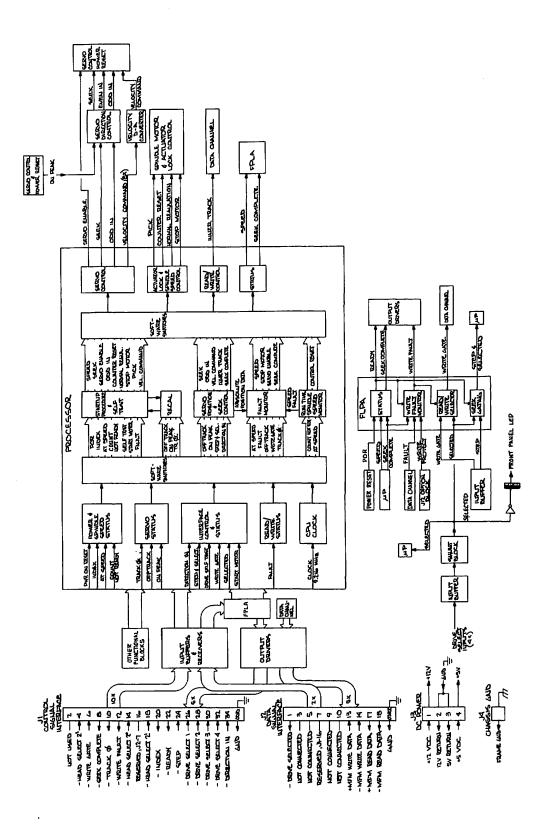

| 8-1  | DATA PCB BLOCK DIAGRAM                     | . 63 |

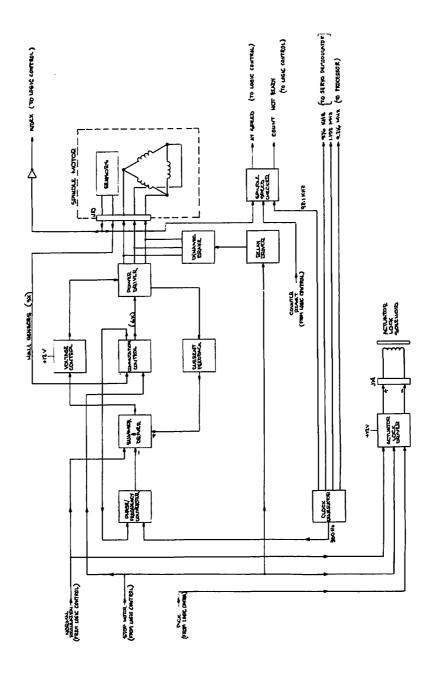

| 9-1  | SERVO PCB BLOCK DIAGRAM                    | . 66 |

| 10-1 | SPARE PARTS LIST/ASSEMBLY (MLC-1.X)        | . 72 |

| 10-2 | SPARE PARTS LIST/ASSEMBLY (MLC-2.X)        |      |

| 11-1 | DATA PCB TEST POINT DESCRIPTIONS           | . 74 |

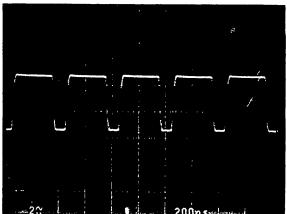

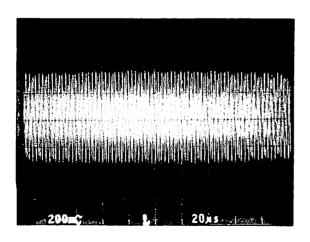

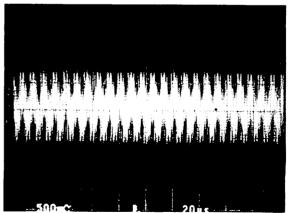

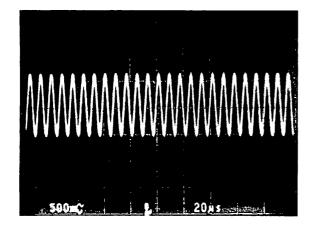

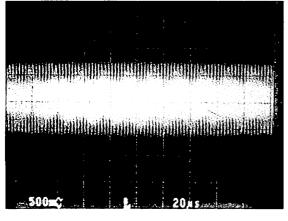

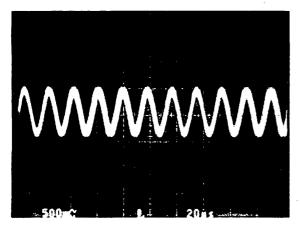

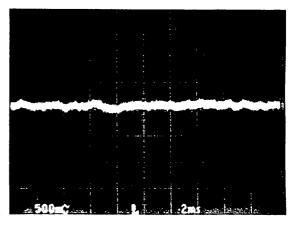

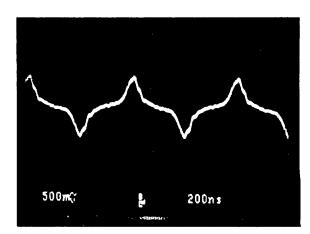

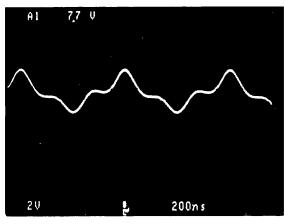

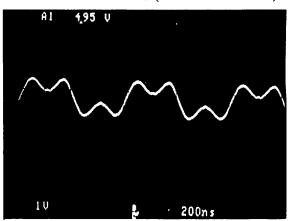

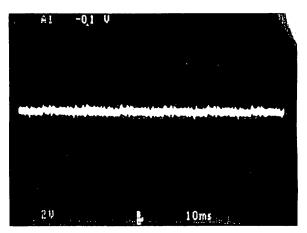

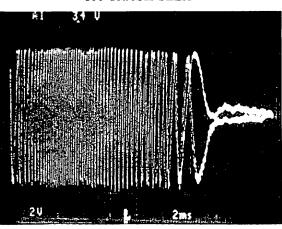

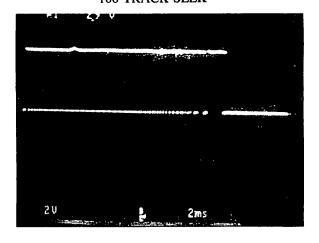

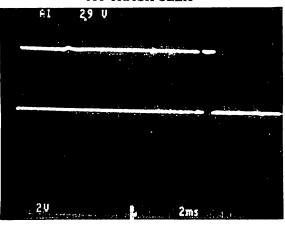

| 11-2 | TEST POINT OUTPUTS                         |      |

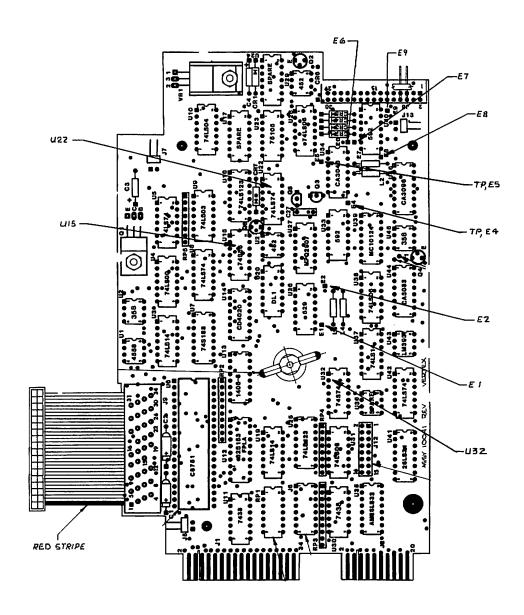

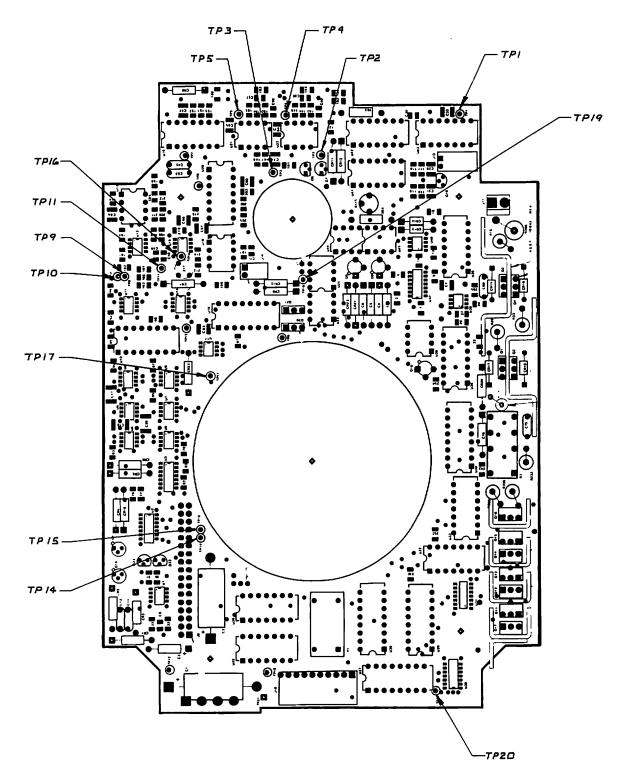

| 11-3 | MLC 1.X TEST POINT LOCATIONS DATA PCB      | . 77 |

| 11-4 | SERVO PCB TEST POINT DESCRIPTIONS          | . 78 |

| 11-5 | TEST POINT OUTPUT                          | . 78 |

| 11-6 | MLC 1.X TEST POINT LOCATIONS SERVO PCB     |      |

| 12-1 | DATA PCB TEST POINT DESCRIPTIONS           |      |

| 12-2 | TEST POINT OUTPUTS                         |      |

| 12-3 | MCL 2.X TEST POINT LOCATIONS               | . 86 |

| 12-4 | SERVO PCB TEST POINT DESCRIPTIONS          | . 87 |

| 12-5 | TEST POINT OUTPUTS                         |      |

| 12-6 | MLC 2.X TEST POINT LOCATIONS               | . 91 |

| A-1  | SINGLE DRIVE PACKAGING                     | . 93 |

| A-2  | FOUR-PACK DRIVE PACKAGING                  |      |

| A_3  | FIGHT DACK DRIVE DACKACING                 | 06   |

## 1 INTRODUCTION

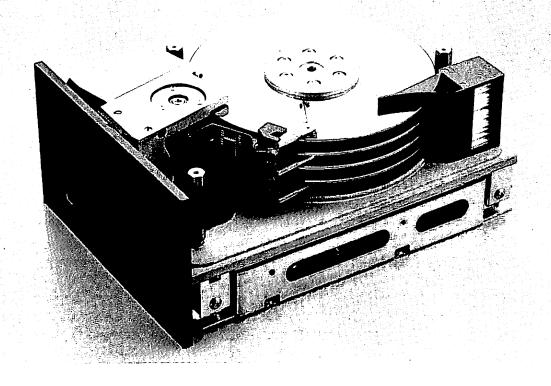

## 1.1 General Description

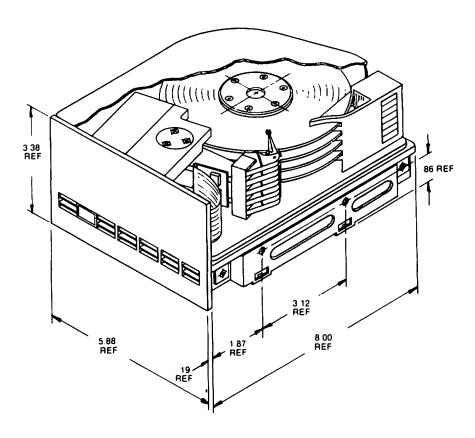

The Priam V100 Family of Disk Drives is a series of random access storage devices using 2, 3, or 4 nonremovable 5½ inch disks. Each disk surface employs one movable head to service up to 1166 tracks. Total unformatted capacities of four models are 30.8 (V130), 51.4 (V150), 72.0 (V170), and 85.0 (V185) megabytes.

Fast access time and high track density are achieved through the use of a rotary voice coil head positioner in conjunction with a dedicated servo surface.

The inherent simplicity of mechanical construction allows maintenance free operation throughout the life of the drive. Both electronic boards are mounted outside the sealed head disk assembly, allowing field serviceability.

Mechanical and contamination protection for the heads, actuator and disks is provided by an impact resistant metal cover. A self contained re-circulating system supplies clean air through a 0.3 micron filter. A separate filter allows for ambient pressure equalization without introduction of contaminants. Adequate air flow and uniform temperature distribution throughout the head and disk area are assured.

The track following servo system allows the heads to continuously follow the recorded track, and reduces off track due to non-repetitive spindle run-out, vibration, and environmental temperature changes: Read and write operations can be performed after power up with no thermal stabilization delay.

Superior data integrity results from the use of shock isolators, carbon overcoated metal film media, a head landing/shipping zone, and automatic actuator lock.

The electrical/physical interface is compatible with other available ST412/506 interfaced products, and includes the same data transfer rate, connectors, DC power, mechanical mounting holes and package size.

Customer options include:

- 1. Radial operation—Outputs active without drive selected.

- 2. Power On sequencing for multiple drive applications.

- 3. Non-Multiplexed Index.

- 4. Write Protect.

- 5. Radial Seek Complete.

## 1.2 Specification Summary

#### 1.2.1 Physical Specifications

## Power requirements

#### $12 \text{ VDC} \pm 10\%$ .

Maximum Ripple 120 mV P-P @ 10.92 VDC Minimum.

Peak Current 4.5 Amp-Motor Start For 10 Seconds.

Running Current 2.0 Amp avg. (Track Following).

Peak Running Current 2.8 Amp (Seeking).

Maximum Power Dissipation 54 Watts Peak for 10 Seconds during motor start.

Average Power Dissipation 27 Watts (12 Volts).

#### $5 \text{ VDC} \pm 5\%$

Maximum Ripple 120 mV P-P @ 4.88 VDC Minimum.

1.5 Amp avg./max.

Average Power Dissipation 7.5 Watts (5 Volts).

#### **Dimensions and Weight**

| Height* | 3.25 in (8.26 cm)  |

|---------|--------------------|

| Width*  | 5.75 in (14.61 cm) |

| Depth*  | 8.00 in (20.32 cm) |

| Weight  |                    |

<sup>\*</sup> Does not include Faceplate

#### **Environmental Limits**

#### **Ambient Temperature**

| Operating     | . 4°C to 50°C (40°F to 122°F) |

|---------------|-------------------------------|

| Nonoperating4 | 0°C to 60°C (-40°F to 140°F)  |

| Gradient      |                               |

| Relative Humidity                                     |                                         |           |              |             |

|-------------------------------------------------------|-----------------------------------------|-----------|--------------|-------------|

| Operating                                             |                                         | 8% to     | 80% (nonc    | condensing) |

| Operating                                             |                                         | Max       | imum Wet     | Bulb 85°F   |

| Nonoperating                                          | · • • • • • • • • • • • • • • • • • • • | 5% to     | 95% (nonc    | condensing) |

| Nonoperating                                          |                                         |           |              |             |

| Shock and Vibration                                   |                                         |           |              |             |

| Operating                                             | 2                                       | G max, 11 | ms. Half     | Sine Wave   |

| . •                                                   |                                         |           |              | , 22-600Hz  |

| Nonoperating                                          |                                         |           |              |             |

| . 0                                                   |                                         |           |              | , 22-600Hz  |

| Transport                                             |                                         |           |              |             |

| Altitude                                              |                                         |           | ,            |             |

| Operating30                                           | 05 m (-1000                             | ft) to +3 | .000 m (+    | 10.000 ft)  |

| Nonoperating30:                                       |                                         |           |              |             |

| Acoustical Noise                                      |                                         | •         |              | -           |

| 1100000001110000                                      | • • • • • • • • • • •                   | Jo ubu,   | one meter    | mom cover   |

|                                                       |                                         |           |              |             |

| 1.2.2 Functional Specifications                       |                                         |           |              |             |

|                                                       |                                         |           |              |             |

| Storage capacity                                      |                                         |           | , <u>(</u> , |             |

|                                                       | V130                                    | V150      | V170         | V185        |

| Unformatted*                                          | 30.8MB                                  |           | 72.0MB       | 85.0MB      |

| Formatted (typical sector formats)                    |                                         |           |              | 00.01/12    |

| $(32 \times 256 \text{ bytes})$                       | 24.3MB                                  | 40.4MB    | 56.6MB       | 66.9MB      |

| $(17 \times 512 \text{ bytes})$                       | 25.8MB                                  | 43.0MB    | 60.1MB       | 71.0MB      |

| Data tracks                                           | 2961                                    | 4935      | 6909         | 8162        |

| Data Cylinders                                        | 987                                     | 987       | 987          | 1166        |

| Disks                                                 | 2                                       | 3         | 4            | 4           |

| Data Surfaces                                         | 3                                       | 5         | 7            | 7           |

| Heads, Read/Write                                     | 3                                       | 5         |              | 7           |

| Head, Servo                                           | 1                                       | 1         | 7            | í           |

| Bytes per Track                                       |                                         | 1         | 1            | 1           |

| Unformatted                                           |                                         | 10,416    |              |             |

| Formatted (typical sector formats)                    |                                         | 10,410    |              |             |

| $32 \times 256$ byte sectors                          |                                         | 8,192     |              |             |

| $17 \times 512$ byte sectors                          |                                         | 8,704     |              |             |

| Maximum Bit Density (bits/inch)                       | 9,897                                   | 9,897     | 9,897        | 10,526      |

| Maximum Flux Density (flux reversals/inch)            | 9,897                                   | 9,897     | 9,897        | 10,526      |

| Track Density (tracks/inch)                           | 960                                     | 960       | 960          | 1,047       |

| Access time (including settling and transmission of s |                                         | 900       | 900          | 1,047       |

| Track-to-track: 5 milliseconds Maximum                | step puises)                            |           |              |             |

| Average: 30 milliseconds ± 10%                        |                                         |           |              |             |

| Maximum: 60 milliseconds                              |                                         |           |              |             |

| Maximum Average Latency Time: 8.33 milliseco          | onds                                    |           |              |             |

| , Mariniani Morago Datoney Time, 0.33 mmsecc          | ,1143                                   |           |              |             |

Rotational Speed: 3600 rotations/minute ± 0.1%

Data Transfer Rate: 5 megabits/second (625 kilobytes/second) \*Recording Code: Modified Frequency Modulation (MFM)

Interface: ST412/506 Compatible Start Time: Less than 25 seconds Stop Time: Less than 25 seconds

\*NOTE: All models support the use of 2.7 RLL encoding in addition to MFM. When used with a controller utilizing RLL encoding, drive capacity may be expected to increase up to 50% over the values stated above. Note that error rate criteria may vary depending upon the type of RLL encoding scheme used.

#### 1.2.3 Reliability Specifications

Mean-time-between-failures (MTBF)

Mean-time-to-repair (MTTR)

Component life

More than 20,000 power on hours less than 30 minutes 5 years

Error rate

Recoverable Errors

Unrecoverable Errors

Seek Errors

1 per 10<sup>10</sup> bits read 1 per 10<sup>12</sup> bits read 1 per 10<sup>6</sup> seeks

#### 1.2.4 Disk Defects

Disk defects are imperfections in the media surface. No unit will be shipped if surface analysis identifies more than 30, 50, 70, or 85 total defective <u>tracks</u>/drive for the V130, V150, V170, and V185 respectively. Note that even at these maximum values, only 1% of the drive capacity is unavailable. Additionally, no defects will be present on cylinder 0, heads 0, 1, and 2.

Testing for defects involves an analysis of the total media surface under marginalized test conditions. Defect information is included on the test data sheet shipped with the drive, and on the error map label affixed to the drive. Format is cylinder number, head number and bytes from index. Location accuracy is  $\pm 10$  bytes.

In a single format operation, it is probable that errors will not be detected on all of the locations defined. However, all should be considered defects and flagged by the using system to ensure long term data reliability.

The use of an error correction code (ECC) rather than cyclic redundancy check (CRC) is recommended for best data integrity.

## 2 FUNCTIONAL CHARACTERISTICS/OVERVIEW

## 2.1 General Operation

The V100 Series drives consist of read/write, head positioning and control electronics, rotary voice coil actuator, media, air filtration system, and disk spin motor.

These components perform the following functions:

- 1. Interpret and generate control signals.

- 2. Position and maintain the heads over the desired track.

- 3. Maintain precise disk rotation speed.

- 4. Read and write data.

- 5. Provide a contamination-free environment.

## 2.2 Read/Write, Servo and Control Electronics

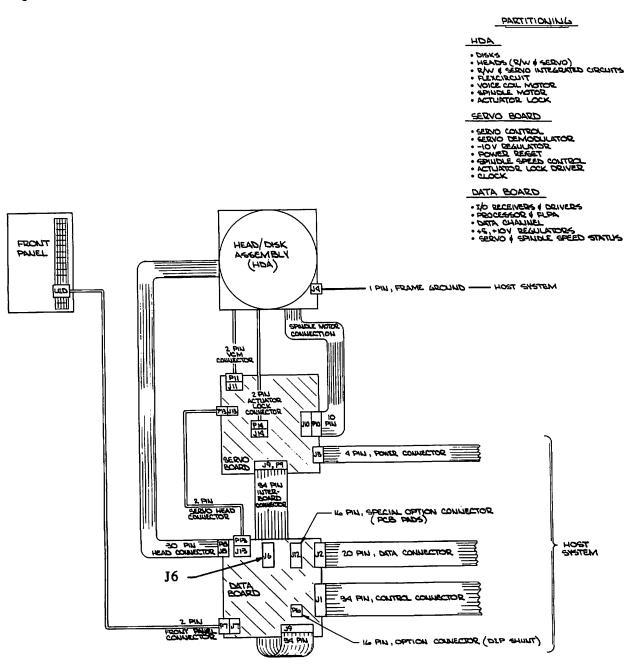

Electronics are packaged on two printed circuit boards. The outermost board, to which control and data signals are connected, includes:

- 1. R/W circuits.

- 2. Interface drivers and receivers.

- 3. Microprocessor and associated logic.

- 4. Write fault detection.

- 5. Drive selection.

- 6. Optional interface functions.

- 7. Index circuit.

The second PCB, mounted under the top board, accepts the required DC voltages and performs the following functions:

- 1. Disk spin motor control.

- 2. Head actuator positioning.

- 3. Track 0 detection.

- 4. -10 voltage regulator.

- 5. Power monitoring.

#### 2.3 Drive Mechanism

A brushless 3 phase DC drive motor rotates the spindle disk assembly at 3600 rpm. The spindle is driven directly with no belt or pulley being used. A crystal controlled phase lock loop maintains precise speed regulation. The motor and spindle are dynamically balanced to ensure a low vibration level. Dynamic braking is used to quickly stop the motor when power is removed. The base plate assembly is shock mounted to the side mounting frames to minimize transmission of vibration through the chassis or frame. Index signal is derived from a transducer inside the drive motor.

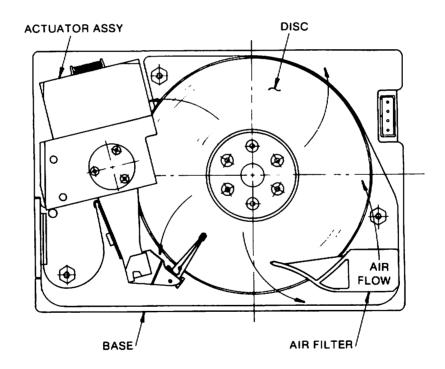

## 2.4 Air Filtration System (Figure 2-1)

The disks, read/write heads and actuator are fully enclosed in a module using an integral recirculation air system and absolute filter to maintain a clean environment. A separate filter permits ambient pressure equalization without entry of contaminants.

Figure 2-1

Air Filtration System

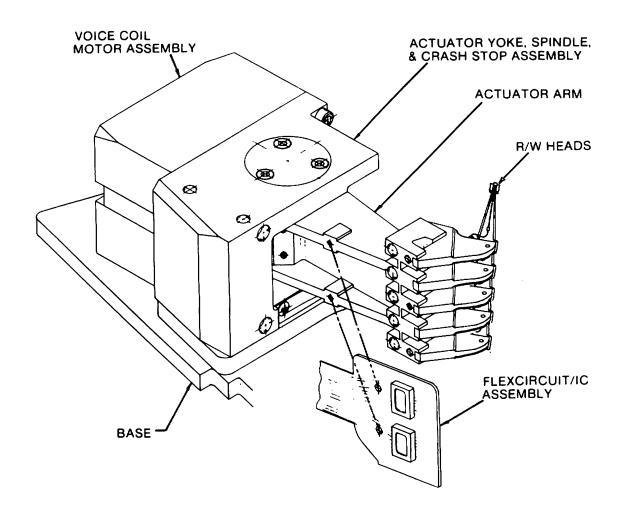

## 2.5 Positioning Mechanism (Figure 2-2)

The read/write heads and servo head are mounted onto a rotary actuator supported by precision ball bearings. A bobbin-type voice coil mounted between two permanent magnets provides the driving force required to rotate the actuator for head positioning. Crash stops are provided to protect the head assemblies should a malfunction cause the actuator to lose control. When the drive is powered down, the actuator is driven to a head landing zone on the inner diameter of the disk. Simultaneously, the actuator is automatically locked over the landing zone to prevent possible head/media damage when the drive is subjected to transport shock or movement around the office.

Figure 2-2

Read/Write Head Positioning Mechanism

### 2.6 Read/Write Heads and Disks

Winchester technology heads and media are used in the V100 Series disk drives. Maximum recording density is 10,526 flux changes per inch. The heads are connected to the external electronics via a flat flexible printed circuit cable. Three integrated circuits are mounted on the cable adjacent to the heads. The circuits provide write current, head selection, and read signal amplification. Amplification of the low level read signal prior to its leaving the sealed unit provides superior signal-to-noise ratio and less sensitivity to noise in the ground system and mounting frame.

## 2.7 Servo System

Actuator positioning and head track following is accomplished on a closed loop basis using a dedicated servo surface. During seek operations, track crossing information is used to optimize actuator deceleration. A "dual frequency" technique is used. This technique is based on amplitude differences between alternating servo tracks written at two different frequencies. On-track for a data head is realized when the servo head is positioned exactly between the two servo tracks. Essentially, the servo head continuously samples the two frequencies, sums and averages the signals, then positions the head at the point where this averaged signal is strongest—exactly between the two tracks. The resultant error signal is linearly proportional to the error (off-track) size, and indicates the off-track direction.

The dual-frequency servo offers several advantages relative to classical di-bit and tri-bit methods:

- 1. It is relatively insensitive to servo surface media defects. The di-bit/tri-bit methods generally require an "error-free" servo surface. This reduces manufacturing yields (particularly for high track density media) and increases the cost of the servo disk. Since the dual-frequency servo continuously samples fA and fB amplitudes, media defects are averaged out and not sensed by the servo.

- 2. Because the dual-frequency method uses a relative amplitude difference of fA and fB frequency, servo head azimuth alignment is not critical. This alignment is critical in di-bit and tri-bit methods, however, again raising production costs and increasing service requirements.

- Since fA and fB frequencies are recorded well below data frequencies, write data noise is easily

filtered out in the event it is injected into the servo read channel via read/write head to servo head

cross talk.

Track 0 is derived from the servo surface information, eliminating the need for a separate sensor for this purpose.

## 3 FUNCTIONAL OPERATIONS

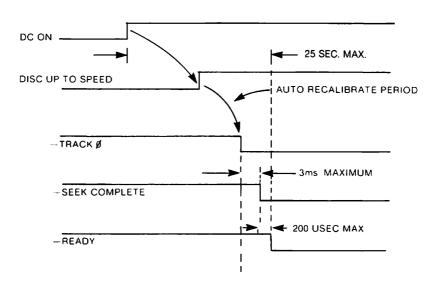

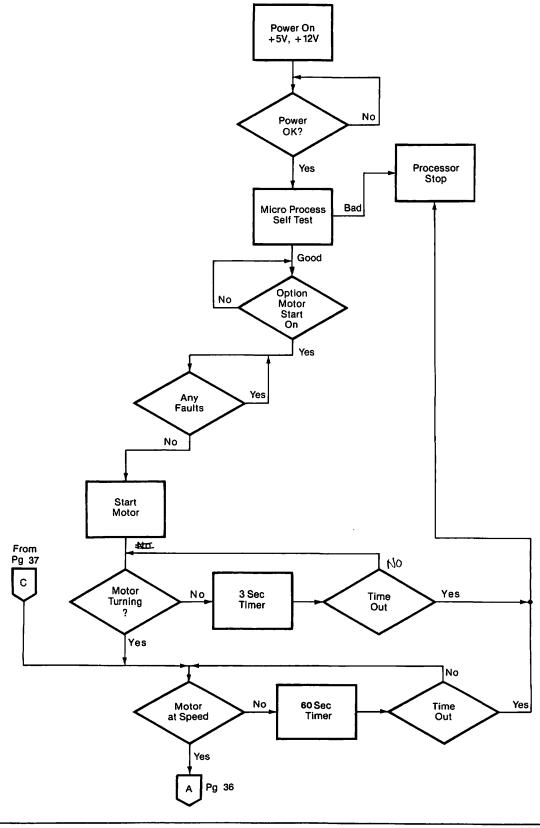

## 3.1 Power Sequencing (Figure 3-1)

Plus 5 and +12 volts may be applied in any order; however, both voltages must be applied to start the spindle drive motor. A speed sense circuit ensures the spindle is up to speed before recalibrating the heads to track  $\emptyset$ . TRACK  $\emptyset$ , SEEK COMPLETE and READY signals on the interface will become true sequentially. The drive will not perform read, write or seek functions until READY becomes true. No commands should be attempted until READY is true. STEP pulses will be ignored, and WRITE GATE will cause a WRITE FAULT.

Figure 3-1

Power Up Sequence

#### 3.2 Drive Selection

Drive selection occurs when one of the DRIVE SELECT lines is activated. Only the selected drive will respond to the input signals, and only that drive's output signals are then gated to the controller interface (see Section 5.6.1 for exception).

## 3.3 Track Accessing

Read/write head positioning is accomplished by:

- A) Deactivating WRITE GATE.

- B) Activating the appropriate DRIVE SELECT line.

- C) Being in the READY condition with SEEK COMPLETE true.

- D) Selecting the appropriate DIRECTION IN state.

- E) Pulsing the STEP line.

Each step pulse will cause the heads to move either 1 track in or 1 track out, depending on the level of the DIRECTION line. A low level on the DIRECTION line will cause a seek inward toward the spindle; a high, outward toward track  $\emptyset$ .

#### 3.4 Head Selection

Any of the heads can be selected by placing the head's binary address on the three (3) HEAD SELECT lines:

| DRIVE | NUMBER OF DATA HEADS | HEAD ADDRESSES      |

|-------|----------------------|---------------------|

| V130  | 3                    | 0, 1, 2             |

| V150  | 5                    | 0, 1, 2, 3, 4       |

| V170  | 7                    | 0, 1, 2, 3, 4, 5, 6 |

| V185  | 7                    | 0, 1, 2, 3, 4, 5, 6 |

|       |                      |                     |

## 3.5 Read Operation

Reading data is from the disk and is accomplished by:

- A) Deactivating the WRITE GATE line.

- B) Activating the appropriate DRIVE SELECT line.

- C) Assuring the drive is READY.

- D) Selecting the appropriate HEAD SELECT levels.

## 3.6 Write Operations

Writing data onto the disk is accomplished by:

- A) Activating the DRIVE SELECT line.

- B) Assuring the drive is READY and SEEK COMPLETE is true.

- C) Selecting the proper HEAD SELECT levels.

- D) Ensuring no WRITE FAULT conditions exist.

- E) Activating WRITE GATE and placing data on the WRITE DATA line.

## 3.7 System Integration Considerations

The drive is designed with sufficient margin to allow meeting specified error rates under all DC supply voltage variations and environmental conditions listed under specifications. External factors affecting error rates are the data separator in the controller and system/ground noise levels. These items subtract from the overall margin of the drive as shipped.

Examples of system/ground noise influences are:

- -Radiated and conducted noise from switching power supplies.

- -Proximity of drive to noise sources such as CRTs.

- -Circulating ground currents and ground loops in the system cabling and ground connections.

Examples in the data separator are:

- -Nominal data bit centering in the separator data window with a data pattern which exhibits no superposition bit shift.

- -Phase lock loop frequency and phase response.

## 4 THEORY OF OPERATION

#### 4.1 Overview

The V100 Series disk drive consists of a sealed head-disk assembly (HDA) containing a rotary voice-coil head positioning mechanism (actuator), media, read/write heads, a servo head, a spindle motor, and air filtration components. Also included in drive assembly, external to the HDA, are two printed circuit boards that perform read/write, servo, and interface control electronics.

Interpretation and generation of control signals are performed by a microprocessor and a programmable logic array (PLA). Positioning of the heads is achieved by driving the actuator with a dedicated track following servo system. Speed control of the spindle motor is performed by a phase-controlled driver circuit using a 360-Hz reference signal. Encoded data is written to and read from the disks by means of a read/write data channel. Write errors are reported by read preamplifier/write driver ICs in the read/write data channel. Contamination protection for the heads, actuator, and media is achieved by enclosing these components in a sealed head-disk assembly having a built-in air filter.

The following paragraphs provide a more detailed description of the disk drive components and electronic circuits, as shown in the disk drive functional block diagrams (Figures 8-1 and 9-1).

## 4.2 Head-Disk Assembly

Details of the components contained in the sealed head-disk assembly are provided in the following paragraphs.

#### 4.2.1 Actuator

The read/write heads and servo head are mounted on a rotary arm supported by precision ball bearings. A bobbin-type voice coil is attached to the rotary arm and mounted between two permanent magnets. These components comprise a rotary voice-coil head positioning mechanism (actuator). This mechanism provides the driving force required to move the rotary arm for head positioning. The magnetic field in the gap between the magnets allows the acceleration of the rotary arm to be controlled by the voice-coil current. Drive current for the voice coil is supplied by the actuator servo control circuit. Crash stops are provided to protect the heads should a malfunction cause the actuator servo control circuit to lose control. When the disk drive is powered down, the rotary arm is driven to a non-data area head landing zone at the inner diameter of the disk. Simultaneously, the arm is automatically locked over the landing zone to prevent possible head/media damage if the disk drive is inadvertently subjected to excessive shock during relocation or shipment. Drive current for the actuator lock solenoid is supplied by an actuator lock driver circuit.

#### 4.2.2 Recording Media

The recording media consists of a carbon overcoated thin film metal magnetic coating on either side of a 130-millimeter (5.12 inch) diameter aluminum substrate. In the V100 Series, there are several such disks in the sealed head-disk assembly, with up to seven surfaces used for data and one surface used for prerecorded servo information.

#### 4.2.3 Read/Write Heads

The disk drive employs Winchester technology read/write heads, one for each data surface. The heads are designed to fly above the disks supported by a thin cushion of air, which acts as an air bearing to the heads. The flying height is approximately 16 microinches at the inner diameter of the disk. When the disk drive is powered down, the actuator moves the heads to a "landing zone" at the inner diameter of the disks where the heads come to rest on the surface.

Each head consists of a gapped ferrite core mounted in a ferrite slider. There are two windings wound around the ferrite core and the windings are connected at a common point and phased such that the common point acts as a center tap. These windings are used for both reading and writing by detecting or producing a magnetic field at the tap in the ferrite core.

In a write operation, data is written by passing a current through the windings of the selected head. This current generates a flux field across the gap and aligns the magnetic particles contained in the surface of the disk. The writing process orients the poles of each magnetized particle to permanently store the direction of the flux field as the particles pass beneath the head. The direction of the flux field is a function of the write current direction. Erasing is accomplished by writing over any data which may have been previously recorded on the disk.

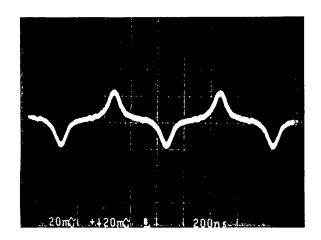

In the read operation, as the data surface passes beneath a head, the magnetically stored flux fields intersect the gap in the ferrite core. Gap motion through the flux field causes a voltage to be induced into the windings wound around the core. This induced voltage is analyzed by the read circuitry to define the data recorded on the surface of the disk. Each flux reversal, caused by a write current polarity change, generates a readback voltage pulse.

There are two read preamplifier/write driver ICs mounted on the rotary arm of the actuator, adjacent to the heads. Each IC provides write current, head selection, and read signal amplification for four read/write heads. The ICs are connected to the read/write data channel electronics external to the sealed head-disk assembly via a flexible printed-circuit cable.

#### 4.2.4 Read Preamplifier/Write Driver IC

The read preamplifier/write driver IC is a standard integrated circuit designed for disk drive read/write head control. The IC can select 1 of 4 heads, read from or write to the selected head, and supply a write fault signal. One IC is used in the V130 and there two ICs in all other V100 Series Drives. Control signals for the ICs are supplied by the head select and control logic block.

The IC is enabled by Chip Enable signal CE-L. Binary Head Select signals HS1-H, HS2-H are decoded by the IC to select the desired head. Reading and writing is controlled by Write Select signal WS. When WS is high, the write mode is selected, and when WS is low, the read mode is selected.

When the IC is in the write mode, differential current applied across the DX, DY lines is used to switch the current drawn from the write current source to the head of the selected channel. Head voltage swings, generated by the switching of write current through the inductive head, are monitored by a head transition detect circuit in the IC. Absence of proper head voltage swings indicates an open or short in either half of the head winding or an absence of write current. This will cause a current to flow into the Unsafe (US) output line. This line is connected to the fault detector which will pass a write fault message to the PLA.

When the IC is in the read mode, data is read from the selected head, amplified, and output on the differential DX, DY lines to the read chain amplifier and signal conditioner. If a fault condition exists such that write current is applied to the IC when it is in the read mode, the write current will be drawn from the Unsafe line and the fault will be detected by the fault detector.

#### 4.2.5 Servo Head

The servo head is a read-only head constructed similarly to the read/write heads. The output of the head is amplified by a servo preamplifier IC mounted on the rotary arm of the actuator.

#### 4.2.6 Servo Preamplifier IC

The servo preamplifier IC is a two-stage differential amplifier designed for use as a preamplifier for a magnetic servo head. The preamplifier output, labeled SERVO+, SERVO-, is connected to the input of the actuator servo control demodulator via the flexible printed-circuit cable used to connect the read preamplifier/write driver ICs to the read/write data channel.

#### 4.2.7 Spindle Motor

The spindle motor is a 3-phase brushless DC motor which spins the disks at a speed of 3600 rpm. Incorporated in the motor are three Hall-effect sensors which are used by the spindle speed control circuit to indicate which of the three phases should be driven. An optical sensor in the motor provides an Index signal, INDX-L.

#### 4.2.8 Air Filtration Components

A self-contained recirculating filter supplies clean air through a 0.3 micron filter to the sealed head-disk assembly. A separate filter allows for ambient pressure equalization within the sealed head-disk assembly without the induction of contaminants.

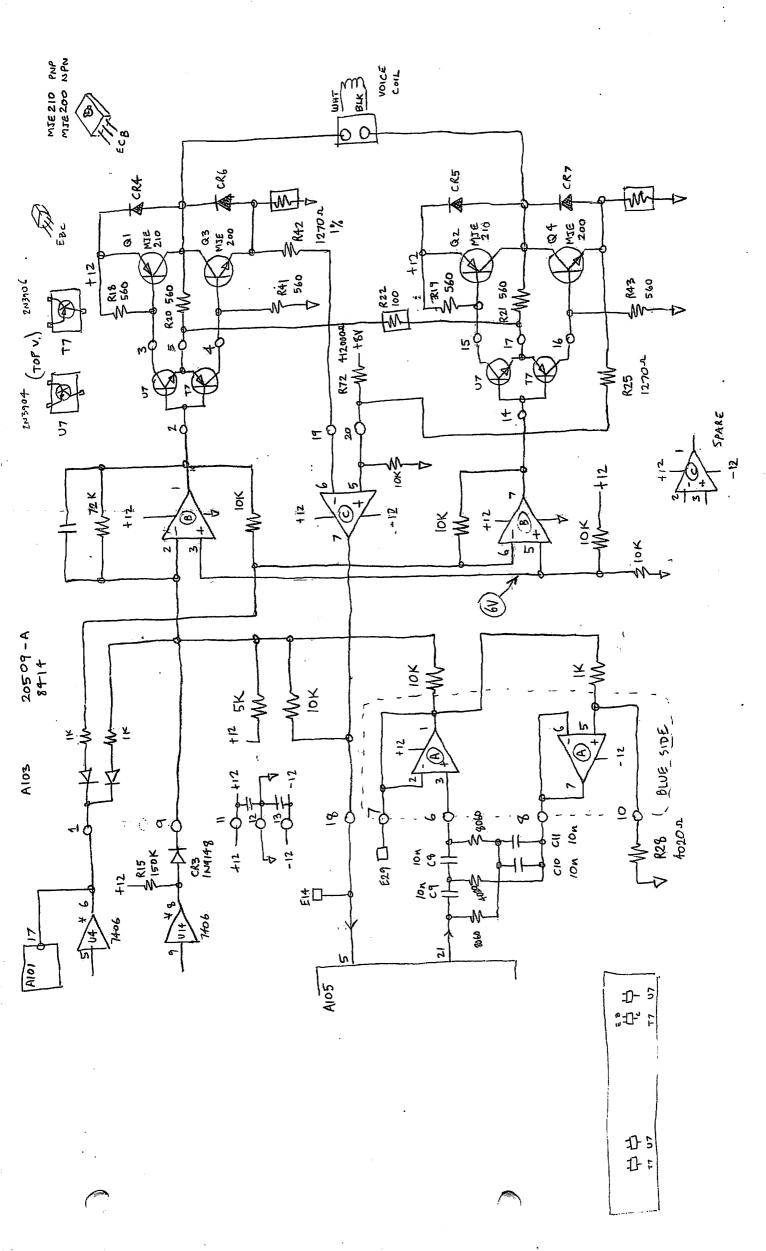

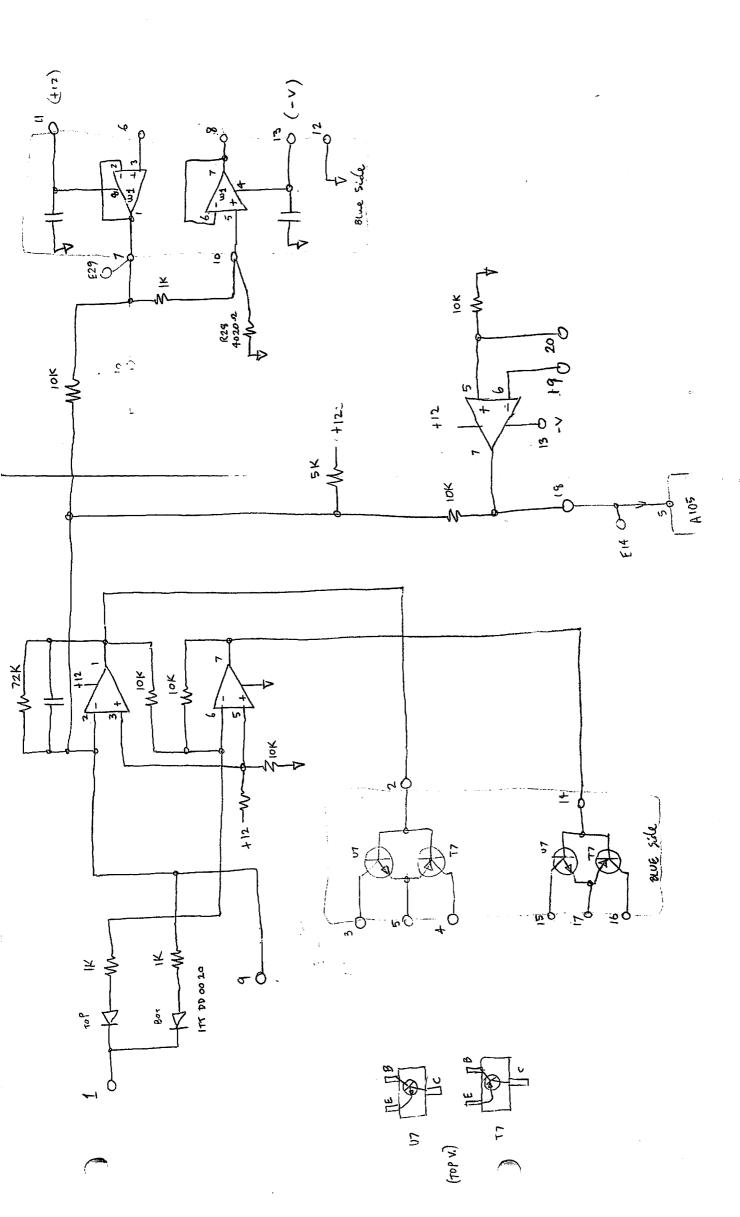

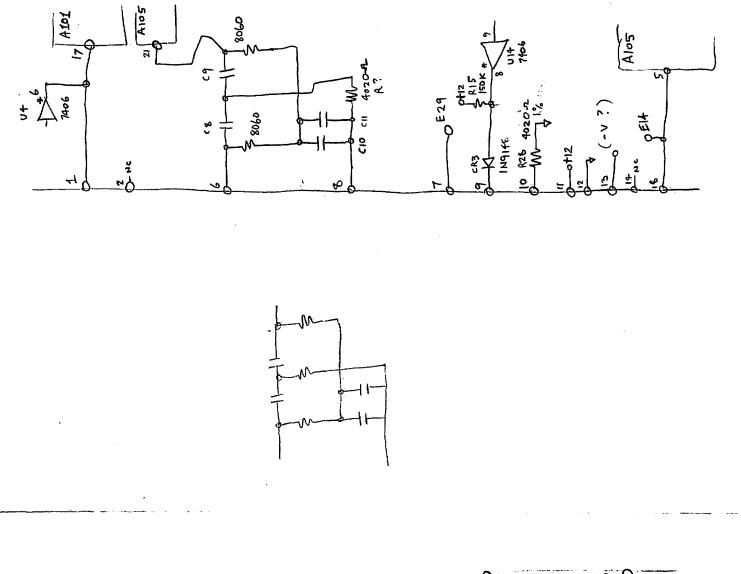

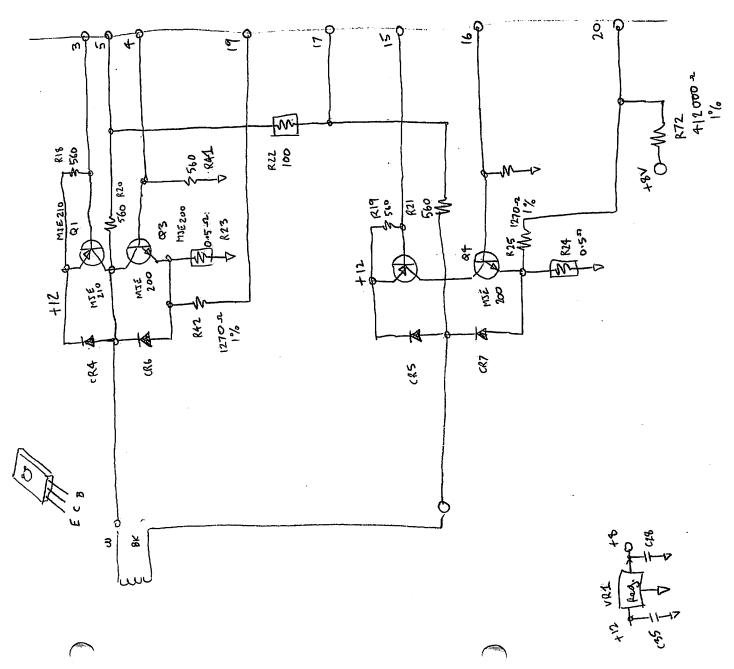

#### 4.3 Servo PCB

Functions performed by the servo PCB are described in the following paragraphs.

#### 4.3.1 Actuator Lock Driver

The actuator lock is controlled by a solenoid which is energized at power on after the microprocessor detects that the spindle motor is up to speed (At Speed signal true). At this time, the microprocessor activates its Pick line which in turn causes the actuator lock driver to energize the lock solenoid. The actuator arm is now released, allowing the heads to move over the disks.

#### 4.3.2 Clock Generator

The clock generator consists of a crystal oscillator and a number of count-down registers. The clock generator has five outputs—9.216 MHz for the microprocessor, 1152 kHz and 576 kHz for the demodulator in the actuator servo control circuit, 92.1 kHz for the spindle speed checker circuit, and 360 Hz for the spindle speed control circuit.

#### 4.3.3 Spindle Speed Control

The three Hall-effect sensor outputs from the spindle motor are input to a ROM commutator in a solid-state spindle speed control circuit which decides which of the three outputs from the circuit should be driven to spin the motor in the proper direction. The speed of the motor is controlled by a phase-lock frequency regulator which compares a 360-Hz signal from the clock generator with the signals from the three Hall-effect sensors. This regulator circuit provides feedback to drivers in the speed control circuit such that the speed of the motor is maintained at 3600 rpm, plus or minus 3.6 rpm.

At power on, after the Power On Reset signal is turned off, the microprocessor sets the Stop Motor signal false, causing the spindle motor brake to pick. At the same time, the microprocessor disables the spindle speed control circuit by deactivating the Normal Regulation line. This allows the spindle motor to accelerate without any speed regulation. The microprocessor monitors the motor speed by measuring the time interval between Index pulses. When the time interval between the pulses indicates that the speed is within one percent of 3600 rpm, the microprocessor enables the speed control circuit by activating the Normal Regulation line. The microprocessor stops the spindle motor by application of Stop Motor to the spindle speed control and relay driver circuits.

#### 4.3.4 Spindle Speed Checker

The spindle speed checker circuit monitors the speed of the spindle motor by measuring the time between Index pulses from the spindle motor Hall-effect sensor compared with a 92.1-kHz reference signal from the clock generator. The microprocessor monitors the At Speed and Counter Not Ready outputs from the speed checker circuit and shuts down operation of the disk drive if the speed is determined to be outside of a predetermined range.

#### 4.3.5 Spindle Motor Brake Relay and Relay Driver

The spindle speed control circuit includes a dynamic brake which brings the spindle motor to a rapid halt when the microprocessor issues a Stop Motor signal. Stop Motor activates the relay driver which in turn causes the spindle motor brake relay to connect low-value resistors across the winding of the spindle motor. At the same time, Stop Motor input to the speed control circuit disables the 3-phase drive to the motor.

#### 4.3.6 Actuator Servo Control

Actuator positioning and head track following is achieved on a closed loop basis using a dedicated servo surface. The servo system employs a dual frequency technique based on an amplitude difference between alternating servo tracks written at two different frequencies. On track is realized for a data head when the servo head is positioned exactly between two servo tracks. In operation, a

demodulator circuit continuously samples the two frequencies from the servo head, sums and averages the two signals, and produces a position error signal (PES). This PES signal is linearly proportional to the error (off track) amount and also indicates the off track direction.

During track following, the PES voltage is input to a transconductance amplifier which supplies drive current to the actuator voice coil. This causes the actuator to hold the servo head at a point where the PES voltage is zero—exactly between the two servo tracks. Since the servo head and the read/write heads are fixed on the rigid rotary arm of the actuator, any movement of the servo head is translated to all of the read/write heads.

The position error signal is also used during a seek operation. As the rotary arm is moving across the disks during a seek, the PES voltage develops track crossing pulses which are counted by the microprocessor to determine track location. Also, the slope of the PES voltage is used to determine the velocity of the rotary arm during the seek operation.

The dual frequency technique described above is relatively insensitive to servo surface media defects. Also, servo head azimuth alignment is not a critical factor in the operation of the system.

The actuator servo control circuitry includes a demodulator, mode select switch, tachometer, digital-to-analog converter (DAC), and amplifier. Details of these circuits are provided in the following paragraphs.

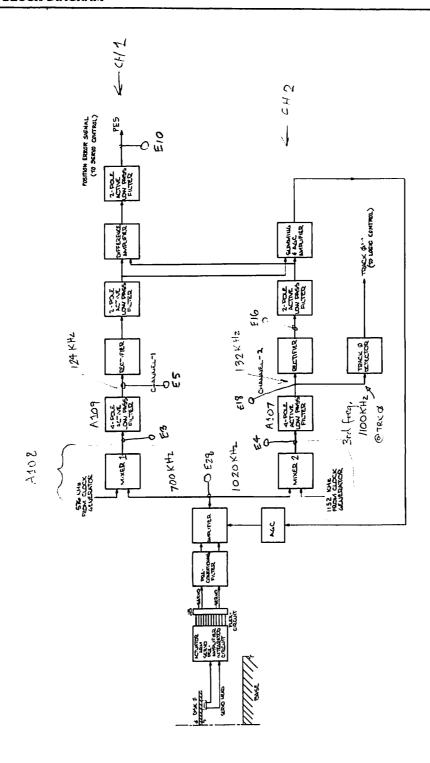

#### 4.3.7 Demodulator

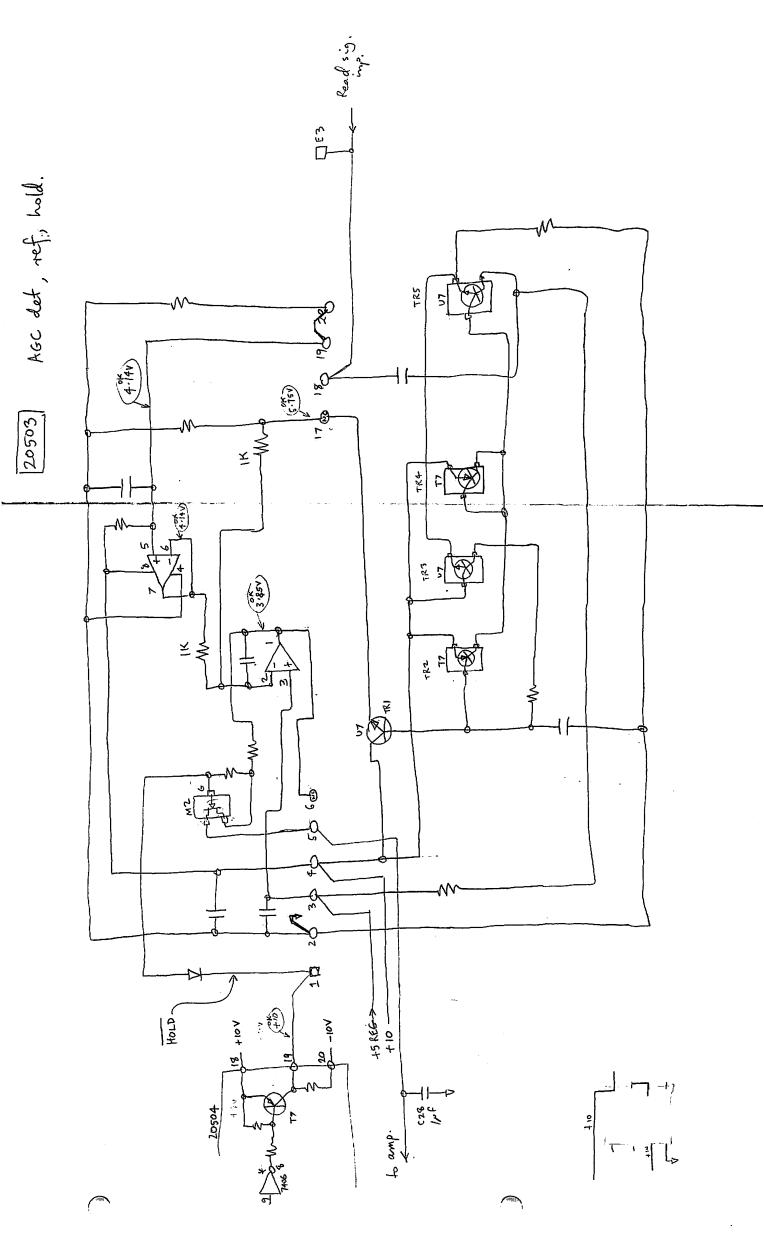

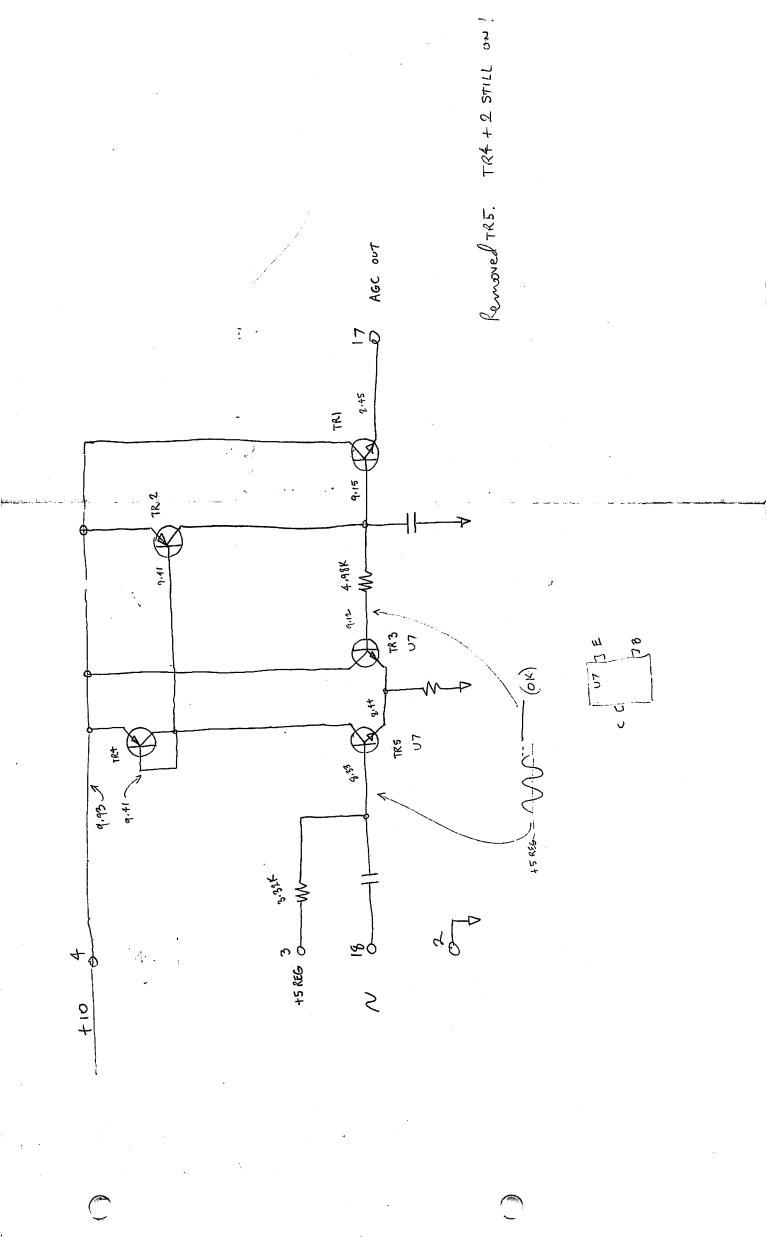

The Servo+, Servo- signal (read from the servo surface via the servo head and the servo preamplifier IC) consists of a combination of the frequencies recorded on alternate servo tracks—700 kHz and 1020 kHz. This signal is amplified and then separated into two frequencies by two identical mixer channels in the demodulator. In one channel, the 700 kHz is mixed with 576 kHz from the clock generator to produce 124 kHz. In the other channel, the 1020 kHz is mixed with 1152 kHz from the clock generator to produce 132 kHz. Higher frequencies are attenuated with active low-pass filters in the mixer channels. The two outputs from the mixer channels are rectified, averaged, and fed to the input of a difference amplifier. The output of this amplifier is Position Error Signal (PES). When the servo head is positioned exactly between two servo tracks (read/write head on track), PES is zero. Displacement from this position (read/write head off track) causes PES to go either positive or negative, depending on the direction of offset and with an amplitude equal to the amount of the offset.

The rectified and averaged outputs from the two mixer channels are also fed to a summing and AGC amplifier which supplies an AGC voltage to the amplifier at the input of the demodulator.

The demodulator also contains a track zero detector. This circuit senses the presense of a third frequency (1100 kHz) recorded on the servo surface to identify track zero. The Track 0 output from the detector is coupled to the microprocessor and the Track Zero signal TRK0-L on the ST412/506 Interface.

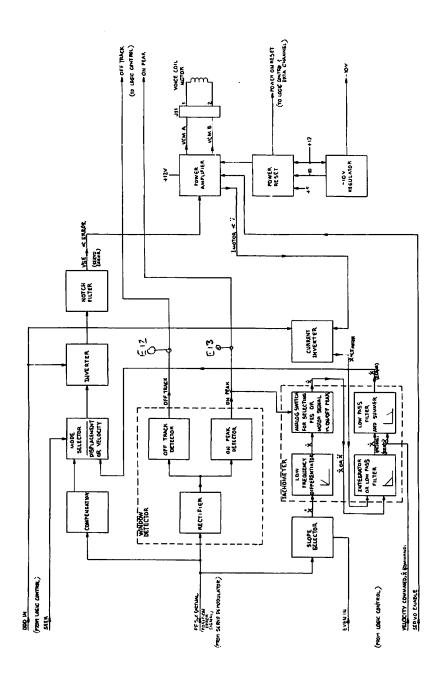

#### 4.3.8 Mode Select Switch

The mode select switch is a solid-state circuit which places the actuator servo control circuitry in either a seek (velocity) or track follow mode of operation. Operation of the switch is controlled by the Seek signal from the microprocessor.

#### 4.3.9 Seek Mode

The seek mode of operation is selected by the microprocessor when it switches the mode select switch to the seek position with the Seek line. This selects a number of circuit blocks which together comprise a negative feedback servo control system supplying drive current to the actuator voice coil. These circuits include a velocity digital-to-analog converter (DAC), tachometer, slope selector, current inverter, on-peak detector, inverter, and power amplifier.

#### 4.3.10 Velocity DAC

The velocity DAC is a standard integrated-circuit digital-to-analog converter which outputs a velocity DC voltage to the servo system in response to an 8-bit velocity command from the microprocessor.

#### 4.3.11 Tachometer

The tachometer provides a measurement of the actuator velocity by differentiating the slope of the PES signal as the actuator crosses tracks. However, the PES voltage becomes non-linear at the peaks of its triangle-shaped waveform. Therefore, at this time the power amplifier current to the actuator voice coil is integrated to provide an indication of actuator velocity.

#### 4.3.12 Slope Selector

The slope selector circuit, programmed by the Even In signal from the microprocessor, selects a PES slope of the proper polarity for the tachometer to provide a negative feedback.

#### 4.3.13 Current Inverter

The current inverter, with a gain of plus or minus one and programmed with the Odd In signal from the microprocessor, selects a current of the proper polarity from the power amplifier for input to the tachometer.

#### 4.3.14 On-Peak Detector

The on-peak detector operates at approximately 3.5 volts to initiate the switch between the differentiated PES signal and the integrated motor current in the tachometer. The output of the On-Peak detector is also coupled to the microprocessor to signal track crossings.

#### 4.3.15 Power Amplifier

The power amplifier is a transconductance amplifier which supplies current to the actuator voice coil in response to an error voltage input. The amplifier output lines are labeled VCMA, VCMB. The amplifier is enabled by the Servo Enable line from the microprocessor.

#### 4.3.16 Inverter

The inverter has a gain of plus or minus one and is programmed with signal Odd In from the microprocessor. The purpose of the inverter is to select an error voltage of the correct polarity for input to the power amplifier. The input to the inverter is from the tachometer (seek mode) or signal PES (track follow) as selected by the mode-select switch.

#### 4.3.17 Track Follow Mode

The track follow mode of operation is selected by the microprocessor at the end of a seek operation when the addressed track has been reached. Signal PES is applied via the track follow position of the mode select switch through the inverter to the input of the power amplifier. Signal Odd In from the microprocessor programs the inverter to select a PES voltage of the proper polarity to provide a negative feedback signal to the amplifier.

#### 4.3.18 Off-Track Detector

The off-track detector monitors the amplitude of the PES signal and provides an Off Track output to the microprocessor whenever the PES voltage exceeds plus or minus 1.5 volts.

#### 4.3.19 Seek Operation

The disk drive must have Ready RDY-L and Seek Complete SKCMP-L true before a seek operation can begin. With the disk drive in this state, the microprocessor is in its basic loop, monitoring Motor Speed, Off Track, and looking for either a Step STEP-L pulse or Write Gate WGATE-L, both of which are gated by Drive Select DS0-L. When a Step pulse is received, the Step signal forces Seek Complete SKCMP-L false. If Write Gate is true and Seek Complete goes false, a fault condition will

be issued, automatically deactivating the write circuitry. When a Step pulse is received and Write Gate is not true, then the microprocessor will initiate a seek operation. The microprocessor will set the direction of the seek from the information on the Direction DIR-L line. The microprocessor will also set the seek mode, at which time the actuator servo control circuit will cause the actuator to move. The speed at which the actuator moves is dependent on the rate at which the Step pulses are received. Maximum performance of the actuator is attained if the time interval between Step pulses is less than 39 microseconds.

The microprocessor counts the track crossings until there are no more step pulses and the actuator is crossing the last track. At this time, the microprocessor switches the actuator servo control from the seek mode to the track follow mode. The microprocessor now starts a settling timer and looks for an off-track condition. If an off-track condition exists, the microprocessor restarts the settling timer. This is done until the off-track condition is cleared plus settling time. Once this is accomplished, the microprocessor sets the Seek Complete SKCMP-L line.

#### 4.3.20 Restore to Track ∅ Operation

To perform a restore to track  $\emptyset$  operation, the microprocessor enables the actuator servo control circuit and moves the actuator over the data area and out of the landing zone into the outer guard band area. Once the microprocessor detects that the actuator is in the outer guard band area, the microprocessor will cause the actuator servo control circuit to settle the actuator on a data track. The microprocessor will set direction out with a slow velocity, and count the track crossings until the track zero signal is detected. The microprocessor will now cause the servo control circuit to lock onto a track and check for the track  $\emptyset$  signal. After the servo control circuit is locked onto track  $\emptyset$ , the microprocessor will initialize its maximum and minimum track counter. When this is accomplished, the microprocessor will activate Drive Ready signal DRV and Seek Complete signal SKCMP-L.

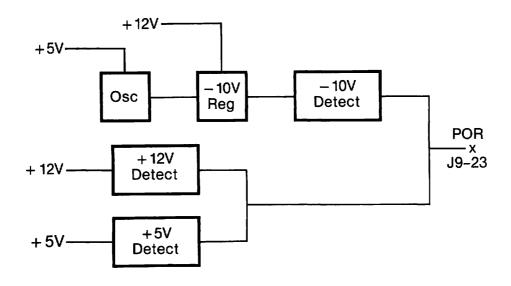

#### 4.3.21 Power On Reset (POR)

The power on reset circuit monitors the +5V, +12V, and -10V voltages in the disk drive. (The +5 and +12 voltages are input from an external power supply and the -10 volt supply is generated internally in the disk drive.) At power on, the Power On Reset output signal is active, holding the electronics in disk drive in a reset condition until the voltages reach their proper levels. During operation of the disk drive, if any one of the voltages falls below a predetermined level, Power On Reset will become active and shut down operation of the disk drive.

#### 4.4 Data PCB

Functions performed by the Data PCB are described in the following paragraphs.

#### 4.4.1 Microprocessor and PLA

The V100 Series employs a microprocessor and a programmed logic array (PLA) to control its internal operations. These devices receive commands from the device dependent controller over the control lines of the ST412/506 Interface bus. These operations include servo control, spindle speed control, read/write operations, and error/fault reporting.

The microprocessor consists of a single chip microcomputer IC which incorporates an 8-bit central processing unit (CPU), 8 kilobytes of program memory (ROM), 256 bytes of data memory (RAM), input/output lines, and a serial port. The microcomputer is clocked by an external 9.126-MHz clock generator. (This generator also provides 1.152-MHz and 576-kHz signals for the actuator servo control demodulator and a 360-Hz signal for the spindle motor speed control circuit.)

The programmed logic array is a custom-designed IC which augments the operation of the microprocessor. Functions handled by the PLA include status logic, write fault monitor, read/write selection, and step control.

#### 4.4.2 Microprocessor/PLA Control Signals

Signals generated by the microprocessor for control purposes within disk drive include: Seek, Odd In, Pick, Counter Reset, Normal Regulation, Stop Motor, Inner Track, Servo Enable, Even In, Velocity Command, Speed, and Seek Complete. PLA generated signals include Write Gate, Seek Complete, Write Fault, and Ready.

Signals input to the microprocessor from circuitry internal to disk drive include: Power On Reset, Index, At Speed, Count Not Ready, Fault, Track 0, Off Track, On Peak, Direction In, Write Gate, and 9.216 MHz clock. Internal inputs to the PLA include Power On Reset, Fault, Write Gate, Drive Select, Stop, Seek Complete, and At Speed.

#### 4.4.3 Disk Drive Control Functions

The ST412/506 Interface control signals input to disk drive via input buffers are Step STEP-L, Drive Select DS0-L, Head Select HS0-L through HS8-L, Direction DIR-L, and Write Gate WGATE-L. These signals are applied to either the microprocessor or the PLA.

The ST412/506 Interface control signals output from disk drive via output drivers are Seek Complete SKCMP-L, Track 0 TRK0-L, Write Fault WFLT-L, and Ready RDY-L. The majority of these signals are output by the microprocessor or the PLA.

Head Select lines HS0-L through HS8-L are applied via input buffers to head select and control logic which outputs Chip Enable signal CE and head select lines to the read preamplifier/write driver ICs in the sealed head-disk assembly.

#### 4.4.4 Input Buffers

The ST412/506 Interface control signals from the controller are input to the microprocessor and the PLA via schmitt trigger input buffers.

#### 4.4.5 Output Drivers

The ST412/506 control signals from disk drive are output via open-collector drivers. Each driver is capable of sinking a maximum of 48 milliamperes at its low level (true state) with a maximum of 0.4 measured at the driver. When the driver is in its high level (false state), the driver transistor is off. The output control signals are gated by a Drive Select line developed from the Drive Select input DS0-L.

#### 4.4.6 Disk Drive Data Functions

Data signals passed between disk drive and the controller are passed over the ST412/506 Interface data lines. MFM Read Data signals RMFM+, RMFM- from the read/write data channel are output to the controller via a differential line driver. MFM Write Data signals WMFM+, WMFM- from the controller are input to the drive read/write data channel via a line driver.

#### 4.4.7 Read/Write Data Channel

The read/write data channel includes head select and control logic, a read chain which amplifies and qualifies the differential MFM-encoded read signal from the read preamplifier/write driver ICs in the sealed head-disk assembly, and a write channel which converts the TTL-level MFM-encoded write data signal from the controller into write current drive for the read preamplifier/write driver ICs.

#### 4.4.8 Head Select and Control Logic

The head select and control logic block performs a hardware decode of ST412/506 Head Select signals HS0-L through HS4-L and the Write Gate signal from the PLA. The output signals from the block enable the write driver/read preamplifier IC, select one of four read/write heads, and activate the read function or write function. The output lines are labeled Chip Enable CE0-L, CE1-L; binary Head Select bits HS1-H, HS2-H; and Write Enable WS. When two ICs are used to control seven heads, Chip Enable CE0-L selects one IC for controlling heads 0 through 3, and CE1-L selects the other IC for controlling heads 4 through 6. Signals HS1-L, HS2-H, and WS are input to both ICs.

#### 4.4.9 Read Chain

The read chain receives differential voltage DX, DY from the read preamplifier portion of the read preamplifier/write driver ICs. This signal represents magnetic transitions seen by the head as it flies over the magnetic media. Whenever the head passes over a magnetic transition, the preamplifier differential output peaks. The read chain amplifies this differential analog signal and converts it to a stream of differential logic-level pulses, one for every signal peak. These MFM-encoded pulses are sent to the controller for decoding. The read chain circuitry includes an amplifier/signal conditioner stage and a differential line driver.

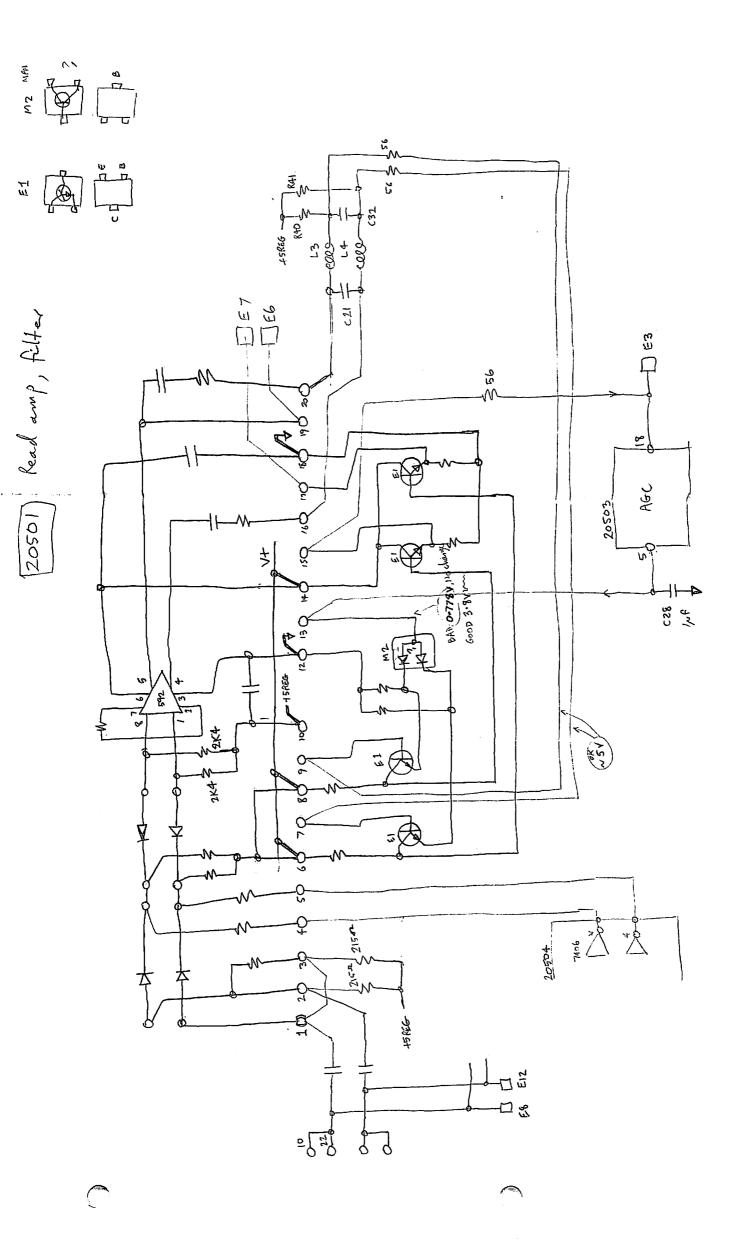

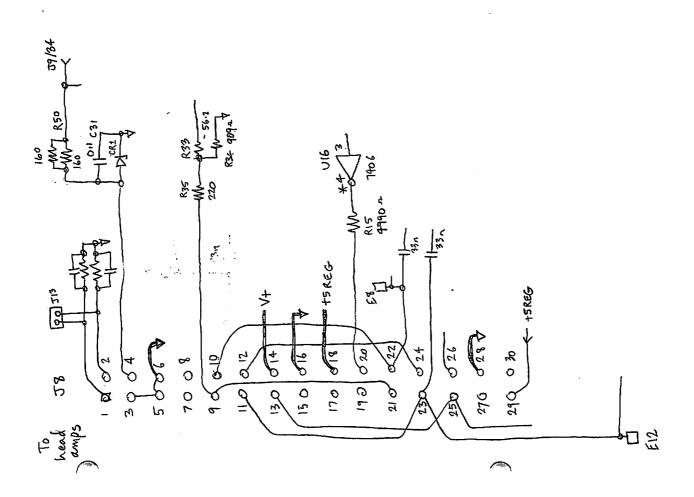

#### 4.4.10 Amplifier/Signal Conditioner

In the amplifier section of the block, the differential DX, DY input is amplified, filtered and subjected to automatic gain control (AGC). A diode matrix at the input of the amplifier, controlled by the Write Enable signal from the microprocessor, isolates the read chain from the write chain during a write operation. The AGC circuit compensates for signal variations caused by normal differences in head flying height, head characteristics, and media. The AGC circuit includes an AGC hold feature which maintains AGC control when writing. Following AGC, the signal is differentiated, filtered and input to a zero-crossing detector which converts the differential analog signals into logic-level pulses.

The signal conditioner section prevents noise in the analog input signal from producing false zero-crossings. This is achieved by applying the input of the zero-crossing detector to a gating circuit which effectively screens out spurious pulses caused by noise.

#### 4.4.11 Differential Line Driver

The qualified output signal is coupled via a differential line driver to the ST412/506 Interface. The output lines from the line driver are labeled RMFM+, RMFM-.

#### 4.4.12 Write Chain

The write chain receives differential MFM-encoded write data from the controller and converts the data to a differential signal suitable for transmission to the write driver section of the read preamplifier/write driver ICs. The write chain circuitry includes a line receiver, a transition generator, a write current source, and a write fault detector.

#### 4.4.13 Line Receiver

The line receiver translates the differential MFM-encoded write data on the ST412/506 Interface WMFM+, WMFM— lines into a single-ended format suitable for input to the transition generator. The output of the line receiver is a positive-going pulse for every magnetic transition to be written on the disk.

#### 4.4.14 Transition Generator

The transition generator divides the MFM frequency by two so that the logic level of the output determines the direction of current through the head. Each transition in MFM generates a transition on the media.

#### 4.4.15 Write Current Source

The write current source provides current for the read/write heads and supplies a write control (WC) signal to the read preamplifier/write driver ICs. The write current source is enabled by the Write Gate line from the PLA and has two outputs, selected by the Inner Track line. For tracks 0 to 511, the write current output is 32 milliamperes and for tracks 512 and above, the write current is 27.5 milliamperes.

#### 4.4.16 Write Fault Detector

During a write operation, the microprocessor monitors certain key parameters of the function via the write fault detector. If an abnormal condition is detected, the PLA activates the Write Fault signal WFLT-L. Inputs to the write fault detector include Unsafe signal US from the write driver/read preamplifier IC, and other logic lines. The faults which can cause WFLT-L to become active are discussed in sections 4.5.8 and 5.3.3.

## 4.5 Operational Sequence

The following paragraphs describe the series of events which occur from the time power is applied to the drive to the actual writing and reading of data.

#### 4.5.1 Power On Reset

Power On Reset is active, holding the drive electronics in a reset condition, until the +5 volt, +12 volt DC power supplies are on.

Figure 4-1 Power Reset

If any of the above functions fail, Power On Reset will be activated.

#### 4.5.2 Motor Start

After the POR is turned off, the microprocessor checks the Customer Option line called Start Motor to see if it is true. If so, the processor forces the Stop Motor signal false which causes the motor brake relay to pick. The processor also disables the line called Normal Regulation, thus allowing the motor to accelerate without any regulation. The processor monitors the motor speed by measuring the time between index pulses. When the time between index pulses reaches <1% of 3600 rpm, the processor activates the line called Normal Regulation.

The Motor Speed Regulator is a phase lock frequency regulator which uses 360 Hz from the driver oscillator and signals from the three Hall-Device sensors from the motor to control the speed of the motor.

The processor monitors the lines called At Speed and Count Not Ready to ensure that the motor is operating correctly throughout the rest of the time that the drive is in operation.

Reference Servo Diagrams Section 9

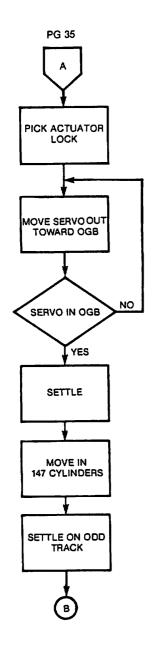

#### 4.5.3 Actuator Lock

The actuator lock is picked after At Speed is true to the processor. The processor activates the line called Pick, which in turn activates the actuator lock driver. By picking the actuator lock, this allows the actuator to move the head out into the data zone of the pack. The processor waits for a period of time before enabling the servo to ensure that the actuator lock did pick.

Reference Servo Diagrams Section 9

#### 4.5.4 Servo Restore to Track Ø

The processor enables Pick which moves the actuator over the data area and out of the landing zone to the outer guard band area. Once the processor detects that the actuator is in the outer guard band area, the processor will cause the servo to move to and settle on a data track. The processor will Set Direction Out and a slow velocity, counting track crossings until the track 0 signal is detected. The processor will cause the servo to lock onto a track and check for the track 0 signal. After the servo is locked onto a track and track 0 is activated, the processor will initialize its minimum and maximum track counter. When this is accomplished the processor will activate Drive Ready and Seek Complete.

Reference Data Board Diagrams Section 8 and Servo Board Diagrams Section 9

#### 4.5.5 Seek Operation

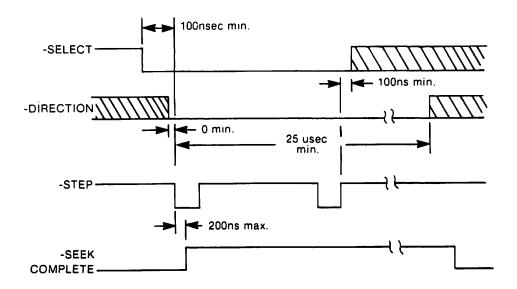

The Drive has to have Ready and Seek Complete active before a seek operation can start. With the drive in this condition, the processor is in its basic loop monitoring Motor Speed, Off Track and looking for either a Step pulse or Write Gate which are gated by Drive Select. When a Step pulse is received, the Step pulse forces Seek Complete false. If Write Gate is active and Seek Complete goes false, this will cause a fault condition to be issued, automatically deactivating the write circuitry. When a Step pulse is received and Write Gate is not active, then the processor will initiate a Seek operation. The processor will set the direction of motion from the interface line called Direction. It will also set Seek mode, at this time the servo will start to move. The speed in which the servo moves is dependent on the rate at which the Step pulses are received and the distance it has to travel. The servo will reach its maximum velocity if the pulse rate of the Step pulses is faster than 39 microseconds.

The processor counts the number of track crossings and compares it to the number of Step pulses. When the servo is crossing the last track, the processor switches the servo from Seek mode to Position mode. It starts the settling timer and looks for an Off-Track condition.

If an Off-Track condition exists, the processor restarts the settling timer. This is done until the Off-Track condition is cleared plus settling time. Once this is accomplished, the processor sets Seek Complete.

Figure 4-2 General Seek Timing

- DIRECTION change can be concurrent with the first STEP.

- DIRECTION must not be changed within 25 µsec from the leading edge of the first STEP pulse; after this time, it is latched and ignored until Seek Complete is true.

- SEEK COMPLETE will go false within 200ns after the leading edge of STEP.

- Drive cannot be deselected prior to the trailing edge of the last STEP pulse +100ns to assure detection of the last pulse.

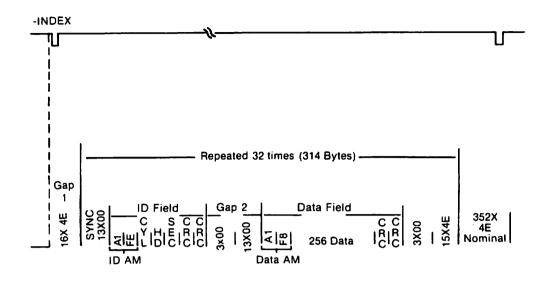

#### 4.5.6 Track Format

The purpose of a format is to organize a data track into smaller sequentially numbered blocks of data called sectors. The format is a soft sectored type which means that the beginning of each sector is defined by a prewritten identification (ID) field which contains the physical sector address plus cylinder and head information. The ID field is followed by a user supplied data field.

The format is a slightly modified version of the IBM System 34 double density format which is commonly used on floppy disk drives. The encoding method is Modified Frequency Modulation (MFM).

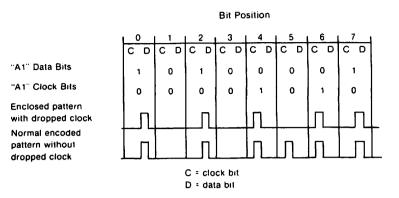

Figure 4-4 shows the track format based on 32 sectors, each having 256 bytes of user information. The beginning of both the ID and data fields are flagged by unique characters called address marks. An address mark is two bytes in length. The first byte is an "A1" data pattern. This is followed by either an "FE" pattern for an ID address mark, or an "F8" pattern for the data address mark.

The "A1" pattern is made unique by violating the encoding rules of MFM omitting one clock bit. This makes the address mark pattern unique to any other serial bit combination that occurs on the track. See Figure 4-3 depiction of the "A1" byte. Each ID and data field is followed by a 16-bit cyclic redundancy check (CRC) character used for a particular data pattern.

Surrounding the ID and Data fields are gaps to establish physical and timing relationships between these fields.

#### 4.5.6.1 GAP 1

Gap 1 is to provide for variations in Index detection. Gap 1 is 16 bytes long, but must be at least 12 bytes. Gap 1 is immediately followed by a sync field preceding the first ID field.

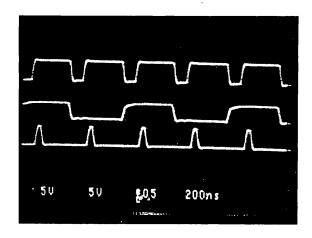

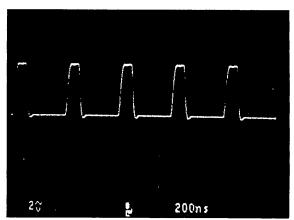

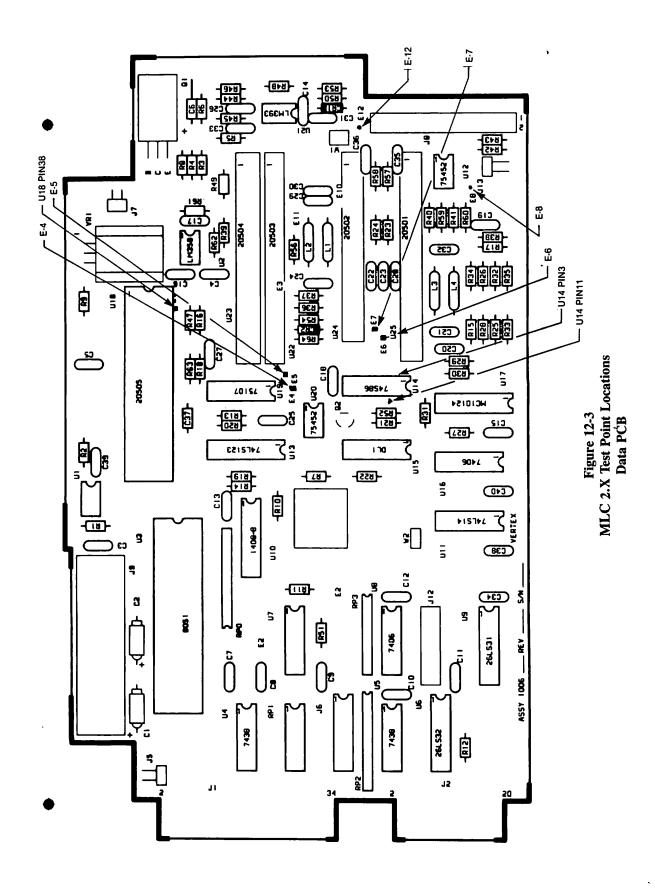

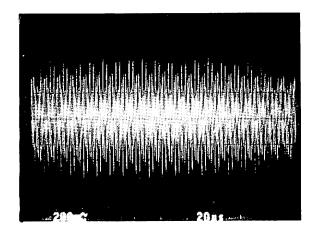

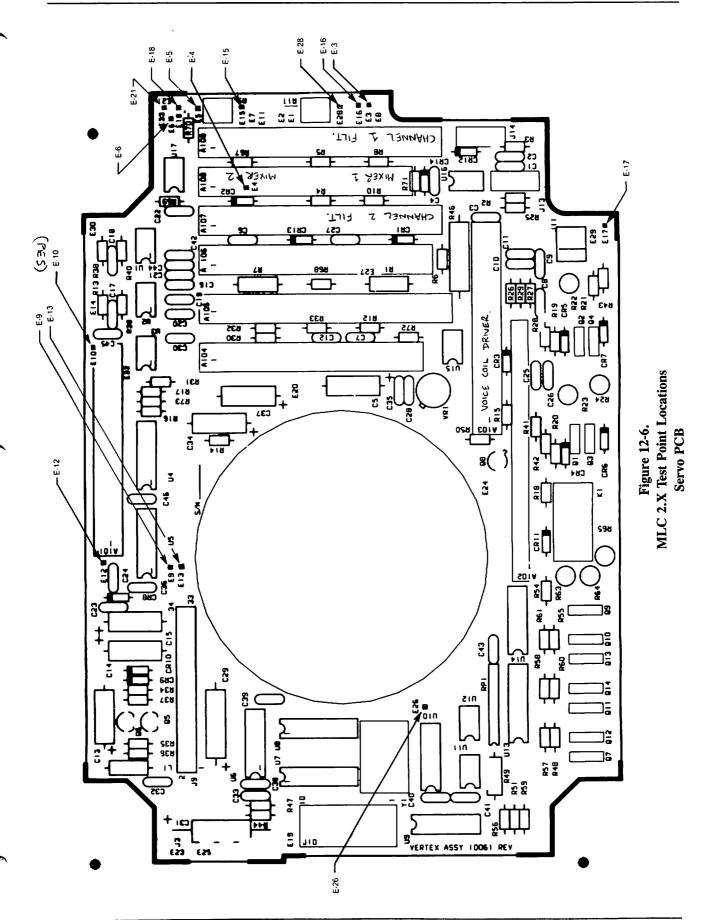

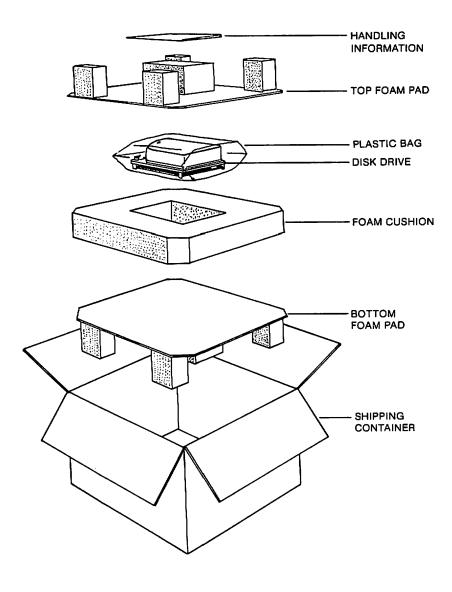

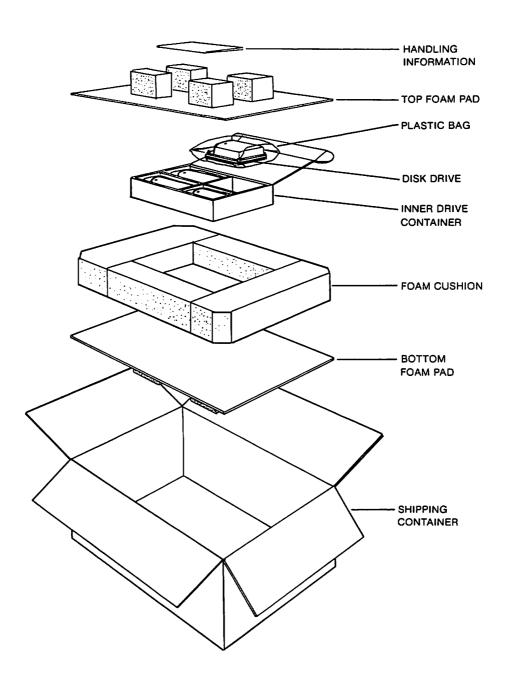

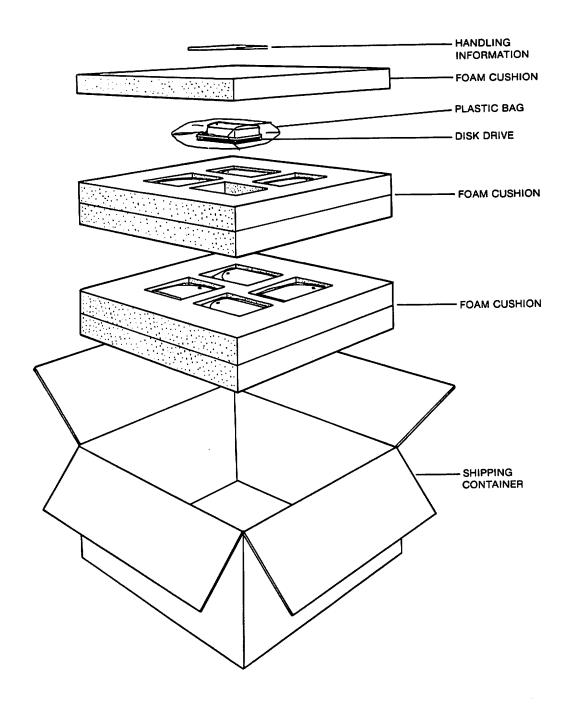

### 4.5.6.2 GAP 2