# PRIME CENTRAL PROCESSOR SUMMARY

### **Central Processor Features**

| Central Processor                            | 100  |      | 2                                     | 200                                              |                | 300          |                                               | 400          |                  | 00                                               |

|----------------------------------------------|------|------|---------------------------------------|--------------------------------------------------|----------------|--------------|-----------------------------------------------|--------------|------------------|--------------------------------------------------|

| Feature Availability                         | Std. | Opt. |                                       |                                                  |                | Opt.         |                                               |              | Std              | Opt.                                             |

| 8-channel programmable DMA system            | 1/   |      | V                                     |                                                  | √              | - P          | 1/                                            | Ори          | 1/               | Opt.                                             |

| 32-channel programmable DMA system           |      |      | •                                     |                                                  | V              |              | 1/                                            |              | 7/               |                                                  |

| Extended direct memory access (DMC, DMT)     |      | 1    |                                       | 1                                                | 1              |              | 1/                                            |              | 7/               | 1                                                |

| Direct memory queue (DMQ)                    |      |      |                                       | <del>                                     </del> |                |              | 1/                                            |              | 7/               |                                                  |

| Full control panel                           | 1/   |      | 1                                     |                                                  | 1/             |              | 7/                                            |              | 7/               |                                                  |

| Unimplemented instruction trap               | 1    |      | 1/                                    |                                                  | 1/             |              | 7/                                            |              | 7/               |                                                  |

| High-speed register file                     |      |      | · · · · · · · · · · · · · · · · · · · |                                                  |                |              | ,                                             |              |                  |                                                  |

| (32 addressable 16-bit registers)            | √    |      | √                                     |                                                  | 1/             |              | <b>v</b> /                                    |              | √                |                                                  |

| Dual register sets                           |      |      |                                       |                                                  |                |              |                                               |              |                  | <b>†</b>                                         |

| (128 addressable 32-bit registers)           |      |      |                                       |                                                  |                |              | <b>v</b> /                                    |              | <b>√</b>         |                                                  |

| 8 general purpose registers                  |      |      |                                       |                                                  |                |              | , <u>, , , , , , , , , , , , , , , , , , </u> |              | 7/               |                                                  |

| Hardware multiply/divide and                 |      |      |                                       |                                                  |                |              |                                               |              |                  |                                                  |

| double precision arithmetic                  |      | √    |                                       | √                                                | √              |              | <b>v</b>                                      |              | 7/               | Ì                                                |

| Automatic program loaders (standard devices) |      | 1    |                                       | 1                                                | 7/             |              | 1                                             |              | 7/               | <u> </u>                                         |

| Microverification routines                   |      |      |                                       | 1/                                               | - <del>√</del> |              | 1/                                            |              | <u> </u>         | <b></b>                                          |

| Processor byte parity                        |      |      | <b>√</b>                              |                                                  | 1              |              | 1/                                            |              | - <del>v</del>   | <del>                                     </del> |

| Memory byte parity                           |      |      | 1/                                    |                                                  | 1/             |              | 1/                                            |              | <u> </u>         |                                                  |

| Error correcting memory                      |      |      |                                       |                                                  |                |              |                                               | 7/           | 1/               |                                                  |

| Single- and double-precision                 |      |      |                                       |                                                  | -              |              |                                               | ,            |                  |                                                  |

| floating-point arithmetic                    |      |      |                                       | √                                                |                | √            | <b>1</b> /                                    |              | /ر               |                                                  |

| 32-bit arithmetic logic unit                 |      |      |                                       | Ť                                                |                |              | 7/                                            |              | <del>- 1</del> / |                                                  |

| 32-bit integer arithmetic                    |      |      |                                       |                                                  | 1/             |              | 7/                                            |              | _ <del>√</del>   |                                                  |

| 64-bit floating-point arithmetic             |      |      |                                       |                                                  |                |              | 7/                                            |              | 1/               |                                                  |

| Virtual memory capability (paging)           |      |      |                                       |                                                  | <b>√</b>       |              | 7/                                            | <del>-</del> | 7/               |                                                  |

| Virtual memory capability                    |      |      |                                       |                                                  |                | <del>-</del> |                                               |              |                  |                                                  |

| (paging and segmentation)                    |      |      |                                       |                                                  |                |              | √                                             |              | 7/               |                                                  |

| Stack processing instructions                |      |      |                                       |                                                  | <b>√</b>       |              | 1/                                            |              | 7/               |                                                  |

| Writable control store                       |      |      |                                       |                                                  | •              | 7            | ,                                             | 7/           | <u> </u>         |                                                  |

| 2K-byte cache (80 nanosecond cycle time)     |      |      |                                       | <del>-</del>                                     |                | , ,          | v                                             |              | 1/               |                                                  |

| Hardware process exchange                    |      |      |                                       |                                                  |                |              |                                               |              | 1/               |                                                  |

| Ring protection structure                    |      |      |                                       |                                                  | <b>√</b>       |              | 1/                                            |              | 7/               |                                                  |

| Business instructions                        |      |      |                                       |                                                  | ,              |              | , , , , , , , , , , , , , , , , , , ,         |              | 7/               |                                                  |

| Fast floating-point arithmetic               |      |      |                                       |                                                  |                |              |                                               |              | 7/               |                                                  |

## **Operational Characteristics**

| Central Processor      | 100                  | 200                   | 300                   | 400           | 500           |

|------------------------|----------------------|-----------------------|-----------------------|---------------|---------------|

| Word Size: Memory      | 16 bits              | 16 bits               | 16 bits               | 16 bits       | 16 bits       |

| Internal               | 16 bits              | 16 bits               | 16 bits               | 32 bits       | 32 bits       |

| Instruction size       | basic format 16      | oits; extended forma  | at, 32 bits           |               |               |

| Addressing             | direct, indexed a    | ınd indirect in secto | red and relative m    | nodes;        |               |

|                        |                      | e word format); and   |                       |               |               |

| Minimum-maximum        | ,                    |                       |                       |               |               |

| main memory            |                      |                       |                       |               |               |

| (K bytes $K = 1,024$ ) | 8-128 <b>K</b> bytes | 8-128K bytes          | 64-512 <b>K</b> bytes | 128K-8M bytes | 256K-8M bytes |

| Memory access time     | 680 ns.              | 600 ns.               | 600 ns.               | 600 ns.       | 600 ns.       |

# **Operational Characteristics**

| Central Processor                                 | 100                                     | 200                                       | 300                           | 400                        | 500                        |

|---------------------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------|----------------------------|----------------------------|

| Memory increment per board                        | 8K,16K,32K bytes                        | 8K,16K,64K bytes                          | 64K bytes                     | 64K, 256K bytes            | 256K bytes                 |

| Maximum program size                              | 128K bytes per pr                       | ogram                                     | 32M bytes                     | 32M bytes                  |                            |

| Maximum virtual memory space                      |                                         | _                                         | 128K bytes/user               | 32M bytes                  | 32M bytes                  |

| I/O data path                                     | 16 bits                                 | 16 bits plus 2<br>parity bits             | 16 bits plus 2<br>parity bits | 16 bits plus 2 parity bits | 16 bits plus 2 parity bits |

| Maximum DMT I/O rate                              | 1.3 Mb/sec.                             | 2Mb/sec.                                  | 2.5Mb/sec.                    | 2.5Mb/sec.                 | 2.5Mb/sec.                 |

| Addressable registers in high-speed register file | 32 (includes index<br>register, DMA add | c register, accumula<br>dresses, etc.)    | ators, stack                  | 128                        | 128                        |

| Standard instructions                             | 112                                     | 117                                       | 145                           | 318                        | 545                        |

| Optional instructions                             | 9                                       | 37                                        | 19                            | _                          |                            |

| Instruction types                                 | memory reference                        | , input/output, ger                       | eric, shift                   |                            |                            |

| Typical instruction times                         |                                         |                                           |                               |                            |                            |

| Add to memory                                     | $2.44 \mu s$                            | 1.96µs                                    | 1.56µs                        | 0.56μs                     | 0.56μs                     |

| Skip on condition                                 | 2.84-3.30μs                             | 2.04-2.32µs                               | 1.92μs                        | $1.92 \mu \mathrm{s}$      | $1.92\mu s$                |

| Hardware multiply                                 | 14μs                                    | 10.48μs                                   | 8.50μs                        | 4.20μs                     | 4.20μs                     |

| Hardware divide                                   | 18.2-19.6μs                             | 13.68-14.72μs                             | 13.50μs                       | 4.76μs                     | 4.76μs                     |

| Single Precision                                  | <del>-</del>                            |                                           |                               |                            |                            |

| Floating-Point add                                |                                         | 9.35+.48 <b>A</b> +.8 <b>n</b> µ <b>s</b> | 9.25μs                        | $5.18\mu s$                | $3.72\mu s$                |

| Floating-Point multiply                           |                                         | 27.82µs                                   | 25.20µs                       | 9.00μ <b>s</b>             | 4.02μs                     |

| Floating-Point divide                             |                                         | 39.46µs                                   | 37.90μs                       | $11.92 \mu s$              | $6.04 \mu s$               |

| Double Precision                                  | _                                       |                                           |                               |                            |                            |

| Floating-Point add                                |                                         |                                           |                               | $6.46 \mu s$               | 4.80μs                     |

| Floating-Point multiply                           |                                         |                                           |                               | $20.14 \mu { m s}$         | 6.46µs                     |

| Floating-Point divide                             |                                         |                                           |                               | $24.04 \mu s$              | 8.68µs                     |

## **Electromechanical Specifications**

| Chassis Capacity               | 5 boards                                                                     | 10 boards                                                        | 17 boards                                                          |

|--------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------|

| Chassis dimensions (W x H x D) | $45.6 \mathrm{cm} \mathrm{x}  26.7 \mathrm{cm} \mathrm{x}  49.5 \mathrm{cm}$ | $45.6 \mathrm{cm} \times 40 \mathrm{cm} \times 49.5 \mathrm{cm}$ | $45.6 \mathrm{cm} \times 66.7 \mathrm{cm} \times 49.5 \mathrm{cm}$ |

| Weight (including fans and     |                                                                              |                                                                  |                                                                    |

| power supply)                  | 22.7 kg                                                                      | 24.9 kg                                                          | 45.6 kg                                                            |

| Operating temp. range (°C)     | ()°-5()°                                                                     | 0°-50°                                                           | 0°-50°                                                             |

| Max. rel. humidity (no cond.)  | 95%                                                                          | 95%                                                              | 95%                                                                |

| Mounting                       | table top or rack                                                            | rack                                                             | rack                                                               |

| Typical heat dissipation       | •                                                                            |                                                                  |                                                                    |

| (BTU/hr.)                      | 2,000                                                                        | 3,600                                                            | 4,000                                                              |

| Voltage range (VAC)            | 190-250                                                                      | 190-250                                                          | 190-250                                                            |

| Hz (single-phase)              | 47-63                                                                        | 47-63                                                            | 47-63                                                              |

| Amps (typical)                 | 5                                                                            | 9                                                                | 10                                                                 |

| Power supply                   | 100 amp. main supply, chassis-mounted                                        | 100 amp. main supply, chassis-mounted                            | 100 amp. main supply, chassis-mounted                              |

# PRIME PERIPHERALS SUMMARY

| Storage Module Subsystem S | pecifications 300Mb | 80 <b>M</b> b        | 40 <b>M</b> b | 12Mb<br>Moving<br>Head | Diskette      |

|----------------------------|---------------------|----------------------|---------------|------------------------|---------------|

| Bytes Per Disk             | 292.7M              | 77.0M                | 38.4M         | 11.6M                  | 267.5K        |

| Bytes Per Sector           | 2,080               | 2,080                | 2,080         | 896                    | 880           |

| Sectors Per Track          | 9                   | 7 9                  | 9             | 8                      | 4             |

| Tracks Per Drive           | 15,637              | 4,115                | 2,055         | 1,624                  | 76            |

| Cylinders Per Drive        | 823                 | 823                  | 411           | 406                    | 76            |

| Average Latency Time (MS)  | 8.3                 | 8.3                  | 8.3           | 12.5                   | 83            |

| Minimum Seek Time (MS)     | 6                   | 6                    | 6             | 8                      | 20            |

| Average Seek Time (MS)     | 30                  | 30                   | 30            | 38                     | 390           |

| Maximum Seek Time (MS)     | 55                  | 55                   | 55            | 70                     | 770           |

| Transfer Rate (Bytes/Sec.) | 1.2 <b>M</b>        | 1.2M                 | 1.2M          | 325 <b>K</b>           | 31.2 <b>K</b> |

| Height                     | 36 in.              | 34 in.               | 34 in.        | 10.3 in.               | 12.2 in.      |

|                            | 91.4 cm             | 86.3 cm              | 86.3 cm       | 26.2 cm                | 30.9 cm       |

| Width                      | 23 in.              | 19 in.               | 19 in.        | 19 in.                 | 19 in.        |

|                            | 58.4 cm             | 48.2 cm              | 48.2 cm       | 48.2 cm                | 48.2 cm       |

| Depth                      | 36 in.              | 34 in.               | 34 in.        | 28.5 in.               | 20 in.        |

|                            | 91.4 cm             | 86.3 cm              | 86.3 cm       | 72.4 cm                | 50.8 cm       |

| Weight                     | 550 lbs.            | 243 lbs.             | 243 lbs.      | 130 lbs.               | 50 lbs.       |

|                            | 247.5 kg.           | 109.3 kg.            | 109.3 kg.     | 58.5 kg.               | 22.5 kg.      |

| 60Hz Start Current         | 39 Amp.             | 30 Amp.              | 30 Amp.       | 12 Amp.                | 14 Amp.       |

|                            | 208 Vac.            | 120 Vac.             | 120 Vac.      | 115 Vac.               | 115 Vac.      |

| 60Hz Run Current           | 8.0 Amp.            | 8.2 Amp.             | 8.2 Amp.      | 2.5 Amp.               | 4 Amp.        |

|                            | 208 Vac.            | 120 Vac.             | 120 Vac.      | 115 Vac.               | 115 Vac.      |

| 50Hz Start Current         | 39 Amp.             | 22 Amp.              | 22 Amp.       | 7 Amp.                 | 7 Amp.        |

|                            | 220 Vac.            | 220 Vac.             | 220 Vac.      | 220 Vac.               | 220 Vac.      |

| 50Hz Run Current           | 9.5 Amp.            | 4.9 Amp.             | 4.9 Amp.      | 1.5 Amp.               | 2 Amp.        |

|                            | 220 Vac.            | 220 Vac.             | 220 Vac.      | 220 Vac.               | 220 Vac.      |

| Operating Temperature      | 60-90°F             | 60-90°F              | 60-90°F       | 60-90°F                | 60-100°F      |

| v.<br>:                    | 15.5−32.2°C         | 15.5−32.2 <b>°</b> C | 15.5−32.2℃    | 15.5−32.2℃             | 15.5–37.7℃    |

| Operating Humidity         |                     |                      |               |                        |               |

| (non-condensing)           | 20-80%              | 20-80%               | 20-80%        | 20-80%                 | 20-80%        |

| BTU/Hr.                    | 4550                | 2390                 | 2390          | 1700                   | 1600          |

| KVA Rating                 | 1.23                | 0.70                 | 0.70          | .3                     | 0.46          |

Magnetic Tape Subsystem Specifications

# Standard Performance Subsystem

### High Performance Subsystem

| Drive Speeds     |                 |                |          |                      |                                        |                      |          |            |

|------------------|-----------------|----------------|----------|----------------------|----------------------------------------|----------------------|----------|------------|

| Forward          | 45 ips (1       | 14 cm/sec)     | 45 ips ( | 114 cm/se            | ec)                                    | 75 ips (             | (190 cm  | /sec)      |

| Rewind (nominal) |                 | 08 cm/sec)     |          | 200 ips (508 cm/sec) |                                        | 200 ips (508 cm/sec) |          |            |

| Tape Handling    | Auto-retracting |                | Auto-ret | Auto-retracting      |                                        | Vacuum               | Colum    | ın         |

|                  | buffer a        | rms            | buffer   | arms                 |                                        |                      |          |            |

| Altitude         | 0-20,000        | ft (0-6561 m)  | 0-20,000 | 0 ft (0-656          | 61 m)                                  | 0-4000               | ft (0-12 | 19 m)      |

| Tape Reel Size   | Up to 101/      | inches (26 cm) | Up to 10 | 1½ inches            | (26  cm)                               | Up to 10             | 1½ inch  | es (26 cm) |

| Recording        |                 |                |          | 100 mars             | ······································ | ·····•               |          |            |

| Format (tracks)  | 7               | 9              | 7        | 9                    | 9                                      | 9                    | 9        | 9          |

| Mode             | NRZI            | NRZI           | NRZI     | NRZI                 | PE                                     | NRZI/                | NRZI     | NRZI/      |

|                  |                 |                |          |                      |                                        | PE                   |          | PE         |

# Magnetic Tape Subsystem Specifications (Continued)

### Standard Performance Subsystem

## High Performance Subsystem

| Density (bpi)          | 556/800 | 800            | 556/800     | 800 | 1600 | 800/16  | 00 800 | 800/1600 |

|------------------------|---------|----------------|-------------|-----|------|---------|--------|----------|

| Available as 1st drive | Yes     | Yes            | No          | No  | No   | Yes     | No     | Yes      |

| Available as 2nd,      | Yes     | Yes            | Yes         | Yés | Yes  | Yes     | Yes    | Yes      |

| 3rd or 4th drive       |         |                |             |     |      |         |        | :        |

| Height                 |         | 63.5 in.       |             |     | 63   | 3.5 in. |        |          |

|                        | -       | 161.2 cm       |             |     | 16   | 1.2 cm  |        |          |

| Width                  |         | 27.2 in.       |             |     | 2'   | 7.2 in. |        |          |

|                        |         | 69.0 cm        |             |     | 69   | 9.0 cm  |        |          |

| Depth                  |         | 42 in.         | 42 in.      |     |      |         |        |          |

|                        |         | 106.6 cm       |             |     | 100  | 6.6 cm  |        |          |

| Weight                 |         | 365 lbs.       |             |     | 4    | 35 lbs. |        |          |

|                        |         | 164.2 kg.      |             |     | 19.  | 5.7 kg. |        |          |

| Power 60Hz             |         | 120 Vac.       |             |     | 1    | 20 Vac. |        |          |

| Power 50Hz             |         | 230 Vac.       |             |     | 2    | 30 Vac. |        |          |

| Operating Temperature  | 6       | 0-90°F         |             |     | 60-  | 90°F    |        |          |

|                        | 15.5-   | -32.2 <b>℃</b> | 15.5−32.2°C |     |      |         |        |          |

| Operating Humidity     | 3       | 0-80%          |             |     | 30-  | 80%     |        |          |

| (non-condensing)       |         |                |             |     |      |         |        |          |

| BTU/Hour               |         | 1025           |             |     | 29   | 00      |        |          |

# **Unit Record Device Specifications**

| •                      | Matrix<br>Printer | Chain           | Printer         | Band<br>Printer |

|------------------------|-------------------|-----------------|-----------------|-----------------|

| Speed (lpm)            |                   |                 |                 |                 |

| 64 Characters          | 200               | 300             | 600             | 1220            |

| 96 Characters          | 125               | 200             | 430             | 905             |

| Print Positions        | 132               | 132             | 132             | 132             |

| Characters per inch    | 10                | 10              | 10              | 10              |

| Lines per inch         | 6                 | 6               | 6               | 6 or 8          |

| Paper Specifications   |                   |                 |                 |                 |

| Width (inches)         | 4 to 14.875       | 3.5 to 19.5     | 3.5 to 19.5     | 5 to 18.75      |

| Number of copies       | Original plus 5   | Original plus 5 | Original plus 5 | Original plus 5 |

| Vertical Forms Control | 2 channel         | 8 channel       | 8 channel       | 12 channel      |

| Static Eliminator      | NA                | Yes             | Yes             | Yes             |

| Self Test              | NA                | Yes             | Yes             | Yes             |

| Height                 | 39.5 in.          | 1               | 0 in.           | 46.0 in.        |

|                        | 100.3 cm          | 106.            | 0 cm            | 116.8 cm        |

| Width                  | 28.0 in.          |                 | 5 in.           | 48.5 in.        |

|                        | 71.1 cm           | I .             | 7 cm            | 123.1 cm        |

| Depth                  | 24.5 in.          | 32.             | 0 in.           | 24.5 in.        |

|                        | 62.2 cm           | 1               | 2~cm            | 62.2 cm         |

| Weight                 | 150 lbs.          |                 | 0 lbs.          | 800 lbs.        |

|                        | 67.5 kg.          | 256.            | 5 <b>kg</b> .   | 360 kg.         |

| Power 60Hz             | 115 Vac.          |                 | 5 Vac.          | 230 Vac.        |

| Power 50Hz             | 230 Vac.          | 1               | 0 Vac.          | 230 Vac.        |

| Operating Temperature  | 50-105°F          | 40-9            |                 | 50-110°F        |

|                        | 10−40.5°C         | 4.4-3           | 5℃              | 10-37.7℃        |

| Operating Humidity     |                   |                 |                 |                 |

| (non-condensing)       | 5-95%             | 40-8            |                 | 10-90%          |

| BTU/Hour               | 2700              | 270             |                 | 11150           |

| KVA                    | 0.80              | 0.8             | 0               | 3.30            |

## **Unit Record Device Specifications**

|                       |                    | Card          |

|-----------------------|--------------------|---------------|

|                       | Card               | Reader/       |

|                       | Reader             | Punch         |

| Speed (cpm)           |                    |               |

| Read                  | 300                | 300           |

| Punch                 | _                  | 50-200        |

| Capacity              |                    |               |

| Hopper                | 550                | 1000          |

| Stacker               | 550                | 850           |

| Reject                | -                  | 100           |

| Card Mechanism        | Vacuum Picker      | Vacuum Pickei |

| Card Type             | 80 Column          | 80 Column     |

| Print Station         | _                  | Single line   |

| Height                | 11.0 in.           | 41 in.        |

|                       | $27.9~\mathrm{cm}$ | 104.1 cm      |

| Width                 | 19.2 in.           | 44.0 in.      |

|                       | 48.8 cm            | 111.7 cm      |

| Depth                 | 14.0 in.           | 28.0 in.      |

|                       | 35.5 cm            | 71.1 cm       |

| Weight                | 60 lbs.            | 570 lbs.      |

|                       | 27 kg.             | 256.5 kg.     |

| Power 60Hz            | 115 Vac.           | 230 Vac.      |

| Power 50Hz            | 230 Vac.           | 230 Vac.      |

| Operating             | 50-100°F           | 50-100°F      |

| Temperature           | 10−37.7°C          | 10−37.7°C     |

| Operating<br>Humidity |                    |               |

| (non-condensing)      | 40-80%             | 30-90%        |

| BTU/Hour              | 2025               | 6400          |

| KVA Rating            | 0.60               | 1.90          |

Paper Tape Reader And Reader/Punch Specifications Reader Reader/Pu

| Specifications           | Reader          | Reader/Punch   |

|--------------------------|-----------------|----------------|

| Peak Speed               | 200cps          | 200cps Read    |

|                          | •               | 75cps Punch    |

| Reading Direction        | Bidirectional,  | Bidirectional, |

|                          | under program   | under program  |

|                          | control         | control        |

| Drive Mechanism          | Stepper motor   | Stepper motor  |

|                          | and sprocket    | and sprocket   |

|                          | wheel           | wheel          |

| Reading Method           | Photoelectric   | Photoelectric  |

| Height                   | 7 in.           | 10.5 in.       |

|                          | 17.7 cm.        | 26.6 cm.       |

| Width                    | 19 in.          | 19 in.         |

|                          | 48.2 cm.        | 48.2 cm.       |

| Depth                    | 6 in.           | 12 in.         |

|                          | 15.2 cm.        | 30.4 cm.       |

| Weight                   | 15 lbs.         | 47.5 lbs.      |

|                          | 6.7 <b>kg</b> . | 21.3 kg.       |

| Power 60Hz               | 115 Vac.        | 115 Vac.       |

| Power 50Hz               | 220 Vac.        | 220 Vac.       |

| Operating<br>Temperature | 41-131 °F       | 41-131 ℉       |

|                          | 5-55 ℃          | 5–55 ℃         |

| Operating Humidity       |                 |                |

| (non-condensing)         | 10-90%          | 10-90%         |

| BTU/Hour                 | 390             | · 800          |

| KVA Rating               | 0.11            | 0.23           |

| Operating Humidity       |                 | 30.000         |

| (non-condensing)         | 10-95%          | 10-95%         |

| BTU/Hour                 | 2400            | 2400           |

| KVA Rating               | 0.70            | 0.70           |

# Electrostatic Printer/Plotter Operational Specifications

| 1                                                                                               | Low                                                                                                                                                                    | High                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TD. C                                                                                           | Density                                                                                                                                                                | Density                                                                                                                                                    |

| Typeface                                                                                        | Plot Gothic                                                                                                                                                            | Plot courier                                                                                                                                               |

| Resolution, Dots/Inch                                                                           |                                                                                                                                                                        |                                                                                                                                                            |

| Vertical and                                                                                    |                                                                                                                                                                        |                                                                                                                                                            |

| Horizontal                                                                                      | 100                                                                                                                                                                    | 200                                                                                                                                                        |

| Writing Head                                                                                    |                                                                                                                                                                        |                                                                                                                                                            |

| Configuration                                                                                   | dual array                                                                                                                                                             | dual array                                                                                                                                                 |

| Total Writing Nibs                                                                              | 1024                                                                                                                                                                   | 2112                                                                                                                                                       |

| Font, Dot Matrix                                                                                | 7 <b>x</b> 9                                                                                                                                                           | 16 x 16                                                                                                                                                    |

| Characters Per Inch                                                                             | 12.5                                                                                                                                                                   | 12.5                                                                                                                                                       |

| Columns Per Line                                                                                | 132                                                                                                                                                                    | 132                                                                                                                                                        |

| Printed Lines Per                                                                               |                                                                                                                                                                        |                                                                                                                                                            |

| Fan-fold Page                                                                                   |                                                                                                                                                                        |                                                                                                                                                            |

| (Min/factor                                                                                     |                                                                                                                                                                        |                                                                                                                                                            |

| Setting/max)                                                                                    | 1/54/61                                                                                                                                                                | 1/64/61                                                                                                                                                    |

| Printer Lines Per Inch                                                                          |                                                                                                                                                                        |                                                                                                                                                            |

| (Factory Setting)                                                                               | 6.6                                                                                                                                                                    | 8.0                                                                                                                                                        |

| Plot Width, Inches                                                                              | 10.24                                                                                                                                                                  | 10.56                                                                                                                                                      |

|                                                                                                 |                                                                                                                                                                        |                                                                                                                                                            |

| ASC11 Character Set                                                                             | 96                                                                                                                                                                     | 96                                                                                                                                                         |

| ASC11 Character Set<br>Speed Asynchronous                                                       | 1000 lpm                                                                                                                                                               | 1000 lpm                                                                                                                                                   |

| ASC11 Character Set Speed Asynchronous                                                          | 1000 lpm<br>(printer)                                                                                                                                                  | 1000 lpm<br>(printer)                                                                                                                                      |

| ASC11 Character Set<br>Speed Asynchronous                                                       | 1000 lpm<br>(printer)<br>1.2 ips                                                                                                                                       | 1000 lpm<br>(printer)<br>1.0 ips                                                                                                                           |

| Speed Asynchronous                                                                              | 1000 lpm<br>(printer)                                                                                                                                                  | 1000 lpm<br>(printer)                                                                                                                                      |

| Speed Asynchronous Simultaneous                                                                 | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)                                                                                                                          | 1000 lpm<br>(printer)<br>1.0 ips<br>(plotter)                                                                                                              |

| Speed Asynchronous Simultaneous Print/Plot                                                      | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)<br>standard                                                                                                              | 1000 lpm<br>(printer)<br>1.0 ips<br>(plotter)<br>standard                                                                                                  |

| Speed Asynchronous Simultaneous                                                                 | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)<br>standard<br>38 in.                                                                                                    | 1000 lpm<br>(printer)<br>1.0 ips<br>(plotter)<br>standard<br>38 in.                                                                                        |

| Speed Asynchronous  Simultaneous Print/Plot Height                                              | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm                                                                                         | 1000 lpm<br>(printer)<br>1.0 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm                                                                             |

| Speed Asynchronous Simultaneous Print/Plot                                                      | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.                                                                               | 1000 lpm<br>(printer)<br>1.0 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.                                                                   |

| Speed Asynchronous  Simultaneous Print/Plot Height  Width                                       | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm                                                                    | 1000 lpm<br>(printer)<br>1.0 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm                                                        |

| Speed Asynchronous  Simultaneous Print/Plot Height                                              | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.                                                          | 1000 lpm<br>(printer)<br>1.0 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.                                              |

| Speed Asynchronous  Simultaneous Print/Plot Height Width Depth                                  | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.<br>45.7 cm                                               | 1000 lpm<br>(printer)<br>1.0 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.<br>45.7 cm                                   |

| Speed Asynchronous  Simultaneous Print/Plot Height  Width                                       | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.<br>45.7 cm<br>160 lbs.                                   | 1000 lpm<br>(printer)<br>1.0 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.<br>45.7 cm<br>160 lbs.                       |

| Speed Asynchronous  Simultaneous Print/Plot Height Width Depth Weight                           | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.<br>45.7 cm<br>160 lbs.<br>72 kg.                         | 1000 lpm<br>(printer)<br>1.0 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.<br>45.7 cm<br>160 lbs.<br>72 kg.             |

| Speed Asynchronous  Simultaneous Print/Plot Height  Width  Depth  Weight  Power 60Hz            | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.<br>45.7 cm<br>160 lbs.<br>72 kg.<br>115 Vac.             | 1000 lpm<br>(printer)<br>1.0 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.<br>45.7 cm<br>160 lbs.<br>72 kg.<br>115 Vac. |

| Speed Asynchronous  Simultaneous Print/Plot Height  Width  Depth  Weight  Power 60Hz Power 50Hz | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.<br>45.7 cm<br>160 lbs.<br>72 kg.<br>115 Vac.<br>230 Vac. | 1000 lpm (printer) 1.0 ips (plotter)  standard 38 in. 96.5 cm 19 in. 48.2 cm 18 in. 45.7 cm 160 lbs. 72 kg. 115 Vac. 230 Vac.                              |

| Speed Asynchronous  Simultaneous Print/Plot Height  Width  Depth  Weight  Power 60Hz            | 1000 lpm<br>(printer)<br>1.2 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.<br>45.7 cm<br>160 lbs.<br>72 kg.<br>115 Vac.             | 1000 lpm<br>(printer)<br>1.0 ips<br>(plotter)<br>standard<br>38 in.<br>96.5 cm<br>19 in.<br>48.2 cm<br>18 in.<br>45.7 cm<br>160 lbs.<br>72 kg.<br>115 Vac. |

### DESCRIPTION

The Prime 400 is a fast, large-capacity processor that offers an economical combination of high-speed computation and large virtual memory. Compatible with all other Prime processors, it runs software written for multi-user Prime 500, 350, and 300 systems and single-user Prime 100 and 200 systems. It runs programs up to 32 million bytes long. It supports up to 63 simultaneous users. It is logically compatible with all Prime peripherals, controllers, and I/O interfaces, so users can make plug-in upgrades from other Prime processors quickly and easily at a fraction of the total system cost. And its performance and capacity features give it up to a three-to-one speed increase over the Prime 300.

With features like cache memory, segmented and paged memory management and high-speed data transfer rates, the Prime 400 is a powerful and versatile processor for large-scale interactive data processing and computational timesharing systems. The Prime 400 is also ideally suited for distributed processing applications that off-load batch-oriented mainframes, and networks that use smaller Prime processors.

## **FEATURES**

- Up to 32 million bytes of virtual address space per user

- Up to 63 simultaneous users

- Segmented and paged virtual memory management

- Optionally available error correcting MOS main memory expandable to 8 million bytes

- 2K-byte, 80 nanosecond access cache memory

- Embedded operating system for fast user access to all operating system resources

- Hardware-implemented rings of protection for system and user software security

- Automatic microprogrammed system integrity monitor

- Microcode word parity checking

- Hardware stack architecture to optimize shared procedures

# PERFORMANCE FEATURES

Prime 400 users will be immediately aware of two fundamental characteristics: the processor is very fast, and the memory and peripheral configurations it supports are very large. The features of the processor's architecture responsible for the nearly three-to-one increase in speed compared to the Prime 300 are:

STACK ARCHITECTURE. Prime 400 programs operate in an environment consisting of a stack segment (containing all local variable values), an instruction or procedure segment, and a linkage segment

(containing statically allocated variables and linkages to common data). Especially efficient addressing modes are provided to access stack and linkage variables. Hardware implemented CALL and RETURN instructions eliminate software stack management routine overhead.

The Prime 400's stack structure optimizes the efficiency of such operations as parameter passing, subroutine and procedure calls, arithmetic expression evaluation and dynamic allocation of temporary storage and context switching.

CACHE MEMORY. A high-speed 80 nanosecond access 2K-byte, bipolar memory acts as a buffer between the central processor and main memory. Using a complex algorithm to determine what main memory information the central processor will most likely use, the cache memory significantly increases the apparent speed of the main memory. The cache algorithm assures a better than 85% "hit rate", reducing the effective main memory cycle time to approximately 400 nanoseconds. Memory mapping is completely overlapped with cache memory access, further reducing total instruction times.

HIGH-SPEED ARITHMETIC UNIT. The Prime 400 does all arithmetic and logical operations in its 32-bit-wide arithmetic unit. Processing data using a 32-bit format, rather than a 16-bit format, significantly improves the execution times of single- and double-precision integer and floating point arithmetic instructions. Also, the design of the arithmetic unit permits complex address formation, such as base plus displacement plus indexing calculations.

MICROPROGRAMMED CONTROL STORE. A comprehensive microcode structure reduces both the number of microcode steps and the time required for each step in an instruction execution cycle. For example, an add instruction is completed in two microcode steps, compared to five in the Prime 300.

INTERLEAVED MAIN MEMORY. The Prime 400 stores consecutive memory locations on separate memory boards, and uses two-way interleaving to speed up sequential memory accesses and maximize the cache hit rate. In effect, interleaving provides 32-bit transfers between the memory and CPU by allowing the processor to read or write two 16-bit words at a time.

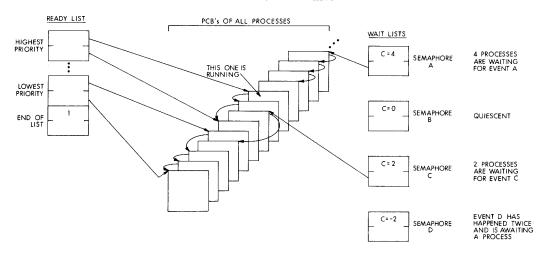

**DUAL REGISTER SETS.** The Prime 400 processor has 128 32-bit hardware registers organized in two separate sets. These registers handle such functions as controlling the processor's 32 high-speed DMA channels and storing machine states during process exchange operations. The processor's process exchange mechanism dynamically and automatically assigns register sets to processes.

PROCESS EXCHANGE. A combination of hardware and firmware automatically allocates central processor resources to the highest priority process (a continuously executing sequence of machine code) in a queue of processes ready for execution. Process exchange handles the swapping of machine states necessary for coordinating between processes ready for execution and those waiting for a specific event to occur. Pirmware within the process exchange mechanism automatically dispatches the next ready process of execution, without software intervention.

### REAL & VIRTUAL MEMORIES

The Prime 400, like all other Prime central processors, uses MOS main memory. The processor can address up to 8 million bytes of main memory. Using 16K-bit memory chips, Prime offers up to 256K bytes of memory on a standard 16 x 18 inch (40.6 x 45.7cm) circuit board. The main memory's effective access time of 600 nanoseconds is nearly as fast as the central processor because of the Prime 400's 2K-byte cache memory. The cache is an integral part of the central processors, rather than being located on the main memory boards. This prevents memory bus delays from slowing down cache-to-processor transfers.

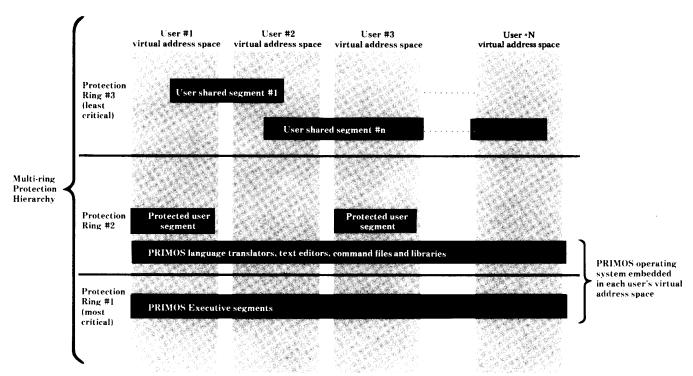

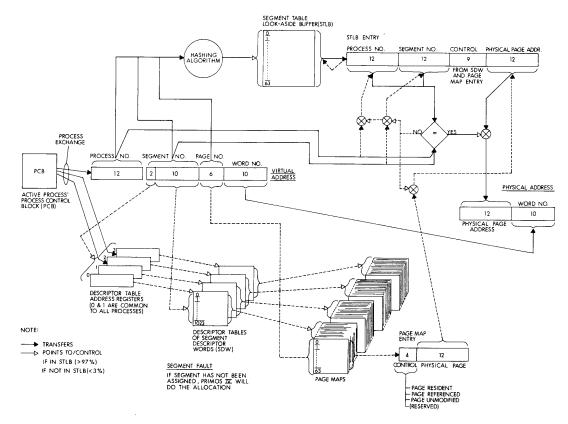

The Prime 400 uses virtual memory management facilities to provide multiple users with individual address spaces far in excess of the system's physical memory. These include both segmentation and paging, and provide all system users with individual virtual address spaces of 32 million bytes. Each user's address space consists of 128K-byte segments, half of which are available for user programs and half for PRIMOS operating system software. By embedding operating system functions in each user's virtual memory space, all operating system functions are immediately available as if they were an integral part of a user's program, reducing system overhead.

### SYSTEM INTEGRITY FEATURES

The Prime 400 features powerful and flexible error detection capabilities. Parity checking is provided throughout the processor and main memory. Microverification routines, invoked either automatically or under program control, test the validity of the central processor's logic and use a diagnostic status word to indicate the cause of a malfunction. A machine-check mode of operation lets the user establish the remedial actions the system will take when it detects data errors or hardware fault conditions.

The processor is also equipped with a comprehensive, hardware-controlled memory protection system. A multi-ring protection hierarchy lets users assign programs to any of several security levels. Thus, multiple users can have open access to specified programs, while other programs and databases can be protected against unauthorized access, and operating system software can be guarded against accidental user intrusion.

## INSTRUCTION SET

The Prime 400's instruction repertoire is a compatible superset of the machine instructions available with smaller Prime central processors. Addressing mode compatibility assures that user programs written for any other Prime processor can run on the Prime 400 without modification.

In addition to its compatibility with smaller Prime processors, the Prime 400 offers unique addressing modes and instructions that significantly expand its processing power. Over 80 instructions, including 32-bit arithmetic, NOTIFY and WAIT, and conditional store, provide better operating system communication, enhanced data handling capabilities and cooperating process communication. Also, enhanced address formation allows all instructions, both new and old, to use any combination of four user-accessible base address registers, two index registers and 32-bit indirect words. This permits all instructions to reference a virtual memory space of up to 32 million bytes, compared to the Prime 300's 128K-byte maximum.

# INPUT/OUTPUT

Direct-to-memory input/output operations are supported by three types of program-assignable I/O channels. Thirty-two program-assignable DMA channels, controlled by high-speed channel address registers, provide high throughput with a minimum of central processor control overhead. The channels have a maximum data rate of 2.5 million bytes per

second. DMC channels, controlled by channel address words in the cache memory, offer an unlimited number of channels for medium-speed I/O transfers. The DMC channels have a maximum transfer rate of 960K bytes per second. DMT channels are provided for device controllers, such as the controllers for moving-head disks, that execute channel control programs. The maximum DMT throughput rate is 2.5 million bytes per second.

In addition to these direct-to-memory channels, a DMQ mode of operation provides a circular queue for handling communication devices. The queue reduces operating system overhead by eliminating interrupt handling on a character-by-character basis.

# SYSTEM SOFTWARE

A single, multifunction operating system—PRIMOS—provides all control functions necessary to support multiterminal, batch, and multitask real-time operations. PRIMOS is embedded in each user's virtual memory space, assuring rapid access to operating system resources by user programs. The operating system supports shared, reentrant procedures, so multiple users can share a single copy of a software module, such as a FORTRAN compiler. In addition to FORTRAN IV, PRIMOS also supports BASIC, BASIC/VM, ANSI '74 COBOL, RPG II, and Macro Assembler languages. PRIMOS includes database-oriented file management resources that permit multiple keyed accesses to on-line data bases.

PRIMOS VIRTUAL MEMORY MANAGEMENT

| PRIME 400 CPU |        |

|---------------|--------|

|               |        |

|               | ME     |

|               | 40     |

|               | $\sim$ |

# DESCRIPTION

The Prime 500 is the newest and most powerful member of Prime's family of hardware- and software-compatible central processors. It runs software previously written for single-user Prime 100 and 200 systems, as well as user programs written for multiuser Prime 300 and 400 systems, without modification. And since it is logically compatible with all Prime peripheral devices, controllers and I/O interfaces, plug-in upgrades from other Prime processors are easily accommodated at a small fraction of the total system cost. The Prime 500 also offers new performance enhancements for floating-point arithmetic, decimal arithmetic, character manipulation and editing operations, and can provide better than a three-to-one performance improvement, depending on the instruction mix, over the Prime 400.

With features such as cache memory, segmented memory management and new high-speed instructions, the Prime 500 is a powerful and versatile base for large-scale Prime systems providing interactive data processing and computational timesharing services. The Prime 500 is also ideally suited for distributed processing applications involving the off-loading of batch-oriented mainframes and networks including smaller Prime processors.

# **FEATURES**

- 32M-byte virtual address space

- Up to 63 simultaneous users

- · Segmented and paged virtual memory management

- Error correcting MOS main memory expandable to 8M bytes

- 2K-byte, 80 nsec access cache memory

- Business instructions for decimal arithmetic, character manipulation, and editing operations

- · High-speed floating-point arithmetic unit

- 32-bit arithmetic unit

- Dual sets of 64, 32-bit registers for fast context switching via process exchange

- Eight, 32-bit general registers

- · 32-bit internal decor

- Embedded operating system for fast user access to all operating system resources

- Hardware-implemented rings of protection for system and user software security

- Automatic microprogrammed system integrity monitor

- Microcode word parity checking

- Hardware stack architecture to optimize shared procedures

# PERFORMANCE FEATURES

Users of the Prime 500 will be immediately aware of two fundamental characteristics: the processor is very fast, and the memory and peripheral configurations it can support are very large. The processor shares many of the high-performance features of the Prime 400 and adds to this performance base a new, high-speed floating-point arithmetic unit, direct hardware execution of business instructions, and an expanded instruction set that supports the processor's eight general registers. The most significant features of the Prime 500's architecture responsible for its high performance levels are described below.

**BUSINESS INSTRUCTIONS.** The Prime 500 provides high-level support for ANSI '74 COBOL and other business-oriented languages through comprehensive instructions designed for decimal arithmetic, character field manipulation, and editing operations.

Decimal arithmetic operations support packed or unpacked signed numbers of up to 18 digits. Operands differing in data type and/or scale factor are automatically handled during add, subtract, multiply, and divide, and comparison operations. Rounding may be specified on numeric operations and instructions are provided for binary/decimal and decimal/binary conversions.

Character operations can be performed on field sizes of virtually any length. Operations for moves, compares, translates, searches, etc. automatically handle justification, truncation, and padding. Numeric and character editing instructions are provided which easily produce fields in ANSI '74 COBOL-like picture formats.

Business-type operations are performed with a limited number of in-line instructions and, depending on the instruction mix, performance can be improved three or more times compared with the Prime 400.

FAST FLOATING-POINT ARITHMETIC. Users of Prime 500 systems can expect instruction execution times for single- and double-precision floating-point arithmetic to be comparable to those of the considerably more expensive IBM System 370 Model 158. Users upgrading from a Prime 400 can run all existing programs without any modification, and can expect an approximate three-to-one improvement in floating-point instruction performance, depending on the particular floating-point instructions involved.

One of the reasons for the Prime 500's fast floating-point speeds is the use of parallel logic in the floating-point arithmetic unit. Thus, binary multiplication is done four bits at a time, division is done three bits at a time and addition 48 bits at a time. This is significantly faster than the single bit algorithms traditionally used for multiply and divide. Separate logic handles exponents, control, and interim values, so that exponent and fraction calculations are done concurrently with arithmetic processing.

TYPICAL FLOATING-POINT TIMES CHART

| Instruction                                   | Prime 400                   | Prime 500                  | IBM 370/158             |  |

|-----------------------------------------------|-----------------------------|----------------------------|-------------------------|--|

| Single Precision<br>Add<br>Multiply<br>Divide | 5.18 μsec.<br>9.00<br>11.92 | 3.72 μsec.<br>4.02<br>6.40 | 2.4 μsec.<br>2.3<br>8.9 |  |

| Double Precision                              | 6.46                        | 4.90                       | 9.9                     |  |

| Multiply                                      | 20.14                       | 4.80<br>6.46               | 2.2<br>3.6              |  |

| Divide                                        | 24.04                       | 8.68                       | 23.2                    |  |

**STACK ARCHITECTURE.** Prime 500 programs operate in an environment consisting of a stack segment (containing all local variable values), an instruction or procedure segment, and a linkage segment (containing statically allocated variables and linkages to common data). Highly efficient addressing modes are provided to access stack and linkage variables. Hardware implemented CALL and RETURN instructions eliminate the overhead of software stack management routines.

The Prime 500's stack structure has been designed to optimize the efficiency of such operations as parameter passing, subroutine and procedure calls, arithmetic expression evaluation and dynamic allocation of temporary storage and context switching.

CACHE MEMORY. A high-speed (80 nanosecond access) 2-K byte, bipolar memory acts as a buffer between the central processor and main memory. Using a complex algorithm to determine the main memory information that will most likely be used next by the central processor, the cache memory increases the apparent speed of the main memory to near that of the processor. The cache algorithm assures a better than 85% "hit rate". Memory mapping is completely overlapped with cache memory access for further reduction of total instruction execution times.

HIGH-SPEED INTEGER ARITHMETIC UNIT. All integer arithmetic and logical operations are performed in the processor's 32-bit wide arithmetic unit. Using a 32-bit format, rather than a 16-bit format, significantly improves the execution times of single- and double-precision integer arithmetic. Additionally, the design of the arithmetic unit permits complex address formation, such as base plus displacement and indexing, to be efficiently handled.

MICROPROGRAMMED CONTROL STORE. A highly efficient microcode structure, like that used on the Prime 400, assures high-speed instruction execution. The number of microcode steps as well as the time required for each step in an instruction execution cycle has been significantly reduced compared to smaller Prime processors, so that an add instruction, for example, is completed in two microcode steps versus five on a Prime 300.

INTERLEAVED MAIN MEMORY. Consecutive memory locations are on separate memory boards so that two-way interleaving can be used to speed up sequential memory accesses and maximize the cache hit rate. In effect, interleaving provides 32-bit transfers between memory and CPU by allowing the processor to read or write two 16-bit words at a time.

DUAL REGISTER SETS. The processor is equipped with 128, 32-bit hardware registers. These registers handle a variety of functions such as controlling the processor's 32 high-speed DMA channels and storing machine states in dual register sets during process exchange operations. Assignment of these register sets to processes is managed dynamically and automatically by the process exchange mechanism of the processor.

PROCESS EXCHANGE. A combination of hardware and firmware automatically controls the allocation of CPU resources to the highest priority process (a continuously executing sequence of machine code) in a queue of processes ready for execution. Process exchange handles the swapping of machine states necessary for coordinating between processes ready for execution and those waiting for a specific event to occur. Firmware within the process exchange mechanism automatically dispatches the next ready process for execution, without software intervention.

### **REAL & VIRTUAL MEMORIES**

The Prime 500, like all other Prime CPU's, uses MOS main memory exclusively. The processor can address up to 8M bytes of main memory. The main memory's access time of 600 nanoseconds is reduced to near that of the central processor through the use of a 2K byte cache memory. The cache is an integral part of the CPU, rather than being located on the main memory boards, thereby preventing memory bus delays from slowing down cache-to-processor transfers.

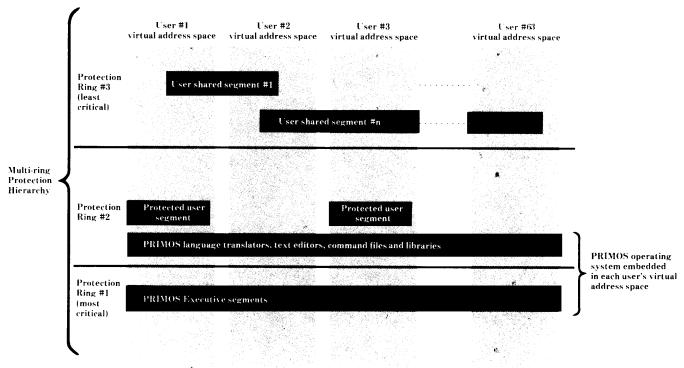

To provide multiple users with individual address spaces far in excess of the physical memory available with a system, the Prime 500 CPU is equipped with virtual memory management facilities. These facilities include both segmentation and paging, and provide all system users with individual virtual address spaces. Each user's address space consists of 128K-byte segments, half of which are available for user programs and half for PRIMOS operating system software. By embedding operating system functions in each user's virtual memory space, all operating system functions are immediately available as if they were an integral part of a user's program, thereby reducing system overhead.

PRIMOS VIRTUAL MEMORY MANAGEMENT

# PRIME 500 CPUI

### **System Integrity Features**

The Prime 500 shares the same powerful and flexible error detection features available on the Prime 400. Parity checking is provided throughout the processor and main memory. Microverification routines can be invoked, either automatically or under program control, to test the validity of the CPU's logic and indicate, via a diagnostic status word, the cause of a malfunction. A machine-check mode of operation allows the user to establish the remedial actions the system will take upon detection of data errors or hardware fault conditions. Additionally, the parity of each control word (microcode) is automatically checked.

The processor is also equipped with a comprehensive, hardware-controlled memory protection system. A multi-ring protection hierarchy allows programs to be assigned to any of several security levels. Thus, multiple users can have open access to specified programs, other programs and databases can be protected against unauthorized access, and operating system software can be guarded against accidental user intrusion.

### **Instruction Set**

The Prime 500's instruction repertoire is a compatible superset of the machine instructions available with smaller Prime CPU's. Addressing mode compatibility is also provided so that user programs written for any single-user Prime 100 or 200 or any multiuser Prime 300 and 400 will run without modification on the Prime 500.

The Prime 500 features instructions that support the processor's eight general registers, and instructions for decimal arithmetic, character manipulation, and editing operations.