Prime Computer, Inc.

## FDR3059-101B **Assembly Language** Programmer's Guide Rev. 16.3

The Assembly Language Programmer's Guide

## The Assembly Language Programmer's Guide

by Rosemary Shields

Published by Prime Computer, Incorporated Technical Publications Department 145 Pennsylvania Avenue, Framingham, MA 01701 Copyright © 1981 by Prime Computer, Inc. Third Printing January 1981 All rights reserved.

The information contained in this document is subject to change without notice and should not be construed as a commitment by Prime Computer, Incorporated. Prime Computer assumes no responsibility for any errors that may appear in this document.

This document reflects the software as of Master Disk Revision Level 16.

PRIMOS® is a trademark of Prime Computer, Inc. Credits.

## **Concept and Production**

William I. Agush

Typesetting.

Allied Systems

Covers.

Mark-Burton

Text.

Eastern Graphics

## 1 INTRODUCTION

Introduction 1-1 Organization and usage 1-1 Related documents 1-1

## 2 CONVENTIONS

Prime conventions 2-1

Instruction description conventions 2-1

Function group definitions 2-2

Table 2-1. Function definitions 2-3

Format definitions 2-3

Table 2-2. Format definitions 2-3

General data structure 2-3

Table 2-3. Data structures 2-4

Processor characteristic 2-5

Table 2-4. Processor characteristics 2-5

Terminal session example 2-5

## 3 ASSEMBLING

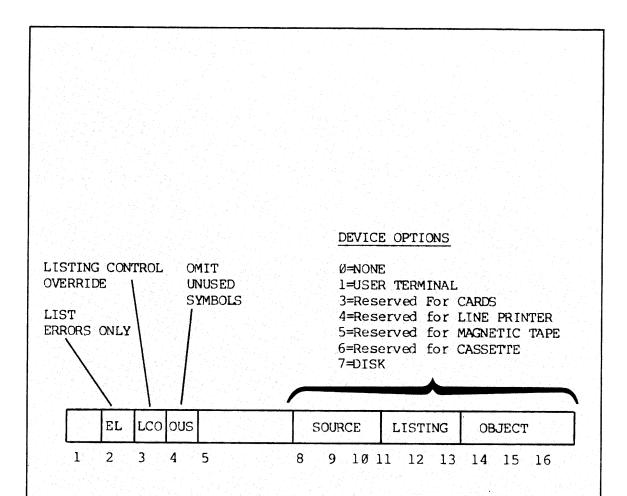

Invoking the Prime Macro Assembler (PMA) 3-1

File usage 3-1

Assembler messages 3-2

Listing format 3-2

Figure 3-1. A-Register details 3-3

Figure 3-2. Example of assembly listing 3-4

## 4 LOADING R-MODE PROGRAMS

Introduction 4-1

Using the loader under PRIMOS 4-1

Normal loading 4-1

Load maps 4-3

Loader concepts 4-4

Figure 4-1. Examples of load maps 4-7

Command summary 4-8

## **5** LOADING SEGMENTED PROGRAMS

Introduction 5-1

Using SEG under PRIMOS 5-1

Normal loading 5-2

Load maps 5-3

Figure 5-1. Example of load map 5-5

Advanced SEG features 5-7

Command summary 5-8

SEG-level commands 5-9

LOAD subprocessor commands 5-10

MODIFY subprocessor commands 5-13

## 6 EXECUTING

Execution of unsegmented runfiles 6-1 Execution of segmented runfiles 6-2 Installation in the command UFD (CMDNC0) 6-2 Run-time error messages 6-5

## 7 DEBUGGING

Tools 7-1 Advanced debugging techniques 7-2 Debugging-PRIMOS severe errors 7-2 Memory overflow errors 7-3

## **8** INTERFACING WITH THE SYSTEM LIBRARIES

Table 8-1. System libraries 8-1 Figure 8-1. SR Subroutine CALL conventions 8-2 Figure 8-2. VI subroutine CALL conventions 8-3

## 9 DATA AND INSTRUCTION FORMATS—SRVI

Data structures 9-1

Processor characteristics 9-8

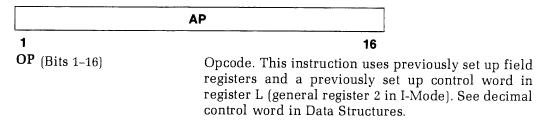

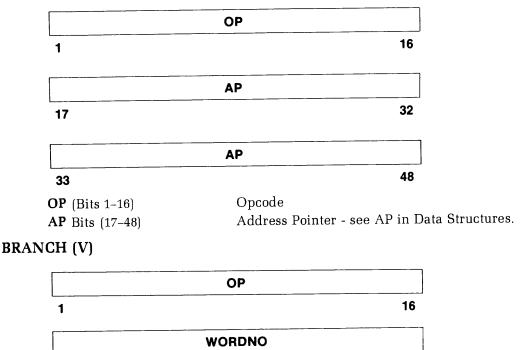

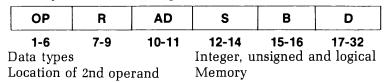

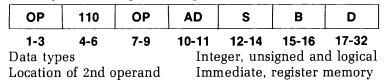

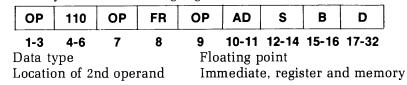

Instruction formats—I-mode 9-16

Table 9-1. Address formation special case selection 9-18

## 10 MEMORY REFERENCE CONCEPTS (SRV)

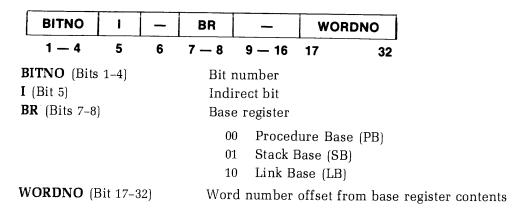

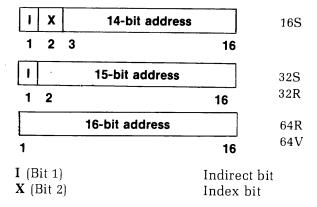

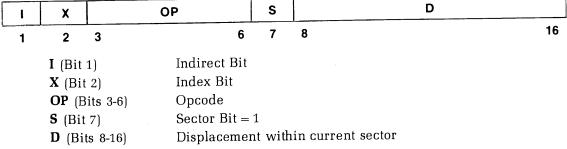

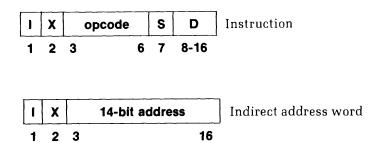

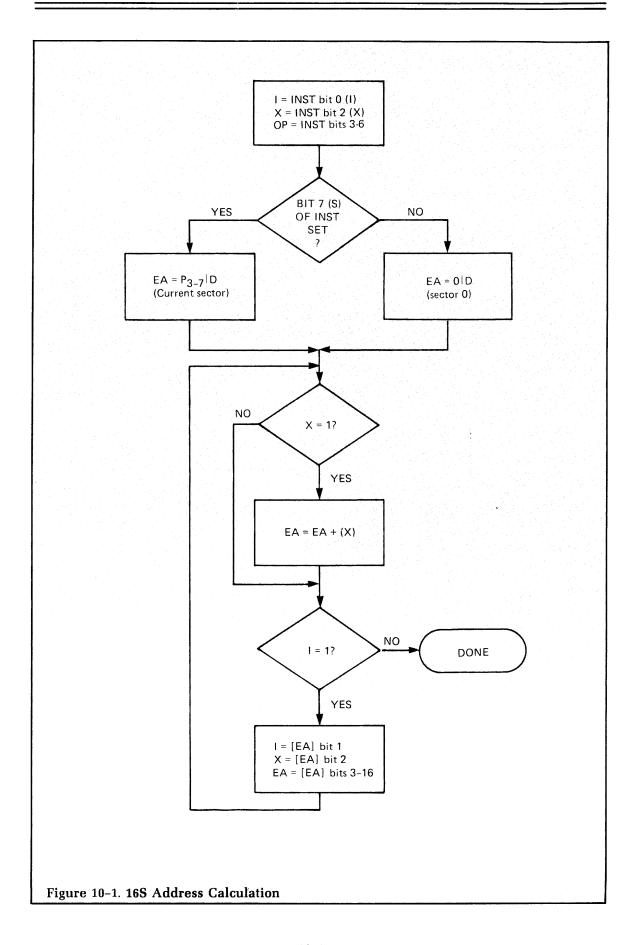

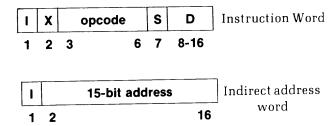

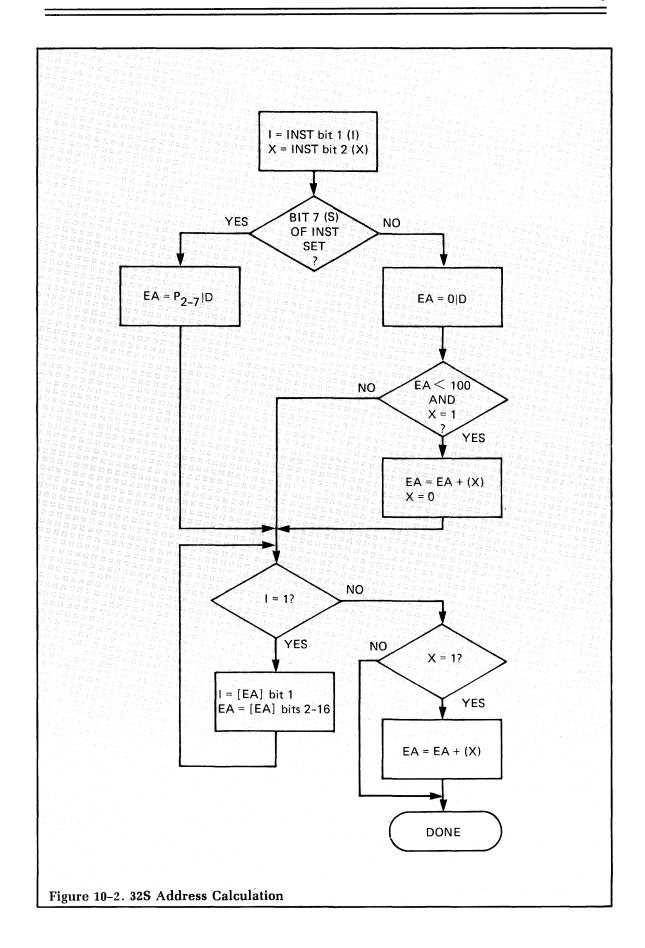

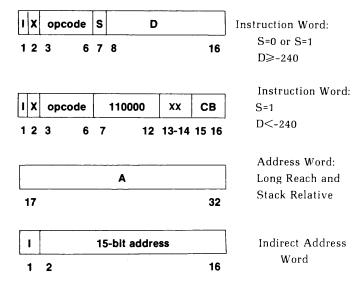

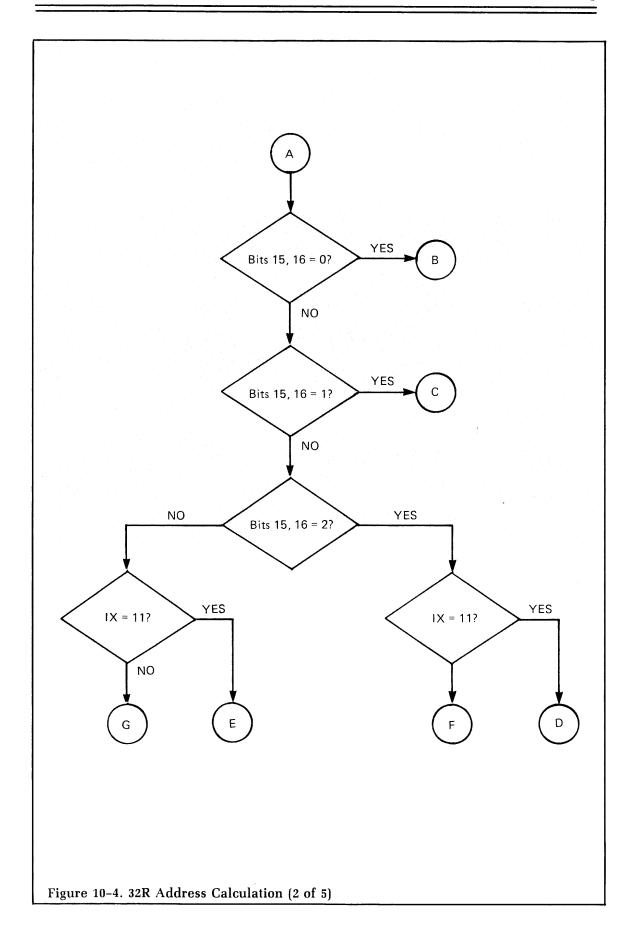

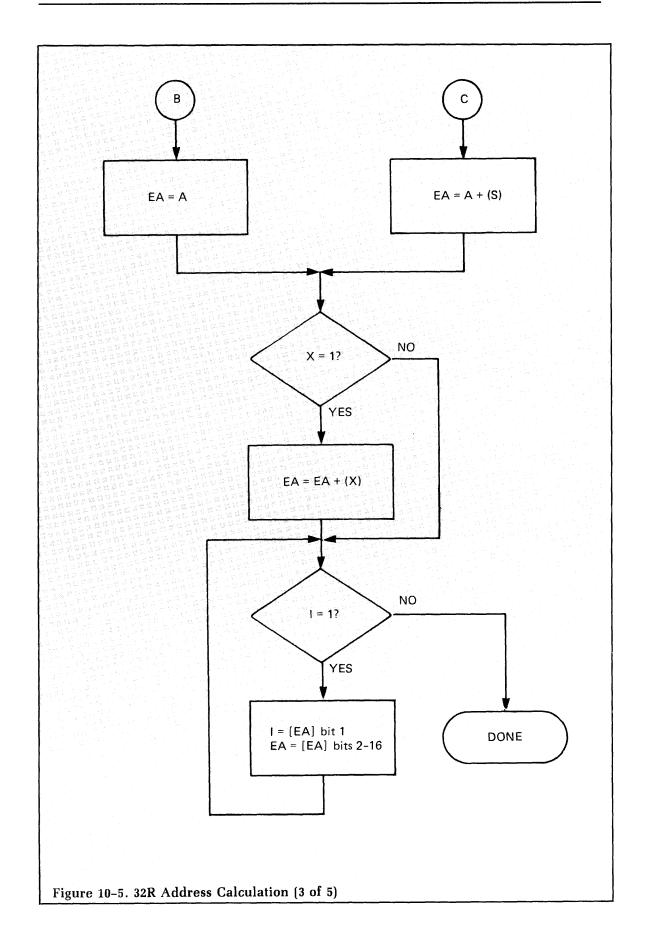

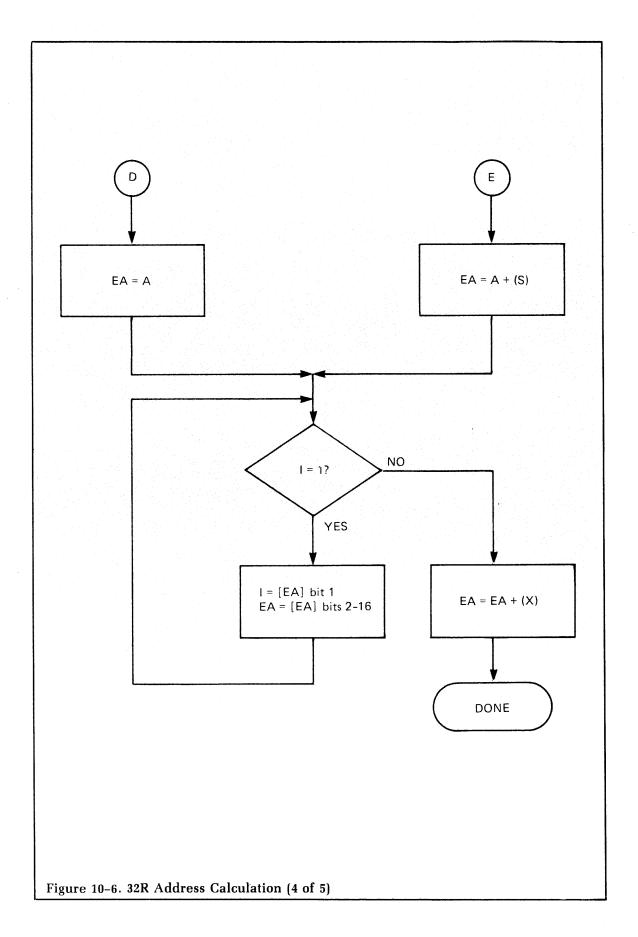

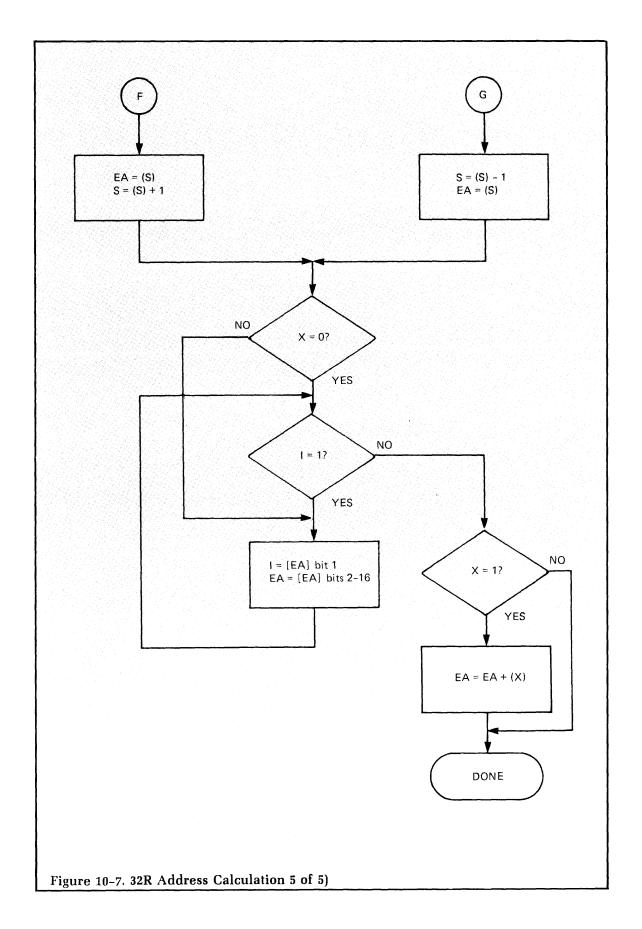

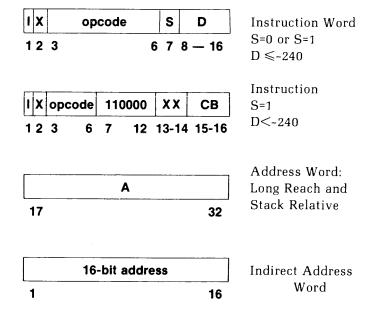

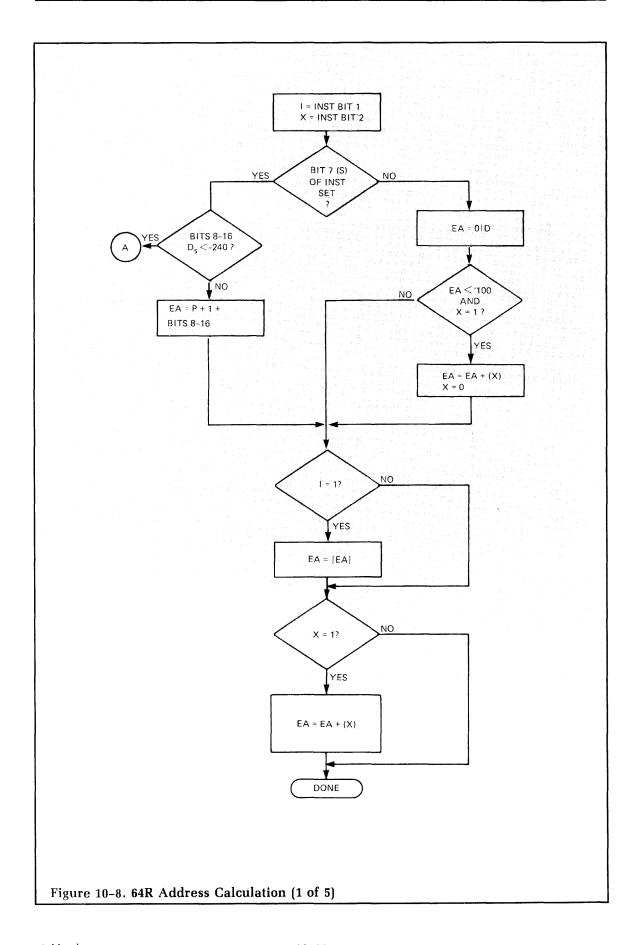

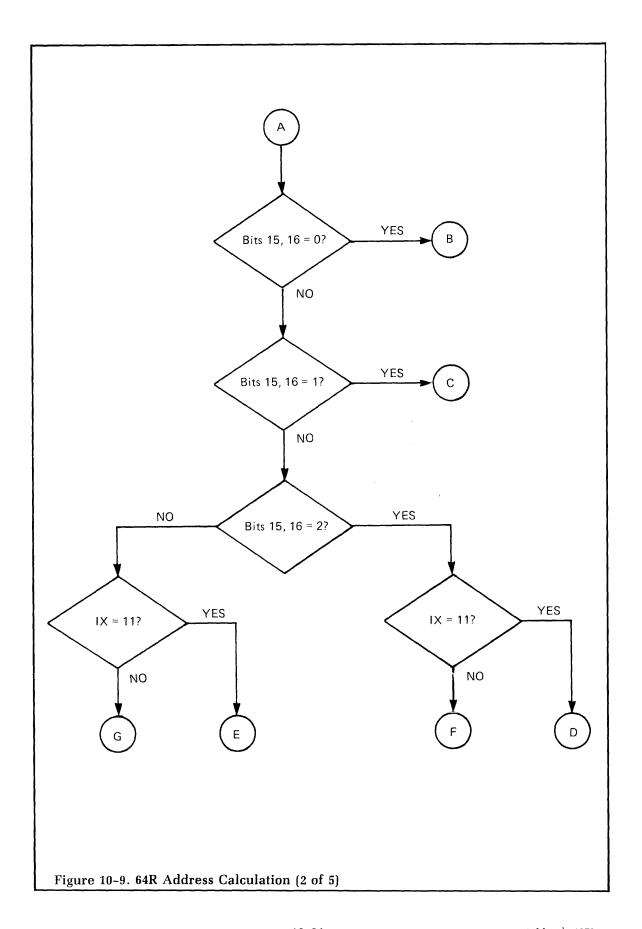

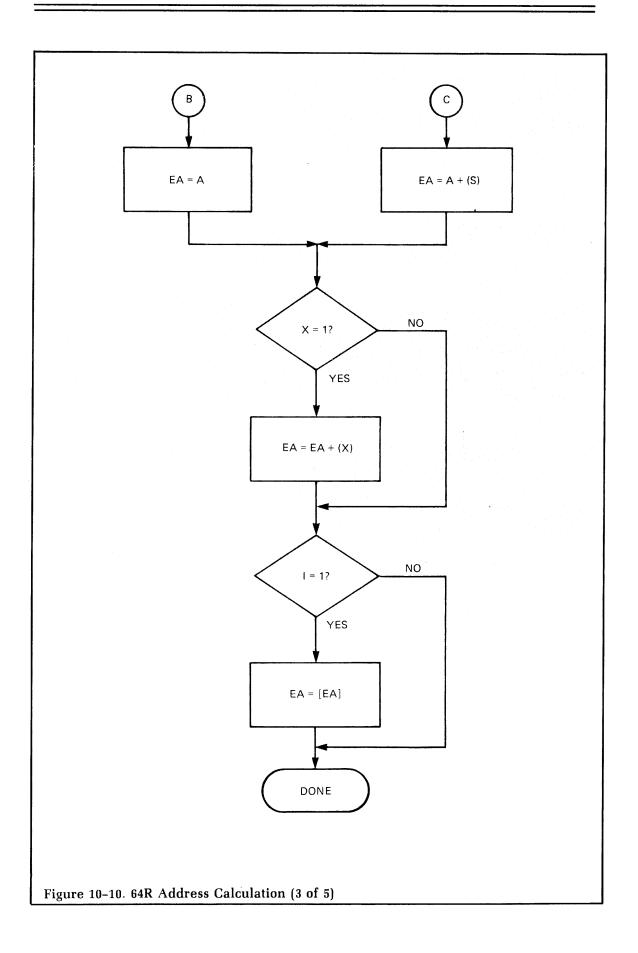

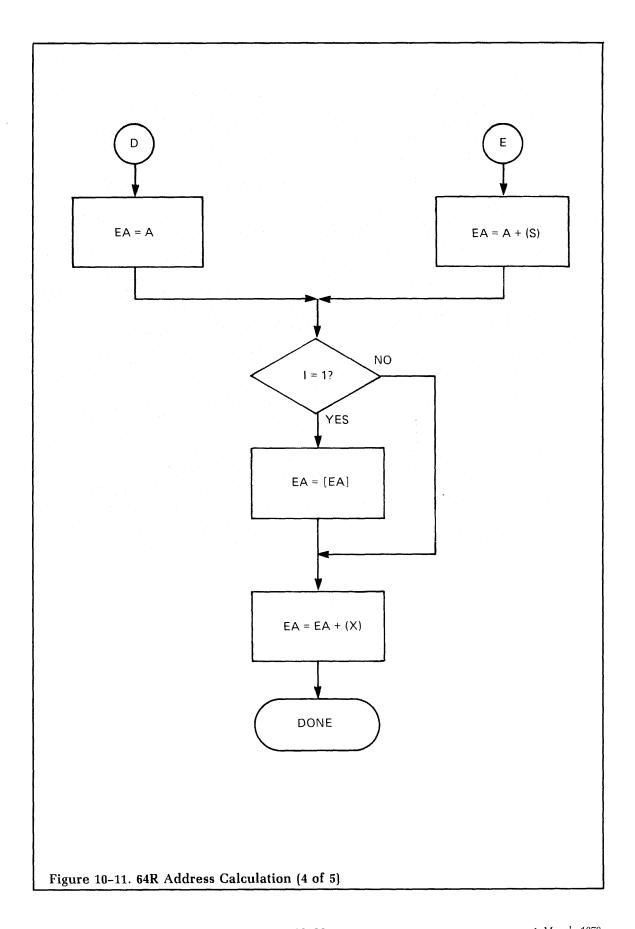

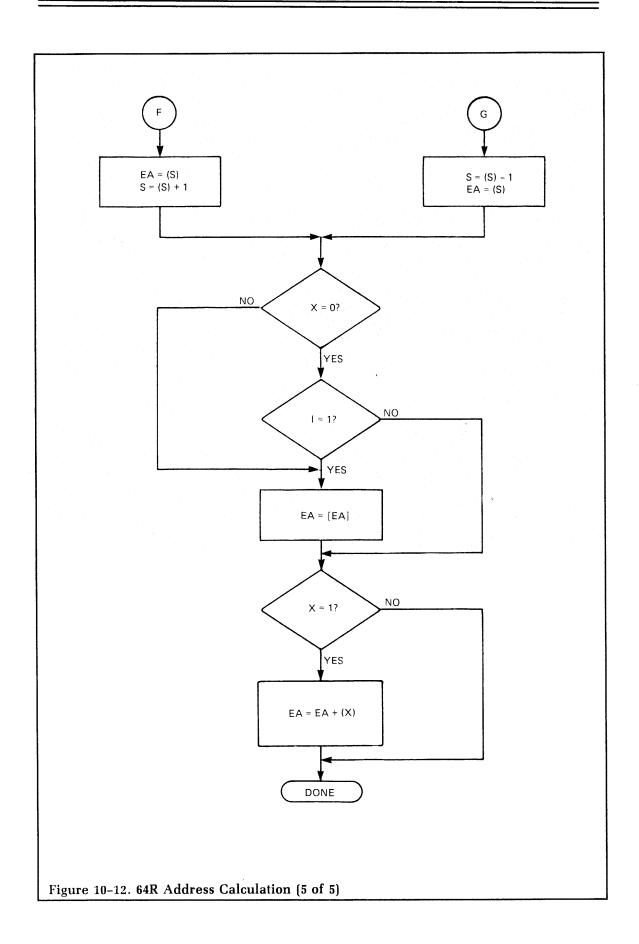

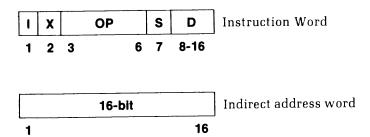

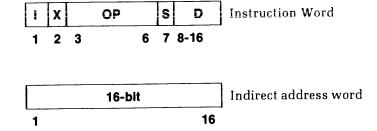

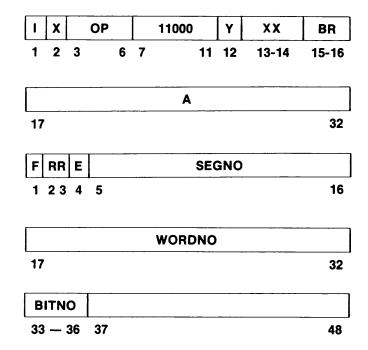

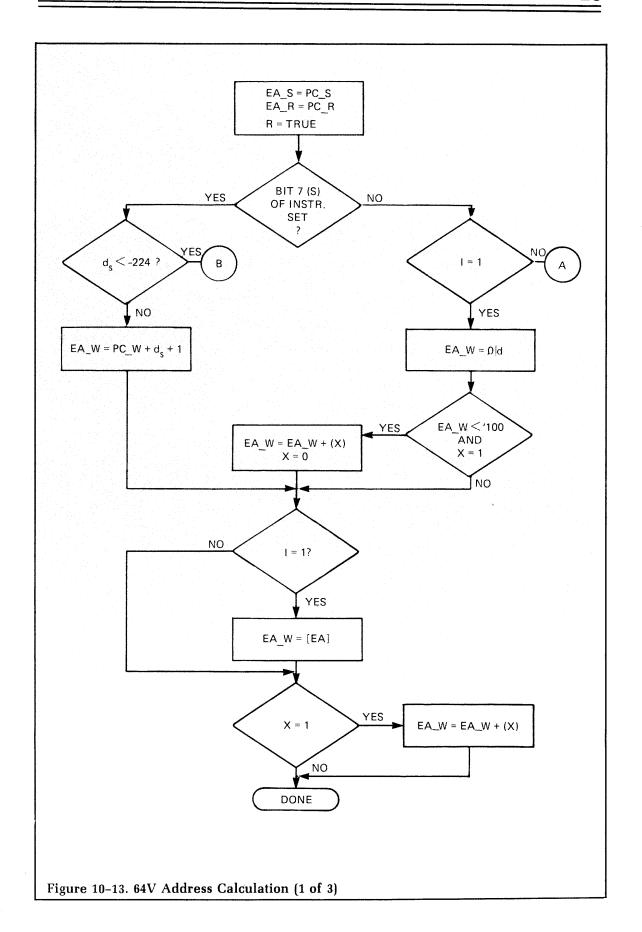

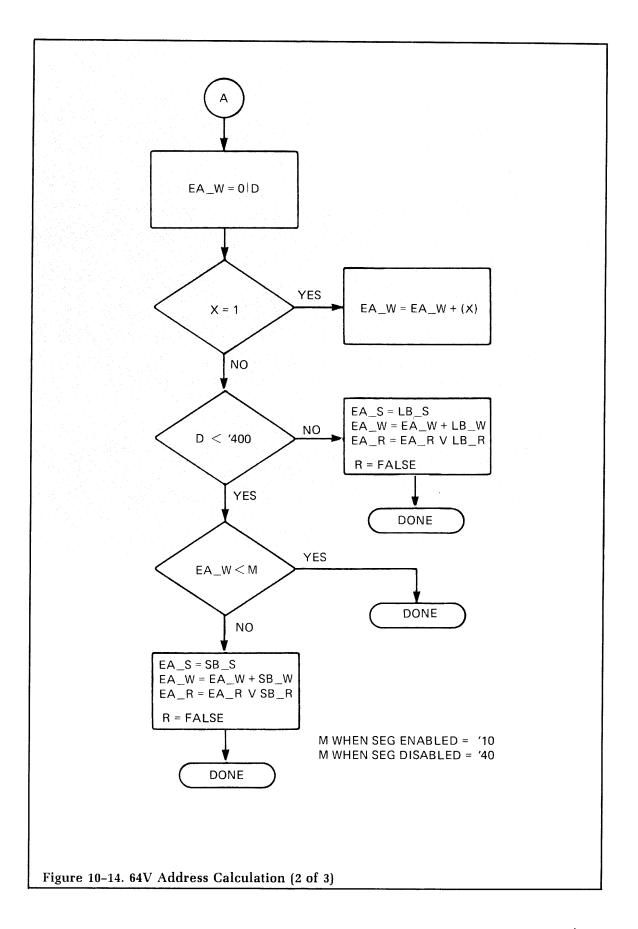

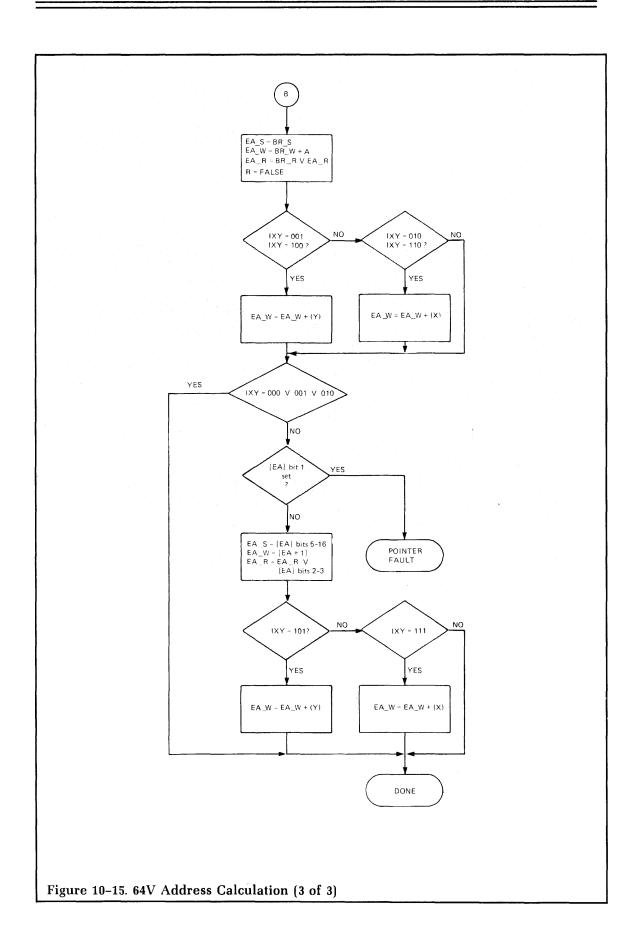

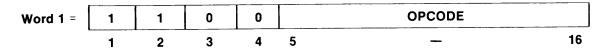

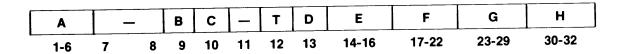

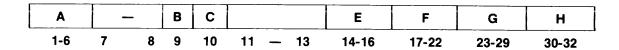

Background concepts 10-1 Table 10-1. Memory reference instruction format 10-2 Memory reference instruction formats 10-4 Table 10-2. V-mode two word memory reference 10-9 Addressing mode summaries and flow charts 10-10 Figure 10-1. 16S address calculation 10-11 Figure 10-2. 32S address calculation 10-13 Figure 10-3. 32R address calculation (1 of 5) 10-16 Figure 10-4. 32R address calculation (2 of 5) 10-17 Figure 10-5. 32R address calculation (3 of 5) 10 - 18Figure 10-6. 32R address calculation (4 of 5) 10-19 Figure 10-7. 32R address calculation (5 of 5) 10-20 Figure 10-8. 64R address calculation (1 of 5) 10-23 Figure 10-9. 64R address calculation (2 of 5) 10-24 Figure 10-10. 64R address calculation (3 of 5) 10-25 Figure 10-11. 64R address calculation (4 of 5) 10-26 Figure 10–12. 64R address calculation (5 of 5) 10–27 Figure 10–13. 64V address calculation (1 of 3) 10–31 Figure 10–14. 64V address calculation (2 of 3) 10–32 Figure 10–15. 64V address calculation (3 of 3) 10–33

Field operations—FIELD 11-15

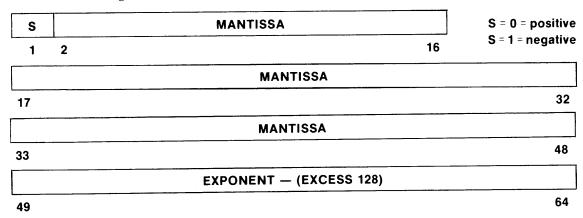

Floating point arithmetic—FLPT 11-16

Table 11-3. Floating point exception codes 11-16

Table 11-4. Floating point mantissa and exponent ranges 11-17

## 11 INSTRUCTION DEFINITIONS

Addressing mode—ADMOD 11-1 Branch—BRAN 11-2 Character string operations—CHAR 11-5 Clear register—CLEAR 11-7 Decimal arithmetic—DECI 11-8 Table 11-1. Decimal data type 11-9 Table 11-2. Edit sub-operations 11-14 Key Manipulation—KEYS 11-31 Logical operations—LOGIC 11-32 Logical test and set—LTSTS 11-33 Machine control—MCTL 11-34 Move data—MOVE 11-39 Program control and jump—PCTLJ 11-43 Process exchange—PRCEX 11-49 Queue management—QUEUE 11-49 Shift group—SHIFT 11-50 Skip conditional—SKIP 11-53 Table 11-5. Combination skip group 11-55

## 12 I-MODE INSTRUCTIONS

Addressing mode—ADMOD 12-1 Branch—BRAN 12-1 Character operations—CHAR 12-3 Clear register and memory—CLEAR 12-14 Decimal arithmetic—DECI 12-5 Field Operations—FIELD 12-5 Floating point arithmetic—FLPT 12-6 Integer arithmetic—INT 12-9 Integrity check for hardware—INTGY 12-14 Input/output—I/O 12-14 Key manipulation—KEYS 12-14 Logical operations—LOGIC 12-15 Logical test and set-LTSTS 12-16 Machine control—MCTL 12-17 Move data—MOVE 12-17 Program control and jump—PCTLJ 12-19 Process exchange—PRCEX 12-10 Queue management—QUEUE 12-10 Shift—SHIFT 12-21

## 13 INSTRUCTION SUMMARY CHART

Instruction summary 13-1

## 14 LANGUAGE STRUCTURE

Introduction 14-1

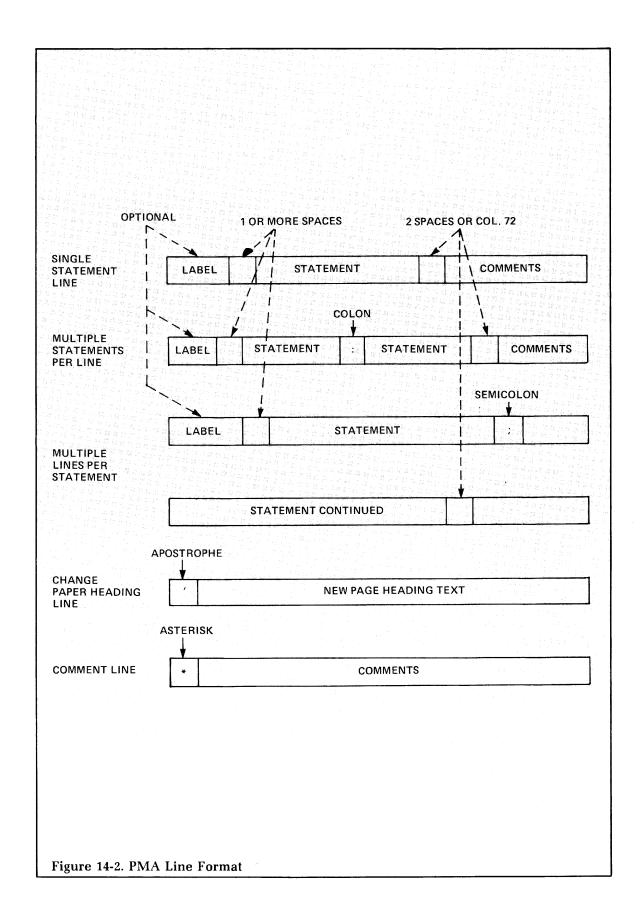

Lines 14-1

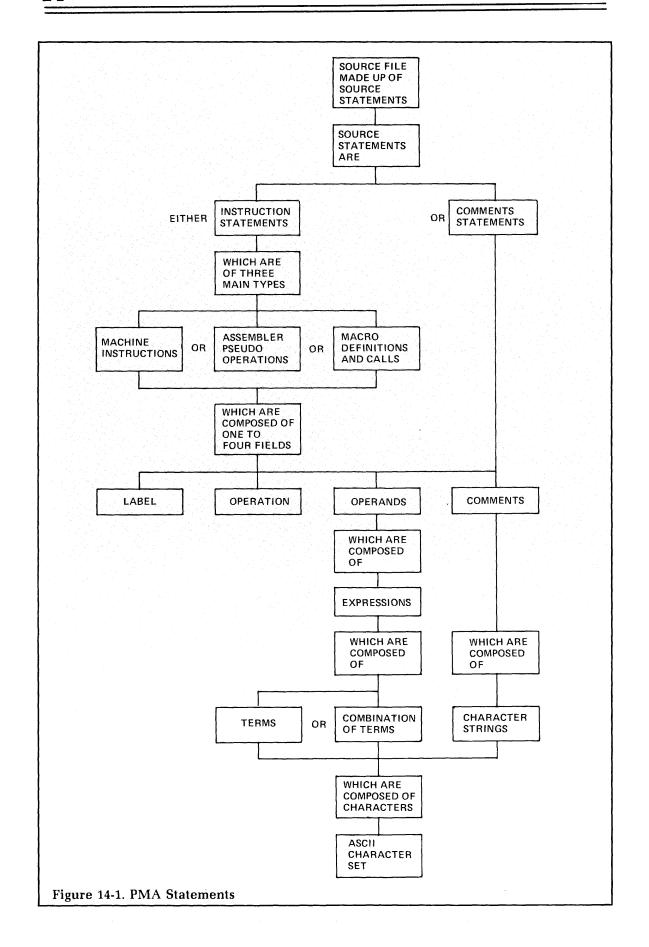

Statements 14-1

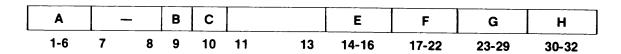

Figure 14-1. PMA statements 14-2

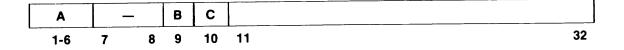

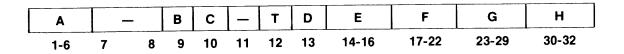

Figure 14-2. PMA line format 14-3

Memory reference instruction format 14-5

Instruction formats—I-Mode 14-5

Table 14-1. Assembler formats 14-7

How to write V or I mode code in PMA 14-8

## 15 DATA DEFINITION

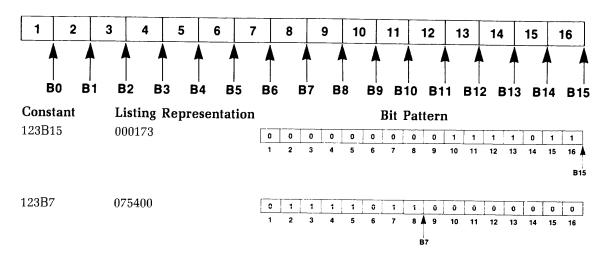

Table 15-1. Numeric constants 15-2

Terms 15-5

Figure 15-1. Floating point data formats 15-6

Table 15-2. Modes 15-8

Expressions 15-8

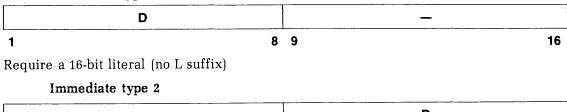

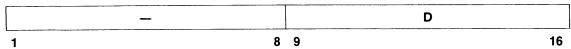

Literals 15-10

Assembler attributes 15-11

## **16** PSEUDO OPERATIONS

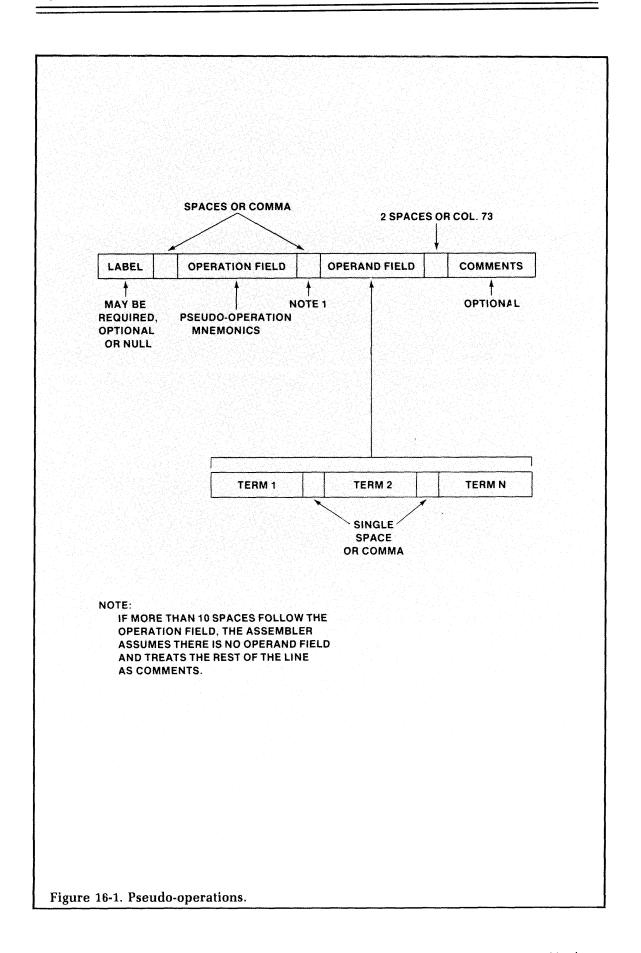

Introduction 16-1

Table 16-1. Pseudo-operation summary 16-2

Figure 16-1. Pseudo-operations 16-4

Assembly control psuedo-operations (AC) 16-5

Address definition pseudo-operations (AD) 16-7

Conditional assembly pseudo-operations (CA) 16-8

Data defining pseudo-operations (DD) 16-10

Listing control pseudo-operations (LC) 16-11

Literal control pseudo-operations (LT) 16-12

Loader control pseudo-operations (LO) 16-13

Macro definition pseudo-operations (MD) 16-16

Program linking pseudo-operations (PL) 16-18

Storage allocation pseudo-operations (SA) 16-20

Symbol defining pseudo-operations (SD) 16-20

## 17 MACRO FACILITY

Introduction 17-1 Macro definition 17-2 Macro calls 17-3 Nesting macros 17-5 Conditional assembly 17-6 Macro listing 17-6

## 18 INTRODUCTION TO TAP, PSD, VPSD

Using TAP 18-1

Table 18-1. Debugging command summary 18-1

Using PSD 18-3

Table 18-2. PSD/VPSD versions 18-3

Using VPSD 18-3

Command line format 18-4

Table 18-3. Input/output formats (PSD and VPSD) 18-5

## 19 TAP COMMAND SUMMARY

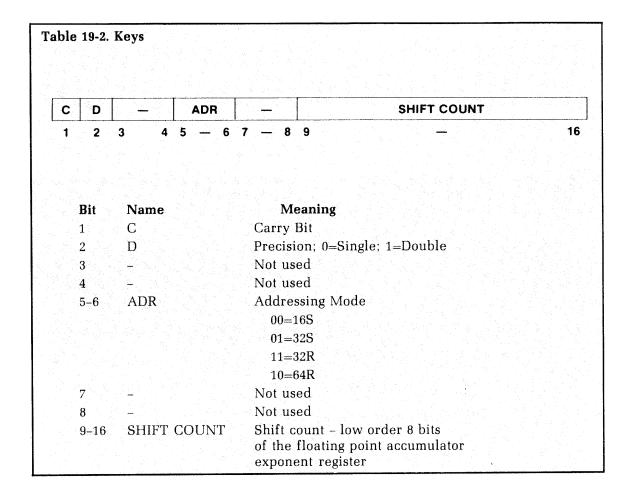

TAP command summary 19-1 Table 19-1. TAP terminators 19-1 Table 19-2. Keys 19-3

## **20** PSD COMMMAND SUMMARY

PSD command summary 20-1 Table 20-1. PSD terminators 20-1 Table 20-2. Key values: R and S mode 20-4

## 21 VPSD COMMAND SUMMARY

Table 21-1. VPSD terminators 21-1

Table 21-2. Key values: R and S modes 21-4

Table 21-3. Key values: V mode 21-5

## A ASSEMBLER ATTRIBUTES

**B** ASCII CHARACTER SET

C ERROR MESSAGES

## OVERVIEW

## Introduction

## INTRODUCTION

This document is a comprehensive user guide for the Prime Macro Assembler (PMA) programmer. In this one document you will find almost everything you will need to know to write, assemble, load, debug and execute an assembly language program. We assume the following background: you are an experienced assembly language programmer although you may be unfamiliar with Prime's PMA; and you have been introduced to Prime's PRIMOS operating system and its major utilities through the use of a high-level language such as FORTRAN and COBOL. (If not, we recommend you read one of our other language user guides before undertaking a PMA project.)

## ORGANIZATION AND USAGE

This document is organized into five major parts:

- Part 1. Overview and conventions (Sections 1 and 2)

- Part 2. PMA Usage (Sections 3 through 8)

- Part 3. Machine Formats and Instructions (Sections 9 through 13)

- Part 4. PMA Reference (Sections 14 through 17)

- Part 5. Debugging Utilities Reference (Sections 18 through 21)

In addition to a tutorial section for the new PMA programmer (Part 2), it contains complete descriptions of:

Machine instructions

Data structures

Assembler pseudo operations

Assembler macro facilities

TAP, PSD and VPSD debugging facilities

## **RELATED DOCUMENTS**

The FORTRAN Programmer's Guide

Reference Guide, System Architecture

The New User's Guide to Editor and Runoff

PRIMOS Commands Reference Guide

Reference Guide. PRIMOS Subroutines

PRIMOS Programmer's Companion

FORTRAN Programmer's Companion

Assembly Language Programmer's Companion

Reference Guide, LOAD and SEG

## Conventions

## PRIME CONVENTIONS

Symbols, abbreviations, special characters and conventions frequently used in this document are defined below.

## Prime filename conventions

| Filename   | Function                |

|------------|-------------------------|

| Bfilename  | Binary (object) file    |

| Lfilename  | Listing file            |

| C_filename | Command file            |

| filename   | Source file             |

| *filename  | Saved (executable) file |

| M_filename | Map file                |

| #filename  | SEG runfile             |

## Note

Filenames may be a maximum of 32 characters.

## **Text conventions**

An item in all capital letters must be included verbatim. Rust colored letters indicate acceptable abbreviations. In TAP, PSD and VPSD commands enter *only* the rust colored letters. A quote mark (apostrophe) preceding a number means octal.

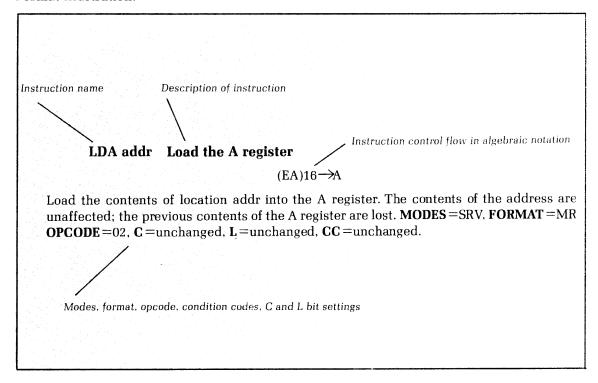

## INSTRUCTION DESCRIPTION CONVENTIONS

This section describes each of the instructions in the context of the mode where they are first used. To avoid duplicate descriptions while facilitating retrieval, each instruction is described once, but listed in I-mode if appropriate.

## Format illustration:

## Instruction summary and description conventions

| A             | A Register (16-bits)            |

|---------------|---------------------------------|

| В             | B Register (16 bits)            |

| L             | L Register (A B)                |

| E             | E Register (32-bits)            |

| F             | Floating Point Register         |

| Н             | Half Register (16-bits, I Mode) |

| R             | Full register (32-bits, I Mode) |

| C             | C-Bit in the keys               |

| L-bit         | L-Bit in the Keys               |

| CC            | Condition Codes                 |

| LB            | Link Base Register              |

| SB            | Stack Base Register             |

| PB            | Procedure Base Register         |

| XB            | Temporary Base Register         |

| S             | S-Mode                          |

| R             | R-Mode                          |

| $\mathbf{V}$  | V-Mode                          |

| I             | I-Mode                          |

| FAR           | Field Address Register          |

| FLR           | Field Length Register           |

| $\rightarrow$ | Replaces                        |

|               |                                 |

## **FUNCTION GROUP DEFINITIONS**

The instruction definitions are grouped by primary function, such as integer arithmetic. Table 2-1 below contains the definitions for all the function groups and modes. If you wish to find a particular instruction, Section 13 contains an alphabetic list.

| Table 2-1. Function Definitions |   |   |                           |   |  |

|---------------------------------|---|---|---------------------------|---|--|

| Definition                      | S | R | V                         | I |  |

| Addressing Mode                 | X | X | X                         | X |  |

| Branch                          |   |   | X                         | X |  |

| Character                       |   |   | X                         | X |  |

| Clear field                     | X | X | X                         |   |  |

| Decimal Arithmetic              |   |   | X                         | X |  |

| Field Register                  |   |   | X                         | X |  |

| Floating Point Arithmetic       |   | X | X                         | X |  |

| Integer Arithmetic              | X | X | X                         | X |  |

| Integrity                       | X | X | X                         | X |  |

| Input/Output                    | X | X | X                         | X |  |

| Keys                            | X | X | X                         | X |  |

| Logical Operations              | X | X | X                         | X |  |

| Logical Test and Set            | X | X | X                         | X |  |

| Machine Control                 | X | X | $\mathbf{X}_{\mathbf{x}}$ | X |  |

| Move                            | X | X | X                         | X |  |

| Program Control and Jump        | X | X | X                         | X |  |

| Process Exchange                |   |   | X                         | X |  |

| Queue Control                   |   |   | X                         | X |  |

| Shift                           | X | X | X                         | X |  |

| Skip                            | X | X | X                         | X |  |

## FORMAT DEFINITIONS

Each instruction has a format. The formats and their meaning are summarized in Table 2-2. The specific bit definitions are defined in Section 9—Data and Instruction Formats and Section 10—Memory Reference Concepts.

| able 2-2. Format De | efinitions                              |   |   |              |   |

|---------------------|-----------------------------------------|---|---|--------------|---|

| Mnemonic            | Definition                              | S | R | $\mathbf{V}$ | I |

| GEN                 | Generic                                 | X | X | X            | X |

| AP                  | Address Pointer                         |   |   | X            | X |

| BRAN                | Branch                                  |   |   | X            |   |

| IBRN                | Branch I-mode                           |   |   |              | X |

| CHAR                | Character                               |   |   | X            | X |

| DECI                | Generic Decimal                         |   |   | X            | X |

| PIO                 | Programmed I/O                          | X | X | X            | X |

| SHFT                | Shift                                   | X | X | X            | X |

| MR                  | Memory Reference –<br>Non I-mode        | X | X | X            |   |

| MRFR                | Memory Reference –<br>Floating Register |   |   |              | X |

| MRNR                | Memory Reference<br>Non Register        |   |   |              | X |

| RGEN                | Register Generic                        |   |   |              | X |

## **GENERAL DATA STRUCTURES**

Table 2-3. Data Structures—summarizes all the data structures manipulated by instructions.

| Class                                         | S            | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V            | I                               |

|-----------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------|

| <b>Integer (Unsigned)</b><br>16-bit<br>32-bit | X            | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X<br>X       | X<br>X                          |

| Integer (Signed)<br>16-bit<br>31-bit          | X<br>X       | X<br>X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | X            | X                               |

| 32-bit                                        |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $X_{\alpha}$ | X                               |

| Floating Point                                |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                                 |

| 32-bit<br>64-bit                              |              | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X            | $\frac{\mathbf{X}}{\mathbf{X}}$ |

|                                               |              | Δ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X            | $oxed{X}$                       |

| Decimal                                       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                                 |

| Character String                              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | X            |                                 |

| Word<br>16-bit<br>32-bit                      |              | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X            |                                 |

| Halfword - 16 bit                             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                                 |

| Byte                                          | $\mathbf{x}$ | Χ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X            |                                 |

| Indirect Pointer (IP)                         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                                 |

| 16-bit<br>32-bit<br>48-bit                    |              | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X<br>X<br>X  | X                               |

| Address Pointer (AP)                          |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | X            |                                 |

| Stacks                                        |              | 化物物质的<br>医性压缩                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                 |

| Segment Header<br>Frame Header                |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | X<br>X       |                                 |

| Argument Template                             |              | and 等。<br>and 等<br>and and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Χ            |                                 |

| Entry Control Block                           |              | (2) 10 日本 10 | Χ            |                                 |

| Queue Control Block                           |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | X            |                                 |

## PROCESSOR CHARACTERISTICS

Table 2-4, Processor Characteristics, lists the program visible portions of the hardware.

| able 2-4. Processor Characteristic | cs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |   |   |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|--|

| Class                              | <b>S</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R | V | I |  |

| Registers                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   |  |

| S, R mode                          | $\mathbf{X}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | X |   |   |  |

| V, I mode                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | X | X |  |

| Field Registers                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | X | Χ |  |

| Floating Registers                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Χ | X | Χ |  |

| Keys                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   |  |