### MAN1673

MACRO ASSEMBLER User Guide

> Revision A May 1975

145 Pennsylvania Ave. Framingham, Mass. 01701 Copyright 1975 by

Prime Computer, Incorporated

145 Penhsylvania Avenue

Framingham, Massachusetts 01701

Performance characteristics are subject to change without notice.

# CONTENTS

|                                                                                                       | Page                         |

|-------------------------------------------------------------------------------------------------------|------------------------------|

| SECTION 1 INTRODUCTION                                                                                | 1-1                          |

| SCOPE OF HANDBOOK                                                                                     | 1-1                          |

| REFERENCE DOCUMENTS                                                                                   | 1-1                          |

| PRIME 200 ASSEMBLY LANGUAGE                                                                           | 1 - 2                        |

| Basic Assembly Language Elements<br>Symbolic Instructions<br>Constants, Literals, Variables, and      | 1-3<br>1-6<br>1-8            |

| Expressions<br>Symbolic Names<br>Pseudo Operations<br>Macro Facility                                  | 1-9<br>1-10<br>1-10          |

| USING THE MACRO ASSEMBLER                                                                             | 1-12                         |

| Two-Pass Assembly Object Output Listing Format Location Count Symbol Cross Reference Listing          | 1-12<br>1-13<br>1-13<br>1-15 |

| ASSEMBLER/LOADER INTERACTION                                                                          | 1-16                         |

| Desectorizing and Address Resolution<br>Extended Addressing Mode<br>Loading Subroutines<br>Memory Map | 1-16<br>1-17<br>1-17<br>1-18 |

| LOADING AND OPERATING PROCEDURES                                                                      | 1-18                         |

| SECTION 2 GENERAL ASSEMBLY LANGUAGE RULES                                                             | 2-1                          |

| FREE-FORM INPUT TEXT                                                                                  | 2-1                          |

| Line Format                                                                                           | 2-1                          |

| CONSTANTS, VARIABLES AND EXPRESSIONS                                                                  | 2 - 5                        |

| Constants<br>Variables<br>Expressions                                                                 | 2 - 5<br>2 - 7<br>2 - 8      |

|                                                                                                                                                                                                                    | Page                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| SECTION 3 INSTRUCTION STATEMENTS                                                                                                                                                                                   | 3-1                                                         |

| INSTRUCTION STATEMENT GENERAL FORMAT                                                                                                                                                                               | 3-1                                                         |

| Label<br>Operation Field<br>Variable Field                                                                                                                                                                         | 3-1<br>3-1<br>3-7                                           |

| MEMORY REFERENCE INSTRUCTIONS                                                                                                                                                                                      | 3-11                                                        |

| Operation Field<br>Variable Field                                                                                                                                                                                  | 3-13<br>3-13                                                |

| INPUT/OUTPUT INSTRUCTIONS                                                                                                                                                                                          | 3-14                                                        |

| SHIFT INSTRUCTIONS                                                                                                                                                                                                 | 3-16                                                        |

| BIT REFERENCE INSTRUCTIONS                                                                                                                                                                                         | 3-18                                                        |

| GENERIC INSTRUCTIONS                                                                                                                                                                                               | 3 - 20                                                      |

| SECTION 4 PSEUDO-OPERATIONS                                                                                                                                                                                        | 4 - 1                                                       |

| STATEMENT FORMAT                                                                                                                                                                                                   | 4-1                                                         |

| ASSEMBLY CONTROLLING PSEUDO-OPERATIONS                                                                                                                                                                             | 4 - 4                                                       |

| ABS (Set Mode to Absolute) REL (Set Mode to Relocatable) ORG (Define Origin Location) FIN (Insert Literals) MOR (More Input Required) END (End of Source Statements) CF1 Through CF5 GO, GO TO (Forward Reference) | 4 - 4<br>4 - 4<br>4 - 6<br>4 - 6<br>4 - 6<br>4 - 7<br>4 - 7 |

| LISTING CONTROL PSEUDO-OPERATIONS                                                                                                                                                                                  | 4 - 8                                                       |

| LIST (Enable Listing) NLST (Inhibited Listing) EJCT (Eject Page)                                                                                                                                                   | 4 - 8<br>4 - 8<br>4 - 8                                     |

| LOADER CONTROLLING PSEUDO-OPERATION                                                                                                                                                                                | 4 - 9                                                       |

| EXD (Enter Extended Addressing Mode) LXD (Leave Extended Addressing Mode) SETB (Set Base Sector)                                                                                                                   | 4 - 9<br>4 - 9<br>4 - 9                                     |

|                                                                                                                                                                                                                                                                                                 | Page                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| DATA DEFINING PSEUDO-OPERATIONS                                                                                                                                                                                                                                                                 | 4-11                                                                         |

| OCT (Set Octal Constant) HEX (Set Hexadecimal Constants) VFD (Define Variable Fields) BCI (Define ASCII String) DAC (Local Address Definition)                                                                                                                                                  | 4-11<br>4-23<br>4-24<br>4-25<br>4-26<br>4-27<br>4-28<br>4-29<br>4-30<br>4-31 |

| VARIABLE (SYMBOL) DEFINING PSEUDO-OPERATIONS                                                                                                                                                                                                                                                    | 4 - 32                                                                       |

| EQU (Define Variable),<br>SET (Redefine Variable)                                                                                                                                                                                                                                               | 4 - 32<br>4 - 32                                                             |

| STORAGE ALLOCATION PSEUDO-OPERATIONS                                                                                                                                                                                                                                                            | 4 - 34                                                                       |

| 10.10 IDIOCK DUALUTIE WAUM Ofmodal                                                                                                                                                                                                                                                              | 4 - 34<br>4 - 34<br>4 - 34<br>4 - 35<br>4 - 36                               |

| PROGRAM LINKING PSEUDO-OPERATIONS                                                                                                                                                                                                                                                               | 4 - 38                                                                       |

| EXT (Flag External References) CALL (External Subroutine Reference) SUBR, ENT (Define Entry Points)                                                                                                                                                                                             | 4 - 3 8<br>4 - 3 9<br>4 - 4 0                                                |

| CONDITIONAL ASSEMBLY PSEUDO-OPERATIONS                                                                                                                                                                                                                                                          | 4 - 4 4                                                                      |

| IF (Conditional Statement) IFM (Continue Assembly if Minus) IFP (Continue Assembly if IFZ (Continue Assembly if IFX (Continue Assembly if IFN (Continue Assembly if IFN (Continue Assembly if IFN (End Conditional Assembly Area) ELSE (Reverse Conditional Assembly IFALL (Force From Message) | 4 - 4 4<br>4 - 4 5<br>4 - 4 5<br>4 - 4 5<br>4 - 4 6<br>4 - 4 6               |

|                                                                                                                                                                                                                                                               | Page                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| SECTION 5 MACRO FACILITY                                                                                                                                                                                                                                      | 5-1                                                                                    |

| MACRO DEFINITIONS AND CALLS                                                                                                                                                                                                                                   | 5 - 2                                                                                  |

| MAC (Begin Macro Definition) ENDM (End Macro Definition) Argument References Macro Calls Arguments Values Argument Substitution Argument Values in Parentheses Dummy Words Argument Identifiers Assembler Attribute References Local References Within Macros | 5 - 2<br>5 - 3<br>5 - 3<br>5 - 3<br>5 - 4<br>5 - 4<br>5 - 5<br>5 - 5<br>5 - 7<br>5 - 8 |

| MACRO LISTING AND ASSEMBLY CONTROL                                                                                                                                                                                                                            | 5-10                                                                                   |

| LSTM (List Macro Expansions) LSMD (List Macro Expansions - Data Only NLSM (No Listing of Macro Expansions) BACK, BACK TO (Loop Back - Macros Only) SAY (List Message to Operator)                                                                             | 5-12                                                                                   |

| MACRO EXAMPLES                                                                                                                                                                                                                                                | 5-15                                                                                   |

| SECTION 6 SOURCE FILE MERGING COMMANDS                                                                                                                                                                                                                        | 6-1                                                                                    |

| \$INSERT<br>\$UPDATE<br>\$COPY<br>\$DONE                                                                                                                                                                                                                      | 6-1<br>6-2<br>6-2<br>6-2                                                               |

| APPENDICES                                                                                                                                                                                                                                                    |                                                                                        |

| A PRIME 200 Instructions (Op Code Order)                                                                                                                                                                                                                      | A-1                                                                                    |

| B PRIME 200 Instructions (Class Order)                                                                                                                                                                                                                        | B-1                                                                                    |

| C PRIME 200 Instructions (Mnemonic Order)                                                                                                                                                                                                                     | C-1                                                                                    |

| D I/O Device Codes                                                                                                                                                                                                                                            | D-1                                                                                    |

| E ASCII Character Codes                                                                                                                                                                                                                                       | E-1                                                                                    |

| F Object File Formats                                                                                                                                                                                                                                         | F-1                                                                                    |

| G Assembler Error Messages                                                                                                                                                                                                                                    | G-1                                                                                    |

# ILLUSTRATIONS

| Figure | <u>Title</u>                                            | Page  |

|--------|---------------------------------------------------------|-------|

| 1-1    | Example of PRIME 200 Macro Assembly Language Statements | 1-5   |

| 1-2    | Interpretation of Symbolic Instruction                  | 1-7   |

| 1-3    | Example of Assembly Listing                             | 1-14  |

| 1 - 4  | Example of Memory Map                                   | 1-19  |

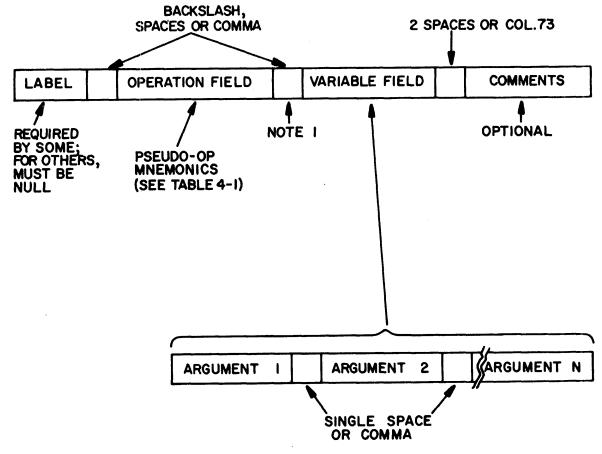

| 2-1    | Source Input Line Formats                               | 2 - 2 |

| 3-1    | General Format of Instruction Statements                | 3 - 8 |

| 3 - 2  | Assembly and Loading of Memory Reference<br>Instruction | 3-12  |

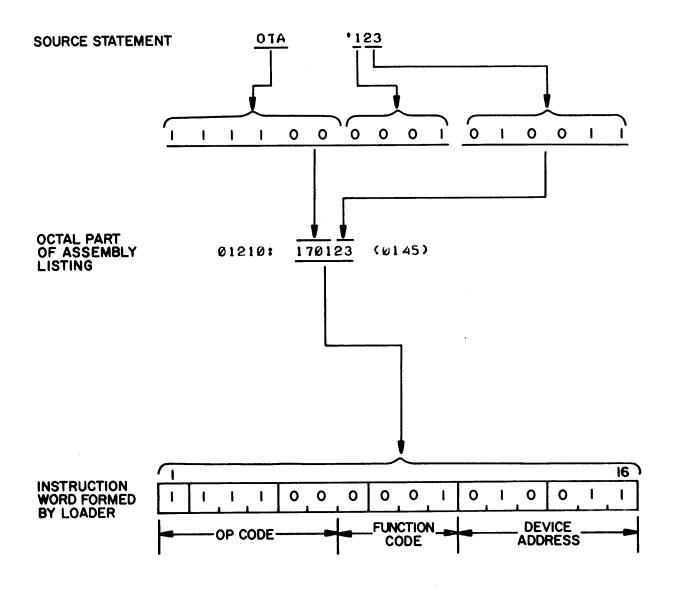

| 3 - 3  | Assembly and Loading of Input/Output Instruction        | 3-15  |

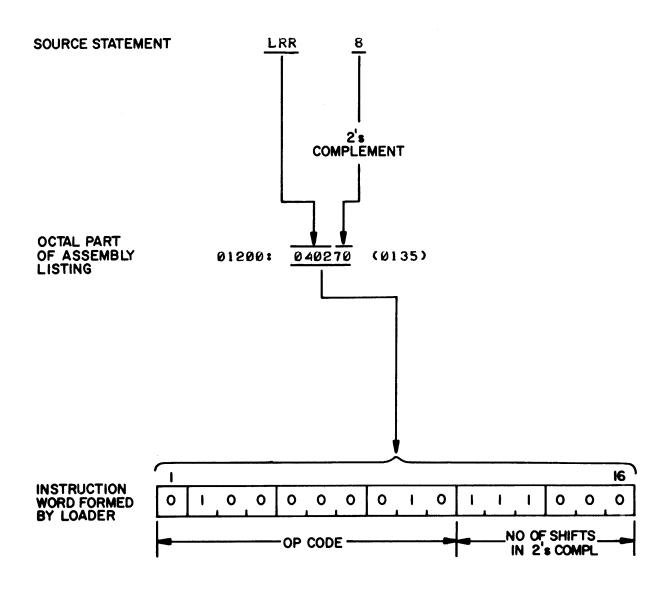

| 3 - 4  | Assembly and Loading of Shift Instructions              | 3-17  |

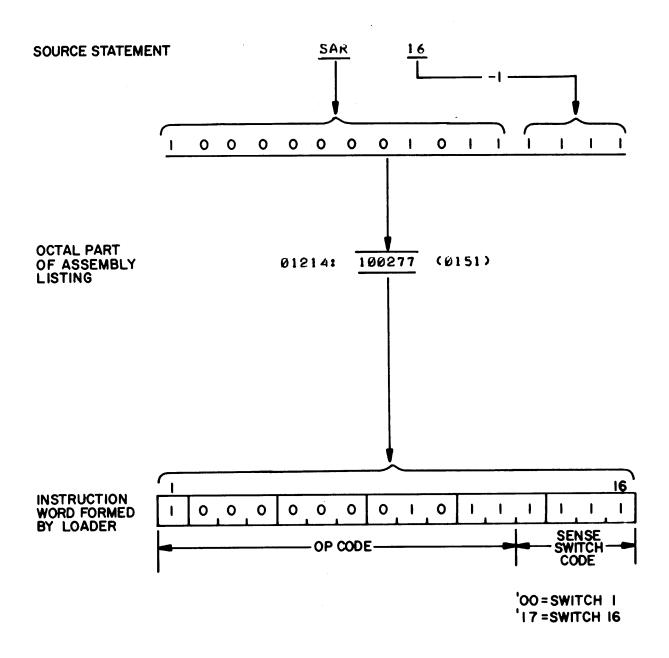

| 3 - 5  | Assembly and Loading of Bit Reference<br>Instructions   | 3-19  |

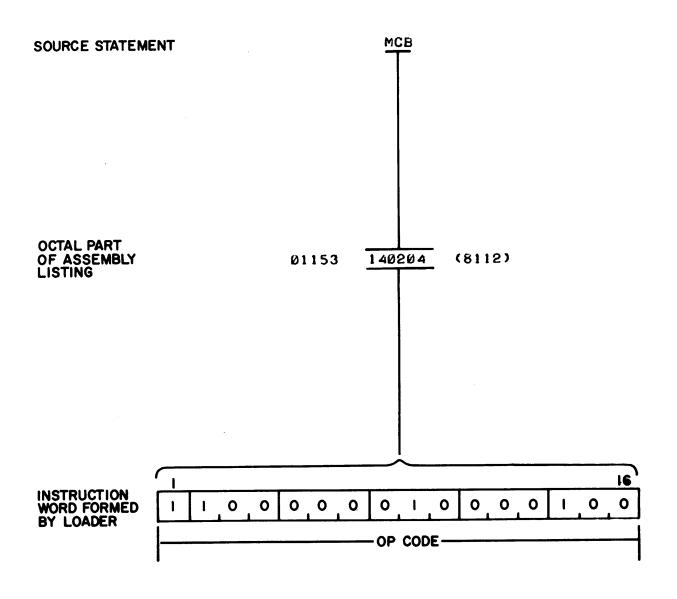

| 3-6    | Assembly and Loading of Generic Instructions            | 3-21  |

| 4 - 1  | General Format of Pseudo-Operation Statements           | 4 - 3 |

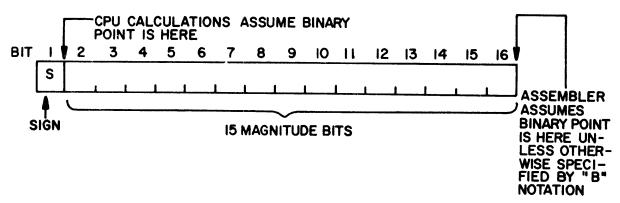

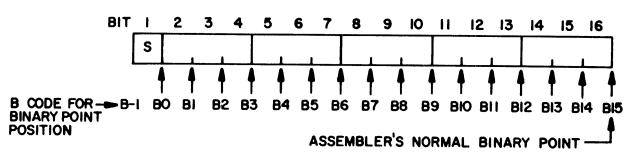

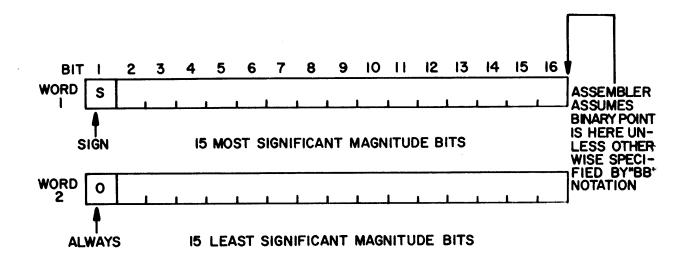

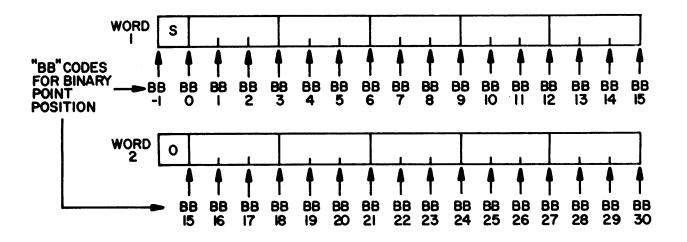

| 4 - 2  | Single Precision Fixed Point Constants                  | 4-14  |

| 4 - 3  | Double Precision Fixed Point Constants                  | 4-17  |

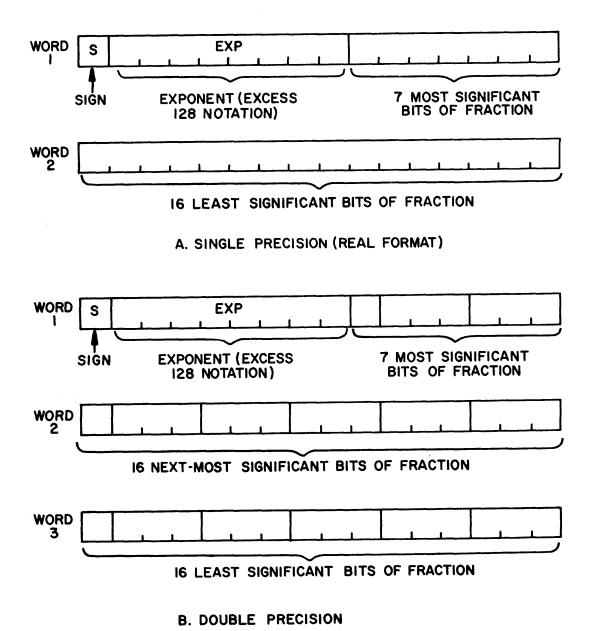

| 4 - 4  | Floating Point Word Formats                             | 4-19  |

|        | TABLES                                                  |       |

| 3-1    | Summary of PRIME 200 Instruction Codes                  | 3 - 2 |

| 4-1    | Summary of Pseudo-Operations                            | 4 - 2 |

| 4 - 2  | Numerical Formats in DATA Statements                    | 4-13  |

#### SECTION 1

#### INTRODUCTION

#### SCOPE OF HANDBOOK

This handbook is a detailed reference manual for the PRIME 200 Macro Assembly Language. It is organized in six sections for ease of reference.

This section introduces the assembly language, describes the action of the program, and discusses the interaction of the assembler with its companion program, the PRIME 200 Linking Loader.

Section 2 discusses statement formats and language features common to all types of assembly language statements.

Section 3 contains the rules for forming instruction statements using PRIME 200 instruction mnemonics.

Section 4 describes pseudo-operations (directives to the assembler and loader).

Section 5 defines the Macro facility, a way to define program statements that can be called for execution by easily interpreted English language statements.

Section 6 defines commands used to invoke functions of RDALN, routine that merges lines from two or more source files during assembly.

The handbook is concluded by several appendices and a detailed subject index.

#### REFERENCE DOCUMENTS

The following publications are recommended to supplement this handbook:

PRIME 200 Programmer's Reference Manual

PRIME 200 Operator's Guide

PRIME 200 DOS Reference Manual

PRIME 200 RTOS Reference Manual

### PRIME 200 ASSEMBLY LANGUAGE

The PRIME 200 Macro Assembly Language has the usual provisions for symbolic instructions, symbolic addresses, and control pseudo-operations expected by computer users. It also offers many other advanced features:

\* Free Format:

Source statements are independent of column boundaries and permit free use of spaces. Multiple statements per line are permitted, and statements may be continued from line to line.

\* Symbols:

Symbols or Variables assigned to address and data locations may contain up to 32 characters.

\* Constants:

Wide variety of constant forms: decimal, octal, hexadecimal, ASCII, double precision, floating point, literals.

\* Expressions:

Symbols and constants may be linked in expressions using 14 different arithmetic, logical, and shift operators.

\* Pseudo-Operations:

Over 50 pseudo-operations for assembly control, listing control, loader control, data definition, variable definition, storage allocation, program linking, and conditional assembly.

\* Macro Facility:

Programmer can define macros to be called by application-related language statements. Arguments are identified by position or flagged by key words. Looping, local references, and nesting are permitted.

The main purpose of an assembly language is to reduce the clerical chores required to prepare a binary program that can be executed by the computer. Of course, it is possible to look up the binary code for a given instruction and key it into a memory location using front panel controls. For example, an instruction to load the A register from location '377 of sector O would be the octal code '004377. The octal code for any PRIME 200 instruction can be determined from the Programmer's Reference Manual. (Also see Table 3-1.)

But manual key-in of programs is tedious, error prone, and the bare binary codes can only be interpreted by a painstaking analysis. This mode of program entry is usually limited to key-in loader bootstrap programs and short test sequences. A symbolic assembly language has become the universal means of preparing programs of any size. An assembly language provides a vocabulary of symbolic, or mnemonic, codes - and a grammar of statement forms - to represent machine language instructions in a format that is easily read and interpreted by the original programmer or any other reader familiar with the language.

# Basic Assembly Language Elements

Figure 1-1 illustrates a section of a typical program written in PRIME 200 Macro Assembly Language. The basic unit of information processed by the PRIME 200 assembler is the line. When originated at an ASR-33 Teletype keyboard, a line consists of up to 72 ASCII characters (75 for ASR-35) occurring between carriage return - line feed characters. When input is from unit record equipment, a line consists of an 80-character card field.

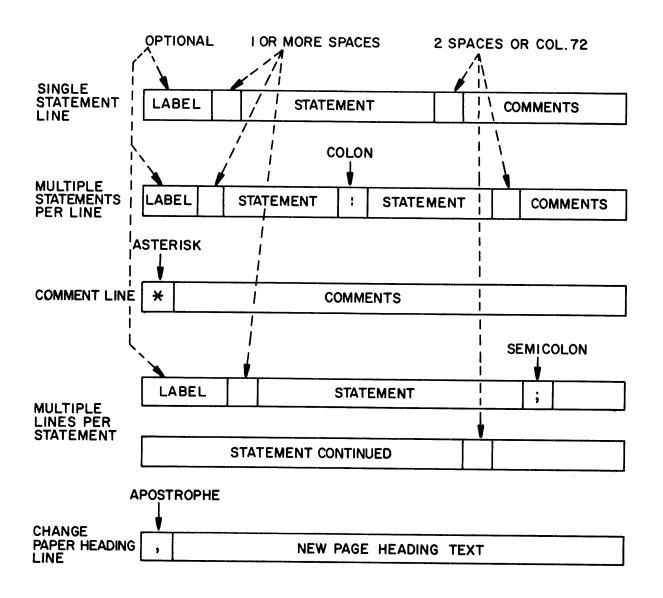

There are statement lines, comment lines and change page heading lines. A statement line has a space in column 1, an optional label, one or more statements, and an optional comment field. A comment line has an asterisk in column 1; the rest of the line is ignored except for listing purposes.

A change page heading line has an apostrophe in column 1; the rest of the line becomes the page heading for all subsequent listing pages.

A <u>label</u> is an ASCII character string that identifies the <u>locations</u> count of the first statement in the line. Examples are the name of the entry point for a subroutine or the symbolic name of a storage location. These and other common features of the language are described in detail in Section 2.

The PRIME 200 processes four types of <u>statements</u>, each with a unique format: instructions, pseudo-operations, macro calls, and file merging commands. These are described in detail in Sections 3 through 6, respectively.

```

*SHORT DEMO PROGRAM EXAMPLE

\hat{p}_{i}^{k}

ABS

43000

ORG

CRA

DISPLAY A REG IN PANEL IND

11720

OTA

C

SRIL

JMF:+:

005

IRX

11

JMP

Ħ

-:

IRX

JMF

E

DATA INDICATORS COUNT SLOWLY

AOA.

DELIBERATE ERROR LINE

FAIL

JMP

30000

OCT

005

END

FMD

```

Figure 1-1. Example of PRIME 200 Macro Assembly Language Statements

## Symbolic Instructions

The A Register load operation mentioned above can be represented in the form:

### LDA '377

where LDA is the mnemonic of the LDA instruction and '377 is the octal representation of the memory address where the data is located. The programmer may also control the flag and tag bits symbolically, as in:

## LDA\* '377,1

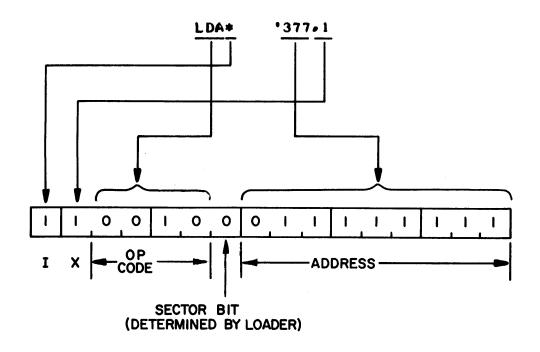

where the asterisk specifies indirect addressing and the ,1 specifies indexing. After being processed by the assembler and loader, this statement would be converted into a binary instruction word, shown in Figure 1-2. The resulting word would have an octal value of '144377.

Figure 1-2. Interpretation of Symbolic Instruction.

# Constants, Literals, Variables, and Expressions

This assembler permits a variety of forms for data constants, thereby eliminating conversions from decimal to binary, octal, or hexadecimal. Examples:

| '123   | - ' 777 | '-1777  | Octal       |

|--------|---------|---------|-------------|

| \$89AB | -\$FFFF | \$-00FF | Hexadecima1 |

| 1234   | -9999   | 32767   | Decima1     |

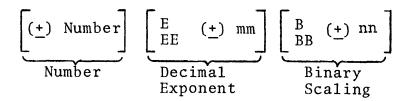

The constant forms shown above are all single-precision (ie. are converted to a single 16-bit data word - 15 magnitude bits plus sign). For decimal numbers, double precision and floating point quantities may be specified:

| 1.23BB6 | 1.23EE2BB6 | Fixed Point<br>Double<br>Precision |

|---------|------------|------------------------------------|

| 1.23E2  | 1.1092     | Floating Point<br>Single Precision |

| 1.23EE2 |            | Floating Point<br>Double Precision |

The assembler also accepts ASCII constants:

| C'A'  | (The letter A, left justified in a 16-bit word)  |

|-------|--------------------------------------------------|

| C'AB' | (The letters A and B packed into a 16-bit word.) |

Another form of constant with a self-defining symbolic name is the literal:

= '77 Octa1

= \$39FB Hexadecimal

= 199 Decimal

= C'X' (one character) ASCII

= C'XY' (two characters)

<u>Variables</u>, also called symbols or symbolic names, may be assigned to identify memory locations. Symbols are defined by being used in the label field of a statement, or by the EQU or SET pseudo-operations. The assembler accepts alphanumeric symbols of up to 32 characters:

Α

ALPHA

ABCDEFGHIJKLMNOPQRSTUVWXYZ123456

Expressions may be formed using constants or variables, linked by 14 different arithmetic, logical and shift operators:

$A + 3 \qquad ALPA*(4 - B) \qquad A .LS.(ALPA/5)$

A .AND. '3737 BETA .GE.A+\$FF

### Symbolic Names

Symbolic names may be coined by the programmer and assigned to memory locations, so that data locations and program entry points can be specified by self-explanatory codes rather than numerical values. For example, the load A instruction could be coded as

LDA\* DATA,1

provided the symbol DATA is defined somewhere in the program as equal to memory location '377. During the first pass of an assembly operation, the assembler builds a

symbol table that relates each symbol (also called variable, or symbolic name) to the location where it is defined. On the second pass, the numerical value of each symbol is substituted for the alphanumeric expression, wherever it is used in an address field.

Symbolic names can, in many cases, be modified or processed by arithmetic operators, as in

LDA DATA-1

LDA DATA\*4-1

## Pseudo Operations

In addition to instruction statements, the assembly language provides pseudo operation statements that give the programmer control of the assembly process itself and of the loading operation that follows assembly.

In the example of Figure 1-1, several pseudo-operations are used. The program example begins with an ABS, specifying absolute loading mode. An ORG statement sets the assembler's location count (discussed later) to '3000. A OCT statement equates the symbol DOS to the octal quantity '30000. The program example ends with a mandatory END statement. These and many other pseudo-operations are described in detail in Section 4.

# Macro Facility

The macro feature of this assembler enables the programmer to define functions that can be expressed in easily interpreted English (or other) language statements:

#### TRANSFER DATA TO DAC

### TURN ON VALVE 312

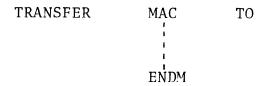

Statements of this sort are made possible by a process called macro definition. With the aid of the MAC and ENDM pseudo-operations, a system programmer can create macro prototypes.

The TRANSFER statement, above, might be defined by the following sequence of statements:

TRANSFER MAC TO

LDA <1>

OTA <2>

ENDM

The MAC pseudo-operation introduces the macro definition by assigning the name TRANSFER to the macro and identifying the word TO as a dummy word (a word that can be used to increase the intelligibility of macro calls without being mistaken for an argument).

Variable fields of the LDA and OTA instructions call for arguments, symbolized by numerals enclosed within angle brackets. Values for arguments are supplied by the macro call statements. For example the statement TRANSFER DATA to DAC calls for the TRANSFER macro to be assembled, with the symbol DATA substituted for argument <1>, and the symbol DAC substituted for argument <2>. The TRANSFER macro would then be assembled as follows:

After a set of macros has been defined by a system-level programmer, a specialist in a particular application field can formulate macro calls in plain language to solve his application problems, without becoming involved in the details of assembly language programming. Definition, listing, and assembly are discussed in detail in Section 5.

The Macro Assembler translates ASCII source files and produces an object file, for processing by the Linking Loader, and an optional listing file, to be printed as a record of the source language statements and the octal codes to which they have been translated. The files may be printed or punched on tape during assembly or they may simply be stored (on disk, for example) until they are needed. Device options are specified by register settings at the start of assembly.

## Two-Pass Assembly

The assembler program itself is first loaded into computer memory. The assembler occupies approximately 4K memory locations; the absolute location in CPU memory depends on the amount of memory available, and the type of system (DOS-based, stand-alone, etc.).

To use the assembler, the operator sets up an input device containing a source program file. Devices to receive the object files and listing output (optional) are specified by entries in CPU registers and the assembler is started.

This two-pass assembler first reads the source file to locate and assign values to any alphanumeric variables (symbols) used in instruction or pseudo-operation variable fields. The source file is then returned to the beginning and read again. On the second pass, the assembler substitutes numerical values for all variables and evaluates expressions, thus converting symbolic references to 16-bit binary quantities. The assembler then outputs the object file and a listing, if requested.

### Object Output

The object output of the assembler is in a special format suitable for input to the Linking Loader. Instructions, data constants, and directives to the Loader are encoded as blocks of data in various sizes and formats. (For details, see Appendix F.) When object files are punched on paper tape, they are in an "invisible" character format; none of the frames punched on the tape will cause printing on an ASR. (This saves paper by eliminating nonsense printout when the ASR is used as the loading device.)

## Listing Format

The object file is in an arbitrary binary format that is meaningful only to the loader, but the optional listing file pairs an octal representation of the object code with the actual source input statements they represent, in a format that is meaningful to the programmer.

Figure 1-3 shows a section of a typical assembly listing and defines the main features. The format is organized in columns, but when long labels or other free format features are encountered, extra space is used as required.

Each page of the listing begins with a header provided by the source statements, and a sequential page number. The first statement in a program is used as the initial page header, unless it starts with a quotation mark ("). If column 1 of any statement contains an apostrophe ('), columns 2-72 of that statement become the title for all pages that follow until a new title is specified.

Columns 1-4 are reserved for error flags. (See Appendix G.) Columns 5-9 contain an octal assignment address location count and columns 11-19 contain the octal object code generated by each statement. Columns 21-26 contain a decimal line sequence number and columns 28-108 contain the source statement (ASCII Image) truncated if necessary depending on printer limitations.

```

(0001) *SHORT DEMO PROGRAM EXAMPLE

(8882) *

(00003) *

(8884)

ABS.

DISPLAY A REG IN PANEL IND

993868 (9895)

ORG

3000

6300001

140040 (0006)

CRA

原图的原生。

171728 (8007) C

OTA

1720

03002

100028 (0008)

SRi

GROOT:

41 03012 (0009)

JUFF

005

夏国的日本土

140114 (0010) A

IRX

838665

61.03884 (0011)

JMF

H

DATA INDICATORS COUNT SLOWLY

63966 -

140114 (0012) B

IRX

DELIBERATE ERROR LINE

636671

01 03006 (0213)

JMF

В

83818±

141286 (8814)

AOA

|-

(0015)

FAIL

03011 01 03001 (0016)

JHE

Γ.

03012

030000 (0017) DOS

COL

30000

003013 (0018)

END

Ħ

003004

0010

9911

0013

E

003006

9912

\mathbb{C}

003001

0067

0016

009

003012

8889

8617

```

Figure 1-3: Example of Assembly Listing

( VERSION P. 01)

0001 LINES WITH ERRORS.

### Location Count

The assembler assigns a sequential location count to each element in the object code that will be converted to a CPU memory location. (Instruction statements always generate one line of code; data defining pseudo-operations may generate one or more lines, depending on the constant format.)

The starting value for the location count is zero, unless another origin is specified by the ORG pseudo-operation. The assembler normally increments the location count by 1 after each entry but a new count can be established by another ORG statement at any point in a program. In the example of Figure 1-3, an ORG statement sets the origin to '3000 and the location count is stepped sequentially from that value.

Figure 1-3 also shows how symbols are assigned numerical values in relation to location counts. The symbol A for example, is equated to '3000 when it is used in the label field of the IRS instruction in that location.

The address field of the JMP instruction in location 3005 contains a reference to the symbol A. Notice that the JMP instruction is assembled with the assigned value of A ('3004) in its address field.

## Symbol Cross Reference Listing

At the end of the assembly listing appears a cross-reference listing of each symbol's name (in alphabetical order), the symbol's assignment address or value, and a list of all reference to that symbol. Each reference is identified by a 4-digit decimal line number.

The information necessary for the cross-reference listing is stored in the symbol table. If, during assembly, the symbol table becomes full, cross-reference information is sacrificed in order for assembly to continue. If this occurs, the cross-reference listing will contain only the alphabetic symbol names and their assignment addresses.

If listing is inhibited (by NLST pseudo-operation), the cross reference listing is not listed. The same listing device is used for the cross-reference as is used for the Pass 2 assembly listing.

The last line of the listing specifies the version of the assembler and the number of lines containing error flags.

The Linking Loader is required to interpret the object code blocks, form 16-bit binary instruction and data codes, and load them in the proper locations of main memory. The actual location in which a word is loaded depends on whether absolute (ABS) or relocatable (REL) mode has been specified. (ABS is the assembler's default mode.) In absolute mode, the assembler-assigned location count becomes the actual instruction location. In relocatable mode, an address offset, entered into a register at the start mode of loading, is added to the location count. The E32R and E64R addressing modes further modify this procedure.

Two or more relocatable programs can be packed together anywhere in memory without wasted space, even though the final locations are unknown at the time of programming. The "linking" feature of the assembler-loader combination permits main programs and subroutines to share common data locations and entry points.

# Desectorizing and Address Resolution

In assembly language there is no way to specify that the sector bit of memory reference instructions is to be set, except to count instructions and data locations and deliberately keep track of the current sector. In a program of any length, bookkeeping of this type would become tedious. Instead, the assembler and loader take over this function. They jointly keep track of sector information and set or clear the sector bit of each memory instruction at the time it is loaded.

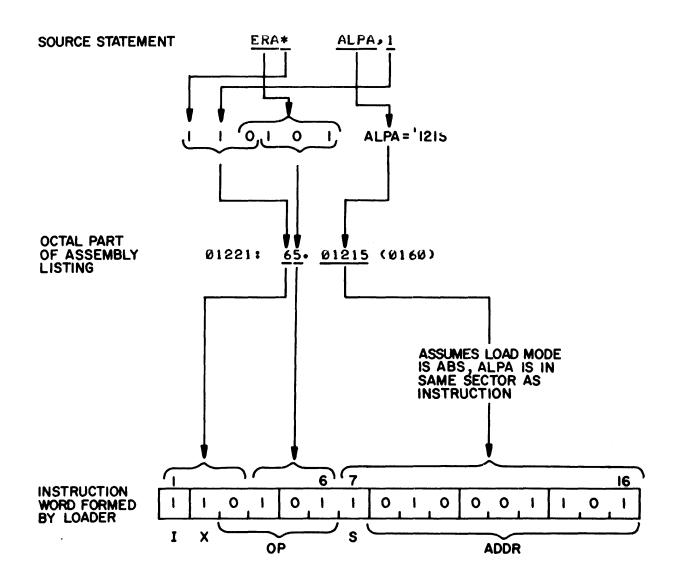

The binary object code output of the assembler includes a 14-bit or 15-bit address for each memory reference instruction, depending on whether or not extended addressing is in effect. (See EXD pseudo-operation).

In 16K sectored addressing mode (E16S), the assembler presents a 14-bit binary address to the loader, along with an indirect bit and indexing bit. As the loader processes the instruction, it compares the instruction's 14-bit address with the current location count. If the instruction and the address are in the same sector, the loader truncates the address to 9 bits, loads it into the instruction address field (bits 8-16) and sets the instruction's sector bit (bit 7).

However, if the instruction's 14-bit address specifies a different sector than the one containing the instruction, the loader assigns a location in a table of cross-sector indirect words and loads the 14-bit address (plus indirect and indexing bits) in that location. The indirect bit and address field of the instruction word itself are set to point to the indirect word. Since the indexing bit is moved to the indirect location, the index bit of the instruction itself is cleared.

Ordinarily, the table of indirect words begins at location '100 of Sector zero and grows upward as required. However, another base sector can be specified by the SETB pseudo-operation, and the starting location for the links can be altered by a register setting at the time of loading.

# Extended Addressing Mode

If extended addressing mode has been set up by the EXD pseudo-operation, the assembler presents 15-bit addresses to the loader. (Bit 2 of the address is interpreted as a magnitude bit rather than the index bit.) The check for cross-sector references is made as usual, and an indirect link is formed if necessary. The full 15-bit address is stored in a resulting indirect link location (indexing cannot be specified).

It is important to specify that code be loaded in the mode in which it is to execute. If the source program contains a EXD pseudo-operation, extended addressing mode must also be set up for the CPU by an E32S or E32R instruction.

# Loading Subroutines

If the main program calls for external subroutines, the loader halts and waits for the user to assign the library or other files containing subroutines to the input device already selected. The loader then identifies and loads every subroutine called by the main program. Subroutines are desectorized and linked together in consecutive memory locations unless new ORG values are assigned.

## Memory Map

At any time during loading of a series of programs and subroutines, the loader can be directed to print a memory map. The map shows the locations occupied by the program in memory, specifies locations for common storage, shows subroutine entry locations, and identifies subroutines that have been called but are not yet loaded. A memory map for the program example discussed earlier appears in Figure 1-4.

#### LOADING AND OPERATING PROCEDURES

Loading and operating procedures for the Macro Assembler vary according to the type of installation, memory size, and supporting software. Appropriate procedures are available in one of the following documents:

PRIME 200 Operator's Guide

PRIME 200 DOS Operator's Guide

\*START 01000 \*HIGH 03014 \*NAMES 20035 \*COMN 23777 \*PBRK 03014 \*BASE 00100 LIST 00001

Figure 1-4. Example of Memory Map

#### SECTION 2

### GENERAL ASSEMBLY LANGUAGE RULES

The following language features are common to all types of statements. Features that are peculiar to instruction statements, pseudo-operation statements, and macro calls are defined in later Sections.

# FREE-FORM INPUT TEXT

Input text for the PRIME 200 assembler may be prepared in a number of ways. Perhaps the most common is text prepared at a teleprinter with the aid of the PRIME 200 text editor. The resulting source program exists as a file in memory or on the disk, and can be punched on paper tape in ASCII format. For text prepared in this way, the basic unit of information is a line, as delimited by carriage return-line feed (CRLF) characters. Because of the mechanical limitations of most teleprinter devices, lines are usually limited to 72 or 75 characters.

Input text may also be coded by hand on paper forms which are then keypunched to produce unit record cards. Each card is equivalent to one teleprinter line, but may contain up to 80 characters.

# Line Format

PRIME-200 assembler input lines consist of labels, statements, and comments strung together in a free (column independent) format without regard for tabulation positions or arbitrary column boundaries. The assembler recognizes statements within a line, and subfields within statements, by delimiters consisting of spaces, colons, commas, backslash (tab character), and semicolons. (Labels and comments are optional.) For examples see Figure 2-1.

Labels: Labels are used to assign mnemonic codes to memory locations - for example, the name of a subroutine entry location or the symbolic address of a constant or storage cell. Labels are optional. If a line includes a label, the first character of the label must be in column 1 of the line. (Otherwise column 1 must be blank.) Labels must conform to the character set and size prescribed for variables.

Figure 2-1. Source Input Line Formats

Statements: The PRIME 200 assembler accepts four types of statements: symbolic instructions, pseudo-operations, macro calls and commands to the RDALN source file update program. Each of these has a different sub-field format, and is described in a later section of this manual.

If the line does not have a label, the first statement begins with column 2 or the first non-space character. Otherwise the statement begins with the first non-space character following the label.

A statement is terminated by two spaces or column 73, whichever comes first. Subsequent characters are assumed to be comments and are ignored except for listing.

Multiple Statements per Line: Statements can be packed two or more per line, separated by colons (:). The first non-space character following the colon is processed as the first character of the next statement. The last statement in the line is terminated by two spaces or column 73, and the rest of the line treated as comments.

If the line begins with a label, the label is attached to the first statement during assembly.

Continued Statements: The last statement in a line may be interrupted by a semicolon (;) and continued on the next line. The rest of the line following the semicolon is treated as comments. Processing of the statement continues with the first non-space character in the following line. Semicolons occurring within comments are not interpreted as a continuation request.

Comments: All text following column 72, or following a statement and two or more spaces, is treated as comments, and ignored except for listing. Comments can contain all printing ASCII characters.

Comment Lines: If column 1 of a line contains an asterisk (\*) the rest of the line is treated as comments. (Comment lines can be used to continue comments begun in the preceding statement line.)

Change Page Heading Lines: A line that contains an apostrophe (') in column 1 is assumed to contain the text of all subsequent page titles.

$\underline{\text{Examples}}\colon$  The following assembly listing illustrates many of the free-form input features.

```

(0197) *---TEST OF LONG LABELS.

02.01215 (0198) ABCDEFGHIJ*KLMNOPQRSTUVWXYZ0123456789 LDA ALPA

01252:

01253:

02.01252 (0199)

ABCDEFGHIJ*KLMNOFQRSTUVWXYZ01234567789

LDA

(0200) *

(0201) *---TEST OF FREE FORMAT AND LINE CONTINUATION

(0202) AB;

(820%)

1

Ħ.

01254: 06.01215 (0204)

00

ALPA.

01255

0000001

(0205)

1.

01256: 01 01215 (0206) AB JMP ALPA

01257:

140114 (0207)

IRX

COMMENT

01260:

041166 (0208)

LLS 10

01261: 26 01220 (0209)

ADD.

BETA, 1

01262 :

041067

(0210)

9

COMMENT

(0211) *

(0212) *---TEST OF MULTIPLE INSTRUCTIONS PER LINE.

01263:

02 00001 (0213) ABX LDA

1.

ADD

2:

STA

3

01264

06.00002

01265: 04 00003

140040 (0214)

01266:

CRA: IAB: CRA: STA @

01267:

999291

01270:

140040

```

CONSTANTS, VARIABLES AND EXPRESSIONS

## Constants

Symbolic names and address expressions used within the assembler program statements may contain decimal, octal, hexadecimal or ASCII constants.

Magnitudes: Numerical constants used in expressions are limited to the magnitudes that can be represented by the single-precision (16-bit) PRIME 200 binary arithmetic word:

| Type        | Max. Negative | Max. Positive   |

|-------------|---------------|-----------------|

| Decimal     | -32768        | +32767          |

| Octal       | - '100000     | + '777777       |

| Hexadecima1 | -\$4000       | <b>+</b> \$7FFF |

Leading zeroes can be omitted. If the sign is omitted, the quantity is assumed to be positive.

Double precision and floating point constants may be set up using the data defining pseudo-operations described in Section 4. However, these constants cannot be used within expressions.

Decimal Constants: All numerical quantities are assumed to be decimal (base 10) unless they are tagged with the octal, hexadecimal or ASCII designator symbols shown below.

Octal Constants: Octal constants (base 8) are identified by an apostrophe or O designator:

Note that the sign follows the octal designator. In expressions, however, the minus operator must precede the designator: SYMBOL-'123 is legal, but SYMBOL+'-123 is not.

Hexadecimal Constants: Hexadecimal constants (base 16) are identified by a dollar sign or X designation:

\$30BF or X'30BF' \$-30BF or X'-30BF' Here also the sign follows the designator, but in expressions the minus operator must precede the designator: SYMBOL-\$30BF is legal, but SYMBOL+\$-30BF is not.

The hexadecimal digit values are:

| Hexadecimal Digit | Decimal Value |

|-------------------|---------------|

| 0 - 9             | 0 - 9         |

| A                 | 10            |

| В                 | 11            |

| С                 | 12            |

| D                 | 13            |

| Е                 | 14            |

| F                 | 15            |

ASCII Constants: One or two eight-bit ASCII character codes can be represented by the following notation:

- C'A' Represents the ASCII code for the character A, left-justified in a 16-bit field with a trailing space character.

- C'AZ' Represents the codes for the ASCII characters A and Z, packed into a 16-bit field with A left justified and Z occupying the rightmost 8 bits.

Any printing character of the ASCII character set can be used.

# Examples:

| 87888  | 140646 |        | P2#6 | DATA | COAC  |

|--------|--------|--------|------|------|-------|

| 0.7961 | 148737 | (6995) |      | DATA | C'AZ' |

### Variables

Variables are alphanumeric strings, often called "symbols" or "symbolic names", that are equated to numerical values in various ways. If a variable is used as the label of a statement, it is assigned the value of the location count for that statement. Variables may also be defined by the SET, EQU and DAC pseudo-operations described in Section 4.

Variables can be from 1 to 32 characters long. The first character must be a letter (A-Z), and the remaining characters may be letters, numerals (0-9) or the dollar sign (\$). Variables containing more than 32 characters are allowed but only the first 32 characters are recognized by the assembler. Variable names must be unique (cannot be defined more than once).

Examples: The following examples show some of the ways a variable "VARI35\$" can be used.

02002: 02.01234 (0006) P2\$7 LDA VARI35\$ 02003: 02.01333 (0007) LDA VARI35\$+177 001234 (0008) VARI35\$ SET 11234 02004: 01.01232 (0009) JMP VARI35\$-2

### Expressions

Expressions consist of constants or variables joined by operators. All variables within an expression must be defined as single precision values or addresses. Absolute, relative and external values cannot be used in the same expression.

### Examples:

02005 02 00107 (0010) P2\$8 LDA K100+3 02006: 64 03:42 (0011) STA \*+VARI35\$-K100

Operators: The PRIME 200 assembler is able to process the following arithmetic, logical, relational and shift operators while evaluating expressions in instruction address fields, arguments in macro calls, etc.

- \* Arithmetic Multiply

- / Arithmetic Divide

- + Arithmetic Add

- Arithmetic Subtract

- OR. Logical OR (16 bits)

- .XOR. Logical XOR (16 bits)

- .AND. Logical AND (16 bits)

- .EQ. Relational EQ (resulting in 0 or 1)

- .NE. Relational NE (resulting in 0 or 1)

- .GT. Relational GT (resulting in 0 or 1)

- .LT. Relational LT

- .GE. Relational GE (resulting in 0 or 1)

- .LE. Relational LE (resulting in 0 or 1)

- .RS. Logical Right Shift (16 bits)

- .LS. Logical Left Shift (16 bits)

Space Conventions: Operators may be followed by a single space (optional). The logical, relational and shift operators must be preceded with a space so that the period beginning these symbols will not be interpreted as a decimal point.

Operator Priority: In expressions with more than one operator, the order of evaluation is governed by operator priority. The operator with the highest priority is performed first. In cases of equal priority, the evaluation proceeds from left to right. Parentheses may be used to alter the natural order of evaluation.

| <u>Priority</u> | <pre>Operator(s)</pre>      |  |  |  |  |  |

|-----------------|-----------------------------|--|--|--|--|--|

| Highest         | * / +RSLSGTGEEQNELELTANDOR. |  |  |  |  |  |

| Lowest          | .XOR.                       |  |  |  |  |  |

Relational Operators: These are most often used in the argument field of IF pseudo-operations. However they may be used in other expressions. Examples of the correct syntax are:

|                  |                | (0234) | +TEST | RELATIO       | NFIL. | OPERA        | FORIS.        |     |       |   |

|------------------|----------------|--------|-------|---------------|-------|--------------|---------------|-----|-------|---|

| 61364            | 999964         | (8235) | DATA  | 5 EQ.         | 5.    | 5 .EQ.       | 60            | f;  | EQ.   | 5 |

| 01305            | 000000         | *      |       |               |       |              |               |     |       |   |

| <b>9</b> 1.396 : | 0000000        |        |       |               |       |              |               | ,   | 6 IFT | _ |

| 01.307           | 966666         | (9236) | DATA  | 5 , NE.       | 5.    | 5 NE.        | 6,            | 6   | NE.   | 5 |

| 0131.0°          | 000001         |        |       |               |       |              |               |     |       |   |

| 01311 °          | 696661         |        |       |               |       | , m., m.,    |               | ,-  | C T-  | 5 |

| 01312:           | 999999         | (0237) | DATA  | 5 GT          | 5.    | 5 . GT.      | tov           | to  | . GT  | ! |

| 01313            | 999999         |        |       |               |       |              |               |     |       |   |

| Ø1.314:          | 000001         |        |       |               |       | ,            |               | ,   | 1 7   | = |

| 01315:           | 999999         | (0238) | DATA  | 5 LT.         | D.    | 5 . LT.      | t <u>n</u> i, | μ.  | LT.   | ) |

| 01316:           | 000000         |        |       |               |       |              |               |     |       |   |

| 01317:           | 999999         |        |       |               |       | pras ,, pras |               |     | , p   | 5 |

| 01320:           | 999991         | (0239) | DATA  | 5 . GE.       | 56    | 5 . GE.      | to a          | ļī, | . GE. | 1 |

| 01321            | 999999         |        |       | a compresso o |       |              |               |     |       |   |

| 01322:           | 999991         |        |       |               |       |              |               |     |       |   |

| 01.323:          | <b>99999</b> 4 | (0240) | DATA  | 5 LE.         | 5.    | 5 . LE       | 67            | 6   | LE.   | 5 |

| 01.R24 :         | 000001         |        |       |               |       |              |               |     |       |   |

| 01325 ·          | 999999         |        |       |               |       |              |               |     |       |   |

|                  |                |        |       |               |       |              |               |     |       |   |

Shift Operators: The shift operators perform a logical right or left shift of an expression, using the syntax:

Argument Expression RS. Shift Count Expression

where the shift count expression has a numerical value from  $1\ \text{to}\ 16$ .

Examples:

(0241) \* (0242) \*---TEST SHIFT OPERATOR. 01326: 999191 (0243) DATA (1010 RS. 3) (1010 LS. 3) (1010 LS. 4 01327: 010188 01330: 020200 01331: 010100 (0244) DATA (1010 .RS. -3, (1010 .LS. -3 01332: 000101 (0245) \*

## <u>Logical Operators</u>: Examples are shown below.

|        |         | (0229) | *TEST | LOGICAL    | OPERATORS |

|--------|---------|--------|-------|------------|-----------|

| 01301: | 001101  | (0230) | DATA  | 11100 .    | OF 10101  |

| 01302: | 001.001 | (0231) | DATA  | 11100      | XOR 0101  |

| 01303: | 000100  | (0232) | DATA  | $^{2}1100$ | AND 0101  |

|        |         | (8233) | *     |            |           |

# <u>Sign Conventions</u>: In expressions containing the + and - operators, integer constants may be signed:

| 82867:  | 02.01715 | (0013) | P2#12  | LDA  | ZILCH-\$3E |

|---------|----------|--------|--------|------|------------|

| 02010   | 02.01715 | (0014) |        | LDA  | ZILCH+#-3E |

| 02011   | 02.01755 | (0015) |        | LDA  | ALPHA-137  |

| OPPILE: | 02.01755 | (0016) |        | LDA  | ALPHA+1-37 |

| 02013:  | 999999   | (8017) | ZILCH  | DEC  | 0          |

| 92914:  | 9991.4%  | (0018) | AL PHA | DATA | 99         |

#### SECTION 3

#### INSTRUCTION STATEMENTS

This section defines the form of all PRIME 200 instruction statements, shows how instructions are processed by the assembler and loader, and covers syntax elements peculiar to instruction statements.

Table 3-1 lists the instruction mnemonics acceptable to the assembler. Note that some instructions have two mnemonics; those in parentheses are accepted for compatibility with other assemblers. Mnemonics in Table 3-1 are in order by functional type. The instructions are sorted by op-code in Appendix A, by class in Appendix B, and by mnemonic in Appendix C.

## INSTRUCTION STATEMENT GENERAL FORMAT

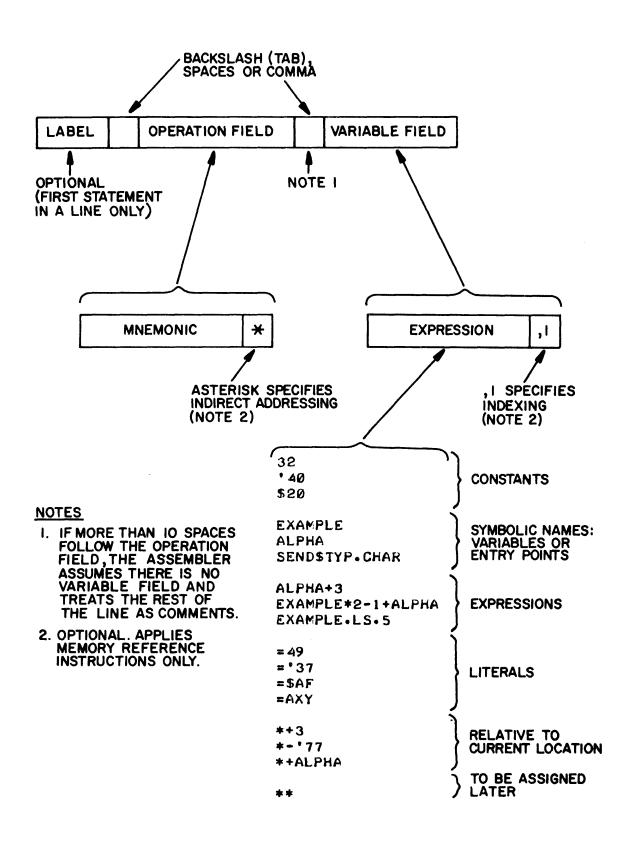

The essential elements of an instruction statement are an operation field and a variable field, separated by spaces, a comma, or a backslash tab symbol (\), as shown in Figure 3-1. The content of each field depends on the type of instruction being processed. Memory reference instructions have different requirements than I/O, shift, bit reference, or generic instructions. Label and comment fields are optional.

#### Labe1

if a label is present, it is assigned the current location count and entered in the symbol table.

## Operation Field

The operation field must contain one of the PRIME 200 instruction mnemonics listed in Table 3-1. An asterisk, for indirect addressing, applies to memory reference instructions only. Parentheses are ignored:

| 04.242 | GO | គគគ។ ១ | (0181) | (LDA)  | 10             |

|--------|----|--------|--------|--------|----------------|

|        |    |        | (0182) | (LDA*) | 10             |

|        |    |        | (0183) | (LDA)* | 10             |

|        |    |        |        | (LDA)* | 10.1           |

| 01245  | 60 | 00012  | (0184) | CLUMAT | ala fait i ala |

Table 3-1. Summary of PRIME 200 Instruction Codes

| CIASS | OP CODE    | PNEMONIC         | DEFINITION                               |

|-------|------------|------------------|------------------------------------------|

|       |            | REGISTER         |                                          |

| G     | 140040     | CRA              | CLEAR A                                  |

| Ği    | 140014     |                  | CLEAR B                                  |

| G     | 140010     |                  | CLEAR LONG (A AND B)                     |

| MR    | <b>0</b> 2 | LDA              | LOAD A                                   |

| MIS   | 04         | STA              | STORE A                                  |

| लाह   | 15         | LDX              | LOAD INDEX (ASSEMBLER SETS INDEX BIT)    |

| MR    | 15         | STX              | STORE INDEX (ASSEMBLER CLEARS INDEX BIT) |

| MR    | 1.3        | IMA              | INTERCHANGE MEMORY AND A                 |

| G     | 000201     | IAB              | INTERCHANGE A AND B                      |

| G     | 140104     | XCA              | TRANSFER A TO B AND CLEAR A              |

| G     | 140204     |                  | TRANSFER B TO A AND CLEAR B              |

| Či    | 000111     | CER              | COMPUTE EFFECTIVE ADDRESS                |

|       |            | ARITHMETI        | <del>-</del> .                           |

|       |            | FIRE LIPTIE I LI | '                                        |

| MR    | <b>0</b> 6 | ADD              | ADD MEMORY TO A                          |

| MR    | 97         | SUB              | SUBTRACT MEMORY FROM A                   |

| G     | 141206     | AOA (A1A)        | ADD ONE TO A                             |

| G     | 140304     | H2H              | ADD TWO TO A                             |

| G     | 140110     | 50A (51A)        | SUBTRACT ONE FROM A                      |

| G     | 140310     | 52A              | SUBTRACT TWO FROM A                      |

| 13    | 141216     | ACA              | ADD C-BIT TO A                           |

| £i.   | 140320     | CSA              | COPY SIGN TO C-BIT, SET SIGN OF A PLUS   |

| G     | 140100     | SSP              | SET SIGN OF A PLUS                       |

| G     | 140500     | SSM              | SET SIGN OF A MINUS                      |

| G     | 1.40024    | CHS              | CHANGE SIGN OF A                         |

| G     | 140407     | TCA              | TWO'S COMPLEMENT A                       |

| G     | 000205     | PIM              | POSITION FOR INTEGER MULTIPLY            |

| Ĺi    | 000211     | PID              | POSITION FOR INTEGER DIVIDE              |

| MR    | 1.65       | MEN'T            | MULTIFLY                                 |

| MR    | 17         | DIA              | DIVIDE                                   |

Table 3-1 (Cont)

| MR                                   | 82 *                                                                                   | DLD                                                                                           | DOUBLE PRECISION LOAD                                                                                                                                                                                                                                                 |  |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MR                                   | 이 <b>로</b><br>이러 *                                                                     | DST                                                                                           | DOUBLE PRECISION STORE                                                                                                                                                                                                                                                |  |  |  |  |  |

| MR                                   | 86 *                                                                                   | DAD                                                                                           | DOUBLE PRECISION ADD                                                                                                                                                                                                                                                  |  |  |  |  |  |

| MR                                   | 07 *                                                                                   | DSB                                                                                           | DOUBLE PRECISION SUBTRACT                                                                                                                                                                                                                                             |  |  |  |  |  |

| 7 14 %                               |                                                                                        |                                                                                               |                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                                      |                                                                                        |                                                                                               |                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                                      |                                                                                        | INPUT/OUTF                                                                                    | PUT                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                                      |                                                                                        |                                                                                               | *****                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| TO                                   | 14                                                                                     | OCP                                                                                           | OUTPUT CONTROL PULSE                                                                                                                                                                                                                                                  |  |  |  |  |  |

| IO                                   | 34                                                                                     | SKS                                                                                           | SKIP IF SET                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 10                                   | 54                                                                                     | INA                                                                                           | INPUT TO A                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 10                                   | 74                                                                                     | OTA                                                                                           | OUTPUT FROM A                                                                                                                                                                                                                                                         |  |  |  |  |  |

| G                                    | 000511                                                                                 | ISI                                                                                           | INPUT SERIAL INTERFACE TO A                                                                                                                                                                                                                                           |  |  |  |  |  |

| G                                    | 000515                                                                                 | OSI                                                                                           | OUTPUT SERIAL INTERFACE FROM A                                                                                                                                                                                                                                        |  |  |  |  |  |

| 10                                   | 74                                                                                     | SMK                                                                                           | SET INTERRUPT MASK                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                                      |                                                                                        |                                                                                               |                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                                      |                                                                                        | CONTROL                                                                                       |                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                                      |                                                                                        | CONTROL                                                                                       |                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| G                                    | 999999                                                                                 | CONTROL<br>HLT                                                                                | HALT                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                                      | 000000<br>000001                                                                       |                                                                                               | HALT<br>NO OPERATION                                                                                                                                                                                                                                                  |  |  |  |  |  |

| G                                    |                                                                                        | HLT                                                                                           |                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                                      | 000001                                                                                 | HLT<br>NOP                                                                                    | NO OPERATION                                                                                                                                                                                                                                                          |  |  |  |  |  |

| G<br>G<br>G                          | 000001<br>140600                                                                       | HLT<br>NOP<br>SCB                                                                             | NO OPERATION SET C-BIT RESET C-BIT ENTER SINGLE PRECISION MODE                                                                                                                                                                                                        |  |  |  |  |  |

| G<br>G<br>G                          | 000001<br>140600<br>140200                                                             | HLT<br>NOP<br>SCB<br>RCB                                                                      | NO OPERATION SET C-BIT RESET C-BIT ENTER SINGLE PRECISION MODE ENTER DOUBLE PRECISION MODE                                                                                                                                                                            |  |  |  |  |  |

| G<br>G<br>G<br>G                     | 000001<br>140600<br>140200<br>000005                                                   | HLT<br>NOP<br>SCB<br>RCB<br>SGL                                                               | NO OPERATION SET C-BIT RESET C-BIT ENTER SINGLE PRECISION MODE ENTER DOUBLE PRECISION MODE ENTER MACHINE CHECK MODE                                                                                                                                                   |  |  |  |  |  |

| 6<br>6<br>6<br>6<br>6                | 000001<br>140600<br>140200<br>000005<br>000007                                         | HLT<br>NOP<br>SCB<br>RCB<br>SGL<br>DBL<br>EMCM<br>LMCM                                        | NO OPERATION SET C-BIT RESET C-BIT ENTER SINGLE PRECISION MODE ENTER DOUBLE PRECISION MODE ENTER MACHINE CHECK MODE LEAVE MACHINE CHECK MODE                                                                                                                          |  |  |  |  |  |

| 6<br>6<br>6<br>6<br>6<br>6           | 000001<br>140600<br>140200<br>000005<br>000007<br>000503                               | HLT<br>NOP<br>SCB<br>RCB<br>SGL<br>DBL<br>EMCM<br>LMCM<br>RMC (RMP)                           | NO OPERATION SET C-BIT RESET C-BIT ENTER SINGLE PRECISION MODE ENTER DOUBLE PRECISION MODE ENTER MACHINE CHECK MODE LEAVE MACHINE CHECK MODE RESET MACHINE CHECK                                                                                                      |  |  |  |  |  |

| 6<br>6<br>6<br>6<br>6<br>6<br>6      | 000001<br>140600<br>140200<br>000005<br>000007<br>000503<br>000501                     | HLT<br>NOP<br>SCB<br>RCB<br>SGL<br>DBL<br>EMCM<br>LMCM<br>RMC (RMP)<br>F16S(DXA)              | NO OPERATION SET C-BIT RESET C-BIT ENTER SINGLE PRECISION MODE ENTER DOUBLE PRECISION MODE ENTER MACHINE CHECK MODE LEAVE MACHINE CHECK MODE RESET MACHINE CHECK ENTER 16K SECTOR ADDRESSING MODE                                                                     |  |  |  |  |  |

| 6<br>6<br>6<br>6<br>6<br>6<br>6      | 000001<br>140600<br>140200<br>000005<br>000007<br>000503<br>000501<br>000021           | HLT<br>NOP<br>SCB<br>RCB<br>SGL<br>DBL<br>EMCM<br>LMCM<br>RMC (RMP)<br>F16S(DXA)              | NO OPERATION SET C-BIT RESET C-BIT ENTER SINGLE PRECISION MODE ENTER DOUBLE PRECISION MODE ENTER MACHINE CHECK MODE LEAVE MACHINE CHECK MODE RESET MACHINE CHECK ENTER 16K SECTOR ADDRESSING MODE ENTER 32K SECTOR ADDRESSING MODE                                    |  |  |  |  |  |