BUSINESS ASSEMBLY LANGUAGE

REFERENCE MANUAL

# QANTEL

**BUSINESS**

**ASSEMBLY**

**LANGUAGE**

(Q/BAL)

REFERENCE MANUAL

QANTEL Sales Offices: 3474 Investment Blvd., Hayward, CA 94545, (415) 783-3410 · 1700 So. El Camino Real, San Mateo, CA 94402, (415) 349-8400 · 8622 Bellanca Avenue, Los Angeles, CA 90045, (213) 641-8644 · 1 Alexander Lane, Littleton (Denver), CO 80121, (303) 770-2411 · 1000 Skokie Blvd., Wilmette (Chicago), IL 60091, (312) 256-2800 · P.O. Box 13302, Kansas City, MO 64105, (816) 842-0384 · 725 14th St., Marion, IO 52303, (319) 377-8277 · 26525 Southfield Rd., Southfield, MI 40875, (313) 356-6686 · 500 North Avenue, Wakefield, MA 01880, (617) 246-0936 · 1381 Marshall Avenue, St. Paul, MN 55104, (612) 646-6573 · 245 Park Avenue, New York, NY 10017, (212) 867-5035 · 2316 Seventh Avenue South. Birmingham, AL 35233, (205) 252-0114 · 2907 Bay-to-Bay Blvd., Tampa, FL 33609, (813) 837-2438.

# TABLE OF CONTENTS

# SECTION I – GENERAL DESCRIPTION

| PARAGRAPH    |                                           | PAGE |

|--------------|-------------------------------------------|------|

| 1-1          | Introduction                              | 1-1  |

| 1-4          | Related Reference Publications            | 1-1  |

| 1-6          | Definition of Terms                       | 1-2  |

| 1-8          | System Description                        | 1-3  |

| 1-12         | High-Speed Memory                         | 1-3  |

| 1-14         | Control Memory                            | 1-3  |

| 1-16         | Hexadecimal System                        | 1-3  |

| 1-19         | ASCII                                     | 1-4  |

| 1-21         | System Specifications                     | 1-4  |

| 1-23         | Assembler Description                     | 1-4  |

| 1-26         | Pass One                                  | 1-5  |

| 1-28         | Pass One Error Detection                  | 1-5  |

| 1-32         | Pass Two                                  | 1-6  |

| 1-34         | Update Operation                          | 1-6  |

| 1-34         | Source Program Library Files              | 1-6  |

| 1-38         | Magnetic Tape Source Program Files        | 1-6  |

|              | Disc Source Program Files                 | 1-6  |

| 1-40         | · · · · · · · · · · · · · · · · · · ·     | 1-7  |

| 1-42         | Object Program Library Files              | 1-7  |

| 1-45         | Loadable Object Programs                  | 1-8  |

| 1-47         | Library Object Files                      | 1-0  |

| 2-1          | SECTION II – PROCESSOR FUNCTIONS  General | 2-1  |

| 2-3          | Data Format                               | 2-1  |

| 2-5          | Instruction Format                        | 2-1  |

| 2-6          | Single-Address Instructions               | 2-1  |

| 2-8          | Two-Address Instructions                  | 2-2  |

| 2-11         | Indirect Addressing                       | 2-2  |

| 2-11         | Operation Code and Variant                | 2-3  |

| 2-14         | Instruction Length                        | 2-3  |

| 2-10<br>2-21 | Addressing Structure                      | 2-4  |

| 2-21         | Reserved Memory                           | 2-4  |

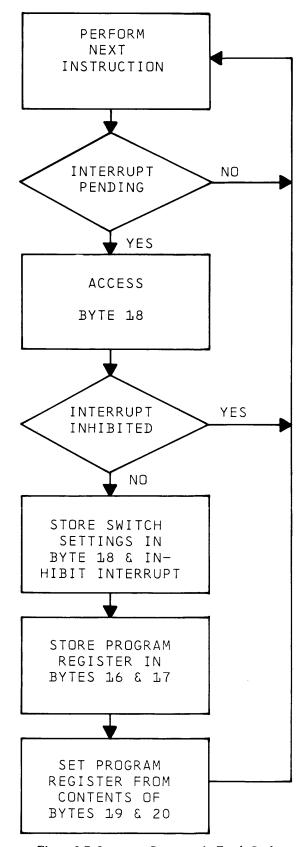

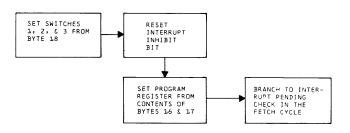

| 2-25<br>2-25 | Interrupt Feature                         | 2-4  |

| 2-23         | Switch Settings                           | 2-6  |

| 2-33         | Switch One                                | 2-6  |

| 2-35<br>2-35 | Switch Two                                | 2-6  |

| 2-33<br>2-37 | Switch Three                              | 2-6  |

|              | Standard Instructions                     | 2-7  |

| 2-40         |                                           | 2-7  |

| 2-42         | Data Handling Instructions                | 2-7  |

| 2-43         | Move - MOV (OP CODE 6)                    | 2-7  |

| 2-45         | Store Accumulator - STA (OP CODE 6)       |      |

| 2-47         | Load - LD (OP CODE 5)                     | 2-8  |

| 2-50         | Edit - EDT (OP CODE 9, VARIANT 9)         | 2-9  |

| 2-54         | Unedit - UED (OP CODE 9, VARIANT A)       | 2-10 |

| PARAGRAPH |                                                        | PAGE         |

|-----------|--------------------------------------------------------|--------------|

| 2-58      | Move Numeric - MN (OP CODE 9, VARIANT 4)               | 2-12         |

| 2-60      | Move Zone - MZ (OP CODE 9, VARIANT 5)                  | 2-12         |

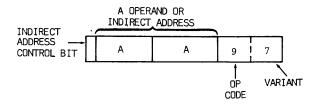

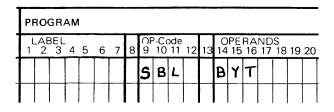

| 2-62      | Shift Bit Left - SBL (OP CODE 9, VARIANT 7)            | 2-13         |

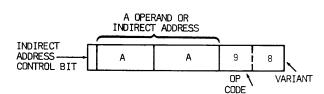

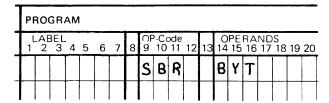

| 2-64      | Shift Bit Right - SBR (OP CODE 9, VARIANT 8)           | 2-13         |

| 2-66      | Pack - PAK (OP CODE 9, VARIANT B)                      | 2-14         |

| 2-70      | Unpack - UPK (OP CODE 9, VARIANT C)                    | 2-15         |

| 2-72      | Translate - TRN (OP CODE 8, VARIANT 2)                 | 2-15         |

| 2-74      | Arithmetic and Logical Instructions                    | 2-16         |

| 2-75      | Decimal Arithmetic Instructions - General              | 2-16         |

| 2-78      | Add Decimal - ADD (OP CODE 1)                          | 2-17         |

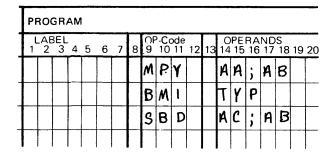

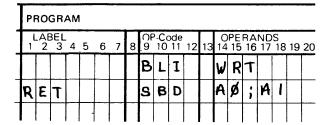

| 2-82      | Subtract Decimal - SBD (OP CODE 2)                     | 2-18         |

| 2-84      | Multiply Decimal - MPY (OP CODE 3)                     | 2-18         |

| 2-87      | Divide Decimal - DIV (OP CODE 4)                       | 2-19         |

| 2-91      | Add Binary - ADB (OP CODE D)                           | 2-21         |

| 2-93      | Subtract Binary - SBB (OP CODE E)                      | 2-22         |

| 2-95      | And - AND (OP CODE 9, VARIANT Ø)                       | 2-23         |

| 2-98      | Or - OR (OP CODE 9, VARIANT 10)                        | 2-23         |

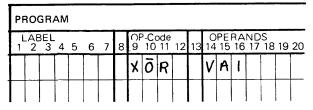

| 2-100     | Exclusive Or - XOR (OP CODE 9, VARIANT 2)              | 2-24         |

| 2-102     | Decision and Control Instructions                      | 2-24         |

| 2-103     | Branch On Overflow - BOV (OP CODE A, VARIANT 1)        | 2-24         |

| 2-105     | Branch On Minus - BMI or BGT (OP CODE A, VARIANT 2)    | 2-25         |

| 2-103     | Branch On Non-Zero - BNZ or BNE (OP CODE A, VARIANT 3) | 2-26         |

| 2-107     | Branch Equal - BEQ or BZ (OP CODE A, VARIANT 4)        | 2-26         |

| 2-103     | Branch Not Minus - BNM or BLE (OP CODE A, VARIANT 5)   | 2-20         |

| 2-111     | Unconditional Branch - BRU (OP CODE A, VARIANT 7)      | 2-27         |

| 2-115     | Halt and Branch - HLT (OP CODE A, VARIANT 8)           | 2-27         |

| 2-113     | Branch and Link - BLI (OP CODE A, VARIANT 9)           | 2-27         |

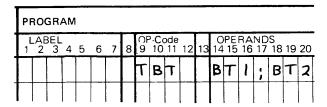

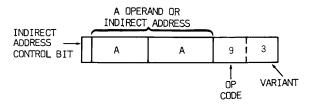

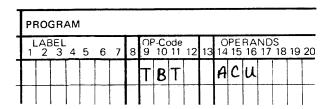

| 2-117     | Test Bit - TBT (OP CODE 9, VARIANT 3)                  | 2-27         |

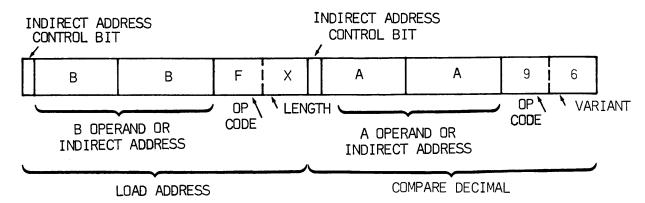

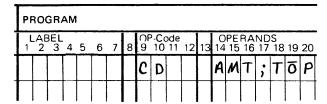

| 2-119     | Compare Decimal - CD (OP CODE 9, VARIANT 6)            | 2-28         |

| 2-122     | Compare Logical - CMP (OP CODE 7)                      | 2-20         |

| 2-123     | Return From Interrupt - RTI (OP CODE 9, VARIANT F)     | 2-30         |

| 2-127     | No Operation - NOP (OP CODE A, VARIANT Ø)              | 2-31         |

| 2-129     | Programming Note                                       | 2-31         |

| 2-131     | Special Instructions                                   | 2-31         |

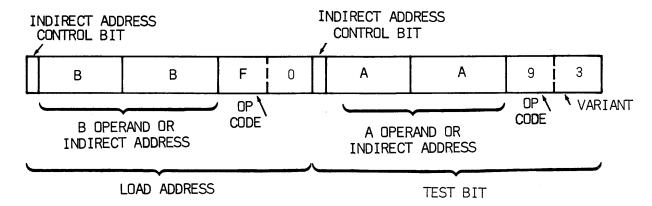

| 2-133     | Load Address - LDA (OP CODE F)                         | 2-32         |

| 2-134     | Micro-Instruction Mode - MIM (OP CODE A, VARIANT B)    | 2-32         |

| 2-130     | Search Equal - SEQ (OP CODE 8, VARIANT 3)              | 2-32         |

| 2-139     | Search Equal - SEQ (OF CODE 6, VARIANT 3)              | 2-33         |

|           | SECTION III – ASSEMBLER INSTRUCTION CODING             |              |

| 3-1       | General                                                | 3-1          |

| 3-3       | Labels                                                 | 3-1          |

| 3-5       | Label Form                                             | 3-1          |

| 3-7       | Label Value                                            | 3-3          |

| 3-9       | Label Length                                           | 3-3          |

| 3-11      | Programmer Access To Symbol Lengths (.)                | 3-3          |

| 3-13      | Decimal Values                                         | 3-4          |

| 3-15      | Hexadecimal Values                                     | 3 <b>-</b> 4 |

| 3-17      | Current Location Operand (*)                           | 3 <b>-</b> 4 |

| 3-17      | Expressions                                            | 3-5          |

|           | AND                | J - J        |

| PARAGRAPH    |                                                          | <b>PAGE</b> |

|--------------|----------------------------------------------------------|-------------|

| 3-22         | Free Format Coding                                       | 3-5         |

| 3-24         | First Character Position                                 | 3-5         |

| 3-26         | Comment Character (*)                                    | 3-5         |

| 3-28         | Pin Address Character (@)                                | 3-5         |

| 3-30         | Letters (A to Z)                                         | 3-5         |

| 3-32         | Space (Blank)                                            | 3-6         |

| 3-34         | Digits $(\emptyset \text{ to } 9)$ or Special Characters | 3-6         |

| 3-36         | Label Field                                              | 3-6         |

| 3-38         | Op-Code Field                                            | 3-6         |

| 3-40         | A/B Operand Field                                        | 3-6         |

| 3-44         | Indirect Addressing                                      | 3-7         |

| 3-46         | Comment Field                                            | 3-8         |

|              | SECTION IV – ASSEMBLER DIRECTIVES                        |             |

| 4-1          | Introduction                                             | 4-1         |

| 4-1          | Origin Control (ORG)                                     | 4-1         |

| 4-5<br>4-5   | End Control (END)                                        | 4-1         |

| 4-3<br>4-7   | Define Constant (DC)                                     | 4-2         |

| 4-10         |                                                          | 4-2         |

| 4-10<br>4-12 | Define Address Constant (DAC)                            | 4-2<br>4-2  |

| 4-12<br>4-14 | Define Area (DA)                                         | 4-2         |

| 4-14<br>4-16 | Equate (EQU)                                             | 4-3         |

| 4-10<br>4-19 | Execute (EXE)                                            | 4-3<br>4-3  |

|              |                                                          |             |

|              | SECTION V - INPUT/OUTPUT INSTRUCTIONS AND DEVICES        |             |

| 5-1          | Introduction                                             | 5-1         |

| 5-3          | Buffered I/O Devices                                     | 5-1         |

| 5-8          | Unbuffered I/O Devices                                   | 5-2         |

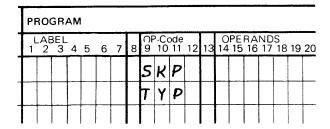

| 5-11         | Status                                                   | 5-2         |

| 5-13         | Status Byte                                              | 5-2         |

| 5-16         | Flag Bits                                                | 5-2         |

| 5-18         | Status Bits                                              | 5-3         |

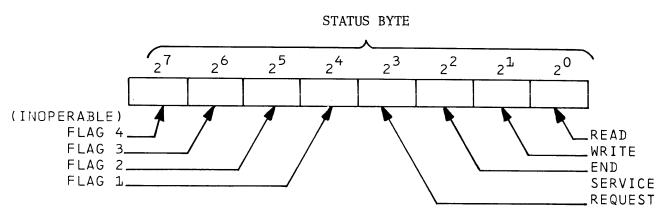

| 5-22         | Read Sequence                                            | 5-3         |

| 5-24         | Firm Status                                              | 5-4         |

| 5-28         | I/O Instructions                                         | 5-4         |

| 5-30         | I/O Read And Write Instructions                          | 5-5         |

| 5-31         | Read - RD (OP CODE 0)                                    | 5-5         |

| 5-33         | Read and Count - RDC (OP CODE 0, VARIANT 2)              | 5-5         |

| 5-36         | Read Hex - RHX (OP CODE 0, VARIANT 1)                    | 5-5         |

| 5-39         | Read Hex Count - RHC (OP CODE 0, VARIANT 3)              | 5-6         |

| 5-41         | Write - WR (OP CODE B, VARIANT 0)                        | 5-6         |

| 5-43         | Write and Count - WRC (OP CODE B, VARIANT 2)             | 5-7         |

| 5-46         | Write Hex - WHX (OP CODE B, VARIANT 1)                   | 5-8         |

| 5-48         | Write Hex and Count - WHC (OP CODE B, VARIANT 3)         | 5-8         |

| 5-50         | I/O Control Instructions                                 | 5-9         |

| 5-50<br>5-51 | Reset I/O - RIO (OP CODE 9, VARIANT E)                   | 5-9         |

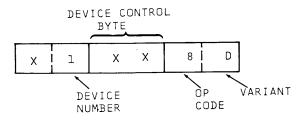

| 5-53         | Status-In - SIN, Set Read - SRD and Device Control - CTL | 5-7         |

| J-JJ         | (OP CODE 9 VARIANT D)                                    | 5-9         |

| ARAGRAPH   | 1                                           |

|------------|---------------------------------------------|

| 5-61       | Read Status 2 - RS2 (OP CODE 8, VARIANT 4)  |

| 5-63       | Initial Program Load (IPL)                  |

| 5-66       | Programming Notes                           |

| 5-69       | Input/Output Devices                        |

| 5-70       | Typewriter                                  |

| 5-72       | Typewriter Flags and Signals                |

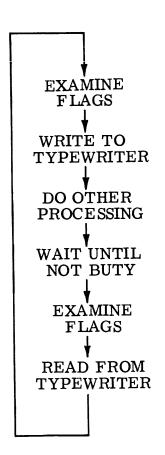

| 5-75       | Typewriter Status Checking                  |

| 5-78       | Typewriter Device Control                   |

| 5-80       | Typewriter Reset I/O                        |

| 5-82       | Typewriter Set Read                         |

| 5-84       | Magnetic Tape Transports                    |

| 5-87       |                                             |

|            | Magnetic Tape Device Control                |

| 5-89       | Magnetic Tape Status Checking               |

| 5-91       | Disc Drive                                  |

| 5-96       | Disc Status Checking and Control            |

| 5-98       | Card Reader                                 |

| 5-100      | Card Reader Set Read                        |

| 5-102      | Card Reader Status Checking                 |

| 5-104      | Paper Tape Reader/Punch                     |

| 5-106      | Ten-Key Keyboard                            |

| 5-108      | Ten-Key Device Control                      |

| 5-110      | Ten-Key Status Checking                     |

| 5-112      | Line Printers                               |

| 5-114      | Line Printer Device Control                 |

| 5-116      | Line Printer Status Checking                |

| 5-118      | System Clock/Interval Timer                 |

| 5-120      | Setting System Clock                        |

| 5-120      | Reading Interval Timer                      |

| 5-125      | System Clock/Interval Timer Status Checking |

|            | SECTION VI – ASSEMBLER OPERATION            |

| 6-1        | Introduction                                |

| 6-4        | Program Loading                             |

| 6-6        | IPL From Magnetic Tape Library              |

| 6-8        | IPL From A Disc Library                     |

| 6-10       | · - · · · · · · · · · · · · · · · · · ·     |

| 6-12       | Assembler Programs                          |

|            |                                             |

| 6-13       | Pass 1 Operation                            |

| 6-15       | Pass 2 Operation                            |

| 6-17       | Error Messages                              |

|            | APPENDIXES                                  |

| APPENDIX A | Hexadecimal-Decimal Number Conversion Table |

| APPENDIX B | ASCII Code                                  |

| APPENDIX C |                                             |

|            |                                             |

| APPENDIX D | QANTEL Standard Instruction Set             |

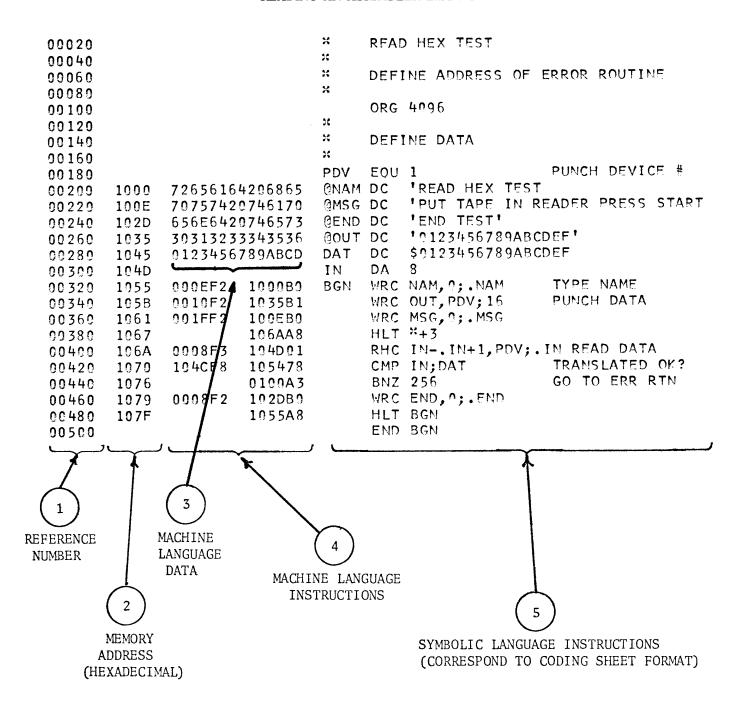

| APPENDIX E | Reading An Assembler Listing                |

| APPENDIX F | Programming Techniques                      |

### LIST OF ILLUSTRATIONS

| FIGURE<br>NUMBER |                                                                      | PAGE |

|------------------|----------------------------------------------------------------------|------|

| 1-1              | Assembler Create Operation                                           | 1-5  |

| 1-2              | Assembler Update Operation                                           | 1-6  |

| 1-3              | Program Library Files                                                | 1-7  |

| 1-4              | Object Program Formats                                               | 1-7  |

| 2-1              | Eight-bit Byte                                                       | 2-1  |

| 2-2              | Single-Address Instruction Machine Language Format                   | 2-1  |

| 2-3              | Single-Address Instruction Coding Example                            | 2-2  |

| 2-4              | Two-Address Instruction Machine Language Format                      | 2-2  |

| 2-5              | Two-Address Instruction Coding Example                               | 2-2  |

| 2-6              | Machine Language Representation of Instruction Length                | 2-3  |

| 2-7              | Interrupt Sequence in Fetch Cycle                                    | 2-5  |

| 2-8              | Return from Interrupt Instruction                                    | 2-6  |

| 2-9              | Move (MOV) Instruction Machine Language Format                       | 2-8  |

| 2-10             | Move (MOV) Instruction Coding Example                                | 2-8  |

| 2-11             | Store Accumulator (STA) Instruction Machine Language Format          | 2-8  |

| 2-12             | Store Accumulator (STA) Instruction Coding Example                   | 2-8  |

| 2-13             | Single-Address Load (LD) Instruction Machine Language Format         | 2-9  |

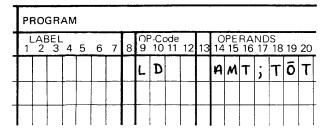

| 2-14             | Single-Address Load (LD) Instruction Coding Example                  | 2-9  |

| 2-15             | Two-Address Load (LD) Instruction Coding Example                     | 2-9  |

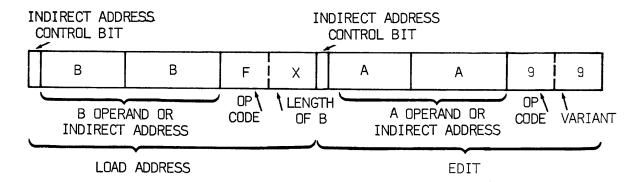

| 2-16             | Two-Address Edit (EDT) Instruction Machine Language Format           | 2-9  |

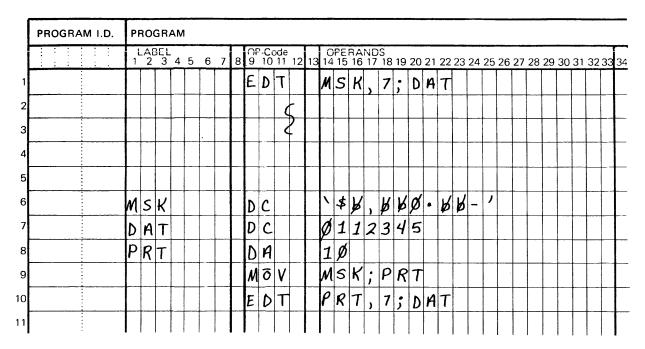

| 2-17             | Two-Address (EDT) Instruction Coding Example                         | 2-10 |

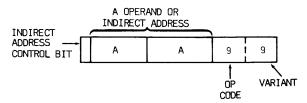

| 2-18             | Single-Address Edit (EDT) Instruction Machine Language Format        | 2-10 |

| 2-19             | Single-Address Edit (EDT) Instruction Coding Example                 | 2-10 |

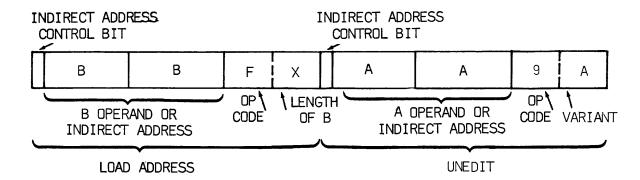

| 2-20             | Two-Address Unedit (UED) Instruction Machine Language Format         | 2-11 |

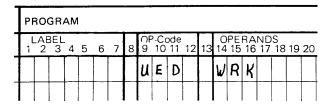

| 2-21             | Two-Address Unedit (UED) Instruction Coding Example                  | 2-11 |

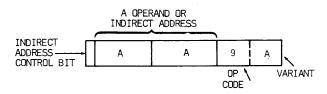

| 2-22             | Single-Address Unedit (UED) Instruction Machine Language Format      | 2-11 |

| 2-23             | Single-Address Unedit (UED) Instruction Coding Example               | 2-11 |

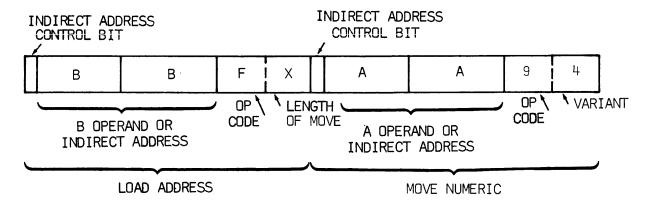

| 2-24             | Two-Address Move Numeric (MN) Instruction Machine Language Format    | 2-12 |

| 2-25             | Two-Address Move Numeric (MN) Instruction Coding Example             | 2-12 |

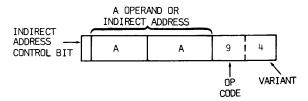

| 2-26             | Single-Address Move Numeric (MN) Instruction Machine Language Format | 2-12 |

| 2-27             | Single-Address Move Numeric (MN) Instruction Coding Example          | 2-12 |

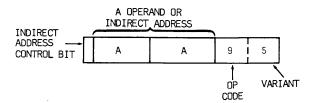

| 2-28             | Two-Address Move Zone (MZ) Instruction Machine Language Format       | 2-13 |

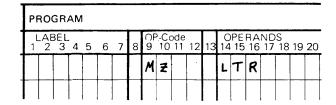

| 2-29             | Two-Address Move Zone (MZ) Instruction Coding Example                | 2-13 |

| 2-30             | Single-Address Move Zone (MZ) Instruction Machine Language Format    | 2-13 |

| 2-31             | Single-Address Move Zone (MZ) Instruction Coding Example             | 2-13 |

| 2-31             |                                                                      | 2-13 |

| 2-32             | Shift Bit Left Operation                                             | 2-14 |

| 2-33             | Shift Bit Left (SBL) Instruction Coding Example                      | 2-14 |

| 2-34             | Shift Bit Right Operation                                            | 2-14 |

| 2-35             | Shift Bit Right (SBR) Instruction Machine Language Format            |      |

| 2-30             |                                                                      | 2-14 |

| 2-37             | Shift Bit Right (SBR) Instruction Coding Example                     | 2-14 |

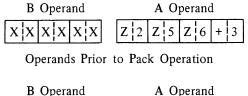

|                  | Pack Operation                                                       | 2-14 |

| 2-39             | Two-Address Pack (PAK) Instruction Machine Language Format           | 2-14 |

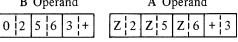

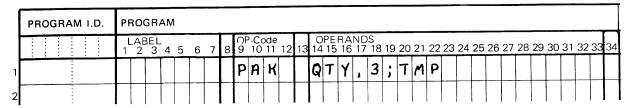

| 2-40             | Two-Address Pack (PAK) Instruction Coding Example                    | 2-15 |

| 2-41             | Single-Address Pack (PAK) Instruction Machine Language Format        | 2-15 |

| 2-42             | Single-Address Pack (PAK) Instruction Coding Example                 | 2-15 |

| 2-43<br>2-44     | Unpack Operation                                                     | 2-15 |

| 1-44             | IWO-Address Linnack ILIPK Linstruction Machine Language Format       | 2-16 |

| NUMBER                   |                                                                           | PAGE |

|--------------------------|---------------------------------------------------------------------------|------|

|                          | Two-Address Unpack (UPK) Instruction Coding Example                       | 2-16 |

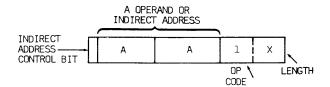

| 2-45<br>2-46             | Single-Address Unpack (UPK) Instruction Machine Language Format           | 2-16 |

| 2 <del>-40</del><br>2-47 | Single-Address Unpack (UPK) Instruction Coding Example                    | 2-16 |

|                          |                                                                           | 2-10 |

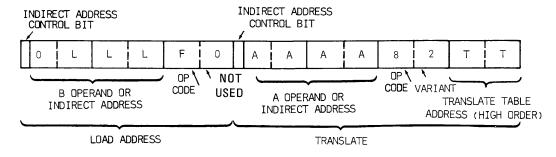

| 2-48                     | Translate (TRN) Instruction Machine Language Format                       | 2-17 |

| 2-49                     | Translate (TRN) Instruction Coding Example                                | 2-17 |

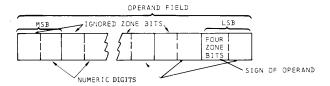

| 2-50                     | Decimal Arithmetic Operand Field                                          | 2-17 |

| 2-51                     | Single-Address Add Decimal (ADD) Machine Language Format                  | 2-17 |

| 2-52                     | Single-Address Add Decimal (ADD) Instruction Coding Example               | 2-17 |

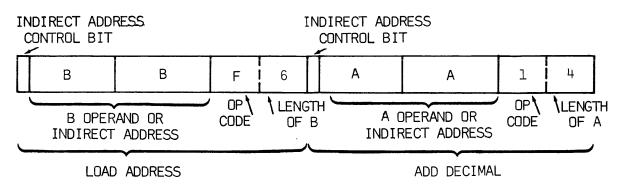

| 2-53                     | Two-Address Add Decimal (ADD) Instruction Machine Language Format         | 2-18 |

| 2-54                     | Two-Address Add Decimal (ADD) Instruction Coding Example                  | 2-18 |

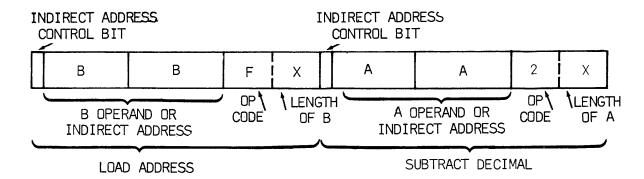

| 2-55                     | Two-Address Subtract Decimal (SBD) Instruction Machine Language Format    |      |

| 2-56                     | Two-Address Subtract Decimal (SBD) Instruction Coding Example             | 2-19 |

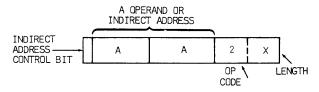

| 2-57                     | Single-Address Subtract Decimal (SBD) Instruction Machine Language Format | 2-19 |

| 2-58                     | Single-Address Subtract Decimal (SBD) Instruction Coding Example          | 2-19 |

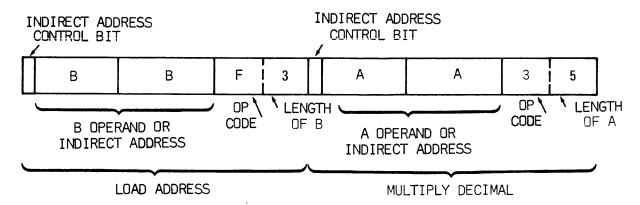

| 2-59                     | Two-Address Multiply Decimal (MPY) Instruction Machine Language Format    | 2-20 |

| 2-60                     | Two-Address Multiply Decimal (MPY) Instruction Coding Example             | 2-20 |

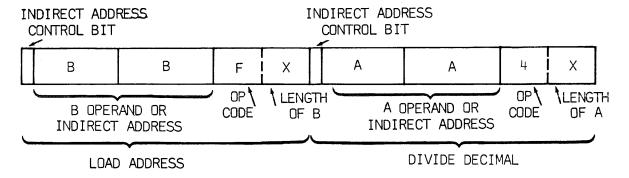

| 2-61                     | Two-Address Divide Decimal (DIV) Instruction Machine Language Format      | 2-20 |

| 2-62                     | Two-Address Divide Decimal (DIV) Instruction Coding Example               | 2-20 |

| 2-63                     | Single-Address Divide Decimal (DIV) Instruction Machine Language Format   | 2-21 |

| 2-64                     | Single-Address Divide Decimal (DIV) Instruction Coding Example            | 2-21 |

| 2-65                     | Two-Address Add Binary (ADB) Instruction Machine Language Format          | 2-21 |

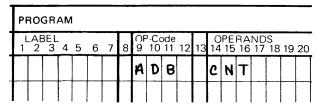

| 2-66                     | Two-Address Add Binary (ADB) Instruction Coding Example                   | 2-21 |

| 2-67                     | Single-Address Add Binary (ADB) Instruction Machine Language Format       | 2-22 |

| 2-68                     | Single-Address Add Binary (ADB) Instruction Coding Example                | 2-22 |

| 2-69                     | Two-Address Subtract Binary (SBB) Instruction Machine Language Format     | 2-22 |

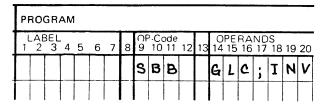

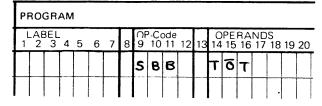

| 2-70                     | Two-Address Subtract Binary (SBB) Instruction Coding Example              | 2-22 |

| 2-71                     | Single-Address Subtract Binary (SBB) Instruction Machine Language Format  | 2-22 |

| 2-72                     | Single-Address Subtract Binary (SBB) Instruction Coding Example           | 2-22 |

| 2-73                     | Two-Address AND Instruction Machine Language Format                       | 2-23 |

| 2-74                     | Two-Address AND Instruction Coding Example                                | 2-23 |

| 2-75                     | Single-Address AND Instruction Machine Language Format                    | 2-23 |

| 2-76                     | Single-Address AND Instruction Coding Example                             | 2-23 |

| 2-77                     | Two-Address OR Instruction Machine Language Format                        | 2-24 |

| 2-78                     | Two-Address OR Instruction Coding Example                                 | 2-24 |

| 2-79                     | Single-Address OR Instruction Machine Language Format                     | 2-24 |

| 2-80                     | Single-Address OR Instruction Coding Example                              | 2-24 |

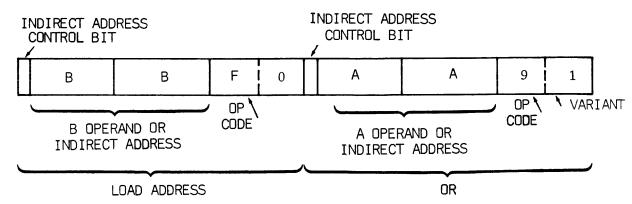

| 2-81                     | Two-Address Exclusive OR (XOR) Instruction Machine Language Format        | 2-25 |

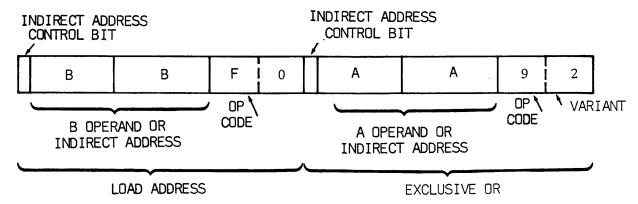

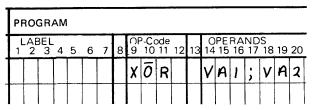

| 2-82                     | Two-Address Exclusive OR (XOR) Instruction Coding Example                 | 2-25 |

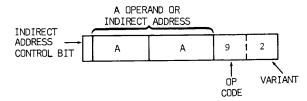

| 2-83                     | Single-Address Exclusive OR (XOR) Instruction Machine Language Format     | 2-25 |

| 2-84                     | Single-Address Exclusive OR (XOR) Instruction Coding Example              | 2-25 |

| 2-85                     | Branch On Overflow (BOV) Instruction Machine Language Format              | 2-25 |

| 2-86                     | Branch On Overflow (BOV) Instruction Coding Example                       | 2-25 |

| 2-87                     | Branch On Minus (BMI) Instruction Machine Language Format                 | 2-26 |

| 2-88                     | Branch On Minus (BMI) Instruction Coding Example                          | 2-26 |

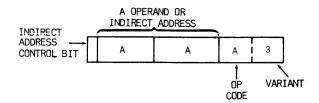

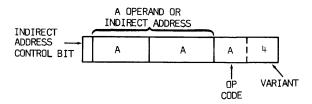

| 2-89                     | Branch On Non-Zero (BNZ) Instruction Machine Language Format              | 2-26 |

| 2-90                     | Branch On Non-Zero (BNZ) Instruction Coding Example                       | 2-26 |

| 2-91                     | Branch Equal (BEQ) Instruction Machine Language Format                    | 2-26 |

| 2-92                     | Branch Equal (BEQ) Instruction Coding Example                             | 2-26 |

| 2-93                     | Branch Not Minus (BNM) Instruction Machine Language Format                | 2-27 |

| 2-94                     | Branch Not Minus (BNM) Instruction Coding Example                         | 2-27 |

| <b>~</b> ∕ ¹             | Timing ( Transport County Promises 1 , 1 , 1 , 1 , 1 , 1 , 1 , 1          | '    |

| FIGURE<br>NUMBER       |                                                                          | PAGE       |

|------------------------|--------------------------------------------------------------------------|------------|

| 2-95                   | Unconditional Branch (BRU) Instruction Machine Language Format           | 2-27       |

| 2-96                   | Unconditional Branch (BRU) Instruction Coding Example                    | 2-27       |

| 2-97                   | Halt and Branch (HLT) Instruction Machine Language Format                | 2-28       |

| 2-98                   | Halt and Branch (HLT) Instruction Coding Example                         | 2-28       |

| 2-99                   | Branch and Link (BLI) Instruction Machine Language Format                | 2-28       |

| 2-100                  | Branch and Link (BLI) Instruction Coding Example                         | 2-28       |

| 2-101                  | Two-Address Test Bit (TBT) Instruction Machine Language Format           | 2-29       |

| 2-102                  | Two-Address Test Bit (TBT) Instruction Coding Example                    | 2-29       |

| 2-103                  | Single-Address Test Bit (TBT) Instruction Machine Language Format        | 2-29       |

| 2-104                  | Single-Address Test Bit (TBT) Instruction Coding Example                 | 2-29       |

| 2-105                  | Two-Address Compare Decimal (CD) Instruction Machine Language Format     | 2-29       |

| 2-106                  | Two-Address Compare Decimal (CD) Instruction Coding Example              | 2-30       |

| 2-107                  | Single-Address Compare Decimal (CD) Instruction Machine Language Format  | 2-30       |

| 2-108                  | Single-Address Compare Decimal (CD) Instruction Coding Example           | 2-30       |

| 2-109                  | Two-Address Compare Logical (CMP) Instruction Machine Language Format    | 2-30       |

| 2-110                  | Two-Address Compare Logical (CMP) Instruction Coding Example             | 2-30       |

| 2-111                  | Single-Address Compare Logical (CMP) Instruction Machine Language Format | 2-30       |

| 2-112                  | Single-Address Compare Logical (CMP) Instruction Coding Example          | 2-30       |

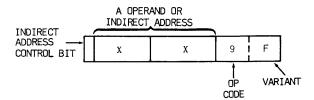

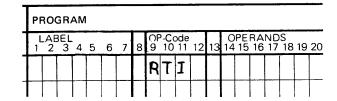

| 2-112                  | Return From Interrupt (RTI) Instruction Machine Language Format          | 2-30       |

| 2-113                  | Return From Interrupt (RTI) Instruction Coding Example                   | 2-31       |

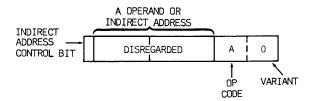

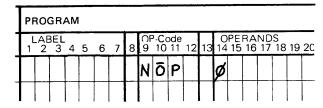

| 2-115                  | No Operation (NOP) Instruction Machine Language Format                   | 2-31       |

| 2-116                  | No Operation (NOP) Instruction Coding Example                            | 2-31       |

| 2-117                  | Load Address (LDA) Instruction Machine Language Format                   | 2-31       |

| 2-118                  | Micro-Instruction Mode (MIM) Instruction Machine Language Format         | 2-32       |

| 2-119                  | Search Equal (SEQ) Instruction Machine Language Format                   | 2-32       |

| 2-119                  | Search Equal (SEQ) Instruction Coding Example                            | 2-32       |

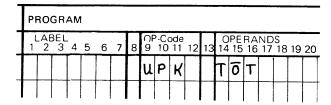

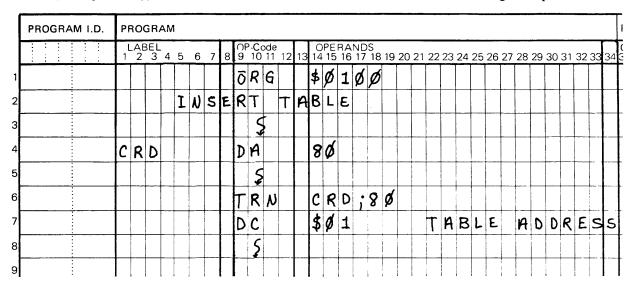

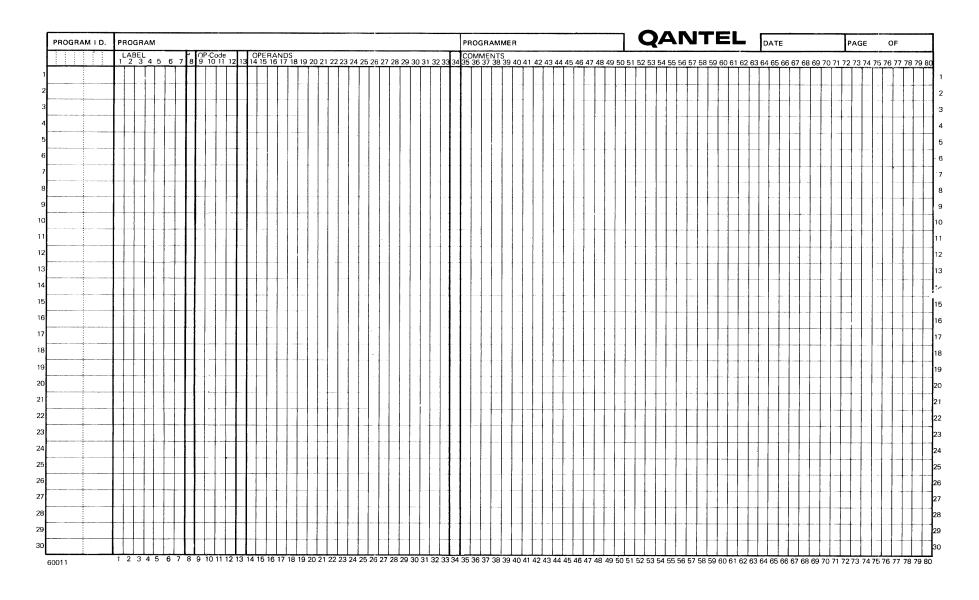

| 3-1                    | QANTEL Business Assembler Language Coding Form                           | 3-2        |

| 3-2                    | Correct Labels Coding Example                                            | 3-2        |

| 3-3                    | Incorrect Labels Coding Example                                          | 3-3        |

| 3-4                    | "Length Of" Operator (.) Coding Example                                  | 3-3        |

| 3-5                    | Correct Coding of Decimal Values                                         | 3-3        |

| 3-6                    | Correct Coding of Hexadecimal Values                                     | 3-4        |

| 3-7                    | Current Location Operand (*) Coding Example                              | 3-4<br>3-4 |

| 3-8                    | Expressions Coding Examples                                              | 3-5        |

| 3 <b>-</b> 9           | A/B Operand Field Format Requirements                                    | 3-3<br>3-7 |

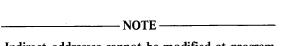

| 3-10                   | Indirect Addressing Coding Example                                       | 3-7<br>3-7 |

| 4-1                    | Origin Control (ORG) Instruction Coding                                  | 4-1        |

| 4-2                    | End Control (END) Instruction Coding                                     | 4-1<br>4-1 |

| 4-3                    | Alphameric, Decimal and Hexadecimal Define Constant (DC) Coding          | 4-1        |

| 4-3<br>4-4             | Define Address Constant (DAC) Coding                                     | 4-2<br>4-2 |

| 4-5                    | Define Area (DA) Coding                                                  | 4-2<br>4-3 |

| 4-6                    | Equate Instruction Coding                                                | 4-3<br>4-3 |

| <del>4-</del> 0<br>4-7 |                                                                          | 4-3<br>4-4 |

| 4-7<br>4-8             | Implementation of the Execute (EXE) Instruction                          |            |

| 4-8<br>5-1             | Typewriter Control Instructions                                          | 4-4<br>5-2 |

| 5-1<br>5-2             |                                                                          | 5-2<br>5-4 |

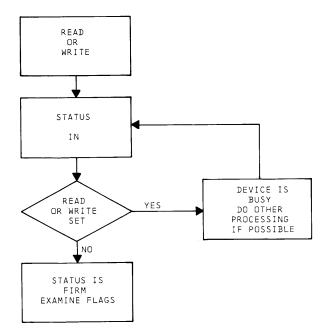

| 5-2<br>5-3             | Reading A Buffered Device                                                | 5-4<br>5-5 |

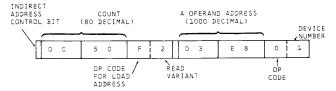

| 5-3<br>5-4             | Read Instruction (RD) Machine Language Format Example                    | 5-5<br>5-5 |

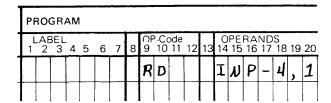

| 5-5                    | Read Instruction (RD) Machine Language Format Example                    | 5-5<br>5-5 |

| 5-5<br>5-6             | Read and Count Instruction (RDC) Machine Language Format                 | 3-3<br>5-5 |

|                        |                                                                          |            |

| FIGURE<br>NUMBER |                                                                  | PAGE         |

|------------------|------------------------------------------------------------------|--------------|

| 5-7              | Read and Count Instruction (RDC) Coding Example                  | 5-6          |

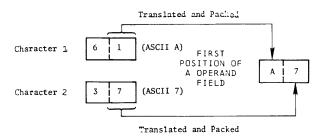

| 5-8              | Read Hex Instruction Two-Byte Combination Method                 | 5-6          |

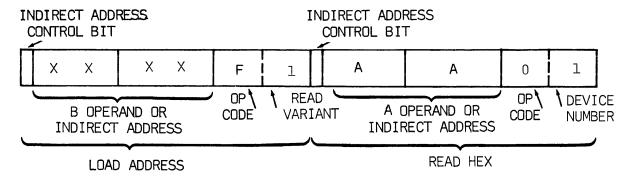

| 5-9              | Read Hex Instruction (RHX) Machine Language Format               | 5-6          |

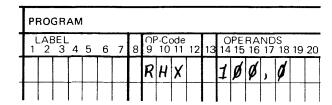

| 5-10             | Read Hex Instruction (RHX) Coding Example                        | 5 <b>-</b> 6 |

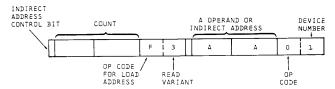

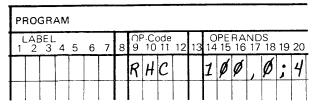

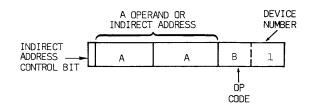

| 5-11             | Read Hex and Count Instruction (RHC) Machine Language Format     | 5-7          |

| 5-12             | Read Hex and Count Instruction (RHC) Coding Example              | 5-7          |

| 5-13             | Write Instruction (WR) Maching Language Format                   | 5-7          |

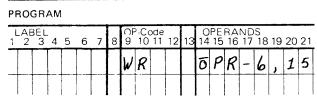

| 5-14             | Write Instruction (WR) Coding Example                            | 5-7          |

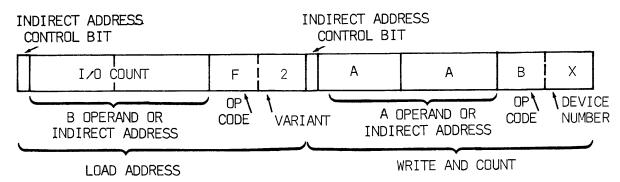

| 5-15             | Write and Count Instruction (WRC) Machine Language Format        | 5-7          |

| 5-16             | Write and Count Instruction (WRC) Coding Example                 | 5-8          |

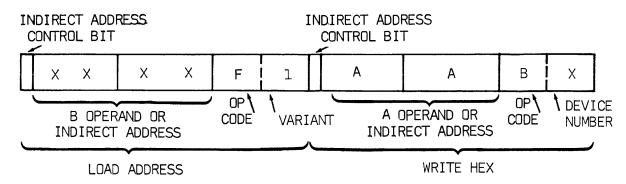

| 5-17             | Write Hex Instruction (WHX) Machine Language Format              | 5-8          |

| 5-18             | Write Hex Instruction (WHX) Coding Example                       | 5-8          |

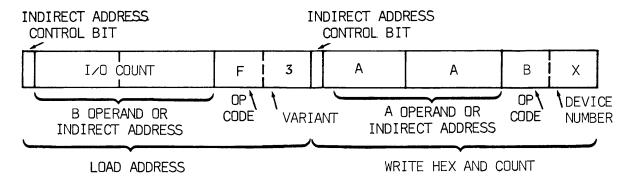

| 5-19             | Write Hex and Count Instruction (WHC) Machine Language Format    | 5-9          |

| 5-20             | Write Hex and Count Instruction (WHC) Coding Example             | 5-9          |

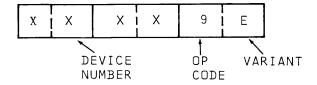

| 5-21             | Reset I/O Instruction (RIO) Machine Language Format              | 5-9          |

| 5-22             | Reset I/O Instruction (RIO) Coding Example                       | 5-9          |

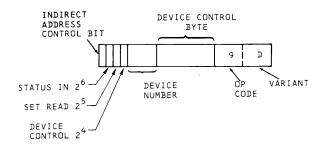

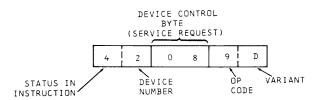

| 5-23             | Status-In (SIN), Set Read (SRD) and Device Control (CTL)         | - /          |

|                  | Instructions Machine Language Format                             | 5-9          |

| 5-24             | Status-In Instruction (SIN) Machine Language Format Example      | 5-10         |

| 5-25             | Status-In Instruction (SIN) Coding Example                       | 5-10         |

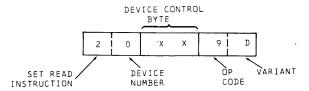

| 5-26             | Set Read Instruction (SRD) Machine Language Format Example       | 5-10         |

| 5-27             | Set Read Instruction (SRD) Coding Example                        | 5-10         |

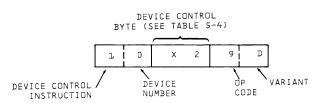

| 5-28             | Device Control Instruction (CTL) Machine Language Format Example | 5-11         |

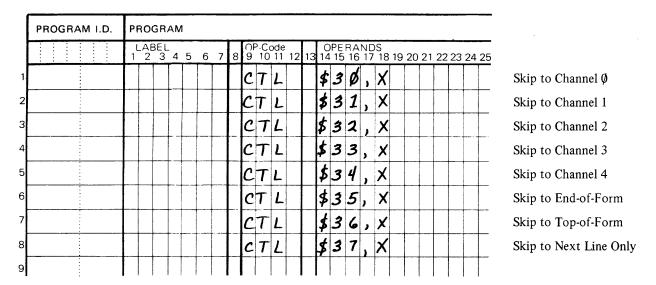

| 5-29             | Device Control Instruction (CTL) Coding Example                  | 5-11         |

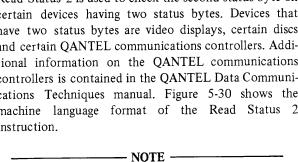

| 5-30             | Read Status 2 Instruction (RS2) Machine Language Format          | 5-11         |

| 5-31             | Typewriter Status-In Instruction Coding                          | 5-13         |

| 5-32             | Checking Multiple Status Conditions                              | 5-13         |

| 5-33             | Typewriter Device Control Instruction Coding                     | 5-14         |

| 5-34             | Typewriter Reset I/O Instruction Coding                          | 5-14         |

| 5-35             | Typewriter Set Read Instruction Coding                           | 5-14         |

| 5-36             | Magnetic Tape Transport Device Control Instruction Coding        | 5-15         |

| 5-37             | Disc Seek Instruction (SEK) Machine Language Format              | 5-16         |

| 5-38             | Disc Address Field Organization                                  | 5-16         |

| 5-39             | 7.6M Byte Disc Status-In Instruction Coding                      | 5-16         |

| 5-40             | 30.7M Byte and 60M Byte Disc Status-In Instruction Coding        | 5-17         |

| 5-41             | Disc Drive Control Instructions Coding                           | 5-17         |

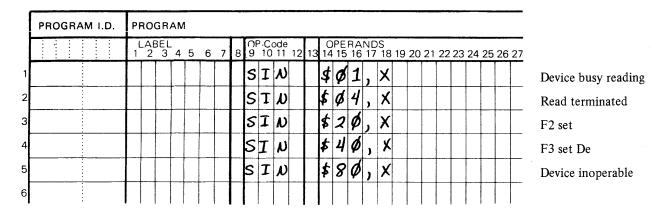

| 5-42             | Card Reader Status-In Instruction Coding                         | 5-18         |

| 5-43             | Paper Tape Reader/Punch Status-In Instruction Coding             | 5-18         |

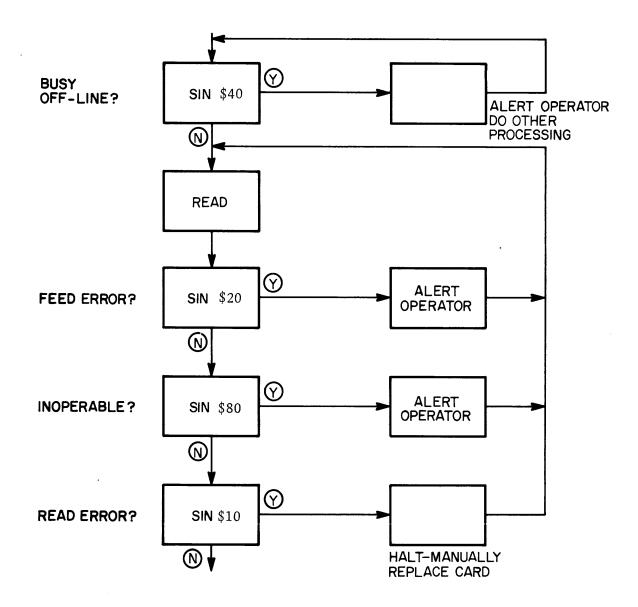

| 5-44             | Card Reader Status Checking Flowchart                            | 5-19         |

| 5-45             | Ten-Key Keyboard Device Control Instruction Coding               | 5-19         |

| 5-46             | Ten-Key Keyboard Status-In Instruction Coding                    | 5-20         |

| 5 <b>-</b> 47    | 60-100 LPM Serial Printer Device Control Instruction Coding      | 5-20         |

| 5-48             | Line Printer Device Control Instruction Coding                   | 5-21         |

| 5-49             | 60-100 LPM Serial Printer Status-In Instruction Coding           | 5-21         |

| 5-50             | Line Printer Status-In Instruction Coding                        | 5-21         |

| 5-51             | System Clock Time-of-Day Setting                                 | 5-21         |

| 5-52             | Interval Timer Read Coding                                       | 5-22<br>5-22 |

| 5-53             | System Clock/Interval Timer Status-In Instruction Coding         | 5-22         |

# LIST OF TABLES

| TABLE<br>NUMBER |                                                  | PAGE |

|-----------------|--------------------------------------------------|------|

| 1-1             | Table of Terms                                   | 1-2  |

| 1-2             | Hexadecimal Numbering System                     | 1-3  |

| 1-3             | System Specifications                            | 1-4  |

| 2-1             | Instruction Length Indicators                    | 2-3  |

| 2-2             | Reserved High-Speed (Main) Memory Allocations    | 2-4  |

| 2-3             | Rules for AND Operation                          | 2-23 |

| 2-4             | Rules for OR Operation                           | 2-24 |

| 2-5             | Rules for Exclusive OR (XOR) Operation           | 2-24 |

| 5-1             | I/O Control Byte Flag Bits                       | 5-3  |

| 5-2             | I/O Control Byte Status Bits                     | 5-4  |

| 5-3             | I/O Control Instruction Bits                     | 5-10 |

| 5-4             | Device Control Byte and Typewriter Signal Lamps  | 5-11 |

| 5-5             | Device and Allowable Read and Write Instructions | 5-14 |

QANTEL ANSWER PROCESSOR SYSTEM

# **SECTION I**

# GENERAL DESCRIPTION

#### 1-1. INTRODUCTION

- 1-2. The QANTEL Business Assembly Language (Q/BAL) is provided by QANTEL Corporation to permit assembly language programming of the QANTEL/ANSWER Processor System. Assembly language programming allows the programmer to write programs using mnemonics instead of machine language instructions and operation codes. The assembler mnemonics are indicative of the particular instructions and the assembler programs contain many aids to greatly simplify programming for the QANTEL/ANSWER Processor System.

- 1-3. The purpose of this reference manual is to provide the experienced programmer with the information necessary to use the QANTEL Business Assembly Language and to familiarize the programmer with the operation of the QANTEL/ANSWER Processor System standard instructions. The manual is divided into six sections and supporting Appendixes. These sections contain the following information:

- a. Section I, General Description describes the reference manual, lists related publications, provides definitions of terms, describes features and specifications of the QANTEL hardware, and describes the functional operation, library capabilities and object program formats of the QANTEL Business Assembly Language.

- b. Section II, Processor Functions describes machine language processor functions and programming requirements for the QAN-TEL/ANSWER Processor System.

- c. Section III, Assembler Instruction Coding describes the coding formats and the rules for coding QANTEL Business Assembly Language statements.

- d. Section IV, Assembler Directives describes the instructions used to control the assembler and to produce constants and data areas.

- e. Section V, Input/Output Instructions and Devices — describes the various input/output instructions and programming requirements for the various input/output devices.

- f. Section VI, Assembler Operation provides the operating procedures for the Q/BAL Assembler programs.

- g. Supporting Appendixes.

#### 1-4. RELATED REFERENCE PUBLICATIONS

- 1-5. The QANTEL Business Assembly Language Reference Manual is complemented by the following additional QANTEL publications:

- a. QANTEL Business Assembly Language Programmers Training Manual especially useful for teaching new programmers.

- b. QANTEL Micro-Assembler Manual required only for those customers intending to alter the instruction set.

- c. Product Specifications for the QANTEL/

ANSWER Processor System and I/O Devices

for original equipment manufacturers.

TABLE 1-1. TABLE OF TERMS

| TERM                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit                     | Single binary digit having the value of zero or one.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Byte                    | An 8 storage location in memory which may assume any of 256 possible bit configurations (from hex 00 to FF).                                                                                                                                                                                                                                                                                                                                              |  |  |

| Operand                 | Data represented in a byte, or combination of bytes, that is used in some operation.                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Operand<br>Address      | Operands in the QANTEL/ANSWER Processor System are addressed by referring to the least significant byte (highest memory location), except in the case of input/output instructions.                                                                                                                                                                                                                                                                       |  |  |

| Buffer                  | Refers to a hardware device or main memory positions used for the temporary storage of data. In both cases, the buffer size is described by its length in bytes.                                                                                                                                                                                                                                                                                          |  |  |

| Assembler               | Software package that allows programmers to use symbolic language references for instructions and addresses, thereby simplifying the programming task.                                                                                                                                                                                                                                                                                                    |  |  |

| Standard<br>Instruction | A micro-program stored in the Read-Only Memory that represents a function found on all QANTEL/ANSWER Systems, e.g., Add Decimal, Edit, Branch and Link, Read, etc.                                                                                                                                                                                                                                                                                        |  |  |

| Micro-<br>Instruction   | Single byte instructions contained in the Read-Only Memory (or main memory) that are decoded to preform specific operations.                                                                                                                                                                                                                                                                                                                              |  |  |

| ROM                     | Read-Only Memory. A hard-wired control memory that delivers a series of micro-instructions specified (addressed) by the decoded standard instruction. The ROM is installed in the QANTEL/ANSWER Processor System at the factory and cannot be altered.                                                                                                                                                                                                    |  |  |

| Fetch/Execute<br>Cycles | Preformance of an instruction is completed by the fetch and Execute cycles. In the fetch cycle, the instruction is read from main memory, and is examined byte-by-byte so that its format can be determined. Once all addresses and operation codes have been examined, the execution cycle performs the actual operation indicated by the instruction.                                                                                                   |  |  |

| A and B<br>Operands     | Generally, the A operand is the source operand, and the B operand is the resultant or second operand. In an Add Decimal Instruction, for example the A operand is added to the B operand, and the result is placed in the B operand.                                                                                                                                                                                                                      |  |  |

| IPL                     | Initial Program Load.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| ASCII                   | American Standard Code for Information Interchange.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Length                  | The number of consecutive bytes to be operated on by an instruction. Length is variant in several standard QANTEL Instructions, and is counted down as the instruction is executed byte-by-byte. When count zero is reached, the length of the operand field is said to be exhausted. The maximum length of most variable length instructions (except Move), is sixteen bytes, and is represented by zero in the instruction. Minimum length is one byte. |  |  |

#### 1-6. DEFINITION OF TERMS

1-7. Some of the terms used throughout this reference manual may have different meanings to the readers as a result of their previous experience. Table 1-1 defines some of these terms to make the interpretation of the information as easy as possible for a reader desiring to acquaint himself with the detailed operation of the QANTEL/ANSWER Processor System.

Successful operation of the QANTEL/ANSWER Processor System and pre-programmed environment (standard applications software packages)

does not require a detailed knowledge of the processor operation.

- NOTE -

#### 1-8. SYSTEM DESCRIPTION

- 1-9. The QANTEL/ANSWER Processor system is designed for small-scale data applications as self-contained units or as intelligent terminals (satellite). The heart of QANTEL Processor System is a serial processor which eliminates the need for complex software, thereby reducing the effort required to implement operational work. Simultaneous input/output and computing is provided through hardware buffering during operation with many of the standard QANTEL peripherals.

- 1-10. With the QANTEL/ANSWER Processor system, the user has the option to utilize pre-programmed applications, to program at the processor standard instruction levels or, for the experienced staff, to program at the micro-instruction level. Processor organization, together with an extremely basic Read-Only Memory word design, provides the unusual versatility of the QANTEL/ANSWER Processor Systems. The standard internal code of the processor is in ASCII format. However, any desired data format may be used, permitting QANTEL/ANSWER Processor System to operate satellite to any major computer.

- 1-11. The components of the basic system are normally mounted in a standard L-shaped secretarial desk with I/O typewriter recessed in the desk extension side. The power supply/processor control panel is mounted underneath the extension.

#### 1-12. High-Speed Memory

1-13. Program and data storage within the processor are provided by an eight-bit, variable address, IC main memory that has a complete cycle time of 1.5 microseconds. Cycle time is the time required to transfer one byte of information from memory to the memory register and regenerate the byte back into storage. The main memory is made up of modules, each having 4096 separately addressable eight-bit locations. At the time of this printing memory combinations of one, two, four, six, or eight modules are available.

#### 1-14. Control Memory

1-15. Processor internal control is a function of micro-instructions generated in the Read-Only Memory (ROM). The standard ROM now contains 1536 control words that are used to configure the algorithms of micro-instructions that make up the standard instruction set and disc control instruction logic. Machines that were

installed prior to the release of the ANSWER Processor Systems, and that did not include a disc drive, and the additional 512 word disc ROM that was installed with these machines, contained a ROM of 1024 control words. Therefore, these machines will not contain the newest standard instructions. These new standard instructions are noted on the list of QANTEL Standard Instructions shown in Appendix D. On the ANSWER Processor System an additional 512 control words are available, as an option, to supply any other instructions desired by the user. Also, all or part of the microinstruction complement furnished by the ROM may be optionally specified by the user to meet special demands.

#### 1-16. Hexadecimal System

- 1-17. Machine language addresses and characters used in the processor are in binary form. Because binary combinations are often difficult to work with and describe, QANTEL publications use the hexadecimal numbering system to represent characters and addresses.

- 1-18. The Hexadecimal system is a method commonly used to describe the 16 different configurations of four binary bits. Table 1-2 shows how the first ten configurations (in binary sequence) are represented by the decimal numbers zero through nine (0-9). The last six configurations are represented by the alphabetic letters A through F.

TABLE 1-2. HEXADECIMAL NUMBERING SYSTEM

| HEXADECIMAL<br>(BASE 16) | BINARY<br>(BASE 2) | DECIMAL<br>(BASE 10) |

|--------------------------|--------------------|----------------------|

| 0                        | 0000               | 0                    |

| 1                        | 0001               | 1                    |

| 2                        | 0010               | 2                    |

| 3                        | 0011               | 3                    |

| 4                        | 0100               | 4                    |

| 5                        | 0101               | 5                    |

| 6                        | 0110               | 6                    |

| 7                        | 0111               | 7                    |

| 8                        | 1000               | 8                    |

| 9                        | 1001               | 9                    |

| A                        | 1010               | 10                   |

| В                        | 1011               | 11                   |

| C                        | 1100               | 12                   |

| D                        | 1101               | 13                   |

| E                        | 1110               | 14                   |

| F                        | 1111               | 15                   |

#### - NOTE

A complete hexadecimal-to-decimal conversion table is presented in Appendix A at the rear of this manual.

#### 1-19. ASCII

1-20. ASCII is used within the QANTEL/ANSWER Processor Systems. A complete ASCII table is included in Appendix B as an aid to system planning exercises.

#### 1-21. System Specifications

1-22. Pertinent specifications for the QANTEL/ANSWER Processor System are listed in table 1-3. More detailed specifications are contained in the respective

QANTEL Product Specifications available for original equipment manufacturers.

#### 1-23. ASSEMBLER DESCRIPTION

- 1-24. The Q/BAL Assembler programs described in the following paragraphs perform several general functions. These functions include:

- a. Line Entry accepts each line of the coded assembler language program by means of keyboard entry from the typewriter or 80-column punched cards and checks each statement for correct syntax.

- b. Generation of Program Source File generates an intermediate source program that can be modified using typewriter or card input.

#### TABLE 1-3. SYSTEM SPECIFICATIONS

#### **PROCESSOR**

Main Memory

IC memory, 4096 eight-bit locations, expandable to 8192, 16384, and

32768, 1.5 microsecond cycle time.

**Processor Control**

Read-Only Memory with 50 nano-second cycle time.

Physical Dimensions

26" x 17" x 17½"

(max. configuration)

#### INPUT/OUTPUT (Basic System)

**Typewriter**

IBM 735 Heavy Duty Selectric 14.7 characters per second Fully buffered

(128 characters)

#### NOTE

The basic QANTEL/ANSWER Processor System may be expanded using additional I/O typewriters, magnetic tape units, disc drives, card readers, printers, communications capabilities, CRT's, optical mark readers, ten-key keyboards, and a programmers control console. For specifications on these varied I/O devices refer to the QANTEL Product Information sheets and engineering specifications.

#### POWER SUPPLY

Input Voltages

105-125 vac, 210-250 vac at 48 to 61 HZ

Primary Power

Failure Protection

Primary power interruptions of up to eight milliseconds cause no ill

effect on system operation

Short Circuit Protection

Fuse protection provided

Physical Dimensions

17" x 17" x 7"

ENVIRONMENTAL

CONDITIONS

0 to +40°C (32°F to 104°F), up to 85% relative humidity without

condensation

- c. Production of Object Program and/or Listing

assembles the program source file and

produces a loadable object program and/or a

printed listing of the assembled program

showing the instructions in both assembler

and machine language. A loadable object

program, once loaded, forms an executable

set of machine instructions and associated

data that is capable of performing useful

data processing tasks.

- 1-25. The following paragraphs describe the two passes of the Q/BAL assembler, program update operation, source program library files, and the object program library files.

#### 1-26. Pass One

- 1-27. The QANTEL Business Assembly Language uses two separate programs, run in sequence, to perform the assembly operation. The first assembler program generates the source program and is referred to as Pass One. Operation of the Pass One program performs the following functions:

- a. Accepts the Assembly language input from the typewriter or card reader and/or previously created source file (disc or magnetic tape) and checks for errors in format, operation codes, statement syntax and label assignments.

- b. Creates a table of the labels or tags used as the program statements are entered and assigns values to these labels.

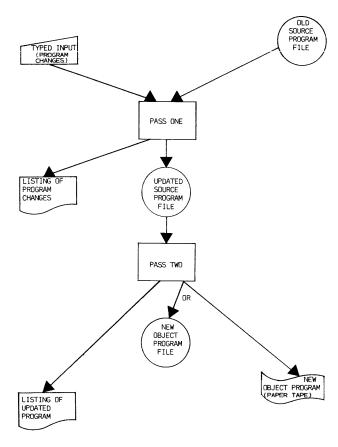

- c. Places the entered program and tag table on the new source file to create the source programs for processing by Pass Two. Refer to figures 1-1 and 1-2.

#### 1-28. PASS ONE ERROR DETECTION

- 1-29. There are many possible errors that may occur in the syntax of an input statement. Each of these error is detectable during Pass One operation. When an error is detected during Pass One operation, an appropriate diagnostic message will be generated. The exact mode of presentation for this diagnostic message is dependent on the device used for input of the new or modified source statements.

- 1-30. When the typewriter is used for input, it is assumed that the programmer (as opposed to an opera-

Figure 1-1. Assembler Create Operation

tor without knowledge of the program) is entering the lines of source code. When an error is detected, an appropriate diagnostic message will be printed out, and the program will request that the user re-enter the line in question. This mode of operation is especially useful for small modifications of existing source programs that are resident on magnetic tape or disc. Also, this feature is useful for initial use by a programmer who is not experienced in the use of the QANTEL Business Assembly Language.

1-31. Using the card reader as an input device to the assembler is especially appropriate when a number of programmers are developing programs using the QANTEL Business Assembly Language, and an operator is available to supervise the assembly of these programs. When using the card reader, the operator cannot correct an erroneous input line at the time the error occurs, therefore, the Pass One program will mark the line in error on the source file, produce an appropriate diagnostic message on the file, and proceed to the next input line. When the resultant source file is processed by Pass Two of the assembler, these diagnostic messages will be printed following the lines in error. This will allow the programmer to code the appropriate corrections to his

Figure 1-2. Assembler Update Operation

program and resubmit the corrections to the operator for updates. When the lines in error have been replaced or deleted by the subsequent updates of the source tape, the error messages will be ignored and not passed on when an updated source file is created.

#### 1-32. Pass Two

1-33. As shown in figure 1-1, the Pass Two program is run subsequent to the Pass One operation to accept the source program file and produce an object program file. During this operation, the assembly language instructions are translated into machine language instructions. The result of the Pass Two operation is an absolute or machine language object program and a printed listing of the program. This listing shows the instructions in both the assembler and machine languages. The production of either the object program or the printed listing may be suppressed at the option of the operator or programmer. The listing of the source and machine language instructions will provide an aid to the programmer for debugging and future modification of the assembled program.

#### 1-34. Update Operation

1-35. A previously assembled program may be updated by modifying the old source program, eliminating any need to re-enter the entire program. As shown in figure 1-2, the old source program can be modified by Pass One of the assembler using corrections or changes entered by way of the typewriter or card reader. The result of this update operation is a new, or updated, source program that may be assembled by the Pass Two operation of the Q/BAL Assembler programs. The final result of the update operation is a new source program, a new object program, and a new listing.

#### 1-36. Source Program Library Files

1-37. As described in the previous paragraphs, the Pass One operation of the Q/BAL Assembler produces a source program. This source program can reside on either magnetic tape or disc. Some of the advantages of magnetic tape and disc source program files are described in the following paragraphs.

# 1-38. MAGNETIC TAPE SOURCE PROGRAM FILES

1-39. Magnetic tape source files can be arranged by the assembler and/or the library maintenance programs so that several programs can be contained on one reel of tape. Further details on this are presented in the Assembler Operating Instructions, Section VI. The Pass One operation permits the operator to request the desired source program file from the tape when necessary for updating purposes. Advantages of maintaining multiple source program files on one magnetic tape include a more efficient use of magnetic tape, and an ease of producing a single object file containing all programs of the library. This is especially advantageous when all programs are part of the same system. The primary disadvantage of using magnetic tape for multiple source program storage is the extended processing time required to copy programs not being updated when those programs contain many lines of code.

#### 1-40. DISC SOURCE PROGRAM FILES

1-41. The use of disc for source program files allows assembly of programs on systems configured with one disc drive and one magnetic tape unit. In addition to all of the advantages of magnetic tape source files, the use of disc source files also offers the user the advantage of greater speed and flexibility that is not available when using magnetic tape source files.

#### 1-42. Object Program Library Files

- 1-43. Like source programs, object programs can be maintained on either magnetic tape or disc. However, the assembler will create object files on magnetic tape only. The differences in the speed and convenience of disc over magnetic tape object files is great. This is especially so when it becomes necessary to mount and dismount tape reels. The object program library files can be created or updated by either of the two following methods:

- a. Adding, replacing, or deleting individual object programs on the library file by means of the appropriate magnetic tape or disc library maintenance program.

- b. Performing the Pass Two operation on the entire source program library file (magnetic tape output only).

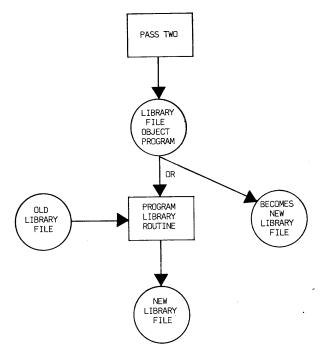

- 1-44. Any object program produced by the QANTEL Business Assembly Language program can be placed on an existing library file using the appropriate QANTEL library maintenance program. Figure 1-3 illustrates how the object programs are fed into the library routine with the existing library file to produce an updated or new library file.

#### 1-45. LOADABLE OBJECT PROGRAMS

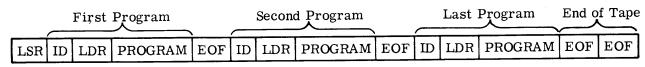

1-46. A loadable object program is one that has only its own loader on the first portion of the object tape,

LDR PROGRAM

"LOADABLE" PROGRAM FORMAT (Paper or Magnetic Tape)

Figure 1-3. Program Library Files

immediately preceding the object program. Refer to figure 1-4. All object programs produced by QANTEL Business Assembly Language programs are of this type. However, the magnetic tape and disc object programs produced by the assembler programs are usually object programs that constitute a library file containing one or more object programs.

| LSR | ID | LDR | PROGRAM | EOF | EOF |

|-----|----|-----|---------|-----|-----|

| 1   |    |     |         |     |     |

"LIBRARY FILE" PROGRAM FORMAT (Magnetic Tape only)

MULTIPLE PROGRAM "LIBRARY FILE" PROGRAM FORMAT (Magnetic Tape only)

LSR = Library Search Routine

LDR = Loader Routine

ID = Program Seven-Character Identification EOF = End-of-File Indicator (hexadecimal 13)

Figure 1-4. Object Program Formats

#### 1-47. LIBRARY OBJECT FILES

1-48. The library file object program consists of one or more loadable object programs identified by a unique (within the file) seven character program identifiers that precedes the object program loader. See figure 1-4. The first record of the object tape contains a Library Search Routine (LSR) capable of searching the object tape file for a routine specified by the operator. End-of-File

(EOF) characters are written on the magnetic tape to mark the end of each object program. Two consecutive EOF characters are written to mark the end of the entire library file. The library file may be used as a separate library or, it may be combined with other library files to construct a larger library file. This is accomplished by using the appropriate program library maintenance routine.

# **SECTION II**

# PROCESSOR FUNCTIONS

#### 2-1. GENERAL

2-2. The QANTEL/ANSWER Processor System has 51 standard instructions that are hard-wired in the Read-Only Memory (ROM). See section I for a description of the ROM. These instructions include fourteen input/output processing and control instructions, and 37 data handling, arithmetic and logical, decision and control, and special instructions. This section provides a description of the various processor functions such as data and instruction formats, addressing structure, the interrupt feature, and the various switch settings. Also included are descriptions of all the standard instructions, except for I/O instructions, along with examples of both machine language instruction format and examples of assembly language instruction coding. The I/O instructions are described fully in section V of this manual.

#### 2-3. DATA FORMAT

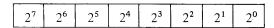

2-4. The basic unit of information used in the QANTEL/ANSWER Processor System is the byte. Each byte is made up of eight binary bits and can represent an alphabetic letter, a numerical digit, a special character, or a hexadecimal number from 00 to FF. The byte is the smallest addressable unit in the processor, which has a storage capacity of either 4096, 8192, 16384, 24576, or 32768 such bytes. Each of the eight bits within a byte is identified by its binary weight expressed in powers of two as illustrated in figure 2-1. Throughout QANTEL publications, the low order bits are always placed to the right side of the byte. The internal code used in the processor is ASCII. Appendix B of this manual shows a complete ASCII table. ASCII is used to represent all

alphameric characters, operands, and special control characters (e.g., communications).

Figure 2-1. Eight-bit Byte

#### 2-5. **INSTRUCTION FORMAT**

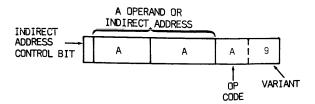

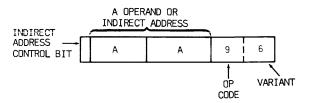

#### 2-6. Single-Address Instructions

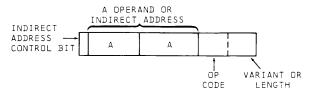

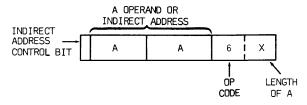

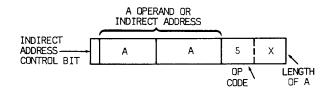

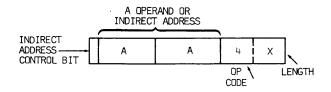

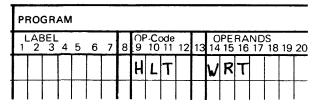

2-7. The QANTEL/ANSWER Processor is a single-address and two-address computer. When single address instructions are used, the instruction operand address becomes the address of the A operand field. An accumulator, which occupies the low order 16 positions of main memory, becomes the implied B operand field. The format of the single-address instruction is basically the same as that of the two-address instruction (described in the following paragraphs), except that it consists of only three (instead of six) bytes. Figure 2-2 illustrates the machine language format of a single-address instruction and figure 2-3 shows a sample of single-address instruction coding.

Figure 2-2. Single-Address Instruction Machine Language Format

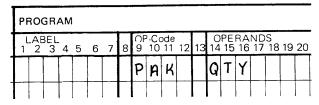

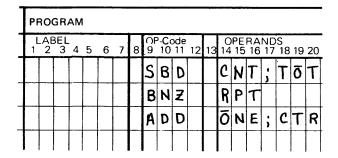

| PI     | 30       | GR.      | ΑN | 1 |   |   |   |         |      |           |    |    |    |          |          |          |         |    |

|--------|----------|----------|----|---|---|---|---|---------|------|-----------|----|----|----|----------|----------|----------|---------|----|

| 1<br>1 | -AE<br>2 | 3EL<br>3 | 4  | 5 | 6 | 7 | 8 | OF<br>9 | 2-Co | ode<br>11 | 12 | 13 | 14 | PE<br>15 | RA<br>16 | ND<br>17 | S<br>18 | 19 |

|        |          |          |    |   |   |   |   | ը       | A    | K         |    |    | Q  | τ        | Y        |          |         |    |

|        |          |          |    |   |   |   |   |         |      |           |    |    |    |          |          |          |         |    |

|        |          |          |    |   |   |   |   |         |      |           |    |    |    |          |          |          |         |    |

Figure 2-3. Single-Address Instruction Coding Example

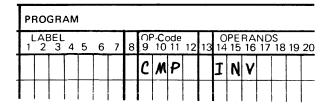

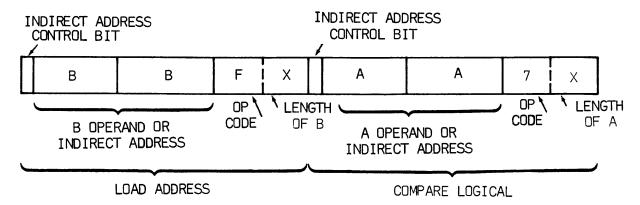

#### 2-8. Two-Address Instructions

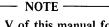

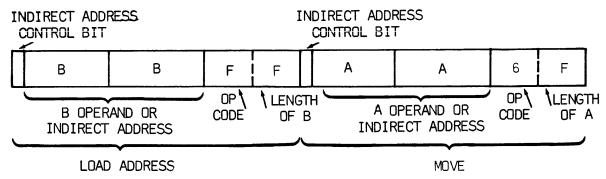

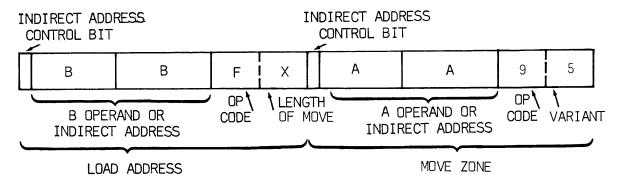

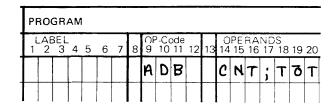

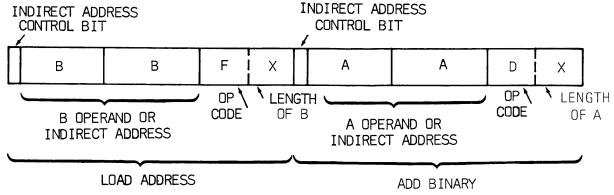

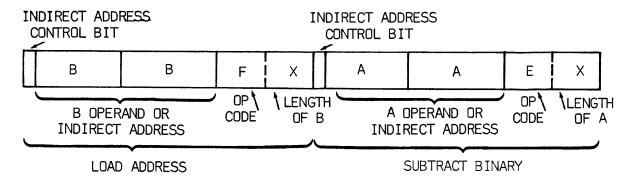

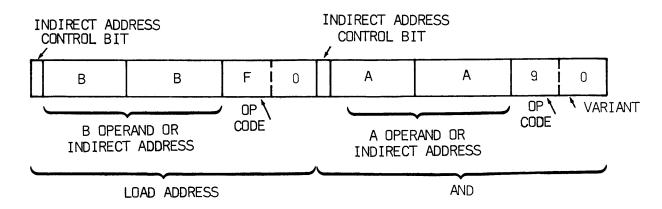

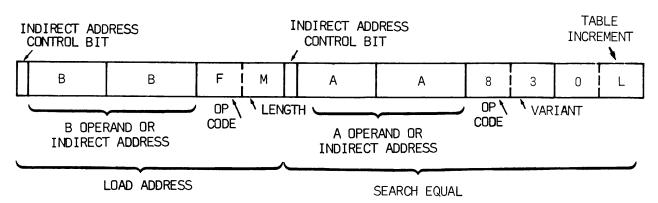

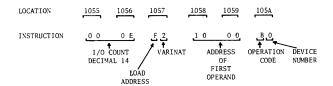

2-9. All two-address instructions are made possible by the Load Address instruction which indicates to the processor that the instruction is to be treated as the two-address type. The Load Address instruction is described fully in paragraph 2-134. In the fetch cycle for the two-address instruction, the operation code included with the first instruction (Load Address instruction) initiates a sequence that continues fetching, so that both operands are identified prior to the execution.

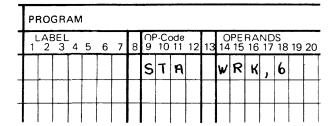

2-10. In the two-address instruction (with the exception of the Read or Write I/O instruction), the operand address of the Load Address instruction is the address of the B operand field, and the operand address of the second instruction is the address of the A operand field. In either mode of addressing (single-address or two-address), the individual instructions are always three bytes in length, making a total of six bytes for a complete two-address instruction. The two-address instruction has the format shown in figure 2-4. Figure 2-5 shows a coding example of a two-address instruction.

Refer to section V of this manual for a complete description of two-address I/O instructions. This includes the different types of Read and Write instructions.

| PI     | 30       | GR  | ΑN | ı |   |   |   |         |           |           |    |    |         |          |          |          |         |    |    |          |

|--------|----------|-----|----|---|---|---|---|---------|-----------|-----------|----|----|---------|----------|----------|----------|---------|----|----|----------|

| 1<br>1 | _AE<br>2 | 3EL | 4  | 5 | 6 | 7 | 8 | OF<br>9 | ۲.C<br>10 | ode<br>11 | 12 | 13 | 0<br>14 | PE<br>15 | RA<br>16 | NC<br>17 | S<br>18 | 19 | 20 | <u>-</u> |

|        |          |     |    |   |   |   |   | ρ       | A         | К         |    |    | Q       | Ť        | Y        | ,        | 1       | M  | Р  |          |

|        |          |     |    |   |   |   |   |         |           |           |    |    |         |          |          |          |         |    |    |          |

|        |          |     |    |   |   |   |   |         |           |           |    |    |         |          |          |          |         |    |    |          |

Figure 2-5. Two-Address Instruction Coding Example

Individual field definition may differ; however, the definitions are explained as each instruction is examined later in this section.

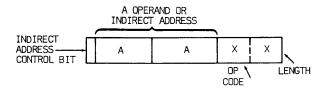

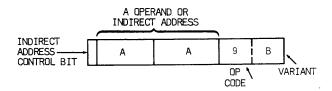

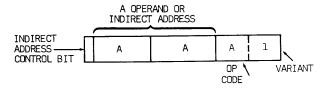

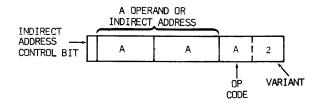

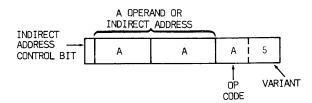

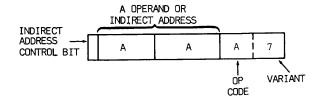

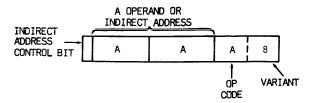

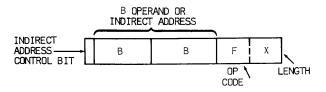

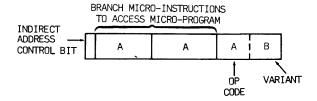

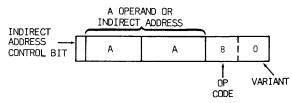

#### 2-11. Indirect Addressing

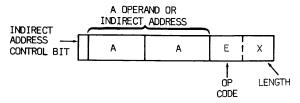

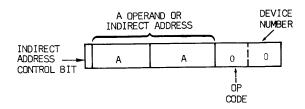

2-12. The most significant bit in any instruction is the indirect address control bit. If the indirect address control bit is in the "1" state, indirect addressing is indicated to the processor, and the instruction address is used as source of the operand address. If the most significant bit (of the most significant byte) of the indicated address is also in the "1" state, it is also used as an indirect address and the operation will continue until an operand address is found with the indirect address control bit in the "0" state. Indirect addressing is invaluable when it is necessary to reference a location that it is not convenient to address directly.

Figure 2-4. Two-Address Instruction Machine Language Format

- NOTE -

Indirect address looping is a possibility in the QANTEL/ANSWER Processor, and care should be exercised to insure proper setup of instruction formats.

2-13. Indirect addressing is valid for both the single-address and two-address instructions. This powerful feature can be used to index through a table, or for other operations that require changing addresses.

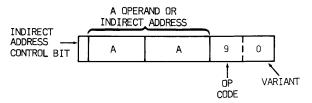

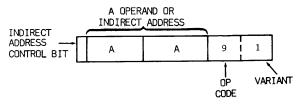

#### 2-14. Operation Code and Variant

2-15. The most significant four bits of the least significant byte in any instruction is the operation code. See figures 2-2 and 2-4. The operation code, in conjunction with a variant (if required), indicates the type of operation to be performed by the instruction. The variant occupies the least significant four bits of the instructions, when used. All operation codes and variants are listed with their respective instruction definition and mnemonic in Appendix D at the rear of the manual. In addition, each QANTEL Instruction is described under the heading of Standard Instructions. Description is in sufficient detail to provide the programmer with a working knowledge of the QANTEL Standard Instructions.

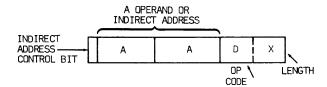

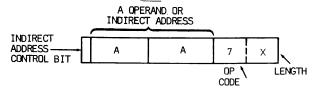

#### 2-16. Instruction Length

2-17. Instructions with operand that are variable in length (Add, Subtract, Store, etc.) carry length indicators in the instruction. When used, the length indicator occupies the least significant four bits of the instruction as shown in figure 2-6. Also, certain instructions (e.g. Move Numeric) utilize a length only when the two-address form is used. In this case, the length is specified in the Load Address instructions.

Figure 2-6. Machine Language Representation of Instruction Length

2-18. In the single-address mode, the length of the B operand field is 16 positions (the length of the accumulator).

NOTE

Using the two-address mode is often more economical in elapsed time, especially if the operand length is much less than maximum.

- 2-19. In all except the Input/Output instructions (see section V), the length indicator specifies the operand field length beginning at the least significant byte (highest memory position).