# VT3 Theory of Operation

**TD-4102**

Technical Manual

FIRST PRINTING: JUNE 1980 SECOND PRINTING: AUGUST 1981 THIRD PRINTING: FEBRUARY 1982

# VT3 Theory of Operation

First Printing: June 1980

$\bigcirc$  Qantel Corporation  $\square$

# Table of Contents

### • HARDWARE

|   | Physical DescriptionI-1                             |

|---|-----------------------------------------------------|

|   | Block Diagram ExplanationI-3                        |

|   | Explanation of the Logic Drawings:                  |

|   | Sheet 1 (Microprocessor and Input Ports)            |

|   | Sheet 2 (Program ROM and Utility RAM)I-11           |

|   | Sheet 3 (Address Counter, MUX, and Display RAM)I-13 |

|   | Sheet 4 (Horizontal Timing)I-15                     |

|   | Sheet 5 (Vertical Timing and Interrupt Control)1-19 |

|   | Sheet 6 (Character Generator and CRT Interface)I-22 |

|   | Sheet 7 (Baud Rate Generator and UART)              |

|   | Sheet 8 (Keyboard Interface and DC Voltage)I-27     |

|   | Sheet 9 (Signal and DC Power Distribution)          |

|   | Sheet 10 (Transformer and Wiring Diagrams)          |

|   | PS-9 Power SupplyI-30                               |

|   | VT3 Documents                                       |

|   | IC Listing for the VT3I-33                          |

| • | OPERATIONAL DESCRIPTION                             |

|   | Display ScreenII-1                                  |

|   | KeyboardII-5                                        |

|   | Microcode SummaryII-7                               |

|   | Data Paths and TranslationII-18                     |

|   | Typewriter ModeII-19                                |

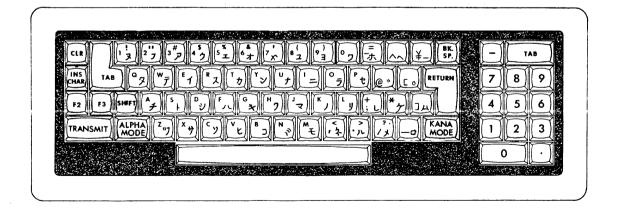

|   | Katakana KeyboardII-20                              |

| • | CONFIGURATION INFORMATION                           |

|   | Network TypesIII-1                                  |

|   | Logic Board Jumper SettingsIII-4                    |

|   | P1 Connector                                        |

|   | P2 ConnectorIII-7                                   |

| • | TEST PROCEDURES                                     |

|   | Manual TestIV-1                                     |

|   | Available VT3 Test ProgramsIV-3                     |

|   |                                                     |

|   | APPENDIX |

|---|----------|

| • |          |

,

| UART Pin DesignationsV-1                     |

|----------------------------------------------|

| IC SpecificationsV-4                         |

| VT3 Domestic Character SetV-13               |

| Keyboard StatusV-14                          |

| UART Status RegisterV-14                     |

| Terminal Information WordV-14                |

| VT3 Status ByteV-15                          |

| Memory and I/O DecodingV-16                  |

| PS-9 Logic DrawingFoldout                    |

| VT3 Logic DrawingsFoldouts                   |

| FIGURE LIST                                  |

|                                              |

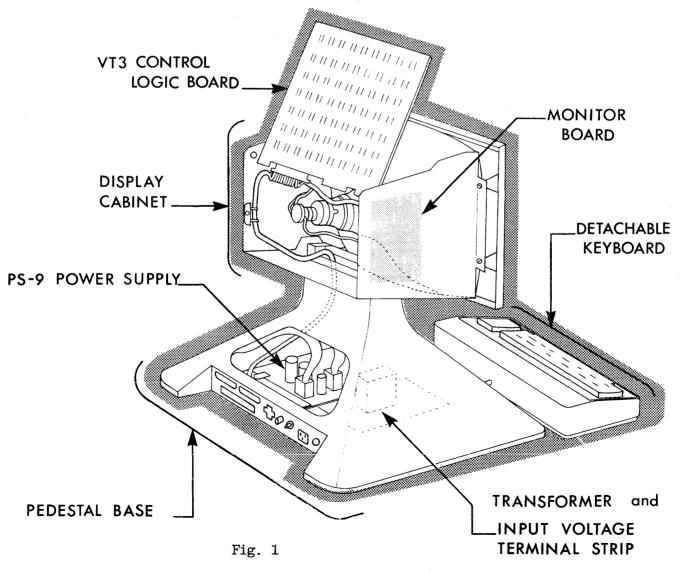

| Figure 1 Major Components of the VT3I-1      |

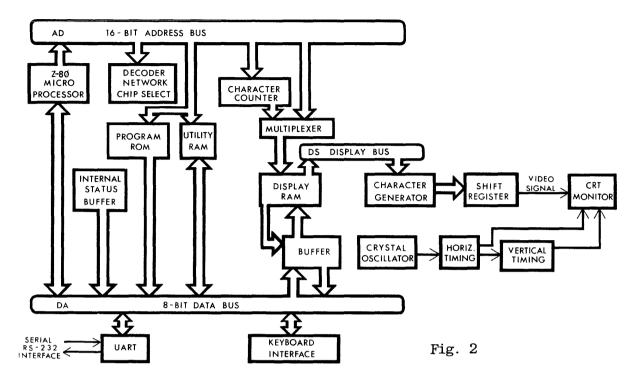

| Figure 2 Block DiagramI-4                    |

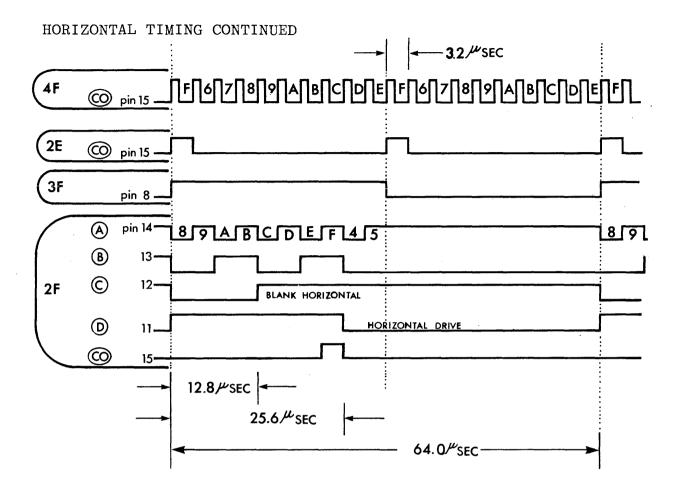

| Figure 3 Horizontal TimingI-17               |

| Figure 4 Horizontal TimingI-18               |

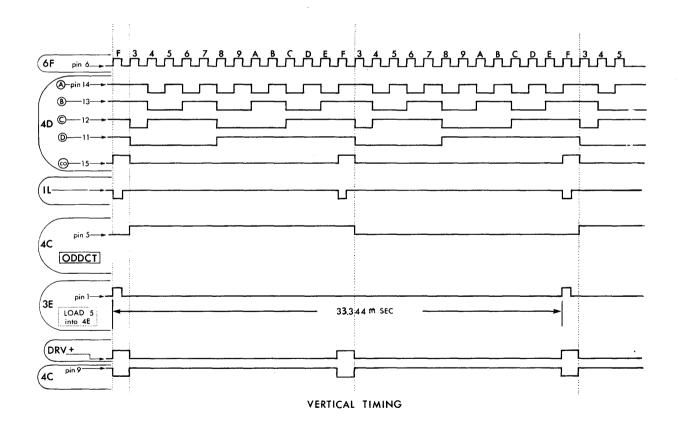

| Figure 5 Vertical TimingI-20                 |

| Figure 6 Interlaced Character Slices         |

| Figure 7 VT3 KeyboardII-4                    |

| Figure 8 Data Paths and TranslationII-18     |

| Figure 9 Katakana KeyboardII-19              |

| Figure 10 - Data Conversion for StorageII-21 |

| Figure 11 - Katakana Character SetII-22      |

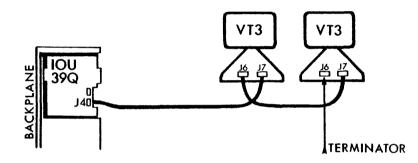

| Figure 12 - Direct String Network            |

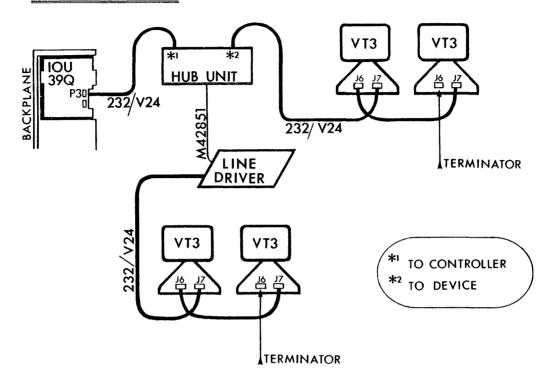

| Figure 13 - Hub Unit NetworkIII-2            |

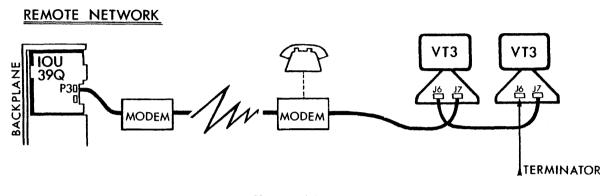

| Figure 14 - Remote NetworkIII-3              |

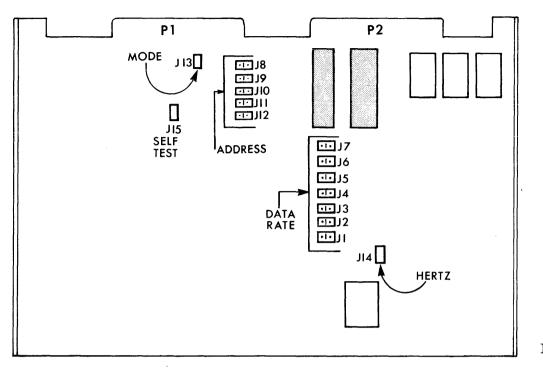

| Figure 15 - Jumper PlacementIII-4            |

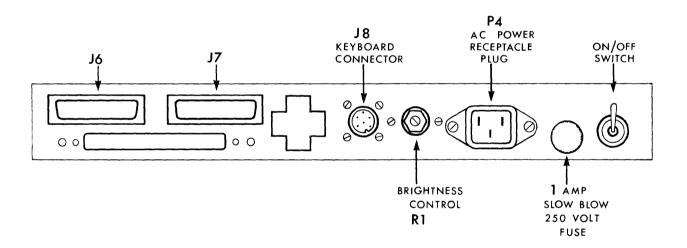

| Figure 16 - VT3 Pedestal Back Panel          |

| Figure 17 - Control Logic Board: P1          |

| Figure 18 - Control Logic Board: P2          |

# Hardware

PHYSICAL DESCRIPTION

The various components of the Qantel Video Terminal 3 reside within three separate enclosures: the display cabinet, the pedestal base, and the keyboard. Within the fully pivoting display cabinet are the Z-8Ø based control logic board and the CRT with its monitor board. The supporting pedestal base contains the PS-9, a standard linear power supply providing the DC voltages for VT3 operation. The keyboard, with interchangeable keytops to match different character sets, contains a single board featuring a small speaker (for the alarm). Three variations of character sets are available - domestic, Swedish, and Japanese. Other sets are planned for the future.

#### PHYSICAL DESCRIPTION CONTINUED

Convection cooling is used in each of these enclosures to maintain normal operating temperatures.

External controls are minimal; the back of the pedestal features an on-off switch and brightness control. The J6 and J7 connectors, also on the back panel, permit system interfacing and daisy-chaining of additional VT3's. The AC power cable is detachable. The main power fuse, rated at 1 amp, 250 volts, is also located on this back panel.

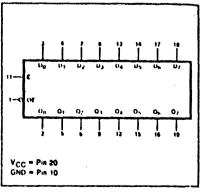

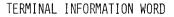

Switch settings provided within the display cabinet condition the VT3 for variables in operation. The control logic board allows switch setting of asynchronous communication speeds ranging from 300 bps to 19,200 bps; 50 Hz or 60 Hz operation; individual VT3 address within the communication network; and initial display screen parameters (27 lines of 64 characters or 24 lines of 80 characters).

Input voltages can be matched to transformer capabilities by means of a ten-position terminal strip connecting with the primary windings of the transformer. Thus, operation is possible with input voltages of 100, 115, 215, 230, and 240 VAC.

A maximum of thirty-one VT3's may be configured off a single controller through direct connection, hub units, line drivers, and modems. The IOU-39Q performs the role of controller in conjunction with the VT3.

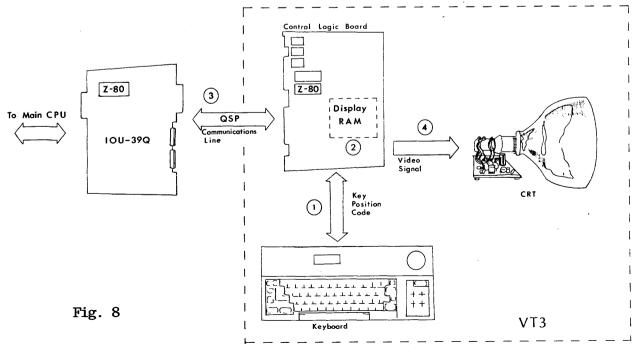

#### BLOCK DIAGRAM EXPLANATION

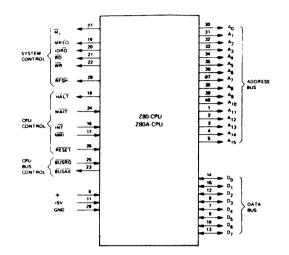

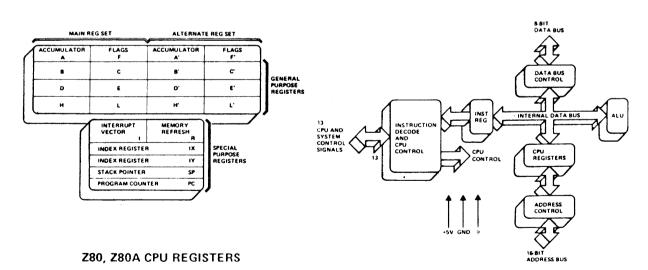

The block diagram illustrates the components of the control logic board in relation to the keyboard, the communications line, and the CRT. The basic operations, as dictated by the instructions in the Program ROM, are carried out by the  $Z-8\emptyset$ microprocessor. The Z-80 must continually update the Display RAM with character information derived from the keyboard and central processor. Each character space on the CRT display screen is represented by a memory location within the Display By actively monitoring the communications line through RAM. the UART (Universal Asynchronous Receiver-Transmitter), and the keyboard interface, and loading arriving characters into the RAM, the Z-80 is able to ensure the display screen presentation is current within the realm of system program activities.

The Z-80 microprocessor directs data on the 8-bit DB bus by selectively enabling the appropriate components upon the control logic board. The 16-bit AD (Address) bus carries this directional information to one of the following (depending on the address value):

- A decoder network which provides chip select signals to activate specific components.

- The address inputs of the Program ROM or Private Utility RAM.

- The Address circuitry for the Display RAM, tied into the CRT's video timing network through a Character Counter and Multiplexer.

The timing network is designed to allow the Z-80 access to the Display RAM during a brief period between individual character accessing by the scan circuitry. Access is available as well during the horizontal and vertical blanking periods.

Z-8 $\emptyset$  clock periods are regulated by a 4.0 Megahertz oscillator. This results in a 0.25 microsecond duration for each T-state.

The Decoder Network generates chip select signals based on information the Z-80 provides along the AD bus and certain control lines (MREQ, MONE, and IORQ). As illustrated on Sheet 7 of the logic drawings, two high-speed 1-of-8 Decoder chips handle selection of memory (CSA0 - CSA5) and selection of I/O ports (CSC0 - CSC7). The specific chip select information is presented in the Appendix of this manual.

The Program ROM contains 6K bytes of microcode used to structure the activities of the Z-8Ø in performing basic operations of the VT3. Three 2K by 8 bit memory chips are used, selected by chip selects CSAØ or CSA1 and address lines AD1Ø and AD11.

The Utility RAM acts as a storage area for the Z-80 for program variables and scratchpad space during various program sequences. It consists of four 1K by 4 bit memory chips accessed

#### BLOCK DIAGRAM EXPLANATION CONTINUED

in pairs for a total memory area of 2K by 8 bits.

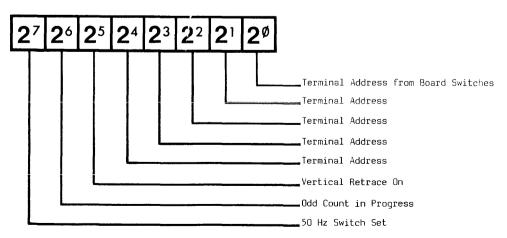

The Internal Status Buffer is a tri-state buffer (7B seen on Sheet 1 of the logic drawings) which, when enabled, can supply the Z-80 with the following information: selected VT3 address as represented by jumpers J8 through J12; presence of the DRV+ signal and ODDCT+, both indicative of key aspects of video timing; and the 60HZ signal, showing the condition of jumper J14 - the 50 or 60 Hz switch.

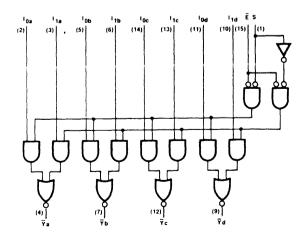

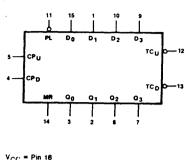

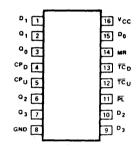

The Character Counter supplies the address to the Display RAM for accessing a particular location, akin to a position on the CRT display screen. Consisting of three 4-bit presettable counters, the Character Counter is loaded by the Z-80 with the appropriate address to start each row. The counter is incremented throughout the horizontal scan automatically. The Z-80 may bypass addressing the Display RAM through the Character Counter, addressing instead directly through the Multiplexer. When a specific signal is present as a result of timing considerations (SMEN-), the Z-80 can use this mode of addressing.

The Multiplexer, three Quad 2-Input Data Selector/Multiplexer chips, feeds the inputs to the Display RAM chips with addresses from either the Character Counter or directly off the Z-80's AD bus.

The Display RAM consists of four 1K x 4 bit memory chips accessed in pairs to create a 2K by 8 bit display memory. Characters encoded in ASCII values are stored in locations to represent a one-to-one relationship with the CRT display screen. A timing signal releases accessed characters to the

#### BLOCK DIAGRAM EXPLANATION CONTINUED

DS bus (Display Bus) where the ASCII value is applied to a Character ROM to produce the correct dot matrix pattern. A pair of octal latches, one for input and the other for output, act as a buffer between the Display RAM and the DA bus.

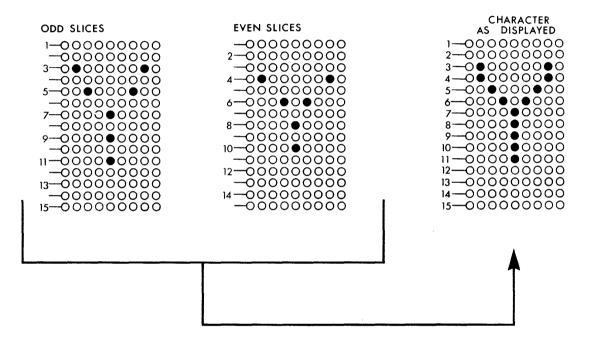

The Character Generator, 16K of ROM, receives the 8-bit ASCII value from the DS bus and produces a portion of the dot pattern, one slice of the matrix, based on the horizontal scan row information received from a line counter. The line counter consists of a Dual-D flip-flop and 4-Bit Synchronous Counter that maintains count of the slice of a particular character being produced, one row of a possible fifteen. During the course of each horizontal scan row, eight slices of a character are assembled (all even or all odd lines). The interlaced scan returns after finishing the rest of the frame and inserts the slices that were missed the first time.

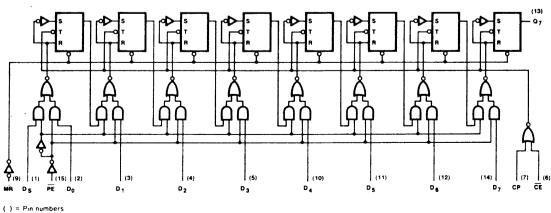

The Shift Register (Parallel In - Serial Out/Serial In -Serial Out 8-Bit Shift Register) accepts a parallel byte from the Character Generator and shifts it out serially to form the video signal sent directly to the CRT. A LOAD+ signal generated as a part of the horizontal timing controls the rate of the video signal.

The Horizontal and Vertical Timing circuitry is based on the clock signal sent from an 11.25 MHz oscillator. The resulting signals are used to control access of the Display RAM, clock the shift register, produce specific interrupts to the Z-80, create the horizontal and vertical inputs to the video monitor board, produce the blanking signals, and generate the odd-even interlace flag.

I--6

#### BLOCK DIAGRAM EXPLANATION CONTINUED

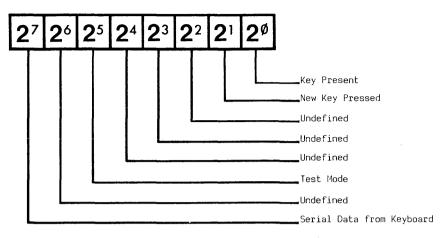

The Keyboard Interface allows the Z-80 through a tri-state buffer to receive incoming strobe signals from the keyboard, detect the New Key Pressed flag, and receive serial bits from the keyboard on the DKEY+ data line. Incoming data bits are clocked by the Z-80 sending out the signal CLOCK+ to the keyboard. The Z-80 may also sound the alarm, the keyboard audio signal, by setting the Alarm Latch.

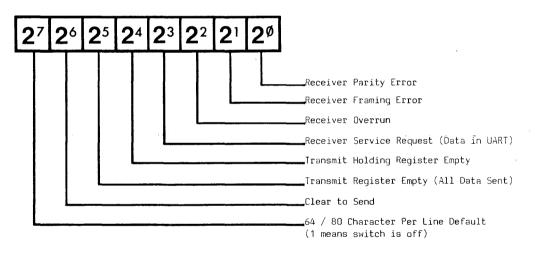

The UART (Universal Asynchronous Receiver-Transmitter) provides the link to the RS-232 serial communication line, directly interfacing the UART of the managing IOU-39Q controller. The Z-8 $\emptyset$  monitors the state of the UART to detect the Data Ready condition (indicating incoming data) or Transmit Holding Register Empty (allowing the Z-8 $\emptyset$  to transmit data). EXPLANATION OF THE LOGIC DRAWINGS - SHEET 1 MICROPROCESSOR AND INPUT PORTS

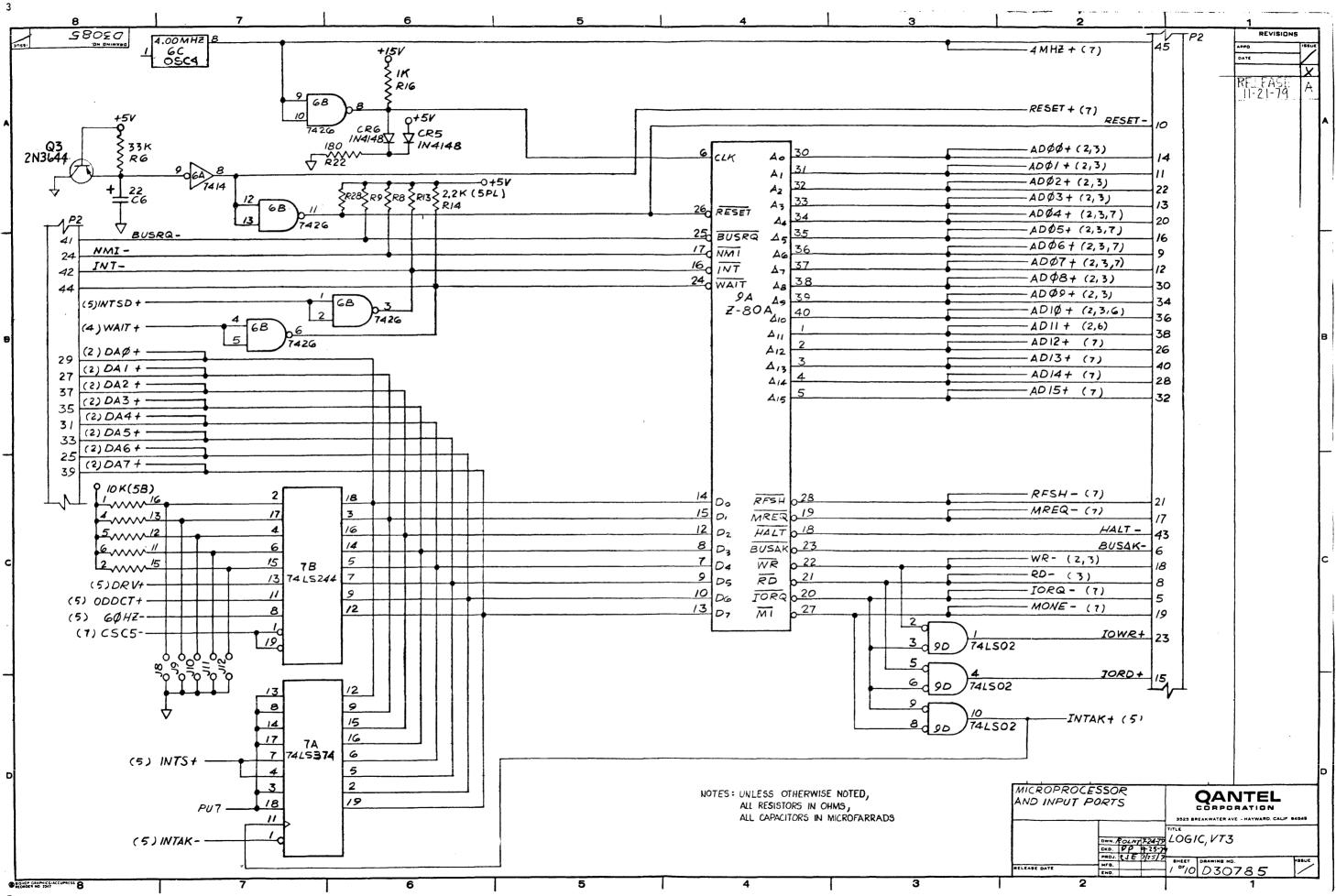

In the upper lefthand corner of Sheet 1, the IC chip 6C, a 4.00 MHz clock oscillator, provides the Z-89 with a squarewave clock input resulting in a basic T-state period of 0.25 microseconds. The diode-clamped driver network provides edgeshaping and voltage control for the clock signal to meet Z-89 requirements (necessary at higher frequency operation). The 4 MHz signal also is routed to a timing network to control the UART's baud rate.

The RC network located at A8 on the sheet remains low for 50 microseconds after power up to reset the Z-80 microprocessor and the UART.

The connector P2, shown at the far left and right of the sheet, allows access to the Z-80 control, data, and address lines through test panel interface.

The Z-80, operating according to the microprogram stored in the 6K ROM, must coordinate tasks on two levels. Data and control characters must be received and properly channeled as they arrive from the UART and the keyboard. The functions required to accomplish this may be thought of as a foreground operation. Also, the display screen must be continually refreshed. The Z-80 performs this as a background level task by generating addresses and timing control signals at regular intervals.

#### MICROPROCESSOR AND INPUT PORTS CONTINUED

The Interrupt line (INT-) is used to notify the Z-8 $\emptyset$  of the conclusion of a horizontal scan, vertical scan, or act as a prompt for the Z-8 $\emptyset$  to check communications line activity through the UART. The method by which these interrupts are generated is discussed further on the sheets on which they originate (see Sheets 4 and 5).

The WAIT line when activated produces a condition within the Z-80 suspending all operations until the line goes inactive. WAIT in this case is used to prevent the Z-80 from accessing the Display RAM during certain periods of the memory access cycle.

The 8-bit Data Bus, DAØ through DA7, links the Z-80 to the significant components of the control logic board. Refer to the block diagram on page I-4 for an overview of which components are interfaced.

Tri-state buffer 7B is used by the Z-80 by activating Chip Select CSC5 to obtain the following information. DRV+ (the Vertical Drive signal) when absent indicates the presence of the vertical blanking period. ODDCT+, a product of the vertical timing network, differentiates between the odd and even scan as dictated by the interlace pattern. 60Hz- denotes the presence of jumper J14, necessary for operation with 60Hz power input. (Jumper J14 removed conditions the timing for 50Hz operation.)

Jumpers J8-J12 are used to select the address for the video terminal within a terminal network. The address \$1F may not be used as it is reserved for broadcast messages (to all terminals simultaneously). The Z-80 thus derives the terminal identity by reading the state of these jumpers.

#### MICROPROCESSOR AND INPUT PORTS CONTINUED

Tri-state buffer 7A allows the Z-80 upon sensing an Interrupt to determine the nature of the Interrupt (Scan Interrupt or Timer Interrupt). The Z-80 reacts to its INT line being pulled by issuing active IORQ and MI. These signals ANDed create INTAK (Interrupt Acknowledge) which clocks Buffer 7A, loading restart vector at its inputs. This restart vector will be an \$FF if the signal INTS+ is present (a timing indication that a Scan Interrupt is occuring). The absence of INTS+ result in \$CF, denoting a Timer Interrupt.

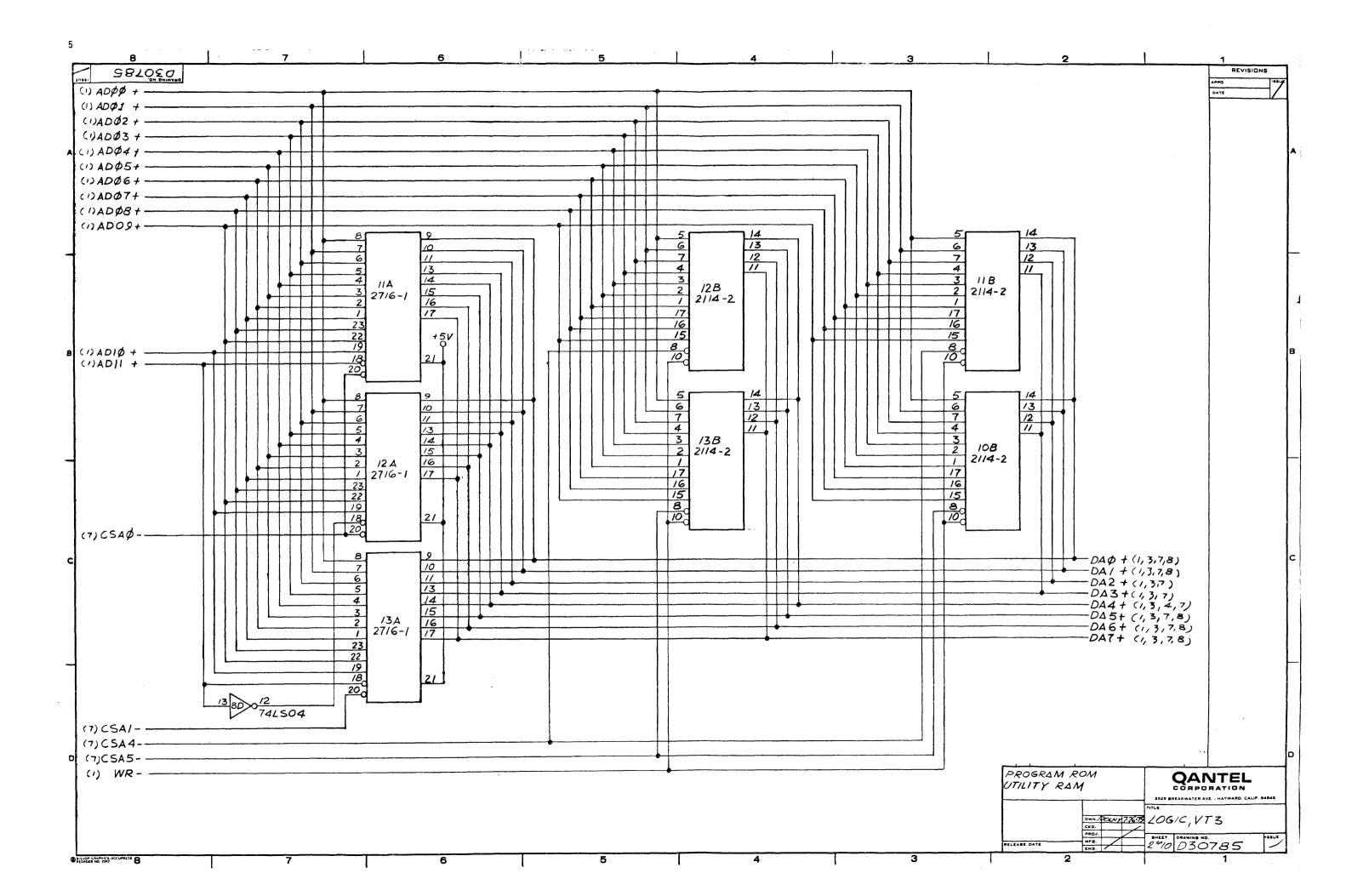

### EXPLANATION OF THE LOGIC DRAWINGS - SHEET 2 PROGRAM ROM AND UTILITY RAM

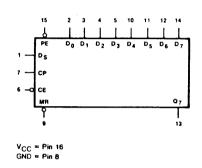

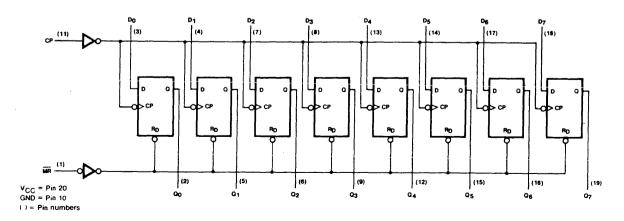

Three 2716 programmable read only memory chips store the microprogram for the Z-8 $\emptyset$ , providing a maximum of 6K bytes (by 8-bit) storage area. Address lines AD $\emptyset$  through AD1 $\emptyset$  from the Z-8 $\emptyset$ interface the address inputs of the chips.

AD11 in combination with chip select signals CSAØ and CSA1 select the individual IC for the chosen portion of memory. CSAØ, when AD11 is low, selects IC 11A. IC 12A is accessed when AD11 is high at the same time as CSAØ. This covers memory addresses \$ØØØØ through \$ØFFF. CSA1 in combination with a low AD11 selects 1C 13A. This begins memory addressing at \$1000. Although only 6K of ROM is currently used, space is allotted so that the addition of another memory IC would expand addressing through \$1FFF. The decoding that produces CSAØ and CSA1 can be seen on Sheet 7 of the logic drawings.

Microinstructions are drawn from ROM (via the 8-bit DA bus) during an instruction fetch cycle preceding each Z-80 operation. The microprogram as executed by the Z-80 is examined in the Operational Description segment of this manual.

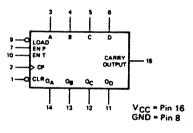

The four 2114 random access memory chips shown on the right half of the sheet represent the Utility RAM. Each memory IC has a capacity of 1Kx4 bits; they are accessed in pairs to produce a total RAM storage area of 2K by 8 bits. Pins 11, 12, 13, 14 offer bidirectional data inputs and outputs, interfacing with the DA bus.

The signal CSA4 selects RAM chips 11B and 12B. CSA5 selects 10B and 13B. Pin 10 acts as the Write Enable, activated by the Z-8Ø (by the signal WR) whenever data is to be loaded into the RAM. Each chip select signal provides 1K (1024 bytes) of

PROGRAM ROM AND UTILITY RAM CONTINUED

storage area; CSA4 from 4000 to 43FF and CSA5 from 5000 to 53FF.

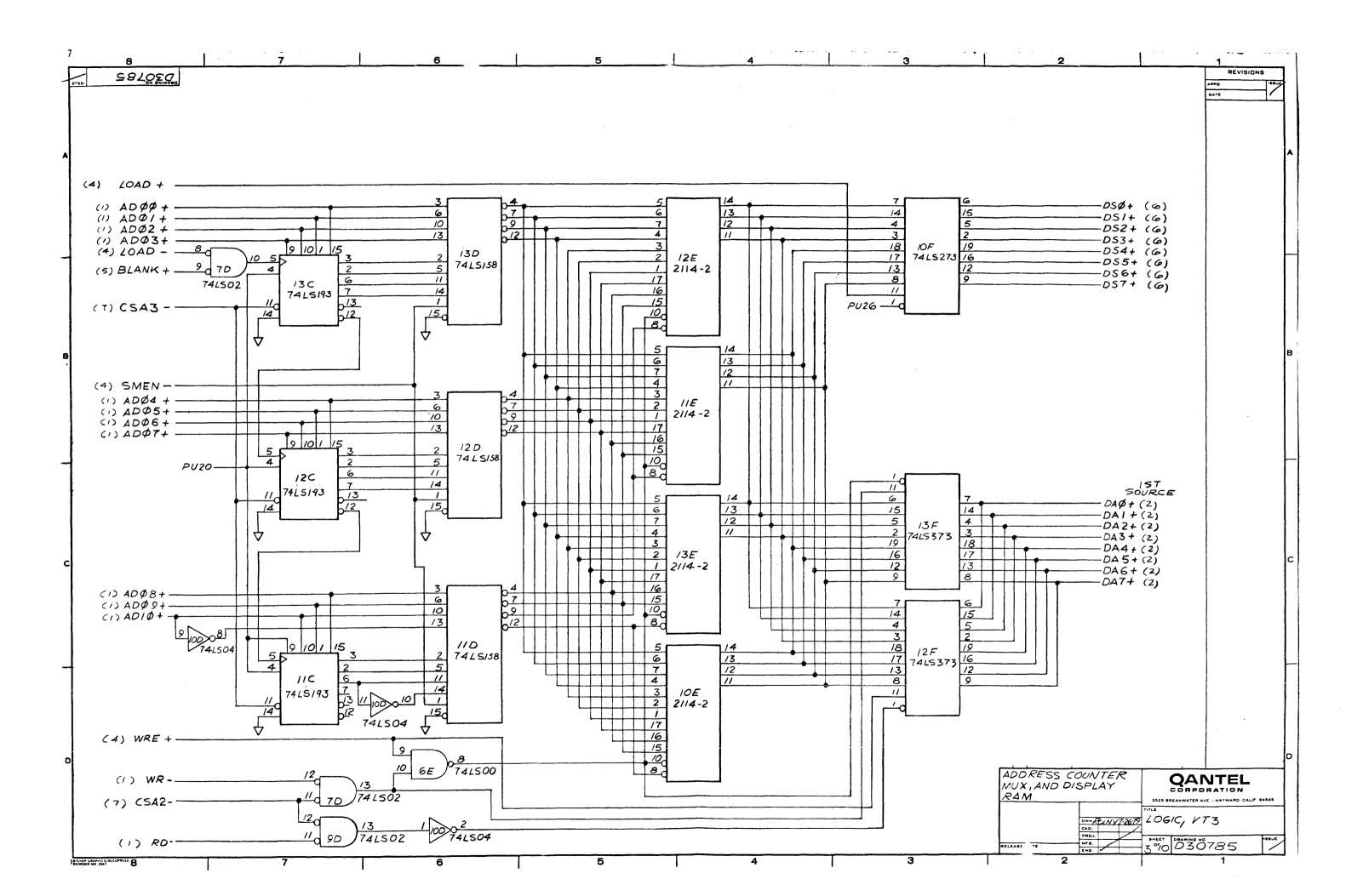

The Utility RAM allows the Z-80 a "scratchpad" area to manipulate program variables, maintain flags, keep track of counts during transfer operations, and provide buffer space for transmit and receive handling. Qantel document #L30786, the microcode listing, describes labels associated with the various Utility RAM addresses. EXPLANATION OF THE LOGIC DRAWINGS - SHEET 3 ADDRESS COUNTER, MUX, and DISPLAY RAM

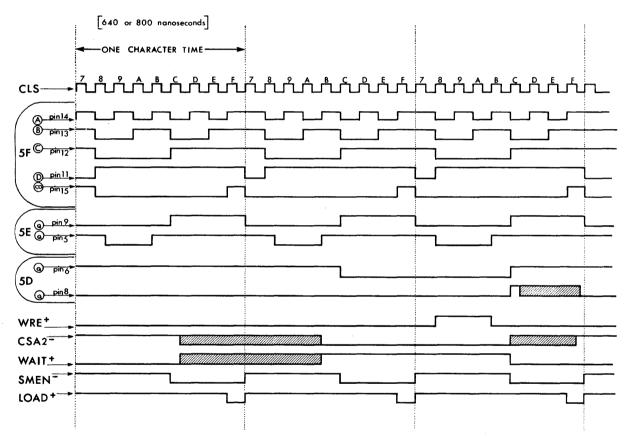

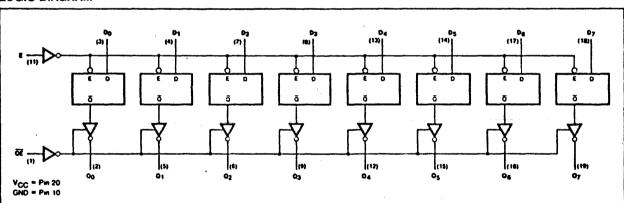

The Display RAM stores characters in a one-to-one ratio corresponding with the characters to appear on the video screen. The scan logic circuitry accesses these characters in a manner synchronized to the horizontal and vertical timing signals; the Z-80 need only intervene to provide a starting address at the advent of each horizontal scan row. The character information in the Display RAM is updated by the Z-80 during "window periods", times when the scan logic is not actively accessing Display RAM or during free time at horizontal or vertical retrace intervals.

LOAD+, a signal originating in the horizontal timing network, acts as a clock for IC 10F, an Octal D flip-flop, storing the data outputs of the Display RAM in preparation for sending the character data out on the Display Bus to be converted to an appropriate dot pattern on the screen. LOAD+ will vary in frequency (see Sheet 4) depending on whether a 64 or 80 character line is being employed. This coordinates character generation with the fixed time of the electron beam scan across the screen to accomodate the number of characters per line.

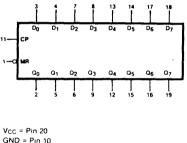

The Address Counter consists of three 74LS193 chips, asynchronously parallel-loading 4-bit up-down counters. Timing hardware generates a maskable interrupt before each horizontal or vertical retrace. Within the microcode, the scan interrupt routine accesses a table to acquire an address which is parallel-loaded into the counters. CSA3-, a signal produced by decoding address lines AD12+, AD13+, AD14+, and AD15+, is generated whenever the Z-80 produces an address between \$3000 to \$37FF or \$3800 (to create a blank scan row) and triggers the parallelloading. Note that outputting \$3800 on the address lines results in \$000 being loaded into the counters. Actual Display

#### ADDRESS COUNTER, MUX and DISPLAY RAM CONTINUED

RAM addresses range between 2000 and 27FF. Once the 4-bit counters are loaded, they increment automatically, clocked by the LOAD- signal, thus stepping through each address of the horizontal row a character at a time. BLANK+, present during blanking intervals, inhibits clocking at AND-gate 7D.

The signal SMEN-, Scan Memory Enable, controls the Select pin of multiplexers 13D, 12D and 11D. This determines whether addressing to the Display RAM will be gated through directly off the Address lines or through the 4-bit counters. When SMEN- is active (low), during execution of scan logic, the Address Counter outputs are gated through. SMEN- going true allows the Z-80 to directly address any location in the Display RAM.

The Z-80 directly addressing the Display RAM, using addresses 22000 to 27FF, creates the decoded signal CSA2-. CSA2- sets a flip-flop (5D) in the horizontal timing network to activate the WAIT line to the Z-80 (synchronizing the slow RAM memory inputs to the faster Z-80). WRE+ is then produced by horizontal timing. WRE+ and SMEN- dictate the period of the "window" during which the Z-80 can write to the RAM. At the same time CSA2combined with WR- (from the Z-80) are ANDed to latch data from the DA bus into Octal Latch 13F. The output is enabled through this latch to the Display RAM (by pin 1 - the output enable pulled active by the WRE+ signal). A READ of the Display RAM can be accomplished in similar fashion by the Z-80 activating the RD- line rather than WR-, thus enabling Octal Latch 12F, gating Display RAM output lines to the DA bus for reading by the Z-80.

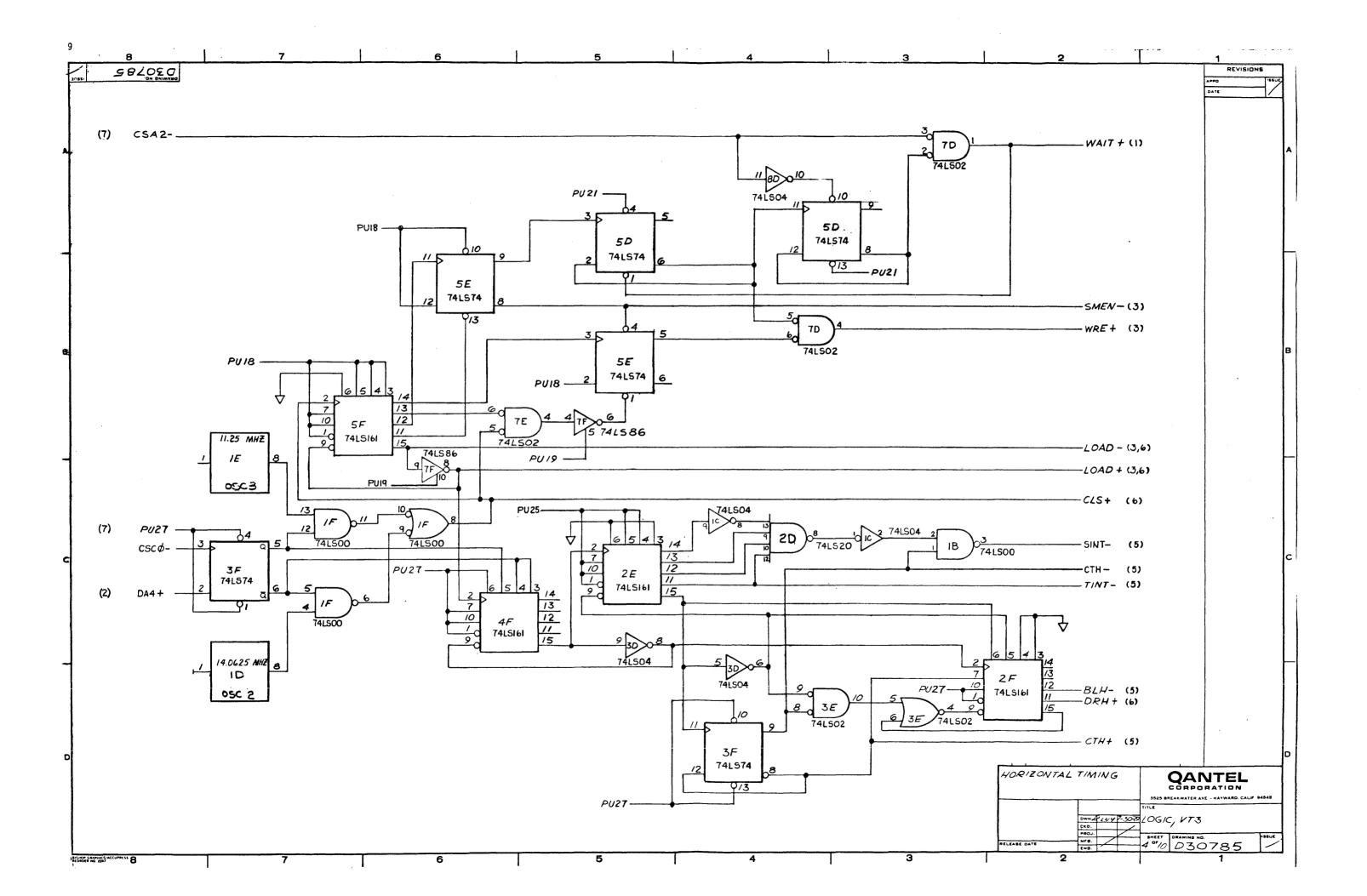

EXPLANATION OF THE LOGIC DRAWINGS - SHEET 4 HORIZONTAL TIMING

All video operation depends on the synchronizing of a dot pattern, produced by the character generator network, with the movement of an electron beam across the face of the video monitor. Thus, the horizontal timing must not only send out a horizontal drive signal to the video monitor and a similarly derived vertical drive signal; but must tell the control logic hardware when characters are to be loaded, what the dot clock rate should be, when Scan and Timer Interrupts should occur, when the Z-80 is clear to load new data into the Display RAM without interfering with Scan Logic, and where blanking periods should take place.

The scanning rate of the video screen electron beam is constant for a given input voltage to the VT3. Obviously, if 80 characters are going to be compressed into a horizontal row rather than 64 characters, the dot clock must operate at a faster frequency and the LOAD+ signal, which draws characters out of Display RAM, must be faster. This is the purpose of flip-flop 3F - to select one of two crystal oscillators to regulate timing of these factors.

The Z-80 activates CSC0 by performing an I/O function to I/O Port \$80. Outputting DA4+ high, when CSC0 clocks sets flipflop 3F. The Q output will thus be high allowing AND-gate 1F to channel the upper crystal oscillator output (1E) through to the horizontal timing network. The CLST (dot clock) will, therefore, become 11.25 MHz. The Q output also goes to 74LS161, a parallel-loading 4-bit counter, presetting it to \$C. This adapts the rest of the timing chain to the requirements of a 64 character per line screen format.

#### HORIZONTAL TIMING CONTINUED

TINT- and SINT- are routed to the clock inputs of two flip-flops seen on Sheet 5, used to regulate the intervals that the Timer Interrupt and the Scan Interrupt occur. TINT- is generated every 32 microseconds, but the actual Interrupt to the Z-80occurs less frequently as controlled by the data input pin 2 of flip-flop 2C (see Sheet 5). SINT- invariably results in an Interrupt to the Z-80 each 64 microseconds (the data input at pin 12 of 2C is held low).

CTH+ (Count Horizontal) produces a positive-going pulse for each horizontal raster row (15.625 KHz) and provides the primary clock for the vertical timing chain.

The BLH- (Horizontal Blanking) and DRH+ (Horizontal Drive) signals are created by 4-bit counter 2F. As the pin 15 carry-out of counter 4F goes low, counter 2F is clocked. When counter 2E carry out is active, counter 2F is preset to \$8, counts to \$F causing the carry-out at pin 15 to load a preset value of \$4. By a count of \$5, CTH+ goes inactive and disables counter 2F. Horizontal Blanking (BLH-) occurs at pin 12, Horizontal Drive at pin 11. See the timing chart, figure , for details.

If an 80 character per line format is selected, by the Z-80 pulling DA4+ low with CSC0, the bottom oscillator, 1D, is channeled through AND-gate 1F. The dot clock in this case becomes 14.0625 MHz. LOAD+ occurs at a faster rate and counter 4F is preset with a \$B, thus changing the timing relationship of the rest of the chain to ensure that BLH-, DRH+, and CTH+ are the same as with 64 C.P.L. format.

Fig. 3 HORIZONTAL TIMING

CSA2-, seen at the top of the sheet, is activated whenever the Z-8 $\emptyset$  tries to access address \$2 $\emptyset$  $\emptyset$  $\emptyset$  through \$27FF (the Display RAM). The factors allowing the Z-8 $\emptyset$  to access the Display RAM are as follows.

SMEN- must be inactive - the output of flip-flop 5E pin 8 high. WAIT+ is set in response to CSA2- and flip-flop 5D pin 8 going low as that flip-flop is set. WAIT+ being active removes the reset to Pin 1 of flip-flop 5D which then can set at a positive clock from 5E pin 9. The ANDing of 5D pin 6 and 5E pin 5 produces the WRE+ signal. WRE+ routes data into (or out of) the Display RAM through the appropriate Octal Latch to the address

I–17

### HORIZONTAL TIMING CONTINUED

multiplexed off the Address lines (as permitted by SMEN- high). Pin 6 of flip-flop 5D will go high as the timing chain continues, thus clocking 5D pin 8 to a reset condition. The resulting high from pin 8 removes the WAIT+ condition to the Z-80. CSA2- will be dropped, once again setting flip-flop 5D pin 9.

HORIZONTAL TIMING

Fig. 4

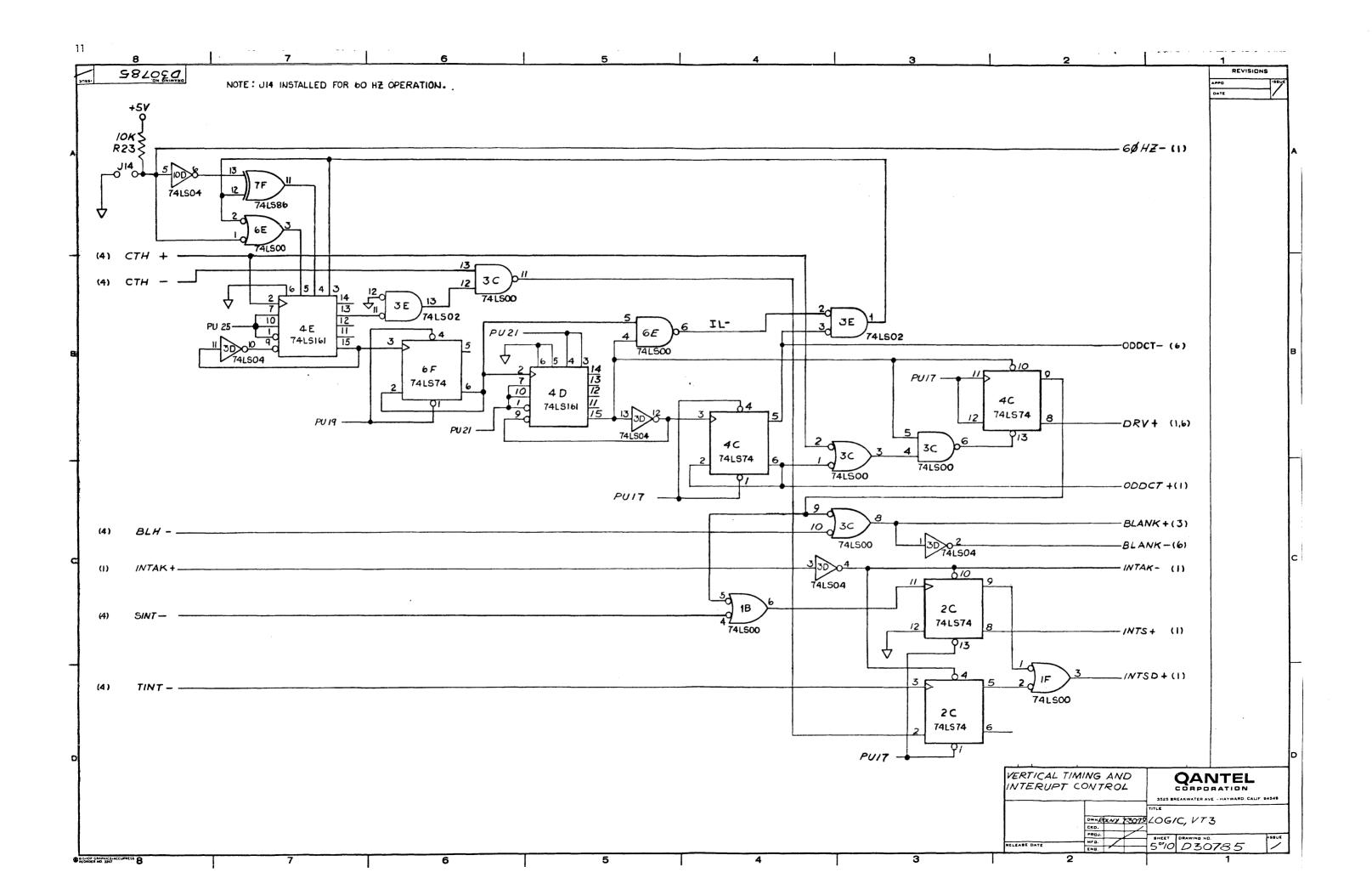

EXPLANATION OF THE LOGIC DRAWINGS - SHEET 5 VERTICAL TIMING AND INTERRUPT CONTROL

The signal CTH+, derived from the horizontal timing chain and oscillating at 15,625 Hertz, is the basis for all vertical timing chain activity. CTH+ clocks the 4-bit counter 4E. The value preset into 4E is dependent on the state of jumper J14, the 50 or 60 Hz select, seen in the upper left of the sheet. The IL- (Initial Load) signal is also a component of the preset to 4E, occurring once for the first horizontal scan frame.

Notice that the signal 60Hz is accessible to the Z-80 (see Sheet 1) through Tri-State Buffer 7B.

Thus, the three primary elements of the vertical timing network, 4-bit counters 4D and 4E, and flip-flop 6F, tailor the vertical drive signal to the monitor, DRV+, by counting a specific number of horizontal scans to fit within the frame rate. With 60Hz selected (the timer counts 59.98 Hz at this rate), 260.5 horizontal scans appear per 1 frame. At 50Hz, 312.5 horizontal scans appear per frame. The vertical timing diagram, figure 5, illustrates the relationship of these signals.

ODDCT- (Odd Count) is produced to mark the sequence of the interface pattern sent to the video screen. A complete frame requires two complete Vertical Drives, one to display the even horizontal scan rows; one to display the odd. ODDCT- is directed to the slice counter, 4-bit counter 9E on Sheet 6, and becomes a part of the address to the Character ROM to select an odd or an even slice. The reciprocal of this signal, ODDCT+, is sent to Tri-State Buffer 7B (seen on Sheet 1) to cue the Z-80 to whether an odd or an even scan is in progress.

#### VERTICAL TIMING AND INTERRUPT CONTROL CONTINUED

The signals BLANK+ and BLANK- are created to inhibit the video output to the monitor during horizontal retrace or vertical retrace periods. Notice that BLH- (Blanking Horizontal) and the complement to the Drive Vertical signal (4C pin 9) are ORed at 3C to ensure the video is inhibited in both instances. BLANK+ is routed to the Scan RAM Address Counter to prevent counting during blanking periods. BLANK- is sent to the Character Generator network (Sheet 6) as the actual video inhibit signal.

At periodic intervals in the timing cycle, two maskable interrupts to the Z-80 occur. Flip-flop 2C regulates the incidence and the nature (timer or scan interrupt) of these interrupts.

The Scan Interrupt has a higher priority - the Z-80 must be notified at the end of each horizontal scan to load an address for the next scan row. A Scan Interrupt occurs every 64 microseconds - before each horizontal and vertical retrace. SINT- (Scan Interrupt) from the horizontal timing network or the Vertical Drive Flip-flop (4C pin 9) clock 2C pin 9 low to generate the signal INTSD+ to the Z-80, which simultaneously sets 2C pin 8 high identifying it as a Scan Interrupt.

A Timer Interrupt occurs less frequently, roughly every 256 microseconds, and is a cue for the Z-80 to check the UART for transmit or receive activity. Z-80 Interrupts are enabled as soon as a Timer Interrupt is recognized to allow the higher priority Scan Interrupt to take place if necessary. The clock for Timer Interrupt also comes from Horizontal Timing at the rate of once per 32 microseconds. However, notice the origin of the data input, 2C pin 2. The signal CTH- and the B output of counter 4E are ANDed at 3C. Since 4E counts

#### VERTICAL TIMING AND INTERRUPT CONTROL CONTINUED

intervals which vary according to its preset value, the data input 2C pin 2 will be active at varying intervals ranging from 64 to 320 microseconds. Identity of a Timer Interrupt is based on the fact 2C pin 8 will be low. The Z-80 responds to its Interrupt line being pulled by checking Tri-State Buffer 7B. The INTS+ line will create a value of \$FF for Scan Interrupt; \$CF for a Timer Interrupt. The Z-80 issues INTAK to read the buffer; the inversion of this signal sets both sides of 2C, clearing INTSD+.

Fig. 5

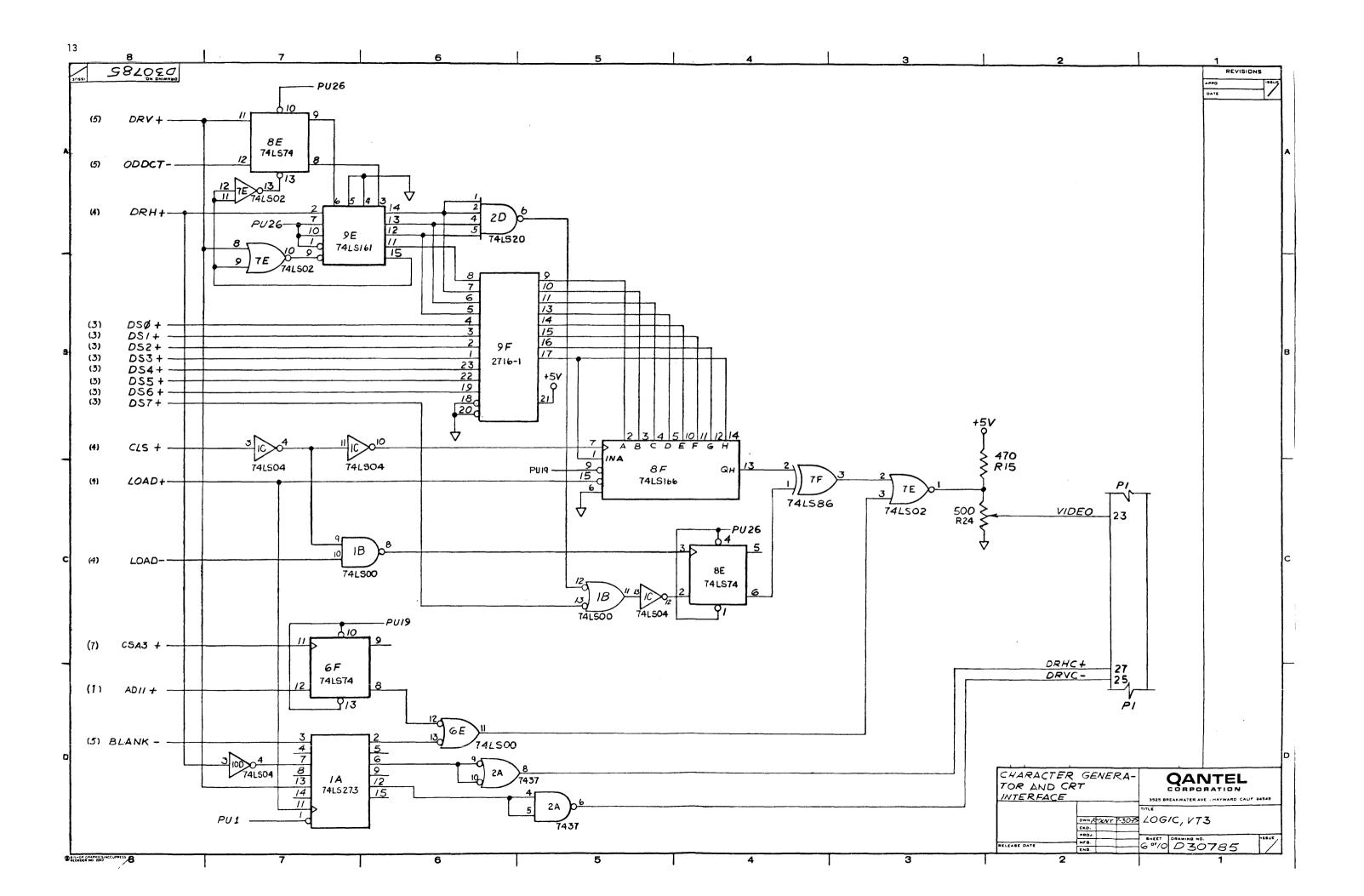

# EXPLANATION OF THE LOGIC DRAWINGS - SHEET 6 CHARACTER GENERATOR AND CRT INTERFACE

The ASCII values from the Display RAM are converted to dot patterns synchronized with the horizontal and vertical timing signals. The Character ROM, 9F, receives the ASCII value on the Display Bus and raster row orientation from the Slice Counter 9E. The resulting 8-bit "slice" of visual character information is loaded into a shift register in parallel form, and shifted out serially at the Dot Clock rate. The ninth bit of the slice comes from the DS pin input (pin 1).

To maintain a valid raster row address, Slice Counter 9E receives the signals DRV+ (Vertical Drive), ODDCT- (Odd Count), and DRH+ (Horizontal Drive). The Slice Counter is preset to 1 initially, but the outputs are wired to the Character ROM address inputs in a manner to simulate counting by two's.

DRV+ clocks the value of ODDCT- into flip-flop 4E, thus resulting in an \$8 being loaded into counter 9E for the first scan of every other frame. The Slice Counter appears to count by two's because of the configuration of its outputs with the Character ROM address inputs. 9E pin 11 (D output) connects with the low order ROM address input. Pins 14, 13, 12 (A, B, C) of 9E connect with the next significant address inputs. This causes the interlacing of the alternate line to occur. With a \$1 preset into it, the Slice Counter will present a '2' to the address inputs. The next horizontal slice. triggered by DRH+, clocks the Slice Counter to '4'. Counting continues... 6, 8, A, C, E ... until the completion of one character row triggers the loading of a '2' to start a fresh character row. With flip-flop 8E changing with the next DRV+ clock, the Slice Counter receives an '8' preset value and proceeds to count the odd lines... 1, 3, 5, 7, 9, B, D, F of each character row.

I - 22

#### CHARACTER GENERATOR AND CRT INTERFACE CONTINUED

Shift register 8F loads an 8-bit parallel "dot pattern" each time it receives a LOAD+ signal from the horizontal timing network. Additionally, the bit in the eighth position is serially loaded into pin 1, the DS input, where it becomes the first bit in the stream to be serially clocked out. Thus, dots in the first and ninth position of each character slice will be identically displayed.

Two signals ORed provide the data input to the Inverse Video Flip-Flop. DS7+, the uppermost bit of the character information word, is one of these signals. The other is derived from the A, B, and C outputs of the Slice Counter, ANDed at 2D so that a count of 14 or 15 produces the active low output. The inverse video function is a result of a high 'not Q' output from 8E applied to exclusive-OR gate 7F. This effectively inverts the video signal, turning highs to lows and lows to highs.

The CRT's video brightness is adjusted by R24, the potentiometer at the rear of the pedestal base.

Flip-flop 6F is set by the Z-8Ø accessing memory location \$38XX (creating the decoded CSA3+ clock and making data input AD11+ high). This flip-flop controls blanking, a low from pin 8 inhibits all video signals to the monitor. The signal BLANK- from the Vertical Timing network also inhibits the video during horizontal and vertical retrace times.

Junction P1 illustrates the interface with the video monitor circuitry. The monitor converts the DRHC+ and DRVC- signals into sawtooth waves driving the yokes to regulate the motion of the CRT's electron beam. The video signal determines

#### CHARACTER GENERATOR AND CRT INTERFACE CONTINUED

which dot positions will be illuminated during scanning to produce the displayed characters and graphics.

#### INTERLACED CHARACTER SLICES

Fig. 6

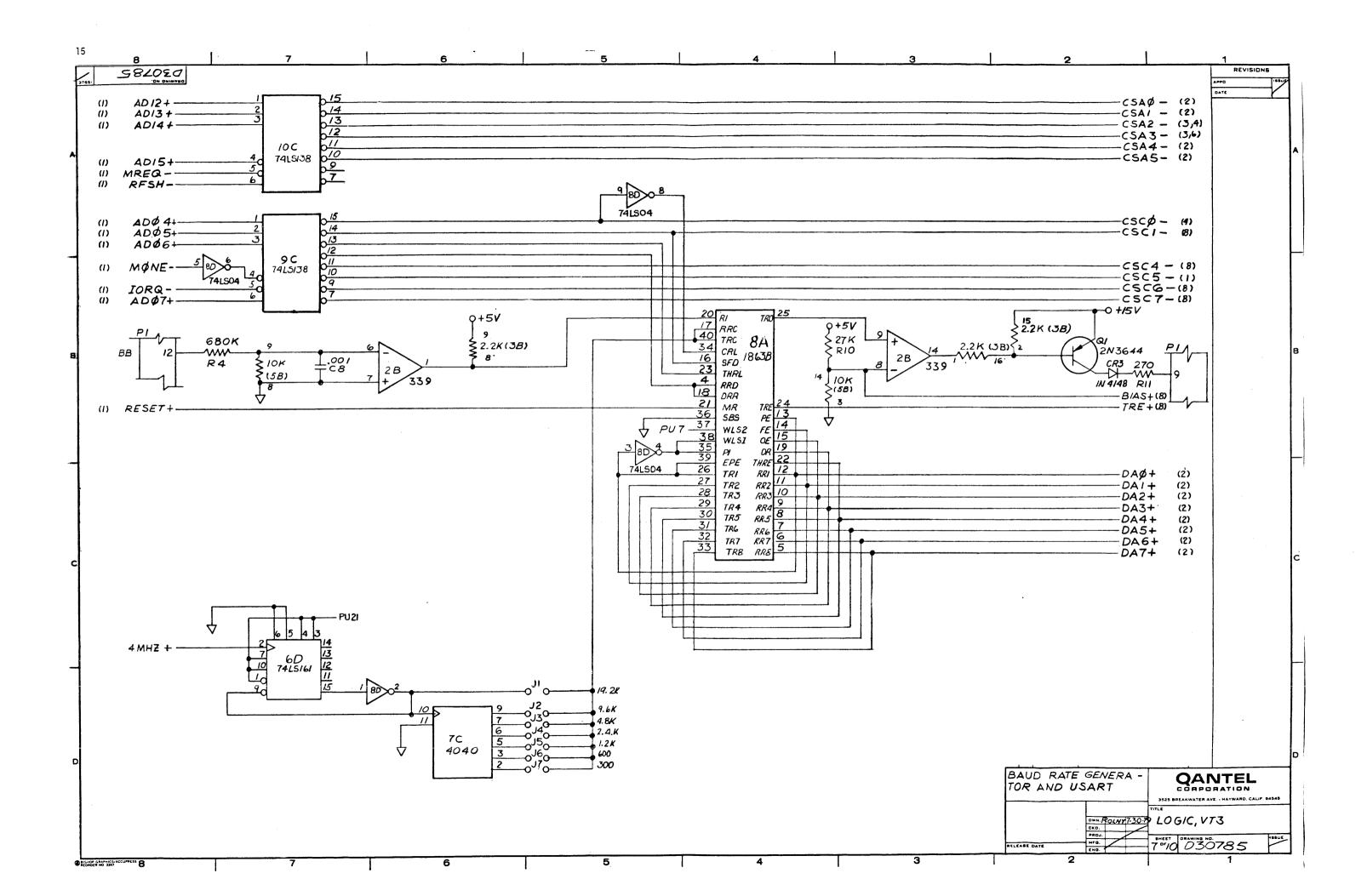

EXPLANATION OF THE LOGIC DRAWINGS - SHEET 7 BAUD RATE GENERATOR AND UART

The UART (Universal Asynchronous Receiver-Transmitter) links the VT3 to the serial communications line, interfacing an IOU-39Q controller which contains an identical UART at its communication line junction. At turn on, the RESET+ pulse activates the UART's Master Reset. The microprogram then dictates the parameters of UART operation by sending out a control word selecting number of data bits and type of parity to be used.

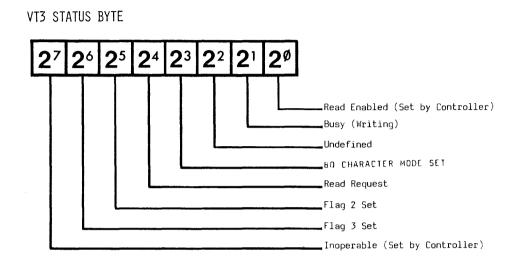

It is through the UART that the Z-80 becomes aware of communication line activity. By issuing an IN90 Input/Output instruction, the Z-80 receives the contents of the UART's status register. Information conveyed includes presence of data in the Receive Register (Service Request), Transmit Holding Register cleared (Ready for Transmitting Data), Transmit Register empty (Data Transmitted), Clear to Send, and error notification. See the Appendix for the actual bit map of this status word. An IN90 also cues the Z-80 to the state of the 64 / 80 character per line jumper (J13) by enabling the buffer 5A on Sheet 8.

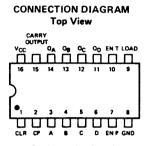

The baud rate is selectable through the group of jumpers J1 -J7 in the lower left portion of the sheet. The 4MHz clock signal channelled into 4-bit counter 6D's clock input produces a Pin 15 Carryout frequency of 307.7 KHz. Since the UART clock input responds with one receiver shift pulse for every 16 received cycles, this corresponds to a baud rate of 19.2K. For lower baud rates, the selection of J2 - J7 connects the outputs of 12-bit ripple counter 7C to the UART's clock input.

Within the B8 grid on the sheet, the interface with the

#### BAUD RATE GENERATOR AND UART CONTINUED

communication lines at connector P1 is shown. Incoming data at RS-232-C levels (+12, -12 volts) is translated to TTL levels (+5, 0 volts) by the circuit surrounding comparator 2B. The data is then serially shifted into the UART's Receive Register utilizing the predetermined format of stop bits, character length, parity, and baud rate. Data being transmitted out the UART's Transmit Register undergoes the reverse of this operation. TTL levels from Pin 25 of the UART are translated to RS-232-C levels by the comparator circuit and channelled to the communication line through Pin 9 of connector P1.

The Appendix contains a list of pin descriptions further detailing UART operation.

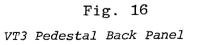

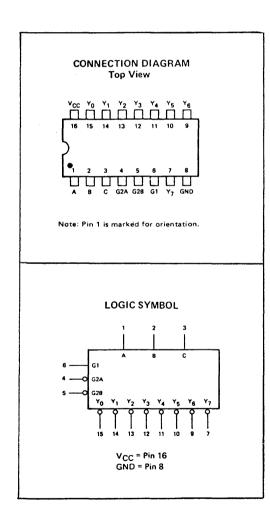

Two octal decoders, 9C and 10C, using 8 address lines and 4 Z-8Ø control lines, create the chip select signals to steer addresses and data to proper destinations on the control logic board. The following diagram details the nature of the chip selects. Note that Decoder 10C is used for memory decoding; Decoder 9C is used for input/output decoding.

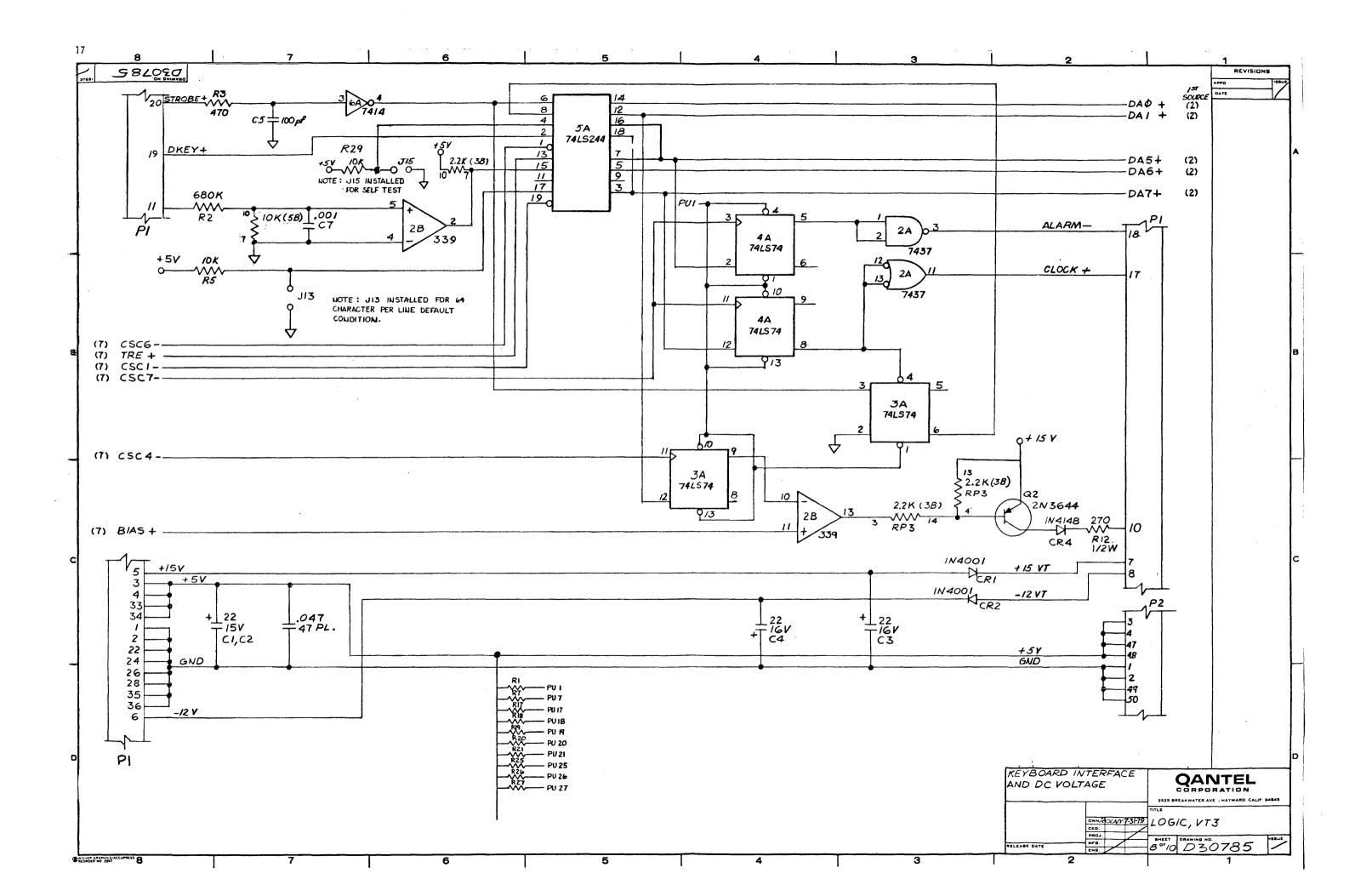

## EXPLANATION OF THE LOGIC DRAWINGS - SHEET 8 KEYBOARD INTERFACE AND DC VOLTAGE

The Tri-State Buffer 5A has two individual sections consisting of four input-outputs. By activating one of the two chip selects, the Z-8 $\emptyset$  accesses the desired lines obtaining information about keyboard activities (CSC6-) or status of the UART (CSC1-).

The top portion of the buffer, as illustrated, allows the Z-8 $\emptyset$  to read the New Key Pressed Latch (3A), the STROBE+ signal, and the DKEY+ line where character information bits are clocked in from the keyboard. STROBE+ becomes active whenever the operator depresses a key. This signal also clocks in the tied-low data line (Pin 2) of Flip-flop 3A, the New Key Pressed Latch. Pin 6 of this flip-flop is tied around to the input of buffer 5A for reading by the Z-8 $\emptyset$ .

Repeat keys are detected when STROBE+ and the New Key Pressed Latch remain active beyond a specified time. The  $Z-8\emptyset$  will, in such an instance, enter the keyboard repeat routine.

Character information bits are clocked in the DKEY+ line by the Z-8 $\emptyset$  toggling the Clock Latch 4A. Pin 11 is clocked by CSC7- while the Data input, Pin 12, is varied by the Z-8 $\emptyset$ manipulating DA7+ (seen at 1A on the sheet).

Flip-flop 4A also contains the elements of the ALARM latch. CSC7- provides the clock to pin 3 while DA5+ provides the Data input to Pin 2. With ALARM activated, a 3.5 KHz signal is generated on the keyboard circuit board to sound the audio speaker. The ALARM latch is reset by the Z-80 microprogram after approximately  $\frac{1}{4}$  of a second, stopping the speaker tone.

#### KEYBOARD INTERFACE AND DC VOLTAGE CONTINUED

The Z-80 notifies the controller of data ready to be transmitted over the communication line by setting Request to Send to the modem. Chip select CSC4- clocks pin 11 of Flip-flop 3A while DA1+ is high to accomplish this. A driver network converts the TTL output of 3A to RS-232-C levels.

The bottom third of the sheet illustrates the diode isolated +15 volt and -12 volt levels which connect with the external terminator shoe. The +5V and Ground connections between P1 and P2 are also illustrated.

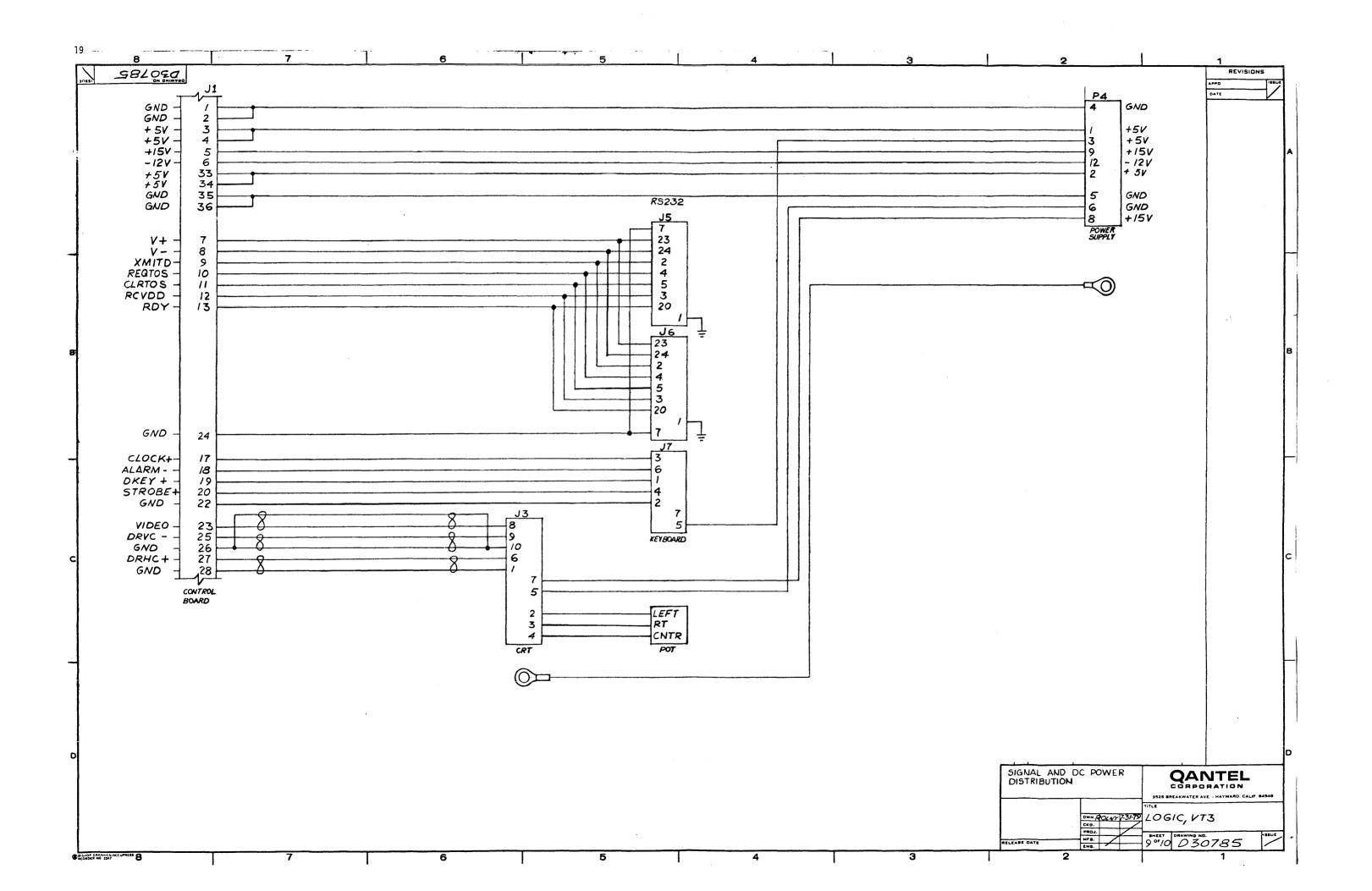

# EXPLANATION OF THE LOGIC DRAWINGS - Sheet 9 SIGNAL AND DC POWER DISTRIBUTION

The logic control board fingers at P1 plug into junction J1 illustrated at the left hand side of Sheet 9. The interconnections between elements of the VT-3 are shown on this page.

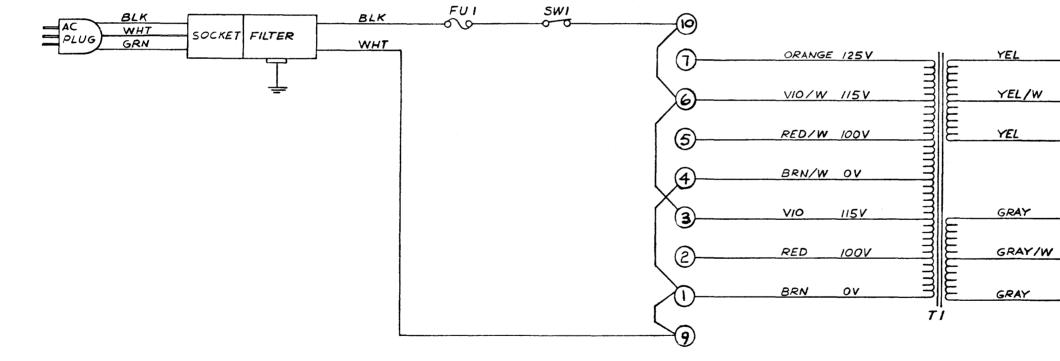

# EXPLANATION OF THE LOGIC DRAWINGS - Sheet 10 TRANSFORMER AND WIRING DIAGRAMS

Sheet 10 illustrates the AC power input as fed to the transformer terminal strip. To accomodate the various possible input voltages (100, 115, 215, 230, 240), the jumper wires to the terminal strip must be placed according to the table on the sheet.

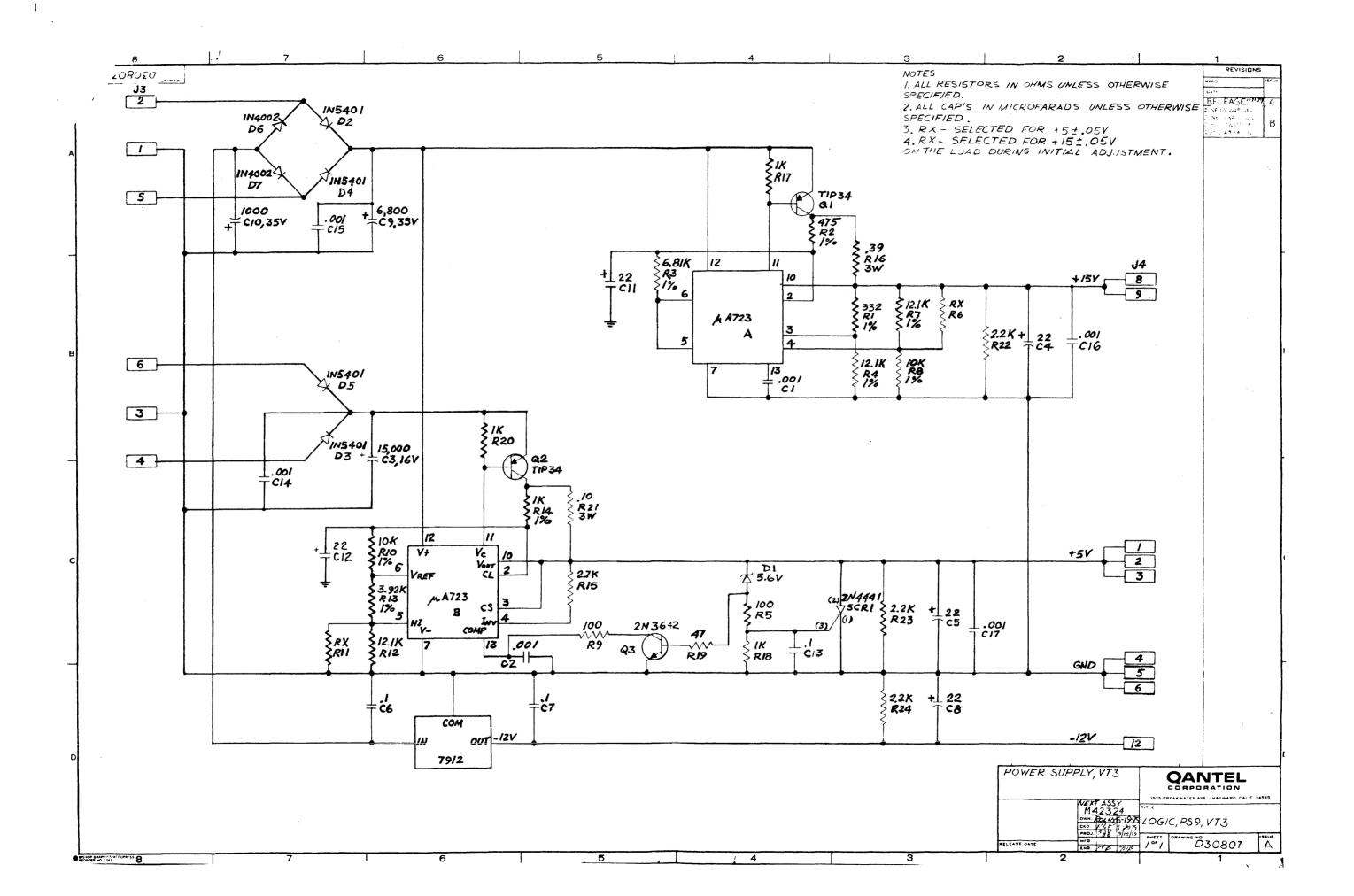

#### PS-9 POWER SUPPLY

The PS-9 functions as a normal, linear power supply within the VT3, providing three DC outputs: +5 volts (3.0 amps); +15 volts (1.5 amps); and -12 volts (.05 amps). Physically, it consists of a printed circuit board and a transformer, both residing within the pedestal base of the VT3.

Input voltages are variable and selected through connections made to the terminal strip of the transformer. Refer to Sheet 10 of the Logic Drawings for configuration of the winding points. Operation is regulated at the expressed voltages between 47 and 63 Hz.

Output voltages are variable by altering the value of the adjustment resistor corresponding to the specific DC output. Outputs when tested should comply to the following parameters.

|      | Minimum | Maximum | Adjusted by |

|------|---------|---------|-------------|

| +5V  | 4.75    | . 5.25  | R11         |

| +15V | 14.85   | . 15.15 | R6          |

| -12V | -10.8   | 13.2    | Fixed       |

Specific procedures for selecting resistor values are detailed in Qantel Document #A30903.

Overvoltage protection is provided on the +5 VDC output, dropping the voltage output to  $\emptyset$  V if the value reaches 5.8 VDC. Each output line is equipped with current protection -- the +5V and +15V to 120% of full load; the -12V to 400% of full load.

Pin designations for J3 and J4 follow.

I - 30

#### PS-9 POWER SUPPLY CONTINUED

| Sign | nal           | Color            | Pin |

|------|---------------|------------------|-----|

| 16V  | SEC           | Yellow           | 4   |

| 16V  | SEC           | Yellow           | 6   |

| 16V  | Center<br>Tap | Yellow/<br>White | 3   |

| 34V  | SEC           | Gray             | 5   |

| 34V  | SEC           | Gray             | 2   |

| 34V  | Center<br>Tap | Gray/<br>White   | 1   |

| Signal | Pin |  |

|--------|-----|--|

| +5VDC  | 1   |  |

| +5VDC  | 2   |  |

| +5VDC  | 3   |  |

| GND    | 4   |  |

| GND    | 5   |  |

| GND    | 6   |  |

| +15VDC | 8   |  |

| +15VDC | 9   |  |

| -12VDC | 12  |  |

#### VT3 DOCUMENTS

| A30694 | IOU-39 Design Specification              |

|--------|------------------------------------------|

| A30730 | IOU-39Q Design Specification             |

| A30786 | VT3 Functional Specification             |

| A30809 | PS-9 Design Specification                |

| A30822 | Qantel Standard Protocol                 |

| A30880 | VT3/QSP Driver Specification             |

| A30901 | Character Set Dot Matrix: ASCII          |

| A30902 | Character Set Dot Matrix: Kana           |

| A30903 | PS-9 Test Procedures/Theory of Operation |

| A30917 | Character Set Dot Matrix: Swedish        |

| A30935 | IOU-39Q Cabling                          |

| A31022 | VT3 Test Procedures                      |

| A31023 | VT3 Control Logic                        |

| D30785 | VT3 Logic Drawings                       |

| D30807 | PS-9 Logic Drawings                      |

| F30730 | IOU-39Q Functional Specifications        |

| F30786 | VT3 Firmware                             |

| L30730 | IOU-39Q Microcode Listing                |

| L30786 | VT3 Microcode Listing                    |

|        |                                          |

#### IC LISTING FOR THE VT3

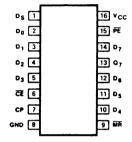

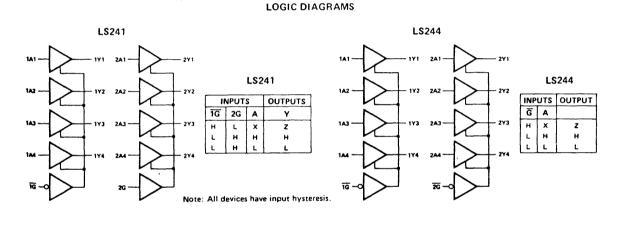

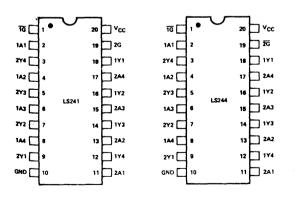

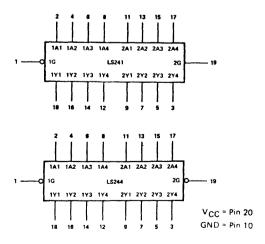

1863B..... Receiver-Transmitter 2114-2.....1K X 4 bit RAM 2716-1.....16K Erasable Programmable Read-Only Memorv 4040.....12-Bit Ripple Counter 74LSØØ.....2-Input NAND gate 74LS74.....Dual-D Flip-Flop 74LS138.....Octal Decoder 74LS158.....Quad 2-Input Data Selector/Multiplexer 74LS166.....PI-SO/ SI-SO, 8-Bit Shift Register 74LS193..... Up/Down Counter 74LS244.....Octal Bus Buffer, Non-Inverting Tri-State 74LS273.....Octal D-Type Flip-Flop 74LS373.....Octal Latch with Tri-State Output CM2000.....Crystal Oscillator Z-8ØA.....Microprocessor

# **Operational** Description

DISPLAY SCREEN

The character sets, English and KANA, illustrated in the Appendix demonstrate the range of VT3's display capabilities. Most of these characters are available to the keyboard operator; however, the graphic symbols (shown as \$10 through 1F) may be entered only through a Write from the main CPU.

The actual display presented on the CRT is subject to a number of variables. Display format, field parameters, cursor position, transmit marks, data display, and other elements are structured in ways discussed in the following section.

The aspect ratio of the display screen, the number of lines by the number of characters per line, varies according to two considerations. A jumper switch, J13, sets screen format at turnon or reset to 27 lines by 64 characters (1728 display characters) or 24 lines by 80 characters (1920 display characters). This switch-selected format may be changed by computer command at any time.

Characters stored in the Display RAM fit within set classifications. Foreground characters appear on the screen as positive, green on black, images. Background characters appear on the screen as negative, black on green, images. Suppressed background characters are represented by foreground spaces. Within the Display RAM, certain control information is stored in the locations seen as suppressed background characters.

Fields further define data display, offering boundaries within which characters may be entered. A normal field is distinguished by a lack of any special background character before it. It may encompass any area of the screen not limited by background or suppressed background characters.

II-1

#### DISPLAY SCREEN CONTINUED

A Right-justified field follows an \$0B. Only numeric characters may be entered into it, including one decimal and one minus sign. To the operator at the keyboard, data being entered occurs at the far right portion of the screen, and shifts to the left as additional data is entered.

Kana fields are available with the Japanese VT3. A \$OF preceding provides identification in the Display RAM.

The main CPU conditions the Display Screen as is appropriate to the User Program being utilized by writing background areas. The operator cannot enter data into these areas. They generally contain information structuring data entry into foreground fields.

The cursor is a blinking character notifying the operator of the location of the next position for data entry. The cursor skips over any background areas as it proceeds left to right a space at a time across the display screen. During rightjustified entry, however, the cursor remains stationary, marking the righthand point at which new data will appear before being shifted right.

The cursor is not displayed during Blind Entry Mode, a method by which the operator may enter password information without displaying it on the screen. 32 characters may be entered in this mode. Read Request to the main CPU is set by TAB, RETURN, or TRANSMIT through the used of Transmit Stop characters at both ends of the blind buffer. Following password entry and main CPU recognition, the cursor is positioned in the first foreground field on the display screen.

II-2

#### DISPLAY SCREEN CONTINUED

The control line occupies the last line of the display screen; the 28th line of a 64 character per line screen or the 25th line of the 80 character per line screen (a line is skipped following the 24th line). The control line is used for system messages. Flag 2 and Flag 3 states are stored as the first 6 characters of the control line. Information used in test sequences is also stored within this line.

#### CONTROL CODES RECOGNIZED BY THE VT3

| CODE   | CHARACTER                     | DESCRIPTION                                                                                                                                                                                                                                                                |

|--------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00     | Null                          | Ignored, except causes write initialization.                                                                                                                                                                                                                               |

| 01xxyy | Set Cursor                    | Causes the terminal to place the cursor at the Row xx, Column yy; xx between 1 and 27 (24),<br>yy between 0 and 63 (79).                                                                                                                                                   |

| 04     | Escape                        | Escape - next character is a control character.                                                                                                                                                                                                                            |

| 0401   | Remember Cursor               | Saves current value of cursor for Restore Cursor command(09).                                                                                                                                                                                                              |

| 0402   | Select 64                     | Sets the display mode to 64 characters per line and 27 lines. The screen is cleared to blanks and the cursor is positioned to home (or the 27th line if typewriter mode).                                                                                                  |

| 0403   | Select 80                     | Sets the display mode to 80 characters per line and 24 lines. The screen is cleared to blanks and the cursor is positioned to home (or the $24$ th line if typewriter mode).                                                                                               |

| 0404   | Select Default                | Sets either the 64 or 80 character display mode depending on the hardware default switch.<br>The screen is cleared to blanks and the cursor is positioned to home (or the last line<br>if typewriter mode).                                                                |

| 0405   | Set Blind Entry               | Clears the 32-byte blind buffer to blanks. At the completion of the write, the cursor is positioned to the beginning of the blind buffer.                                                                                                                                  |

| 0406   | Blank Fill Line               | Replaces all characters from cursor position to end of line with blanks (foreground, back-<br>ground, or suppressed-background). Positions cursor to beginning of next line (or home).                                                                                     |

| 0407   | Clear Field                   | Replaces all characters in field where cursor resides with foreground blanks. Positions cursor to first entry in field (right-most position if RJ field).                                                                                                                  |

| 0408   | Force Transmit                | Causes the VT3 to set 'Read Request'. The VT3 acts as if the operator pressed TRANSMIT after the completion of the Write.                                                                                                                                                  |

| 0409   | Transmit Stop                 | Stored on the screen as a suppressed background character. When the operator presses TAB<br>or RETURN and the cursor advances past a Transmit Stop, the VT3 posts Read Request. In<br>addition SHIFT/TAB and SHIFT/RETURN will not back up over a Transmit Stop character. |

| 040A   | Rollup                        | Moves the screen portion below the cursor line up one line. The cursor line is lost; blank foreground is inserted at the bottom. The cursor is positioned to the beginning of the bottom line. The control line is not affected.                                           |

| 040B   | Roll Down                     | Moves the screen portion below the cursor line down one line. The cursor line is lost. A<br>blank foreground line is inserted at the cursor line. The cursor is positioned to the be-<br>ginning of the current line. The control line is not affected.                    |

| 0400   | Set Suppressed-<br>Background | Causes terminal to accept subsequent data characters as suppressed-background (displayed as spaces).                                                                                                                                                                       |

| 05     | Clear Screen                  | Clears the screen to foreground blanks and positions the cursor to home. The control line is not affected.                                                                                                                                                                 |

#### CONTROL CODES CONTINUED

| CODE | CHARACTER               | DESCRIPTION                                                                                                                                                                                                                                                                                 |

|------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06   | Clear Foreground        | Clears all foreground positions on screen to blanks and positions cursor to first fore-<br>ground position on screen. The control line is not affected.                                                                                                                                     |

| 07   | Alarm                   | Causes audible alarm to sound.                                                                                                                                                                                                                                                              |

| 08   | Set Background          | Causes terminal to accept subsequent characters as background (displayed as black on green).                                                                                                                                                                                                |

| 09   | Restore Cursor          | Positions the cursor to the position it occupied at the start of the write or to the last<br>'remembered' cursor location.                                                                                                                                                                  |

| 0A   | Set Foreground          | Causes terminal to accept subsequent characters as foreground (displayed as green on black).                                                                                                                                                                                                |

| 0B   | Right-Justified         | When placed as the character immediately preceding a foreground field, it designates the field to be right-justified. It is stored on the screen as suppressed-background.                                                                                                                  |

| 00   | Transmit<br>Mark        | Stored on screen as suppressed-background. When the operator presses TAB or RETURN and the cursor advances past a Transmit Delimiter, the VT3 posts Read Request.                                                                                                                           |

| OD   | Cursor Return           | Causes terminal to position cursor to beginning of the next line on screen (or home).                                                                                                                                                                                                       |

| 0E   | Escape                  | Next character is control character.                                                                                                                                                                                                                                                        |

| 0E02 | Reset F2                | Resets Flag 2.                                                                                                                                                                                                                                                                              |

| 0E03 | Reset F3                | Resets Flag 3.                                                                                                                                                                                                                                                                              |

| 0E04 | Reset F2 & F3           | Resets Flag 2 and Flag 3.                                                                                                                                                                                                                                                                   |

| 0E05 | Enter Typewriter        | Sets typewriter mode for writing.                                                                                                                                                                                                                                                           |

| 0E06 | Enter Normal Mode       | Sets normal mode. Clears typewriter mode.                                                                                                                                                                                                                                                   |

| 0E07 | Write Control Line      | Clears the control line to blanks. Subsequent data is written to the control line.                                                                                                                                                                                                          |

| OEOF | Execute Test<br>Program | The remainder of the data is used as a Z80 program to execute. Use a RETURN to exit the program.                                                                                                                                                                                            |

| OF   | Kana Field              | On English systems it is ignored except as a screen place-holder. On Kana systems it<br>causes the field to be declared a Kana field. Characters from the keyboard are interpreted<br>as being in Kana mode until the 'ALPHA MODE' key is pressed or the cursor is moved to a new<br>field. |

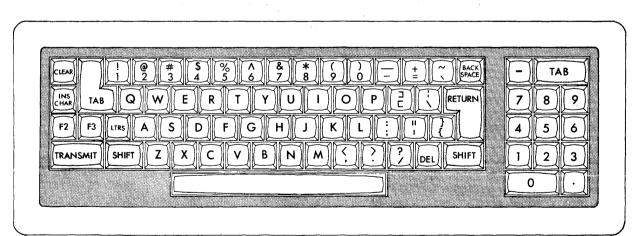

#### VT3 KEYBOARD

#### KEYBOARD

73 momentary contact keys with N-key rollover are incorporated into the VT3 keyboard. Repeat capabilities are possible with some keys and any character key may be repeated if preceded by simultaneously depressing SHIFT and the decimal point key on the numeric cluster. Control keys provide a means for editing (BACKSPACE, CLEAR, and INS CHAR) and data capture when entry is complete (TRANSMIT, TAB, and RETURN). Two flag states, stored in flip-flops, are provided to allow the main CPU to initiate escape sequences: FLAG 2 (F2) and FLAG 3 (F3). Following turn-on or reset, all alphabetic characters will be uppercase; depressing LTRS allows control of upper and lowercase generation. The SHIFT key alters the control function of several keys as shown in the following description:

| CONTROL KEY | NORMAL FUNCTION                                                                                                                                                                                                                     | WITH SHIFT                                                                                                                                                                                                                                                                |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BACKSPACE   | Moves cursor one position left. Stops at<br>first foreground in field or at beginning of<br>screen. In right-justified (RJ) fields it<br>removes the last number entered and shifts<br>the remaining characters one position right. | Moves cursor one position right. Stops<br>at last foreground in screen. Illegal in<br>RJ fields.                                                                                                                                                                          |

| TAB         | Moves cursor to beginning of next foreground<br>field (may be several lines or less than one<br>line). Sets "Read Request" at end of screen<br>or transmission delimiter (Transmit Mark or<br>Transmit Stop).                       | Moves cursor to beginning of present<br>foreground field, or if already there (or<br>RJ field), to beginning of previous fore-<br>ground field. Will not pass beginning of<br>screen or Transmit Stop character.                                                          |

| INS CHAR    | Inserts blank character at cursor position<br>and shifts all characters to the end of the<br>field one position right. The last charac-<br>ter is lost. Illegal in RJ fields.                                                       | Deletes character at cursor position and<br>shifts all characters to the right of the<br>cursor in the same field, one to the left.<br>A blank is inserted at the end of the field.<br>Illegal in RJ field.                                                               |

| CLEAR       | Replaces all characters in field where cur-<br>sor resides with blanks. Cursor is posi-<br>tioned to normal position of first entry<br>in field (left if normal, right if RJ).                                                      | Clears foreground. Resets all foreground<br>characters on the screen to blanks. Cur-<br>sor is positioned to first foreground field<br>on screen. In blind entry mode, it acts<br>like CLEAR.                                                                             |

| RETURN      | Moves cursor to first foreground position<br>after end of line. Sets "Read Request" at<br>end of screen or if a transmission delimiter<br>is encountered. If RJ field, same as TAB.                                                 | Moves cursor to first foreground position<br>in line, or if already there, to first fore-<br>ground position on last previous line con-<br>taining foreground. Will not pass the be-<br>ginning of the screen or a Transmit Stop.<br>If RJ field, then same as SHIFT/TAB. |

| F2          | Toggles "Flag 2", a switch tested by the software.                                                                                                                                                                                  | Performs a terminal reset.                                                                                                                                                                                                                                                |

### KEYBOARD CONTINUED

| CONTROL KEY   | NORMAL FUNCT | ION                                                                                                                         | WITH SHIFT                                                                                                                                                                                   |  |  |  |

|---------------|--------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NUHERIC<br>-  | Produces dec | imal point display.                                                                                                         | Starts keyboard repeat mode. The follow-<br>ing key is repeated at a rate of 15 cps as<br>long as it is depressed by the operator.<br>Note that this applies to the numeric cluster<br>only. |  |  |  |

|               |              |                                                                                                                             |                                                                                                                                                                                              |  |  |  |

| ADDITIONAL CO | NTROL KEYS   | FUNCTION                                                                                                                    |                                                                                                                                                                                              |  |  |  |

| TRANSM        | IIT          | Sets "Read Request" in order to transmit data to the computer.                                                              |                                                                                                                                                                                              |  |  |  |

| F3            |              | Toggles "Flag 3". This is used by the operating system as an escape condition to abort the current program.                 |                                                                                                                                                                                              |  |  |  |

| LTRS          |              | Allows upper and lower case alphabetic characters to be entered. When pressed a second time, it restores 'upper case' mode. |                                                                                                                                                                                              |  |  |  |

|               |              | I                                                                                                                           |                                                                                                                                                                                              |  |  |  |

.

#### MICROCODE SUMMARY

It is beyond the scope of this manual to provide a detailed description of the VT3's firmware. Further information, including flowcharts, may be found in Qantel document #F30786 and by studying the actual microcode listing, document # L30786.

This description will cover in a general way the basic processes carried out by the microcode.

The firmware can be examined most easily by reducing the routines to four, logically independent groups.

#### MAIN ROUTINES

Initialization prepares the logic elements (flags, RAM variables, operation modes) to proceed with the program sequence. Main Control Loop monitors for incoming data and branches to routines to process it. Keyboard Processing and Input handles keyboard data arriving as a result of operator input. Write processes data sent from the main CPU. Read turns display screen information into a QSP data stream for sending to the main CPU.

#### **2**SCAN INTERRUPT HANDLER

Provides a new address for each line of the Display RAM to initiate the refresh process of the display screen.

#### **3**TIMER INTERRUPT HANDLER

Provides periodic checking of the communication line, processes QSP data streams, and handles data transmission. **4** TEST PANEL INTERRUPT HANDLER

Handles the input from the Z-80 test panel interface at the P2 junction.

#### INITIALIZATION

Initialization occurs immediately following power on or whenever a reset action is performed. Essentially, initialization is designed to set up program variables (represented by internal Z-80 flags, RAM storage locations, and applicable flip-flops, and other variables) to allow execution of the program from the beginning stage.

The steps during Initialization include the following:

- Z-80 Stack Pointer set to top of stack.

- Maskable Interrupts are disabled.

- Keyboard speaker turned off.

- Request to Send flip-flop cleared.

- Index register IX is set to start of Private RAM (\$4000).

- Private RAM cleared to zeroes.

- Keyboard line accessed for random characters.

- Screen format is set according to jumper J13.

- Display RAM cleared.

- Auxilliary Z-80 registers (which are used for Scan Interrupt information) are prepared for the first scan.

- Terminal Address is read (from control board Address Switches) and stored.

- UART received register cleared.

#### INITIALIZATION CONTINUED

- Receive routine prepared (through RAM variables) to expect

EOT character from communications line.

- Z-80 Interrupt Mode 0 set.

- Maskable Interrupts enabled.

- Main Control Loop entered.

MAIN CONTROL LOOP

The Main Control Loop consists of a very basic sequence. The keyboard is checked to determine if a key has been pressed. If so, the incoming information is processed. If not, the Main Control Loop checks Private RAM to determine if a Write or a Read command has been received from the main CPU. The appropriate branch is carried out. When the necessary operations are completed, the program returns to the start of the Main Control Loop.

#### KEYBOARD ROUTINE

The Keyboard Routine is designed to respond to operator input from the keyboard: each key pressed initiates either a display or a control sequence. The Kinput Subroutine is contained within the Keyboard Routine and is used for recognizing and clocking in serial keyboard data; translating data to ASCII; handling certain control key functions (LTRS, F2, REPEAT); and turning off the audio alarm after a set time.

The essential processes in the Keyboard Routine are:

► Checks the READ PENDING flag in Private RAM.

- If true, call KINPUT searching for the key pressed indication.

- If a key is pressed, the audio alarm is sounded -- keys cannot be processed while the Read Pending is active.

- If false, checks the FORCE TRANSMIT flag (equivalent to the operator pressing TRANSMIT).

►Blinks the cursor.

► Checks for key pressed.

- ► Responds to the type of key by initiating the correct sequence.

- Character keys are processed by entering display sequence.

- Control key functions are carried out.

The setting of the READ PENDING flag results in a READ REQUEST being delivered to the IOU-39Q during its scanning cycle, thus notifying the main CPU that data is available for reading. The operator can cause READ PENDING to be posted in three ways. The most straightforward way is by simply pressing the TRANSMIT key. This causes the program to scan backwards on the display screen. All the intervening data is transferred to the transmission buffer in Private RAM for eventual passage through the communication line.

#### KEYBOARD ROUTINE CONTINUED

TAB and RETURN may also set READ PENDING if they cause the program to encounter a Transmission Delimiter. In such a case, the program sequence acts like the TRANSMIT sequence.

#### KINPUT SUBROUTINE

This subroutine performs the manipulations required to input and process the encoded data from the keyboard. Once a key depression is recognized (through the Buffer 5A on Sheet 8 of the Logics), the character is shifted in a bit at a time by toggling a flipflop that generates the keyboard clock. The most significant bit arrives first and represents the shift condition. The next 7 bits are the keyboard code - they are translated to ASCII for processing and display. All coded values translated to \$80 or higher are recognized as control keys.

Characters are saved as received until the Repeat flag (initially cleared) is updated to reflect any upcoming repeat function.

Of the available control keys, KINPUT internally handles the following F2; SHIFT/F2; F3; LTRS; REPEAT; ALPHA MODE; and KANA MODE.

#### READ

A READ command from the main CPU is realized by the VT3 through a structured data sequence from the IOU-39Q. From the Main Control Loop, READ is entered whenever the READ IN PROGRESS flag is high. This flag is set during another routine, RECEIVE, which handles communicaiton line activities. Once the first three bytes of the formatted message stream are established by RECEIVE, the READ routine proceeds to continue transmission,

#### READ CONTINUED

taking data from the Transmit Buffer, formatting it according to Qantel Standard Protocol, and releasing it onto the communications line. Compression and transparency of the data is taken care of during this process.

The message format in response to a READ command is as follows:

| DEVICE | STX | STATUS | CURSOR X | CURSOR Y | TEXT | ETX | BCC |  |

|--------|-----|--------|----------|----------|------|-----|-----|--|

|        |     |        |          |          |      |     |     |  |

The cursor position is transmitted, both X and Y coordinates as positioned when the READ PENDING was encountered. (Cursor values are ORed with \$80 so as not to be transparent.)

Each byte in the Transmit Buffer is then sent. When the data has been transmitted, the message format is concluded with a ETX character and BCC (Block Check Character) to ensure data integrity.

The READ PENDING state is maintained if the VT3 does not receive a positive acknowledgement (ACK -- \$06). The entire sequence is then repeated when signaled by the IOU-39Q.

If the transmission succeeds, flags are reset (READ PENDING, F2, and F3) and the cursor is positioned to the next foreground field. The routine returns to the Main Control Loop.

#### WRITE

Characters coming in the UART's receive buffer are processed by the WRITE routine to be placed on the display screen. WRITE commands are received in formatted QSP message streams by RE-CEIVE routine at which time the WRITE PENDING flag is set. As the program is progressing through the Main Control Loop, detection of WRITE PENDING instigates the WRITE routine.

Characters are examined as they are inputted from the receive buffer for specific characteristics. After the write initialization sequence is performed, any characters between \$00 and \$0F are considered control commands; characters higher than \$0F are data characters.

Each control character results in a program branch to accomplish the assigned task. Commands may consist of one, two or three-byte sequences. At the conclusion of processing the command, the program branches back to handle the next character in the receive buffer.

Data characters are stripped of their highest significant bit. Any resulting values between \$00 and \$03 are converted to \$20. This prevents the user program from placing control characters onto the display screen directly.

Characters are placed on the screen in the position denoted by the cursor (which is incremented after each display). Foreground and background characters are distinguished when the character value is ORed with the mode of display. Whenever the cursor is extended beyond the edge of the screen, it is repositioned to the beginning of the screen. The exception to this is typewriter mode in which case the write is truncated when the cursor reaches the edge.

#### II-13

#### WRITE CONTINUED

Following character processing the routine performs a Write Cleanup if the Write Setup flag indicates the screen was modified for display. When in typewriter mode, a Transmit Mark is situated at the end of the data. The cursor is moved forward until it encounters a foreground field, where it is halted awaiting operator entry. The Write Pending flag is set to 0 and the program resumes in the Main Control Loop.

#### SCAN INTERRUPT HANDLER

The Z-80 utilizes its set of auxiliary registers (AF'; BC'; DE'; and HL') to keep track of horizontal and vertical trace progress across the CRT. When the Scan Interrupt routine is entered, these registers are immediately accessed and will contain the information to orient the Z-80.

| В  | Raster Row Counter (0 through 8)                                                    |

|----|-------------------------------------------------------------------------------------|

| С  | 7 indicates odd scan; 8 indicates even scan                                         |

| DE | Next Address to start scanning row                                                  |

| HL | Pointer for the Scan Address Table (used to find the address to be loaded into DE). |

The hardware timing circuits initiate a Scan Interrupt every 64 microseconds. Each time this happens the Z-80 has 16 microseconds to load the correct address for the next starting horizontal row. Maskable Interrupts are disabled and the Z-80, through a hardware buffer, recognizes the branch to address 0038 where the Scan Interrupt Routine is stored.

Each character is composed of 15 raster lines. Since interlacing is employed in VT3 scanning pattern, the character is

II**-1**4

#### SCAN INTERRUPT HANDLER CONTINUED

"sketched in" in two subsequent passes of the entire display screen. A horizontal row address is presented for 7 or 8 times on an alternating basis. The signal ODDCOUNT obtained from the hardware dictates, if true, that the first row be presented 7 times. The next row will be presented 8 times followed by a row 7 times and so on. When ODDCOUNT is false, the first row is presented 8 times, the second 7 times, and so on.