# DATA PROCESSING SYSTEM

# PROGRAMMERS' REFERENCE MANUAL

RCA

ELECTRONIC

5 0 1

DATA PROCESSING SYSTEM

# PROGRAMMERS' REFERENCE MANUAL

A General Introduction to the RCA 501 System

With Special Emphasis on the Computer

Electronic Data

Processing Division

Camden, New Jersey

The data herein presented is subject to minor change, without notice.

Supplements may be provided to advise of such revisions or additions.

# PREFACE

This manual is presented as a programmers' description of the RCA 501 System. As such, it emphasizes the Computer proper and includes only a general functional description of the associated peripheral devices in the RCA 501 System. Advanced programming techniques, operating procedures, and system analysis are not within the scope of this manual, but will be the subject of separate publications.

Particular emphasis has been placed on the individual Computer instructions, to which the largest portion of this manual is devoted. For ready reference in programming, a summary of the instructions, including register settings and automatic functions, and a summary of instruction timing appear in the appendices. A glossary of terms and a list of abbreviations used in the text are also appended.

# CONTENTS\_\_\_\_

|                                                                                                                                                                                                                                                                                                                                                                                               | Page       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| THE RCA 501 SYSTEM: GENERAL DESCRIPTION  High-Speed Memory — Program Control — Tape Selecting and Buffer Unit-A — Tape Selecting  Unit-B — Console — Monitor Printer — Paper Tape Reader — On-Line Printer — Electro-Mechanical Printer — Card Transcriber (Card Reader; Card Editor) — Transcribing Card Punch —  Tapewriter — Tapewriter-Verifier — Random Access File — File Control Unit. | 1          |

| Summary of Peripheral Equipment Performance                                                                                                                                                                                                                                                                                                                                                   | 4          |

| Accuracy Control Accuracy Control                                                                                                                                                                                                                                                                                                                                                             |            |

| RCA 501 Numbering System                                                                                                                                                                                                                                                                                                                                                                      |            |

| Organization of Data on Tape                                                                                                                                                                                                                                                                                                                                                                  |            |

| Variable Item and Message Length                                                                                                                                                                                                                                                                                                                                                              | 9          |

| ON-LINE PERIPHERAL EQUIPMENT: FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                          | 10         |

| Paper Tape Reader                                                                                                                                                                                                                                                                                                                                                                             | 10         |

| Monitor Printer                                                                                                                                                                                                                                                                                                                                                                               | 10         |

| Paper Tape Punch                                                                                                                                                                                                                                                                                                                                                                              |            |

| On-Line Printer                                                                                                                                                                                                                                                                                                                                                                               |            |

| Magnetic Tape Station                                                                                                                                                                                                                                                                                                                                                                         | 12         |

| <b></b>                                                                                                                                                                                                                                                                                                                                                                                       |            |

| THE COMPUTER: FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                          | 13         |

| High-Speed Memory                                                                                                                                                                                                                                                                                                                                                                             | 13         |

| The Basic Instruction                                                                                                                                                                                                                                                                                                                                                                         |            |

| Staticizing                                                                                                                                                                                                                                                                                                                                                                                   |            |

| Automatic Address Modification                                                                                                                                                                                                                                                                                                                                                                |            |

| Program Control                                                                                                                                                                                                                                                                                                                                                                               |            |

| Automatic Storage of Final Contents of A Register — STA                                                                                                                                                                                                                                                                                                                                       |            |

| Automatic Storage of Contents of P Register — STP                                                                                                                                                                                                                                                                                                                                             | 18         |

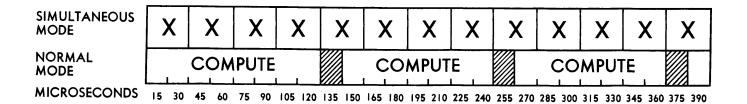

| Simultaneity                                                                                                                                                                                                                                                                                                                                                                                  | 18         |

| THE RCA 501 INSTRUCTIONS  Page numbers for the individual instructions are listed on page 22 (Order of Presentation) and in Appendix IV, page 63 (Operation Code order).                                                                                                                                                                                                                      | 21         |

| APPENDICES                                                                                                                                                                                                                                                                                                                                                                                    |            |

| I. Rollback (Automatic Rerun)                                                                                                                                                                                                                                                                                                                                                                 | 61         |

| II. The RCA 501 Code                                                                                                                                                                                                                                                                                                                                                                          |            |

| III. Illustration of Coding: Computer Program Record                                                                                                                                                                                                                                                                                                                                          |            |

| IV. List of Instructions (in Operation Code order)                                                                                                                                                                                                                                                                                                                                            |            |

| V. Summary of Instructions                                                                                                                                                                                                                                                                                                                                                                    |            |

| VI. Instruction Timing                                                                                                                                                                                                                                                                                                                                                                        |            |

| VII. Standard High-Speed Memory Locations and List of Address Modifiers                                                                                                                                                                                                                                                                                                                       |            |

| VIII. Glossary                                                                                                                                                                                                                                                                                                                                                                                | 7 <b>8</b> |

| IX. Abbreviations Used in Text                                                                                                                                                                                                                                                                                                                                                                |            |

|                                                                                                                                                                                                                                                                                                                                                                                               |            |

| ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                 |            |

| Figure                                                                                                                                                                                                                                                                                                                                                                                        |            |

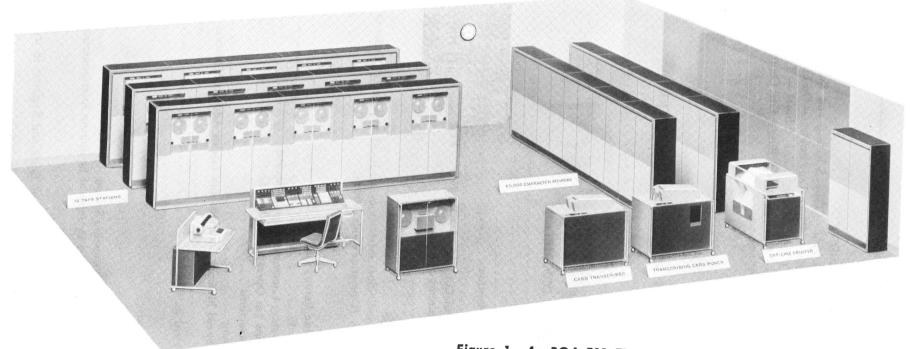

| 1. An RCA 501 Electronic Data Processing System                                                                                                                                                                                                                                                                                                                                               | vi         |

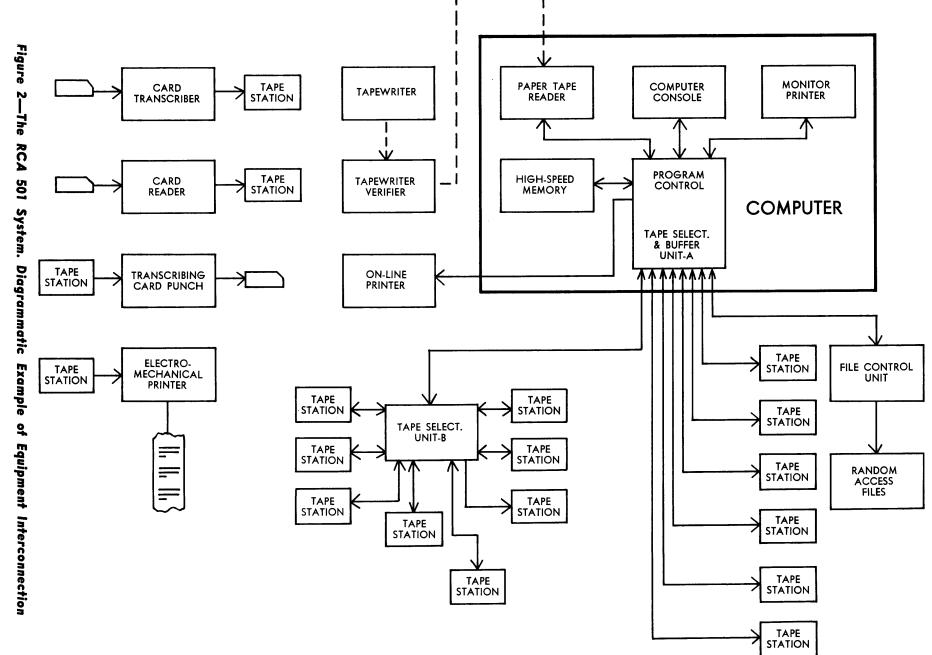

| 2. The RCA 501 System. Diagrammatic Example of Equipment Interconnection                                                                                                                                                                                                                                                                                                                      | 2          |

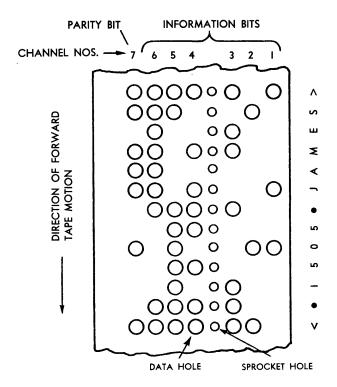

| 3. Recording on Paper Tape                                                                                                                                                                                                                                                                                                                                                                    | 7          |

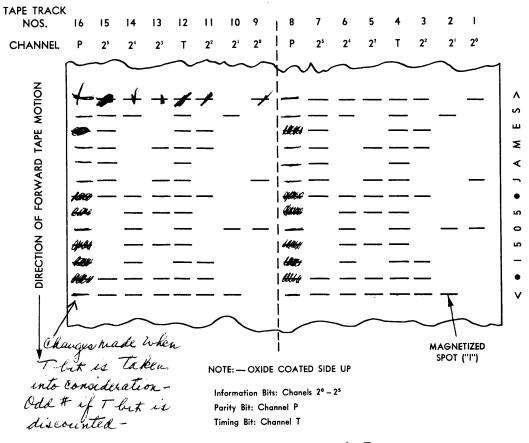

| 4. Recording on Magnetic Tape                                                                                                                                                                                                                                                                                                                                                                 | 7          |

| 5. Simplified Diagram Showing Relationship of Buses and Registers in the Computer                                                                                                                                                                                                                                                                                                             | 16         |

| 6. Standard High-Speed Memory Locations                                                                                                                                                                                                                                                                                                                                                       | 76         |

Figure 1—An RCA 501 Electronic Data Processing System

# THE RCA 501 SYSTEM

# GENERAL DESCRIPTION

The RCA 501 ELECTRONIC DATA PROCESSING SYSTEM is a general purpose, self-checking, readily expandable system, in the intermediate and large-scale performance class. The System incorporates extremely advanced logic, team-developed by engineers and programmers, and based upon extensive study of the characteristics of commercial data. All-transistor logic and printed circuitry contribute to attainment of the original design objectives of combining the highest performance level with the lowest possible cost of equipment and maintenance.

The RCA 501 is a complete system, capable of handling alpha-numeric data with magnetic tape, punched paper tape and punched card input and output, as well as printed output. In addition, drum storage devices provide fast random access, bulk storage for data and programs.

System efficiency is enhanced by:

- completely variable data organization, which conserves space on tape and in the internal memory and decreases processing time;

- four-character parallel transfer;

- increased data transfer rates;

- addressable registers;

- built-in and programmed accuracy controls, checking correct transfer of data in peripheral devices, into and out of the Computer, and within the Computer proper; additional controls ascertain correct arithmetic operations;

- time-shared electronics, permitting simultaneous operation of input-output devices with Computer functions:

- ready expandability of size of the internal memory and the type and number of peripheral devices.

The Computer is a general purpose, digital, sequentially controlled, random access, transistor machine, consisting of a number of integrated units (and attendant power supply): High-Speed Memory, Program Control, Tape Selecting and Buffer Unit, and Console with an associated Monitor Printer and Paper Tape Punch, and a Paper Tape Reader.

The **High-Speed Memory** is a random access, magnetic core device which provides storage and work area for programs and data. The memory is available in increments of 16,384 character locations and may be

expanded to a maximum of 262,144 locations. Each location is individually addressable and can store any one of the sixty-four RCA characters. These characters (RCA 501 Code) include all the letters of the alphabet, the ten decimal digits, control symbols and special marks. One character or four characters in parallel can be addressed, brought into the Memory Register and regenerated in their original locations in one 15-microsecond cycle.

The Program Control is the arithmetic and logical control element of the Computer. It interprets and executes the instructions of the program stored in the High-Speed Memory and performs the automatic accuracy checks. The Computer and the on-line peripheral devices operate in accordance with a stored program of two-address instructions. The instructions that can be executed by the Program Control include all the categories necessary for processing of data: Input-Output, Data Handling, Arithmetic, and Decision and Control. Each instruction is made up of eight RCA characters and consists of four parts: (1) an operation code (read, multiply, transfer, etc.), (2) an A address (usually the High-Speed Memory address of an operand or the left boundary of an operand), (3) a B address (usually the High-Speed Memory address of an operand or right boundary), and an N code. The N code permits automatic modification of address A and/or B through the use of any of the seven (four static and three dynamic) Address Modifiers.

The Tape Selecting and Buffer Unit-A permits connection of one to eight Tape Stations to the Computer, and controls reading from and writing to magnetic tape on these stations. Program instructions designate the appropriate Tape Station for input or output. The number of Tape Stations directly controlled by the Computer may be increased to as many as sixty-three by connection of a Tape Selecting Unit-B to each of the Unit-A trunk lines. Write-out from the Computer to magnetic tape is at the rate of 16,667 or 33,333 characters per second. Read-in from magnetic tape is at the rate of up to 33,333 characters per second.

The **Console** provides for complete monitoring of operation of the Computer and the on-line devices, with panel display and control of register and status level action. Automatic and manual operation, maintenance, program insertion and program testing can be accomplished from the Console.

Console facilities include:

- 1. Manual start and stop at a given instruction or at a given address.

- 2. Control and display of registers and counters.

- 3. Accuracy-checking indicators.

- 4. Indicators for currently performed instruction.

- Indicators for last or currently selected Tape Station.

- 6. Control and display of Character Recognition flip-flops.

- 7. Breakpoint switches.

- 8. Alarm indicators.

The Monitor Printer is an on-line device, similar to an electric typewriter, that prints on paper stock from information received directly from the Computer's memory. It operates at the rate of ten characters per second and is used primarily for program operational control, program testing, and exceptional types of output. The Paper Tape Punch associated with this device can produce seven-hole punched tape simultaneously with the Monitor Printer's output of hard copy.

The **Paper Tape Reader** accepts seven-hole punched paper tape and operates at the rate of 400 characters per second. It is used largely for initial program insertion, program testing, "one-shot" programs, and insertion of periodically changing constants.

High-Speed printing can be accomplished on-line (On-Line Printer) or off-line (Electro-Mechanical Printer) in the RCA 501 System. The print line capacity is 120 characters and the print rate is 600 lines per minute. The On-Line Printer accepts data directly from the Computer memory and operates under the direction of the stored program. The Printer is converted to off-line by the addition of a Data Editor, operating then under the direction of a plugboard program and a paper tape loop, with information received directly from a Magnetic Tape Station.

Included in the peripheral equipment complement for the RCA 501 System are a Card Transcriber, Transcribing Card Punch, Tapewriter, Tapewriter-Verifier, and Random Access File. These devices are only briefly described here, since they will be fully detailed in separate manuals.

The Card Transcriber is comprised of two units, a Card Reader and a Card Editor. The Card Reader may be used without the Editor, in which case editing is reserved for the Computer. This device converts characters on eighty-column punched cards to RCA coded characters on magnetic tape, at the rate of up to 400 cards per minute. The Card Reader includes a control panel, an automatic card-handling mechanism and two card-reading stations. Each card is read at both

stations, and the readings are compared as an accuracy check. The Card Editor permits rearrangement and selective transcription of card data and insertion of additional characters. The Card Transcriber employs transistor circuitry and accuracy checking, including parity, comparison and multi-punch checks.

The Transcribing Card Punch converts RCA coded characters on magnetic tape to punched card code on 80-column cards at the rate of 150 cards per minute. This device employs transistor circuitry and includes a card-punching unit and an electronics unit with a control and indicator panel. The card-punching unit is comprised of an automatic card-handling mechanism, a card-punching station and a card-reading station. A manually wired plugboard is used to rearrange information, to provide for overpunching, and to insert special control symbols and additional characters. Accuracy controls include parity, correct data format, and correct punching checks.

The **Tapewriter** and **Tapewriter-Verifier** are used for original preparation and verification of RCA coded, seven-hole punched paper tape for subsequent input to the Computer via the Paper Tape Reader. These devices are keyboard operated and simultaneously print on paper stock the same information that is being punched on tape. The Tapewriter-Verifier automatically checks the accuracy of its output by comparison with a previously prepared (Tapewriter) punched paper tape. Whenever a character being punched on the Tapewriter-Verifier is not in agreement with the related character on the original tape, both the keyboard and the punch lock. Both devices will function at typing speeds up to 10 characters per second, and both include parity checking.

The Random Access File is a drum storage device which provides fast random access, bulk storage for data and programs and operates under automatic program control. Each unit has a capacity of at least 1.5 million characters, with 192-millisecond average random access time to any data (167 milliseconds for drum access plus 25 milliseconds for relay switching between tracks).

There are 300 tracks on the drum. The capacity of each track is 5000 alpha-numeric characters. The character bits are recorded serially in each track around the drum. Bits are recorded or read at 6.7-microsecond intervals (character transfer rate, up to 18,700 per second).

The drum code is eight-bit serial, with four "1" and four "0" bits per character. Conversion between this and the RCA 501 Code is handled automatically within the File Control Unit.

The File Control Unit used in conjunction with the Random Access File enables the Computer to control

and to read and write information on a maximum of twelve Random Access Files, in accordance with the Computer program. The File Control Unit can be connected to the Tape Selecting and Buffer Unit-A or B in the same manner as the Tape Station. Reading or writing of information on a Random Access File may be accomplished simultaneously with other Computer functions. Simultaneous operation between the Computer and two Random Access Files is possible if each File is connected to a separate File Control Unit.

# Summary of Peripheral Equipment Performance

| On-Line             |                                                  |

|---------------------|--------------------------------------------------|

| Input:              |                                                  |

| Paper tape          | 1000 characters per second                       |

| Magnetic tape       | up to 33,333 characters per second               |

| Random Access File  | 18,700 characters per second                     |

| Output:             |                                                  |

| Magnetic tape       | 16,667 or 33,333 characters per second           |

| Paper Tape Punch    | 10 characters per second                         |

| Monitor Printer     | 10 characters per second                         |

| On-Line Printer     | 600 lines per minute,<br>120 characters per line |

| Random Access File  | <del>-</del>                                     |

| Off-Line            |                                                  |

| Input:              |                                                  |

| Card Transcriber    |                                                  |

| Tapewriter-Verifier | . 10 characters per sec-                         |

### Output:

Electro-Mechanical Printer. 600 lines per minute, 120 characters per line Transcribing Card Punch... 150 cards per minute

ond

# **ACCURACY CONTROL**

Automatic accuracy controls incorporated in the RCA 501 System are designed to prevent incorrect information from entering or leaving the System and are selectively engineered to avoid overloading the System with checks at non-critical points.

# **Accuracy Checking Techniques**

Parity Checking. Each character on tape carries an extra bit to make up an odd number of "1" bits on magnetic tape and an even number on paper tape. Correct parity is ascertained on read-in, during data flow in the Computer, and on write-out. Parity checking in the 501 System is well illustrated in reading and recording of data on magnetic tape. Each character transmitted by a user device (Computer, Card Transcriber, etc.), is checked for parity. On receipt of the character at the Tape Station, where it is recorded in duplicate, echo returns from the recording heads are parity checked in the Tape Station, and the user device is notified that the character was recorded successfully. The user devices also check parity on data received from tape.

Dual Recording on Magnetic Tape. The bits of each character plus a timing bit are recorded in duplicate, in sixteen channels, across the width of the tape. All dually recorded bits of the character are read or written simultaneously. Either one of the two recorded spots for a single bit may be missing, and the bit can still be read. In addition to its value as an accuracy control measure, dual recording lengthens tape life.

Automatic Rerun (Rollback). If a parity error does occur on a magnetic tape "read," the tape is automatically backed up and the read instruction is reexecuted. The Computer stops, with Console indication of the reason for stoppage, if an error is detected on re-reading. (See Appendix I for description of Rollback.)

Arithmetic Accuracy Checking. Each arithmetic cycle of an arithmetic operation is performed twice, first with the original operands and then with the complements all during the same time cycle-and the results are compared for agreement.

# **Application of Accuracy Checking Techniques**

Program Control. The following Program Control conditions cause the Computer to stop:

- 1. Incorrect parity in Memory Address Register.

- 2. Incorrect parity in Memory Register.

- 3. Arithmetic Unit malfunction.

- 4. Incorrect parity on output of bus adder.

- 5. Illegal operand in decimal operation.

- 6. Incorrect parity in Normal Operation Register.

- 7. Incorrect transfer of operation from Normal to Simultaneous Mode.

- 8. Malfunction of previous result indicator.

- 9. Time pulse generator malfunction.

Input-Output. The following input-output conditions cause the Computer to stop:

- 1. Tape Station reading extra bits in Intermessage

- 2. Missing clock pulse when reading from Tape Station.

- 3. Missing clock pulse when writing out from Computer.

- 4. Tape Station does not obey control signals.

- Odd number of characters from paper tape block read.

- 6. Second parity error in tape read (see Automatic Rerun).

- 7. Incorrectly selected tape.

- 8. Incorrect data format (incorrect Start Message-End Message sequence).

- 9. Incorrect parity at the output of Computer write buffer or of the Tape Station writing head.

- 10. Incorrect paper tape parity.

- 11. On-Line Printer not operable.

- 12. On-Line Printer paper supply low.

# THE RCA 501 NUMBERING SYSTEM

The RCA 501 System employs a binary numbering system to represent information, utilizing seven binary digits, or bits, to represent each RCA character (see Organization of Data on Tape, page 6, and the RCA 501 Code, Appendix II).

The following table lists binary equivalents of decimal numbers as they might appear in a theoretical computer that employed, not a constant number of bits to represent each character, or decimal digit, but as many as a given decimal number required.

# A. Partial Table of Decimal and Binary Equivalents

| , ,    |

|--------|

| Binary |

| 0      |

| 1      |

| 10     |

| 11     |

| 100    |

| 101    |

| 110    |

| 111    |

| 1000   |

| 1001   |

| 1010   |

| 1011   |

| 1100   |

| 1101   |

| 1110   |

| 1111   |

| 10000  |

| 100000 |

|        |

Binary-coded decimal representation employs four binary digits, or bits, to represent each decimal digit, e.g., decimal zero is represented as 0000, decimal 3 as 0011, etc. Excess-3 binary-coded decimal representation adds 3 to each decimal digit and employs four bits to represent the resulting digit. An excess-3 binary-coded representation of decimal zero, then, looks like a binary-coded decimal 3; an excess-3 representation of decimal 6 looks like a binary-coded decimal 9 (Table B).

B. Table of Decimal, Binary-Coded Decimal, and Excess-3 Binary-Coded Decimal Equivalents

| Decimal | Binary-Coded<br>Decimal | Excess-3 Binary<br>Coded Decimal |

|---------|-------------------------|----------------------------------|

| 0       | 0000                    | 0011                             |

| 1       | 0001                    | 0100                             |

| 2       | 0010                    | 0101                             |

| 3       | 0011                    | 0110                             |

| 4       | 0100                    | 0111                             |

| 5       | 0101                    | 1000                             |

| 6       | 0110                    | 1001                             |

| 7       | 0111                    | 1010                             |

| 8       | 1000                    | 1011                             |

| 9       | 1001                    | 1100                             |

Of the seven bits that make up each of the sixtyfour RCA characters, the leftmost is the parity bit, used for accuracy checking; the remaining six are the *infor*mation bits. The positional significance of the information bits increases from right to left (from 2° to 2°).

bit position P

$$2^5$$

$2^4$   $2^3$   $2^2$   $2^1$   $2^0$  bits x x x x x x x x x (x = 0 or 1)

The rightmost four information bits  $(2^0 - 2^3)$  constitute the arithmetic portion of a character. (Table B shows only the arithmetic bits.) The RCA Code is so devised that the leftmost two information bits (25 and 24) are the same (01) for all decimal digits (0 through 9); this permits the Computer to consider only the arithmetic portion of characters in decimal arithmetic operations (add, subtract, multiply, divide). Further, the arithmetic portion of each decimal digit is excess-3 binary-coded decimal. The particular advantages here are (1) ease of complementation (note, in Table B, the reverse bit configuration for 0 and 9, 1 and 8, 2 and 7, 3 and 6, 4 and 5), and (2) a carry is propagated in addition of two excess-3 binary coded operands whenever a carry would be propagated by addition of their decimal equivalents.

RCA 501 programs are written in *octal notation*; this applies to data, addressing, and all instruction components. Octal notation serves as a mnemonic device for reading and writing binary representations of RCA characters (see Octal Equivalents in the RCA 501 Code, Appendix II). To read a binary code as octal:

- 1. Ignore the parity bit and divide (visually) the information bits into two 3-bit groups;

- 2. Read the two groups as one octal number by deriving the octal digit for each group.

Each group of three bits has a corresponding octal digit as follows:

|      | Octal |      | Octal |

|------|-------|------|-------|

| Bits | Digit | Bits | Digi  |

| 000  | 0     | 100  | 4     |

| 001  | 1     | 101  | 5     |

| 010  | 2     | 110  | 6     |

| 011  | 3     | 111  | 7     |

# For example:

- 1. The bit configuration for the letter "T" is 1110011. Ignoring the parity bit and dividing the information bits, one can easily see this as 110 011 and read the octal equivalent as 63.

- 2. The bit configuration for decimal digit "9" is 0011100.

[34 = octal equivalent of decimal 9, or  $(9)_{10} = (34)_8$ ].

Since internal addressing is octal and programs are entirely written in octal notation, only the digits 0 through 7 will ever appear on an RCA 501 Computer Program Record (see Appendix III).

# ORGANIZATION OF DATA ON TAPE

# General

The seven-bit binary code for each RCA character is listed in Appendix II. In the RCA 501 Code, the parity bit (P) is chosen to be a "one" or a "zero" so that every character will contain an even number of "one" bits on paper tape and an odd number on magnetic tape. An eighth bit is recorded with each character on magnetic tape for timing.

#### **Definitions**

Bit. A bit is a single binary digit, having a value of either 0 or 1.

Character. An RCA 501 character consists of six information bits and one parity bit combined to represent a decimal digit, a letter of the alphabet, a punctuation or other special mark, or a control symbol (see The RCA 501 Code, Appendix II).

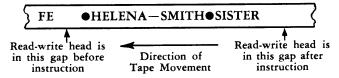

Item. An item consists of such characters as are necessary to specify a particular unit of information (a numerical quantity, an alphabetic name, a street address,

a stock number, etc.). An item is preceded by an Item Separator symbol (ISS).

Message. A message consists of a Start Message symbol (SM); one or more related items, each preceded by an Item Separator symbol; and an End Message symbol (EM), in that order.

Block. On magnetic tape, a block consists of eight or more characters, preceded and followed by an Intermessage Gap. Intra-block blanks must constitute less than 75 microseconds of tape time.

On paper tape, a block consists of an even number of characters equal to or greater than sixteen, without intra-block blanks; it is preceded and followed by an Intermessage Gap. (Corrective overpunching, to delete a character, is ignored in this character count.) The characters must represent only the decimal digits 0 through 7 (octal 23 through 32). (See discussion of decoding circuitry, Paper Tape Reader, page 10.)

Blocks on magnetic or paper tape are read and written without regard to message structure rules—they are delineated by Gaps, rather than by control symbols, and need not contain any control symbols.

Line. A line is composed of the characters from a single message which may be read from magnetic tape into the Electro-Mechanical Printer during a single read cycle. Each such line is terminated with an End Message (EM) or Line Shift (LS) symbol. The LS symbol appears only as the last character of a line. When a Page Change (PC) symbol or an Item Separator symbol is used to provide an additional paper control symbol, it must always be followed by LS or EM and then the Intermessage Gap. Also, either EM or LS preceded and followed by an Intermessage Gap is a line and must be treated as such on tape. (In the Electro-Mechanical Printer, the maximum number of characters that can actually be printed is 120 per line. Each character space to appear in the printed line decreases the 120 maximum by one. On tape, a line may include non-print characters and control symbols in addition to the 120.)

File. A file consists of any number of related information units, in message or block format; it may consist of several tapes (reels) or any part of one tape. A file is terminated by an End File (EF) symbol, preceded and followed by an Intermessage Gap.

In a multi-tape file, all but the last tape are terminated by an End Data (ED) symbol alone, preceded and followed by an Intermessage Gap. The end of file on the last tape is indicated by an EF, preceded and followed by an Intermessage Gap. If this is a full tape, or a partially filled tape with no other valid information following the file data, an ED follows the EF, separated from it and followed by an Intermessage Gap.

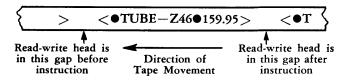

Figure 3—Recording on Paper Tape

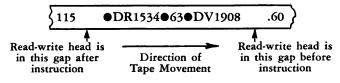

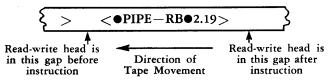

Figure 4—Recording on Magnetic Tape

If more than one file appears on a tape, each file except the last is terminated by an EF only. The last complete file on a tape is terminated by an EF followed by an ED.

ED and EF are each preceded and followed by an Intermessage Gap. They are never accompanied by Start and End Message symbols, and they may never appear within a message.

If a file is read or written in block format, the ED and the EF are treated as separate blocks. If a file is read or written in message format, the ED and the EF are treated as separate messages.

Intermessage Gap. An Intermessage Gap is a length of unrecorded tape sufficient to allow for Gap detection and stopping and starting of the tape. This is a minimum of 0.34" on magnetic tape (for block or message format). On paper tape, it is a minimum of three character positions for message format and a minimum of four character positions for block format.

# Arrangement of Data on Tape

Arrangement of Bits to Form Characters. Figure 3 illustrates the arrangement of information on paper tape. There are seven data hole positions per row. Each row represents a character. The presence of a punched hole represents a "one" bit, and the absence of a hole represents a "zero" bit. The positions of the bits are numbered 2° through 26, corresponding to the information and parity bit positions of an RCA binary coded character. A row with all seven channels (plus an extra, eighth, channel) punched indicates that the character in this row has been deleted; such punching does not represent an RCA 501 character (see The RCA 501 Code, Appendix II).

Bits are recorded on magnetic tape as magnetic spots in rows across the tape (Figure 4). Each bit is written in two locations as an accuracy control measure, giving 16 tracks across the width of the tape (including the timing bit). Each of the two locations is capable of producing a standard signal. Thus, either one of the two recorded spots for a single bit of information may be missing, and the bit can still be read.

Arrangement of Characters to Form Items. All characters are recorded on tape serially so that the characters making up an item follow one another in sequence from most to least significant. Each item is preceded by an Item Separator symbol.

Each item of a message may have variable length. Inclusion of the Item Separator symbols allows the use of variable length items and the omission of items, without changing the positional significance of any item in the message (see Variable Item and Message Length, this page).

Arrangement of Items to Form Messages. The items of a message follow one another in sequence, each being preceded by an Item Separator symbol. In every message of a given type, the nth item always has a given connotation. Therefore, a count of the Item Separator symbols, starting from the first or from a program-oriented point in a message, permits location and identification of any item.

In the event that a particular item is omitted, the Item Separator symbol can be recorded on tape in its proper sequence when it is necessary to preserve the positional significance of the items that follow. However, the Item Separator symbol for an omitted item may also be omitted if there is no valid information following it in the message. In this case, the End Message symbol follows immediately after the last item present. This avoids writing an unnecessary number of consecutive Item Separator symbols at the end of a message.

All messages consist of a Start Message symbol followed by an Item Separator symbol and the characters of the first item, the succeeding items (each preceded by an Item Separator symbol), and an End Message symbol, in that order. The SM and EM symbols appear only in the positions defined herein.

#### Miscellaneous

Equipments that record data on magnetic tape provide for erasing a minimum length of 1.35" at the beginning of each tape before recording. The equipment recognizes the beginning of the tape by a Beginning of Tape Level which is generated by a permanent indicator (Beginning of Tape Control) in a fixed position on the magnetic tape (not an RCA 501 character).

An end of tape warning (ETW) device is provided to indicate that approximately 5 feet of usable magnetic tape are available; this permits recording of an entire message and an End File and/or End Data symbol after the warning is received. This warning is not an RCA 501 character, but is a signal generated by a permanent indicator in a fixed position on the tape.

# Variable Item and Message Length

Data storage in the RCA 501 System incorporates true variable item length. This concept may be more fully appreciated if prefaced with a discussion of fixed and fixed variable word and block length.

"Word" is generally defined as a fixed number of consecutive characters or character locations, and "block" as a fixed number of consecutive words, in primary or secondary storage. These terms, word and block, are more aptly used with respect to fixed and fixed variable systems, but are not particularly applicable to a true variable system.

In a computer system employing fixed word length, the number of characters per word and the number of words per block are characteristic of the system, incorporated in the circuitry. A computer with a fixed word length of 12 characters dictates the use of some multiple (not fraction) of 12 for each and every item (employee number, name, pay rate, etc.), in a message and a fixed number of words for each message in a file. If the employee number is made up of five digits, the word in which this item was stored would be filled out with redundant zeros or spaces (e.g., +64398000000). This would be true for each employee number in the file. The alternative of utilizing these zero-filled positions by packing more than one item into a word entails additional program instructions, with consequent increased processing time, and is possible only to a limited degree. Even with packing of words, the fixed block size may entail zero-filling of one or more entire words at the end of each block.

In a fixed variable (non-standard maximum item length) system, the number of character positions for each item is assigned in accordance with the anticipated maximum for that item. In such a system, then, item (data field) layout is analogous to that used for punched cards. These lengths may be individually predetermined for each file, but remain constant for each message in the file. For example, in an inventory file, cost per unit might vary from two cents for one stock number to

some five-digit figure for another. This maximum would dictate that five character positions be used even where there is only one significant digit; two cents might then be written as 00002. Stock numbers in this file, however, could be assigned a different number of character positions, stock description still a different number, and so on. Thus, fixed variable word length provides greater flexibility than does fixed word length.

Data storage in a true variable item length system does not have the limitations imposed by fixed or fixed variable systems. In the RCA 501, the use of control symbols and the ability to address each character location individually permits the length of any item in any message to be in strict accordance with that item's actual character count. This allows for total variability of item and message length, but does not preclude the use of fixed or fixed variable lengths when the programmer finds this expedient.

In each of these categories—fixed, fixed variable, and true variable—the method of internal storage is extended to external storage; when redundant zeros or space characters are required to fill out a word in the computer memory, they are also carried on tape. With a given tape density (number of characters packed per inch) and a given tape speed (number of inches per second), a characteristic business file would require less tape footage and could be read and written out in less time when true variable item length is utilized.

# On-Line Peripheral Equipment

# FUNCTIONAL DESCRIPTION

#### PAPER TAPE READER

The Paper Tape Reader associated with the RCA 501 System is used to transcribe incoming data to magnetic tape, to enter data initially into the Computer during program testing, to transcribe programs, and to enter into the Computer periodically variable constants for production programs (e.g., today's date).

The Paper Tape Reader is photoelectric and operates at the rate of 1000 characters per second. It uses one-inch wide, seven-hole punched tape; the seven channels across the width of the tape correspond to the seven bit positions (six information bits and one parity bit) of an RCA character. Characters on punched paper tape have even parity. (See Figure 3.) When a character position on paper tape contains a punch in all seven channels, plus an eighth punch, this is interpreted as "delete character"; it is not an RCA character and no attempt is made to read it into the Computer. Information on paper tape may be in either message or block format.

Since the tape does not stop immediately after the last character is read in, but may glide the equivalent of three character positions, a Gap (unpunched tape) of three character positions is left between successive messages, and four character positions between successive blocks.

To facilitate the insertion of programs, a special method is used to block read paper tape. Programs are written, on the code sheet, in octal notation. An RCA 501 Tapewriter is used to create a punched paper tape from the code sheet, so that the program can be read into the Computer. One decimal key is depressed for every octal digit on the code sheet, thereby producing on the tape one RCA character (two octal digits) for every octal digit on the code sheet.

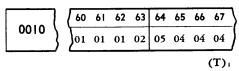

In a block read from paper tape, characters automatically enter decoding circuitry before they are transferred into the HSM. Decoding may be explained as follows: (23)<sub>8</sub> is subtracted (binary subtraction) from the first character on tape, and the rightmost three bits of the difference are stored as the *leftmost* three bits of the decoded character; (23)<sub>8</sub> is subtracted from the second character on tape, and the rightmost three bits of the difference are stored as the rightmost three bits of that decoded character. The combined result, with a parity bit generated, is then stored in the High-Speed Memory in the same fashion as are characters read from magnetic tape. The process is then repeated for each

character on the paper tape until a Gap is recognized. On a block read from paper tape, then, the leftmost three bits (left octal digit) of each character stored in the HSM will be derived from the first, third, fifth, seventh, etc., character read in from the tape; and the rightmost three bits (right octal digit) will be derived from the second fourth, sixth, eighth, etc., character read in from the tape. When the last character on tape has entered the decoding circuitry, an alarm occurs if the count is less than sixteen, or an odd number.

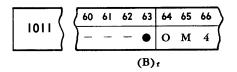

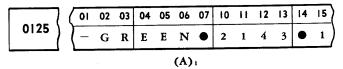

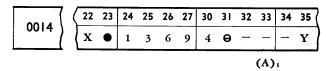

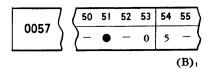

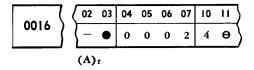

This process may be represented as follows:

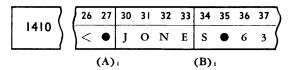

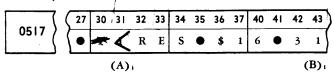

Instruction characters as they appear on code sheet:

Octal digits punched on 23 30 23 24 27 24 23 26 23 23 31 23 23 23 23 23 paper tape

Automatically

circuitry

Difference 00 05 00 01 04 01 00 03 00 00 06 00 00 00 00 00

Decoded characters 05 01 41 03 00 60 00 00 stored in HSM

This decoding occurs only when paper tape is read in block format, permitting the digits 0 through 7 (octal 23 through 32) to be properly decoded. Block format on paper tape is largely restricted to programs for initial insertion into the Computer. Data (as against program instructions) on paper tape are punched and read in message format, in standard RCA 501 Code, and are not subjected to code conversion.

The following formula is used for paper tape read time:

Total no. of char.  $\div$  400 = total time in seconds Start time is negligible for paper tape and is not considered a time factor.

#### MONITOR PRINTER

The Monitor Printer associated with the Computer Console prints out information from the High-Speed Memory of the Computer under the direction of the stored program at the rate of ten characters per second. Two modes of operation are possible:

1. In Computer or program testing, a character will be printed for every RCA character that might be stored in the designated area of the High-Speed Memory.

Carriage return and a line shift automatically occur after printout of an End Message symbol or when the right-hand paper margin is reached.

The table below shows the character that will be printed for each octal number in the High-Speed Memory [e.g., a space symbol, (01)<sub>8</sub>, in the HSM will be printed out as an underline, (23)<sub>8</sub> will be printed out as a decimal zero, (24)<sub>8</sub> as a decimal one, etc.].

| 2nd digit of octal lst no. digit of octal no. | 0 | -              | 2 | 3 | 4             | 5 | 6 | 7  |

|-----------------------------------------------|---|----------------|---|---|---------------|---|---|----|

| 0                                             | а | Under-<br>line | ‡ | ( | )             | * | : | \$ |

| ı                                             | % | ;              | & | , | minus<br>sign | * |   | h  |

| 2                                             | q | r              | 1 | 0 | 1             | 2 | 3 | 4  |

| 3                                             | 5 | 6              | 7 | 8 | 9             | , | # | х  |

| 4                                             | A | В              | С | D | E             | F | G | Н  |

| 5                                             | I | J              | K | L | М             | N | 0 | Ъ  |

| 6                                             | Q | R              | s | Т | U             | V | W | X  |

| 7                                             | Y | z              | s | t | •             | > | < | v  |

2. For edited output, printing of space symbols, Item Separator symbols and End Message symbols can be suppressed. The End Message symbol, though suppressed, will still effect a carriage return and line shift. A suppressed space symbol will cause a horizontal shift of one character position. The Monitor Printer can thus be used for output of documents (summary totals, cost distributions, etc.), utilizing either pre-printed or blank paper stock.

The Paper Tape Punch associated with the Monitor Printer is used for manual preparation of short paper tapes and for output of data from the Computer. Punching is activated by flipping the Punch Switch on the Monitor Printer to the ON position, in which case both punched tape and printed copy on the Monitor Printer are obtained. This mode of operation is subject to the restriction that printing of a lower-case letter (see Monitor Printer chart above) will cause the octal value of the corresponding upper-case letter to be punched in the tape. For example, if the character (00)<sub>8</sub> is read out of the HSM, the lower-case letter "a" will be printed (Monitor Printer) and (40)<sub>8</sub>, the octal value of an upper-case "A," will be punched on tape. [Of course, if (40)<sub>8</sub> is read out of the HSM, an upper-case "A" will be printed and (40)<sub>8</sub> will be punched on tape.]

Monitor Printer output time (with or without paper tape output) may be computed on the basis of the number of characters involved (total no. of char. ÷ 10

= total time in seconds). Start time is negligible and is not considered a time factor.

#### **ON-LINE PRINTER**

The On-Line Printer in the RCA 501 System is an all-transistor device which prepares output documents, printing data directly from the High-Speed Memory of the Computer. Data editing is accomplished in the Computer, under the direction of the stored program. Line skipping is controlled by the Computer program, either directly or through a Tape Loop on the Printer Unit.

Two Computer instructions are directly associated with the On-Line Printer—one initiates printing and the other positions the paper for the next line of printing. The latter instruction may specify the number of lines the paper is to be advanced, or it may refer to one of two information channels in the Tape Loop on the Printer Unit. One channel (Vertical Tabulation) is referenced in order to advance the paper to specific lines within the confines of a page, and the other channel (Page Change) is referenced to move the paper to the start of a new page.

Maximum print capacities are 120 characters per line, 10 characters per horizontal inch, and 6 lines per vertical inch. One line is printed in 66.7 milliseconds. For single-line paper advance, the paper motion time is 30 milliseconds. Printing and paper motion time, then, total less than 100 milliseconds, permitting single-spaced printing at the rate of at least ten lines per second (600 lines per minute). When more than three lines are skipped at one time, however, the paper advance rate is at least 50 lines per second.

Paper stock may be single or multiple sheet fanfold, from 3 to 22 inches in width and up to 17 inches in sheet length. One original plus up to three carbons (11-pound paper and  $7\frac{1}{2}$ -pound carbon) may be used. Hecto and Multilith master stock may also be used.

Fifty-one RCA characters can be printed by the On-Line Printer. These include the 10 decimal digits, the 26 letters of the alphabet, and the following punctuation marks and symbols:

, comma \* asterisk

; semicolon & ampersand

: colon / virgule

. period / per cent

dollar sign

close parenthesis # number sign

ditto or quotes — minus sign

The occurrence in an HSM print-out sector of an RCA character other than one of the fifty-one listed above will leave a blank in the related position in the printed line, with the exception that (00)<sub>8</sub> will result in an overprinting of the three symbols =, + and @. (These

symbols, though present on the print wheel, normally have no RCA Code equivalents.)

For accuracy control, a Printer Unit Inoperable alarm, which stops both the Printer and the Computer, is incorporated. Also, the Printer, by means of a microswitch, can sense a "low paper" condition and send a warning signal to the Computer. When the Computer program calls for Tape Loop activation of a page change and a "low paper" signal is present, both the Computer and the Printer stop, after accomplishment of the page change, to permit replenishment of the paper supply. Thus, printing on a page is completed before the operation is stopped.

# MAGNETIC TAPE STATION

The Magnetic Tape Station is a fully automatic device, with transistor circuitry, which performs reading, writing and erasing operations on  $\frac{3}{4}$ -inch wide Mylar base magnetic tape, under control of the user equipment. On each Tape Station, two  $10\frac{1}{2}$ -inch reels are mounted—a full reel and a take-up reel. The capacity of a reel is 2400 feet of tape, providing a minimum of 2300 feet of usable tape. Tape Station design facilitates manual interchange of reels, which can be accomplished in less than one minute.

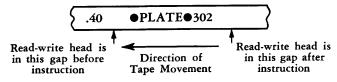

The Tape Station can be instructed to move the tape in a forward or reverse direction. It can be directed to move the tape with or without writing. It can read the tape with or without transferring characters into the High-Speed Memory. It can be instructed to read all of the data serially or search for specified symbols. The Tape Station can, in response to one instruction, unwind the tape to the end, or rewind it to the beginning. Writing on magnetic tape is in the form of significant configurations of magnetic spots (see Organization of Data on Tape and Figure 4).

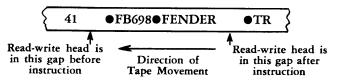

The Tape Station writes at the rate of up to 33,333 characters per second (33.3 KC). It accomplishes this by writing 333.3 characters to the inch while moving the tape at a speed of 100 inches per second. Information on magnetic tape is read at this same rate. It takes only 30 microseconds to read a character on tape into the High-Speed Memory, or to write a character from the memory onto magnetic tape.

Gaps on magnetic tape between messages or blocks are 0.34 inch. Part of the gap is attributable to the fact that tape glides for a short distance after being commanded to stop. On a tape write, 3.5 milliseconds elapse between the tape start command and write-out of the first character from the High-Speed Memory. The same time lapse occurs on a tape read. A lapse of 4.5 ( $\pm$ 0.9) milliseconds occurs when a read-reverse tape instruction immediately follows a write instruction for the same tape. There is otherwise no appreciable delay in switching the direction of tape movement or in switching between reading and writing.

Up to 63 Tape Stations can be directly addressed by the Computer. Eight Tape Stations can be connected to Tape Switching and Buffer Unit-A. As additional Tape Stations are required in an installation, a Tape Switching Unit-B can be substituted for each of the original eight Tape Stations. The addition of one such unit will, therefore, permit as many as 15 Tape Stations to be connected (seven original and eight added) to the Computer. One A Unit and eight B Units are required to connect sixty-three Tape Stations to the Computer. Each Tape Station has a unique (octal) address, (00)<sub>8</sub> — (76)<sub>8</sub>. The 64th address, (77)<sub>8</sub>, is reserved for the Monitor Printer and the Paper Tape Punch and for the Paper Tape Reader.

The first eight Tape Stations (attached to Unit-A) are Computer identified by the left digit of the tape selection number (00, 10, 20, 30 . . . 70). With only these eight Tape Stations in a system, then, any number from 10 to 17 will select Tape Station 10; 30 to 37 will select Tape Station 30, etc. Each Tape Station connected to a B-type unit must be addressed by its individual Tape Station number. For instance, if Tape Stations are connected to 30, 31, 34, 35 and 37 of the 30–37 octet, and 32, 33 or 36 is addressed, a "non-operable" alarm will occur and the Computer will stop.

Tape Station accuracy controls include manual lockout and "write interlock." Manual lockout is provided on each Tape Station to insure safe manual operation procedures. When the Lockout Switch of a Tape Station is in the ON position nothing can be written on the tape at that Station. A "write interlock" feature safeguards reference tapes from human error by preventing writing (and erasing).

# **FUNCTIONAL DESCRIPTION**

# **HIGH-SPEED MEMORY**

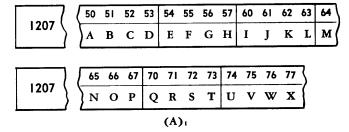

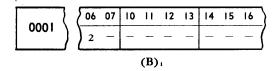

The High-Speed Memory (HSM) in the RCA 501 System is constructed in modules. A module is made up of twenty-eight 64 x 64 matrices of magnetic cores. Each core can represent one bit; a matrix of cores, then, represents 4,096 bits and a module represents 114,688 bits. Since an RCA character is comprised of seven bits, each module can store 16,384 characters in 16,384 individual character locations.

The HSM is expandable from one to sixteen modules (four banks, each with a capacity of 65,536 characters), or up to a maximum of 262,144 character locations. Each location in memory has a unique address, consisting of three RCA characters (= three octal numbers = six octal digits), so that each location, or the contents thereof, is individually addressable. Though somewhat oversimplified, the HSM may be pictured as a rectangular array of locations, with the smallest address in the upper left-hand corner and the largest address in the lower right-hand corner. The lowest address in the HSM is always (000000)<sub>8</sub>. Since the addressing scheme in the RCA 501 employs the octal number system, the highest address in a one-module memory is (037777), and the highest address in a sixteen-module memory is  $(777777)_8$ .

To decrease processing time, the HSM is constructed so that four characters (twenty-eight bits), in four consecutive character locations, can be accessed in a single memory cycle. The Computer memory cycle is 15 microseconds; this means that characters may be addressed, brought into the Memory Register, and regenerated in their original locations every 15 microseconds.

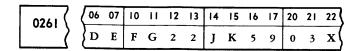

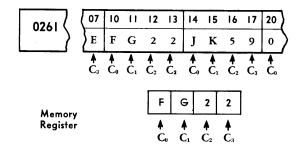

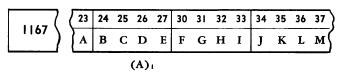

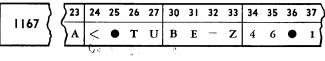

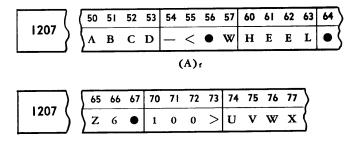

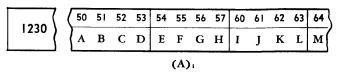

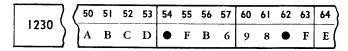

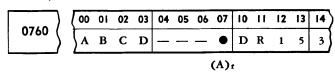

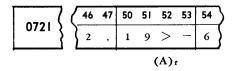

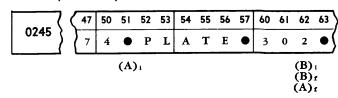

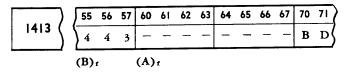

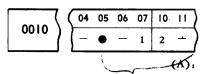

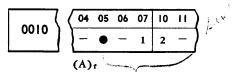

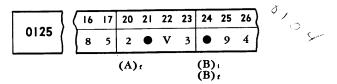

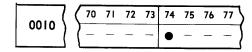

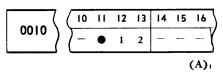

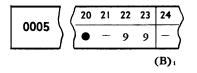

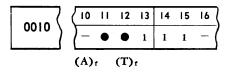

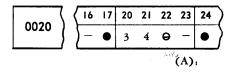

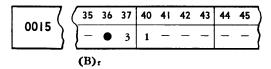

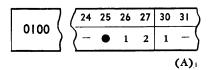

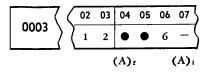

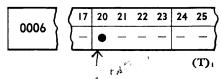

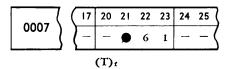

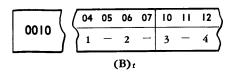

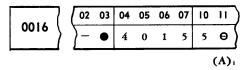

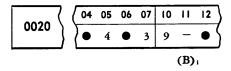

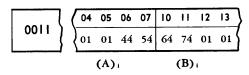

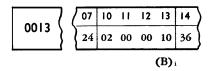

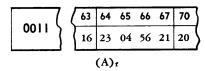

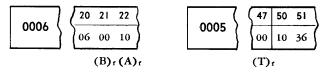

Each of these groups of four locations, or the contents thereof, is called a *tetrad*. A tetrad begins in a location addressed  $(----0)_8$  or  $(----4)_8$  and ends in a location addressed  $(----3)_8$  or  $(----7)_8$ , respectively. In diagrammatic representations of portions of the HSM throughout this manual, tetrads are delineated by heavy vertical lines, as shown below.

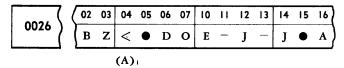

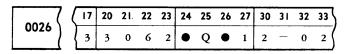

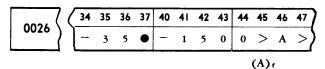

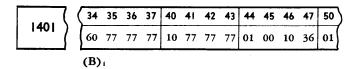

The HSM address of each location shown in the above diagram consists of the two octal digits in the upper portion preceded by the four digits at the left (026106, 026107, etc.). The characters stored in these locations are shown in the lower portion of the diagram.

As stated previously, each character location has a unique address. A tetrad address, however, may be the address of any one of the four locations comprising that tetrad. No matter which one of the four is addressed, the contents of the entire tetrad will be brought into the Memory Register. Depending on the instruction being executed, since some RCA 501 instructions deal with characters singly, and some by tetrads—all four characters in the tetrad, the rightmost three, or only the character from the specified location will be processed.

For convenience in referring to the individual locations or characters within a tetrad, when the specific address is not pertinent, the symbols C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub>, and C<sub>3</sub> are used. These symbols apply to any tetrad in the HSM and to characters in the Memory Register.

The primary purpose of the HSM is the storage of programs and data. These may be stored in any area of the memory, except that the first 164 locations (000000–000243) are reserved as Standard HSM Locations (see Appendix VII). This reserved area stores data used for address modification, special accuracy routines, and data for which special counters would otherwise be required.

# THE BASIC INSTRUCTION

Instruction Format

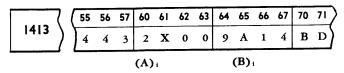

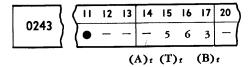

Each of the forty-seven RCA 501 instructions consists of four parts, in the following order:

- 1. Operation Code (a one-character code for add, subtract, item transfer, etc.)

- 2. A Address (three-character HSM address of the augend, minuend, original location of an item, left boundary of a sector, etc.)

- 3. N Character (one-character code that can call for automatic modification of the A and/or the B address; the N character is explained in greater detail under Automatic Address Modification)

- 4. B Address (three-character HSM address of the addend, subtrahend, destination location for an item, right boundary of a sector, etc.)

An instruction, then, is made up of eight RCA characters with the format OAAANBBB.

| О         | $\underbrace{\mathbf{A}\mathbf{A}\mathbf{A}}_{\mathbf{A}}$ | N         | $\underbrace{\text{BBB}}$ |

|-----------|------------------------------------------------------------|-----------|---------------------------|

| Operation | A                                                          | N         | B                         |

| Code      | address                                                    | character | address                   |

In most of the instructions, the entire A address refers to a High-Speed Memory location (or tetrad) and the entire B address refers to another High-Speed Memory location (or tetrad). In these cases, the components of the A address (AAA) or the B address (BBB) need not be differentiated. In some instructions, however, only a portion of the A address or of the B address is used, or one component may designate one value and the other component another value; for example, one part of the A address may be used to specify a symbol and the other part to designate a count, or one part of the B address denotes the Tape Station and the other part is ignored. In these instructions, the components of the A address are referred to as A<sub>1</sub>, A<sub>2</sub> and A<sub>3</sub>, and the components of the B address as B<sub>1</sub>, B<sub>2</sub> and B<sub>3</sub>. This is illustrated below (under Coded Instruction).

Since each location in the High-Speed Memory is individually addressable, whenever instructions do not utilize the entire capacity of the A or B address, it is usually feasible for the programmer to employ the unused (ignored) portion of the address for the storage of constants.

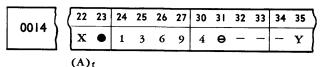

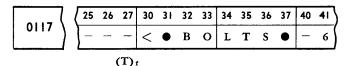

#### Coded Instruction

Instructions are coded in octal notation. Since the octal equivalent of an RCA character consists of two octal digits, a coded instruction will contain sixteen octal digits.

Example of an instruction as coded by the programmer: 16 720003 10 400000

| 16        | 720003<br>A <sub>1</sub> A <sub>2</sub> A <sub>3</sub> | 10        | 400000<br>B <sub>1</sub> B <sub>2</sub> B <sub>3</sub> |

|-----------|--------------------------------------------------------|-----------|--------------------------------------------------------|

| Operation | A                                                      | N         | B                                                      |

| Code      | address                                                | character | address                                                |

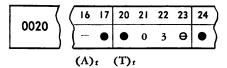

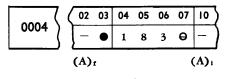

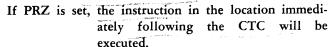

#### Storage of Instructions

Instructions are stored sequentially in the High-Speed Memory. Each instruction is stored in two successive HSM tetrads (eight locations) so that the Operation Code falls in the leftmost  $(C_0)$  location of the first tetrad, with the A address in the remaining three locations  $(C_1, C_2 \text{ and } C_3)$ . The N character and the B address are in the same relative positions in the second tetrad—N in  $C_0$  and B in  $C_1$ ,  $C_2$  and  $C_3$ .

# Staticizing

An instruction can be interpreted and executed by Program Control only after it is brought out of the High-Speed Memory locations in which it has been stored, and its components placed in the proper registers. This process is called *staticizing* and is accomplished in two status levels.

A status level lasts 15 microseconds and is the term applied to a series of pulses which open certain paths over which information can travel. A status level that opens paths leading to or from the High-Speed Memory is called a memory cycle. (Status level and memory cycle are not synonymous, since not all status levels are concerned with opening the paths leading to or from the High-Speed Memory.) Each status level has a specific function. In staticizing of each instruction, the first status level brings the tetrad OAAA into the Memory Register, from which O is sent to the Normal Operation (NO) Register and AAA to the A Register. The second status level brings the tetrad NBBB into the Memory Register, from which N is sent to the N Register and BBB to the B Register.

Thus, staticizing time of 30 microseconds is constant for every instruction. The number of status levels involved, and their sequence, for execution (after staticizing) of a given instruction depends upon what must be accomplished by that instruction.

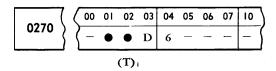

# Automatic Address Modification

The first status level following staticizing checks the two octal digits comprising the N character in the N Register. If these digits are 00, the instruction will be executed as it was stored in the High-Speed Memory. If the first, or left-hand, octal digit is other than 0, the quantity stored in the location indexed by that digit will be added to the contents of the A Register (which has received the A address of the instruction) before the instruction is executed. If the second, or right-hand, octal digit is other than 0, the quantity stored in the location indexed by that digit will be added to the contents of the B Register (which has received the B address of the instruction) before the instruction is executed.

The addition is octal. In effect, subtraction may be performed by storing the eight's complement of the subtrahend (either the unmodified address or the contents of the indexed location). The N character can

thus effect a decrease or increase of the contents of either the A or the B Register, or of both.

Six status levels are used to modify each address. Automatic address modification time, therefore, is 90 microseconds if one address is modified, and 180 microseconds if both addresses are modified.

The locations, and their contents, accessed by the digits of the N character are called *Address Modifiers*. They permit modification not only of addresses, but data also.

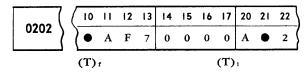

The locations associated with each octal digit that could appear in the N character are as follows:

| Octal Digit | Location of Modifier           |

|-------------|--------------------------------|

| 1           | HSM locations 000111 - 000113  |

| 2           | HSM locations 000221 - 000223* |

| 3           | HSM locations 000131 - 000133  |

| 4           | P Register†                    |

| 5           | HSM locations 000151 - 000153  |

| 6           | T Register                     |

| 7           | HSM locations 000171 - 000173  |

<sup>\*</sup> See STA, page 18.

Four of these Address Modifiers (1, 3, 5 and 7) are static; that is, the contents remain as originally stored unless an instruction specifies that they be altered.

Three of the Address Modifiers (2, 4 and 6) are dynamic. The contents of the P Register will change with each instruction performed; the contents of the T Register will change with each instruction that utilizes this register; the contents of standard HSM locations 000221 – 000223 will change with each instruction in which STA is performed.

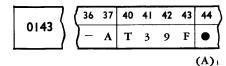

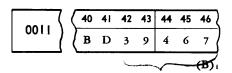

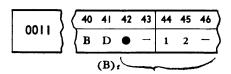

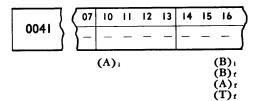

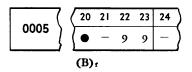

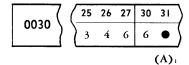

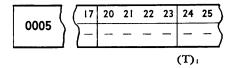

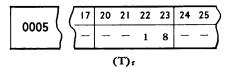

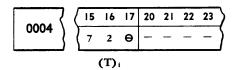

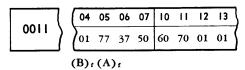

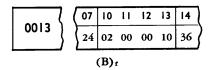

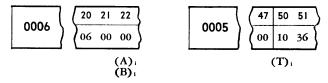

Example of Automatic Address Modification:

Assume the following instruction is stored in HSM locations 000460 - 000467 (000460 serves as the address of this instruction).

Assume, also, that a part of the memory looks like this:

| Address  | 000131 | 000132 | 000133 | 7 |

|----------|--------|--------|--------|---|

| Contents | 04     | 20     | 13     | 3 |

The octal digit 3 in the N character of the instruction will access HSM locations 000131 – 000133 and cause the contents 042013 to be added (octally) to the contents of the B Register (000612). Since the left-hand octal digit of the N character is 0, the contents of the A

Register (003100) will not be changed. Consequently, the instruction actually executed will be

21 003100 00 042625

The instruction remains in HSM locations 000460 – 000467 as it was originally written and stored:

21 003100 03 000612

# PROGRAM CONTROL

Program Control is the arithmetic and control unit of the Computer. It interprets and executes the instructions stored in the High-Speed Memory, directs the sequence of operations in the Computer, controls operation of the on-line input-output devices, and performs the automatic accuracy checks. It includes the circuitry for electronic control, switching and buffering of up to eight input-output trunk lines.

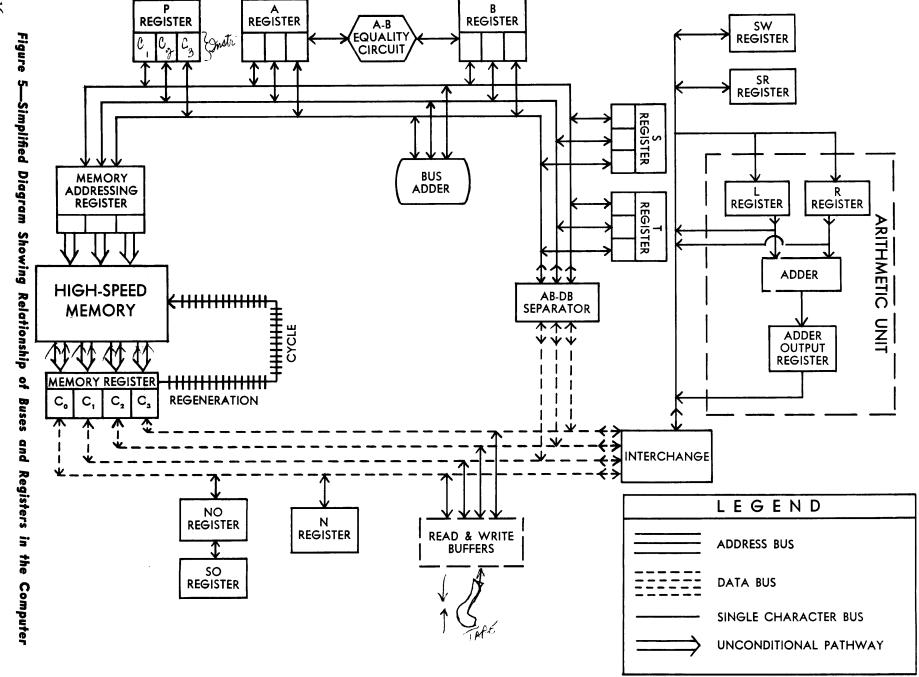

Program Control includes a number of specialized (by function) devices. Those which are of interest to the programmer are diagrammed in Figure 5 and are briefly described below, along with certain automatic Program Control functions.

# Registers

The Memory Addressing Register stores the HSM address of the tetrad to be processed. The capacity of this register is three RCA characters (six octal digits).

The Memory Register has a capacity of four RCA characters. It receives the tetrad contents that emerge from or are to be placed in the High-Speed Memory. A series of Memory Output Gates permit or inhibit entrance into the Memory Register of any or all of the four characters that emerge from the HSM.

The P Register holds the HSM address of the next instruction in sequence.