# Ridge 3200 Processor Reference Manual

(Preliminary)

# PUBLICATION HISTORY

Manual Title: Ridge 3200 Processor Reference Manual

Preliminary Edition: 9091 (DEC 86)

## NOTICE

No part of this document may be translated, reproduced, or copied in any form or by any means without the written permission of Ridge Computers.

The information contained in this document is subject to change without notice. Ridge Computers shall not be liable for errors contained herein, or for incidental or consequential damages in connection with the use of this material.

© Copyright 1983, 1984, 1985, 1986 Ridge Computers. All rights reserved. Printed in the U.S.A.

# PREFACE

This manual provides an overview of the Ridge 3200 processor.

- Chapter 1 lists the characteristics and features of the 3200 processor.

- Chapter 2 describes the logical operation of the individual boards that make up the 3200 processor.

- Chapter 3 describes the Ridge I/O system.

- Chapter 4 describes the Ridge instruction formats and data types.

- Chapter 5 describes the hardware components used by the 3200 to manage processes.

- Chapter 6 describes the operation of traps and interrupts.

- Chapter 7 describes how the 3200 translates virtual addresses to physical addresses.

- Chapter 8 lists the instructions executable in user mode.

- Chapter 9 lists the instructions executable in kernel mode.

## CONVENTIONS USED IN THIS MANUAL

Italics are used to reference items appearing illustrations.

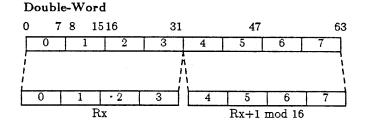

The 16 general registers are referred to as Rx or Ry. A register pair is referenced as RPx and consists of Rx and Rx+1 mod 16. Rx holds the most significant bits and Rx+1 holds the least significant bits.

# TABLE OF CONTENTS

| Chapter 1: OVERVIEW                                |                |

|----------------------------------------------------|----------------|

| INTRODUCTION                                       | 1-1            |

| PROCESSOR CHARACTERISTICS                          | 1-1            |

| KEY FEATURES                                       | 1-2            |

| KET I EXTORES                                      |                |

|                                                    |                |

| Chapter 2: 3200 PROCESSOR ARCHITECTURE             |                |

| INTRODUCTION                                       | 2-1            |

| INTRODUCTIONINSTRUCTION FETCH UNIT                 | 2-3            |

| INSTRUCTION PIPELINE                               | 2-3            |

| BRANCH PREDICTION LOGIC                            |                |

| Conditional Branch Instructions                    | 2-5            |

| Branch Prediction Example                          | 2-5            |

| Unconditional Branch Instructions                  |                |

| REGISTER FILE / MULTIPLIER UNIT                    | 2-7            |

| REGISTER FILE LOGICMULTIPLIER LOGIC                | 2-7            |

| MULTIPLIER LOGIC                                   | 2-7            |

| EXECUTION UNIT                                     | 2-8            |

| REGISTER BYPASS FUNCTION                           |                |

| CACHE / MEMORY CONTROLLER                          | 2-10           |

| CODÉ/DATA CACHE                                    |                |

|                                                    |                |

| Chapter 3: RIDGE I/O SYSTEM                        |                |

| ·                                                  |                |

| INTRODUCTION                                       |                |

| I/O OPERATIONS                                     | 3-2            |

| I/O READ / WRITE                                   | 3-2            |

| I/O Read Operation                                 | 3-3            |

| I/O Write Operation                                | 3-4            |

| I/O INTERRUPTS                                     | ఈరె            |

| Interrupt Operation                                | ) -د           |

| DMA READ / WRITE                                   | ૦-૦            |

| DMA Read Operation  DMA Write Operation            | و-ق<br>10_3    |

| BUS CONTENTION                                     | 3-11           |

| DUAL DAISY-CHAINED SIGNALS                         | 3-11           |

| EXAMPLE OF BUS CONTENTION                          | 3-12           |

| EARTH DE OF BOO COLLECTION                         |                |

|                                                    |                |

|                                                    |                |

| Chapter 4: INSTRUCTION FORMATS AND AD              |                |

| _                                                  | DRESSING       |

| Chapter 4: INSTRUCTION FORMATS AND AD INTRODUCTION | DRESSING<br>41 |

| Register Instruction Format                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                  | 4-2                                                                                                                        |

| Register Instruction FormatMEMORY REFERENCE INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                         | 4-3                                                                                                                        |

| Memory Reference Instruction Formats                                                                                                                                                                                                                                                                                                                                                             | 4-4                                                                                                                        |

| DATA REPRESENTATION                                                                                                                                                                                                                                                                                                                                                                              | 4-5                                                                                                                        |

| INTEGER REPRESENTATION                                                                                                                                                                                                                                                                                                                                                                           | 4-5                                                                                                                        |

| REAL NUMBER REPRESENTATION                                                                                                                                                                                                                                                                                                                                                                       | 4-5                                                                                                                        |

| Single Precision Real Numbers                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

| Double Precision Real Numbers                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

| REAL NUMBERS WITH SPECIAL MEANING                                                                                                                                                                                                                                                                                                                                                                | 4-6                                                                                                                        |

| Special Numbers as Operands                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                            |

| Special Numbers as Results                                                                                                                                                                                                                                                                                                                                                                       | 4-7                                                                                                                        |

| Special Numbers as ResultsREAL NUMBER ROUNDING RULES                                                                                                                                                                                                                                                                                                                                             | 4-9                                                                                                                        |

| DATA STORAGE IN REGISTERS                                                                                                                                                                                                                                                                                                                                                                        | 4-9                                                                                                                        |

| Chapter 5: PROCESS MANAGEMENT                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                     | 5-1                                                                                                                        |

| CODE AND DATA SEGMENTS                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| PROCESSOR MODES                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

| KERNEL MODE                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                            |

| USER MODE                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

| Privileged Process Bit                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| PROCESSOR CONTROL                                                                                                                                                                                                                                                                                                                                                                                | 5-3                                                                                                                        |

| SPECIAL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                | 5-3                                                                                                                        |

| PROCESS CONTROL BLOCK                                                                                                                                                                                                                                                                                                                                                                            | 5-5                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

| Chapter 6: TRAPS AND INTERRUPTS INTRODUCTION                                                                                                                                                                                                                                                                                                                                                     | 6-1                                                                                                                        |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                     | 6-1                                                                                                                        |

| INTRODUCTIONEVENT HANDLING                                                                                                                                                                                                                                                                                                                                                                       | 6-1                                                                                                                        |

| INTRODUCTIONEVENT HANDLINGCPU CONTROL BLOCK                                                                                                                                                                                                                                                                                                                                                      | 6-1<br>6-2                                                                                                                 |

| INTRODUCTION EVENT HANDLING CPU CONTROL BLOCK CCB DATA AREA                                                                                                                                                                                                                                                                                                                                      | 6-1<br>6-2<br>6-4                                                                                                          |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| INTRODUCTION EVENT HANDLING CPU CONTROL BLOCK CCB DATA AREA PAGE FAULT INTERRUPTS DOUBLE-BIT PARITY ERROR                                                                                                                                                                                                                                                                                        |                                                                                                                            |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute                                                                                                                                                                                    |                                                                                                                            |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute                                                                                                                                                                                    |                                                                                                                            |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute  EXTERNAL INTERRUPTS  SWITCH 0                                                                                                                                                     |                                                                                                                            |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute  EXTERNAL INTERRUPTS  SWITCH 0  POWER FAIL WARNING                                                                                                                                 | 6-1<br>6-2<br>6-4<br>6-4<br>6-4<br>6-5<br>6-5<br>6-5<br>6-5                                                                |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute  EXTERNAL INTERRUPTS  SWITCH 0                                                                                                                                                     | 6-1<br>6-2<br>6-4<br>6-4<br>6-4<br>6-5<br>6-5<br>6-5<br>6-5                                                                |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute  EXTERNAL INTERRUPTS  SWITCH 0  POWER FAIL WARNING                                                                                                                                 | 6-1<br>6-2<br>6-4<br>6-4<br>6-5<br>6-5<br>6-5<br>6-5<br>6-6<br>6-6                                                         |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute  EXTERNAL INTERRUPTS  SWITCH 0  POWER FAIL WARNING  TIMER INTERRUPTS  RESET  TRAPS                                                                                                 | 6-1<br>6-2<br>6-4<br>6-4<br>6-5<br>6-5<br>6-5<br>6-5<br>6-6<br>6-6<br>6-6                                                  |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute  EXTERNAL INTERRUPTS  SWITCH 0  POWER FAIL WARNING  TIMER INTERRUPTS  RESET  TRAPS  KERNEL CALLS                                                                                   | 6-1<br>6-2<br>6-4<br>6-4<br>6-4<br>6-5<br>6-5<br>6-5<br>6-5<br>6-6<br>6-6<br>6-6                                           |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute  EXTERNAL INTERRUPTS  SWITCH 0.  POWER FAIL WARNING  TIMER INTERRUPTS  RESET  TRAPS  KERNEL CALLS  DATA ALIGNMENT TRAP                                                             | 6-1<br>6-2<br>6-4<br>6-4<br>6-4<br>6-5<br>6-5<br>6-5<br>6-5<br>6-6<br>6-6<br>6-6<br>6-7<br>6-7                             |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute  EXTERNAL INTERRUPTS  SWITCH 0  POWER FAIL WARNING  TIMER INTERRUPTS  RESET  TRAPS  KERNEL CALLS  DATA ALIGNMENT TRAP  ILLEGAL INSTRUCTION TRAP                                    | 6-1<br>6-2<br>6-4<br>6-4<br>6-4<br>6-5<br>6-5<br>6-5<br>6-5<br>6-6<br>6-6<br>6-7<br>6-7<br>6-7                             |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute  EXTERNAL INTERRUPTS  SWITCH 0  POWER FAIL WARNING  TIMER INTERRUPTS  RESET  TRAPS  KERNEL CALLS  DATA ALIGNMENT TRAP  ILLEGAL INSTRUCTION TRAP  KERNEL VIOLATION TRAP             | 6-1<br>6-2<br>6-4<br>6-4<br>6-4<br>6-5<br>6-5<br>6-5<br>6-5<br>6-6<br>6-6<br>6-7<br>6-7<br>6-7<br>6-7<br>6-7               |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute  EXTERNAL INTERRUPTS  SWITCH 0  POWER FAIL WARNING  TIMER INTERRUPTS  RESET  TRAPS  KERNEL CALLS  DATA ALIGNMENT TRAP  ILLEGAL INSTRUCTION TRAP  KERNEL VIOLATION TRAP  CHECK TRAP | 6-1<br>6-2<br>6-4<br>6-4<br>6-4<br>6-5<br>6-5<br>6-5<br>6-5<br>6-6<br>6-6<br>6-6<br>6-7<br>6-7<br>6-7<br>6-7<br>6-7<br>6-8 |

| INTRODUCTION  EVENT HANDLING  CPU CONTROL BLOCK  CCB DATA AREA  PAGE FAULT  INTERRUPTS  DOUBLE-BIT PARITY ERROR  Double-Bit Parity Error on Instruction Fetch  Double-Bit Parity Error on Instruction Execute  EXTERNAL INTERRUPTS  SWITCH 0  POWER FAIL WARNING  TIMER INTERRUPTS  RESET  TRAPS  KERNEL CALLS  DATA ALIGNMENT TRAP  ILLEGAL INSTRUCTION TRAP  KERNEL VIOLATION TRAP             | 6-1 6-2 6-4 6-4 6-4 6-5 6-5 6-5 6-5 6-5 6-7 6-7 6-7 6-8 6-8                                                                |

| Traps Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-9                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Integer Overflow Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                     |

| Integer Divide By Zero Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                     |

| Before Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                     |

| Real Divide by Zero Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6-12                                                                                                |

| Real Underflow Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                     |

| Real Overflow Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                     |

| Inexact Result Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-14                                                                                                |

| RECOVERY FROM REAL OVERFLOW, UNDERFL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LOW,                                                                                                |

| AND INEXACT RESULT TRAPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6-14                                                                                                |

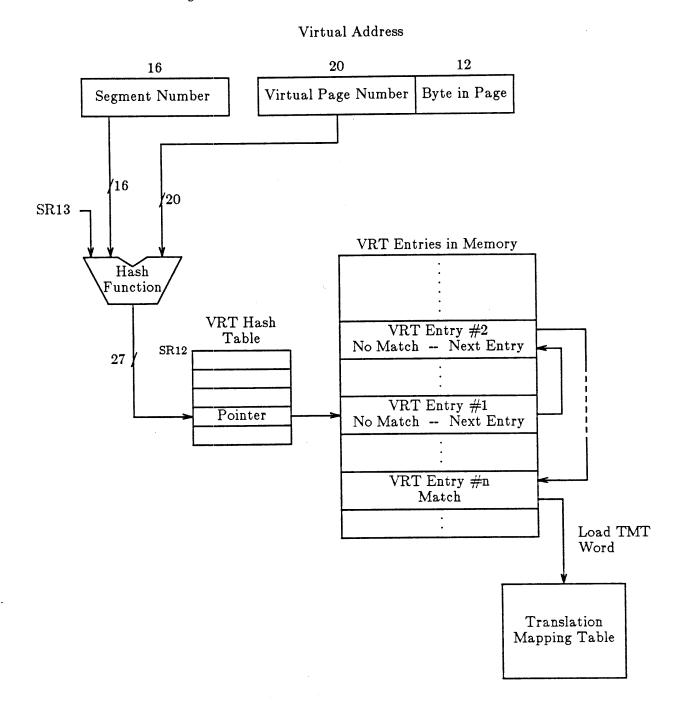

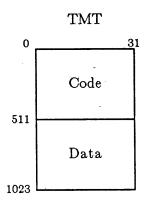

| Chapter 7: VIRTUAL MEMORY MANAGEMEN  INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                     |

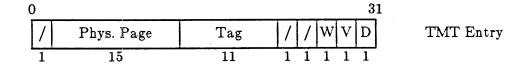

| TMT TABLE ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     |

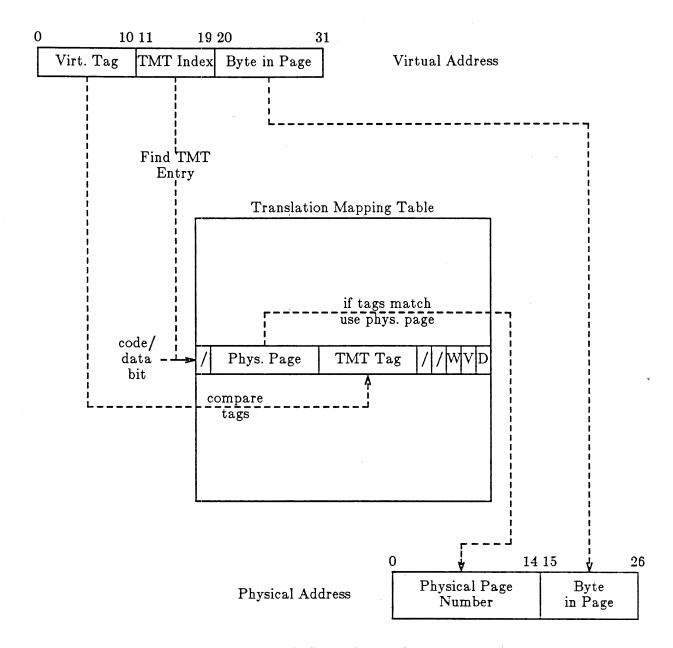

| TMT Entry Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                     |

| TMT Translation Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-7                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                     |

| Chapter 8: USER MODE INSTRUCTIONS  INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8-1                                                                                                 |

| INTRODUCTIONSYNTAX CONVENTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8-1                                                                                                 |

| INTRODUCTIONSYNTAX CONVENTIONSMEMORY REFERENCE INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8-1<br>8-2                                                                                          |

| INTRODUCTIONSYNTAX CONVENTIONSMEMORY REFERENCE INSTRUCTIONS LOAD INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-1<br>8-2<br>8-2                                                                                   |

| INTRODUCTIONSYNTAX CONVENTIONSMEMORY REFERENCE INSTRUCTIONS LOAD INSTRUCTIONSSTORE INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8-1<br>8-2<br>8-2<br>8-3                                                                            |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                     |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                     |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                     |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                     |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                     |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  EXTENDED PRECISION INTEGER INSTRUCTIONS                                                                                                                                                                                                                                                                                                       |                                                                                                     |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  EXTENDED PRECISION INTEGER INSTRUCTIONS  REAL INSTRUCTIONS                                                                                                                                                                                                                                                                                    |                                                                                                     |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  EXTENDED PRECISION INTEGER INSTRUCTIONS  DOUBLE REAL INSTRUCTIONS                                                                                                                                                                                                                                                                             | 8-1 8-2 8-3 8-3 8-3 8-4 8-4 8-5 FIONS 8-6 NS 8-8 8-9                                                |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  EXTENDED PRECISION INTEGER INSTRUCTIONS  DOUBLE REAL INSTRUCTIONS  BIT-ORIENTED INSTRUCTIONS                                                                                                                                                                                                                                                  |                                                                                                     |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  EXTENDED PRECISION INTEGER INSTRUCTION  REAL INSTRUCTIONS  DOUBLE REAL INSTRUCTIONS  BIT-ORIENTED INSTRUCTIONS  TEST INSTRUCTION                                                                                                                                                                                                              |                                                                                                     |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  EXTENDED PRECISION INTEGER INSTRUCTIONS  DOUBLE REAL INSTRUCTIONS  BIT-ORIENTED INSTRUCTIONS  TEST INSTRUCTION                                                                                                                                                                                    |                                                                                                     |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  EXTENDED PRECISION INTEGER INSTRUCTION  REAL INSTRUCTIONS  DOUBLE REAL INSTRUCTIONS  BIT-ORIENTED INSTRUCTIONS  TEST INSTRUCTION  COMPARE INSTRUCTIONS  SHIFT INSTRUCTIONS                                                                                                                                                                    |                                                                                                     |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  EXTENDED PRECISION INTEGER INSTRUCTION  REAL INSTRUCTIONS  DOUBLE REAL INSTRUCTIONS  BIT-ORIENTED INSTRUCTIONS  TEST INSTRUCTION  COMPARE INSTRUCTIONS  SHIFT INSTRUCTIONS  SIGN EXTEND INSTRUCTIONS                                                                                                                                          |                                                                                                     |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  EXTENDED PRECISION INTEGER INSTRUCTION  REAL INSTRUCTIONS  DOUBLE REAL INSTRUCTIONS  BIT-ORIENTED INSTRUCTIONS  TEST INSTRUCTION  COMPARE INSTRUCTIONS  SHIFT INSTRUCTIONS  SIGN EXTEND INSTRUCTIONS  PROGRAM CONTROL INSTRUCTIONS                                                                | 8-1 8-2 8-2 8-3 8-3 8-4 8-4 8-4 8-5 FIONS 8-6 NS 8-7 8-8 8-10 8-10 8-11 8-12 8-13                   |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTOR  EXTENDED PRECISION INTEGER INSTRUCTION  REAL INSTRUCTIONS  DOUBLE REAL INSTRUCTIONS  BIT-ORIENTED INSTRUCTIONS  TEST INSTRUCTION  COMPARE INSTRUCTIONS  SHIFT INSTRUCTIONS  SIGN EXTEND INSTRUCTIONS  PROGRAM CONTROL INSTRUCTIONS  BRANCH INSTRUCTIONS                                                                                         | 8-1 8-2 8-2 8-3 8-3 8-3 8-4 8-4 8-5 FIONS 8-6 NS 8-7 8-8 8-10 8-10 8-11 8-12 8-13 8-14              |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  EXTENDED PRECISION INTEGER INSTRUCTIONS  DOUBLE REAL INSTRUCTIONS  BIT-ORIENTED INSTRUCTIONS  TEST INSTRUCTION  COMPARE INSTRUCTIONS  SHIFT INSTRUCTIONS  SIGN EXTEND INSTRUCTIONS  PROGRAM CONTROL INSTRUCTIONS  BRANCH INSTRUCTIONS  LOOP CONTROL INSTRUCTIONS                                  |                                                                                                     |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  EXTENDED PRECISION INTEGER INSTRUCTIONS  DOUBLE REAL INSTRUCTIONS  BIT-ORIENTED INSTRUCTIONS  TEST INSTRUCTION  COMPARE INSTRUCTIONS  SHIFT INSTRUCTIONS  SHIFT INSTRUCTIONS  PROGRAM CONTROL INSTRUCTIONS  BRANCH INSTRUCTIONS  LOOP CONTROL INSTRUCTION  SUBROUTINE CALL AND RETURN INSTRUCTION | 8-1 8-2 8-2 8-3 8-3 8-4 8-4 8-4 8-5 FIONS 8-6 NS 8-7 8-8 8-10 8-10 8-11 8-12 8-13 8-14 8-15 NS 8-16 |

| INTRODUCTION  SYNTAX CONVENTIONS  MEMORY REFERENCE INSTRUCTIONS  LOAD INSTRUCTIONS  STORE INSTRUCTIONS  LOAD ADDRESS INSTRUCTIONS  REGISTER INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL OPERATOR INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  INTEGER AND LOGICAL IMMEDIATE INSTRUCTIONS  EXTENDED PRECISION INTEGER INSTRUCTIONS  DOUBLE REAL INSTRUCTIONS  BIT-ORIENTED INSTRUCTIONS  TEST INSTRUCTION  COMPARE INSTRUCTIONS  SHIFT INSTRUCTIONS  SIGN EXTEND INSTRUCTIONS  PROGRAM CONTROL INSTRUCTIONS  BRANCH INSTRUCTIONS  LOOP CONTROL INSTRUCTIONS                                  | 8-1 8-2 8-2 8-3 8-3 8-4 8-4 8-4 8-5 FIONS 8-6 NS 8-7 8-8 8-10 8-10 8-11 8-12 8-13 8-14 8-15 NS 8-16 |

| TRAP INSTRUCTIONS                       |     |

|-----------------------------------------|-----|

| Chapter 9: KERNEL MODE INSTRUCTIONS     |     |

| INTRODUCTION                            | 9-1 |

| STATE SWITCHING INSTRUCTIONS            | 9-1 |

| MAINTENANCE INSTRUCTIONS                | 9-3 |

| VIRTUAL MEMORY SUPPORT INSTRUCTIONS     | 9-7 |

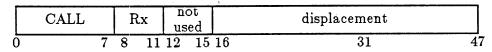

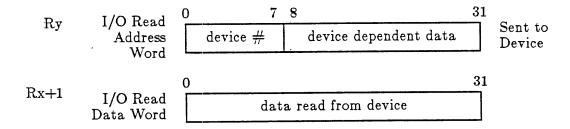

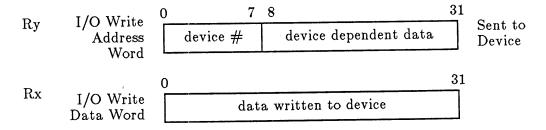

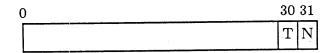

| INPUT/OUTPUT INSTRUCTIONS               | 9-7 |

| APPENDIX A: INSTRUCTION INDEX           | A-1 |

| APPENDIX B: INSTRUCTION EXECUTION TIMES | B-1 |

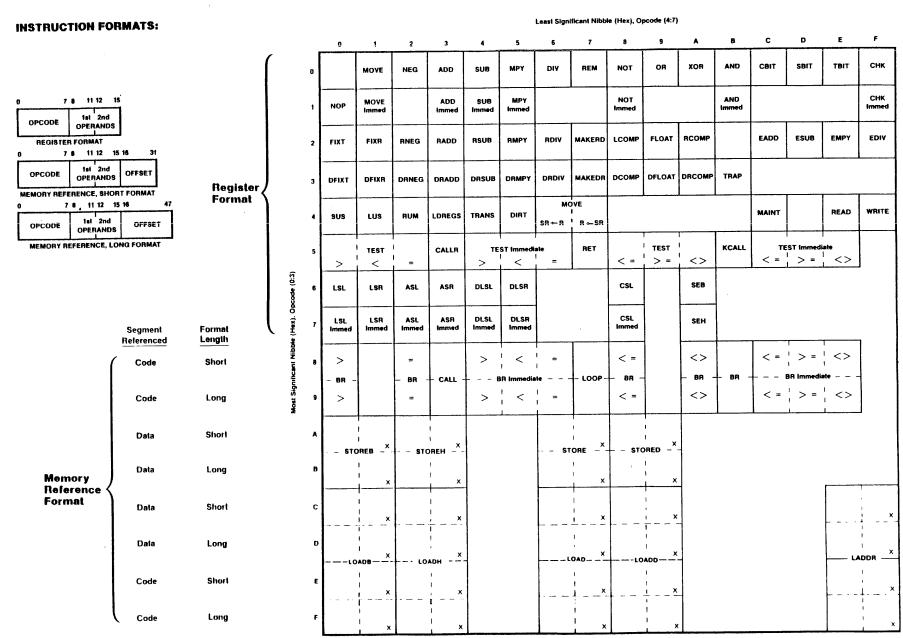

| APPENDIX C: RIDGE OPCODE MAP            |     |

# Chapter 1 OVERVIEW

# INTRODUCTION

The Ridge 3200 is a 32-bit high performance RISC (Reduced Instruction Set Computer) processor implemented in MSI and LSI bipolar logic. The The 3200 has a simple, general purpose, microcoded architecture that incorporates paged virtual memory.

The main objective of RISC architecture is to simplify the functions of the machine, thereby reducing the amount of hardware necessary to implement the processor. The reduction in logic allows a faster cycle time and permits instructions to complete in one machine cycle.

This functional simplification is made possible by reducing the size and complexity of the processor's instruction set. With fewer and simpler instructions, the RISC-based computer is able to execute programs faster and with greater reliability.

## PROCESSOR CHARACTERISTICS

The Ridge 3200 is characterized by the following:

Simple addressing modes. The Ridge 3200 uses only three modes which reduces the amount of logic needed to perform memory references.

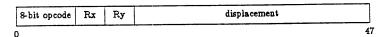

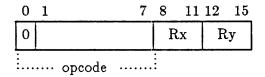

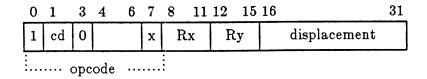

Simple instruction formats. The Ridge 3200 uses three instruction formats that can be decoded with a minimum of logic.

Separated code and data. The Ridge 3200 uses separated code and data eliminating the need for logic that detects and resolves self-modifying code.

High-level language support. The instructions provided are designed to match the code generation capabilities of such languages as FORTRAN, C, and Pascal. The Ridge 3200 instruction set provides simple, quickly-executable instructions which are assembled into their optimum function sequences by the Ridge compilers.

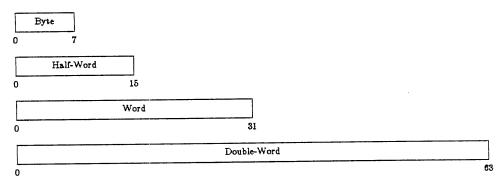

Regularity. Data types and addressing modes are examples of regularity. For memory reference instructions there are four operand sizes and three addressing modes. Each of the addressing modes is available for all operands.

Linear address space. Code and data space are each linear with a byte-addressable area that is four-gigabytes long.

General registers. All registers are available for use as data, indexing, and addressing.

3200 Processor Overview

# **KEY FEATURES**

- Reduced Instruction Set Computer (RISC) Architecture

- 83-nanosecond Processor Cycle Time

- 83-nanosecond Cache Cycle Time and 250-nanosecond access time to Main Memory

- One-clock Cycle Minimum Instruction Time

- 4096-byte paged virtual memory

- Four-gigabytes Linear Address Space

- Separated Code and Data

- Branch Prediction Logic

- Single and Double Real Floating Point Instructions

- 16 General Registers

# Chapter 2 3200 PROCESSOR ARCHITECTURE

# INTRODUCTION

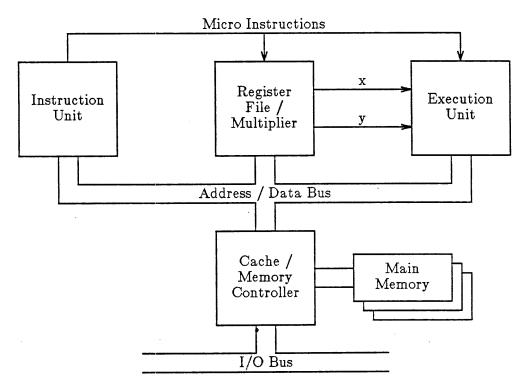

The Ridge 3200 processor consists of four printed circuit boards. These are:

- Instruction Unit

- Register File / Multiplier

- Execution Unit

- Cache / Memory Controller

A private bus to the memory controller provides separate 32-bit address and data lines. The instruction unit and execution unit can each access main memory through the cache. Memory access time for a LOAD instruction is 250 nanoseconds, which includes virtual-to-real memory translation and error correction.

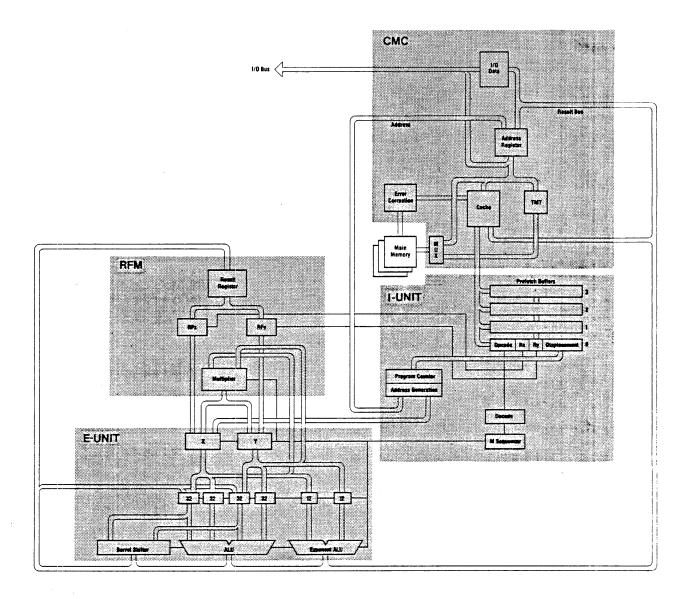

The general organization of the 3200 processor is illustrated in Figure 2-1. A more detailed block diagram of the processor is illustrated in Figure 2-2. References to the processor components illustrated in Figure 2-2 appear as *italics* in the course of this chapter.

Figure 2-1. General Organization of 3200 Processor

3200 Processor Architecture

Figure 2-2. Internal Structure of the 3200 Processor

3200 Processor Architecture

# INSTRUCTION UNIT

The instruction unit (I-UNIT) performs instruction prefetch and decoding. It contains 4 prefetch buffers, decode, address generation, branch prediction, and interrupt logic. The I-unit also contains a microsequencer with 4 banks of control store to provide four-way branching.

The I-unit fetches instructions from the cache ahead of the execution unit and stores them in four word-wide prefetch buffers. Typically, instructions are held in the prefetch buffers before entering a 3-stage instruction pipeline. However, if the prefetch buffers are empty, the I-unit can fetch instructions directly from the cache.

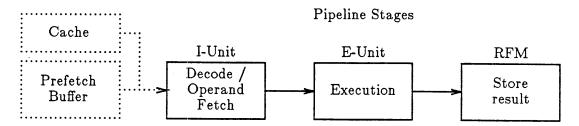

#### INSTRUCTION PIPELINE

The instruction pipeline is composed of three stages: decode/operand fetch, execution, and store result. Each pipeline stage performs its function in one processor cycle. The stages of the processor instruction pipeline are illustrated below.

When the I-unit places an instruction in the pipeline, the following sequence begins:

Decode & Operand Fetch. This first pipeline stage is performed in the I-unit. The Rx and Ry operands in the instruction are used to enable the register select logic. The decoder interprets the instruction to determine what function is to take place. And the microsequencer begins executing microcode.

Execution. The Execution Unit operates on Rx and Ry, the result either passes through the ALU or the barrel shifter and is stored in the result register.

Store Result. The data is moved from the result register into the RFx and RFy register files in the RFM Unit.

The purpose of the pipeline is to increase machine throughput by using parallelism. In a single clock cycle, an instruction can be fetched from memory, another instruction can be decoded, while another instruction is executed and the results produced for another instruction are stored. By pipelining instructions in this way, results can be produced as frequently as every clock cycle.

| Cycles | Cache or<br>Prefetch<br>Buffer | Decode &<br>Operand<br>Fetch | Execute          | Store<br>Result |

|--------|--------------------------------|------------------------------|------------------|-----------------|

| 1      | instruction 1                  |                              |                  |                 |

| 2      | instruction 2                  | instruction 1                |                  |                 |

| 3      | instruction 3                  | instruction 2                | instruction<br>1 |                 |

| 4      | instruction 4                  | instruction 3                | instruction 2    | instruction 1   |

| 5      | -                              | instruction 4                | instruction<br>3 | instruction 2   |

| 6      | -                              |                              | instruction 4    | instruction 3   |

| 7      |                                |                              |                  | instruction 4   |

Figure 2-3. Instruction Flow Through Pipeline Stages

# BRANCH PREDICTION LOGIC

The implementation of branch instructions is critical to the performance of pipelined machines. Without branch prediction, a conditional branch instruction would empty the pipeline, preventing the processor from prefetching the next instruction until the outcome of the branch has been determined.

For this reason, branches can be among the slowest instructions on high performance machines. The Ridge processor incorporates branch prediction logic which loads the instruction that is the most likely result of the branch. This keeps the pipeline full and reduces the chance that the pipeline will be loaded with instructions on the wrong path.

#### Conditional Branch Instructions

Conditional branch instructions contain a static prediction bit in the instruction displacement field that can be set by a compiler. The branch prediction logic in the instruction unit then fetches along the predicted path. This keeps the pipeline full and makes conditional branch instructions fast.

# **Branch Prediction Example**

Consider Pascal REPEAT ... UNTIL loops. The loop is constructed by the compiler as a linear section of code ended with a conditional branch. This branch is part of the UNTIL expression. Usually these loops are executed more than once, so the compiler marks the conditional branch at the bottom of the loop to be "predicted."

When the program is executed, the processor fetches and executes all the instructions in the linear portion of the loop. As the instruction unit decodes the conditional branch at the end of the loop, the prediction bit is detected. Instead of fetching the next sequential instruction as it normally would, the instruction unit fetches the instruction at the top of the loop, which is the branch target. This prefetching the location of the branch target allows loops to execute at the same speed as linear sections of code.

As the loop is executed for its last time, the instruction unit incorrectly fetches the instruction at the top of the loop. This time the UNTIL condition has been reached, and the loop has ended. Now the instruction unit must flush this instruction, then fetch the next sequential instruction to be executed.

An incorrectly predicted conditional branch instruction causes a 1 cycle delay. Measurements have shown this to be infrequent and overall program speed to be increased by the use of the branch prediction logic.

For example, the following PASCAL program:

```

I := 0;

REPEAT;

J := I;

I := I+1;

UNTIL I=100;

```

can be represented by the following instructions:

The following illustrates the path of each instruction through each stage of the pipeline:

| Proc.<br>Cycles | Cache or<br>Prefetch<br>Buffer | Decode &<br>Operand<br>Fetch | Execute | Store<br>Result | Comments                                                                      |

|-----------------|--------------------------------|------------------------------|---------|-----------------|-------------------------------------------------------------------------------|

| 1               | MOVE                           |                              |         |                 |                                                                               |

| 2               | : ADD :                        | MOVE                         |         |                 |                                                                               |

| 3               | BR :                           | ADD                          | MOVE    |                 | 1st MOVE executed                                                             |

| 4               | : :<br>:                       | BR                           | ADD     | MOVE            | Prediction bit detected 1st ADD executed                                      |

| 5               | MOVE                           |                              | BR      | ADD             | Check Branch Condition<br>BR target (MOVE) fetched                            |

| 6               | ADD                            | MOVE                         |         |                 |                                                                               |

| 7               | BR :                           | ADD                          | MOVE    |                 | 2nd time through loop -<br>second MOVE executed                               |

| 8               | <del></del> :                  | BR                           | ADD     | MOVE            | 2nd ADD executed                                                              |

| 9               | MOVE                           |                              | BR      | ADD             |                                                                               |

| •               | •                              | •                            | • .     | •               |                                                                               |

| n               | ···-                           | BR                           | ADD     | MOVE            | Branch Prediction                                                             |

| n+1             | MOVE                           |                              | BR      | ADD             | <ul><li>I = 100, loop complete</li><li>Incorrectly Predicted Branch</li></ul> |

| n+2             | STORE                          | -                            | _       |                 | Flush pipeline. Fetch STORE instruction                                       |

| n+3             | : <b>-</b> :                   | STORE                        |         |                 | STORE instruction decoded                                                     |

| n+4             | i <del>-</del> i               | _                            | STORE   | _               |                                                                               |

| n+5             | i <del>-</del>                 | _                            | STORE   |                 |                                                                               |

| n+6             | -                              | _                            | _       | STORE           |                                                                               |

Figure 2-4. Branch Prediction Example

#### Unconditional Branch Instructions

Unconditional branch instructions also make use of the branch prediction and decode logic in the instruction unit. In unconditional branches, the instruction is decoded, the target location is fetched and placed in the instruction stream.

# REGISTER FILE / MULTIPLIER UNIT

The Register File / Multiplier (RFM) unit contains the register file and multiplication logic. Both the Register File and Multiplier portions are double clocked. In all other respects, these portions are functionally independent of one another.

#### REGISTER FILE

The register file portion of the RFM consists of two register files: RFx and RFy. The RFx register file is made up of 16 general registers, 16 special purpose registers, and a scratch pad area for storing intermediate results and constants. The contents of the RFx register file are duplicated in the RFy register file. Duplicating the registers allows both Rx and Ry to be accessed in a single clock cycle.

During an instruction execution, the register file is accessed in the operand fetch cycle for reading the data from a given register(s) and in store cycle for writing the result back into a given register(s). Since instructions overlap, both read and write capability in a single cycle is required. This is accomplished by dividing the clock cycle into two halves. The first half is used for write access and the second half is for read access.

#### MULTIPLIER

The multiplier operates on integers and the mantissa portion of floating point numbers.

The multiplier is based on a modified version of Booth's recoded algorithm with overlapped scanning to process 4 bits during each half-clock cycle. This allows 2 4-bit multiplies to be done in parallel during each clock cycle.

The RFM unit supports five different modes of multiplication:

- Integer Multiply; 32 x 32-bit with 32-bit product.

- Integer (Immediate) Multiply; 32 x 4-bit with 32-bit product.

- Extended Integer Multiply; 32 x 32-bit with 64-bit product.

- Single Precision Real Multiply; 24 x 24-bit with 25-bit mantissa product.

- Double Precision Real Multiply; 53 x 53-bit with 54-bit mantissa product.

During floating point multiplication, instructions are unpacked and the exponent portion of the operands set to the *E-unit* and the mantissa portion loaded into the *RFM* operand registers. The product of the mantissas is then sent to the *E-unit*, where post normalization and rounding are performed. The product is then merged with the exponent.

# **EXECUTION UNIT**

The arithmetic logic units (ALU), barrel shifter, and register bypass hardware are all contained in the Execution Unit (E-UNIT). The 64-bit barrel shifter can shift up to 64 bits left, right, or circularly in a single clock cycle.

The general data flow for numbers through the execution unit is as follows: Data is fetched from the RFx and RFy register files in the  $Register\ File\ /\ Multiplier\ (RFM)$  unit; put into the x and y registers; operated on by the ALU, then temporarily held in the  $result\ register$  before being stored in the register files. Should data not yet stored in the RFM unit be needed in a computation, the register select logic may bypass the RFM unit and use the data on the bus as input to the ALU.

The execution of floating point instructions is made more efficient by unpacking and sending the exponent to the exponent ALU and the mantissa to the standard ALU. The 64-bit barrel shifter packs (reassembles) the results from the registers into floating point values.

#### REGISTER BYPASS FUNCTION

The execution unit incorporates register bypass hardware that avoids the "pipeline interlock" delay that results when an instruction's operand is dependent on an instruction still in the pipe.

The register bypass function can be illustrated by the following two-instruction sequence that utilizes the register bypass data path in the execution unit. This example also illustrates the use of the instruction pipeline discussed earlier.

The following instruction sequence executes as shown in the table below:

ADD R6, R7; R6 is added to R7 and the sum is put in R6. AND R5, R6; R5 logically ANDs with R6 and the result is put in R5.

| Instruction Pipeline Stage Operation |                                                               |                                                                                                                                                                                                                                    |  |  |

|--------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Clock<br>Cycle                       | ADD                                                           | AND                                                                                                                                                                                                                                |  |  |

| 1                                    | The ADD instruction is fetched.                               |                                                                                                                                                                                                                                    |  |  |

| 2                                    | R6 and R7 are fetched from the register files.                | The AND instruction is fetched.                                                                                                                                                                                                    |  |  |

| 3                                    | The ALU ADDs R6 and R7, and puts the new R6 value on the bus. | R5 and R6 are to be fetched, but the new R6 value is on the bus, not in the register file. R5 is fetched from the register file, while the Ry register select logic bypasses the register file and uses the R6 value from the bus. |  |  |

| 4                                    | The new R6 value is stored in the register file               | The ALU ANDs R5 with R6 and puts the new R5 value on the bus.                                                                                                                                                                      |  |  |

| 5                                    |                                                               | The new R5 value is stored in the register file.                                                                                                                                                                                   |  |  |

During clock cycle 3, the AND instruction must fetch its operand R6. However, the value of R6 in the RFM unit is outdated due to the ADD instruction computing a new R6 value. Consequently, the register bypass is used. This moves instructions through each pipeline stage in one clock cycle, and allows the pipeline to complete one instruction each clock cycle.

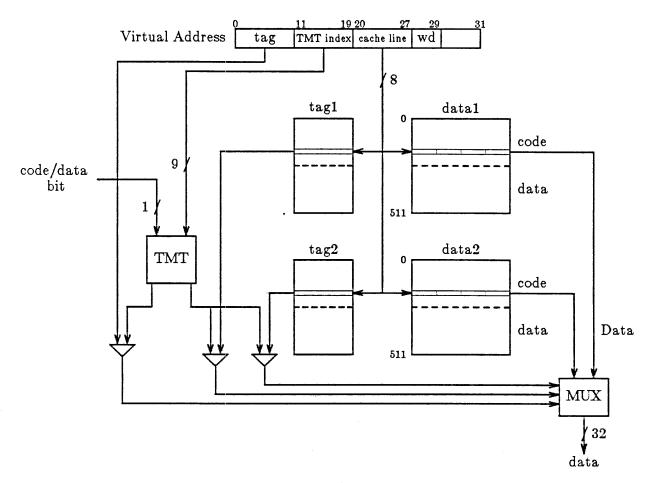

# CACHE / MEMORY CONTROLLER

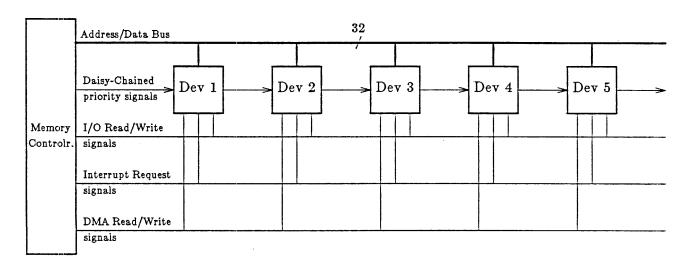

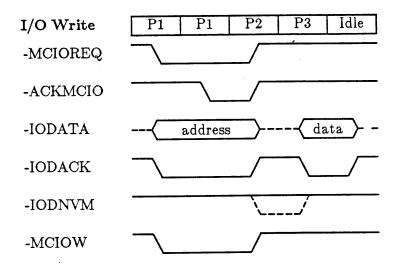

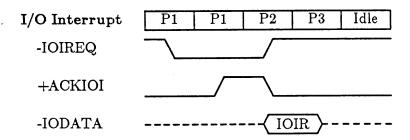

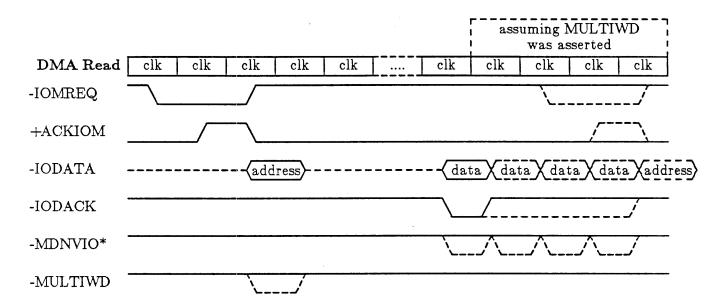

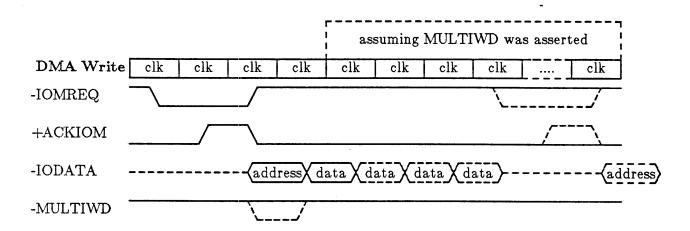

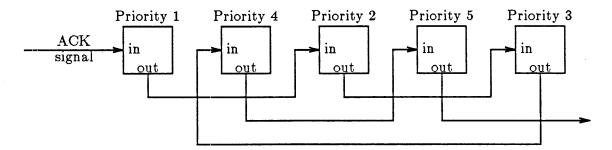

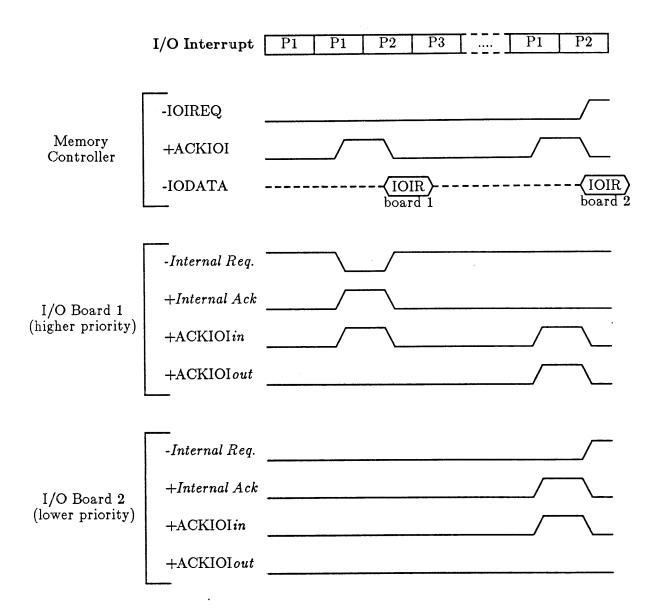

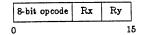

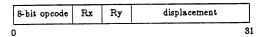

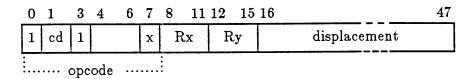

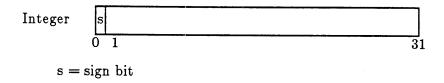

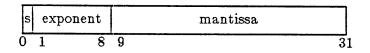

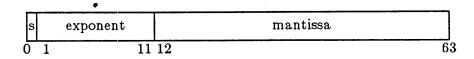

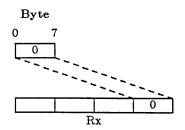

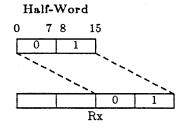

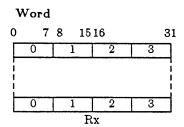

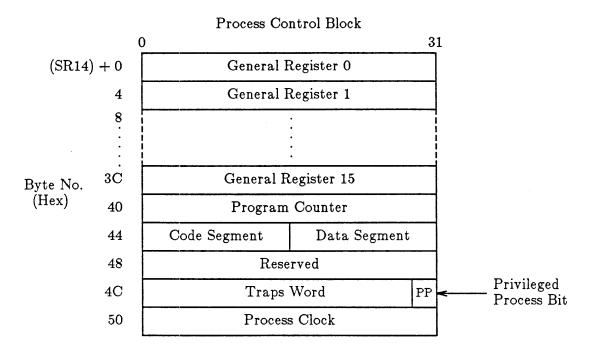

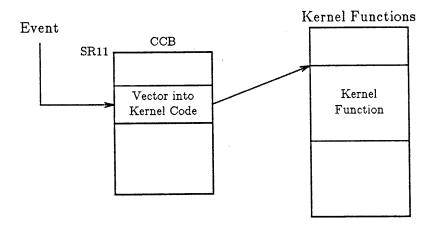

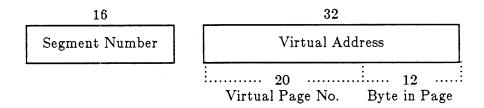

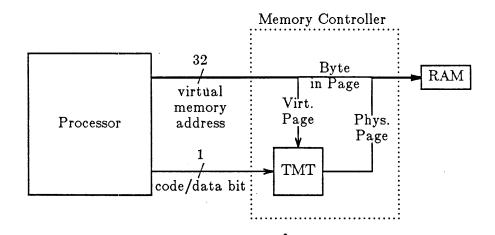

The Cache / Memory Controller (CMC) contains the virtual-to-real translation hardware, error correction logic, a 16k-byte code/data cache, and handles all memory data for the processor and I/O devices. All virtual memory accesses from the processor go through the translation mapping table (TMT) where they are converted to real addresses and presented to the code/data cache and/or main memory. I/O devices on the I/O bus use real addresses and bypass the translation mapping table (TMT).