PRELIMINARY EDITION

ROAR

RPC-4000

Optimizer &

Assembly

Routine

## MANUAL FOR PROGRAMMERS AND OPERATORS

## R O A R

The optimizer and assembly routine  $for\ the$   $RPC\text{-}4000\ electronic\ computer}$

## TABLE OF CONTENTS

| I   | Introduction                        | 1  |

|-----|-------------------------------------|----|

| II  | A Brief Description of the RPC 4000 | 4  |

| III | The Assembly Program                | 21 |

| IV  | Addresses                           | 24 |

| V   | Pseudo Operations                   | 31 |

| VI  | Operation Codes                     | 37 |

| VII | Programming Using ROAR              | 39 |

| III | Programming Examples                | 40 |

| IX  | Input Tape Preparation              | 49 |

| X   | Output Format                       | 52 |

| ХT  | Operator's Instructions             | 53 |

#### INTRODUCTION

The object of an assembly program is to allow the programmer to code instruction for instruction like actual machine language, but to be relieved of the extra chores of optimizing, keeping track of used locations, etc. With the "one over one" addressing system of the RPC-4000, optimization is doubly necessary. It was with these considerations in mind that the first major program for the RPC-4000 should be a symbolic assembler and optimizer.

The overall scheme is this:

The programmer codes his program either in symbolic language or a combination of symbolic language and machine language. The program is then processed by ROAR.

The output of ROAR is of a dual nature. There are

- 1. A hex tape of the assembled program.

- 2. A decimal copy of the assembled program along with a reproduction of the input.

These provide the programmer with a ready means of loading his program as well as a complete record for error correction and program checkout.

On the following pages will be presented a list of definitions of the terms and abbreviations used in the rest of the manual. U Upper half of the double length accumulator

L Lower half of the double length accumulator

X Index register

C Command register

FWA First word address, as of table

LWA Last word address

Lo First location of, as a table

LOC Location, as of an instruction

D-ADDR Data address; bits 5 through 17 of the

command word

N-ADDR Next address, the address where the next

instruction is located. Also bits 18-30 of the

command word

ORDER The instruction code. Bits 0-4 of the command

word

SUBROUTINE A part of a program. A program used as a part

of a larger program to perform a specific function

SYMBOLIC ADDRESS A symbol to which ROAR assigns a machine address.

A symbol contains at least one character that is

not numeric

RECRC Refers to track 127, the 8 word recirculating

track

DB Double Access code

BLOCK An area of sequential drum storage

PROGRAM Unless specified as assembly program, program

refers to the object program - the program being

coded

BC Branch control, an internal sense toggle and

overflow indicator

Replace (Replaces)

NU Not used

PSEUDO OPERATION

An instruction to the assembly program. It takes the same form as an instruction and is reproduced on the printed output. It is not output into the program tape.

AVAILABLE

An available memory location may be used by ROAR for assignment as an instruction or constant, at which time it is made unavailable.

UNAVAILABLE

A memory location is unavailable when it has been reserved through a pseudo-op or assigned by the assembler. Double access tracks and RECRC are unavailable unless specifically made available.

RESERVE

To make a memory location unavailable

REPEAT MODE

The mode of operation in which the execution of an instruction is repeated as specified

q

Applies to the scaling convention we use. Q represents the bit position in the data word that separates integer from fraction. Mathematically: the number to be represented is equal to the data word (which is considered as a fraction) multiplied by  $2^q$

#### A BRIEF DESCRIPTION OF THE RPC-4000

This chapter is designed to provide a programmer s view of the RPC-4000 and to acquaint the reader with some of the terms used by the assembler.

#### MAIN MEMORY

The memory consists of 8192 addresses broken into 128 tracks of 64 sectors. Some of these addresses are redundent as we shall see. Tracks 000 through 122 contain nothing special and may be referred to directly. Tracks 123 and 124 are the leading heads of two double access tracks and, if double access is not to be used, may be used as two more tracks of main memory. Track 125 is the trailing head 16 word times behind the head of track 123; track 126 trails the head of track 124 by 24 word times.

Track 127 is an eight word recirculating line (RECRC). In other words, the group of eight words represented by sectors 00 - 07 is duplicated 8 times as 08 - 15, 16 - 23, etc.

The following table will show the correspondence between the various sectors of track 127 as well as provide a presentation of modulo 8 equivalence for later consideration. The RECRC notation will be discussed in Chapter IV. All the sectors on each line refer to a single word of memory.

| RECRCO or RECRC8 | 00  | 08 | 16 | 24 | 32 | 40 | 48 | 56 |

|------------------|-----|----|----|----|----|----|----|----|

| RECRC1           | 01  | 09 | 17 | 25 | 33 | 41 | 49 | 57 |

| RECRC2           | 02  | 10 | 18 | 26 | 34 | 42 | 50 | 58 |

| RECRC3           | 03  | 11 | 19 | 27 | 35 | 43 | 51 | 59 |

| RECRC4           | 04  | 12 | 20 | 28 | 36 | 44 | 52 | 60 |

| RECRC5           | 05  | 13 | 21 | 29 | 37 | 45 | 53 | 61 |

| RECRC6           | 0.6 | 14 | 22 | 30 | 38 | 46 | 54 | 62 |

| RECRC7           | 07  | 15 | 23 | 31 | 39 | 47 | 55 | 63 |

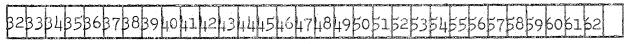

Figure 1

#### COMMAND EXECUTION

The normal operation of the "one over one" address system is as follows:

As an instruction enters the C register, the indicated operation is performed upon the memory location specified by the D address. The next instruction to be executed is located in the memory location given in the N address.

#### TIMING

Instruction timing is generally discussed in terms somewhat removed from direct application to programming. We speak of n milliseconds access time or an addition requiring X microseconds. For the purposes of the programmer this is cumbersome. We plan to relate instruction timing to optimization and, for this purpose, two time units are sufficient.

They are:

1. The drum revolution

1/60 second

16 2/3 millisecond

2. The word time

1/64 drum revolution 260.4 microsecond

The time required for word transfer

between registers and memory

For this discussion we will neglect the track since nothing in timing depends on it.

Let us begin, as in COMMAND EXECUTION, with an instruction entering the C register. At this point the computer is entering phase 3 of a four phase operation. During phase 3 the computer is concerned with waiting while the drum rotates until the next sector is the one specified in the D address. The minimum time for phase 3 is one word time, so that for best optimization the D sector will be two greater than the sector in which the instruction is located.

As an illustration

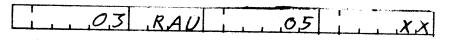

#### SECTOR OCCURRENCE

03 Instruction came from sector 3

04 Phase 3 Search for "next sector is it" NOW:

05 Operand sector

06

This is the most optimum case. Consider a case which is less optimum:

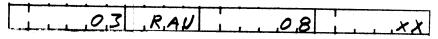

#### SECTOR OCCURRENCE

03 Instruction came from sector 3

04 Phase 3 Search for "next sector is it" Wait

05 Wait

06 Wait

07 Now

08 Operand Sector

09

Once the computer establishes that the next sector is the operand sector, phase 4 is entered. Phase 4 is the execution phase of the instruction (see below).

Phase 3 is limited to one word time on the following instructions:

| HLT-SNS | 00 | SRL  | 12 |

|---------|----|------|----|

| CXE     | 01 | SLC  | 13 |

| LDX     | 07 | PRD* | 16 |

| INP     | 08 | PRU* | 17 |

so that the sector used is generally immaterial.

The time in phase 4 depends upon the instruction being executed:

Shift orders take 4 word times plus 1 word time for each bit position shifted.

The multiply and both divide orders require 67 word times of execution.

The input order is variable, depending upon the number of characters read.

All other orders require 1 word time in phase 4.

After execution, phase 1 is entered. Phase 1 is the search for the sector of the next instruction and requires a minimum of one word time in the same manner as phase 3. In phase 2, the instruction enters the command register and the cycle is complete.

As an example, consider the following instruction sequence:

|     | Location | Order | Data<br>Address | Next<br>Address |

|-----|----------|-------|-----------------|-----------------|

| (1) | 5.0.0    | RAU   | 3,07            | 3.12            |

| (2) | 3.1.2    | ADU   | 14              | 5.15            |

|     |          |       |                 |                 |

\*Sectors of print orders must not be first optimum unless it is desired to bypass the print interlock.

| SECTOR TIME | ACTIVITY |                                       |

|-------------|----------|---------------------------------------|

| 00          | Phase 2  | Command 1 enters C register           |

| 01          | Phase 3  | Search for sector 07 to be next       |

| 02          |          |                                       |

| 03          |          |                                       |

| 04          |          |                                       |

| 0 <i>5</i>  |          |                                       |

| 06          | 07 is ne | ext                                   |

| 07          | Phase 4  | Contents of 0307 to upper             |

| 08          |          | Begin search for sector 12            |

| 09          |          |                                       |

| 10          |          |                                       |

| 11          | 12 is ne | xt                                    |

| 12          | Phase 2  | Command 2 to C register               |

| 13          | Phase 3  |                                       |

| 14          |          | Add C(0014) to upper                  |

| 15          |          | Begin search for sector 15: Long wait |

#### Note

- 1. Command 1 is moderately optimum .

- 2. Execution of command 2 is first optimum.

- 3. The N address of command 2 calls for the least optimum sector.

Print orders require one word time for execution. Further printing will be held up by an interlock until the previous print stroke is completed.

To summarize instruction timing for the RPC-4000, the following table will illustrate in terms of the phase structure.

| Phase      | Activity                                                                                                                                  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1.         | Search to determine that the next sector contains the instruction: 1 to 64 word times                                                     |

| <b>72.</b> | Copy instruction into command register adding indexing portion of X register if indexed: 1 word time                                      |

| 3          | Search to determine that the next sector contains operand: 1 to 64 word times (phase 3 is lamited to 1 word time on certain instructions) |

|            | Execution of command. This is a fixed or variable amount and depends upon the order.                                                      |

## Note About Repeat Mode

Repeat mode operation means extended phase 4 operation. In repeat mode, the execution portion (phase 4) is extended (or repeated) as many times as the count indicates (see repeat mode of operation page 11).

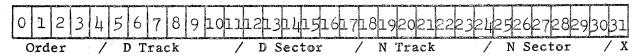

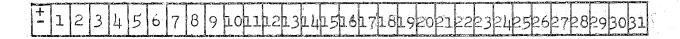

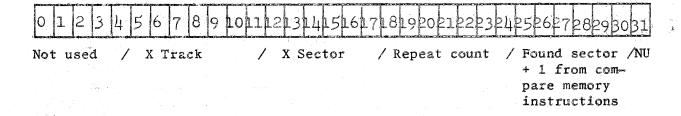

## WORD STRUCTURE

#### Command Word

#### Data Word

Lower Accumulator when used as lower  $\frac{1}{2}$  of product, numerator for division. When used for other functions it uses the data word form.

NU

## INDEX REGISTER

#### REGISTERS

The RPC-4000 has four registers:

| 1. | Command Register  | С            |

|----|-------------------|--------------|

| 2. | Upper Accumulator | U            |

| 3. | Lower Accumulator | $\mathbf{L}$ |

| 4. | Index Register    | X            |

## Command Register C

The command register analyzes the instruction word. The general interpretation of most commands is: Perform the indicated operation upon the contents of the memory location specified by the D address and find the next instruction in the location specified by the N address.

## Upper Accumulator U

The Upper is a one word accumulator capable of arithmetic use. It holds the multiplicand and high order product for multiplication, the high order portion of the dividend and the quotient for division and its sign bit is checked by the test on minus instruction.

## Lower Accumulator L

The lower accumulator may be specified by programming as one or eight words in length. It may be added to, subtracted from, and shifted in conjunction with the upper. During addition and subtraction there is no carry between upper and lower, nor between units of the 8 word lower.

For division L holds the lower half of the dividend, then the remainder. For multiplication it holds the lower half of the double length product. After a shift and count its D address bits hold the number of places shifted.

L is utilized as a mask holder for the compare memory instructions.

#### Index Register X

The X register has several varied uses as follows:

1. Its primary use is as an index register:

If an instruction is indexed, i. e., it contains the index bit (a one at 31), the D address portion of the index register is added to the D address of the instruction as it goes into the command register. The index register portion may be loaded by use of the LDX (07) order. It may be incremented by an indexed LDX order: "Load the X register with the D address of the LDX order, after adding in the previous contents of the X register."

The index register portion of the X register may be tested by use of the CXE (01) order followed by a TBC (23) order.

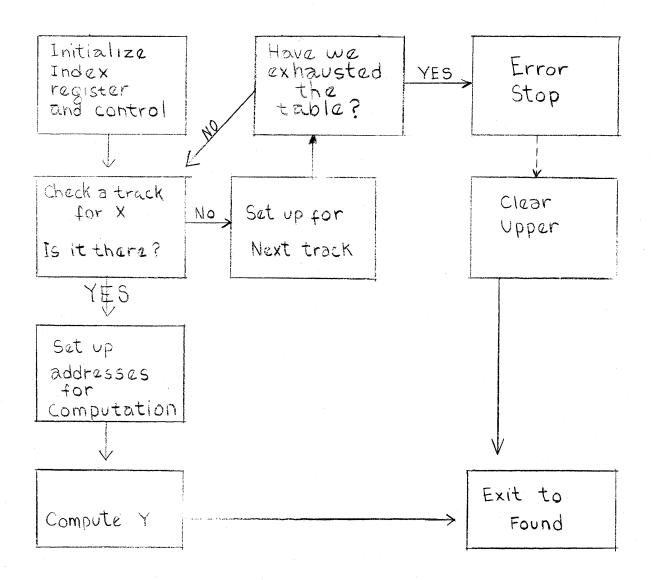

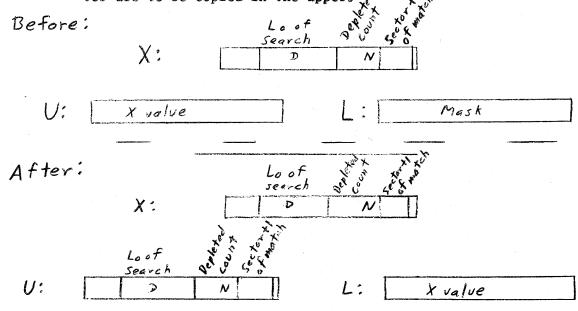

- 2. For repeat mode instructions, e. g., using the compare memory orders as a table look-up, adding a column of figures, etc., the N track holds and counts down the repeat count.

- 3. On the compare memory instructions, one greater than the sector where found, or one greater than the last sector searched (if not found), is placed in the N sector of the X register.

- 4. When not otherwise in use, the X register, through the use of the EXC (09) order, becomes a word of immediate access, high speed storage.

#### Branch Control

The Branch Control is not truly a register but an internal toggle which is capable of being in an on or off position.

The following conditions will turn it on:

A. Overflow conditions resulting from:

Add and subtract in either upper or lower Either divide

- B. Shifting a bit left beyond the normalized position in the upper.

- C. Successful compare (memory, X) instructions

- D. A successful match on SNS (00) instruction

The Branch Control is turned off in the following ways:

A, As the first step in executing these instructions:

SNS (00) Sense (not halt)

CXE (01) Compare index register

CME (20) Compare memory equal

CMG (21) Compare memory greater than or equal

B. Upon execution of the TBC (23) instruction (if on)

#### SPECIAL FEATURES

## Lengthened Lower Accumulator

The lower accumulator may be either one or eight words in length as determined by the EXC (09) order. The 16's bit in the D track of the exchange

command changes it to 8 word length; the 32°s bit changes it to one word length. The lengthened Lower may be read into, and may perform all arithmetical instructions that the one word Lower is capable of, either one word at a time by judicious placing of an operand in memory, or several words at a time by making use of the repeat mode of operation.

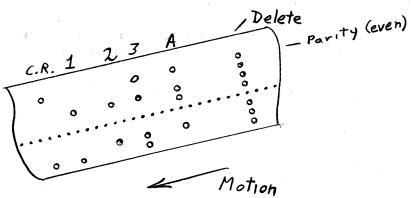

The programmed timing for the 8 word Lower is quite straightforward. It is timing modulo 8. A word entering the 8 word Lower from memory sector zero, for example, may only be operated on, stored into or replaced from a sector zero location, modulo 8; that is sector 0,8,16,24,32,40,48, or 56, of a track. (See figure 1.)

It is suggested that shifting be not done when the lower is lengthened. If programmed, left shifting into the upper will be a bit in turn from each of the lowers for the duration of the shift.

#### Repeat Mode

If the LDC (06) instruction is executed, the N track of the X register will be replaced by the corresponding bits from the memory location specified in the D address, and the execution of the succeeding instruction will be repeated as many times as given in that count.

An example of this operation will be given in Programming Example 1 on page 40 following the discussion on coding. This tool is expected to prove very powerful, for it enables us to perform table look-up (repeated CME or CMG), add a column of numbers (repeated ADU), move blocks of data (repeated RAL, STL coupled with the 8 word Lower), etc..

Track switching is not possible in repeat mode. For example, assume a count of 5 is loaded, followed by a CME (20) 0960 XX. The locations searched are 0960, 0961, 0962, 0963, 0900, 0901 in that order.

#### Command Structure

The following table provides a brief description of the RPC 4000 command structure:

| ORDER  | ORDER  | D ADI        | DRESS    | OPERATION                                                                                                                           | ٠.                               | EFFECT ON                             | *                               |

|--------|--------|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------|---------------------------------|

| SYMBOL | NUMBER | TRACK        | SECTOR   |                                                                                                                                     | U                                | L                                     | X                               |

| HLT    | 00     | 000          | Any      | HALT                                                                                                                                | N.U.                             | N.U.                                  | Index                           |

| SNS    | 00     | <b>≠</b> 000 | Any      | SENSE No operation. Turn the Branch Control on if a track bit (or more) corresponds                                                 | N <sub>•</sub> U <sub>•</sub>    | N.U.                                  | Index                           |

|        |        | •            |          | to a depressed sense switch on the console. The track 64 bit will always turn the Branch Control on.                                |                                  |                                       |                                 |

| CXE    | 01     | A            | В        | COMPARE X EQUAL  1. Turn the BC off.                                                                                                | N.U.                             | N.U.                                  | D addr.<br>compared<br>Indexing |

|        |        |              |          | <ol> <li>Compare the bits of the D address with the corresponding bits of the X register.</li> <li>If equal, turn BC on.</li> </ol> |                                  |                                       | is re-<br>dundent               |

| RAU    | 02     | A            | <b>B</b> | RESET - ADD UPPER Replace the contents of U with the contents of memory location A B                                                | C(AB) → U                        | N.U.                                  | Index                           |

| RAL    | 03     | A            | В        | RESET - ADD LOWER Replace the contents of L with the contents of memory location AB                                                 | N.U.                             | C(AB) → L                             | Index                           |

| SAU    | 04     | <b>A</b> .   | В        | STORE ADDRESS FROM UPPER                                                                                                            |                                  | • • • • • • • • • • • • • • • • • • • |                                 |

|        |        |              |          | Store the D portion of U in the location specified by AB, leaving the rest of the word unchanged                                    | D copied<br>Register<br>1eft un- | N.U.                                  | Index                           |

|        |        |              |          | of the word unchanged                                                                                                               | changed                          |                                       |                                 |

| MST.   | 05     | <b>A</b> .   | В        | MASKED STORE Where U contains 1°s store L into                                                                                      | Mask                             | Data                                  | Index                           |

|        |        |              |          | memory location AB; where U contains O's, leave the memory location unaltered                                                       |                                  | word                                  |                                 |

|        |        |              |          |                                                                                                                                     |                                  |                                       |                                 |

| ORDER<br>SYMBOL | OR DER<br>NUMBEI | D A    | DDRESS<br>K SECTO | OPERATION<br>R                                                                                                |                       | EFFECT      | On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|------------------|--------|-------------------|---------------------------------------------------------------------------------------------------------------|-----------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDC             | 06               | Α      | В                 | LOAD COUNT                                                                                                    | U                     | L           | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 |                  |        |                   | Replace the contents of the N track of the X register with the                                                | N.U.                  | N.U.        | C(AB)→C(N track)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LDX             | 0.7              | ·      |                   | bits of memory location AB. Execute the next instruction in repeat mode, repeating by the amount placed in X. |                       |             | Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LDA             | 07               | A      | В                 | LOAD X                                                                                                        |                       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                  |        |                   | Load the indexing portion of the X register (the D address) with AB, the D portion of the LDX order           | N.U.                  | N.U.        | $AB \rightarrow C(D \text{ addr.})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TAID            |                  |        |                   | INPUT                                                                                                         |                       |             | Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| INP<br>INP      | 08               | 000    | N.U.              | Read: 4 bit                                                                                                   |                       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| INP             | 08               | 064    | N.U.              | Read: 6 bit                                                                                                   |                       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                  |        |                   | If L is at 1 word length, read into the                                                                       |                       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                  |        |                   | If L is at 8 word length, read into L.  No other values of the D.                                             |                       |             | Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 |                  |        |                   |                                                                                                               |                       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                  |        |                   | read. This read is diffe                                                                                      |                       |             | * .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 |                  |        |                   | LGP-30 in that there is no shift prior to the first digit entering                                            |                       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EXC             | 09               | 01     | D                 |                                                                                                               |                       |             | Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 |                  | 01     | В                 | EXCHANGE                                                                                                      |                       |             | znacz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                 | · · · · (        | )2     |                   | Replace the contents of the Lower with the contents of the Upper. $L \rightarrow U$                           |                       | <b>&gt;</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                  | )4     |                   | $U \rightarrow X$                                                                                             |                       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                  | 8      |                   | $X \rightarrow U$                                                                                             |                       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | 1                | 6 Tim: | ing               | Lower to 8 word length                                                                                        | And the second second |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | 3<br>6           | 2 Tim: | ing               | Lower to 1 word length<br>Unspecified as yet                                                                  | The second second     |             | The state of the s |

|                 |                  |        |                   | Any combination of D-track bits is acceptable                                                                 |                       |             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 |                  |        |                   |                                                                                                               |                       |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ORDER    | ORDER  |       | DRESS      | OPERATION                                                                                                                                                |                       | FFECT ON               |       |

|----------|--------|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|-------|

| SYMBOL   | NUMBER | TRACK | SECTOR     |                                                                                                                                                          | Ŭ                     | ${f L}$                | X     |

| DVU      | 10     | A     | В          | DIVIDE UPPER divide the Upper by C(AB): retain the quotient in U and the remainder in L                                                                  | Dividend,<br>Quotient | 0,<br>Remainder        | Index |

| DIV      | 11     | A     | . <b>B</b> | DIVIDE Divide the double length accumulator                                                                                                              | High                  | Low                    | Index |

|          |        |       |            | by C(AB)                                                                                                                                                 | dividend,<br>Quotient | dividend,<br>Remainder |       |

| SRL      | 12     | 000   | В          | SHIFT RIGHT OR LEFT Shift the double length accumulator right by B bits.                                                                                 |                       |                        | Index |

| <i>(</i> | 12     | 001   | В          | Shift the double length accumulator left by B bits. If an overflow is detected, turn BC on.                                                              | <b>4</b>              |                        | Index |

| SLC      | 13     | N.U.  | N.U.       | SHIFT LEFT AND COUNT<br>Normalize the double length number.<br>Shift left until the most significant                                                     | -                     |                        | Index |

|          |        |       |            | bit is in the high order position of<br>the upper. After shifting clear the<br>lower to zeroes and place the number of<br>bits shifted in D sector of L. | 11                    |                        |       |

| MPY 14 A B MULTIPLY Clear the lower to zero. Multiply the upper accumulator by the contents of memory location AB and develop the product in the double length accumulator.  MPT 15 000 B MULTIPLY BY TEN Multiply the upper accumulator by 10.  064 B Multiply the lower accumulator by 10.  PRD 16 A≪64 B PRINT DATA ADDRESS Print the character represented by A on the selected output device.  A≥64 B Select the input and/or output device,  A≥64 B PRINT FROM UPPER Print the left four bits of the upper as channels 5 and 6 from D track of print order  O64 B Print the left six bits of the upper Sign and N.U. Independent of the print order  O64 B Print the left six bits of the upper Sign and left 5 bits.                                                                                                                                                                                                     |   | RDER   | ORDER  |               |        |                                                                                                                                            |              |            |            |  |  |  |  |  | D ADI | DRESS | OPERATION | EFFECT ON |  |  |