# H-81-0027

# COMPUTER GRAPHICS DISPLAY SYSTEM SERIES 8000

TERMINAL CONTROLLER

MAINTENANCE MANUAL

Information Products Division Federal Systems Group

DANIEL WEBSTER HIGHWAY, SOUTH-NASHUA, NEW HAMPSHIRE 03061

603 - 885 - 4321

Sanders Associates, Inc. reserves the right to modify the products described in this manual and to make corrections or alterations to this manual at any time without notice.

First Edition - April 1981

Reprint - September 1981

Reprint - November 1981

# TABLE OF CONTENTS

| Section |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                       | Page                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 1       | GE NE RAL                                                                                                                            | INFORMATION                                                                                                                                                                                                                                                                                                           | 1-1                                                                                                         |

|         | 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7                                                             | Introduction Component Description Terminal Controller Input Devices Output Devices Terminal Controller Physical Description Power and Environmental Requirements Performance Specifications Equipment Identification Test Equipment Required Related Publications Mnemonics Conventions                              | 1-1<br>1-1<br>1-11<br>1-11<br>1-12<br>1-13<br>1-14<br>1-14<br>1-14<br>1-14                                  |

| 2       | OPERATIO                                                                                                                             | ис                                                                                                                                                                                                                                                                                                                    | 2-1                                                                                                         |

|         | 2.1<br>2.2<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4                                                                         | General Controls and Indicators Turn-On Procedure Operating Procedures Normal Operating Procedures Local Mode Commands Standard Transfer Table Operator Performance Checks Turn-Off Procedure                                                                                                                         | 2-1<br>2-1<br>2-1<br>2-3<br>2-3<br>2-8<br>2-13<br>2-13                                                      |

| 3       | THEORY                                                                                                                               | OF OPERATION                                                                                                                                                                                                                                                                                                          | 3-1                                                                                                         |

|         | 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6 | General Signal/Bus Structure Processor Bus Raster Bus Power Bus Processor Bus Control and Timing Bus Control Logic Bus Control Timing Interrupt Logic Read/Write Memory Physical Description Functional Description Operation Operator Checkout Procedure Theory of Operation Detailed Description Parallel Interface | 3-1<br>3-1<br>3-1<br>3-4<br>3-4<br>3-5<br>3-6<br>3-6<br>3-9<br>3-12<br>3-12<br>3-17<br>3-17<br>3-20<br>3-34 |

# TABLE OF CONTENTS (Cont)

| Section |          |                                                  | Page  |

|---------|----------|--------------------------------------------------|-------|

|         | 3.5.1    | Signal Connections                               | 3-34  |

| Ar.     | 3.5.2    | Parallel Interface Internal Buses                | 3-35  |

|         | 3.5.3    | Major Circuits                                   | 3-35  |

|         | 3.5.4    | Operation                                        | 3-39  |

|         | 3.6      | Multiport Serial Interface                       | 3-57  |

|         | 3.6.1    | Major Circuits                                   | 3-58  |

|         | 3.6.2    | Operation                                        | 3-63  |

|         | 3.7      | Display Processor                                | 3-69  |

|         | 3.8      | ROM and Status Card                              | 3-77  |

|         | 3.9      | Digital Graphic Controller                       | 3-91  |

|         | 3.9.1    | Physical Description                             | 3-91  |

|         | 3.9.2    | Application                                      | 3-91  |

|         | 3.9.3    | Functional Description                           | 3-91  |

|         | 3.9.4    | Block Diagram Description                        | 3-93  |

|         | 3.9.5    | Detail Operation                                 | 3-98  |

|         | 3.10     | Mapping Memory                                   | 3-113 |

|         | 3.10.1   | Physical Description                             | 3-113 |

|         | 3.10.2   | Application                                      | 3-113 |

|         | 3.10.3   | Functional Description                           | 3-113 |

|         | 3.10.4   | Block Diagram Description                        | 3-114 |

|         | 3.10.5   | Detailed Operation                               | 3-116 |

|         | 3.10.6   | Operating Sequence                               | 3-110 |

|         | 3.11     | Video Controller                                 | 3-127 |

|         | 3.11.1   |                                                  | 3-133 |

|         | 3.11.2   | Application                                      | 3-133 |

|         | 3.11.3   | Functional Description                           | 3-133 |

|         | 3.11.4   | Block Diagram Description                        | 3-133 |

|         | 3.11.5   | Detailed Operation                               | 3-133 |

|         | 3.12     | Timing Module                                    | 3-130 |

|         | 3.12.1   | Physical Description                             | 3-160 |

|         | 3.12.2   |                                                  | 3-160 |

|         | 3.12.3   | Functional Description                           | 3-162 |

|         | 3.12.3   | runceional bescription                           | J-102 |

| 4       | INSTALLA | ATION                                            | 4-1   |

|         | 4.1      | Environmental Considerations                     | 4-1   |

|         | 4.2      | Equipment Cabinet                                | 4-1   |

|         | 4.3      | Power Panel Assembly                             | 4-1   |

|         | 4.3.1    | Alternative Power Panel Assembly                 | 4-3   |

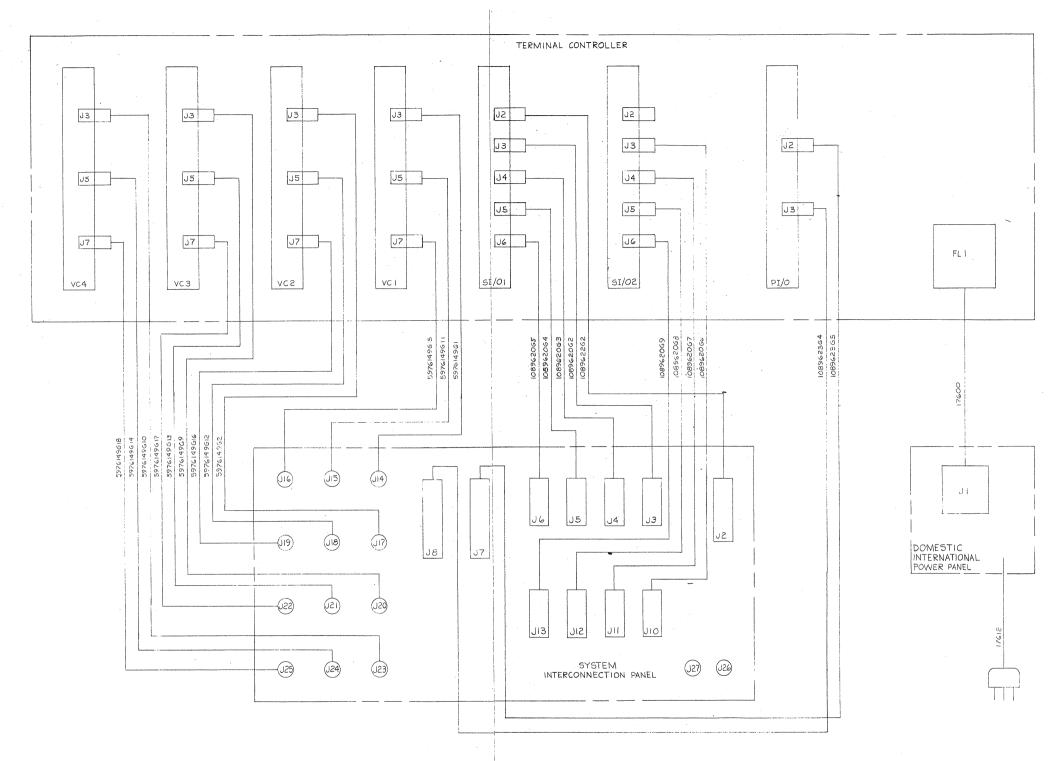

|         | 4.4      | System Interconnect Panel Assembly               | 4-4   |

| •       | 4.5      | Connections to be Made at Installation           | 4-4   |

|         | 4.5.1    | Terminal Controller Mounted in Equipment Cabinet | 4-4   |

|         | 4.5.2    | Terminal Controller without Equipment Cabinet    | 4-7   |

|         | 4.6      | Switch and Jumper Selections                     | 4-10  |

|         | 4.6.1    | Display Processor                                | 4-10  |

|         | 4.6.2    | Read/Write Memory                                | 4-10  |

| •       | 4.6.3    | ROM and Status Card                              | 4-11  |

|         | 4.6.4    | Multiport Serial Interface                       | 4-13  |

|         | 4.6.5    | Parallel Interface                               | 4-17  |

|         | 4.6.6    | Other Cards                                      | 4-20  |

|         |          |                                                  |       |

# TABLE OF CONTENTS (Cont)

| Section  |                                                                                                                                                                                                                                                                                                                         | ' Page                                                         |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 5        | MAINTENANCE                                                                                                                                                                                                                                                                                                             | 5-1                                                            |

|          | 5.1 General 5.2 Maintenance Philosophy 5.3 Test Equipment Required 5.4 Troubleshooting Required 5.4.1 Built-In Diagnostics 5.4.2 Terminal Verification Pattern 5.4.3 Additional Hints 5.5 Adjustments 5.6 Repair 5.6.1 Circuit Card Replacement 5.6.2 Chassis Mounted Components 5.6.3 Special Handling for MOS Devices | 5-1<br>5-1<br>5-1<br>5-1<br>5-2<br>5-3<br>5-16<br>5-19<br>5-19 |

| APPENDIX | A RELATED PUBLICATIONS                                                                                                                                                                                                                                                                                                  | A-1                                                            |

|          | LIST OF ILLUSTRATIONS                                                                                                                                                                                                                                                                                                   |                                                                |

| Number   |                                                                                                                                                                                                                                                                                                                         | Page                                                           |

| 1-1.     | Typical GRAPHIC 8 System Configuration                                                                                                                                                                                                                                                                                  | 1-2                                                            |

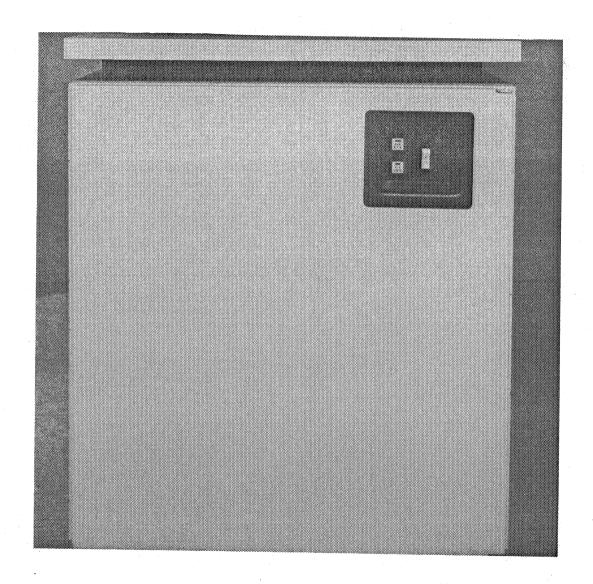

| 1-2.     | GRAPHIC 8 Terminal Controller and Monitor                                                                                                                                                                                                                                                                               | 1-3                                                            |

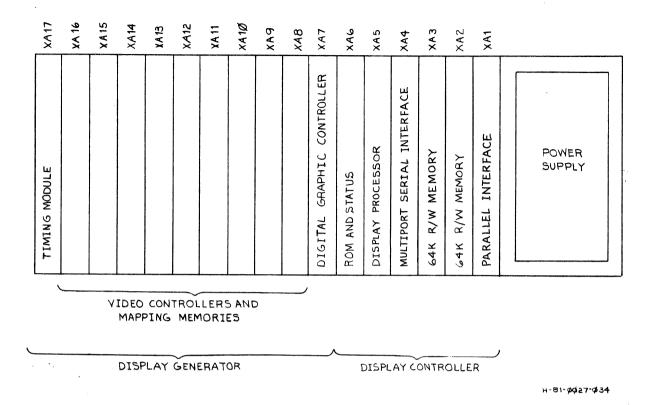

| 1-3.     | GRAPHIC 8 Terminal Controller Organization                                                                                                                                                                                                                                                                              | 1-4                                                            |

| 1-4.     | GRAPHIC 8 System Memory Map                                                                                                                                                                                                                                                                                             | 1-6                                                            |

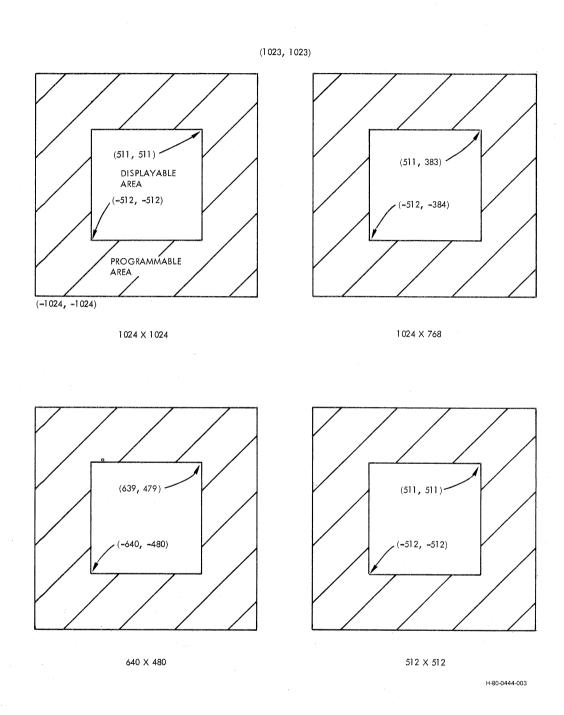

| 1-5.     | Addressable vs. Displayable Areas for Four Screen Resolutions                                                                                                                                                                                                                                                           | 1-8                                                            |

| 1-6.     | Typical Terminal Controller Card Locations                                                                                                                                                                                                                                                                              | 1-13                                                           |

| 2-1.     | Terminal Controller Controls and Indicators                                                                                                                                                                                                                                                                             | 2-2                                                            |

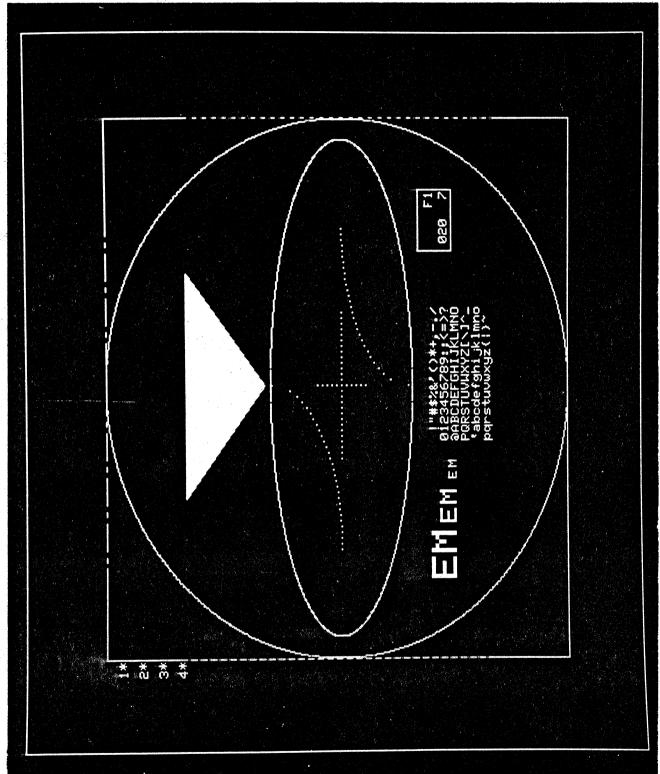

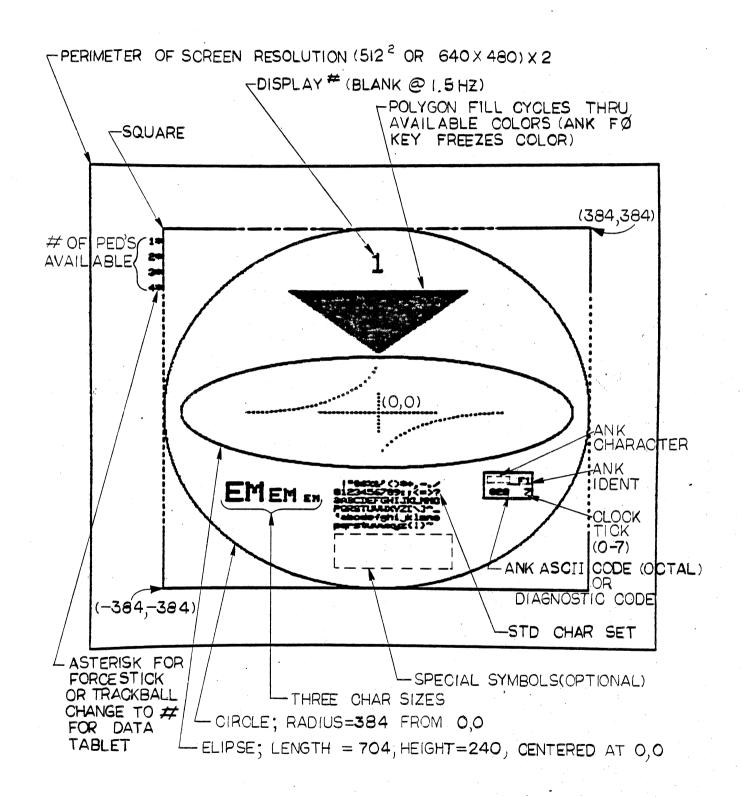

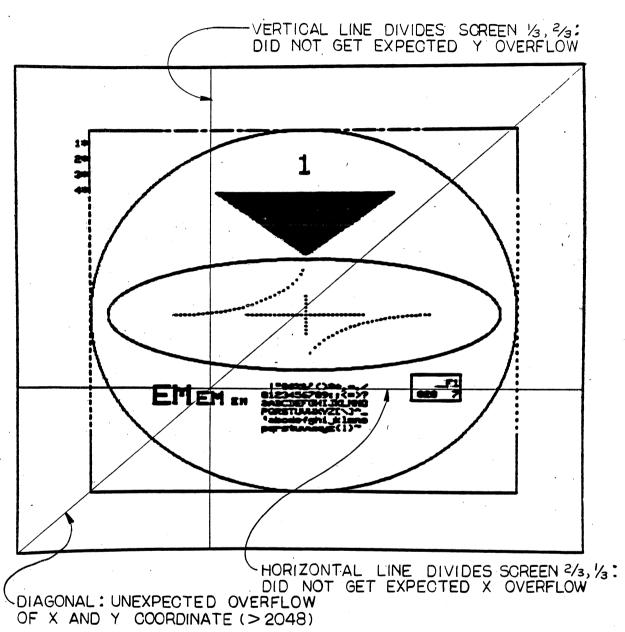

| 2-2.     | Verification Test Pattern                                                                                                                                                                                                                                                                                               | 2-6                                                            |

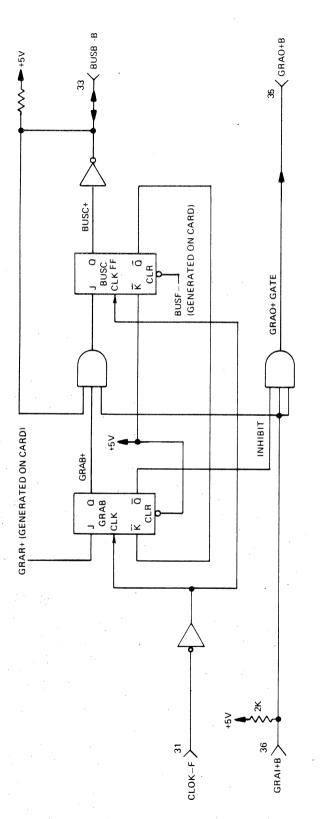

| 3-1.     | Bus Grant Circuit, Simplified Diagram                                                                                                                                                                                                                                                                                   | 3-8                                                            |

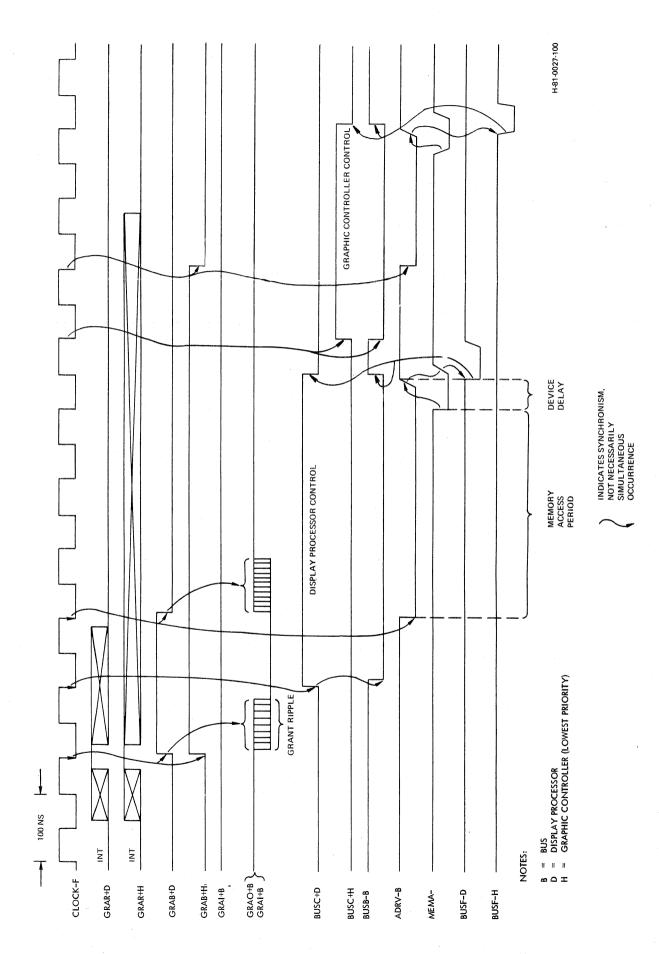

| 3-2.     | Processor Bus Timing                                                                                                                                                                                                                                                                                                    | 3-8                                                            |

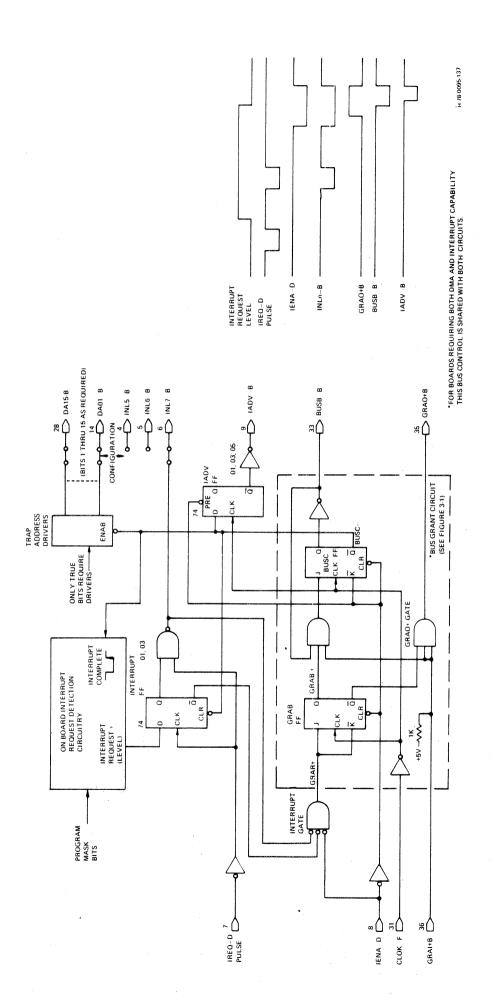

| 3-3.     | Interrupt Logic and Timing                                                                                                                                                                                                                                                                                              | 3-10                                                           |

| 3-4.     | Correspondence between Octal Page Numbers and Their Associated Addresses                                                                                                                                                                                                                                                | 3-14                                                           |

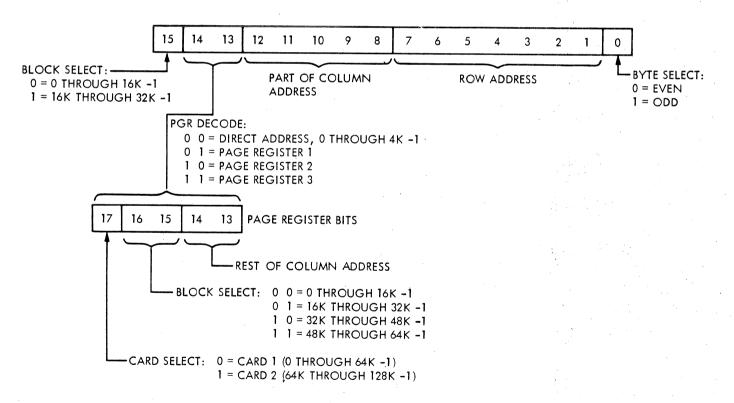

| 3-5.     | Structure of 18-Bit Address                                                                                                                                                                                                                                                                                             | 3-15                                                           |

| 3-6.     | Structure of 16-Bit Address with Memory Mapping                                                                                                                                                                                                                                                                         | 3-15                                                           |

| 3-7.     | Mapping Action                                                                                                                                                                                                                                                                                                          | 3-16                                                           |

| 3-8.     | Large Read/Write Memory, Simplified Block Diagram                                                                                                                                                                                                                                                                       | 3-19                                                           |

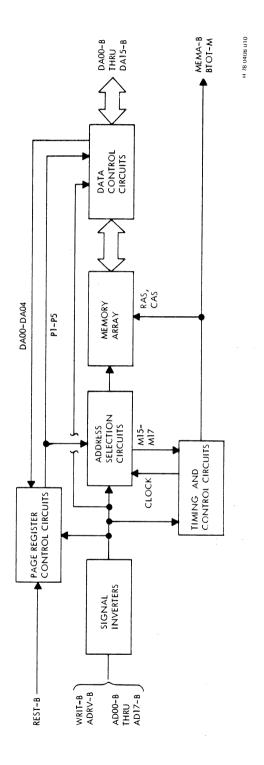

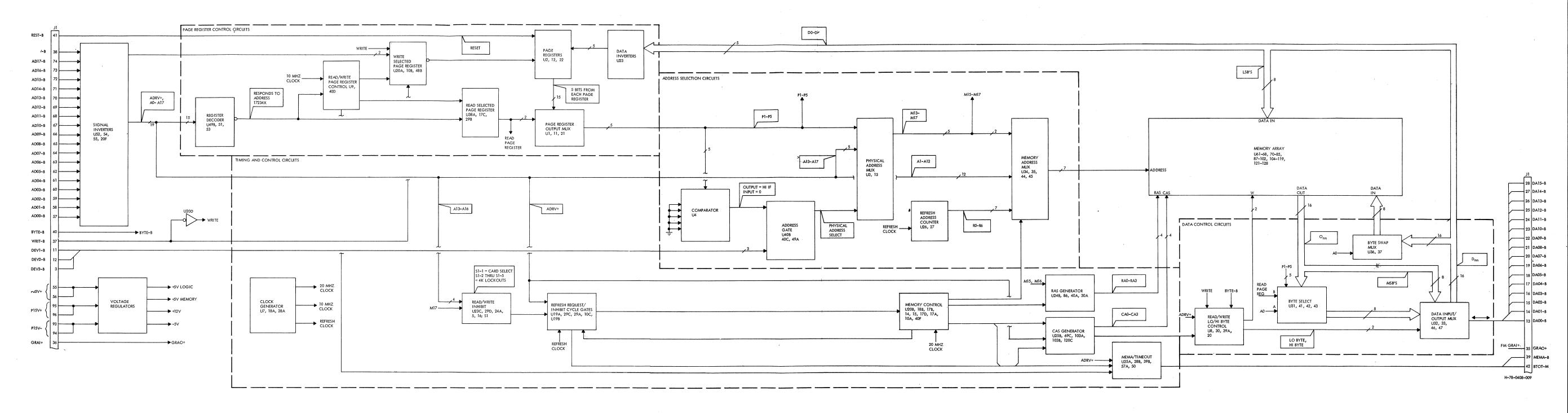

| 3-9.     | Read/Write Memory, Functional Block Diagram                                                                                                                                                                                                                                                                             | 3-29                                                           |

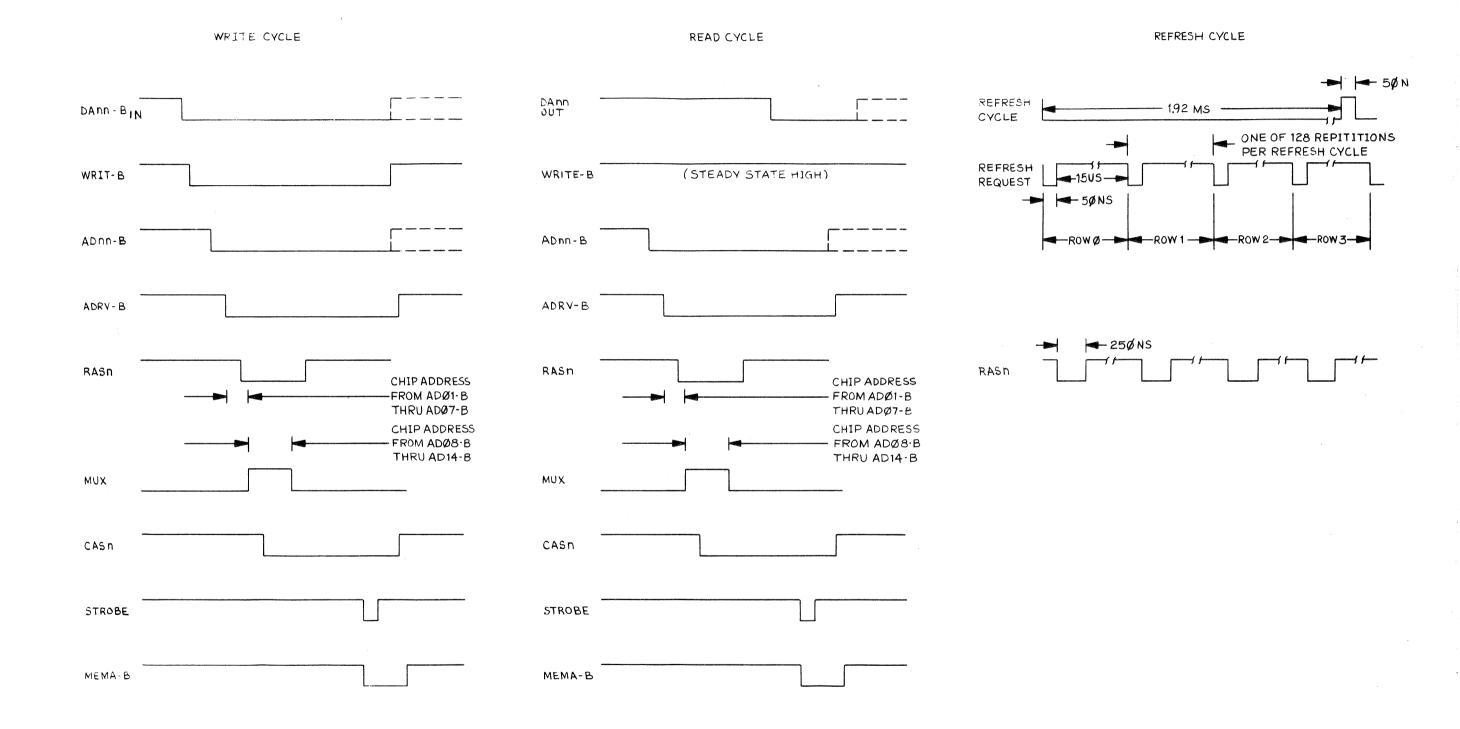

| 3-10.    | Write Cycle, Read Cycle and Refresh Cycle Timing                                                                                                                                                                                                                                                                        | 3-31                                                           |

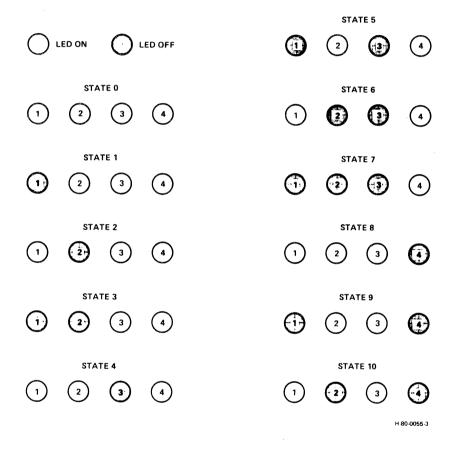

| 3-11.    | Parallel Interface LED Indications                                                                                                                                                                                                                                                                                      | 3-37                                                           |

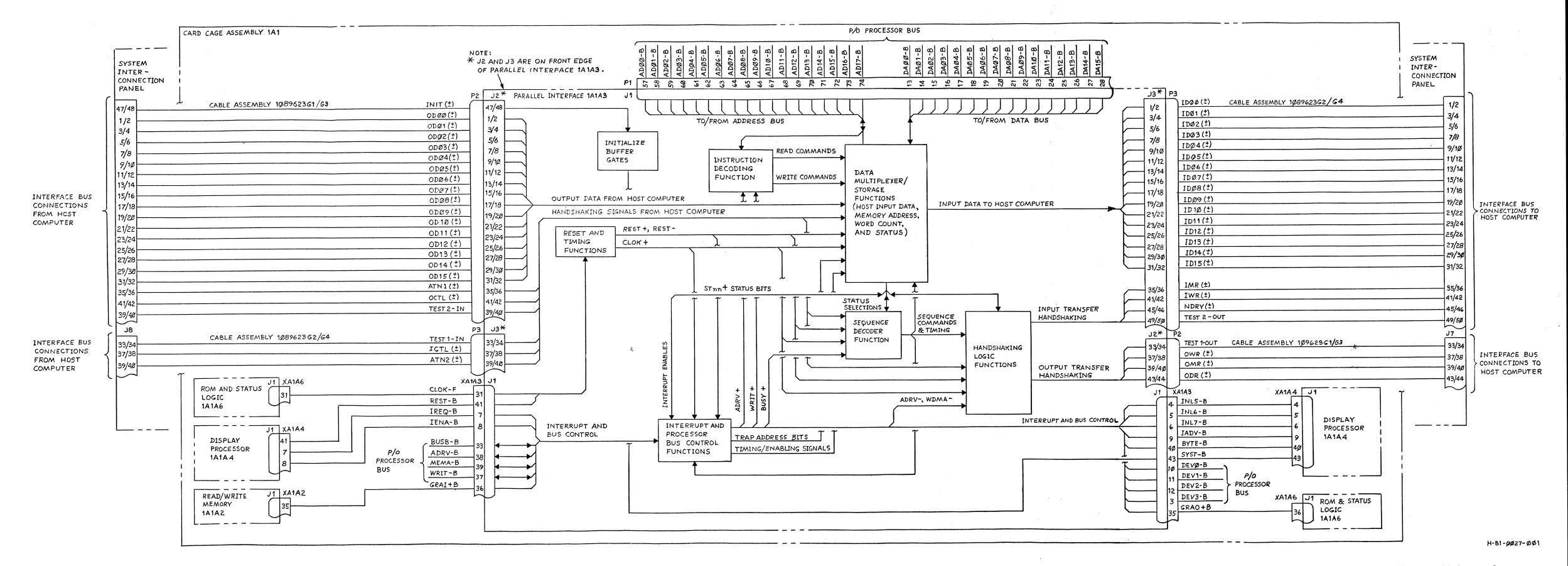

| 3-12.    | Parallel Interface Block Diagram                                                                                                                                                                                                                                                                                        | 3-51                                                           |

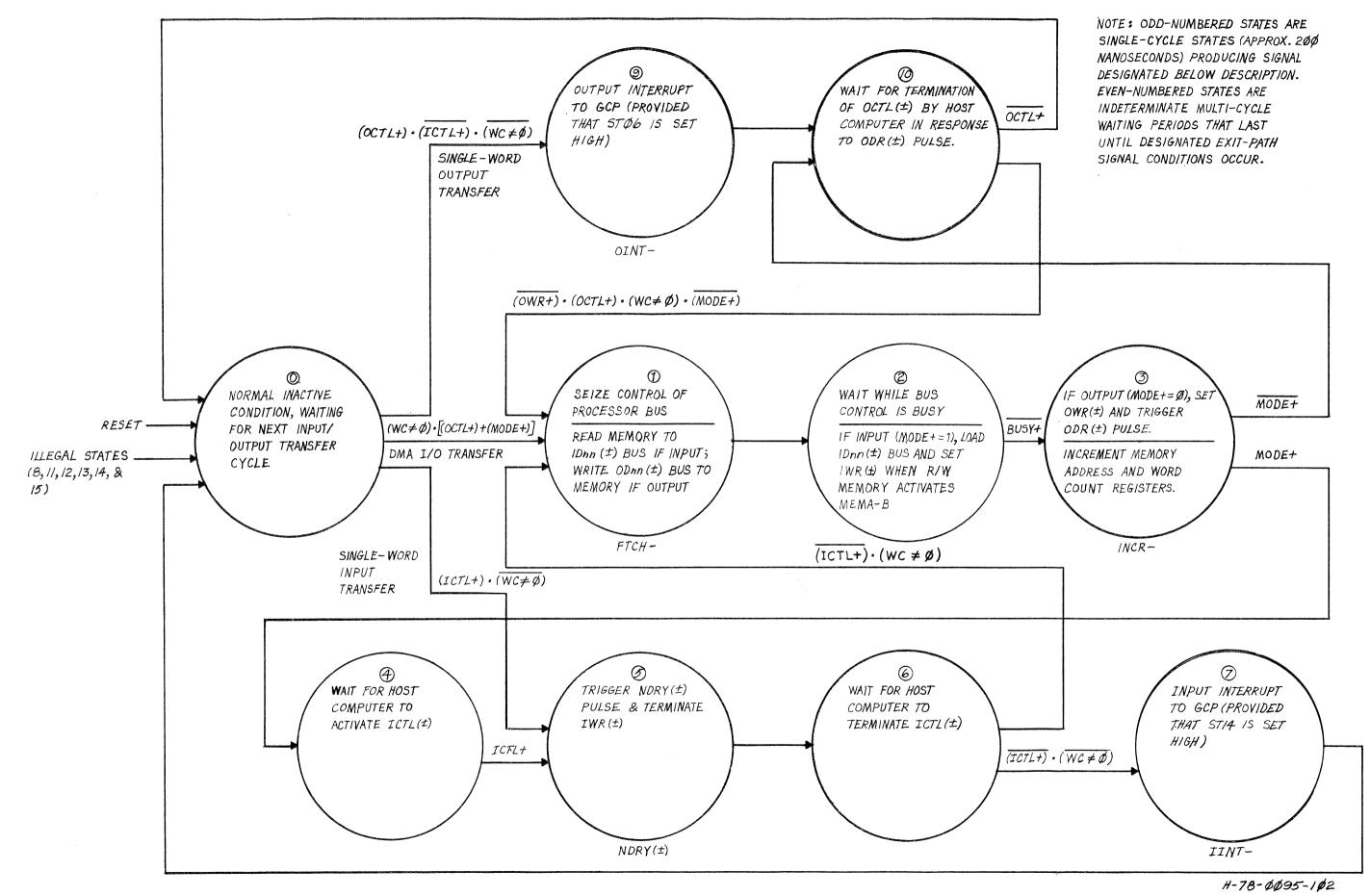

| 3-13.    | Parallel Interface State Diagram                                                                                                                                                                                                                                                                                        | 3-53                                                           |

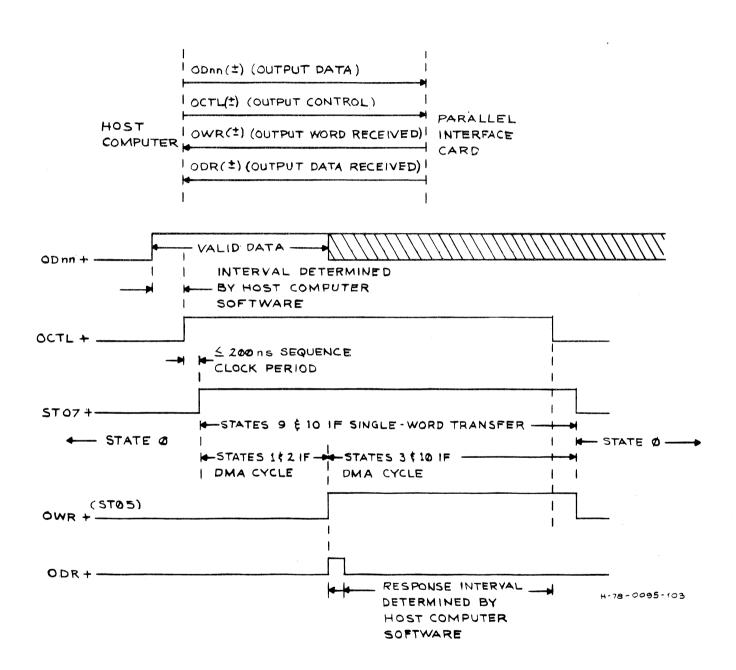

| 3-14.    | Parallel Interface Output Transfer, Timing Diagram                                                                                                                                                                                                                                                                      | 3-55                                                           |

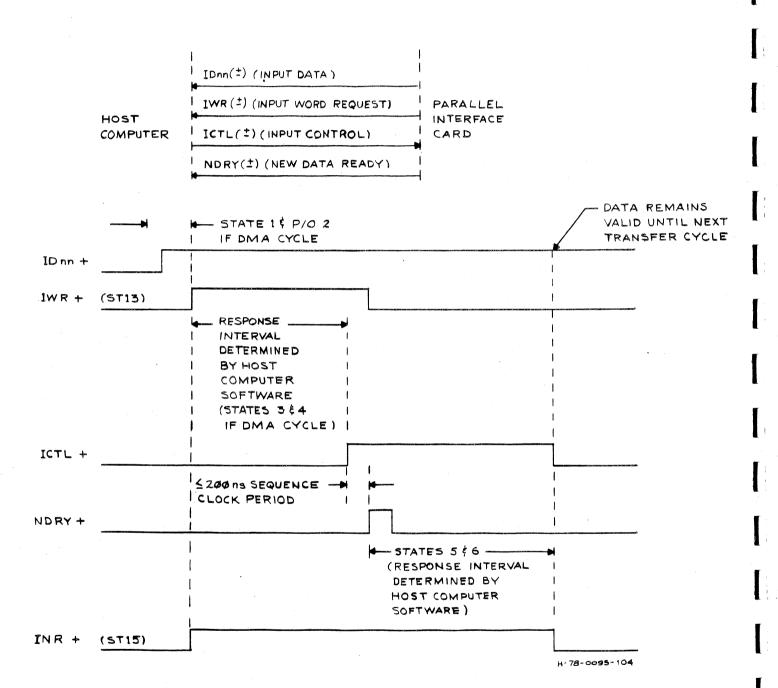

| 3-15.    | Parallel Interface Input Transfer, Timing Diagram                                                                                                                                                                                                                                                                       | 3-56                                                           |

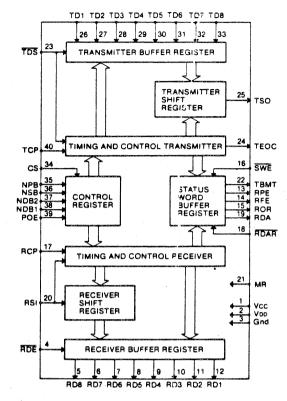

| 3-16.    | UART Functional Block Diagram                                                                                                                                                                                                                                                                                           | 3-58                                                           |

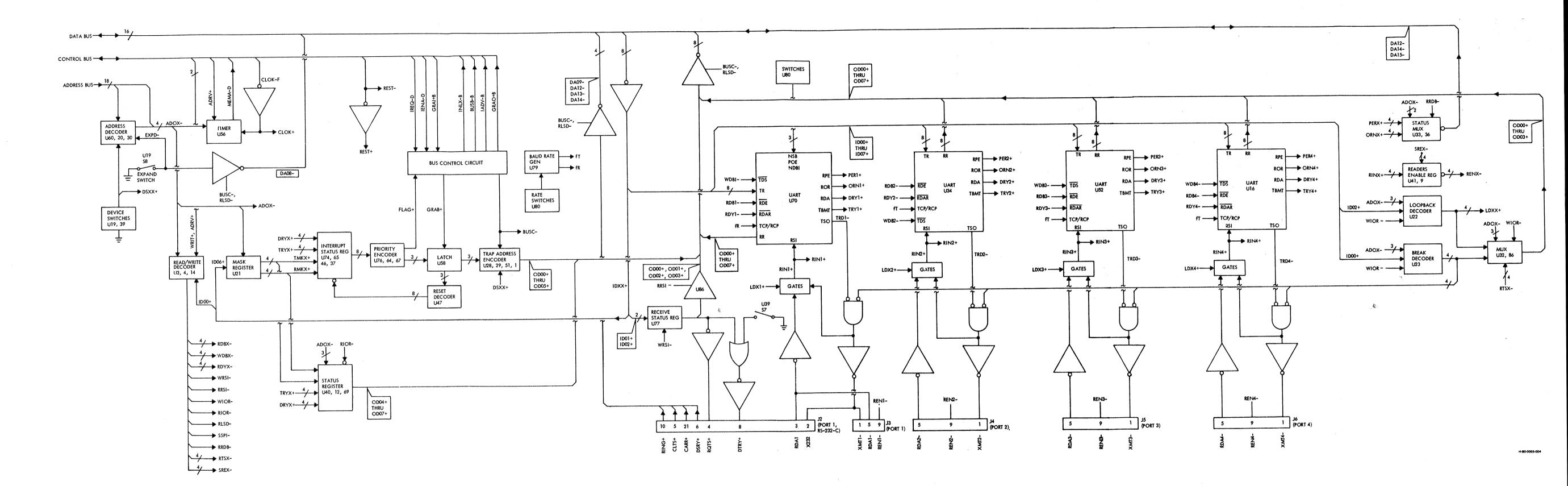

| 3-17.    | Serial Interface, Block Diagram                                                                                                                                                                                                                                                                                         | 3-67                                                           |

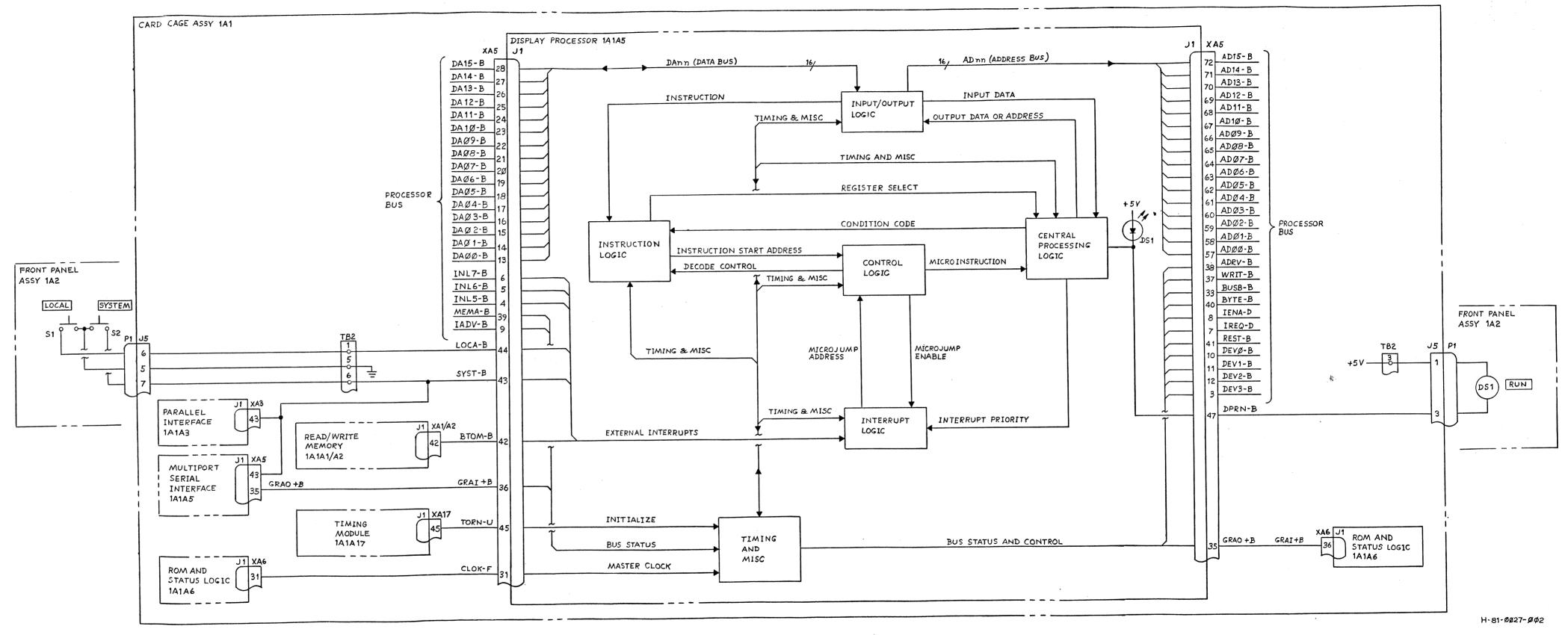

| 3-18.    | Display Processor, Block Diagram                                                                                                                                                                                                                                                                                        | 3-71                                                           |

# LIST OF ILLUSTRATIONS (Cont)

| Number |                                                                            | Page                  |

|--------|----------------------------------------------------------------------------|-----------------------|

| 3-19.  | Display Processor, Functional Block Diagram                                | 3-73                  |

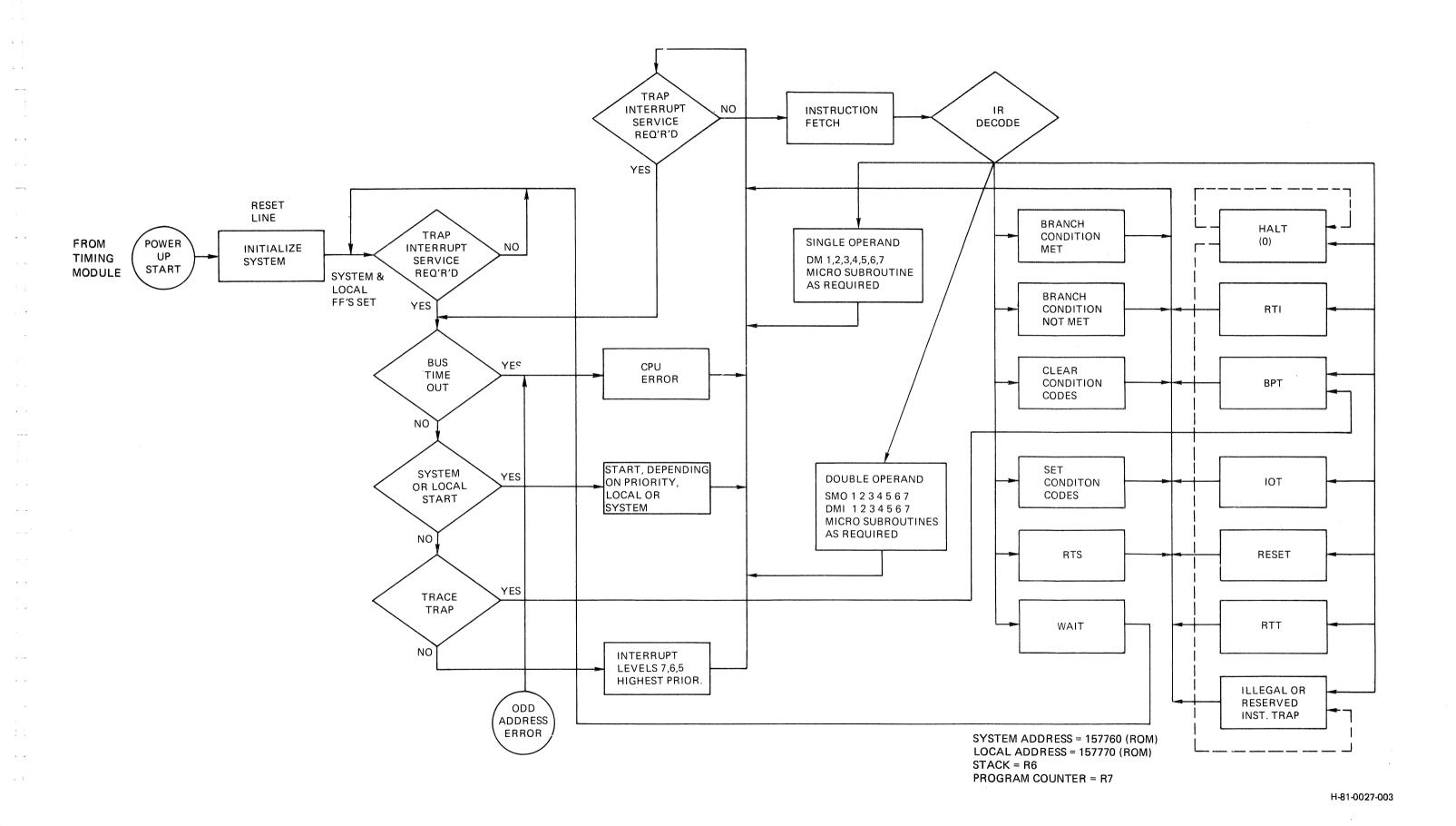

| 3-20.  | Display Processor Flow Diagram                                             | 3-75                  |

| 3-21.  | ROM and Status Card, Block Diagram                                         | 3-87                  |

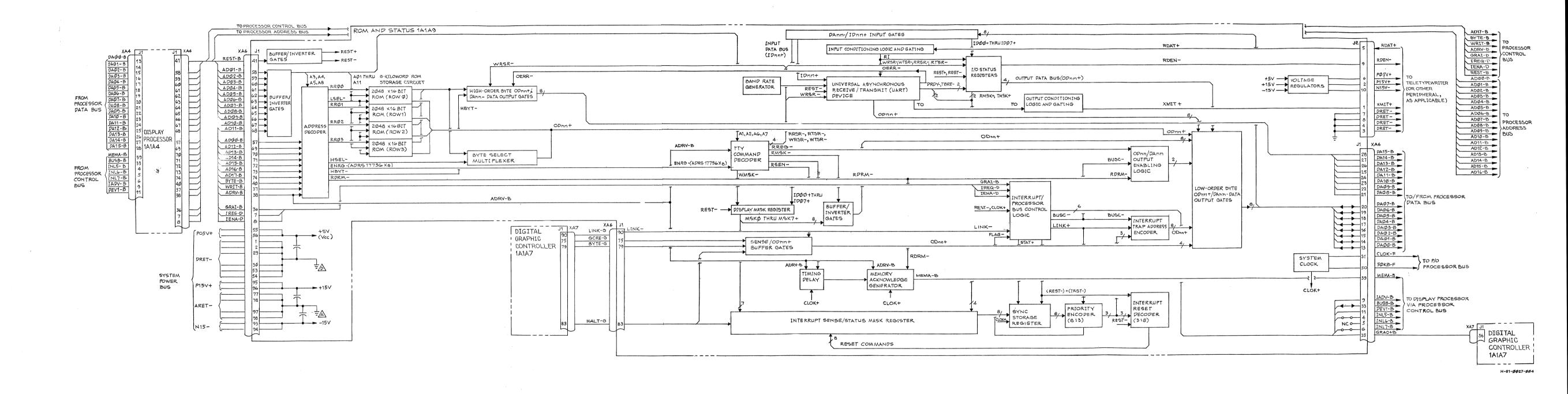

| 3-22.  | ROM and Status Card Functional Block Diagram                               | 3-89                  |

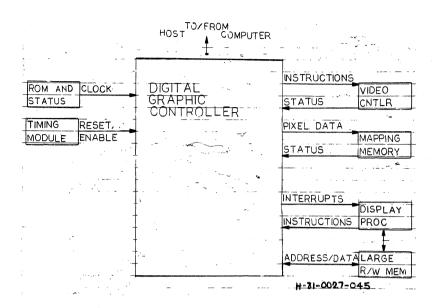

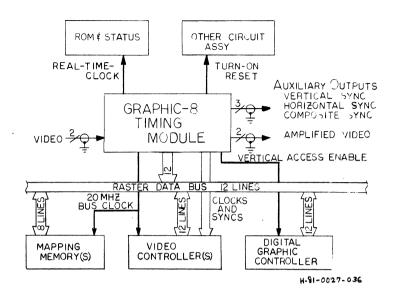

| 3-23.  | Relationship of Digital Graphic Controller to Other                        | 3-92                  |

|        | Elements of the GRAPHIC 8 System                                           |                       |

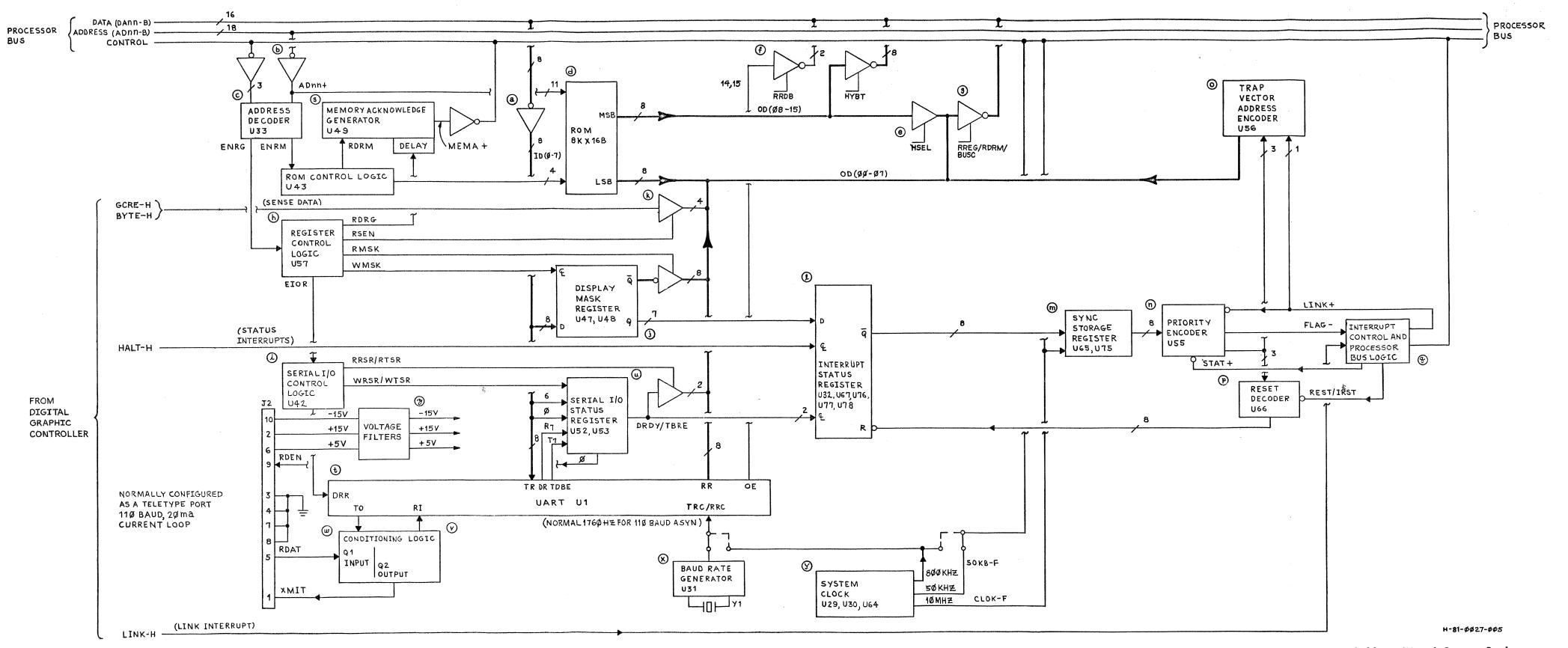

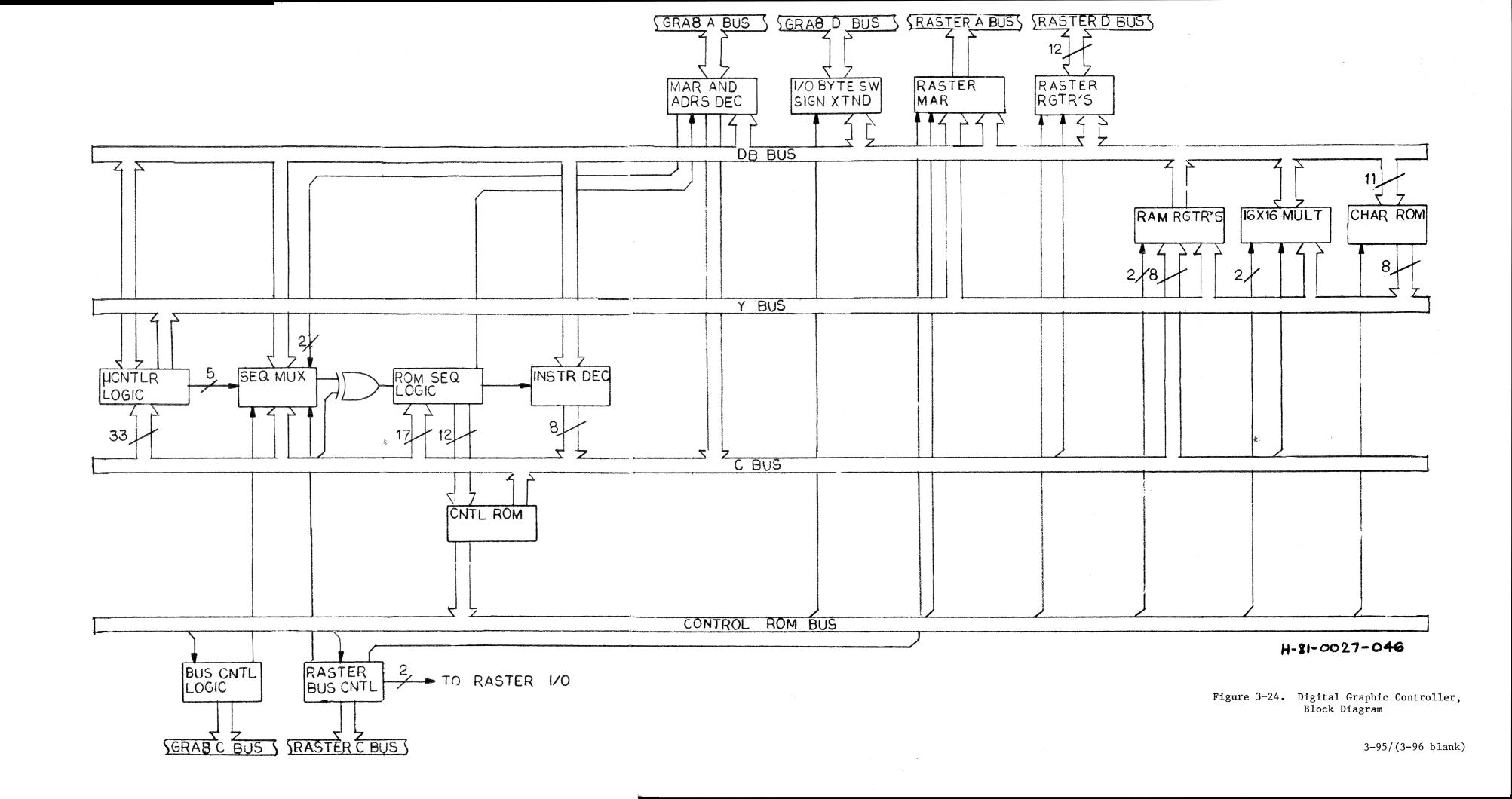

| 3-24.  | Digital Graphic Controller, Block Diagram                                  | 3-95                  |

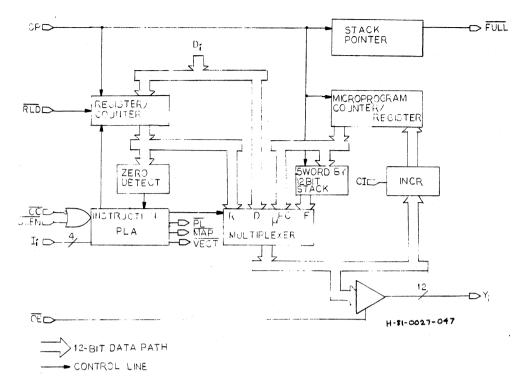

| 3-25.  | ROM Sequencer, Block Diagram                                               | 3-102                 |

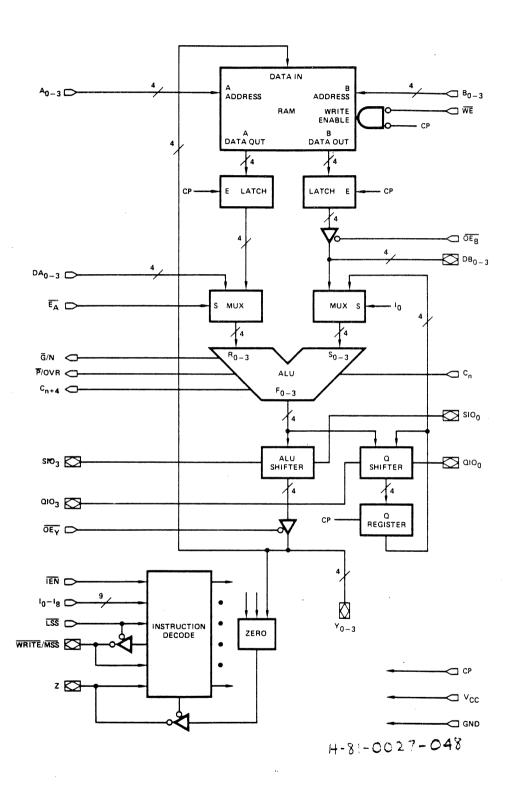

| 3-26.  | Microprocessor Slice, Block Diagram                                        | 3-105                 |

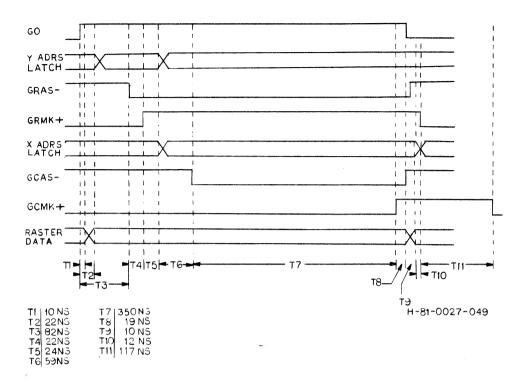

| 3-27.  | Raster Bus Timing Diagram                                                  | 3-111                 |

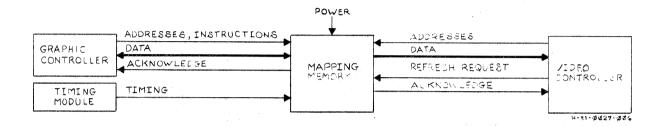

| 3-28.  | Relationship of Mapping Memory to Other Elements of the                    | 3-114                 |

|        | GRAPHIC 8 System                                                           |                       |

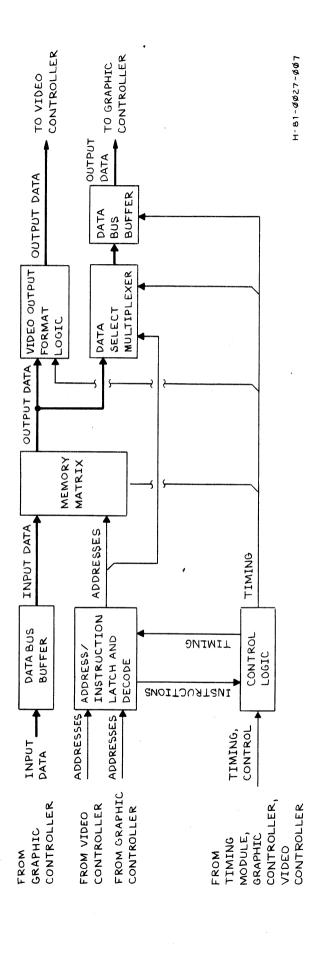

| 3-29.  | Mapping Memory Block Diagram                                               | 3-115                 |

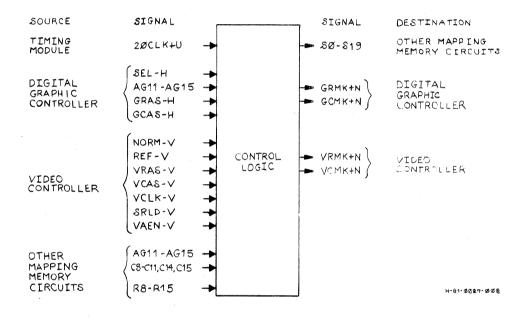

| 3-30.  | Mapping Memory Control Logic Inputs and Outputs                            | 3-116                 |

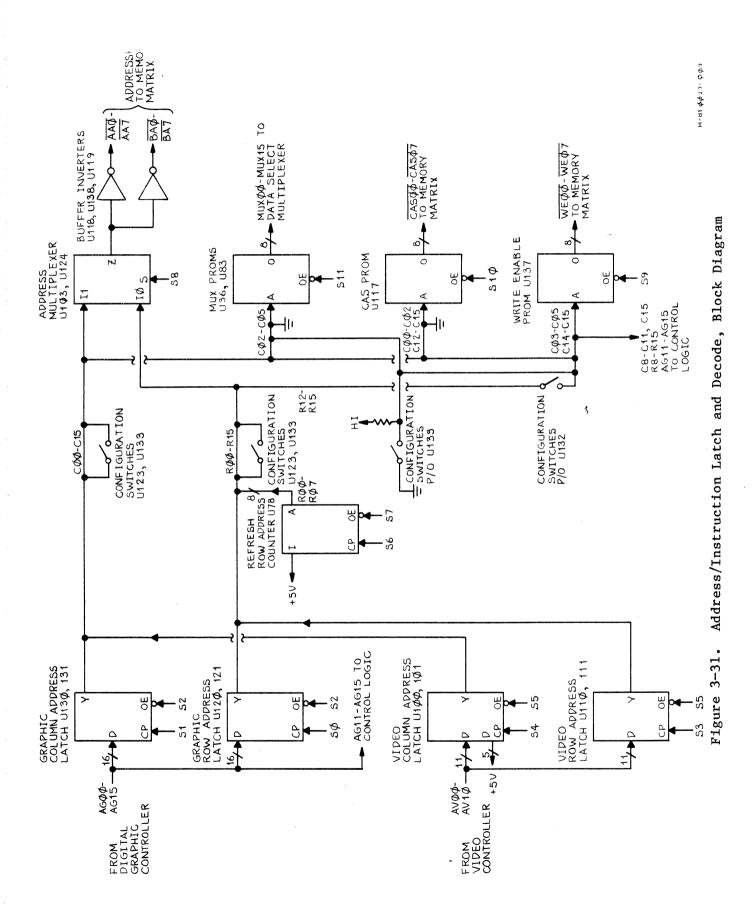

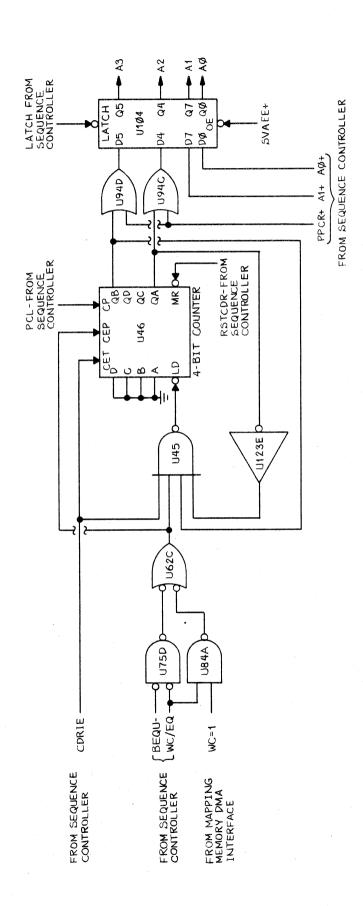

| 3-31.  | Address/Instruction Latch and Decode, Block Diagram                        | 3-121                 |

| 3-32   | Memory Chain Block Diagram                                                 | 3-124                 |

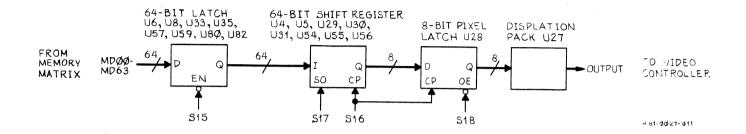

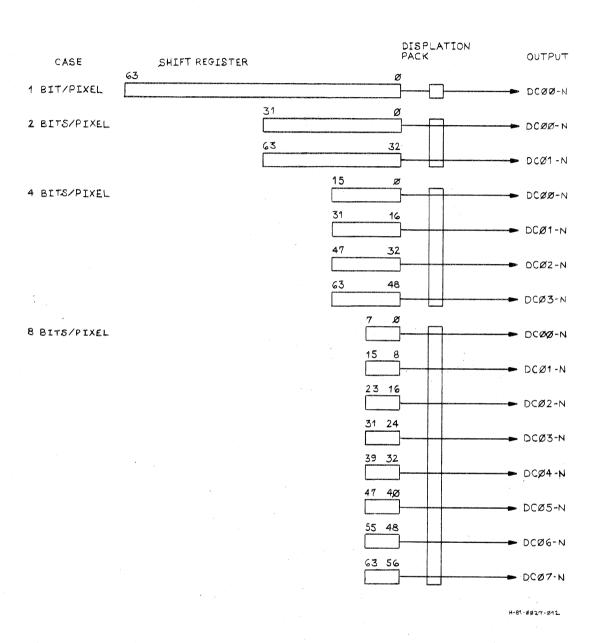

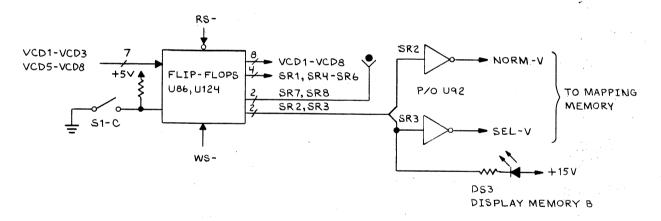

| 3-33.  | Video Output Format Logic Block Diagram                                    | 3-125                 |

| 3-34.  | Video Output Format Configurations                                         | 3-126                 |

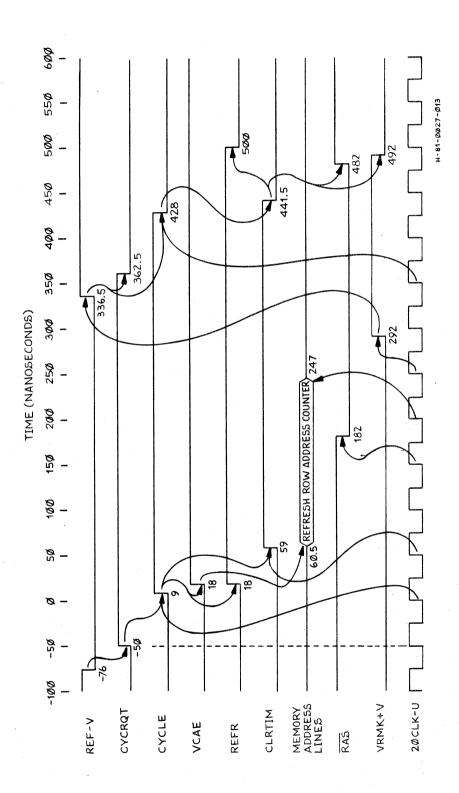

| 3-35.  | Refresh Cycle, Sequence of Events                                          | 3-128                 |

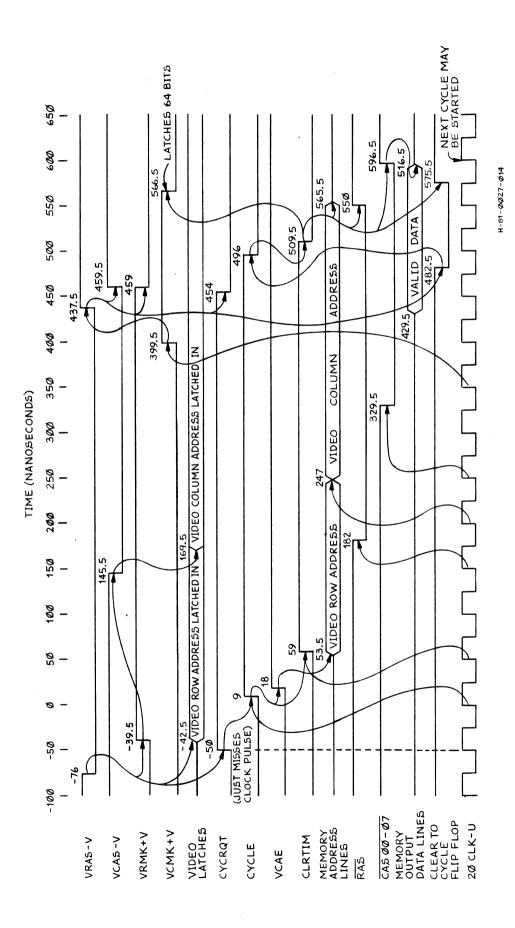

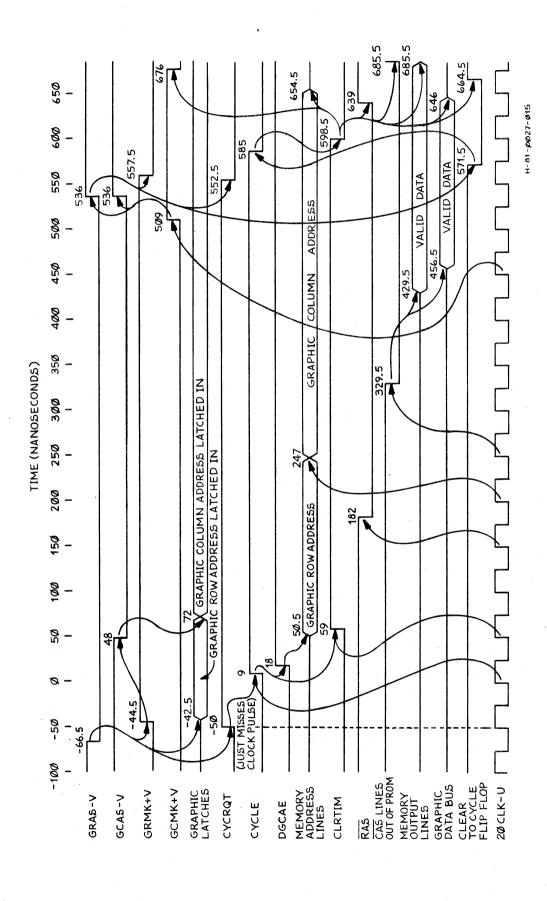

| 3-36.  | Video Read Cycle, Sequence of Events                                       | 3-129                 |

| 3-37.  | Graphic Controller Read Cycle, Sequence of Events                          | 3-130                 |

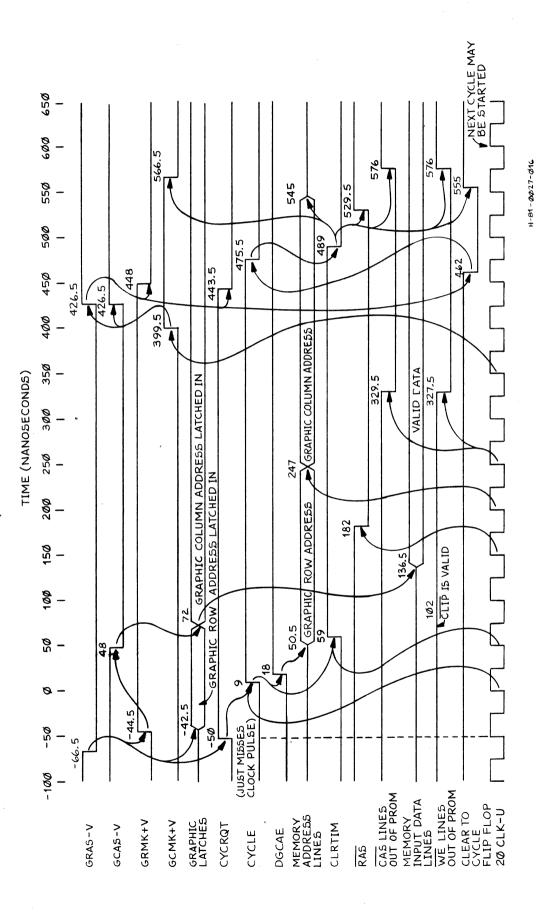

| 3-38.  | Graphic Controller Write Cycle, Sequence of Events                         | 3-131                 |

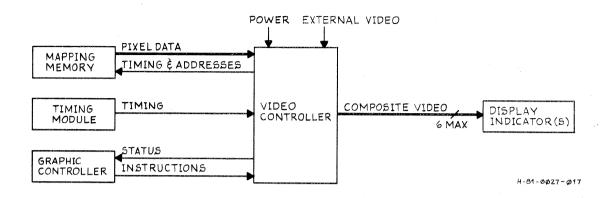

| 3-39.  | Relationship of Video Controller to Other Elements of the GRAPHIC 8 System | 3-134                 |

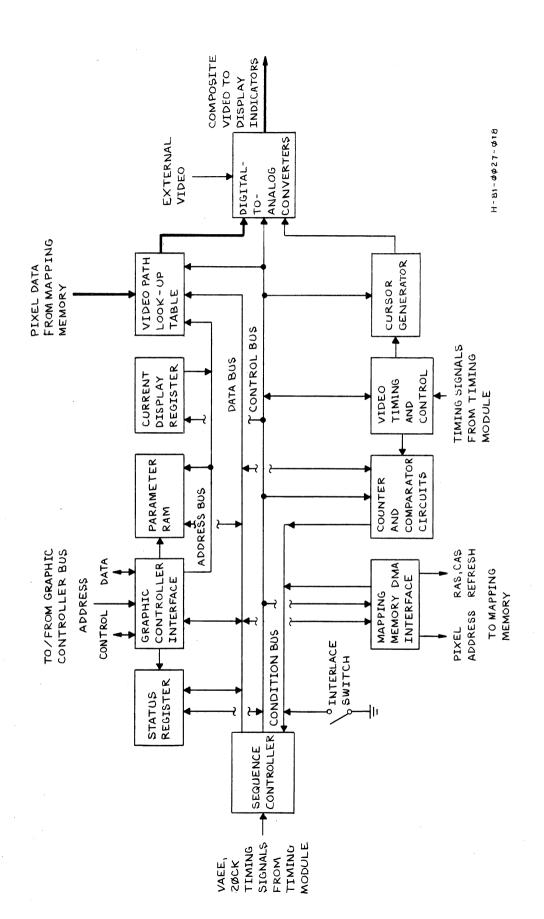

| 3-40.  | Video Controller Block Diagram                                             | 3-135                 |

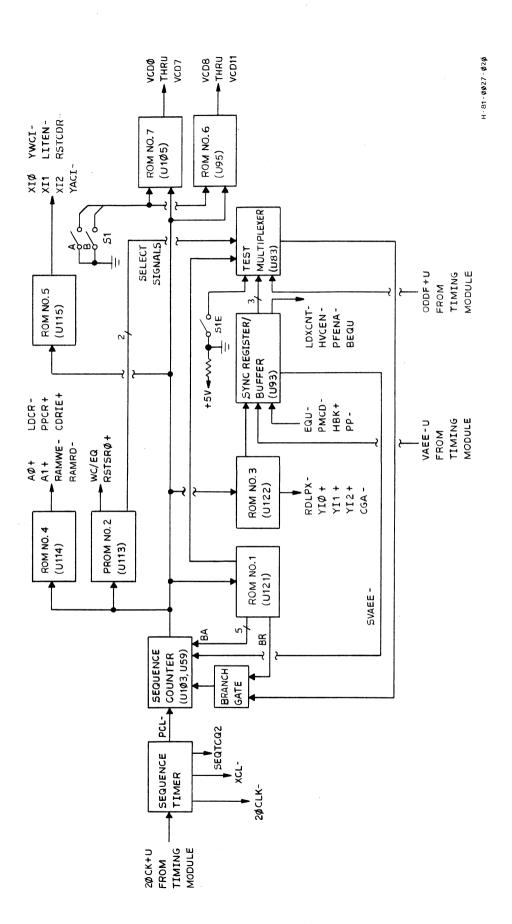

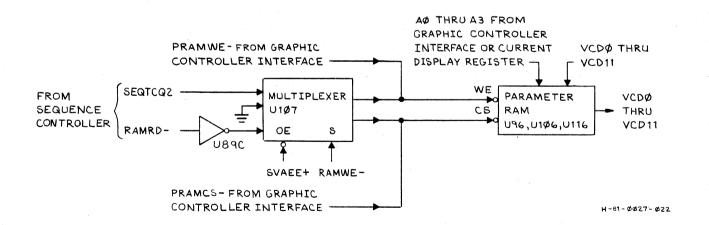

| 3-41.  | Sequence Controller Block Diagram                                          | 3-137                 |

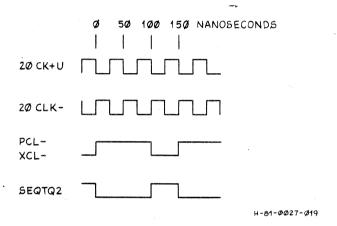

| 3-42.  | Sequence Timer Waveforms                                                   | 3-138                 |

| 3-42A. | Graphic Controller Interface, Block Diagram                                | 3-141                 |

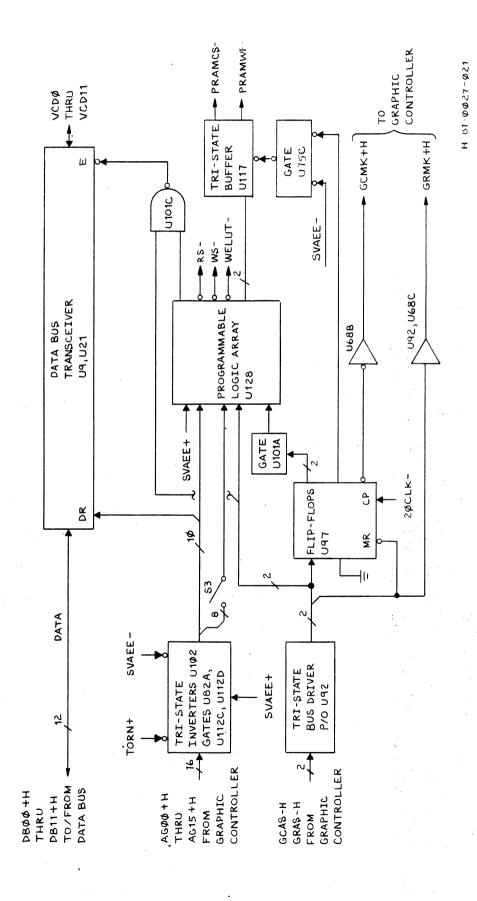

| 3-43.  | Parameter RAM, Block Diagram                                               | 3-142                 |

| 3-44.  | Status Register Block Diagram                                              | 3-143                 |

| 3-45   | Current display Register, Block Diagram                                    | 3-146                 |

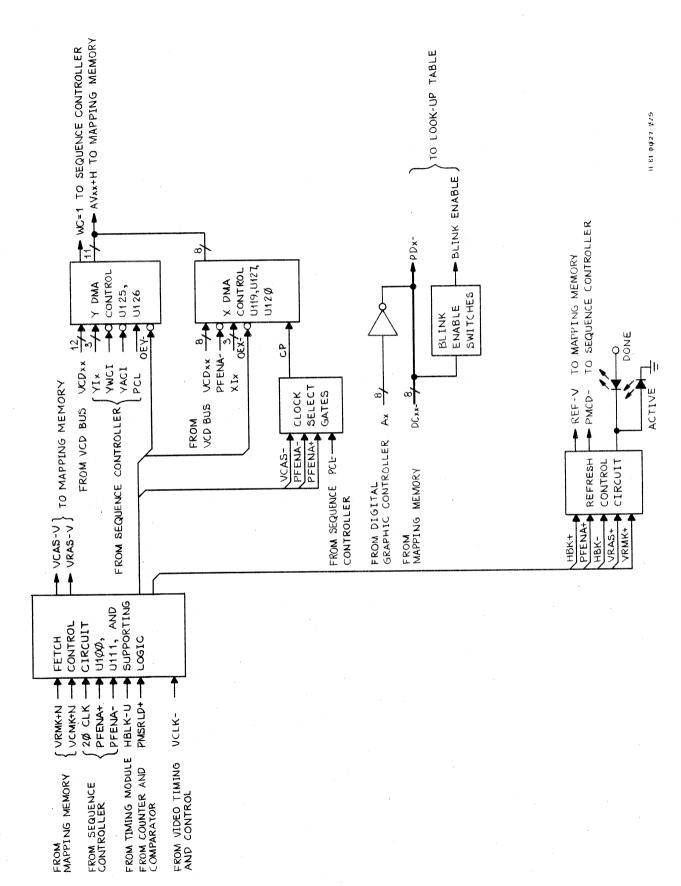

| 3-46.  | Mapping Memory Interfaced, Block Diagram                                   | 3-148                 |

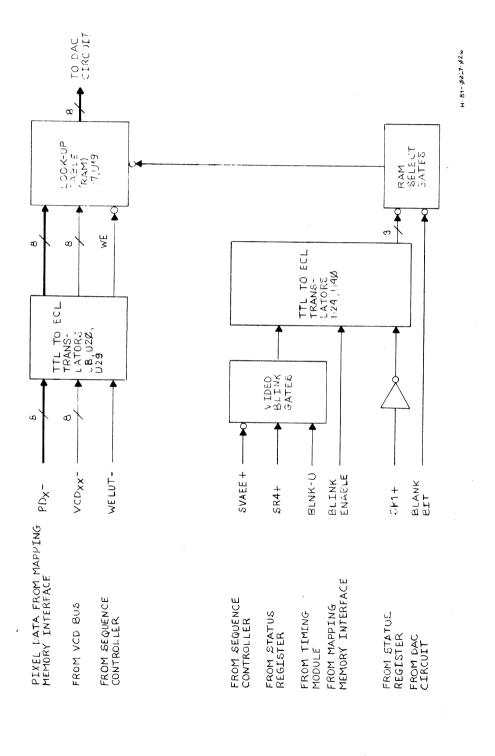

| 3-47.  | Video Path Look-Up Table, Block Diagram                                    | 3-149                 |

| 3-48.  | Video Timing and Control Circuit, Inputs and Outputs                       | 3-150                 |

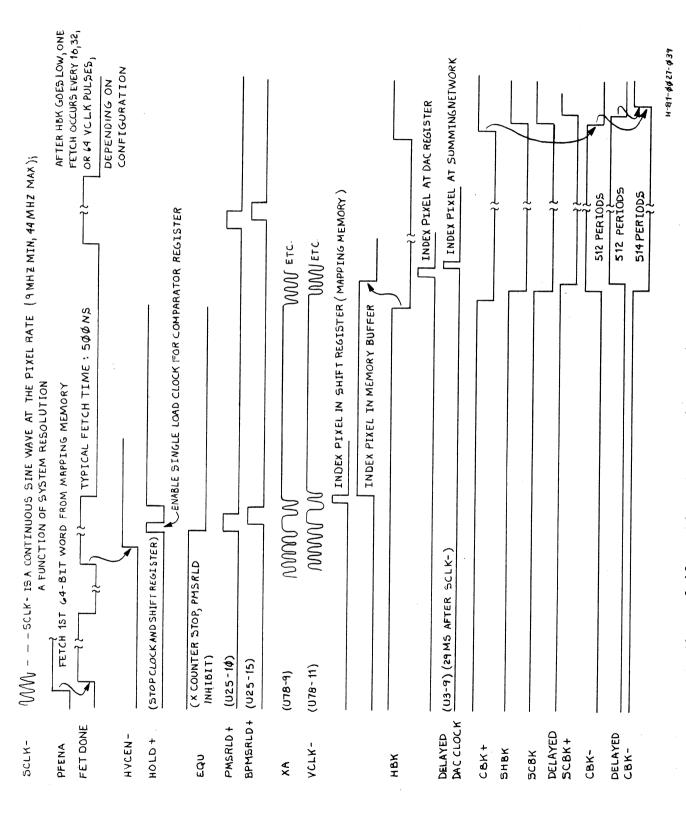

| 3-49.  | Video Timing and Control, Timing Diagram                                   | 3-151                 |

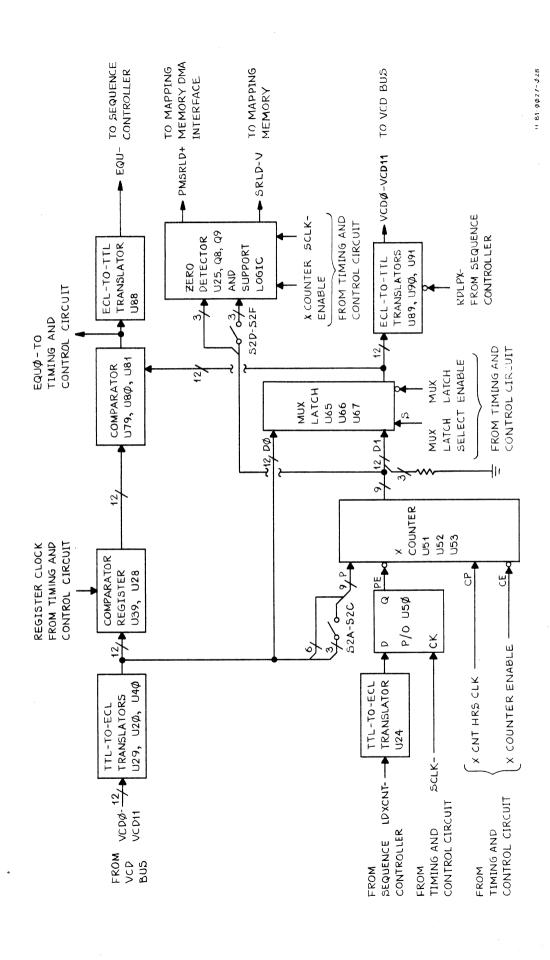

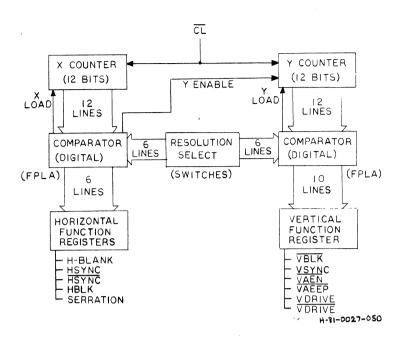

| 3-50.  | Counter and Comparator Circuit                                             | 3-153                 |

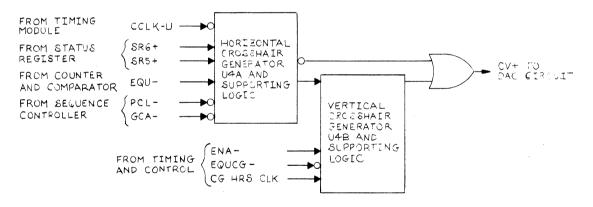

| 3-51.  | Cursor Generator Block Diagram                                             | 3-155                 |

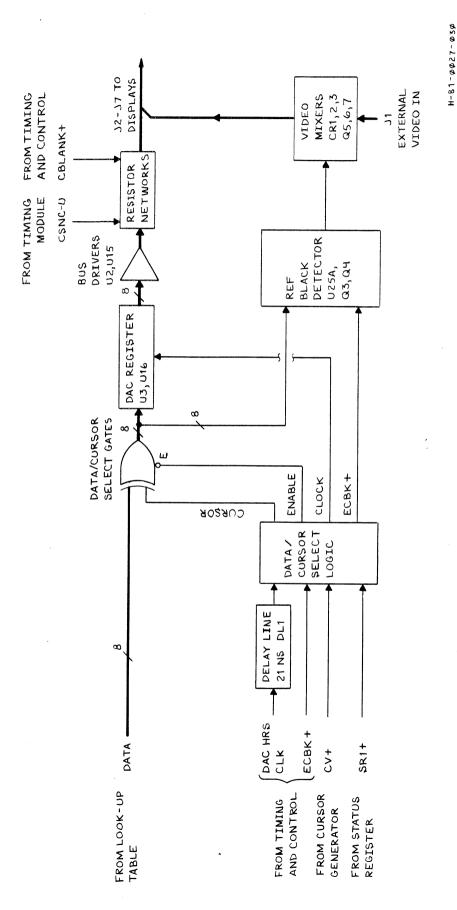

| 3-52.  | DAC Circuits, Block Diagram                                                | 3-157                 |

| 3-53.  | Video Controller Flow Diagram                                              | 3-158                 |

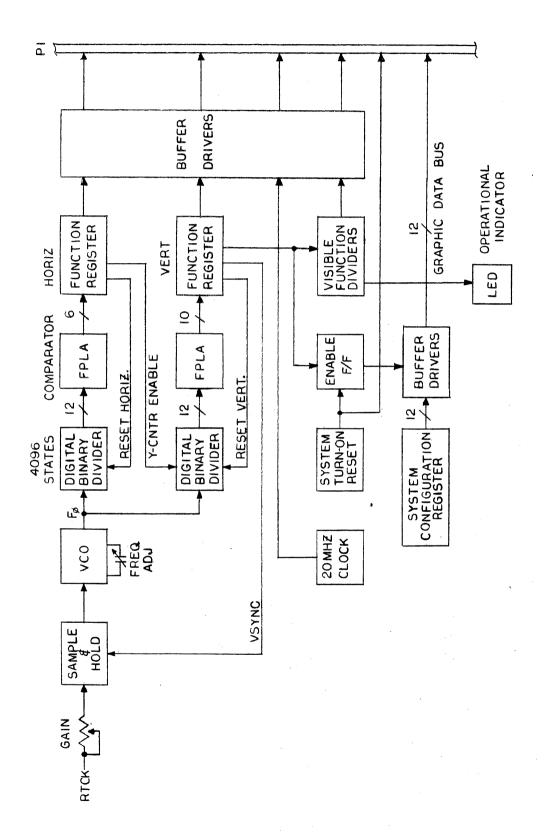

| 3-54.  | Timing Module Functional Application                                       | 3-161                 |

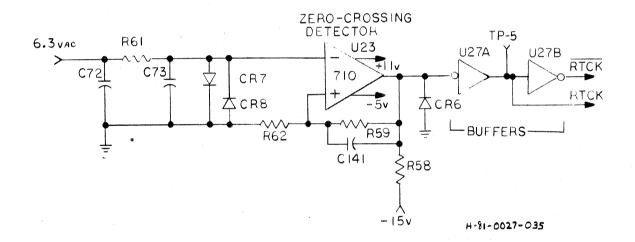

| 3-55.  | Real Time Clock Circuit                                                    | 3-162                 |

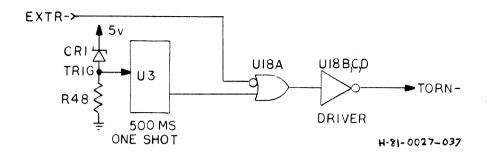

| 3-56.  | Turn-On Reset Generator                                                    | 3-163                 |

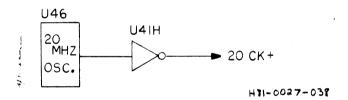

| 3-57.  | 20 MHz Oscillator                                                          | 3-163                 |

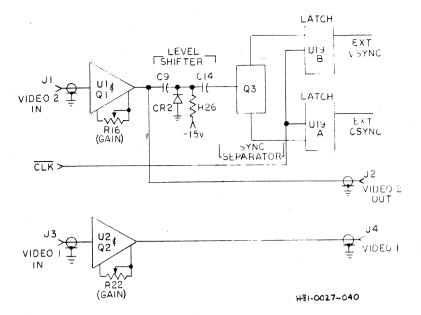

| 3-58.  | Video Amplifiers                                                           | 3-164                 |

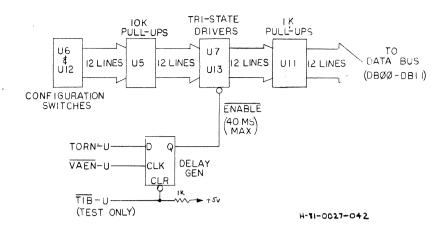

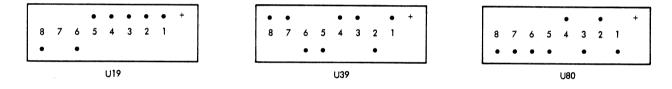

| 3-59.  | Configuration Switch Settings                                              | 3-164                 |

| 3-60.  | System Configuration Register                                              | 3-165                 |

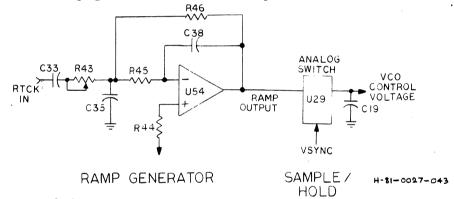

| 3-61.  | Ramp Generator and Sample Hold Circuit                                     | 3-165                 |

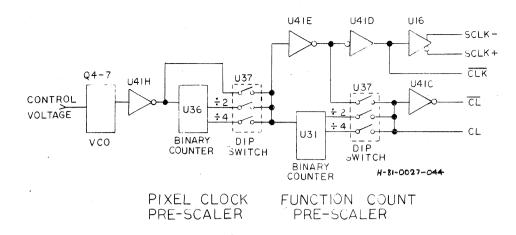

| 3-62.  | VCO, Pixel Clock Prescaler, and Function Count Prescaler                   | 3-166                 |

| 3-63.  | Raster Syncs and Blanks                                                    | 3-167                 |

| 4-1.   | Controller Cabinet Interconnection Diagram                                 | 3-107<br>4 <b>-</b> 5 |

|        | controller capturer interconnection pragram                                | 4-0                   |

# LIST OF ILLUSTRATIONS (Cont)

| Number |                                                                             | Page         |

|--------|-----------------------------------------------------------------------------|--------------|

| 4-2.   | Serial Interface, Normal Switch Positions                                   | 4-17         |

| 5-1.   | Verification Test Pattern                                                   | 5 <b>-</b> 4 |

| 5-2.   | Verification Test Pattern                                                   | 5-5          |

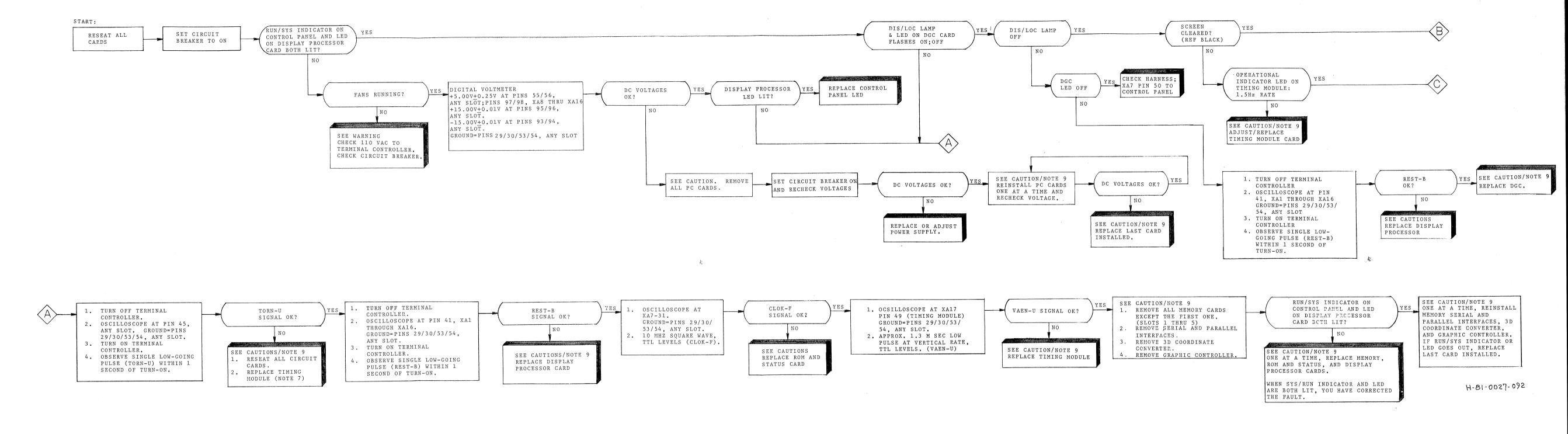

| 5-3.   | Troubleshooting Flow Diagram                                                | 5-7          |

| 5-4.   | Timing Module                                                               | 5-15         |

|        | LIST OF TABLES                                                              |              |

| Number |                                                                             | Page         |

| 1-1.   | Physical Characteristics                                                    | 1-13         |

| 1-2.   | GRAPHIC 8 Terminal Controller (Model 8XXX) Specifications                   | 1-17         |

| 2-1.   | Terminal Controller Controls and Indicators                                 | 2-1          |

| 2-2.   | Serial Interface Port Codes                                                 | 2-7          |

| 2-3.   | Local Mode Command Summary                                                  | 2-9          |

| 3-1.   | Processor Subsystem Cards Preferred Priority Arrangement                    | 3-2          |

| 3-2.   | Processor Bus Signals                                                       | 3-3          |

| 3-3.   | Power Bus (Common to All Cards)                                             | <b>3–</b> 5  |

| 3-4.   | Parallel Interface Interrupt Trap Addresses                                 | 3-38         |

| 3-5.   | Parallel Interface Register Addresses                                       | 3-40         |

| 3-6.   | Parallel Interface Status Register Bit Description                          | 3-40         |

| 3-7.   | Single-Word Output Transfer Sequence                                        | 3-43         |

| 3-8.   | DMA Output Transfer Sequence                                                | 3-45         |

| 3-9.   | Single-Word Input Transfer Sequence                                         | 3-47         |

| 3-10.  | DMA Input Transfer Sequence                                                 | 3-48         |

| 3-11.  | Multiport Serial Interface Devices                                          | <b>3–</b> 59 |

| 3-12.  | Serial Interface Port Device Assignments                                    | 3-60         |

| 3-13.  | Display Mask Register Bits                                                  | 3-79         |

| 3-14.  | DAnn-B Processor Bus Data Word                                              | 3-80         |

| 3-15.  | Interrupt Status Register Input Signals                                     | <b>3-</b> 80 |

| 3-16.  | Priority Encoder Trap Address Values                                        | 3-81         |

| 3-17.  | TTY Receive Status Register (Address 177560 <sub>8</sub> ) Bit Descriptions | 3-84         |

| 3-18.  | TTY Transmit Status Register (Address 177564 <sub>8</sub> )                 | 3-85         |

|        | Bit Descriptions                                                            | 3-03         |

| 3-19.  | TTY Receive Data Buffer (Address 1775628)                                   | 3-85         |

| 3-20.  | TTY Transmit Data Buffer (Address 1775668)                                  | 3-86         |

|        | Bit Descriptions                                                            | 3 00         |

| 3-21.  | ROM Sequencer, Input and Output Functions                                   | 3-102        |

| 3-22.  | Microprocessor Slice, Input and Output Functions                            | 3-104        |

| 3-23.  | Mapping Memory Control Logic Input and Output Signals                       | 3-117        |

| 3-24.  | Memory Options and Configuration Switch Settings                            | 3-120        |

| 3-25.  | Display Select Switch Settings                                              | 3-122        |

| 3-26.  | Video Output Format Configurations                                          | 3-125        |

| 3-27.  | Video Controller Card Select                                                | 3-142        |

|        |                                                                             |              |

# LIST OF TABLES (Cont)

| Number |                                                                      | Page  |

|--------|----------------------------------------------------------------------|-------|

| 3-28.  | Video Controller Status Bits                                         | 3-144 |

| 3-29.  | Switch Settings for Number of Refresh Cycles per<br>Horizontal Sweep | 3-147 |

| 3-30.  | Video Timing and Control Output Signal Functions                     | 3-152 |

| 3-31.  | Pixel Memory Shift Register Length                                   | 3-154 |

| 3-32.  | Configuration Switch Settings                                        | 3-160 |

| 3-33.  | Output Frequencies                                                   | 3-166 |

| 3-34.  | Event Timing                                                         | 3-167 |

| 4-1.   | Connector P3 Configurations                                          | 4-2   |

| 4-2.   | Parallel Interface I/O Connectors, Pin Assignments                   | 4-8   |

| 4-3.   | Multiport Serial Interface I/O Connectors, Pin Assignments           | 4-9   |

| 4-4.   | Read/Write Memory Switches and Jumpers                               | 4-10  |

| 4-5.   | ROM and Status Card Jumper Configurations                            | 4-11  |

| 4-6.   | Multiport Serial Interface Parameter Selections                      | 4-13  |

| 4-7.   | Parallel Interface Parameter Selections                              | 4-17  |

| 5-1.   | Timing Module                                                        | 5-17  |

#### SAFETY PRECAUTIONS

The following are general safety precautions not related to any specific procedure and therefore do not appear elsewhere in this manual. These are recommended precautions that must be understood and applied during installation or maintenance of the terminal controller.

#### AVOID LIVE CIRCUITS

Observe all safety regulations at all times. Do not replace components in the terminal controller power panel assembly with power applied.

#### RESUSCITATION

When working with or near high voltages, be familiar with modern resuscitation methods.

# WARNING

Primary power (100 Vac to 240 Vac) is present at the power panel assembly. Line voltage of 115 Vac is present at the power supply.

Always turn off terminal controller and pull power plug before moving any cabinet- or chassis-mounted component.

## TERMINAL CONTROLLER PROTECTION

Circuit card assemblies in the terminal controller can be damaged by transient surges.

# CAUTION

Always turn off terminal controller before removing or installing any circuit card.

## SPECIAL HANDLING FOR MOS DEVICES

MOS devices are subject to damage caused by static charges. Assemblies that contain MOS devices are mapping memories and timing module. When not installed in the card cage, these assemblies should be stored in black Velostat bags with the MOS warning statement printed on the outside of the bag.

# CAUTION

Always handle these cards only by the card extractors or by the edges of the connector. Avoid touching the card components or the printed circuit.

# WARNING

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. As temporarily permitted by regulation, it has not been tested for compliance with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

#### SECTION 1

#### GENERAL INFORMATION

## 1.1 INTRODUCTION

The Sanders Associates, Inc. GRAPHIC 8<sup>™</sup> is a high-performance, intelligent computer graphics terminal system incorporating refreshed raster display technology. It is designed to interface a host computer and to support operator CRT display monitor stations configured with interactive devices, such as keyboards, trackballs, forcesticks, and data tablets. Also, it can produce permanent hard copy records of displayed data.

The GRAPHIC 8 features a dynamic display update via a double refresh buffer memory technique, and supports up to four CRT display monitors. Resolutions of 512 x 512, 640 x 480, 1024 x 768 (interlaced) or 1024 x 1024 (interlaced) are available. Both color and monochrome versions are offered with up to 8 bits per pixel to provide as many as 256 simultaneous colors or monochrome intensities (or 128 plus blink).

The GRAPHIC 8 display processor is a general purpose digital computer with a set of over 400 instructions that controls a variety of functions to reduce the loading on the host computer. In combination with the host computer, the GRAPHIC 8 system permits the user to display digital data in a visual format on the CRT display monitor and to interact with the displayed image by means of keyboards, forcesticks, trackballs, and data tablets. Its high performance and intelligence make it well suited to a variety of applications, such as CAD/CAM, simulation and training, command and control, cartography, and many others.

#### 1.2 COMPONENT DESCRIPTION

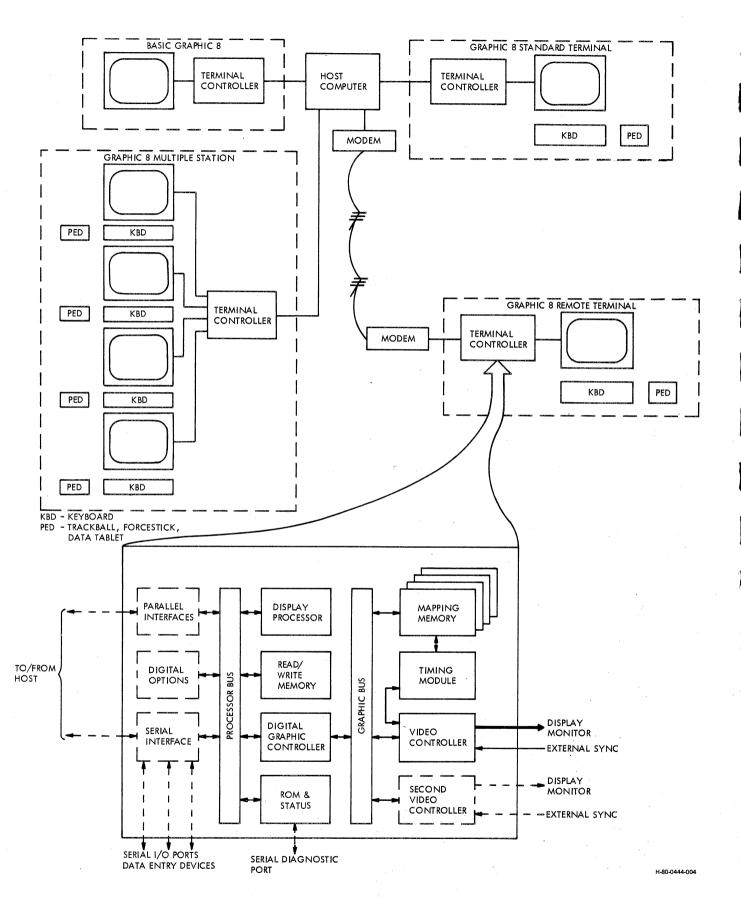

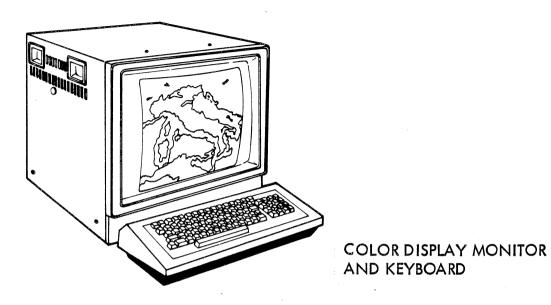

The basic GRAPHIC 8 system (figure 1-1) consists of a terminal controller, (figure 1-2) and a monitor. The basic system can be expanded to include a wide variety of options and enhancements.

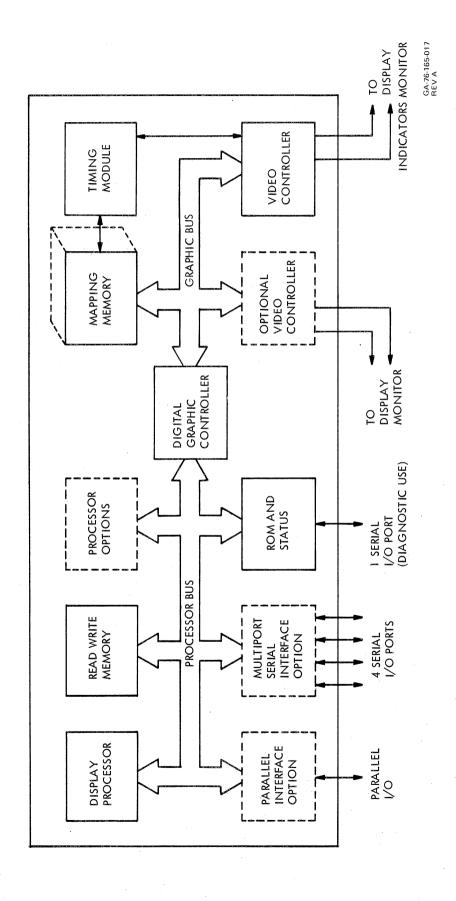

- 1.2.1 TERMINAL CONTROLLER. The GRAPHIC 8 terminal controller consists of a rack mountable card cage and a power supply. As shown in figure 1-3, the cards are interconnected by a processor bus or a graphic bus. The size of controller selected is based on the four following major considerations:

- 1. Color or monochrome

- 2. Number of simultaneous colors or intensities

- 3. Resolution of the display image

- 4. Number of display stations per controller

<sup>\*</sup>GRAPHIC 8 is a trademark of Sanders Associates, Inc.

Figure 1-1. Typical GRAPHIC 8 System Configurations

TERMINAL CONTROLLER

Figure 1-2. GRAPHIC 8 Terminal Controller and Monitor

Figure 1-3. GRAPHIC 8 Terminal Controller Organization

The GRAPHIC 8 terminal controller consists of a power supply and a card cage with slots for 17 cards. Six of the slots are for the processor cards, one slot is for the digital graphics controller, one slot is for the timing module, and the remaining nine slots are for the mapping memory and video controller cards.

1.2.1.1 <u>Display Processor</u>. The display processor card is a general purpose digital computer that runs the GCP and acts as master control for all devices connected to the processor bus. It contains multiple high-speed general-purpose registers that can be used as accumulators, pointers, index registers, or auto-indexing pointers in auto-increment and auto-decrement modes. Functions performed by the display processor card include system initialization, interface handling, local data editing, and local generation of simple display images.

Instructions used for the display processor emulate the instruction set for the PDP-11/34® manufactured by Digital Equipment Corporation (DEC®). They are fetched either from the GCP in read-only memory on the ROM and status logic card or from the read/write memory. An 8-bit configuration switch is program readable (used by GCP) from octal location 177774.

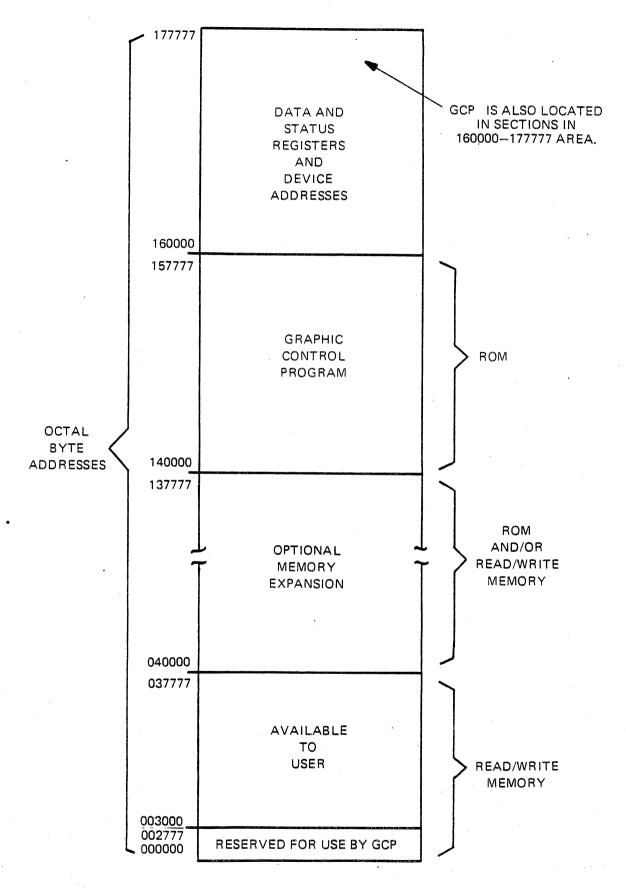

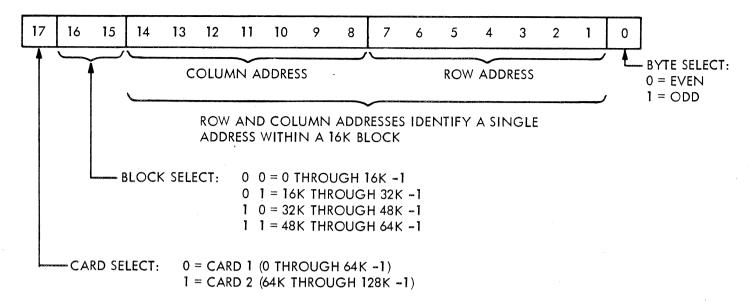

1.2.1.2 Read/Write Memory. Locations in the read/write memory are assigned addresses 0000008 through 7777778 and are accessed by an 18-bit address on the processor bus and by a 16-bit address and mapping registers on the memory card. The 18-bit address can be used to access the location of a word (16 bits) or of an individual byte (8 bits) as required. Figure 1-4 is the GRAPHIC 8 system memory map.

Each read/write memory card is capable of storing  $65,536_{10}$  (64K) sixteen bit words or 128K separately addressable 8-bit bytes. A maximum of two memory cards can be installed in a GRAPHIC 8 system for a total of 128K 16-bit words of memory. The read/write memory card is also available in 16K and 32K word sizes.

#### NOTE

User refresh programs will not execute in RAM memory in the 24K to 32K area (140000-17777). This area is reserved for Sanders' display processor option software. The option software is loaded from the expansion module or is down-loaded from the host.

1.2.1.3 ROM and Status Logic. The ROM and Status logic card contains the read-only memory in which the GCP used to control the display processor is stored (refer to figure 1-4). Also contained on the card are display status and interrupt logic circuits plus a serial interface port to which a teletypewriter may be connected for diagnostic purposes.

The standard read-only memory provided on the ROM and status logic card contains the GCP firmware. The GCP is approximately 6.6K words (16 bits). Like read/write memory, read-only memory may be accessed to retrieve either 16-bit words or individual 8-bit bytes.

<sup>®</sup>PDP and DEC are registered trademarks of Digital Equipment Corporation

Figure 1-4. GRAPHIC 8 System Memory Map

- 1.2.1.4 <u>Multiport Serial Interface</u>. The multiport serial interface card contains four serial interface ports that operate in a serial asynchronous mode using RS-232C or TTL voltage levels with standard transmission rates up to 9600 baud. Additionally, the first port can be operated as a full RS-232C asynchronous interface at transmission rates greater than 9600 baud. For GCP applications, the maximum transmission rate supported is 9600 baud. Normally, the host computer is connected to the first port, which is compatible with the standard communication and terminal interfaces supplied by most computer manufacturers. The remaining three ports on the card are used for peripheral devices.

- 1.2.1.5 Parallel Interface. An optional GRAPHIC 8 parallel interface allows high-speed communications with handshaking and is intended for applications where the GRAPHIC 8 is located in proximity to the host. All parallel interface signals are TTL-compatible. Under program control, the interface operates in either an interrupt driven or a DMA mode. In the latter mode, the interface operates at speeds up to 500,000 16-bit words/second. If a parallel interface card is installed in the terminal controller, GCP assumes that it is connected to the host computer. Therefore, if serial communication with the host computer is desired, a parallel interface card cannot be connected to the processor bus.

#### NOTE

Normally, if a parallel interface port is used, a single parallel interface card (for the host computer) is installed in the terminal controller. For special applications, however, two parallel interface cards may be installed, but are not supported by the standard Graphic Control Program.

1.2.1.6 <u>Digital Graphic Controller</u>. The digital graphic controller is a microprocessor with more than 50 instructions committed to ROM. It retrieves display update instructions from R/W memory, generates vectors, characters, conics, point plots, and fills, and stores these in mapping memory in raster-scan format. The complete series of sequential instructions that defines any particular display image is referred to as a refresh file.

The digital graphic controller may be considered as a device on the processor bus of the terminal controller. It contains its own set of registers that maintain instruction address, control fetch operations, and perform any branching that may be specified by non-graphic instructions. It also calculates relative data when required, loads data into appropriate registers, and initiates execution of refresh file instructions.

Status bits of the digital graphic controller are maintained by circuits on the ROM and status logic card. These bits plus the graphic controller registers are accessible to the display processor which maintains control over the entire terminal controller.

1.2.1.7 Mapping Memory. The mapping memory contains pixel data in a format which allows display refresh in a raster scan mode. The mapping memory may be configured for various resolutions up to 1024 x 1024 (see figure 1-5) and for interlace or non-interlace refresh. A single memory board can be supplied with a capacity of over four million bits. Up to eight bits can be combined per pixel to provide 256 possible colors or intensity levels.

Figure 1-5. Addressable Vs. Displayable Areas for Four Screen Resolutions

A dual mapping memory configuration is for high-speed dynamic update of data. The dual memory concept allows the hardware to clear and update one memory while the second memory is refreshing the display. When the next update occurs, the roles of the two memories are reversed so that the previously updated memory now becomes the refresh memory.

1.2.1.8  $\underline{\text{Video Controller}}$ . The video controller obtains data from the mapping memory and formats it for presentation on the display monitor(s). Outputs are provided as either RGB color or monochrome and as composite video.

External video may be accepted by the video controller and logically ORed with internally-generated video. A single video controller can accomodate up to eight bits per pixel.

The video controller generates one non-destructive, full-screen, crosshair cursor and contains the cursor address registers which are accessible to the user. It controls the split screen function which allows the user to divide the display face into two or three variable-height horizontal bands and fill these bands with data from anywhere in addressable mapping memory. This feature allows the user to simultaneously view up to three separate areas of mapping memory which are not necessarily contiguous.

The video controller contains a 256  $\times$  8-bit word RAM look-up-table (LUT) which allows pseudo-color or pseudo-gray level transformation to be made.

- 1.2.1.9 <u>Timing Module</u>. The timing module generates all display-related timing signals as well as the necessary synchronization signals for the monitors. On-board switches allow selection for compatible operation with the possible resolutions and refresh frequencies.

- 1.2.1.10 Character Generation. Character generation is performed by the digital graphic controller. The basic set of characters supplied is a standard set of 96 ASCII characters. When the ASCII code corresponding to the desired character is applied to the read-only memory, the character is drawn at the position determined by the current position for X and Y.

As determined by instructions from the digital graphic controller, characters of three different sizes can be generated. Characters may also be rotated 90 degrees counterclockwise to accommodate vertical writing requirements. Both normal and rotated characters can be made to blink.

Read-only memory for six groups of 16 characters can be added to provide a total of up to 192 standard and special characters that can be produced by the  $GRAPHIC\ 8.$

1.2.1.11 <u>2-D/3-D Coordinate Converter</u>. The Model 5753 2-D/3-D coordinate converter converts a Sanders graphic display into a three dimensional display capable of independent dynamic manipulation of objects in apparent space. Among the functions provided by the Model 5753 are translation, scaling, rotation, windowing, independent display coordinate mapping, perspective, and zooming with perspective.

The perspective feature is especially useful for realistic viewing of an object. Utilizing perspective, the location of the viewer is defined relative to the image space, and all lines and objects within the image space are then viewed at the proper perspective for that location. The view may be completely orthographic if the viewer does not wish to use the perspective feature.

Objects can be defined within a 64K (X), 64K (Y), by 32K (Z) image space and presented on a 1K by 1K screen or any portion thereof. Translations can be made within the limits of the image space and scaling range is 64 to 1. Rotation can be provided about any axis.

3-D windowing, in conjunction with independent screen coordinate mapping, allows the presentation of any data within a software definable X, Y, Z image space to be presented on the full screen or any portion of the screen. Zooming is accommodated by scaling and changing the user's apparent perspective viewpoint.

Alphanumeric data can be moved about the screen with vector defined data without scaling and rotation.

The 5753 provides for both homogeneous and non-homogeneous matrix operation. Also, transformations of 2-D images can be accomplished including translation, rotation, scaling, and windowing.

1.2.1.12 <u>Data Converter</u>. The model 5744 data converter option transforms incoming floating point binary numbers into displayable numbers. The displayable numbers may be in any of sixteen formats selected by the host. The bi-directional converter also converts the displayed numbers into floating-point binary for transmission back to the host.

The data converter saves host computer time and storage resources by performing these conversions within the graphic terminal. It allows data to be transmitted to and from the host in its most compact form and frees the host programmer from the conversion programming task.

The data converter can perform more than 500 conversions per second, which allows it to be used in high data-rate applications resulting in significant off-loading of the host computer.

The data converter is not supported by the standard Graphic Control Program.

1.2.1.13 EPROM Expansion Module. As options are added to the GRAPHIC 8, the additional software required to handle the options will be stored on the model 7750 expansion module.

The expansion module may contain up to 32K 16-bit words of non-volatile read-only memory (EPROMS). The data may be loaded from the expansion module automatically by pressing the SYSTEM button or when so instructed by the host, depending on the options stored.

- 1.2.2 INPUT DEVICES. Optional data input devices for the GRAPHIC 8 give the operator two-way interaction with the display and processing system. Input devices available include two types of keyboards; a trackball, a forcestick, and a data tablet. The GCP in firmware can support up to eight keyboards, or eight position entry devices (trackball, forcestick, or data tablet). In addition, a teletype-writer or paper tape reader can be connected to the GRAPHIC 8 for the input of maintenance data.

- 1.2.2.1 <u>Keyboards</u>. Standard keyboards available for the GRAPHIC 8 are the Model 5783 and Model 5784 keyboards. The keyboards contain a main block of alphanumeric keys plus a matrix and a row of function keys.

The Model 5783 keyboard offers an alphanumeric block of 58 keys. These keys generate standard seven-bit ASCII codes with an eighth (MSB) bit always set to 1. The alphabetic keys generate both upper and lower case codes. A four-by-four matrix of function keys is located to the right of the alphanumeric block and a row of 16 function keys is located immediately above the alphanumeric block. Each function key generates a single eight-bit octal code from 000 to 037.

An added feature of the Model 5784 keyboard is that each function key contains an LED that can be lighted or turned off as required under program control. The Model 5784 also has provisions for additional keys to the basic board. These keys are for future expansion and are located on both sides of the space bar.

The keyboards operate at a rate of 9600 baud and interface to the terminal controller via ports on the multiport serial interface card.

- 1.2.2.2 <u>Trackball</u>, Forcestick, and Data Tablet. The trackball, forcestick, and data tablet are referred to as PEDs (position entry devices). These devices are used as determined by program control to move a cursor and/or data displayed on the CRT screen. Movement initiated by the trackball is proportional to the speed and direction in which the trackball is rolled. Movement initiated by the forcestick is proportional to the direction and force with which the forcestick is deflected. Movement initiated by a data tablet is proportional to the speed and direction in which the data tablet pen is moved along the data tablet surface. PEDs are connected to the system via ports on the multiport serial interface card(s) in the terminal controller.

- 1.2.2.3 Maintenance Data Input Devices. A teletypewriter and/or a paper tape reader can be connected to the GRAPHIC 8 to input data for maintenance purposes. The teletypwriter is normally connected to a port on the ROM and status card in the terminal controller while the paper tape reader is connected to one of the ports on a multiport serial interface card. The teletypewriter serves basically as a troubleshooting aid. The paper tape reader is used to load special user or diagnostic programs into the GRAPHIC 8.

- 1.2.3 OUTPUT DEVICES. The standard output device for the GRAPHIC 8 is the CRT display monitor. A hardcopy unit is available as an optional output device. Using the same signals that go to a standard display monitor, the hardcopy unit can produce a duplicate on paper of any static image displayed on the CRT of the display monitor. Operation of the hardcopy unit is controlled manually.

An optional hardcopy multiplex switch is available. The multiplex switch is capable of interfacing up to four GRAPHIC 8 displays to a single hardcopy unit.

1.2.3.1 Display Monitors. The GRAPHIC 8 offers the user a choice of configuration of eight  $\overline{\text{CRT}}$  monitors (four monochrome and four color) to provide the right monitor for the intended application.

Positions on the screen are specified in terms of a matrix containing 2048 coordinates in the X dimension and 2048 coordinates in the Y dimension. Two's complement notation is used to designate the coordinates with location 0, 0 being defined as the center of the screen. Of the 2048 by 2048 addressable locations, the displayable area comprises the field of coordinates centered about the middle of the screen. Refer to figure 1-5 for different screen resolutions.

1.2.3.2 <u>Hardcopy</u>. Both monochrome and color hardcopy devices are available for use with the GRAPHIC 8.

## 1.3 TERMINAL CONTROLLER PHYSICAL DESCRIPTION

The terminal controller comprises a card cage, a power supply, and two fans. A control panel covers the front of the unit; a protective cover is mounted on the back.

The terminal controller is mounted either in a standard 19-inch equipment rack or in an optional cabinet. In either case, the control panel is removed for access to the terminal controller.

The circuit cards are inserted into the card cage from the front of the terminal controller, and plug into a wire-wrapped backplane. The blower fans, located beneath the card cage and power supply, draw air from the bottom of the unit and discharge the air through the top.

The basic terminal controller contains nine standard circuit cards. Optional cards are inserted as required. Most applications use both the multiport serial interface and the parallel interface cards. Other cards are available to expand the read/write memory or provide special display functions.

Figure 1-6 shows the circuit card order assumed for this manual. The figure indicates the normal locations for a full complement of circuit cards, including the optional interface cards and read/write memory expansion cards.

Table 1-1 lists the physical characteristics of the terminal controller and circuit cards.

The terminal controller can operate with 100V - 120V or 220V - 240V ac input power. An input power control panel (located in a lower front of the equipment cabinet) contains a fuse, a power receptacle, and a removable configuration plug. The configuration plug must be wired for the proper voltages. The power panel contains two outlets. One outlet is live when the circuit breaker is ON. The other outlet is live when the circuit breaker is on and a control signal is applied through a connector (P2) on the power panel.

Figure 1-6. Typical Terminal Controller Card Locations

Table 1-1. Physical Characteristics

| TERMINAL CONTROLLER                |                                                                                                                                        |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Height<br>Width<br>Depth<br>Weight | 10.5 inches (26.8 cm) 19.0 inches (48.2 cm) including mounting flanges 16.0 inches (40.6 cm) 55 pounds (25 kg) including circuit cards |

| CIRCUIT CARDS                      |                                                                                                                                        |

| Height<br>Width                    | 12-3/8 inches (31.4 cm)<br>7-3/4 inches (19.7 cm)                                                                                      |

#### 1.4 POWER AND ENVIRONMENTAL REQUIREMENTS

The terminal controller requires 250W of single-phase primary power. The power source must be within six cable-feet of the terminal controller.

The terminal controller fits a 10.5-inch vertical space in a standard 19-inch equipment rack, either directly or on slides. The controller can also be supplied as a stand-alone cabinet unit.

The operating environment temperature range is  $+15^{\circ}\text{C}$  (59°F) through  $+40^{\circ}\text{C}$  (104°F). The relative humidity should not exceed 90%.

## 1.5 PERFORMANCE SPECIFICATIONS

Table 1-2 lists the performance specifications for the overall terminal controller and its assemblies where applicable.

## 1.6 EQUIPMENT IDENTIFICATION

The part number of the terminal controller is a function of its card complement and thus varies from installation to installation. The Sanders identification plate at the rear of the terminal controller carries the part number, voltage rating, current rating, and UL, CSA, and VDE identification.

The part number of the card cage is 5977184.

Nomenclatures and part numbers for the circuit cards are etched on the component side of the cards. Serial numbers are stenciled next to part numbers.

All correspondence and documentation concerning the terminal controller or its assemblies should include full identification data.

# 1.7 TEST EQUIPMENT REQUIRED

Digital voltmeter

The following equipment (or equivalent) is recommended for maintenance of the terminal controller:

Oscilloscope Tektronix type 547 with type 1A1 preamplifier

Fluke model 8000A

Multimeter Triplett model 630

Card extender Sanders part no. 4171110

## 1.8 RELATED PUBLICATIONS

Publications relating to the GRAPHIC 8 system are as follows:

| PUBLICATION NO. | <b>k</b>      |                | TITLE                 |              |

|-----------------|---------------|----------------|-----------------------|--------------|

| н-80-0483       | GRAPI         | HIC 8 Technica | al Description        |              |

| H-80-0444       | GRAPI         | HIC 8 Programm | ner's Reference Manua | 1            |

| H-81-0021       | GRAPI         | HIC 8 Fortran  | Support Package Refe  | rence Manual |

| H-81-0027       | GRAPI         | HIC 8 Terminal | Controller Maintena   | nce Manual   |

| H-81-0097       | GRAPI<br>Manu |                | l Controller Maintena | nce Diagrams |

| PUBLICATION NO.* | TITLE                                                                                       |

|------------------|---------------------------------------------------------------------------------------------|

| H-81-0120        | GRAPHIC 8 19-Inch Color Display Manual                                                      |

| н-80-0087        | Terminal Controller Power Supply Model MM23-E0647/115                                       |

| н-79-0350        | Model 5753 2-D/3-D Coordinate Converter User's Manual                                       |

| н-79-0363        | Model 5783 Alphanumeric Function Keyboard/Model 5784 Lighted Alphanumeric Function Keyboard |

| H-78-0044        | Model 5786 Trackball/Model 5787 Forcestick Entry<br>Devices Technical Manual                |

| н-81-0129        | GRAPHIC 8 Installation Manual                                                               |

\*This column lists the manual's basic number. Revisions are indicated on the cover of the manual by a letter following this basic number.

## 1.9 MNEMONICS CONVENTIONS

The convention established for naming mnemonics throughout this manual is as follows. In general, terminal controller mnemonics consist of six characters. The first four are an alphanumeric abbreviation of the signal name. The fifth is a sign (+ or -) that indicates the active state of the signal (high or low). The sixth character is an alphabetic code that identifies the source of the signal as follows:

| SOURCE CODE | SOURCE                     |

|-------------|----------------------------|

| В           | Processor bus signal       |

| D           | Display processor          |

| F           | ROM and status             |

| H           | Digital graphic controller |

| I           | Parallel interface         |

| M           | Read/write memory          |

| N           | Mapping memory             |

| S           | Multiport serial interface |

| U .         | Timing module              |

| V           | Video controller           |

| X           | Multiple source            |

|             |                            |

Register and bus mnemonics use the lowest numeric to designate the least significant bit and the highest numeric to designate the most significant bit. For example, in the terminal controller data bus:

DA00-B = LSBDA15-B = MSG

# Power supply mnemonics are as follows:

| MNEMONIC | DESCRIPTION    |

|----------|----------------|

| PO5V+    | +5 Vdc         |

| P15V+    | +15 Vdc        |

| N1 5V -  | -15 Vdc        |

| ARET-    | Analog ground  |

| DRET-    | Digital ground |

| CGND     | Chassis ground |

|          |                |

Table 1-2. GRAPHIC 8 Terminal Controller (Model 8XXX) Specifications

| GENERAL                           |                                        | GRAPHIC CONTROLLER                           |                      |

|-----------------------------------|----------------------------------------|----------------------------------------------|----------------------|

| Power Source                      | 115 <u>+</u> 10 vac<br>47 to 63 Hz     | Parallel Microprocessor                      | 16 bits              |

| Power                             | 300 Watts                              | Display Instructions                         | 50 plus              |

| Temperature Storage               | 0° to 50°C                             | Synchronized Linkage to<br>Display Processor | Yes                  |

| Temperature Operating             | 15° to 40°C                            | Subroutine Stack                             | Yes                  |

| Relative Humidity                 | 10 to 90%                              | Display Registers                            | 64 plus              |

| Dimensions:                       |                                        | Registers (GP)                               | 4                    |

| Rack Mount Configuration          |                                        | VECTORS/CONICS                               |                      |

| Height<br>Width                   | 10.5 in (26.8 cm)<br>19.0 in (48.2 cm) | Line Texture                                 | 4                    |

| Depth                             | 16.0 in (40.6 cm)                      | Ellipse                                      | any<br>angle         |

| Weight                            | 55 lbs (25 kg)<br>including cards      | CHARACTERS                                   |                      |

| Equipment Cabinet Configur        | _                                      | Font Size                                    | 5 x 7<br>7 x 9       |

| Height<br>Width                   | 30 in (76.2 cm)<br>23 in (58.4 cm)     | Character Set (STD)                          | 96                   |

| Depth                             | 30 in (76.2 cm)                        | User Defined (OPT)                           | 96                   |

| Weight                            | 155 1bs (70.3 kg) on four casters      | Rotation                                     | 90° CLK              |

| DISPLAY PROCESS                   | OR                                     | Sizes                                        | 3                    |

| General Purpose<br>Microprocessor | Yes                                    | Tabular Characters                           | Auto Text<br>Spacing |

| Word Length                       | 16 bits                                | Positioning                                  | Random               |

| Byte Mode                         | 8 bits                                 | MAPPING MEMORY                               |                      |

| Instructions                      | 400 plus                               | Addressable<br>Locations                     | 2048 x<br>2048       |

| Registers                         | 8                                      | Bits/Pixel                                   | 2,4,8                |

| Hardware Stacks                   | Yes                                    | VIDEO CONTROLLER                             |                      |

| Automatic Priority<br>Interrupt   | Yes                                    | Blink                                        | Yes                  |

| Memory                            | 16 bit words                           | Color or Gray Level                          | 256                  |

| ROM                               | 8192 words                             | Screen Splits                                | 3<br>non-            |

| RAM<br>Expansion RAM to           | 65,536 words<br>131,072 words          | Cursor                                       | destructive          |

| INTERFACE OPTIONS                 |                                        | Terminations                                 | 75 ohm               |

| Parallel                          | 16 bits                                | Video                                        | Composite            |

| •                                 | 32 bits (optional)                     | Displays Max                                 | 6                    |

| Serial                            | RS-232C                                |                                              |                      |

, 9 [ 1

#### SECTION 2

#### OPERATION

#### 2.1 GENERAL

This section contains information for operating the GRAPHIC 8 terminal controller. Topics discussed include: controls and indicators, turn-on procedure, and operation in the SYSTEM and LOCAL modes.

## 2.2 CONTROLS AND INDICATORS

Table 2-1 lists the terminal controller controls and indicators, their locations and functions. Figure 2-1 shows their location on the equipment. Circuit connections for the controls and indicators are shown on the applicable terminal controller diagrams in the Terminal Controller Diagrams Manual (H-81-0097).

| Table 2-1. Terminal Co | ontroller | Controls | and | Indicators |

|------------------------|-----------|----------|-----|------------|

|------------------------|-----------|----------|-----|------------|

| NOME NCLATURE                   | LOCATION                   | FUNCTION                                            |

|---------------------------------|----------------------------|-----------------------------------------------------|

| POWER ON/OFF circuit<br>breaker | Top right of control panel | Energizes/deenergizes terminal controller           |

| RUN/SYS pushbutton              | Top right of control panel | Initiates SYSTEM mode (host computer control)       |

| RUN/SYS lamp                    | In RUN/SYS pushbutton      | Indicates display processor card operating          |

| DIS/LOC pushbutton              | Top right of control panel | Initiates LOCAL mode (GCP/<br>operator commands)    |

| DIS/LOC lamp                    | In DIS/LOC pushbutton      | Indicates digital graphic controller card operating |

## 2.3 TURN-ON PROCEDURE

NOTE

Refer to Section 5 for maintenance information if (a) RUN/SYS lamp does not light following power turn-on; (b) host computer subsequently reports terminal controller defective; or (c) terminal controller operation is suspect for any reason.

80-346-015

Figure 2-1. Terminal Controller Controls and Indicators

To turn the terminal controller on, press the 1 side of the POWER ON/OFF circuit breaker. This action lights the RUN/SYS lamp and applies power to the circuit cards.

Delay timers in the circuit cards allow initial power surges to settle, then initialize the terminal controller in the SYSTEM mode. All peripheral devices are reset, and the GCP performs automatic diagnostic tests to verify operation of the basic terminal controller functions.

If the terminal controller is connected to a host computer that is already operating, the controller automatically transmits a performance status report to the computer. If the host computer is not operating, the computer can receive this status report only by initializing the terminal controller as part of its own turnon procedure. In either case, the host computer's response to the status report is a function of the host computer application software.

# 2.4 OPERATING PROCEDURES

The terminal controller has two types of operation:

- 1. Normal Operation: regular controller functions performed in the SYSTEM or LOCAL mode.

- 2. Checkout: operator test of controller operation.

- 2.4.1 NORMAL OPERATING PROCEDURES. After normal turn-on, the terminal controller is in the SYSTEM mode; i.e., under host computer control. Pressing the DIS/LOC pushbutton places the terminal controller in LOCAL mode, under GCP control and operator commands. The terminal controller remains in LOCAL mode until it is placed in SYSTEM mode again as described in paragraph 2.4.1.1.

- 2.4.1.1 SYSTEM Mode Operation. This mode is established when one of the following occurs:

- 1. When primary ac power is applied to the terminal controller.

- 2. When you press the RUN/SYS pushbutton.

- 3. When the terminal controller is in LOCAL mode and you type S on the keyboard.

- 4. When the terminal controller is in LOCAL mode and you type 157760G RETURN on the keyboard.

- 5. When an initialize signal comes from the host computer via the parallel interface or the multiport serial interface.

- 6. When the terminal controller is in the teletypwriter emulation mode (see paragraph 2.4.2.5) and you press function key F13 on the keyboard or the host computer sends octal code 035 (ASCII control character GS Group Separator).

If the terminal controller is already in SYSTEM mode, it can be initialized again by either of the following:

- 1. A discrete initialize signal from the host computer via the parallel interface or the multiport serial interface.

- 2. An IZ (initialize) message from the host computer.

Initialization in the SYSTEM mode automatically causes the built-in diagnostic routines to be performed and the results sent in an error status message to the host computer. The diagnostic routines include GO/NO-GO checks of the graphic controller, display processor, read/write memory, 2-D/3-D coordinate converter (if installed), and either the parallel interface or the multiport serial interface (whichever is the device used for communications with the host computer). The error status message also includes a checksum of GCP stored in read-only memory.

In the SYSTEM mode, responses to all operator actions are determined by the application program of the host computer. Control is exercised and data is transferred by means of messages sent between the host computer and the terminal controller. See the GRAPHIC 8 Programmer's Reference Manual, Sanders document H-80-0444.

The host computer application program accesses all display registers and parameters for organization of display images. The initialization sequence enables the associated keyboards so you can enter commands without special action by the host computer.

The GCP handles all internal display interrupts and operator inputs. The GCP performs all housekeeping required for these events, and sends the host computer a message containing all information needed for operational decisions. However, the host computer can preset the terminal controller to transmit only specified signals under specified conditions.

The GCP processes trackball, forcestick, or data tablet inputs without host computer intervention. The GCP detects all PED (position entry device) inputs and either transmits them to the host computer, or uses them to update the position of a predefined PED identifier symbol on the display. GCP processing of PED symbols is controlled by the host computer application program.

GCP also inserts alphanumeric data from the keyboard into the refresh pattern; you can enter and edit a message without host computer intervention. You complete your entry by pressing the RETURN key, and GCP informs the computer that a new message is ready. The application program indicates how alphanumeric inputs are handled by issuing special commands.

2.4.1.2 LOCAL Mode Operation. After primary power has been applied to the terminal controller, you can initialize the terminal controller in LOCAL mode by pressing the DIS/LOC pushbutton. When you press this pushbutton, the verification test pattern appears on each of the associated display indicators, the terminal controller performs its built-in diagnostic routines, and local mode commands can be executed.

When you press the DIS/LOC pushbutton, the built-in diagnostic exercises the complete memory system. For systems containing more than 32K of memory, it may take several seconds before the terminal verification pattern appears. As part of the memory diagnostic, the memory configuration installed in the terminal controller is saved and can be examined if desired. Address 736 contains the RAM configuration word; address 750 contains the ROM configuration word.

2.4.1.3 <u>Verification Test Pattern and Diagnostics.</u> Figure 2-2 shows the verification test pattern that is displayed on each display indicator when the terminal controller is initialized in the LOCAL mode. The pattern remains displayed until terminated by the proper command or until 45 minutes have elapsed since that last performed operation that affected the pattern.

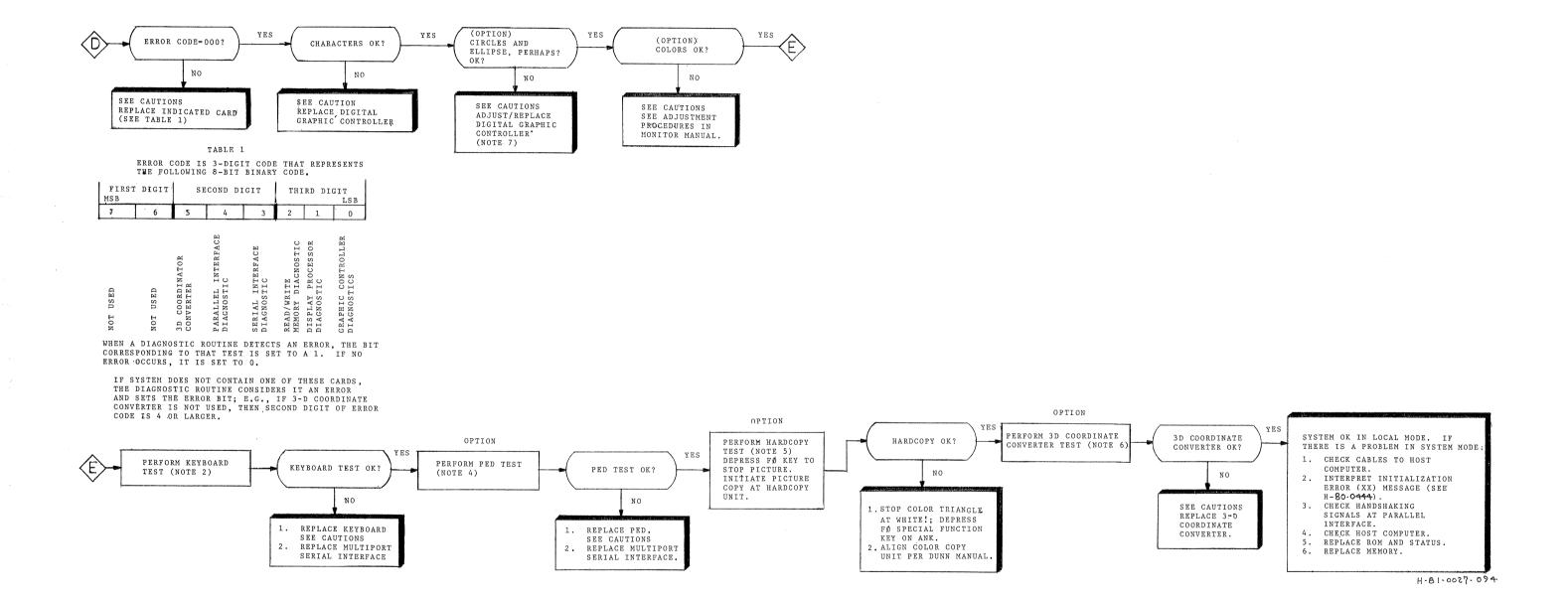

When the system is first initialized in the LOCAL mode, 'XX' appears in the small box in the lower right portion of the pattern. The 'XX' indicates that the code appearing in the same box contains the results of the built-in diagnostic routines that were automatically performed. The diagnostic code is a three-digit octal representation of an eight bit binary code that indicates the results of each diagnostic routine. Bits in the binary code are assigned as follows:

| MSB      |          |                                     |                                  | •                              |                                 |                                 | LSB                              |

|----------|----------|-------------------------------------|----------------------------------|--------------------------------|---------------------------------|---------------------------------|----------------------------------|

| 7        | 6        | 5                                   | 4                                | 3                              | 2                               | 1                               | 0                                |

| NOT USED | NOT USED | 3-D COORDINATE CONVERTER DIAGNOSTIC | PARALLEL INTERFACE<br>DIAGNOSTIC | SERIAL INTERFACE<br>DIAGNOSTIC | READ/WRITE MEMORY<br>DIAGNOSTIC | DISPLAY PROCESSOR<br>DIAGNOSTIC | GRAPHIC CONTROLLER<br>DIAGNOSTIC |