# SCC 655/660/670 DIGITAL COMPUTERS 1.75 µS·24 BIT

# The SCC 655/660/6701.75 µs Digital Computers

"Understandable" is the word that best describes the Scientific Control Corporation Computer family. These flexible machines offer powerful instruction repertoires that uniquely simplify computer programming.

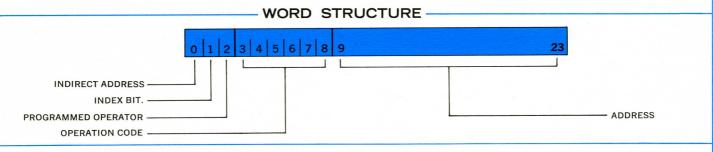

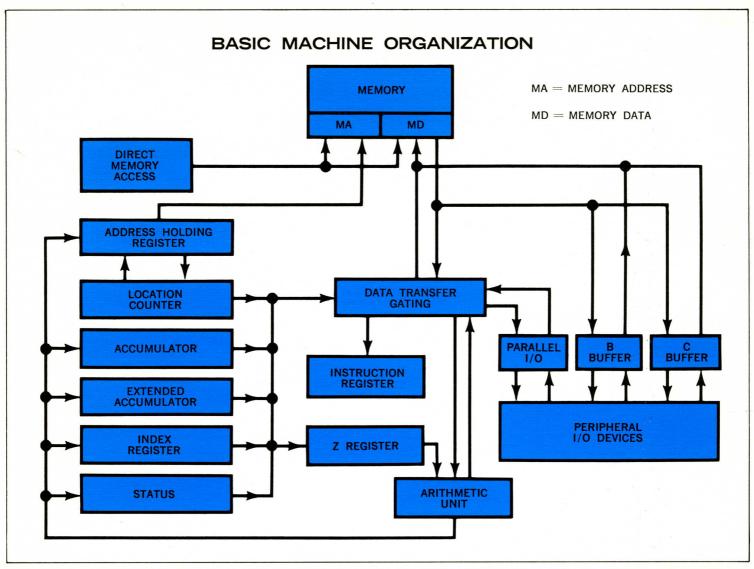

The SCC 655/660/670 series computers are 24 bit, fully parallel binary computers. They provide high speed processing by means of features that include:

- Integrated Circuits

- Direct Memory Access (DMA)

- Fully Parallel Operation

- Hardware Multiply/Divide

- Indexing

- Multi-level Indirect Addressing

- Comprehensive Instruction List

- Flexible Input/Output Structure

- Automatic Subroutine Linkages

### CENTRAL PROCESSING UNIT (CPU)

|                                                  | <u>655</u> | 660        | 670        |

|--------------------------------------------------|------------|------------|------------|

| Word Length (Bits)                               | 24         | 24         | 24         |

| Cycle Time (Microseconds)                        | 1.75       | 1.75       | 1.75       |

| Parallel Word I/O Channel Maximum Word Rate (KC) | Yes<br>190 | Yes<br>190 | Yes<br>190 |

| Priority Interrupt Channels                      | 1-64       | 2-64       | 2-64       |

| Hardware Multiply/Divide                         | Yes        | Yes        | Yes        |

| Program Protect Feature                          | Yes        | Yes        | Yes        |

| Internal Processing                              | Parallel   | Parallel   | Parallel   |

| Fortran Compiler (one pass)                      | Yes        | Yes        | Yes        |

| Symbolic Assembler (two pass)                    | Yes        | Yes        | Yes        |

| Basic Investment for CPU                         | \$15,900   | \$31,000   | \$42,750   |

|                                                  |            |            |            |

The SCC 655 with 38 instructions stands out as the lowest investment for a 24-bit computer.

The SCC 660 is for the user who needs additional processing capability for a modest investment. It offers 59 instructions including a set of micro-instructions.

The SCC 670 is the most powerful 24-bit computer offered by the company. It has 71 instructions that also include a comprehensive set of microinstructions for performing data

transfers and logical and arithmetic operations.

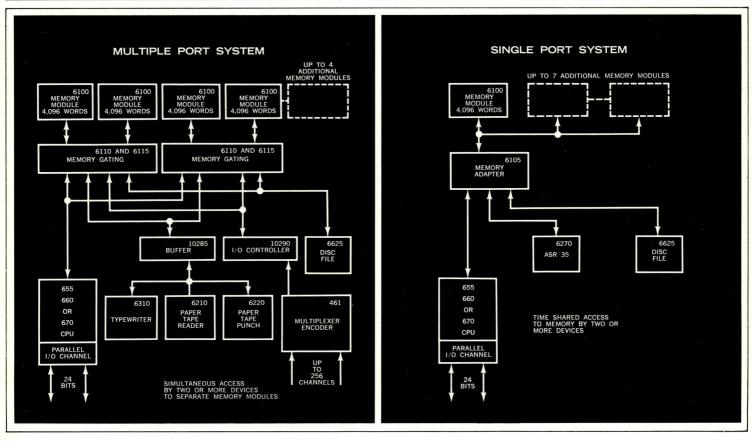

The 24 bit series of computers offer high value for investment. They are fully parallel and provide either single or multiple and simultaneous access channels to the memory. The memory systems can be expanded modularly from 4,096 words to 32,768 words. In addition, character oriented I/O buffers and a comprehensive line of peripherals are available.

### INSTRUCTION LISTS

| Data Transfer Instructions                                                                     |                                                                                                                                                                                                                                                |                                                                                  |                       |                                      |                                                          |                                                |

|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------|--------------------------------------|----------------------------------------------------------|------------------------------------------------|

| Mnemonic                                                                                       | Instruction Name                                                                                                                                                                                                                               | Op Code                                                                          | 655                   | 660                                  | 670                                                      | Cycles                                         |

| LDA<br>STA<br>LDE<br>STE<br>LDX<br>STX<br>EAX<br>LAC<br>LXC<br>XXM<br>SAF<br>LDD<br>STD<br>XAM | Load AC Store AC Load EA Store EA Load Index Store Index Effective Address Into Index Load AC Complemented Load Index Complemented Exchange Index and Memory Store Address Field Load Double Store Double Exchange AC and Memory               | 27<br>35<br>75<br>36<br>71<br>37<br>77<br>45<br>44<br>76<br>42<br>04<br>05<br>62 | × × × × × × ×         | ×<br>×<br>×<br>×<br>×<br>×<br>×<br>× | ×<br>×<br>×<br>×<br>×<br>×<br>×<br>×<br>×<br>×<br>×<br>× | 22222122333333                                 |

|                                                                                                | Instructions                                                                                                                                                                                                                                   | 55                                                                               | ~                     | ~                                    | ~                                                        | 2                                              |

| ADD<br>SUB<br>MPY<br>DIV<br>MIN<br>MDC<br>ADC<br>AAM<br>SBC<br>ADE<br>SBE                      | Add Subtract Multiply Divide Memory Increment Memory Decrement Add with Carry Add AC to Memory Subtract Add to EA Subtract from EA                                                                                                             | 55<br>54<br>64<br>65<br>61<br>60<br>57<br>63<br>56<br>07<br>06                   | X<br>X<br>X<br>X      | ×<br>×<br>×<br>×                     | X<br>X<br>X<br>X<br>X<br>X<br>X                          | 22893323322                                    |

| Logic Instructions                                                                             |                                                                                                                                                                                                                                                |                                                                                  |                       |                                      |                                                          |                                                |

| AND<br>ORA<br>EOR                                                                              | AND to AC<br>OR to AC<br>Exclusive OR to AC                                                                                                                                                                                                    | 14<br>16<br>17                                                                   | ×<br>×                | X<br>X                               | X<br>X<br>X                                              | 2<br>2<br>2                                    |

| Branch Instructions                                                                            |                                                                                                                                                                                                                                                |                                                                                  |                       |                                      |                                                          |                                                |

| BRA<br>BIX<br>BSL<br>BRT<br>BAZ<br>BRI<br>BAN<br>BAP<br>BEN<br>BEZ                             | Branch Increment Index and Branch Store Location Counter and Branch Return Branch Branch on AC Zero Return Branch and Clear Interrup Branch on AC Negative Branch on AC Positive Branch on EA Negative Branch on EA Negative Branch on EA Zero | 01<br>41<br>43<br>51<br>25<br>t 11<br>24<br>26<br>22<br>15<br>21                 | ×<br>×<br>×<br>×<br>× | X<br>X<br>X<br>X<br>X<br>X           | ×<br>×<br>×<br>×<br>×<br>×<br>×                          | 1<br>1<br>2<br>2<br>1<br>2<br>1<br>1<br>1<br>1 |

| Skip Instr                                                                                     | uctions                                                                                                                                                                                                                                        |                                                                                  |                       |                                      |                                                          |                                                |

| SNS<br>SAG<br>SMN<br>SAM                                                                       | Skip if Signal Not Set Skip if AC Greater Skip if Memory Negative Skip if AC and Memory do not compare ones.                                                                                                                                   | 40<br>73<br>53<br>72                                                             | ×<br>×<br>×           | ×<br>×<br>×                          | X<br>X<br>X                                              | 2<br>2<br>2<br>2                               |

| SAE                                                                                            | Skip if AC Equals Memory on EA<br>Mask                                                                                                                                                                                                         | 70                                                                               |                       | ×                                    | ×                                                        | 3                                              |

| SEM<br>SAQ<br>SDE                                                                              | Skip if EA and Memory do not<br>compare ones.<br>Skip if AC equals Memory<br>Difference Exponents and Skip                                                                                                                                     | 52<br>50<br>74                                                                   |                       |                                      | ×<br>×<br>×                                              | 2<br>2<br>3                                    |

#### Shift Instructions

| Mnemonic                                                                  | Instruction Name                                                                                                                                                                                                                                                                 | Op Code                                                                                                                                     | 655              | 660                                  | 670                             | Cycles                                                                                                   |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------|

| LSH<br>LCY<br>RSH<br>RCY<br>NDX<br>ALS<br>ELS<br>ALC<br>ERC<br>ERC<br>SND | Left Shift Left Cycle Right Shift Right Cycle Normalize and Decrement Index AC Left Shift EA Left Shift AC Left Cycle EA Left Cycle AC Right Shift EA Right Shift AC Right Cycle EA Right Cycle EA Right Cycle EA Right Cycle EA Right Cycle Short Normalize and Decrement Index | 67000XX<br>67200XX<br>66000XX<br>66200XX<br>67100XX<br>67040XX<br>67020XX<br>67020XX<br>67020XX<br>66040XX<br>66020XX<br>66240XX<br>66220XX | ×<br>×<br>×<br>× | ×<br>×<br>×<br>×<br>×<br>×<br>×<br>× | X<br>X<br>X<br>X<br>X<br>X<br>X | 2+N/4<br>2+N/4<br>2+N/4<br>2+N/4<br>2+N/4<br>2+N/4<br>2+N/4<br>2+N/4<br>2+N/4<br>2+N/4<br>2+N/4<br>2+N/4 |

| Miscellaneous Instructions                                                |                                                                                                                                                                                                                                                                                  |                                                                                                                                             |                  |                                      |                                 |                                                                                                          |

| HLT<br>NOP<br>XEC                                                         | Halt<br>No Operation<br>Execute                                                                                                                                                                                                                                                  | 00<br>20<br>23                                                                                                                              | X<br>X<br>X      | X<br>X                               | X<br>X                          | 1<br>1<br>1*                                                                                             |

| Input/Output Instructions                                                 |                                                                                                                                                                                                                                                                                  |                                                                                                                                             |                  |                                      |                                 |                                                                                                          |

| TMB<br>WTP<br>TBM<br>RDP<br>ACT<br>TMC<br>TCM                             | Transfer Memory to B Write Parallel Transfer B to Memory Read Parallel Activate Transfer Memory to C Transfer C to Memory                                                                                                                                                        | 12<br>13<br>32<br>33<br>02<br>10<br>30                                                                                                      | ×<br>×<br>×<br>× | ×<br>×<br>×<br>×<br>×                | ×<br>×<br>×<br>×<br>×           | 2+wait<br>2+wait<br>2+wait<br>2+wait<br>1<br>2+wait<br>2+wait                                            |

| Microinstructions                                                         |                                                                                                                                                                                                                                                                                  |                                                                                                                                             |                  |                                      |                                 |                                                                                                          |

| MIC                                                                       | Microinstructions**                                                                                                                                                                                                                                                              | 46                                                                                                                                          |                  | X                                    | X                               | 1                                                                                                        |

<sup>\*</sup>Plus time of instruction executed.

<sup>\*\*</sup>Several instructions for performing data transfers, logical and arithmetic operations.

#### Peripherals

A comprehensive line of peripheral devices are available.

#### Software

SCC offers a Symbolic Assembler, Utility and Math Subroutines, Fortran, Diagnostic Routines and other software from a library of programs. Custom programming is avail-

able through qualified personnel who are capable of obtaining maximum use of the speed and flexibility of SCC Computers.

#### PHYSICAL CHARACTERISTICS

Standard Desk and Rack models available Power: 115 VAC, 60 CPS

Temperature Range: 0 to 60°C

#### **SERVICES**

Installation, warranty maintenance, operator and programmer training as well as complete documentation are offered.

SCC maintains complete support activities for its users. Installation and maintenance services are available through SCC offices strategically located throughout the United States. For pre-procurement demonstration of hardware and programs in Dallas, contact nearest regional office or the marketing department in Dallas.

#### **EASTERN REGION**

College Park, Maryland (Washington, D.C.) 301/779-2510

#### SOUTHEASTERN REGION

Huntsville, Alabama 205/881-8805

#### WESTERN REGION

Los Angeles, California 213/272-9311

#### SOUTHWESTERN REGION

Dallas, Texas 214/241-2111

#### MIDWESTERN REGION

Dallas, Texas 214/241-2111

#### CORPORATE MARKETING

Dallas, Texas 214/241-2111

83.22

## **Scientific Control Corporation**

P.O. Box 34529 • Dallas, Texas 75234 • 214 — 241-2111 • TWX 910-860-5509