#### SDS 940

# THEORY OF OPERATION

Technical Manual

SDS 98 01 26A

March 1967

· ·

SCIENTIFIC DATA SYSTEMS/1649 Seventeenth Street/Santa Monica, California/UP 1-0960

# TABLE OF CONTENTS

| Section |                                 |                              |                                          |                                                                  | Page                            |

|---------|---------------------------------|------------------------------|------------------------------------------|------------------------------------------------------------------|---------------------------------|

| I       | GEN                             | ERAL DES                     | CRIPTION .                               |                                                                  | 1-1                             |

|         | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Docume<br>Physica<br>Feature | entation<br>  Description<br>s           | n                                                                | 1-1<br>1-1<br>1-2<br>1-2<br>1-2 |

|         |                                 | 1.5.1                        |                                          | nput/Output System                                               | 1-6                             |

|         |                                 |                              | 1.5.1.1<br>1.5.1.2                       | Word Parallel System                                             | 1-6<br>1-8                      |

|         |                                 | 1.5.2<br>1.5.3               |                                          | tiplexed Communication Channels<br>mory Access System            | 1-8<br>1-9                      |

|         |                                 |                              | 1.5.3.1<br>1.5.3.2                       | Direct Access Communication Channels<br>Data Multiplexing System | 1-9<br>1-10                     |

|         |                                 | 1.5.4                        | Priority In                              | terrupt System                                                   | 1-10                            |

|         |                                 |                              | 1.5.4.1<br>1.5.4.2<br>1.5.4.3            | External Interrupt<br>Input/Output Channel<br>Real-Time Clock    | 1-11<br>1-12<br>1-12            |

|         | 1.6                             | Input/C                      | Dutput Devid                             | ces                                                              | 1-12                            |

|         |                                 | 1.6.1<br>1.6.2               |                                          | nput/Output Devices                                              | 1-12<br>1-14                    |

| II      | OPER                            | ATION A                      | ND PROGR                                 | AMMING                                                           | 2-1                             |

|         | 2.1<br>2.2<br>2.3               | Changi                       | ng Operation                             | n Modes                                                          | 2-1<br>2-2<br>2-2               |

|         |                                 | 2.3.1                        | Normal M                                 | ode                                                              | 2-2                             |

|         |                                 |                              | 2.3.1.1<br>2.3.1.2<br>2.3.1.3<br>2.3.1.4 | Interrupt Routine Return Instruction<br>Overflow Instructions    | 2-3<br>2-3<br>2-3<br>2-3        |

|         |                                 | 2.3.2                        | Monitor a                                | nd User Mode, Common Operations                                  | 2-4                             |

|         |                                 |                              | 2.3.2.1<br>2.3.2.2<br>2.3.2.3            | Hang-up Prevention                                               | 2-4<br>2-4<br>2-4               |

•

## TABLE OF CONTENTS (Continued)

Section

III

## Page

# II OPERATION AND PROGRAMMING (Continued) 2.3.2.4 Modified Unconditional Branch

|                                 |                                          | 2.3.2.5                                                                          | Instruction                                                                                                            | 2-5<br>2-5                                           |

|---------------------------------|------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                 | 2.3.3                                    | Monitor Mo                                                                       | ode                                                                                                                    | 2-5                                                  |

|                                 |                                          | 2.3.3.1<br>2.3.3.2<br>2.3.3.3<br>2.3.3.4                                         | Exclusive Use of User Map<br>Monitor Map<br>Special Monitor Mode EOM Instructions<br>Branch Instruction Return Address | 2-5<br>2-6<br>2-6                                    |

|                                 |                                          | 2.3.3.5<br>2.3.3.6                                                               | Changes<br>Other Instruction Operation Changes<br>Monitor-to-User Transition Trap                                      | 2-7<br>2-7<br>2-8                                    |

|                                 | 2.3.4                                    | User Mode                                                                        |                                                                                                                        | 2-8                                                  |

|                                 |                                          | 2.3.4.1<br>2.3.4.2                                                               | Privileged Instructions                                                                                                | 2-8<br>2-8                                           |

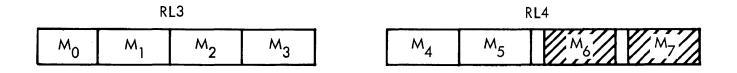

| 2.4<br>2.5<br>2.6<br>2.7<br>2.8 | Memory<br>Software<br>SDS 940<br>SDS 940 | r Interleaving<br>e<br>) Computer (<br>) Mnemonic ]                              | Dperation Codes                                                                                                        | 2-10<br>2-10<br>2-10<br>2-11<br>2-11<br>3-1          |

| 3.1<br>3.2                      | Genera                                   |                                                                                  | · · · · · · · · · · · · · · · · · · ·                                                                                  |                                                      |

|                                 | Machin                                   |                                                                                  |                                                                                                                        | 3-1<br>3-1                                           |

|                                 | Machin<br>3.2.1                          | e Language                                                                       |                                                                                                                        |                                                      |

|                                 |                                          | e Language                                                                       |                                                                                                                        | 3-1                                                  |

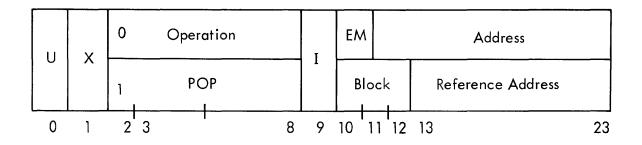

|                                 |                                          | e Language<br>Instruction<br>3.2.1.1<br>3.2.1.2<br>3.2.1.3<br>3.2.1.4            | Word Format                                                                                                            | 3-1<br>3-1<br>3-2<br>3-2<br>3-2<br>3-2<br>3-2        |

|                                 | 3.2.1                                    | e Language<br>Instruction<br>3.2.1.1<br>3.2.1.2<br>3.2.1.3<br>3.2.1.4<br>3.2.1.5 | Word Format                                                                                                            | 3-1<br>3-1<br>3-2<br>3-2<br>3-2<br>3-2<br>3-2<br>3-2 |

# TABLE OF CONTENTS (Continued)

-

~~

| Section |      |                |                                          |                                                                                                                                                               | Page                         |

|---------|------|----------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| III     | THEO | RY OF O        | PERATION                                 | (Continued)                                                                                                                                                   |                              |

|         | 3.5  | 940 Log        | jic                                      |                                                                                                                                                               | 3-4                          |

|         |      | 3.5.1          | Mode Cha                                 | nges                                                                                                                                                          | 3-4                          |

|         |      |                | 3.5.1.1<br>3.5.1.2<br>3.5.1.3            | Normal to Monitor Mode Change<br>Monitor to User Mode Change<br>User to Monitor Mode Change                                                                   | 3-5<br>3-5<br>3-6            |

|         |      | 3.5.2          | Traps                                    | ••••••••                                                                                                                                                      | 3-7                          |

|         |      |                | 3.5.2.1<br>3.5.2.2<br>3.5.2.3<br>3.5.2.4 | Privileged Instruction and Monitor<br>to User Transition Traps<br>Out–of–Bounds Trap<br>Real–Only Trap<br>Real–Only or Out–of–Bounds —<br>Additional Problems | 3-8<br>3-9<br>3-10<br>3-11   |

|         |      | 3.5.3<br>3.5.4 |                                          | terrupt Feature                                                                                                                                               | 3-11<br>3-13                 |

|         |      |                | 3.5.4.1<br>3.5.4.2<br>3.5.4.3            | Branch and Return from Interrupt<br>Routine Instruction ( $\phi 0 \longrightarrow \phi 6$ )<br>New Overflow Instructions<br>Modified EAX Instruction          | 3–13<br>3–14<br>3–15         |

|         |      | 3.5.5          | User Map                                 |                                                                                                                                                               | 3-15                         |

|         |      |                | 3.5.5.1<br>3.5.5.2                       | Select, Clear, and Load Relabeling<br>Register 1                                                                                                              | 3-15<br>3-17                 |

|         |      |                | 3.5.5.3                                  | Register 2                                                                                                                                                    | 3-17<br>3-17                 |

|         |      | 3.5.6          | Monitor M                                | lap                                                                                                                                                           | 3-18                         |

|         |      |                | 3.5.6.1                                  | Select, Clear, and Load Relabeling<br>Register 4                                                                                                              | 3-19                         |

|         |      |                | 3.5.6.2                                  | Monitor Map Control Logic                                                                                                                                     | 3-19                         |

|         |      | 3.5.7          | Memory                                   |                                                                                                                                                               | 3-20                         |

|         |      |                | 3.5.7.1<br>3.5.7.2<br>3.5.7.3<br>3.5.7.4 | Address Lines                                                                                                                                                 | 3-20<br>3-20<br>3-21<br>3-22 |

# TABLE OF CONTENTS (Continued)

| Section |                          |                                             |                                                                                                                                    | Page                            |

|---------|--------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| III     | THEO                     | Y OF OPERATIC                               | ON (Continued)                                                                                                                     |                                 |

|         |                          | 3.5.8 Logic                                 | Terms                                                                                                                              | 3-22                            |

|         |                          | 3.5.8<br>3.5.8                              |                                                                                                                                    | 3-22<br>3-27                    |

| IV      | INST                     |                                             | MAINTENANCE                                                                                                                        | 4-1                             |

|         | 4.1<br>4.2<br>4.3        | General Installe                            | ation Information                                                                                                                  | 4-1<br>4-1<br>4-1               |

|         |                          | 4.3.2 Relabe                                | ral Maintenance Information<br>eling Registers<br>ional Maintenance Information                                                    | 4-1<br>4-2<br>4-5               |

| V       | DRAW                     | INGS                                        | •••••••••••••                                                                                                                      | 5-1                             |

|         | 5.1<br>5.2<br>5.3<br>5.4 | 940 Computer .<br>Memory                    |                                                                                                                                    | 5-1<br>5-1<br>5-2<br>5-3        |

|         |                          | 5.4.2 Direct<br>5.4.3 Time M<br>5.4.4 WY In | ple Access to Memory<br>t Access Communication Channel<br>Multiplexed Communication Channel<br>nput/Output Buffer<br>Jumper Module | 5-3<br>5-4<br>5-4<br>5-4<br>5-5 |

| VI      | STAN                     | DARD EQUIPMEN                               | NT MANUALS                                                                                                                         | 6-1                             |

|         | 6.1                      | General                                     |                                                                                                                                    | 6-1                             |

| VII     | MOD                      | LE DATA SHEET                               | ·S                                                                                                                                 | 7-1                             |

|         | 71                       | General                                     |                                                                                                                                    | 7-1                             |

# LIST OF ILLUSTRATIONS

\_\_\_\_

| Figure |                                                     | Page |

|--------|-----------------------------------------------------|------|

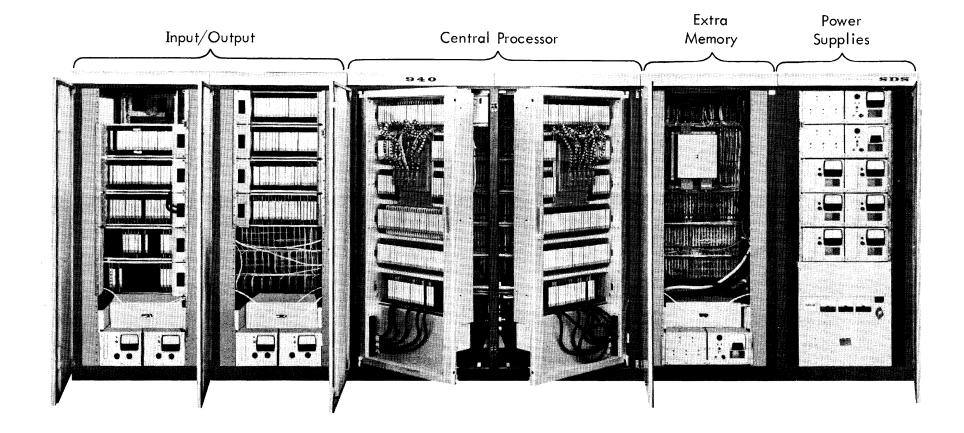

| 1-1    | SDS 940 Computer, Front View                        | 1-3  |

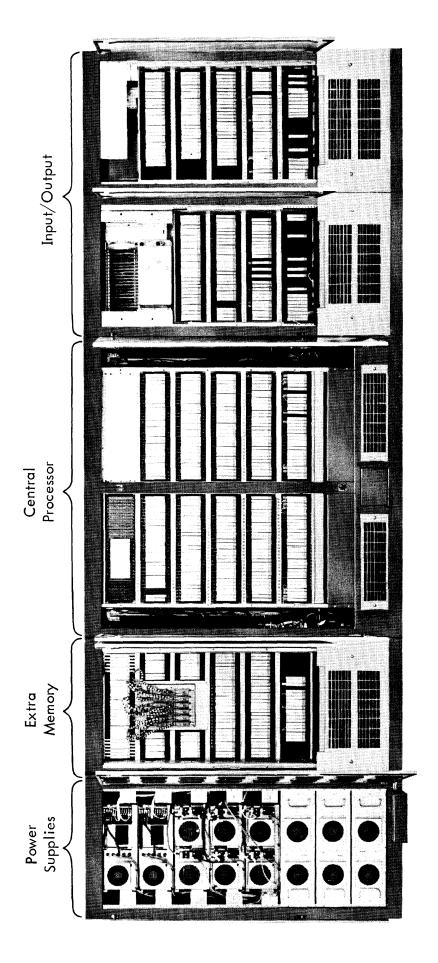

| 1-2    | SDS 940 Computer, Rear View                         | 1-4  |

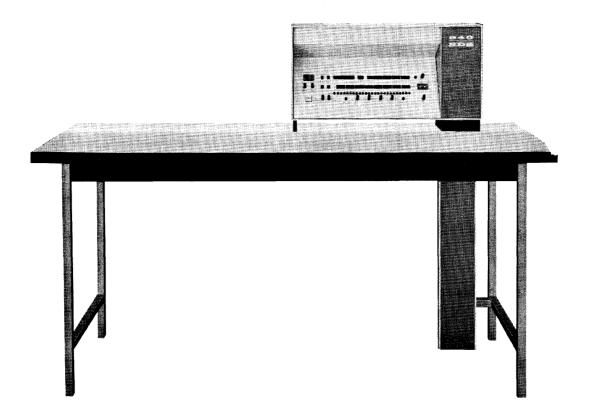

| 1-3    | SDS 940 Computer Console                            | 1-6  |

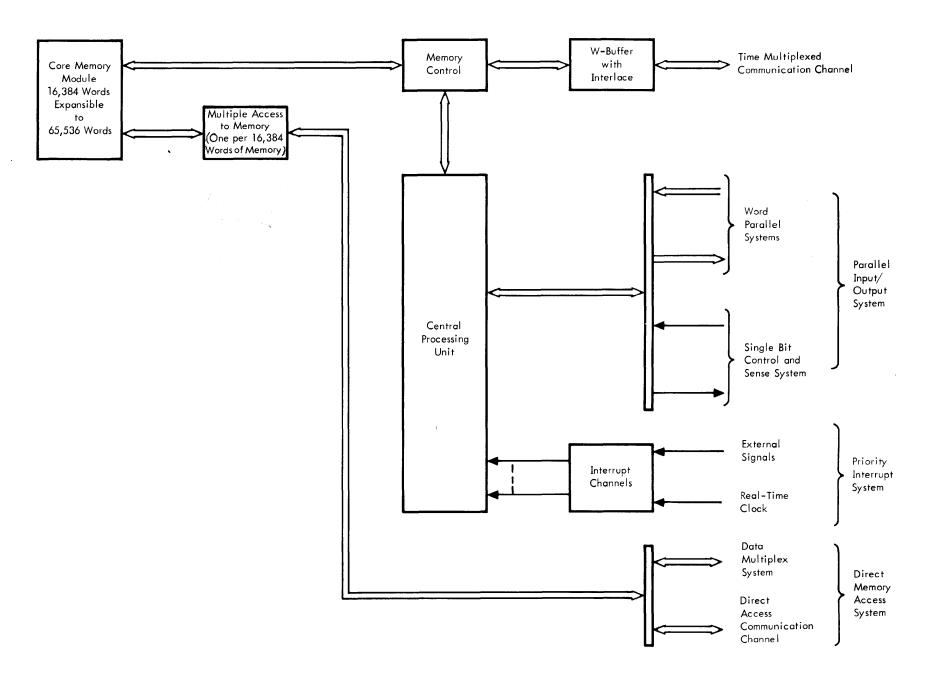

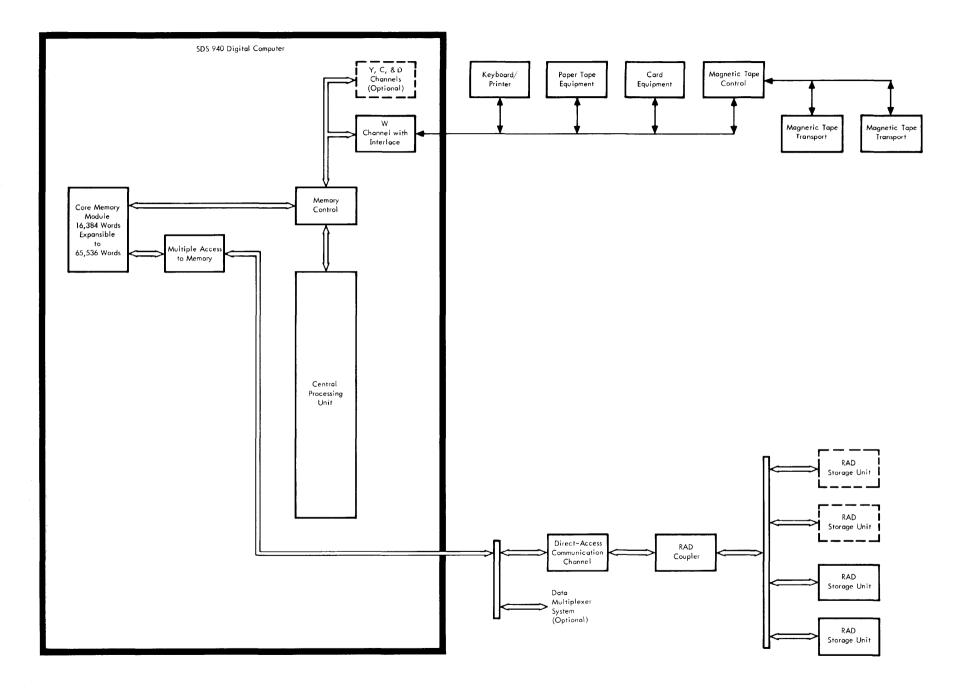

| 1-4    | Basic SDS 940 Computer Configuration                | 1-7  |

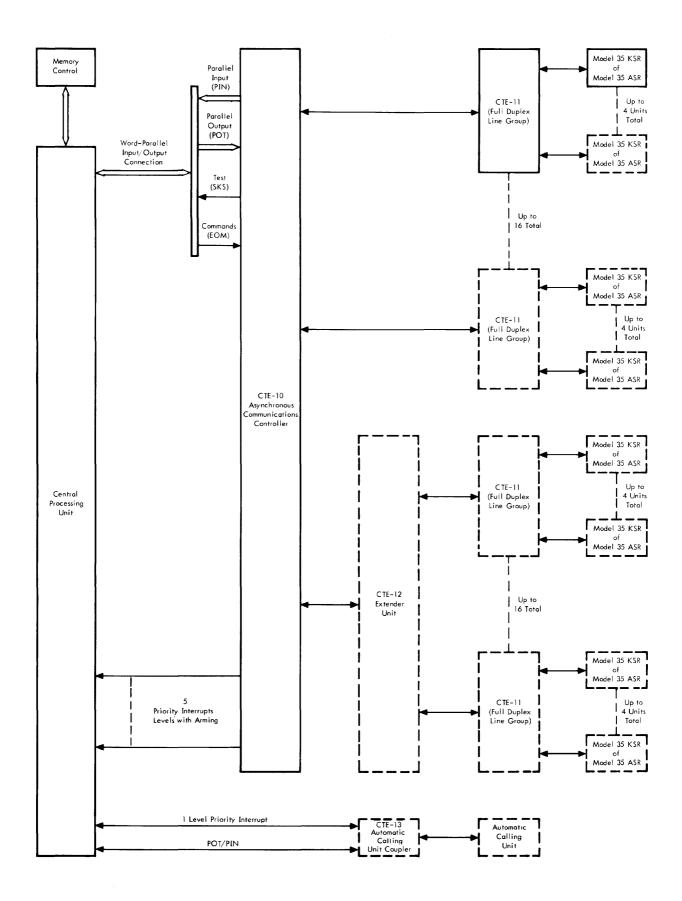

| 1-5    | Buffered Input/Output                               | 1-13 |

| 1-6    | Unbuffered Input/Output                             | 1-15 |

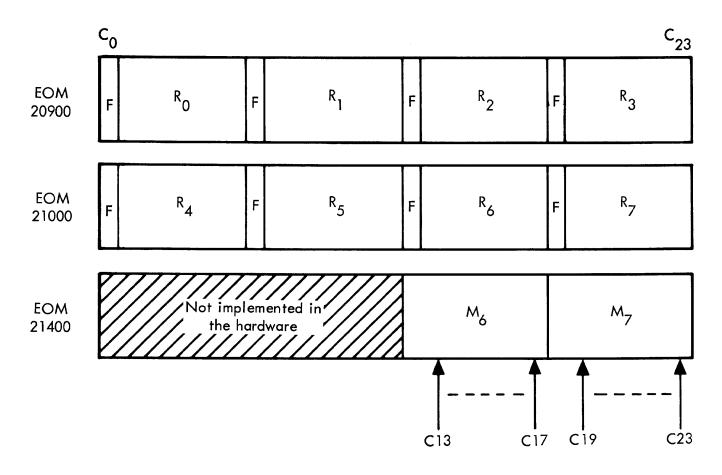

| 2-1    | Parallel Output Map Word Configurations             | 2-7  |

| 3-1    | Instruction Word Format                             | 3-2  |

| 3-2    | Fixed Point Data Word                               | 3-3  |

| 3-3    | Floating Point Data Words                           | 3-3  |

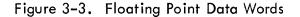

| 3-4    | BRM to Out-of-Bounds Address Timing                 | 3-12 |

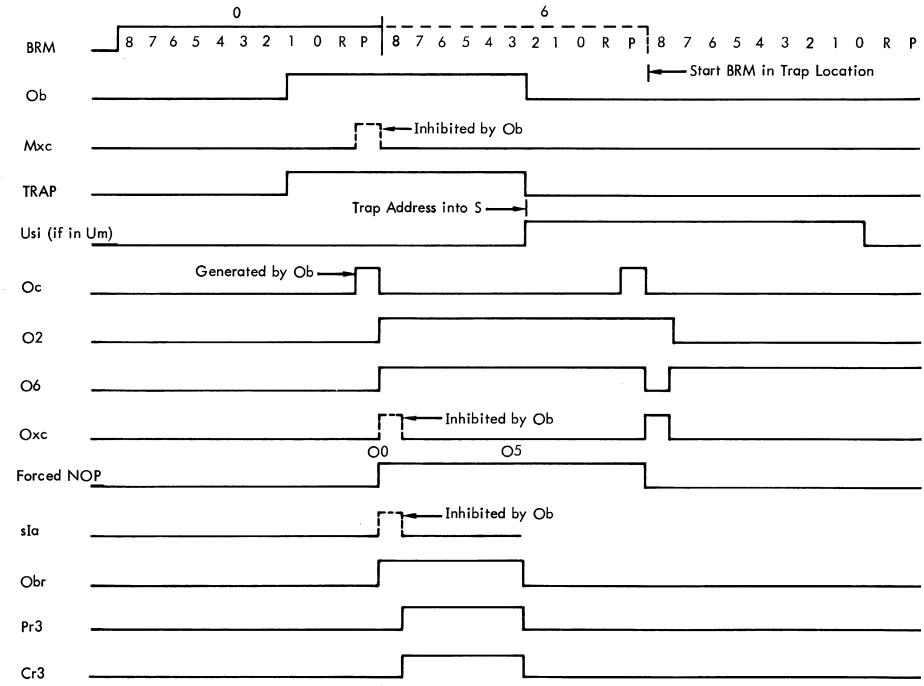

| 3-5    | SDS 940 Computer Mapping Process                    | 3-16 |

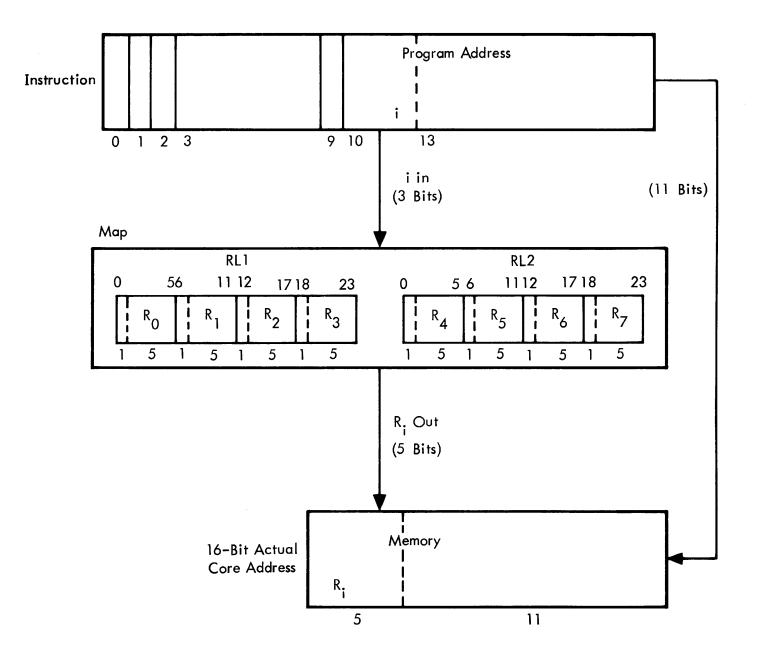

| 3-6    | Monitor Map Register Structure                      | 3-18 |

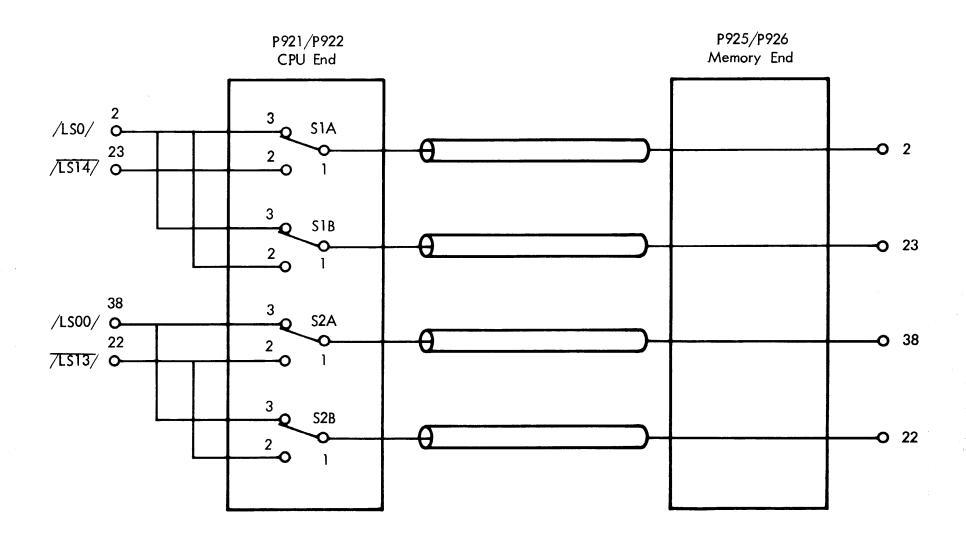

| 3–7    | 940 Computer Interleave Switch Arrangement          | 3-23 |

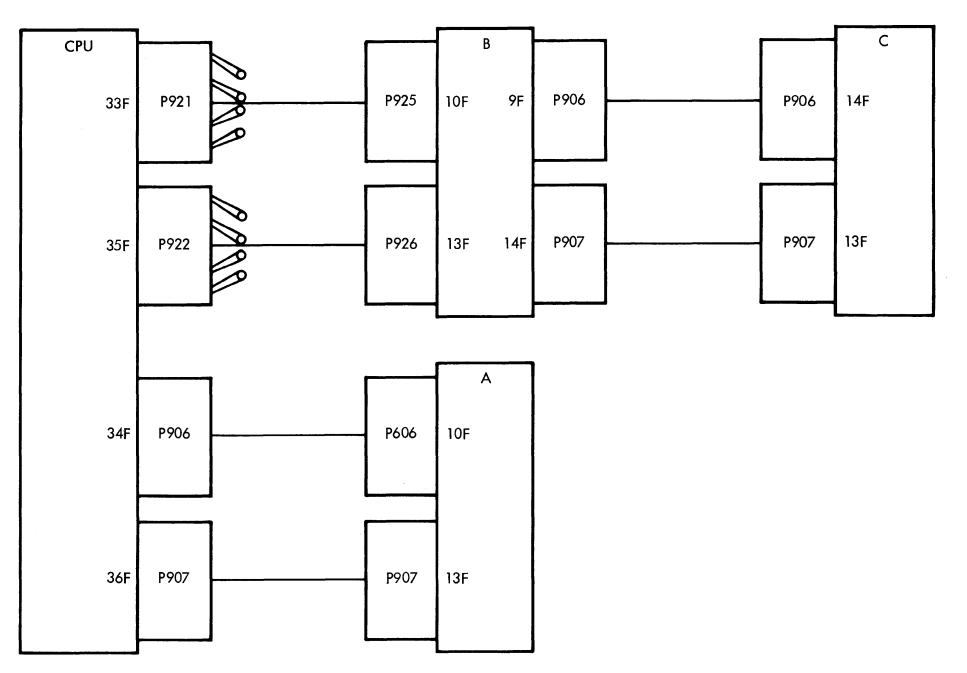

| 3-8    | Two Way Interleave, Three Memory Banks              | 3-24 |

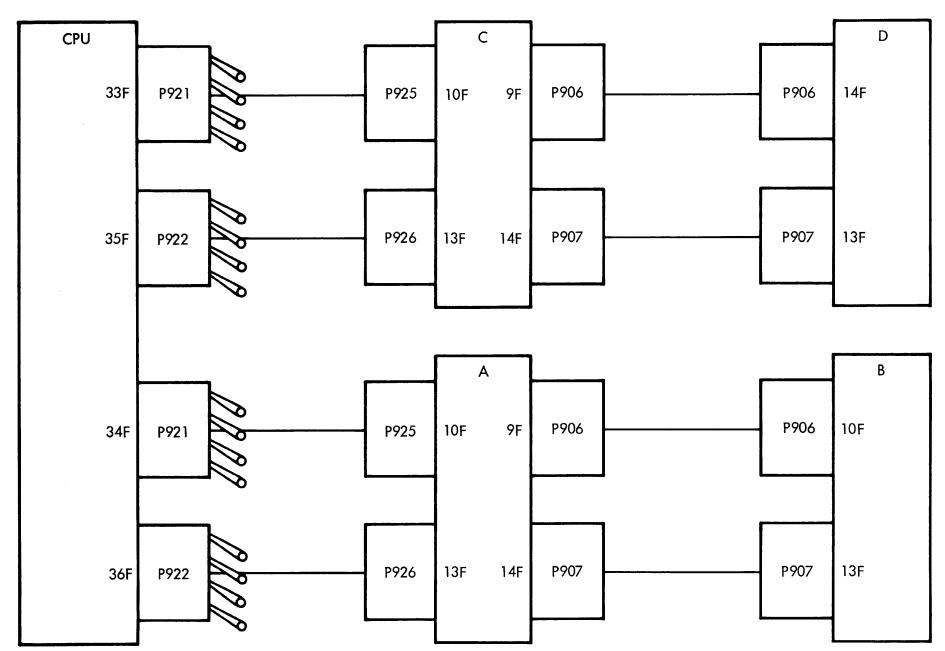

| 3-9    | Four Way Interleave, Four Memory Banks              | 3-25 |

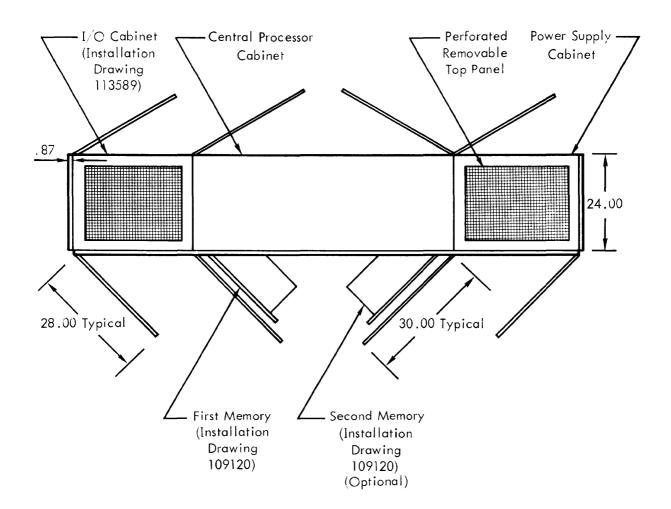

| 4-1    | 940 Computer Size Information                       | 4-2  |

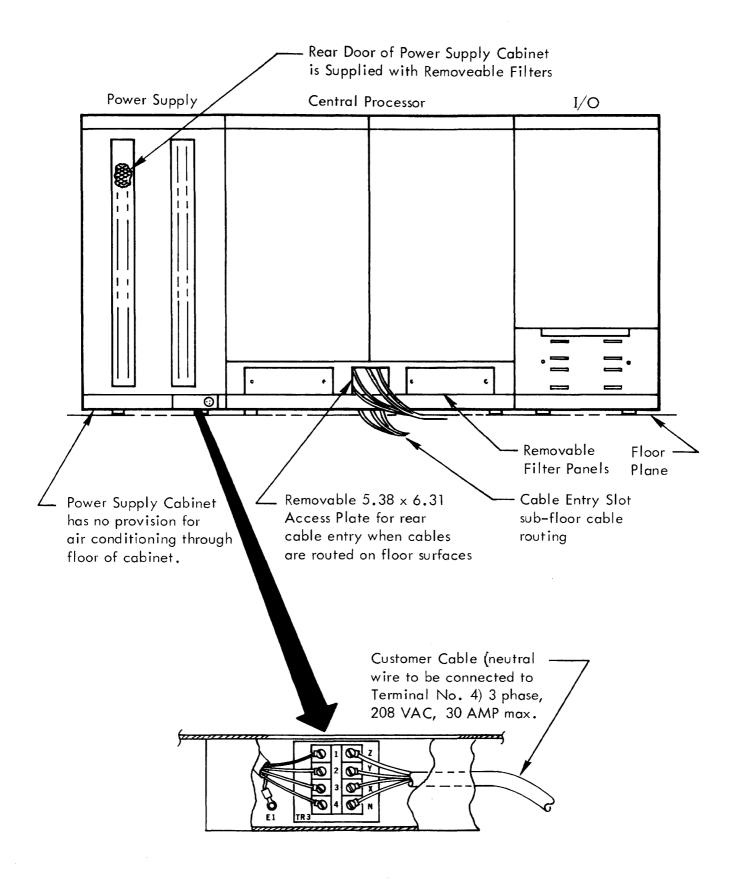

| 4-2    | 940 Computer Power and Air Conditioning Information | 4-3  |

#### LIST OF TABLES

| Table |                                 | Page |

|-------|---------------------------------|------|

| 1-1   | 940 Features                    | 1-5  |

| 1-2   | Buffered Input/Output Equipment | 1-14 |

| 2-1   | Overflow Instructions           | 2-3  |

| 2-2   | Monitor Mode EOM Instructions   | 2-6  |

| 2-3   | Privileged Operation Codes      | 2-9  |

| 2-4   | Time-Sharing Software           | 2-11 |

| 2-5   | 940 Operation Codes             | 2-12 |

| 2-6   | Instruction List                | 2-14 |

| 3-1   | Traps                           | 3–7  |

| 3-2   | Address Line Control            | 3-18 |

| 3-3   | Register Values                 | 3-19 |

# LIST OF TABLES (Continued)

| Table                                                                               |                                                                                                      | Page                                                                             |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 3-4<br>3-5<br>3-6<br>3-7                                                            | Jumper Module ZB 65-60<br>Jumper Module ZB 65-61<br>Jumper Module ZB 65-62<br>Jumper Module ZB 65-63 | 3-26<br>3-26<br>3-27<br>3-27                                                     |

| 4-1<br>4-2                                                                          | Relabeling Register 1 and 2 Information                                                              | 4-4<br>4-5                                                                       |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8<br>5-9<br>5-10<br>5-11<br>5-12 | Computer Assembly Drawings                                                                           | 5-1<br>5-2<br>5-2<br>5-2<br>5-3<br>5-3<br>5-3<br>5-3<br>5-4<br>5-4<br>5-5<br>5-5 |

| 6-1                                                                                 | 940 Computer Documentation                                                                           | 6-1                                                                              |

| 7-1<br>7-2                                                                          | Computer Logic Modules                                                                               | 7-1<br>7-2                                                                       |

.

#### I. GENERAL DESCRIPTION

#### 1.1 GENERAL

The SDS 940 Time-Sharing Computer is a general-purpose digital computer that operates at high internal speeds and uses a random access core memory. The SDS 940 Computer is an SDS 930 General Purpose Digital Computer that has been modified through the addition of special hardware features to produce an excellent computer for time-sharing applications.

From a hardware standpoint, the 940 Computer is a 930 Computer modified to permit time-sharing operation. The requirement that distinguishes the time-sharing atmosphere is many simultaneous users. The modifications enable the logic to preserve the privacy of each user. These modifications combine with the high speed of operation of the central processor to enable many users to use the computer capability simultaneously. The complete line of proven SDS peripheral equipment and all SDS system components are available with the 940 Computer to achieve unparalleled efficiency in handling the flow of information to and from the computer.

From a programming standpoint, the 940 Computer, being an extension of the 930 Computer, is fully compatible with all SDS 900 Series software. Because of this compatibility, the complete set of field-proven SDS software is available as any programs written for an SDS 900 Series computer can be run, without modification, on the 940 Computer. In addition, however, an extensive time-sharing software package is available for the 940 Computer that is not compatible with other SDS 900 Series Computers.

#### 1.2 DOCUMENTATION

Since a single manual presentation of all the documentation concerning the 940 Computer is impractical, this manual provides an introduction to the 940 Computer and provides information for locating additional information that might be useful in operating and maintaining the 940 Computer.

The contents of this manual present the differences between the 940 Computer and the 930 Computer. This manual is primarily for use by field maintenance personnel with a knowledge of the operation and maintenance of the 930 Computer. Thus, Section I, General Description, provides overall pictures of the 940 Computer as it normally appears as well as an overall description and applicable characteristics. Section II, Operation and Programming, describes the modes of operation of the 940 Computer, and presents the operation codes. The logic designed especially for the 940 Computer is described in Section III, Theory of Operation. Installation and maintenance instructions are provided in Section IV insofar as applicable. Lists of reference drawings, standard equipment manuals, and module data sheets are provided in subsequent sections in a manner facilitating ease of reference.

#### 1.3 PHYSICAL DESCRIPTION

The 940 Computer comprises a double-bay central processor cabinet, a single-bay power supply cabinet, a minimum of one single-bay input/output cabinet, and a control console. Figures 1-1 and 1-2 show the front and back of a 940 Computer, respectively.

A special swing-out door located behind the front cabinet doors in the two-bay central processor cabinet houses the memory logic chassis. The first 16, 384-word core memory is behind the left front door, the second 16, 384-word core memory is behind the right front door. Access to the back panel of the memory logic chassis is facilitated by the hinged memory doors. With the memory doors open, maintenance personnel can also gain access to the rear of the central processor logic modules. The central processor modules are loaded and removed from the rear of the cabinet behind the two central doors. Peripheral couplers are housed in the input/output cabinet as required. Additional cabinets can be added to house additional peripheral couplers. Eleven power supplies including power supplies for the two 16, 384-word core memories are housed in the power supply cabinet. Two additional 16, 384-word memories can be added and are housed in individual cabinets. The power supplies required by each memory are housed in the same cabinet as the memory. The additional memory cabinets are inserted between the central processor cabinets and the power supply cabinet.

Controls and indicators for manual operation and monitoring of the 940 Computer are panel mounted on a convenient table for ease of use as shown in Figure 1-3.

#### 1.4 FEATURES

As an extension of the 930 Computer, the 940 Computer retains all the features of the 930 Computer and provides additional special features. Monitor and User modes of operation are available in addition to the 930 Operation Mode. A hardware-implemented memory map, system programmed operators, and non-stop operation protection are also included. Additional 940 Computer features are presented in Table 1-1.

#### 1.5 INPUT/OUTPUT CAPABILITY

The 940 Computer has comprehensive input/output systems that complement the high internal processing speed and versatile instruction repertoire. These input/output systems have a scatter-write and a gather-read capability and can transmit data in word, character, or single-bit form to and from the computer at the speed of internal computation. While the input/output systems assume control of conditions imposed by various characteristics of a wide variety of devices, a high degree of control is left to the programmer. The computer configuration shown in Figure 1-4 contains four types of input and/or output.

- (a) Parallel Input/Output System. Direct parallel input/output of 24-bit information either external or program controlled and sequenced, and up to 16, 384 single-bit signals for output control or input test.

- (b) Time Multiplexed Communication Channels. Buffered input/output of data words, each under direct program control.

---3 ť

Figure 1-1. SDS 940 Computer, Front View

Figure 1–2. SDS 940 Computer, Rear View

1-4

| Table 1–1. | 940 Features |

|------------|--------------|

|------------|--------------|

| Feature             | Definition                                                                                                                                                                                                                                                                                                                                    |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Word Length         | 24 information bits plus parity bit.                                                                                                                                                                                                                                                                                                          |

| Arithmetic          | Binary                                                                                                                                                                                                                                                                                                                                        |

| Memory Size         | 16, 384–word memory is required for the Time–Sharing<br>Software system. Memory is expandable to 65, 536<br>words in 16, 384 word increments.                                                                                                                                                                                                 |

| Access Time         | A 0.7-microsecond access time results in a complete read/write cycle time of 1.75 microseconds.                                                                                                                                                                                                                                               |

| Memory Protection   | An optional feature enables the transfer of register contents to memory in the event of power failure.                                                                                                                                                                                                                                        |

| Memory Interleaving | When two devices are accessing different memory modules, the operations proceed simultaneously.                                                                                                                                                                                                                                               |

| Error Checking      | All memory operations and input/output transmissions are parity checked.                                                                                                                                                                                                                                                                      |

| Priority Interrupts | A completely automatic priority interrupt system<br>provides up to 896 optional priority levels individu-<br>ally armed and disarmed under program control.                                                                                                                                                                                   |

| Input/Output        | Six different input/output methods permit computer<br>operation with diverse input/output devices.<br>Extensive buffering allows numerous input/output<br>operations simultaneous with one another and with<br>computation. Magnetic tape and disc searching is<br>accomplished independent of memory, thereby<br>requiring no computer time. |

| Construction        | Exclusive use of silicon semiconductors assure high<br>reliability; the small component count yields very<br>long Mean time between failure rates. Air<br>conditioning is not required, since the central<br>processor operating temperature range is 10° to<br>40°C.                                                                         |

| Power Requirements  | 3 kva at 208 volts ± 10% (three-phase Y),<br>60 ± 0.5 cps.                                                                                                                                                                                                                                                                                    |

- (c) Priority Interrupt System. Permits immediate reaction to special external and internal conditions.

- (d) Direct Input/Output System. Input/output of characters or words from memory, time-shared and multiplexed with computation or fully buffered and simultaneou with computation.

Each individual type of input/output is more fully described in the paragraphs that follow.

Figure 1-3. SDS 940 Computer Console

1.5.1 PARALLEL INPUT/OUTPUT SYSTEM. The parallel input/output system yields high-speed input/output of data or control and test signals with a transfer rate of one 24-bit word in 1.75 microseconds. This system facilitates operation with many types of asynchronous information under program control.

1.5.1.1 Word Parallel System. Under program control, any word in the memory can be presented in word-parallel format (24 bits) at a processor connector. Also under program control, any 24-bit data word sent to the processor connector can be stored in any memory location. The execution of either operation starts with the transmission of a signal to the external device signifying that the computer is ready for the transmission of data.

2

Figure 1-4. Basic SDS 940 Computer Configuration

During input operation, the computer is in a hold condition until the external device selected has presented the data accompanied by a ready signal. Only after the computer has detected the ready signal can the computer terminate input and continue the program. During output, the computer is in a hold condition until the external device signals the computer that the selected data has been received. Therefore, all input transmissions are close-looped.

To overcome the necessity of locking up the computer during input, the ready signal from the external device can be used to initiate an interrupt that causes the computer to branch to an input routine when data is ready for input. The computer is thus free to execute other programs until information appears at the parallel input connection to be received and stored. To avoid the output hold, the external device can use the interrupt system to signal the computer to output data only after the peripheral device is ready to receive data from the computer.

If a series of data words are to be transferred to or from sequential memory locations, the address portions of these instructions must be modified. Address modification is accomplished by index registers in conjunction with instructions for modifying the register, or by indirect addressing with the addition of instructions used for incrementing or decrementing specified memory locations.

1.5.1.2 Single-Bit Control and Sense System. The single-bit control and sense system issues instructions to all external devices and tests conditions in these external devices. When the computer sends an instruction for execution, a 1.4-microsecond pulse indicates to the device specified by the address portion of the instruction that the computer is requesting a specific operation. This signal is 0 volts for binary zero and +8 volts for a binary one.

When the computer sends an instruction requesting a test for a condition in an external device, a line goes true until that condition response is strobed to the computer. If the signal specified by the address portion of the test instruction is not true, the computer skips the next instruction in sequence. If the signal is true, the computer executes that next instruction in sequence. The computer can perform logical operations based on the presence or absence of the tested signals.

1.5.2 TIME-MULTIPLEXED COMMUNICATION CHANNELS. In addition to the 'word-parallel system, the 940 Computer includes one Time-Multiplexed Communication Channel (W) as standard equipment, as well as provision for three additional channels (Y, C, and D). These channels are capable of automatically controlling the flow of data to and from memory at rates up to 286,000 words per second. Independent channel operation only interferes with computer operation for data transfer between the Time-Multiplexed Communication Channel and memory.

Time-Multiplexed Communication Channels use central processor memory logic to facilitate the input and output of data words. The transfer of each word between the channel buffer and the memory requires two memory cycles. During this transfer time, computation is held up in the central processor. Priority for use of the TMCC input/output logic is in the order: Channel D, C, Y, and W. Any channel operating with interlace has priority over the central processor for memory access. Words can be transmitted between memory and peripheral devices under the

direct control of single instructions. A WIM instruction causes a word transmitted from a peripheral device to be taken from the channel buffer register (W) and placed into a specified memory location (M). A MIW instruction causes a word to be taken from a specified memory location (M) and placed into the channel buffer register (W) for output to the peripheral device currently connected to the channel. Both WIM and MIW instructions are preceded by instructions that set up the input or output operation. The transfer of data is done at the rate that either the WIM instruction for input or the MIW instruction for output can be executed which depends on the peripheral device connected to the channel.

1.5.3 DIRECT MEMORY ACCESS SYSTEM. A direct memory access system is also incorporated in the 940 Computer. This system uses a Multiple Access to Memory unit to provide a path to memory separate from that used by the central processor. Because of the separate access to memory, data transfer through the direct memory access system does not interfere with the central processor unless both are trying to use the same memory module at the same time.

The direct memory access system provides direct transmission between special-purpose peripheral devices and the computer core memory. Devices controlled and sequenced externally can present data and addresses to the direct access connections. Thus, input/output operations can be completely independent of the computer. The special input/output devices present an address plus various timing and control signals to the direct access connection. External data can be stored in any specified location or read from any location specified by the external unit.

Two methods of data handling depending on speed are used in conjunction with the direct memory access system. Individual sources are handled by the Direct Access Communication Channels. Multiple, relatively slow sources are handled by the Data Multiplexing System. Each of the data handling methods are described in the paragraphs that follow.

1.5.3.1 Direct Access Communication Channels. Four Direct Access Communication Channels can be attached to the direct memory access system. Although these channels operate in exactly the same manner as the Time-Multiplexed Communication Channels, they are faster and provide for a true input/output overlap with processing. These channels automatically control the flow of data to and from memory at rates equivalent to 572,000 words per second.

Each Direct Access Communication Channel has memory logic independent of the Central Processor. When memory access is needed to access or store a data word, computation is held up for one cycle if the access is in the same module that the central processor is addressing. If the module is not currently being addressed by the central processor, no time is lost and computation is unaffected. Thus, internal computation and direct access transmissions occur simultaneously and independently when the computer and the channel are accessing different memory modules.

Transmissions to and from core memory are under control of the Direct Access Communication Channel. At the beginning of each memory cycle, the control unit interrogates all channels to determine whether any channel requires a transfer to or from computer memory. Interrogations are performed in such a manner that each channel has priority on the basis of need. Channel control logic permits the transfer of only one word per memory cycle to and from the computer memory, regardless of the number of operating channels that are connected to the computer. 1.5.3.2 Data Multiplexing System. To transmit data directly to and from memory, a Data Multiplexing System has been developed. This system is of particular value in dealing with multiplexed sources of data each of which is slow relative to the maximum memory rate, or for systems which have very high data rates. The data multiplexing system uses the Multiple Access to Memory, which is completely under the control of attached units. The structure of the system permits the connection of unlimited Memory Interface Connections, and a Data Multiplex Channel that can operate with up to 64 Data Subchannels. Priorities can be individually assigned to each Data Subchannel or Memory Interface Connections.

Either internal or external interlace can be used. If internal interlace is used, two interlace words, memory location and word count, are stored in memory and accessed each time a given subchannel transmits information. If external interlace is used, the identical information is held in an external register. Maximum information transfer rate is one word every 5.25 microseconds with internal interlace; the transfer rate is increased to one word every 1.75 microseconds with external interlace.

Internal interlace allows a Data Subchannel to handle continuous data by alternately working from one memory area to another. Since the Data Subchannel can switch automatically from one interlace word to the other, the program is relieved of the necessity of making real-time responses to the zero-count condition.

The external interlace is attached to a Data Subchannel and comprises a 16-bit address register and an 8-bit count register. These registers are loaded automatically from the internal interlace memory locations when the Data Subchannel is activated. After each word is transmitted, the external interlace increments the address register and decrements the count register. When the count equals zero, the Data Subchannel can generate a program interrupt or notify the external device.

Two types of Data Subchannels are available. One Data Subchannel provides multiple input/ output channels for standard SDS peripheral equipment and contains a character assembly/ disassembly register that operates on either one or two 6-bit characters or directly on 12-bit words. The other Data Subchannel accepts only 24-bit information, has no internal storage, and operates on high-speed data. The transmitting and receiving devices provide the necessary storage.

1.5.4 PRIORITY INTERRUPT SYSTEM. For operation under real-time conditions, a priority interrupt system provides greater program control of input/output operations, aids in programming input/output and computer operations simultaneously, and permits immediate recognition and reaction to special external conditions. In addition to the interrupts provided with the input/output channels and power fail-safe option, the 940 Computer can have as many as 896 optional priority interrupts. The system can be enabled or disabled, and individual interrupts can be armed or disarmed as described in the following paragraphs.

Enable/disable functions operate on the entire interrupt system, except for the power fail-safe interrupts that are always enabled and armed. If one or more interrupts occur while the interrupt system is disabled, and the system is subsequently enabled, each of the interrupts is processed in accordance with its priority.

An optional arm/disarm feature permits any chosen interrupt to be individually armed or disarmed. The disarmed condition causes a priority interrupt to retain no record of the arrival of a stimulus, while the disabled condition records all stimuli for later processing.

Each armed interrupt channel can assume three states: inactive, when no interrupt has been received; waiting, with an interrupt received but not being processed; and active, when a received interrupt is being processed. The arm/disarm feature controls whether an interrupt can proceed from the inactive state to the waiting state.

The waiting condition exists

- (a) If the computer is processing a higher priority interrupt,

- (b) If the computer is executing an instruction when the interrupt stimulus arrives,

- (c) If the interrupt system has been disabled.

In all cases, the waiting status of the channel is maintained until the interrupt can be processed.

While in the active state, each interrupt rejects new stimuli. Consequently, if a signal is presented to an interrupt while the computer is processing that interrupt, a jump does not occur. Since each interrupt has a defined purpose, the interrupt in progress should be handling the interrupt situations and no new action should be necessary until after the interrupt has been processed. Thus, the computer ignores the stimulus, regardless of its duration or frequency, until the active status is terminated.

If an interrupt of higher priority occurs while a given interrupt is being processed, that interrupt remains in the active state, but the program jumps to the higher-priority location. After processing the higher interrupt, the program returns to the initial interrupt, unless still another interrupt with higher priority is in waiting status.

Three sources of interrupt are used in the 940 Computer; External, Input/Output Channel, and Real-Time Clock. Each of these interrupt signal types is described in the paragraphs that follow.

1.5.4.1 External Interrupt. Each interrupt, when activated, sends the computer program to a unique memory location. The computer does not evaluate the external stimulus; rather, the computer proceeds automatically to the beginning instruction of a unique response subroutine designed for that particular interrupt. This type of interrupt is referred to as a subroutine priority interrupt to differentiate the operation from another interrupt known as a single instruction priority interrupt. In a single instruction priority interrupt, the memory location contains a single-instruction subroutine; after this instruction has been executed, the computer returns to the program unless a higher priority interrupt has been activated. Any interrupt for a particular system can be single-instruction or subroutine. 1.5.4.2 Input/Output Channel. The Time-Multiplexed Communication Channels and the Direct Access Communication Channels are capable of generating interrupts. Each Time-Multiplexed Communication Channel is normally capable of generating two interrupts for the computer while operating in the compatible mode. The end-of-word interrupt occurs at the end of each word transferred from the channel buffer to the peripheral device on output, or when the channel buffer is filled with data from the peripheral device on input. The end-of-transmission interrupt occurs when the peripheral device disconnects. In the extended mode four separate terminal functions can be programmed. Since these interrupts can be selectively armed and disarmed, the program specifies when and if these interrupts occur. The Direct Access Communication Channels always operate in the extended mode as just described. Refer to the applicable technical manuals for the details of the interrupt capabilities of the Time-Multiplexed Communication Channel and the Direct Access Communication Channel. Refer to the reference manual for details of programming in the compatible and extended modes.

1.5.4.3 Real-Time Clock. The Real-Time Clock (RTC) provides a flexible time-orientation system for the 940 Computer. Timing pulses are derived from the 60 Hertz computer power supply. These pulses are then used to produce a timing mark every 16.67 milliseconds (or, optionally, every 8.33 milliseconds). The RTC can also accept timing marks from a customer-designed source, thereby allowing time measurement to any required resolution for special applications. These timing marks are supplied at standard SDS logic levels to the RTC circuitry. The timing marks provide the computer by means of interrupt programming with either an elapsed-time counter or a continuously incrementing time counter depending upon customer needs.

#### 1.6 INPUT/OUTPUT DEVICES

An extensive group of peripheral devices is available for use with the 940 Computer. Input/ output devices communicate with the computer either directly or through buffers. The following paragraphs describe the two methods of input/output and the devices handled by both.

1.6.1 BUFFERED INPUT/OUTPUT DEVICES. The speed and flexibility of the 940 Computer buffered input/output ensures the efficient use of all types of peripheral equipment. Buffered peripheral devices include magnetic tape units, keyboard/printers, line printers, card readers and punches, paper tape readers and punches, and auxiliary memory discs as shown in Figure 1-5. Analog/digital conversion equipment and other special system equipment can be added by means of the Data Multiplex System. Since no additional buffering is required for these devices, expansion is quickly and easily performed in the field.

The various input/output devices that are available for the 940 Computer buffered input/output are presented in Table 1-2.

Figure 1-5. Buffered Input/Output

1

| Equipment                                                  | Features                                                                                                                                                                                                                                             |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input/Output Typewriter                                    | 15 characters per second; 11– or 15–inch carriage                                                                                                                                                                                                    |

| Keyboard/Printers and<br>Low-Speed Paper Tape<br>Equipment | 10-characters-per-second Teletype input/output<br>units can include 10-character-per-second tape<br>punch and reader                                                                                                                                 |

| High-Speed Paper Tape<br>Equipment                         | 300-character-per-second reader; 60-characters-<br>per-second punch; 8-inch NAB reel spooler. Cart-<br>mounting available                                                                                                                            |

| Magnetic Tape Systems                                      | 7 and 9 tracks; BCD or binary (all compatible with<br>IBM 729 recording mode); 200, 556, and 800-bits<br>per inch recording densities; 60, 75, or 120-inches<br>per second tape velocities; 12,000 to 96,000<br>characters per second transfer rates |

| Magpak System                                              | Low-cost, compact magnetic tape system; 4<br>independent information channels; 6 million<br>character total storage capacity; 1,500 character<br>per second transfer rate                                                                            |

| Line Printers                                              | 140 to 2, 400 line per minute speeds; 12 to 132<br>print positions, 10, 56 and 64 character sets                                                                                                                                                     |

| Card Equipment                                             | 400 and 800 cpm readers; 100 and 300 cpm punches                                                                                                                                                                                                     |

| Mass Random Storage                                        | 524, 288 to 8, 388, 608 character rapid-access<br>devices; 8.3 to 67.1 million character mass memory<br>disc files                                                                                                                                   |

| Graph Plotter                                              | Digital incremental drum plotter; 300 increments per second with 0.01-inch increments                                                                                                                                                                |

| Other Units                                                | Oscilloscope display system                                                                                                                                                                                                                          |

Table 1-2. Buffered Input/Output Equipment

1.6.2 UNBUFFERED INPUT/OUTPUT DEVICES. Unbuffered input/output communications systems are based on the use of two basic units; the asynchronous communications controller and the full-duplex line group. This capability is shown in a typical 940 Configuration in Figure 1-6. The teletype communications system provided with the SDS 940 System permits the transfer of 11-unit, 8-level, 100-words-per-minute teletype information between the 940 Computer and standard Teletype Model 35 KSR or Model 35 ASR units. In addition, an automatic calling unit coupler can be used as described in the Asynchronous Communications Equipment Technical Manual (SDS Publication Number 980111A). This coupler also interfaces with the parallel output and parallel input lines from the computer and uses one level of priority interrupt.

Figure 1-6. Unbuffered Input/Output

.\*

When operating with a full complement of 16 line groups, each controller provides full-duplex capability for 64 teletype lines. All lines can be simultaneously engaged in two-way transmission on a completely asynchronous basis. Multiple sets of such configurations can be tied together to form a communications system of any size. The interface of the communications system thus generated, operates through the word parallel system of the computer and uses four interrupt locations with the operation of a fifth location which is end-of-message interrupt.

The number of users simultaneously communicating with the system in synchronism establishes the operating limit. The computer must remove a character from any input buffer before information bits of the next character arrive. For 11-unit, 8-level code, this interval is 27 milliseconds. Assuming that this interval is treated as only 18 milliseconds, the processing time for a character is approximately 300 microseconds. Thus, 60 lines, all practically in exact synchronism, would constitute a worst-case condition beyond which the computer would lose information. Note that in the above example the actual processing time for the 60 characters from 60 separate lines is only 18 milliseconds out of every 100 milliseconds or 18 percent of the processor time, and that rate overruns could only occur if all 60 lines are simultaneously inputting in almost perfect synchronism. These considerations demonstrate that the communication processing limitations do not set the limit on the number of users who can simultaneously use the system. Even with many users, only a small percentage are simultaneously inputting; and they are probably not synchronized with each other. For example, message processing for 32 users is estimated to use about 5 percent of the available computer time.

#### II. OPERATION AND PROGRAMMING

#### 2.1 GENERAL

In a time-sharing computer, as in any general purpose computer, programs contain the complete sequence of instructions necessary to perform functions or to solve problems. After the operator loads the required programs, sets up the computer, and starts operation, the operation is under control of the stored programs. In this respect, the 940 Computer is almost identical with the 930 Computer. The 940 Computer, however, offers another operation dimension. Any one of a group of remote users can execute instructions in the computer. The 940 Time-Sharing System contains additional hardware/software features that make the computer capability apparently available to each user while preserving the privacy of each user. However, the apparent computer used by the remote users is vastly different from the actual hardware configuration. The reason for this difference is presented in the following paragraphs.

Every multi-programming computer system must provide isolation between independently operating programs because such programs may overwrite each other with data, transfer control to each other, attempt to use the same input/output devices, halt, or otherwise hang up the computer. Isolation problems are usually solved by memory protection, input/output and illegal instruction detection, and system controlled input/output operation. Relocation of program areas and allocation of storage among the concurrent programs become a problem when main memory cannot contain all of the concurrent programs and programs must be moved to and from secondary storage. The mapping feature provides a method for relocation and allocation and also provides memory protection.

In order to insure isolation of user programs, two modes of operation are provided; a user's mode or a systems or monitor mode. The user mode restricts the user to a subset of the 930 Computer instructions. Because both operation modes require changes in programming conventions from the 930 Computer, a third mode called normal or 930 mode is used for normal operation. The normal mode is not used when operating in a time-sharing environment. In the time-sharing environment, a software system, the Executive/Monitor, has complete control over the system.

Only one user can be executing commands at any given instant in time. The Executive/Monitor program activates a user, allows execution of commands for some period, dismisses the user, and activates another user. A user's program runs in the user mode. An input/output operation request produces a mode change to the monitor mode to permit the Executive/Monitor to execute the input/output operation since all input/output operations are done in the monitor mode by the Executive/Monitor program. All interrupts are also processed in the monitor mode. An attempted illegal operation results in a trap condition which in turn results in a transition to monitor mode in which the Executive/Monitor program takes control to perform the necessary action.

Since the scope of this manual does not permit a description of the time-sharing software system, this section describes the instructions added to the 930 Computer that permit computer environment control by time-sharing software. Likewise, the detailed theory of operation section that follows this section only attempts to describe the hardware associated with these added features. Very few changes have been made to the 930 Computer set of operation codes. With the exception of improved interrupt routine exit and alternate overflow indicator instructions, all instruction changes are associated with the new features; namely, mode changing instructions and the memory map instructions. Numerous logic changes to the 930 Computer exist at the hardware level, even though the changes are not discernible at the operational level. A detailed description of the logic changes is given in Section III of this manual.

Because the 940 Computer is an extension of the 930 Computer, this operation and programming section is limited to a description of mode changes, modes of operation peculiar to the 940 Computer, addressing changes, memory operation modes, available software, and the lists of operation codes and machine instructions.

### 2.2 CHANGING OPERATION MODES

Initial operation of the START button on the console control panel forces the machine into the normal mode. A program instruction is required to change from normal to monitor mode. No program or manual method can effect a direct transition from normal mode to user mode. Once the monitor mode is entered, the program controls the transition to the user mode. The transition from monitor mode to user mode is made by executing a branch instruction to a user mapped location (any branch instruction in which user relabeling is invoked). The transition from user to monitor mode is made by executing a System Programmed Operator (SYSPOP) instruction. Because no programmed controlled method for transition from monitor or user mode to the normal mode.

Two situations occurring in the computer logic will also cause mode transition. First, the occurrence of an interrupt or trap when in user mode will cause a transition to monitor mode. Second, following the execution of a single instruction interrupt routine, a transition to user mode will occur if the machine was in user mode at the time that the interrupt occurred.

#### 2.3 MODES OF OPERATION

This section contains a detailed description of the 940 Computer modes of operation. As indicated previously, the modes are designated normal mode, monitor mode, and user mode. Each of the three operation modes are discussed individually in the paragraphs that follow.

2.3.1 NORMAL MODE. When the START switch is operated, the computer logic automatically enters the normal mode. In the normal mode of operation, the 940 Computer operations are almost identical to those of the 930 Computer. In the normal mode, the 940 Computer is compatible with the 930 Computer software.

The 940 Computer operation in the normal mode is different from the normal 930 Computer operation in four ways. None of these differences effect the operation of the standard 930 Computer software. The four differences include three new instructions and a word modification.

2.3.1.1 Interrupt Routine Return Instruction. A new instruction named Branch and Return from Interrupt Routine (designated by the mnemonic BRI) has been added and is operative in both the normal and monitor mode. The instruction utilizes operation code 11 that is normally undefined in the 930 Computer. The description of the execution of this instruction is presented in the discussion of the monitor mode in Paragraph 2.3.3.5.

2.3.1.2 Overflow Instructions. A new set of instructions to control the operation of the overflow indicator has also been added to the 940 Computer. The overflow indicator detects erroneous arithmetic operations that occur during the execution of a program. The instructions utilize operation code 22, a normally undefined operation code in the 930 Computer. The four new overflow instructions are defined as indicated in Table 2-1.

| Mnemonic | Octal Representation | Full Name                         |

|----------|----------------------|-----------------------------------|

| OVT      | 0 22 00101           | Overflow Indicator Test and Reset |

| REO      | 0 22 00010           | Record Exponent Overflow          |

| ROV      | 0 22 00001           | Reset Overflow Indicator          |

| ото      | 0 22 00100           | Overflow Indicator Test Only      |

Table 2-1. Overflow Instructions

The function of the first three of these instructions is identical to that of the instruction of the same name in the 930 Computer. In the 930 Computer, OVT (0 40 20001) is an SKS instruction, and REO (0 02 20010) and ROV (0 02 20001) are EOM instructions. In the 940 Computer, these instructions are still operative. Thus, two different methods are provided in the 940 Computer for invoking the execution of the same operation. The OTO instruction functions in the same fashion as the OVT instruction except that the state of the overflow indicator is not modified.

2.3.1.3 Mode Change Instruction. A new instruction has been added to provide a program controlled transition from the normal mode to the monitor mode. The new instruction uses the 02 operation code designated EOM (Energize Output M). The octal form of this new instruction is 0 02 22000.

2.3.1.4 Data Multiplex Channel Interlace Word. The format of the interlace word for the Data Multiplex Channel is different from that of the Data Multiplex Channel interlace word in the 930 Computer. The word count field of the new word contains only eight bits to permit a maximum record size of only 256 words. This word size enables the data address field to contain sixteen bits and permit addressing a 65,536-word memory.

2.3.2 MONITOR AND USER MODE, COMMON OPERATIONS. Several operations are available in both monitor and user modes, but not available in the normal mode. These common operations are described in the following paragraphs.

2.3.2.1 Hang-up Prevention. An Execute instruction (EXU), or a long chain of Execute instructions, is aborted in response to an interrupt request. The interruption assures that interrupt request acknowledgement is not excessively delayed because of a long chain or infinite loop of Execute instructions. This process is effected by terminating the Execute instruction and initiating the execution of a No Operation (NOP) instruction. The highest priority interrupt request is acknowledged, and the Program Counter contains the address of the aborted instruction. Incrementing of the Program Counter was inhibited during the No Operation (NOP) instruction. The normal interrupt routine exit will return to the interrupted instruction that will be restarted. This feature is effective only when mapping through the user map.

Similarly, execution of an instruction involving indirect addressing is interrupted when an interrupt request occurs during the indirect addressing phase of the instruction execution. Also, an interrupt request at the completion of an Increment Index and Branch Instruction (BRX) which calls for a jump is acknowledged. In this case, the Program Counter contains the location specified by the jump. This feature is effective only when mapping through the user map.

2.3.2.2 User Map. A memory mapping technique provides dynamic relocation of programs and fragmentation of memory. In the monitor mode the user map is enabled by individual instructions. The user map converts program addresses to memory addresses. For instance, addresses within the virtual machine in which the user's program is assuming operation are converted to actual physical core memory locations occupied by the user's program and data.

The memory is considered to be divided into 32 pages containing 2048 words each. When mapping occurs, memory is accessed under control of a 5-bit page number and an 11-bit address that specifies a location within the 2048-word page. The upper three bits of a program address constitute the page number. Mapping hardware replaces the user's page number with a physical page number, which may be different from time to time as the program is moved in and out of memory. The users program is not aware of the page structure of the memory. Thus, mapping hardware permits memory fragmentation by allowing user's storage to be located in noncontiguous blocks, that appear to the user and to the machine to be contiguous. The 14 bits of the address field permit only 16,384 words or eight pages to be directly addressable by any user at any one time.

2.3.2.3 Unauthorized Memory Access Protection. The user map provides protection against unauthorized memory accesses. Protection against any access to a 2048 word page of memory is effected by not placing the high order bits associated with the given page in any one of the eight mapping registers. To prevent a running program of fewer than eight pages from accessing a page outside its addressing range, those mapping registers associated with unused and therefore prohibited pages are loaded with an octal 40. If an attempt is made to reference a memory location having an address pointing to a relabeling register with this content, a trap to location 418 will result. The term trap is to be distinguished from the interrupt defined by SDS. The trap is a forced transfer to a fixed location; hence a trap routine is interruptible by any other interrupt or trap condition.

At the occurrence of the trap, the Program Counter contains the location of the offending instruction. If the instruction attempted a jump to an out-of-bounds location, the Program Counter contents depend on the status of the address. The notation L : INS A is used for the following information in which L equals the location of instruction, INS is the instruction, A equals the effective address of the instruction before mapping, and P equals the contents of the Program Counter.

L: BRM A 1. A illegal, (P) = L 2. A legal but A + 1 illegal, (P) = A + 1 L: BRR A 1. A illegal, (P) = L 2. (A) + 1 illegal, (P) = (A) + 1 L: POP (P) = L L: BRU A (P) = A L: BRX A (P) = A L: BRI A 1. A illegal, (P) = L 2. (A) illegal, (P) = (A)

An intermediate level of memory protection is afforded by the flag bits. Reading and writing in any assigned block of memory is permitted if the associated flag equals zero. If the flag equals one, and the register contains something other than 40g, the associated block is read-only. An attempt to store information in a read-only block results in a No Operation (NOP) and a trap to location 43g. The Program Counter contains the information indicated previously when a jump to an out-of-bounds location was attempted.

2.3.2.4 Modified Unconditional Branch Instruction. The interrupt termination function of the Unconditional Branch Instruction (BRU) is inhibited in both the monitor and user mode.

2.3.2.5 Overflow Instructions. The group of overflow instructions using the operation code 22 are effective in all operation modes. These instructions are described in Paragraph 2.3.1.2.

2.3.3 MONITOR MODE. The several operations unique to monitor mode are described in the following paragraphs.

2.3.3.1 Exclusive Use of User Map. Mapping through the user map becomes effective when the sign bit of the instruction being executed is detected as a one. The machine will invoke the user map for the duration of this instruction. Thus, if the sign bit of a word fetched during indirect addressing is equal to one, all further memory references made by this instruction will be mapped through the user map. 2.3.3.2 Monitor Map. In the monitor mode, if the sign bit of the instruction is zero, the address is mapped through the monitor map. Monitor mapping is one-to-one for all addresses in the range 0 through 300008-1. Monitor program addresses in this range always result in equivalent core addresses in this range. For addresses in the range 300008 through 340008-1, monitor mapping is through the 5 bits contained in M6. For addresses in the range 340008 through 377778, monitor mapping is through the 5 bits contained in M7. The only access limitation imposed by the monitor map in that physical locations 0 through 37778 cannot be accessed using M6 or M7. A zero value in M6 or M7 is reserved to denote an out-of-bounds condition in the same manner as the 408 is used in the user map.

In the actual implementation, the sign bit of the instruction is inspected to determine whether or not to go through the user map. If this bit is a zero and the user map is not required, the three high order bits of the address are inspected to see if they contain the values 110 or 111. If they do not, the address is used without mapping. If they contain 110, the five bits of M6 are concatenated with the remaining low order eleven bits of the address to obtain the sixteen bit address of the actual location in memory. If they contain 111, the five bits of M7 are used in a similar fashion. The convention used overrides any use of memory extension register EM3 in the monitor mode. However, EM2 could be employed in this mode if desired.

2.3.3.3 Special Monitor Mode EOM Instructions. A special set of Energize Output M (EOM) instructions has been incorporated to enable entry to the monitor mode. In the monitor mode, a monitor program may exercise environment control. These special instructions in the octal configuration and functions are presented in Table 2-2.

| Octal Configuration | Function                                           |

|---------------------|----------------------------------------------------|

| 0 02 20400          | Clear and select RL1 for loading                   |

| 0 02 21000          | Clear and select RL2 for loading                   |

| 0 02 21400          | Clear and select RL4 for loading                   |

| 0 02 22000          | Perform the transition from normal to monitor mode |

| 0 02 22400          | Enable the monitor-to-user transition trap         |

| Table 2–2. Monitor Mode EOM Instructions |

|------------------------------------------|

|------------------------------------------|

All of these EOM instructions may also be executed in the normal mode. The first three instructions in Table 2-2 must be followed by a Parallel Output (POT) instruction. The POT words have the structures shown in Figure 2-1.

Figure 2-1. Parallel Output Map Word Configurations

2.3.3.4 Branch Instruction Return Address Changes. The return address associated with Mark Place and Branch (BRM), Return Branch (BRR), and Programmed Operation (POP) instructions has two changes.

- (a) The overflow indicator is stored in bit two rather than in the sign bit.

- (b) The sign bit is set to one to indicate that the return address is to be mapped through the user map. An example of setting the sign bit to a one is the occurrence of an interrupt when the machine is in user mode. In all other cases, the sign bit is set to zero.

2.3.3.5 Other Instruction Operation Changes. The operation of two other instructions has been changed. The Copy Effective Address into Index Register (EAX) instruction and the Branch and Return from Interrupt Routine (BRI) instructions have been changed as described in the following paragraphs.

In addition to performing all of its normal operations, in the monitor mode, the execution of a Copy Effective Address into Index Register (EAX) will also cause the sign bit to be set to zero if the effective address is not mapped through the user map and set to one if the effective address is so mapped.

The operation code 11 has been designated Branch and Return from Interrupt Routine (BRI) and functions in a manner similar to Return Branch (BRR) instruction, with the following exceptions:

- (a) The return address is not incremented.

- (b) The overflow indicator is first cleared and then set with the contents of bit 2 in the return address word. The BRR operation simply merges the two indicators.

- (c) The highest currently active priority interrupt is terminated.

The BRI instruction is effective in both monitor mode and normal mode.

2.3.3.6 Monitor-to-User Transition Trap. A special monitor-to-user transition trap function has been incorporated. For a definition of the term trap, see Paragraph 2.3.2.3. This trap is enabled by a program operating in the monitor mode with an EOM described in Paragraph 2.3.4. The monitor-to-user transition trap is automatically disabled whenever the trap is entered. The trap is also disabled whenever any other trap occurs. If this trap is enabled, the program will trap to location 448 whenever a monitor-to-user mode transition is attempted.

2.3.4 USER MODE. The two most distinguishing characteristics of user mode are that memory mapping through the user map is always effective, and that several instructions, called privileged instructions, are not available to the user and will cause a trap if their execution is attempted. Another feature unique to the user mode is an extension of the standard programmed operator mechanism. These characteristics are described in the paragraphs that follow.

2.3.4.1 Privileged Instructions. The set of privileged instructions consists of all undefined order codes, Halt, all input/output instructions, all standard EOM instructions (operation code 02), and all standard sense instructions (operation code 40). An attempt to execute a privileged instruction while in user mode results in the execution of a No Operation (NOP) instruction and, subsequently, a trap to location 408. The program counter is not incremented during the execution of the NOP instruction. Consequently, the address stored by the Mark Place and Branch (BRM) instruction in location 408 is that of the offending instruction. A list of the privileged instructions are presented in Table 2-3.

2.3.4.2 System Programmed Operators. Input/output operations are performed by the Time-Sharing Monitor program. Many complex services are performed by the executive program. To provide a method of calling for these services as if they were individual instructions, the System Programmed operators feature enables these instructions to be called. The form of programmed operator instruction used with the time-sharing software is designated SYSPOP; therefore, call instructions for services available in the Executive and Monitor programmed operator instruction (POP) with C0 = 0 and C2 = 1 will cause a transfer to the user mapped location 0. Also in the user mode, execution of a Programmed Operator 0. and C2 = 1 will cause a transfer to the absolute (non-mapped) location designated by C2 through C8 with the

link word being stored in absolute word 0. In addition, a transition from user mode to monitor mode will occur and the sign bit of the return address in absolute word 0 will be set indicating that this address is to be user mapped.