Price: \$12.50

# SIGMA 3 CENTRAL PROCESSOR UNIT (CPU) MODEL 8101/8102 TECHNICAL MANUAL

PRELIMINARY RELEASE

# TO THE CUSTOMER ENGINEER:

| In this attempt to make your job easier by providing you with good, usable documentation, we must have feedback from you to test its validit | у. |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| You can help us in this effort by taking a few minutes to complete the following survey and returning it to us.                              |    |

|   | •                                                 |      |

|---|---------------------------------------------------|------|

| ① | Which of the following terms best descripour job: | ibes |

|   | Systems Engineer Diagnostician Instructor         |      |

|   | Customer Engineer/Field Engineer<br>Trainee       |      |

| he material was: | Yes     | No |

|------------------|---------|----|

|                  |         |    |

| ed               |         |    |

|                  |         |    |

| ted              |         |    |

| ined             |         |    |

|                  | ed<br>I | ed |

| (3) How did you use this manual:        |  |

|-----------------------------------------|--|

| As an introduction to the subject       |  |

| For additional knowledge of the subject |  |

| Maintenance                             |  |

| 4 | If you feel that specific changes should be made, check the appropriate block and cite the changes in the comments section: |

|---|-----------------------------------------------------------------------------------------------------------------------------|

|   | Suggested change (page)                                                                                                     |

|   | Error (page)                                                                                                                |

|   | Suggested addition (page)                                                                                                   |

|   | Suggested deletion (page)                                                                                                   |

| (5) | COMMENTS: (If there is not enough space here for your comments, use the back of this sheet) |

|-----|---------------------------------------------------------------------------------------------|

|     |                                                                                             |

|     |                                                                                             |

|     |                                                                                             |

|     |                                                                                             |

Please complete this survey and return to:

MANAGER, MAINTENANCE AND SELF-STUDY DOCUMENTATION

MAIL STOP C2-16, AIRPORT FREEWAY CENTER 5250 W. CENTURY BOULEVARD LOS ANGELES, CALIFORNIA 90045

# TABLE OF CONTENTS

| ection |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page | Section |       |                                                       | Page |

|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-------|-------------------------------------------------------|------|

|        | INTRO | DDUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | <br> C  | FUNC  | TIONAL DESCRIPTION (Contd)                            |      |

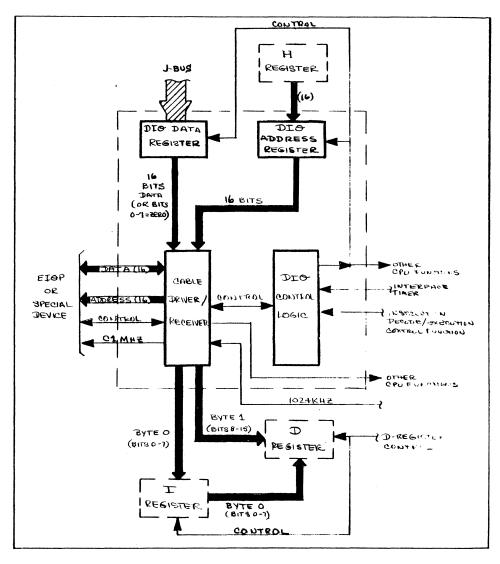

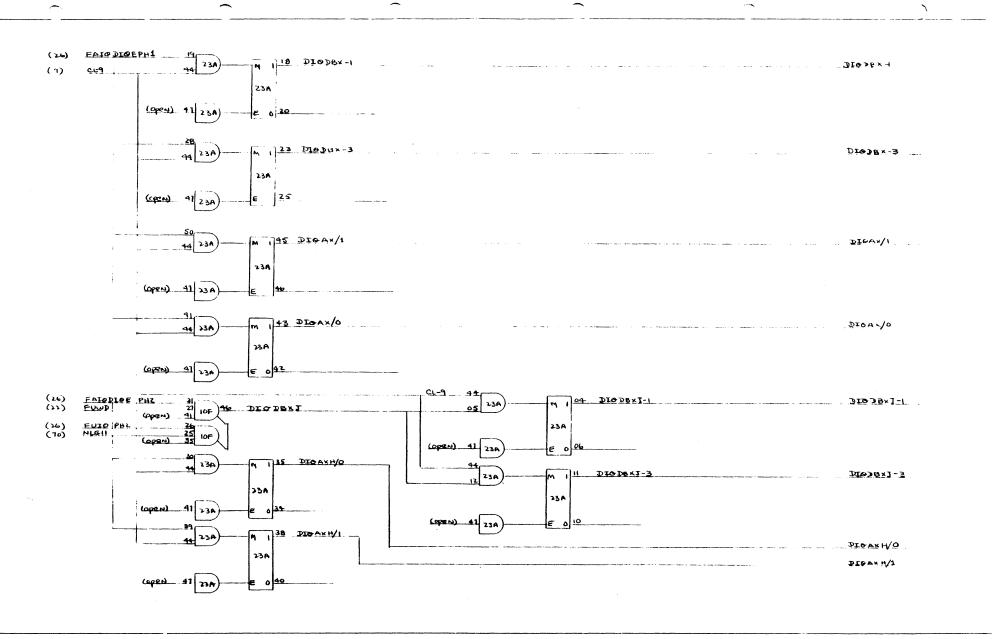

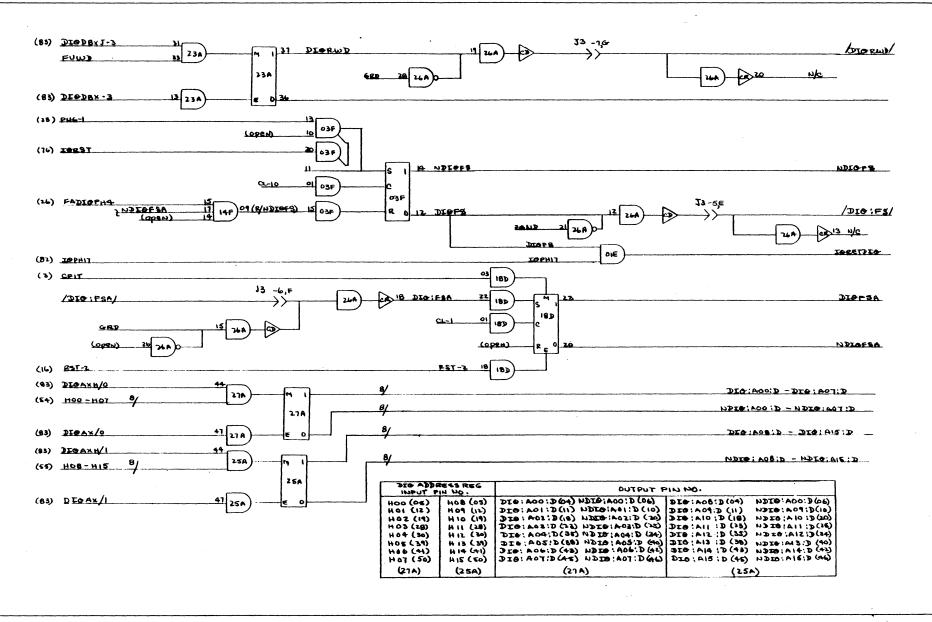

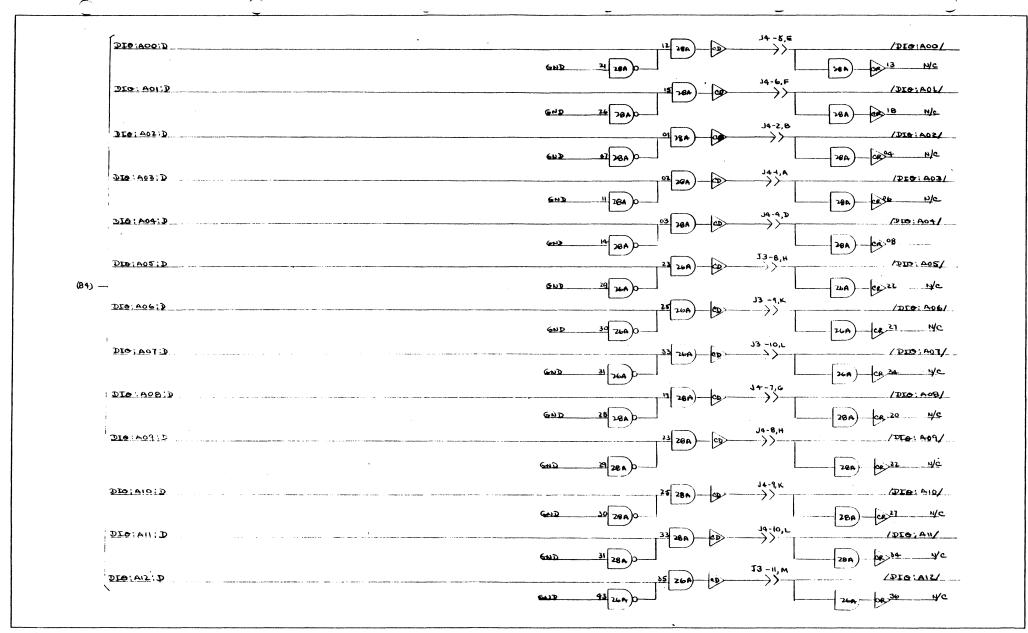

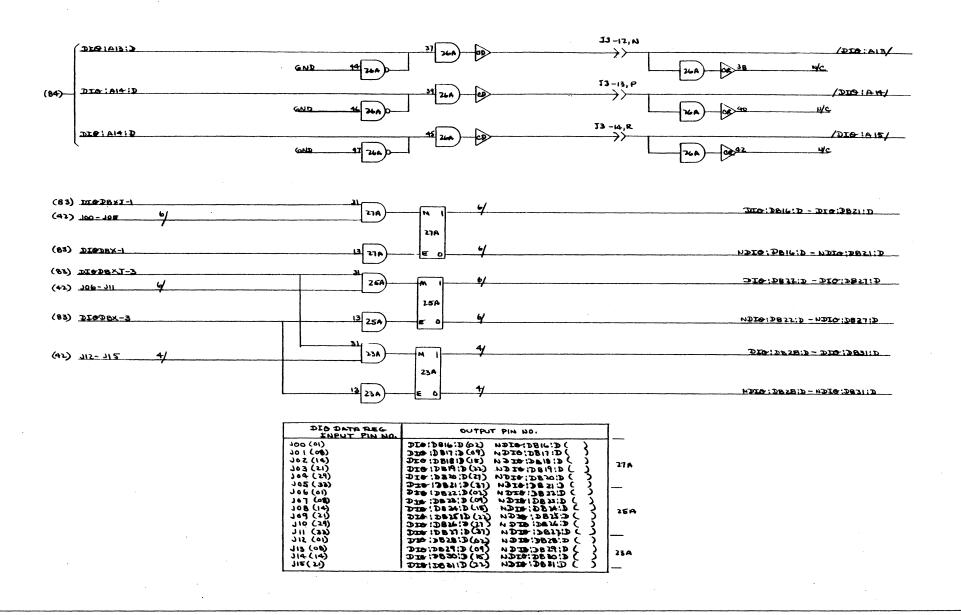

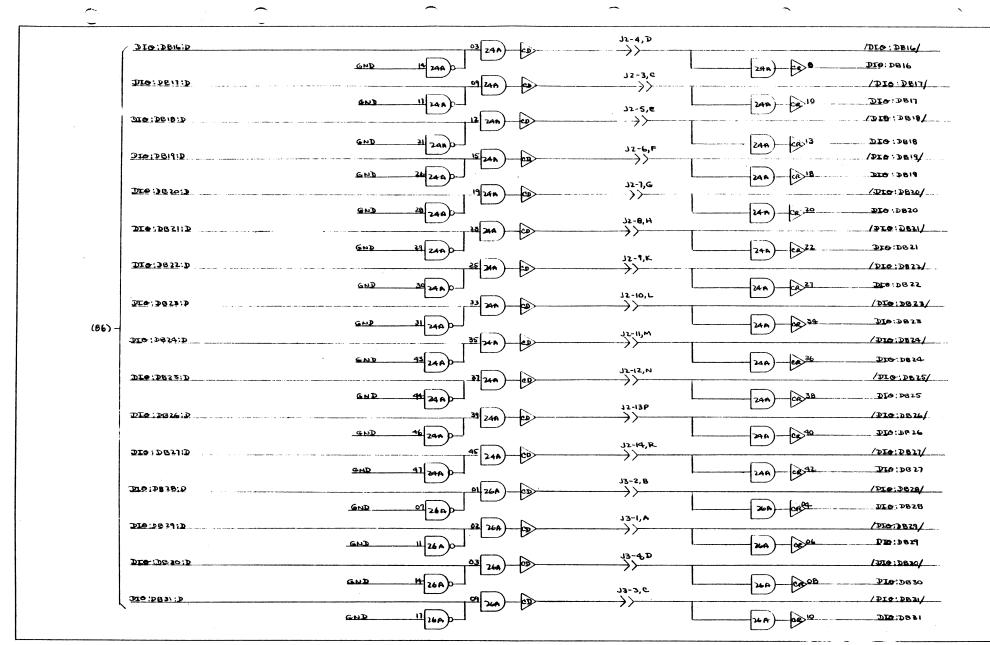

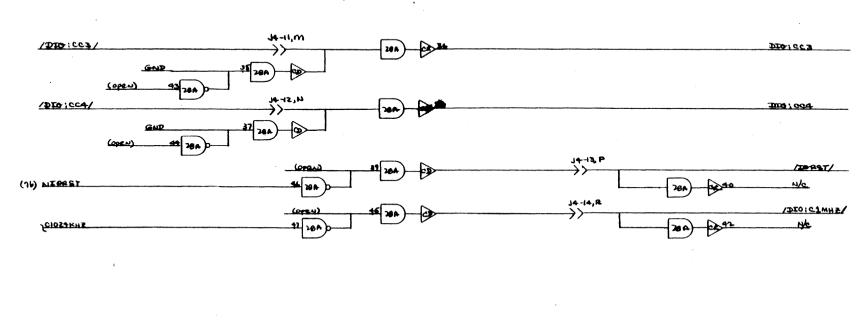

|        | 1-1   | Scope of Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-2  | (Contd) | 2-40  | DIO Interface (CPU Interface Function)                | 2-11 |

|        | 1-2   | Content of Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-2  |         | 2-46  | Adder Function                                        |      |

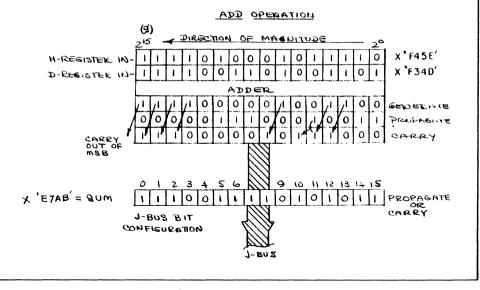

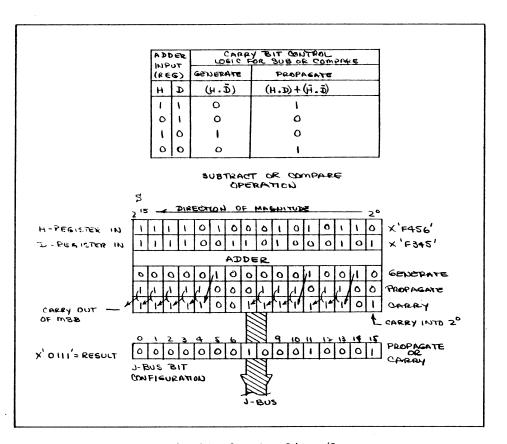

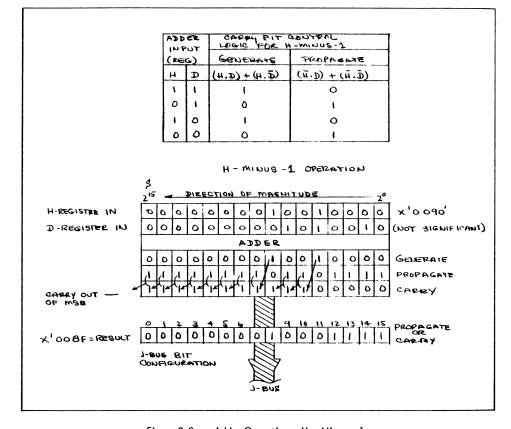

|        | 1-3   | Related Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-2  |         | 2-52  | Adder                                                 |      |

|        | 1-4   | Prerequisites to Manual Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-2  |         | 2-66  | J-Bus Function                                        | 2-16 |

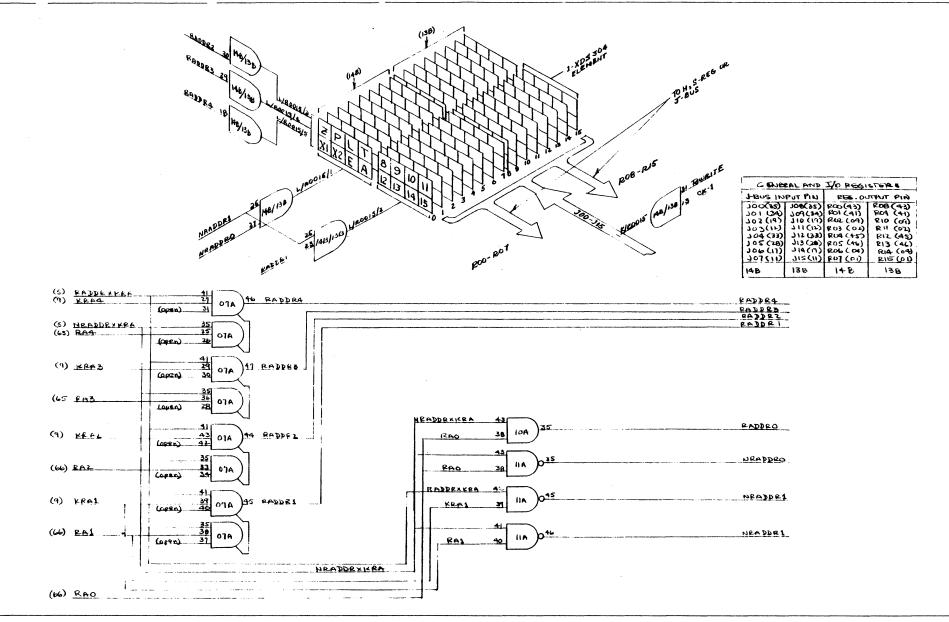

|        | 1-5   | Sigma 3 Central Processor Unit (CPU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-2  |         | 2-67  | J-Bus and Arithmetical Register Group                 | 2-16 |

|        | 1-6   | Physical Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 1       | 2-75  | D-Register (Register Function)                        | 2-10 |

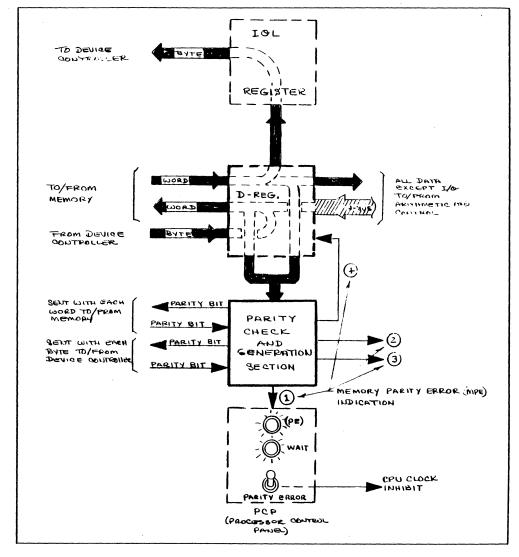

|        | 1-7   | CPU Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-2  |         | 2-85  | Parity Check/Generation Section                       | 2-20 |

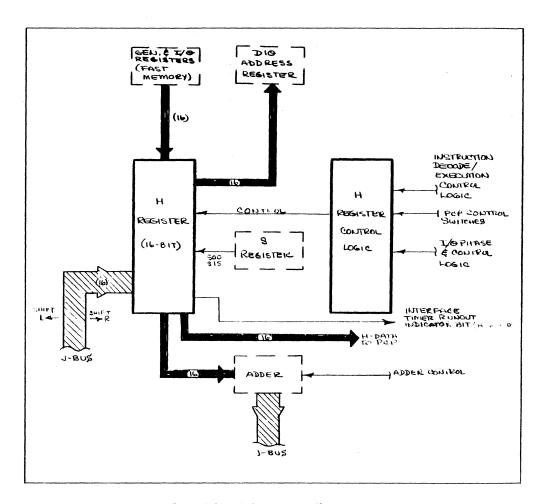

|        | 1-8   | Capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-3  |         | 2-88  | H-Register (Register Function)                        | 2-22 |

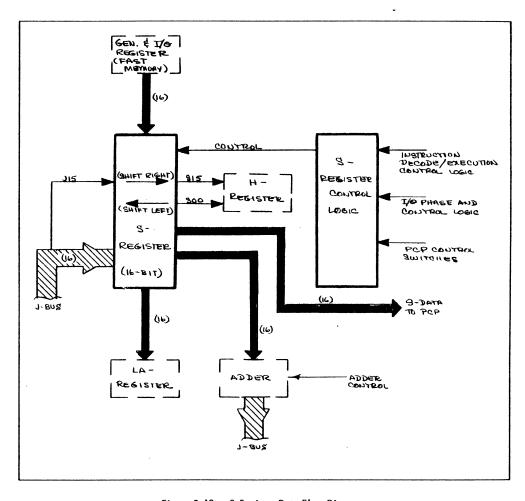

|        | 1-9   | Memory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1_3  |         | 2-96  | S-Register (Register Function)                        | 2-24 |

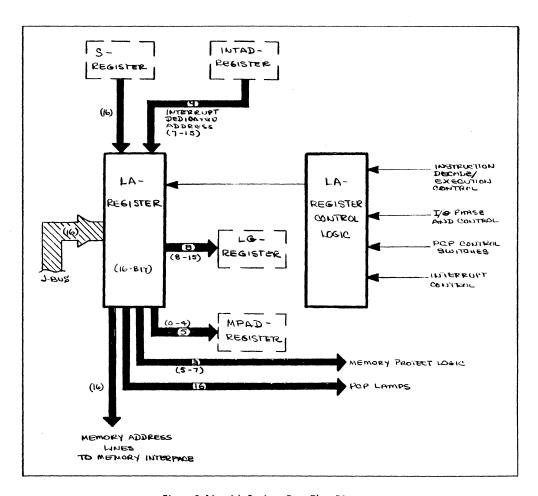

|        | 1-10  | Input/Output Interface (IIOP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-3  |         | 2-103 | LA-Register (Register Function)                       | 2-24 |

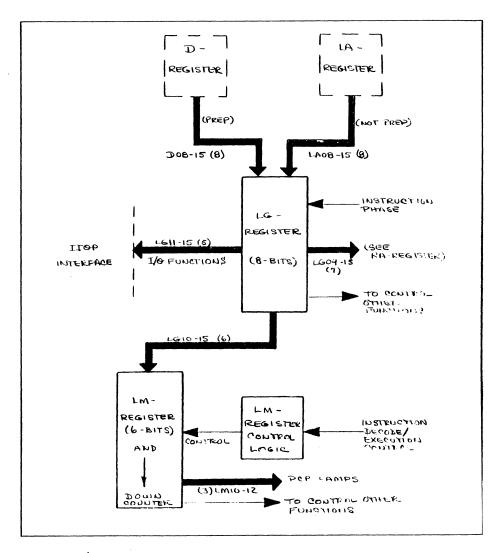

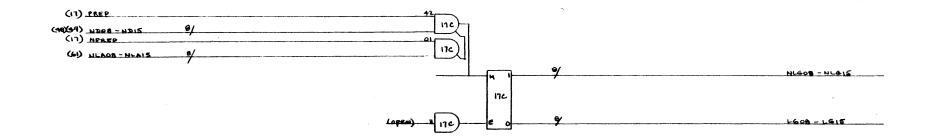

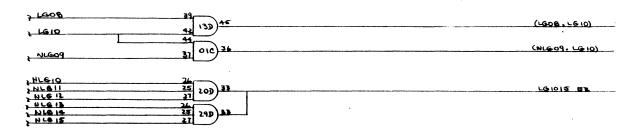

|        | 1-11  | Direct Input/Output Interface (DIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-5  |         | 2-109 | LG and LM-Registers (Register Function)               | 2-26 |

|        | 1-12  | CPU Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-5  |         | 2-110 | LG-Register                                           |      |

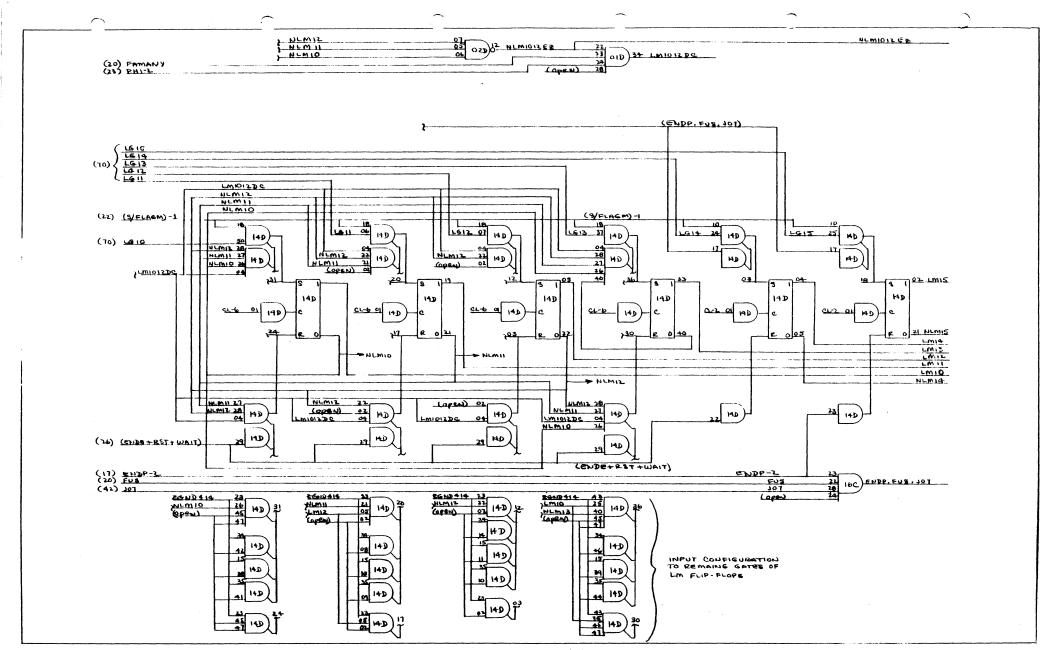

|        | 1-13  | Power Fail-Safe Option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-5  |         | 2-117 | LM-Register                                           |      |

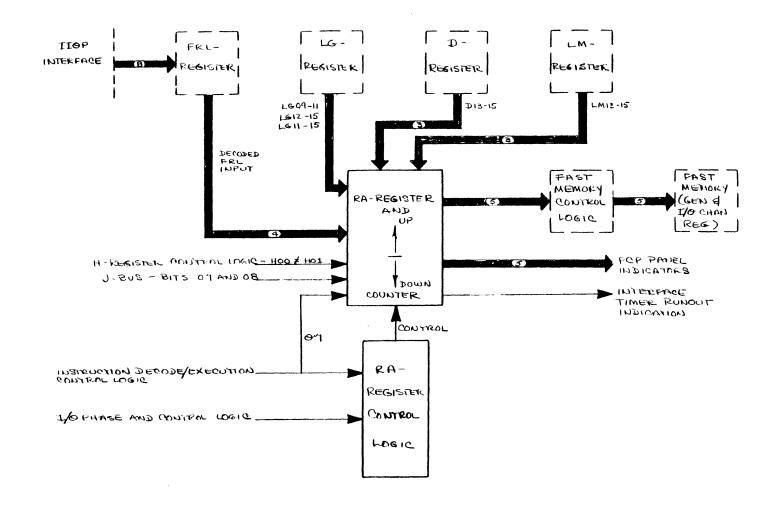

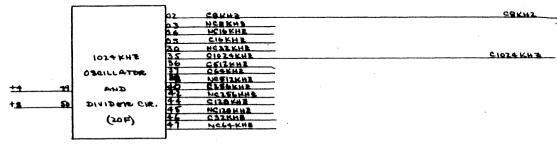

|        | 1-14  | Real-Time Clock Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-5  |         | 2-121 | RA-Register (Register Function)                       | 2-27 |

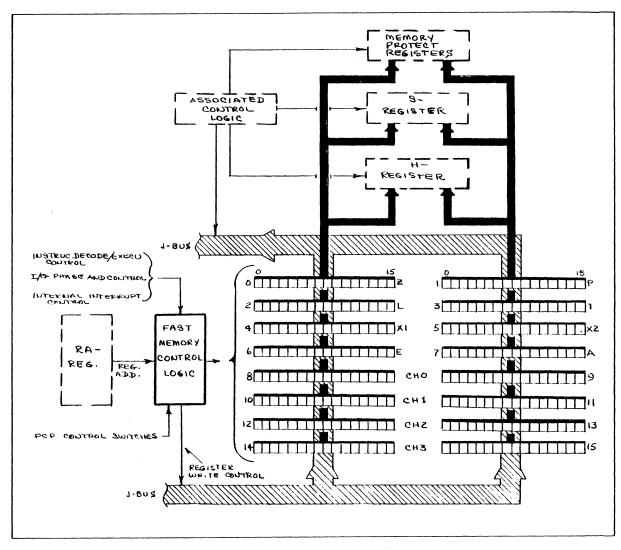

|        | 1-15  | Additional I/O Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-5  |         | 2-131 | General and I/O Channel Registers (Register Function) |      |

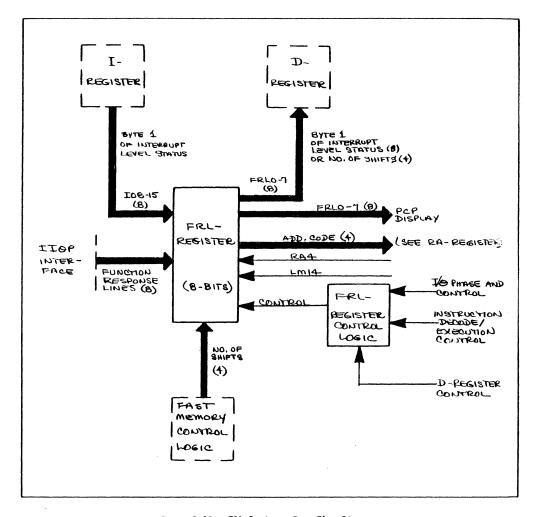

|        | 1-16  | Protect Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-6  |         | 2-137 | FRL-Register (Register Function)                      |      |

|        | 1-17  | Extended Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-6  |         |       | the magnitude (magnitude of other total)              | 2-02 |

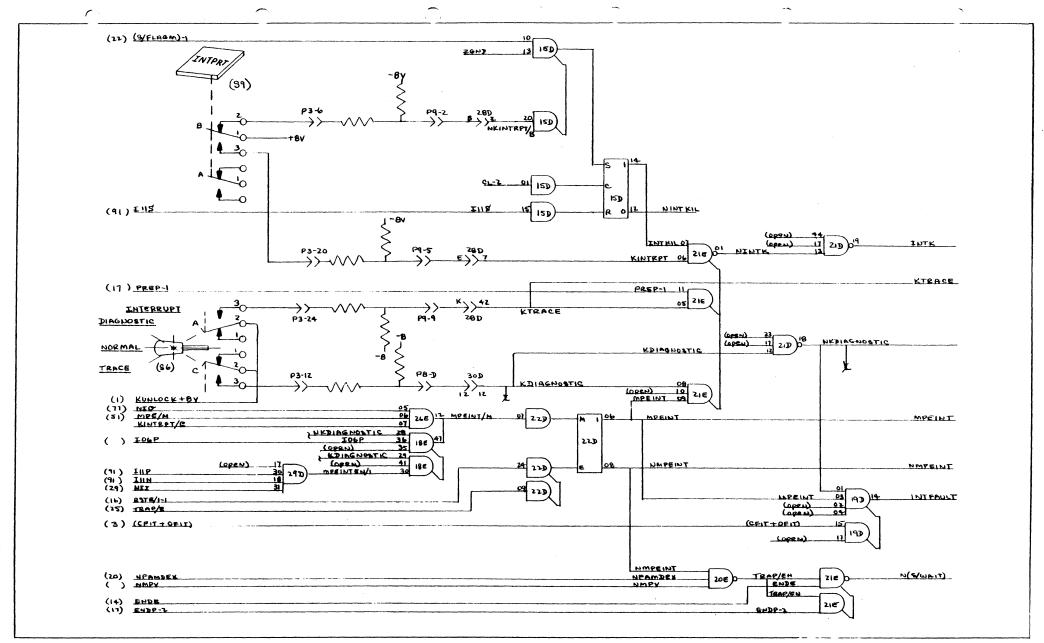

|        | 1-18  | Integral Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-6  |         |       |                                                       |      |

|        | 1-19  | External Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-6  |         |       |                                                       |      |

|        | 1-20  | General Specifications for CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-6  | 111     | DETAI | LED PRINCIPLES OF OPERATION                           |      |

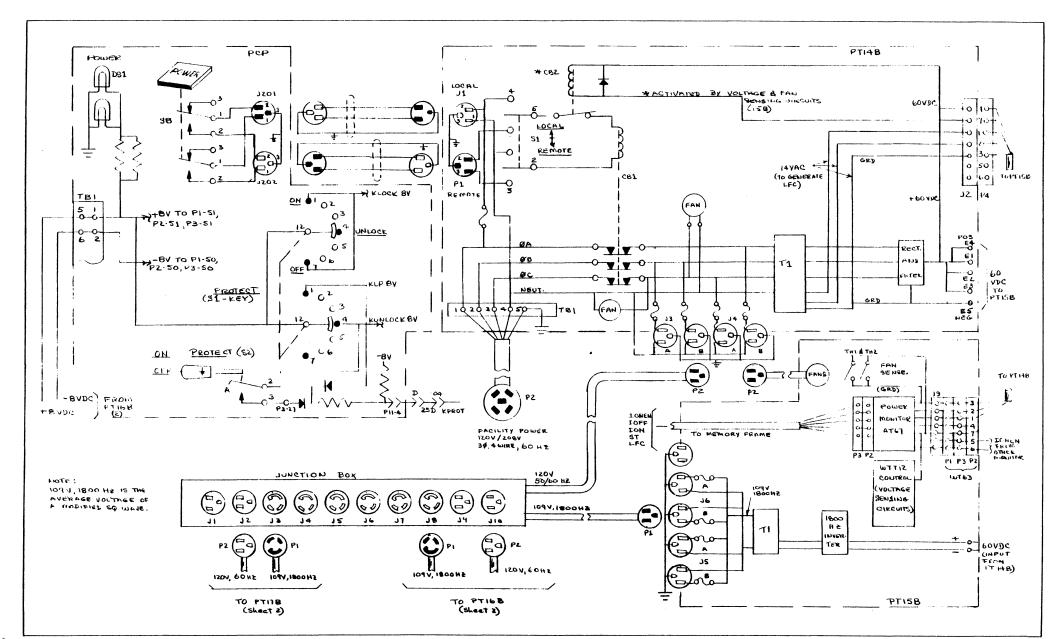

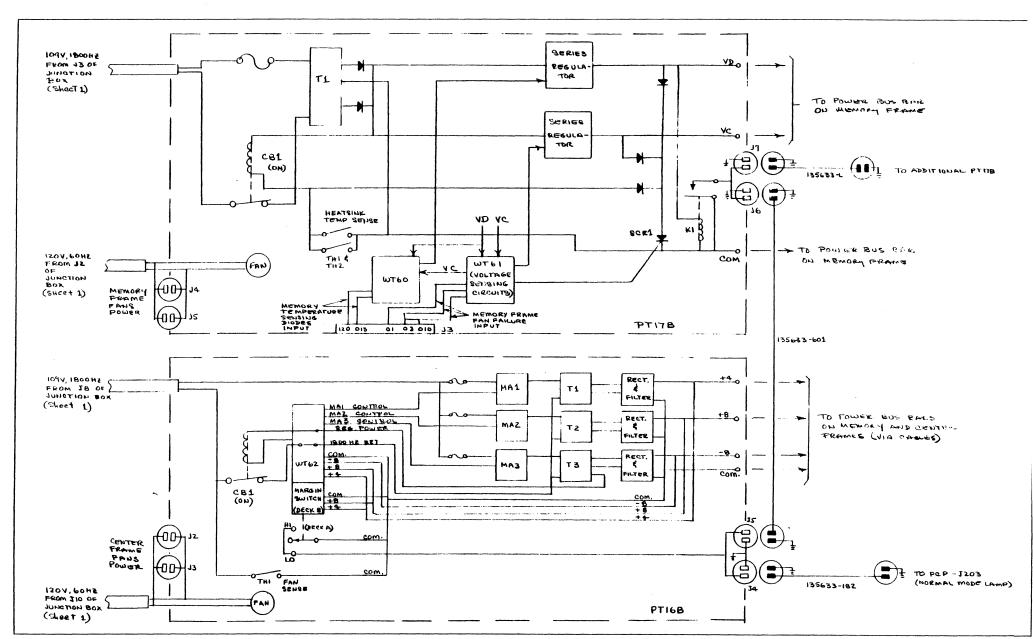

|        | 1-22  | Sigma 3 System Power Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-6  |         |       |                                                       |      |

|        |       | organization of the contraction |      |         | 3-1   | Introduction                                          | 3.1  |

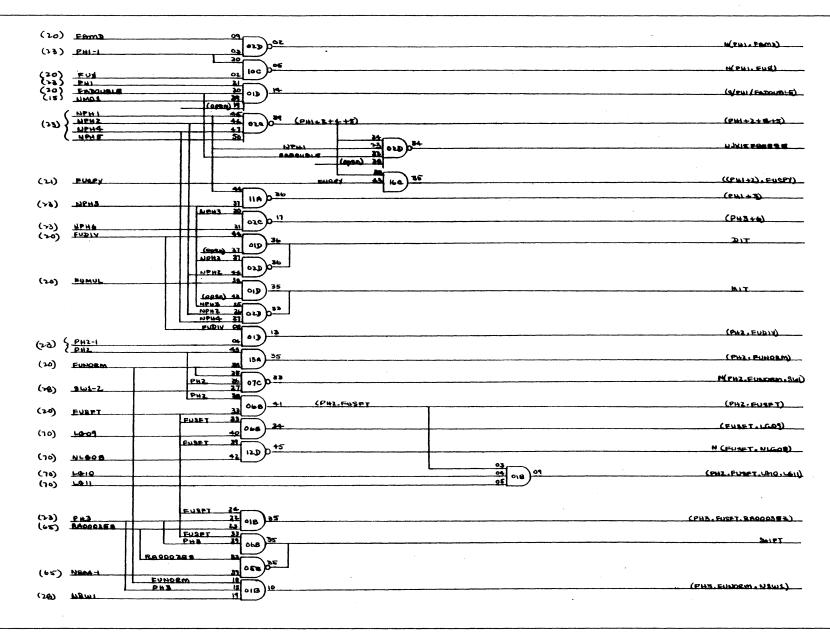

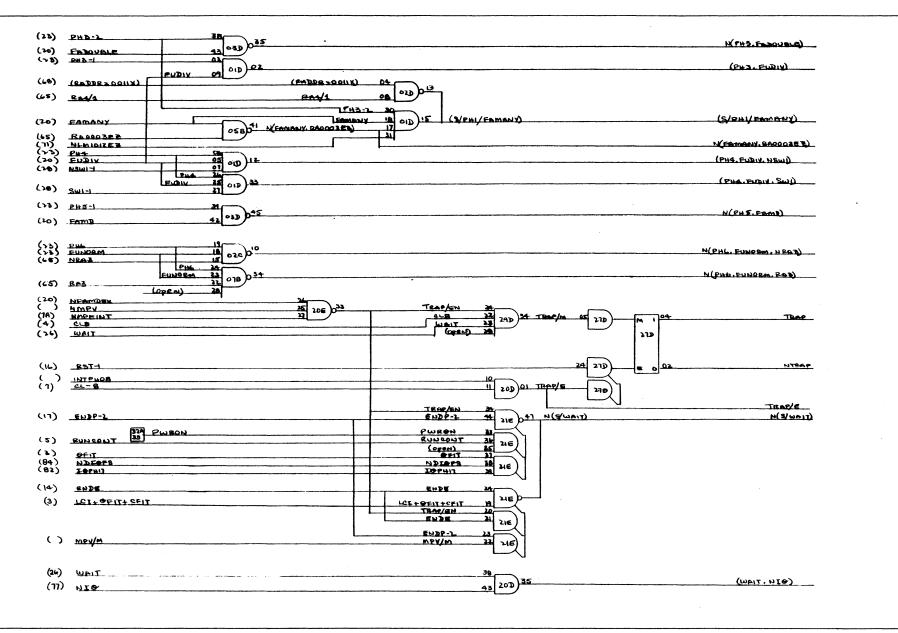

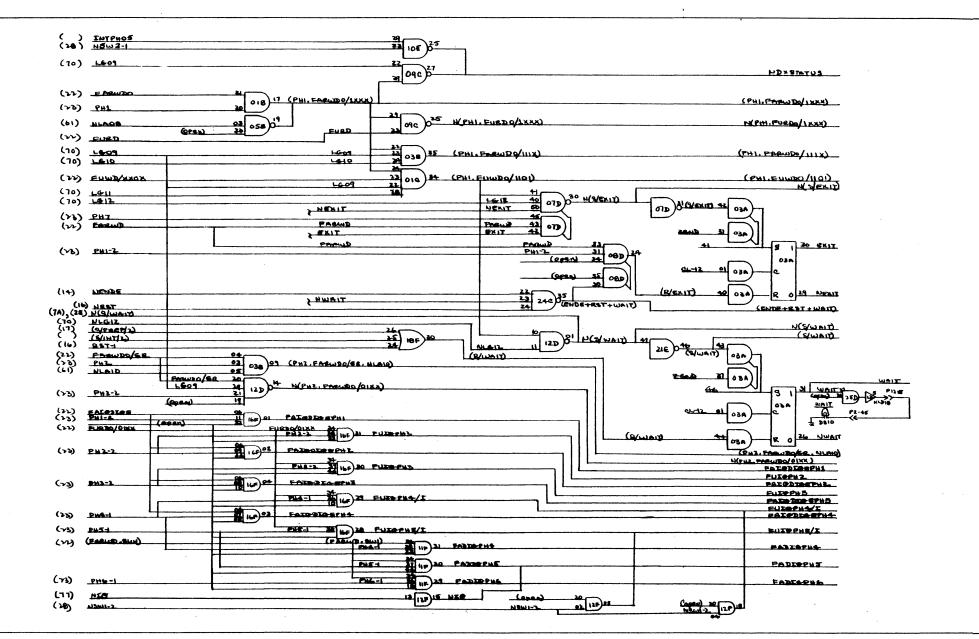

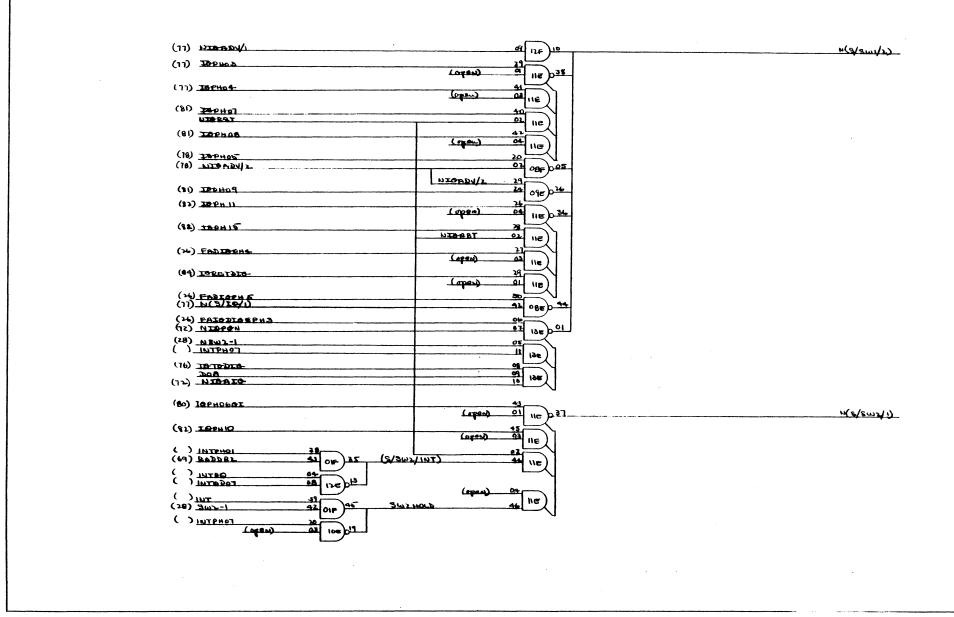

|        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |         | 3-2   | Logic Diagrams                                        |      |

| H      | FUNC  | TIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |         | 3-7   | PCP Mode of Operation                                 |      |

| ••     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |         | 3-8   | System Operation Procedure - PCP Control              | 3_1  |

|        | 2-1   | Central Processor Unit (CPU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-1  |         | 3-10  | Fetching and Storing Data - PCP Control               | 3-14 |

|        | 2-9   | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1  |         | 3-12  | Program Control Operation                             | 3-17 |

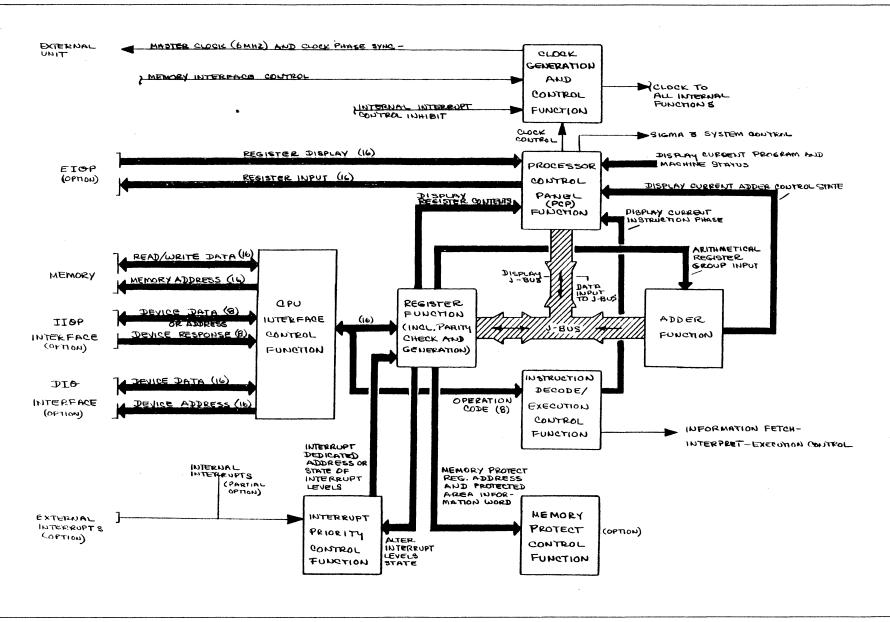

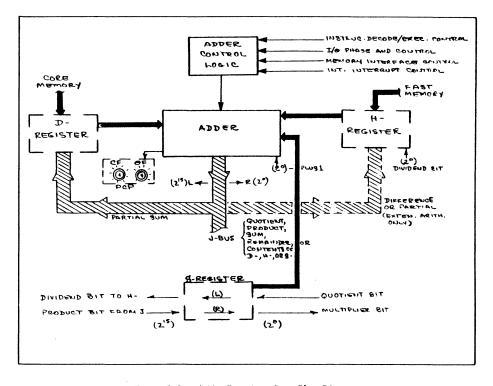

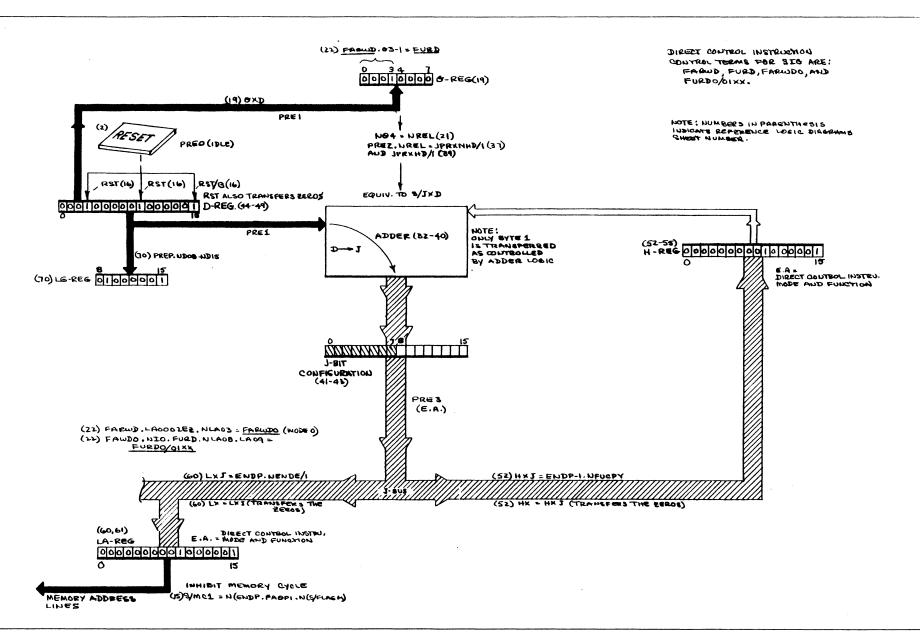

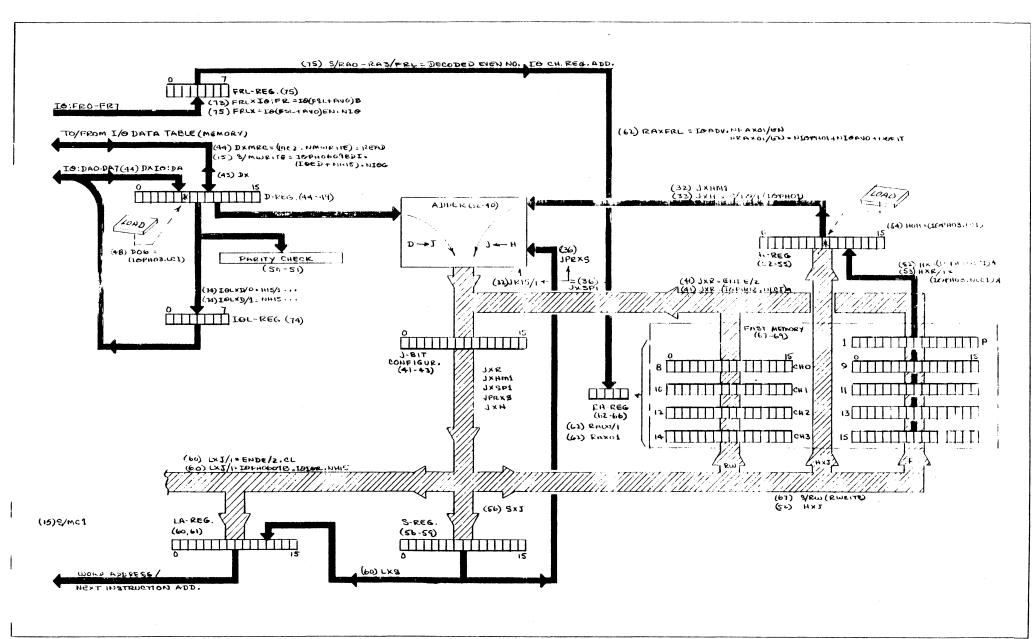

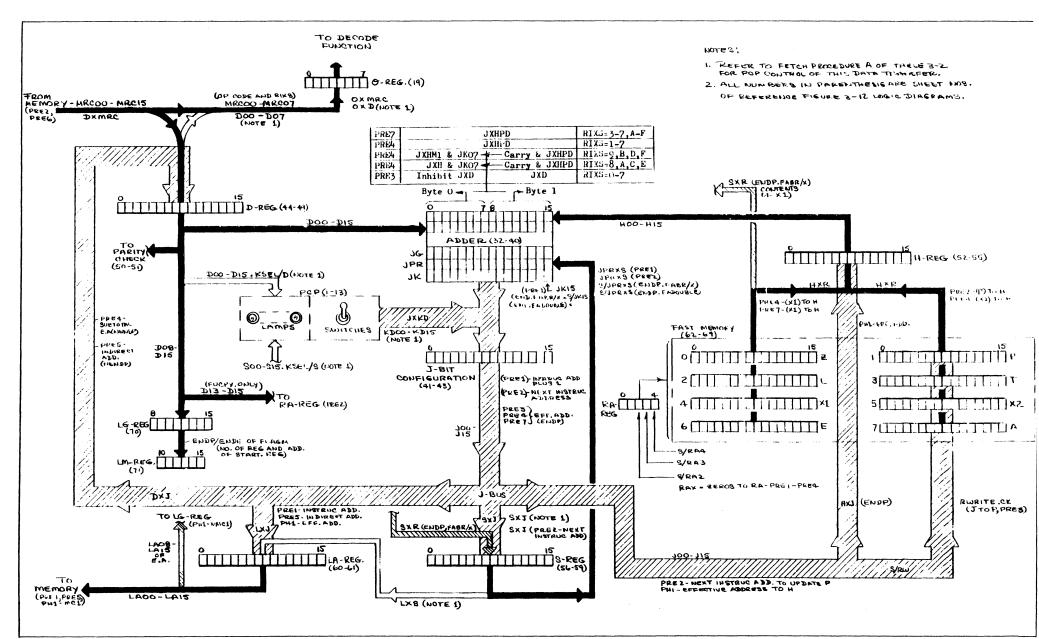

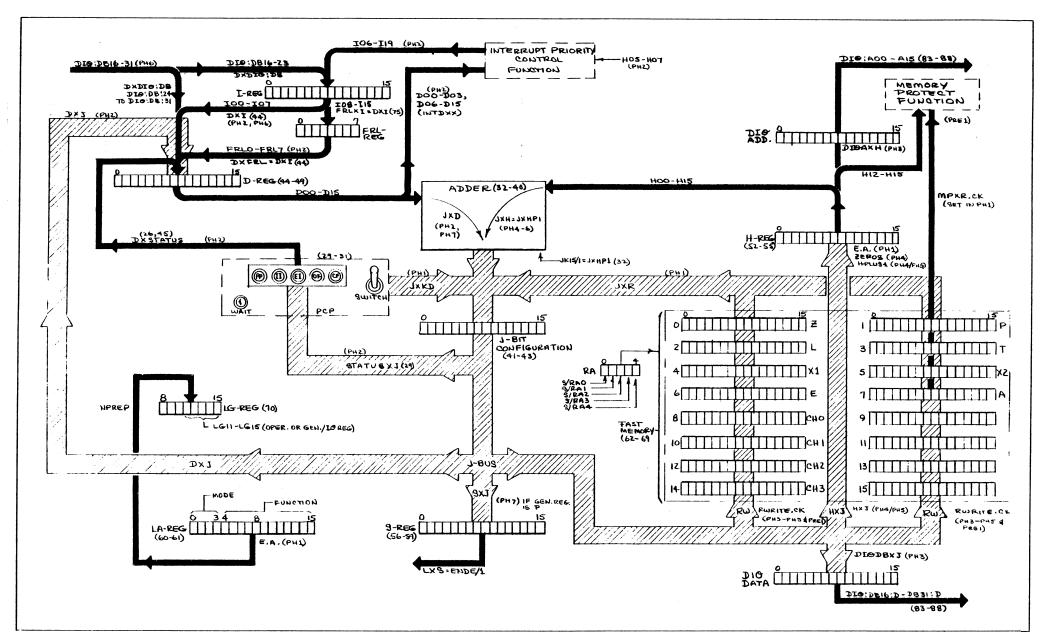

|        | 2-10  | CPU Data Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-2  |         | 3-16  | Instruction Preparation Sequence                      |      |

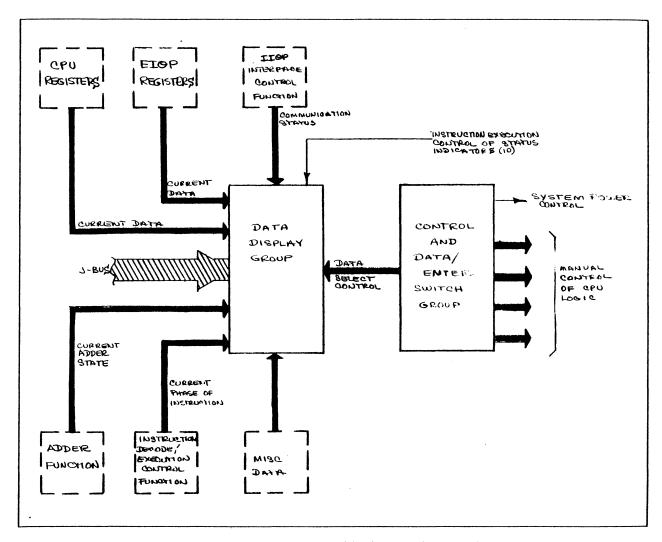

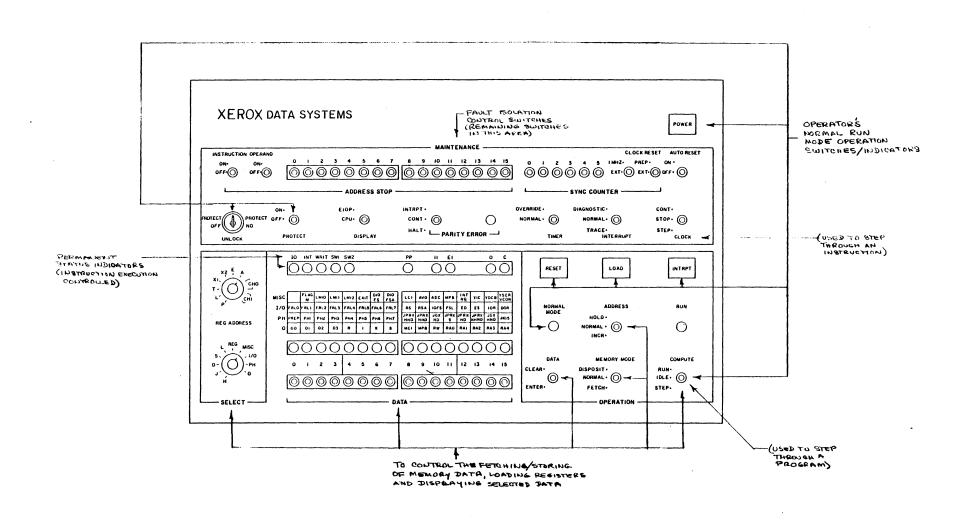

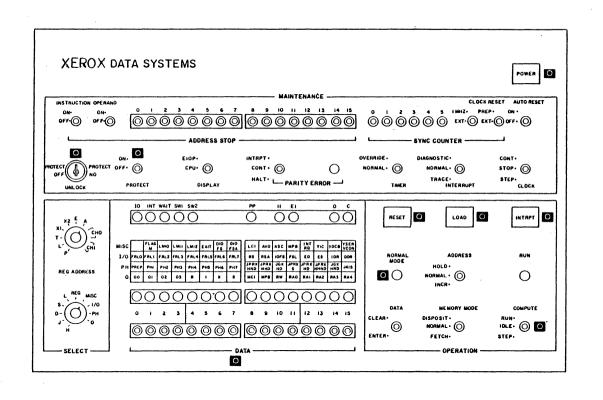

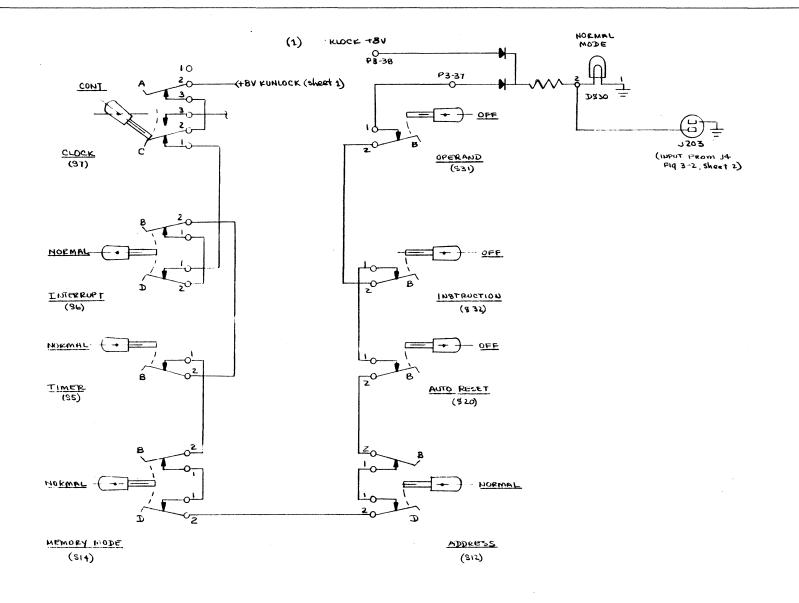

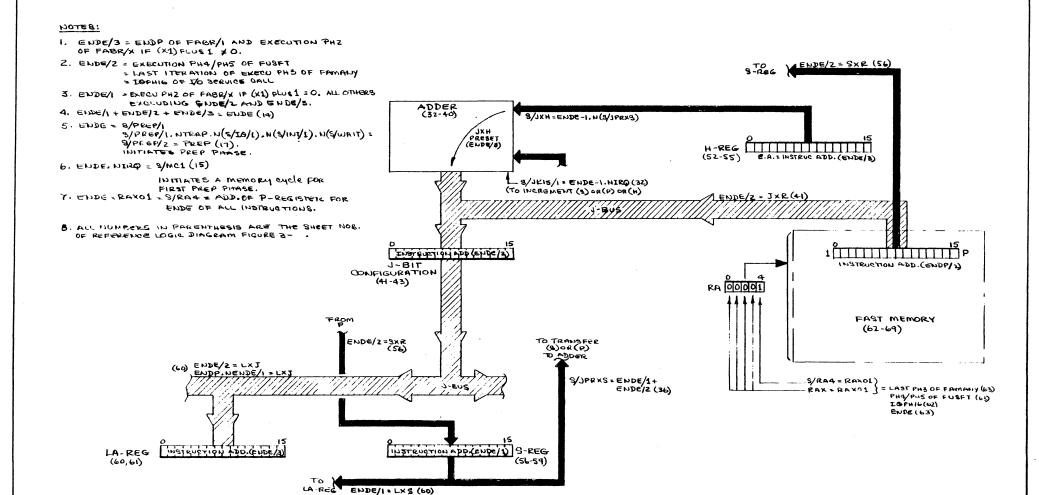

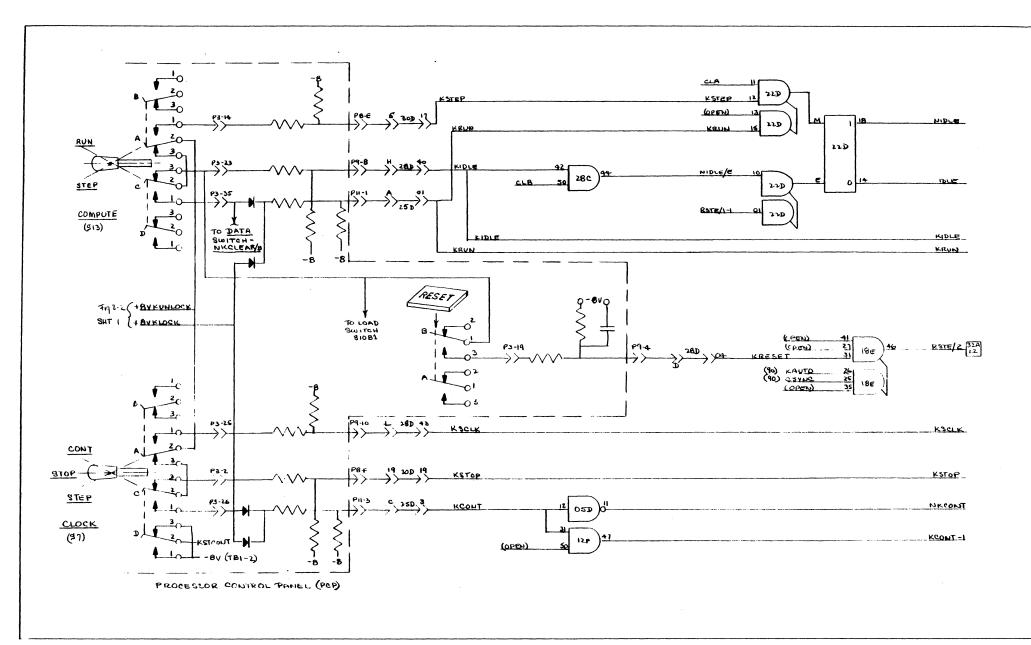

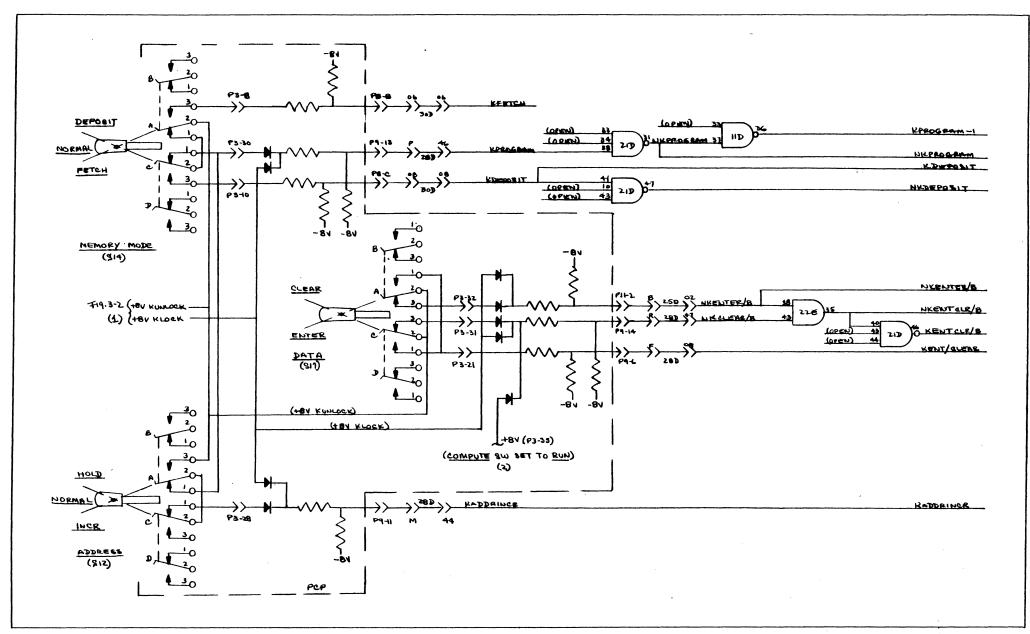

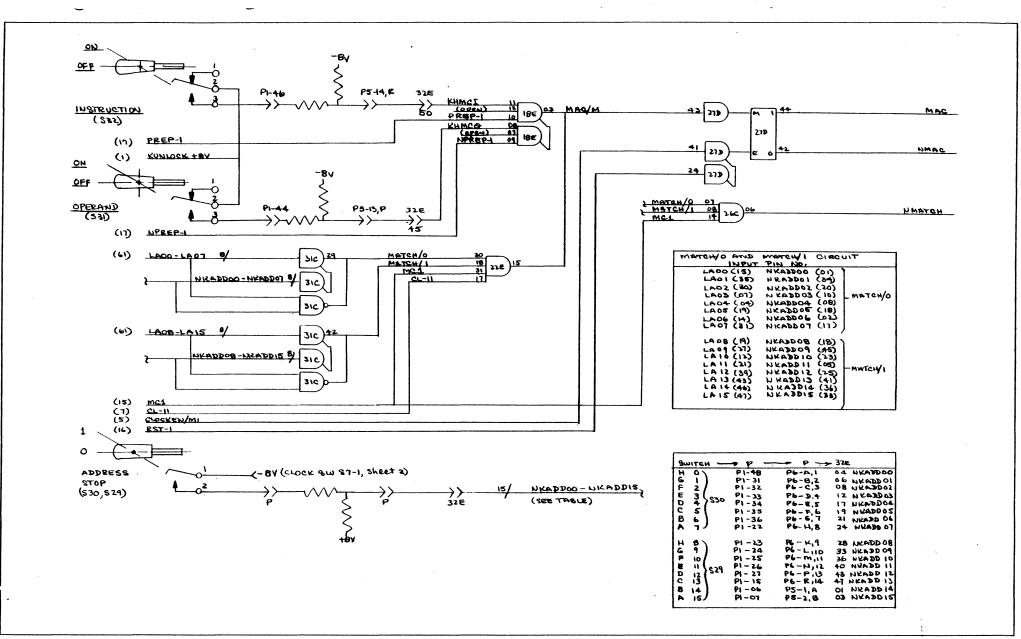

|        | 2-15  | Processor Control Panel (PCP) Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-4  |         | 3-22  | Source of Next Instruction Address                    |      |

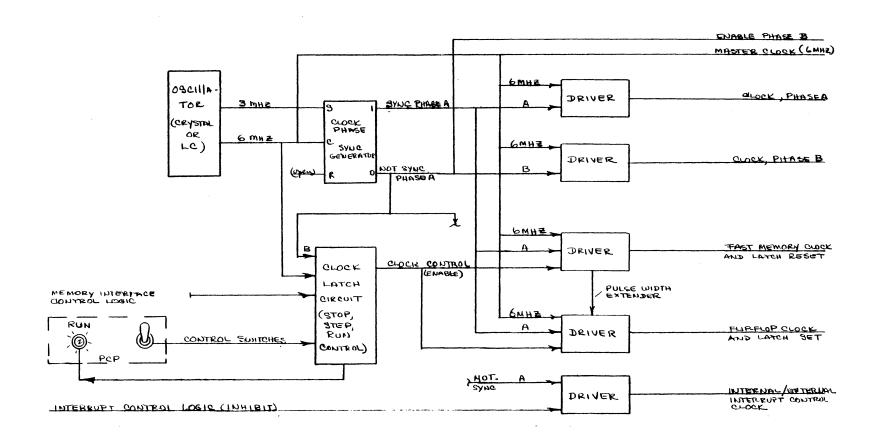

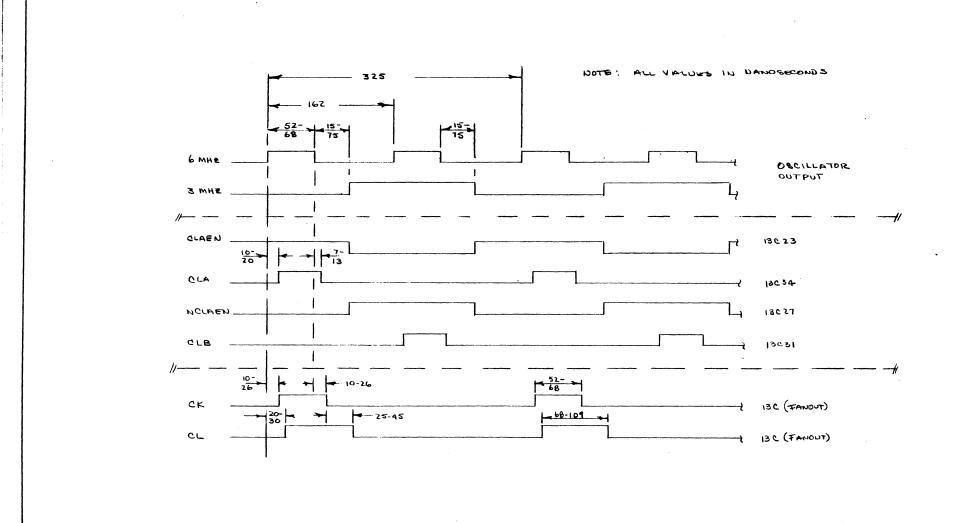

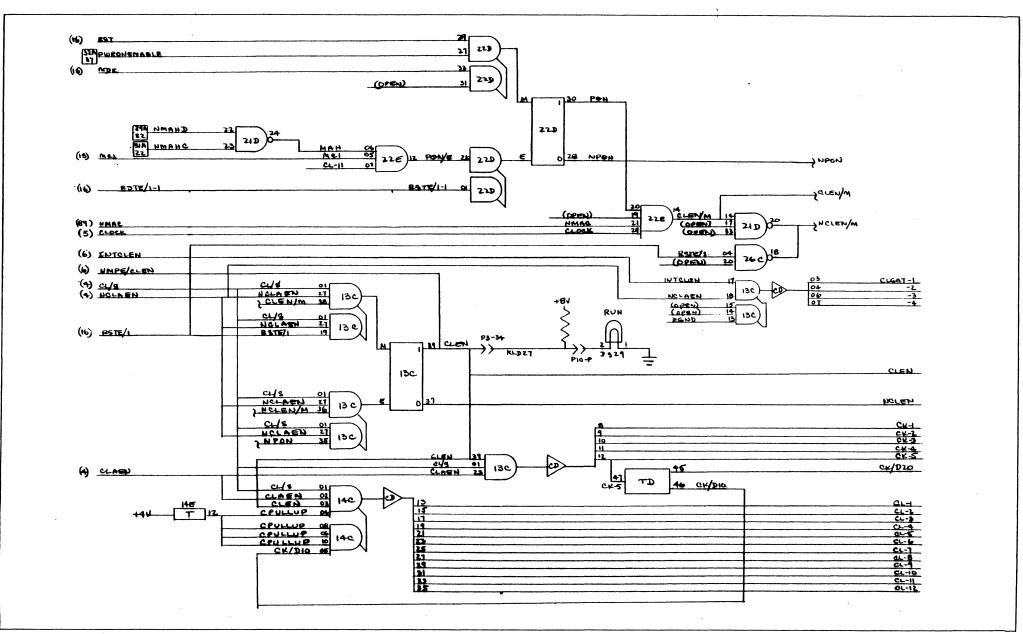

|        | 2-18  | Clock Generation and Control Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |         | 3-27  | Instruction Execution Sequence                        |      |

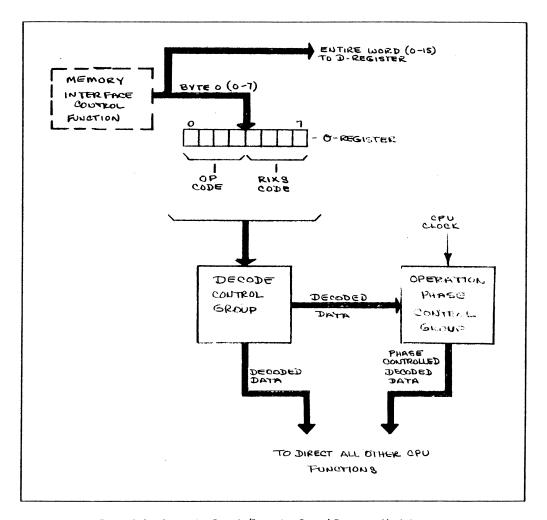

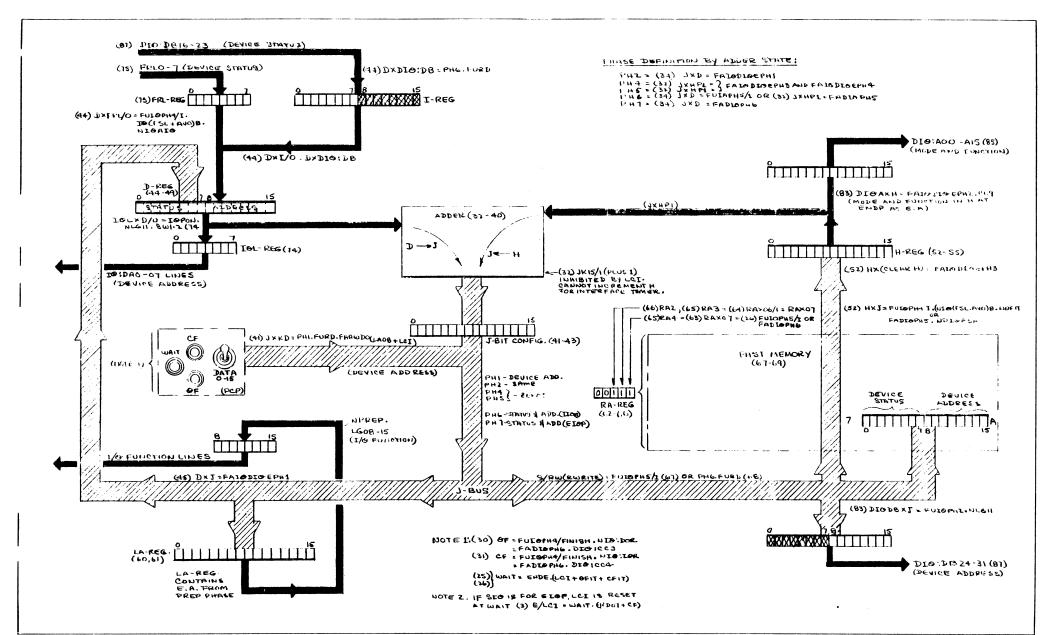

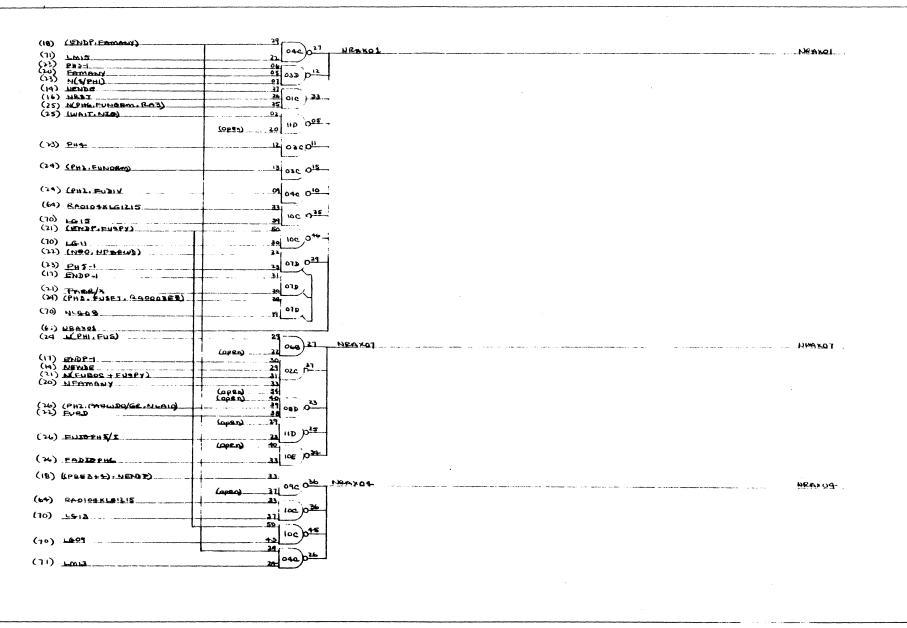

|        | 2-13  | Instruction Decode/Execution Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-8  |         | 3-29  | Direct Control Instruction                            |      |

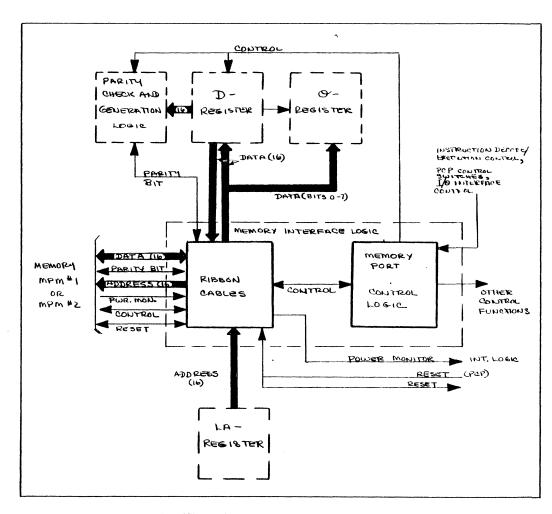

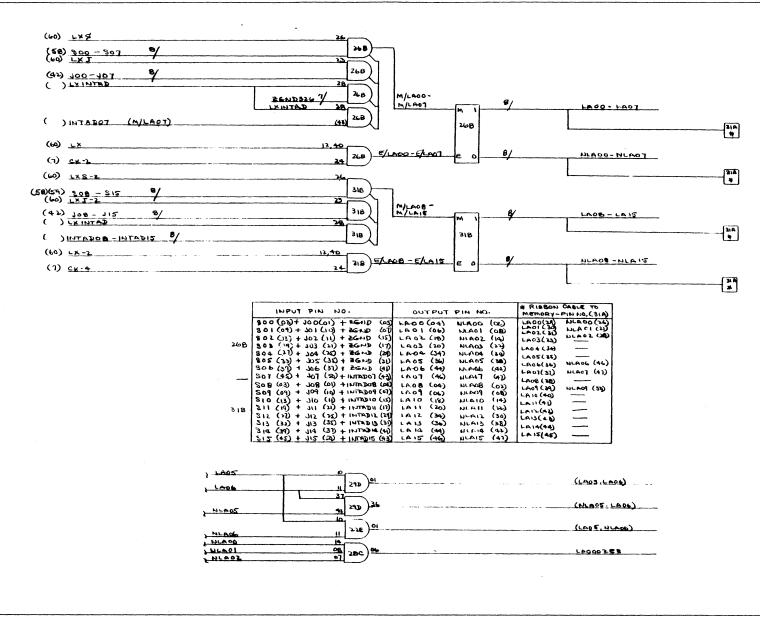

|        | 2-28  | Memory Interface (CPU Interface Function)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-9  |         | 3-    | Memory Reference Instruction (To be added)            | 5.30 |

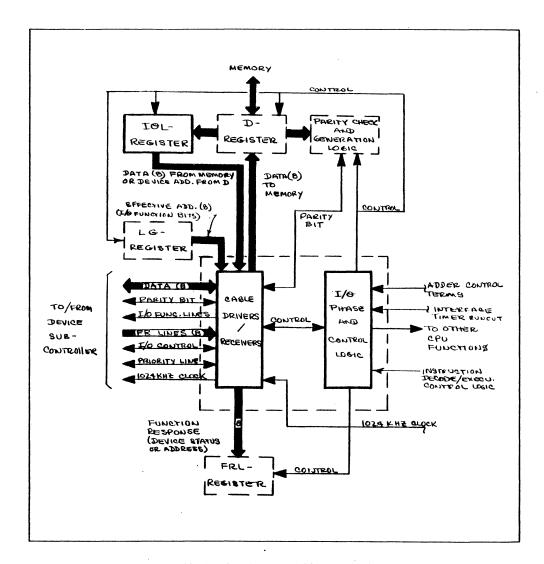

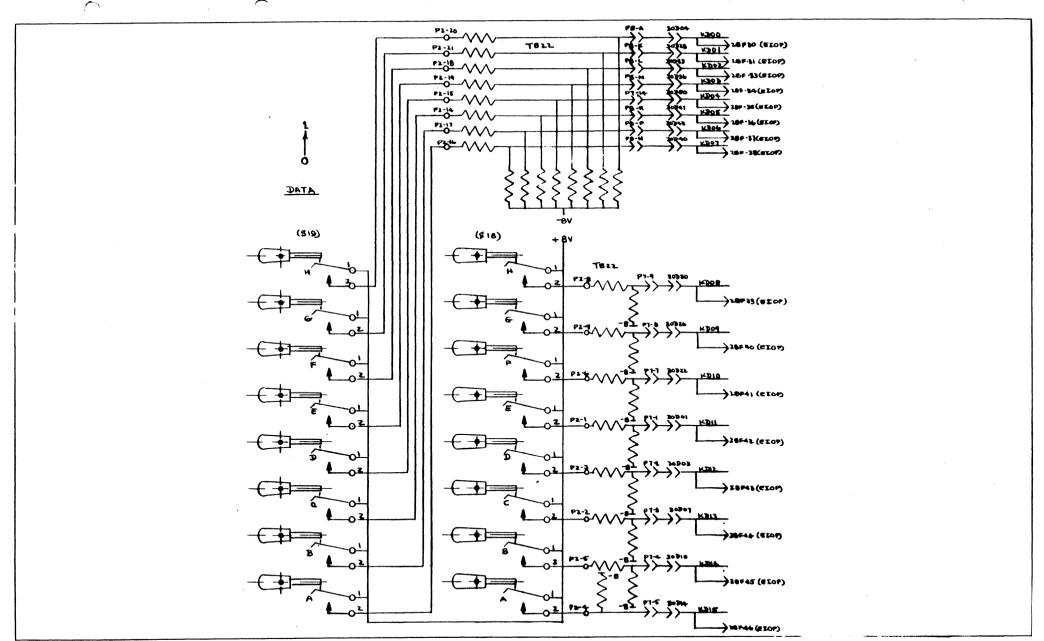

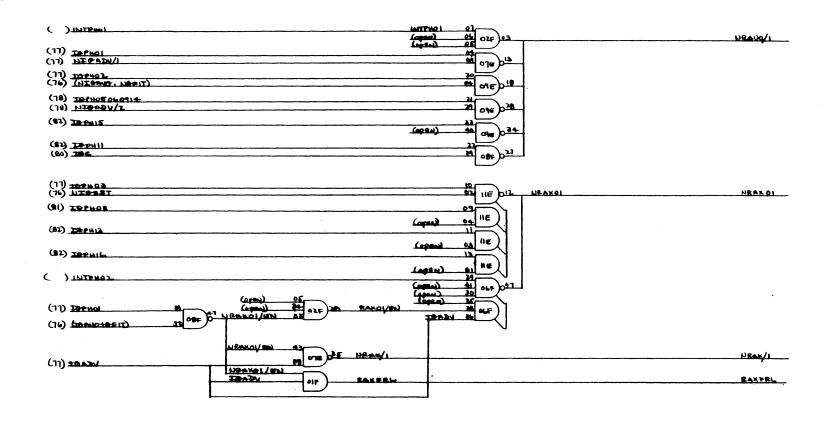

|        | 2-20  | IIOP Interface (CPU Interface Function)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-10 |         | 3-    | FUCPY and SHIFT Instructions (To be added)            |      |

# ILLUSTRATIONS

| Figure | Title                                                           | Page | Figure | Title                                           |                                         | Page |

|--------|-----------------------------------------------------------------|------|--------|-------------------------------------------------|-----------------------------------------|------|

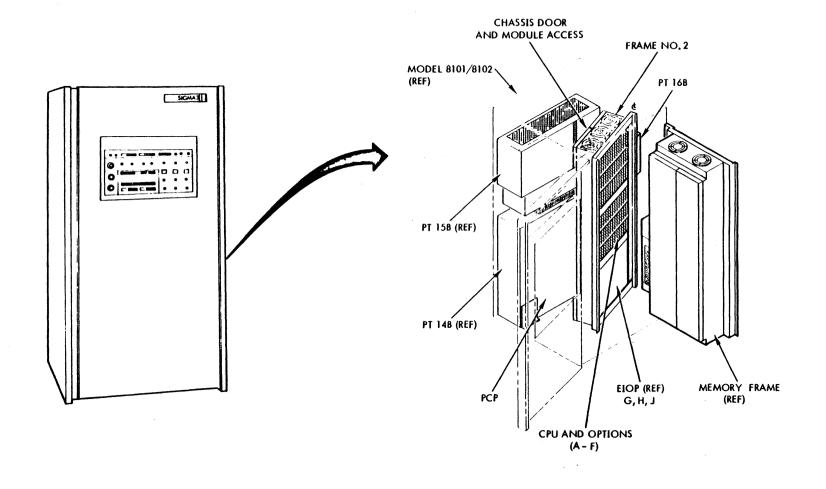

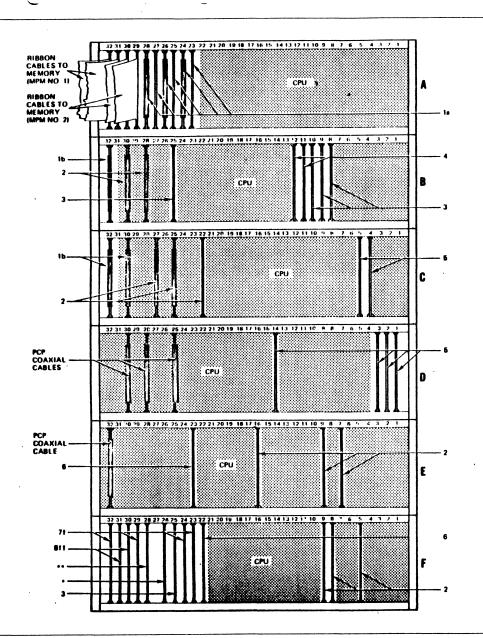

| 1-1    | Sigma 3 Central Processor Unit (CPU), Location in 8101/8102     |      | 2-17   | General and I/O Channel Registers (Fast Memo    | ory) Data Flow Diagrams .               | 2-31 |

|        | Model Cabinet                                                   | 1-1  | 2-18   | FRL-Register Data Flow Diagram                  |                                         |      |

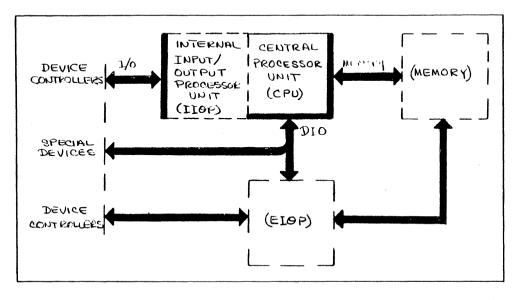

| 1-2    | Relation of the CPU to the Sigma 3 Computer System              | 1-3  | 2-19   | Interrupt Priority Control Function, Block Diag | ram (To be added)                       |      |