## INPUT/OUTPUT PROCESSOR (IOP) Model 8000 and 8001

**IPU CONSOLE IOP**

Reference Manual

April 1983

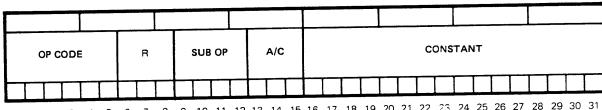

Publication Order Number: 301-000170-000

This manual is supplied without representation or warranty of any kind. Gould Inc., S.E.L. Computer Systems Division therefore assumes no responsibility and shall have no liability of any kind arising from the supply or use of this publication or any material contained herein.

Copyright 1980

Gould Inc., S.E.L. Computer Systems Division

Printed in U.S.A.

#### **HISTORY**

The Input/Output Processor (IOP) Model 8000 Reference Manual, Publication Order Number 301-000170-000, was printed July, 1980.

Publication Order Number 301-000170-001 (Change 1) was printed December, 1982.

Publication Order Number 301-000170-002 (Change 2) was printed April 1983. The updated manual contains the following pages:

| * Change<br>Number | * Change<br>Number   |

|--------------------|----------------------|

| Title page         | 4-1                  |

| 3-13/3-140         | 5-2 through 5-3/5-40 |

On a change page, the portion of the page affected by the latest change is indicated by a vertical bar in the outer margin of the page. However, a completely changed page will not have a full length bar, but will have the change notation by the page number.

<sup>\*</sup> Zero in this column indicates an original page.

#### HISTORY

The Input/Output Processor (IOP) (Models 8000 and 8001) Reference Manual, Publication Order Number 301-000170-000, was printed July, 1980.

Publication Order Number 301-000170-001 (Change 1) was printed December, 1982. The updated manual contains the following pages:

| * Change          | * Change          |

|-------------------|-------------------|

| Number            | Number            |

| Title page        | 4-1               |

| 1-1 through 1-4 0 | 4-6 through 4-580 |

| 2-1/2-2 1         | 5-11              |

| 3-1 through 3-140 | 5–2 through 5–4   |

On a change page, the portion of the page affected by the latest change is indicated by a vertical bar in the outer margin of the page. However, a completely changed page will not have a full length bar, but will have the change notation by the page number.

<sup>\*</sup> Zero in this column indicates an original page.

## CONTENTS

| Chapte | er                       |                                                                               |                                                                                                                                                                                                                          | Page                                 |

|--------|--------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 1      | GEN                      | ERAL IN                                                                       | FORMATION                                                                                                                                                                                                                | 1-1                                  |

|        | 1.1<br>1.2<br>1.3<br>1.4 | Product<br>Function                                                           | tion  Description  nal Description  sole IOP Difference                                                                                                                                                                  | . 1-2                                |

| 2      | CON                      | FIGURA                                                                        | TION INFORMATION                                                                                                                                                                                                         | 2-1                                  |

|        | 2.1<br>2.2               | Software<br>Hardwar                                                           | e                                                                                                                                                                                                                        | · · 2-1                              |

| 3      | OPE                      | RATION                                                                        |                                                                                                                                                                                                                          | 3-1                                  |

|        | 3.1<br>3.2               | 3.1.1<br>3.1.2                                                                | Information                                                                                                                                                                                                              | · · 3-1                              |

|        | 3.3                      | System (3.3.1)<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.5<br>3.3.5<br>3.3.7 | Control Panel Command Attention (@@A CR) Enter Console Mode (@@C CR) Enter Panel Mode (@@P CR) Address Stop Commands Clear Memory (CLE CR) CRAM Memory Address (CRMA=XXXXX CR) CRAM Memory Write (CRMD=XXXXXXXXXXXXX CR; | 3-7<br>3-8<br>3-8<br>3-8<br>3-10     |

|        |                          | 3.3.8                                                                         | =XXXXXXXXXXXXX CR)                                                                                                                                                                                                       |                                      |

|        |                          | 3.3.9<br>3.3.10<br>3.3.11<br>3.3.12<br>3.3.13<br>3.3.14                       | CS=XXXXXXXX CR). Rub Out (ASCII 08). Effective Address (EA CR). Execute CRAM (EXEC CR) General Purpose Register (GPR CR; GPRA=XXXXXXXXX CR) HALT CR                                                                      | . 3-10<br>. 3-10<br>. 3-10<br>. 3-10 |

|        |                          | 3.3.15<br>3.3.16<br>3.3.17                                                    | Initial Program Load (IPL) CR; IPL=XXXX CR) Line Feed LF Memory Address Read (MA=XXXXXX CR; CR) Memory Address Read Virtual (MAV=XXXXXX CR;                                                                              | . 3-11                               |

|        |                          | 3.3.18<br>3.3.19<br>3.3.20<br>3.3.21                                          | CR)                                                                                                                                                                                                                      | . 3-11<br>. 3-12                     |

| Chapter |             |           |                             |                  |                     |                                       | 1       | Page            |

|---------|-------------|-----------|-----------------------------|------------------|---------------------|---------------------------------------|---------|-----------------|

|         |             | 3.3.22    | Primary and                 | d Secondary Pa   | nel (PRIP CR        | and                                   |         |                 |

|         |             |           | SECP CR)                    |                  |                     |                                       |         | 3-12            |

|         |             | 3.3.23    | Program St                  | atus Doublewo    | rd (PSD CR :        |                                       |         |                 |

|         |             | 3.3.24    | Program St                  | atus Word (PSV   | V CR •              |                                       |         |                 |

|         |             | J•J•ZŦ    | PSW-XXXX                    | XXXX CR)         |                     |                                       |         | 3-12            |

|         |             | 3.3.25    | Reset (RST                  | (R)              |                     |                                       |         | 3-13            |

|         |             | 3.3.26    | RUN CR .                    |                  |                     |                                       |         | 3-13            |

|         |             | 3.3.27    | SHIFT DE                    | L (ASCII 7F) .   |                     |                                       |         | 3-13            |

|         |             | 3.3.28    | STEP CR                     |                  |                     |                                       |         | 3-13            |

| 4       | SOET        | WADE DE   |                             | NG               |                     |                                       |         | . 4-1           |

| 4       |             |           |                             |                  |                     |                                       |         |                 |

|         | 4.1         | Input/Out | put (IOP) Pi                | rogramming       | • • • • • • • • •   |                                       | • • • • | . 4-1           |

|         | <i>i.</i> 2 | 4.1.1     | Software E                  | nvironment       |                     |                                       | • • • • | 4-3             |

|         |             | Input/Out | tput System:<br>Japut/Outpu | s Components.    |                     |                                       |         | . 4-5           |

|         |             | 4.2.1     | 4.2.1.1                     | Innut/Output \   | Jamory Addres       | sing                                  |         | . 4-5           |

|         |             |           | 4.2.1.2                     | Extended I/O I   | nstructions         |                                       |         | . 4-5           |

|         |             |           |                             | 4.2.1.2.1        | Start I/O           |                                       |         | . 4-5           |

|         |             |           |                             | 4.2.1.2.2        | Test I/O            |                                       |         | . 4-6           |

|         |             |           |                             | 4.2.1.2.3        | Halt I/O            |                                       |         | . 4-6           |

|         |             |           |                             | 4.2.1.2.4        | Enable Channe       | el Interrupt                          |         | . 4-6           |

|         |             |           |                             | 4.2.1.2.5        | Disable Chann       | el Interrupt                          |         | . 4-6           |

|         |             |           |                             | 4.2.1.2.6        |                     | mel Interrupt .                       | • • • • | . 4-6           |

|         |             |           |                             | 4.2.1.2.7        | Deactivate Ch       |                                       |         |                 |

|         |             |           |                             |                  | Interrupt           | •••••                                 | • • • • | . 4-6           |

|         |             |           |                             | 4.2.1.2.8        | Reset Channe.       | 1                                     | • • • • | . 4-6           |

|         |             |           |                             | 4.2.1.2.9        | Stop 1/0            |                                       | • • • • | . 4-6           |

|         |             |           |                             | 4.2.1.2.10       |                     |                                       |         |                 |

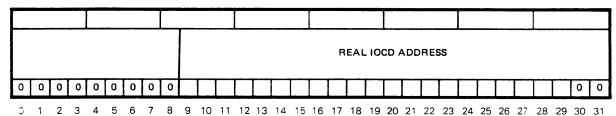

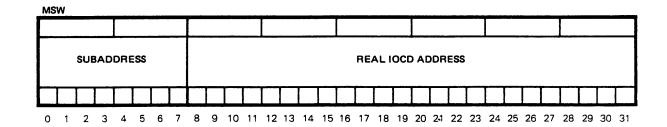

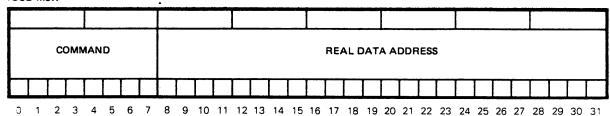

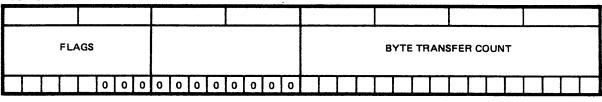

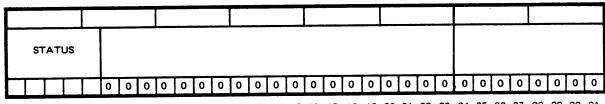

|         |             |           | 4.2.1.3                     | I/O Initiation   | Command List        | Address                               | • • • • | . 4-7           |

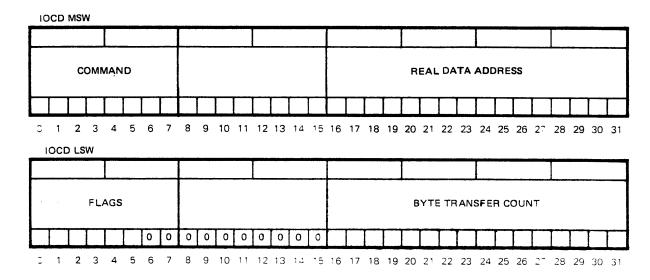

|         |             |           | 4.2.1.4<br>4.2.1.5          | Input/Output (   | Command Doub        | leword                                | • • • • | 4-7<br>4-7      |

|         |             | 4.2.2     | 1/O Comma                   | input/Output (   | John Hand Doub      | · · · · · · · · · · · · · · · · · · · |         | . 4-8           |

|         |             | 4.2.2     | 4.2.2.1                     | Execution of L   | O Commands          |                                       |         | . 4-8           |

|         |             |           |                             | 4.2.2.1.1        | Write               |                                       |         | . 4-8           |

|         |             |           |                             | 4.2.2.1.2        | Read                |                                       |         | . 4-8           |

|         |             |           |                             | 4.2.2.1.3        | Read Backwar        | :d                                    |         | . 4-8           |

|         |             |           |                             | 4.2.2.1.4        | Control             |                                       |         | . 4-9           |

|         |             |           |                             | 4.2.2.1.5        | Sense               |                                       |         | . 4-9           |

|         |             |           |                             | 4.2.2.1.6        | Transfer in Ch      | nannel                                |         | . 4-9           |

|         |             |           |                             | 4.2.2.1.7        | Channel Cont        | rol                                   | • • • • | . 4-9           |

|         |             | 4.2.3     | I/O Termin                  | nation           |                     |                                       |         | . 4-9           |

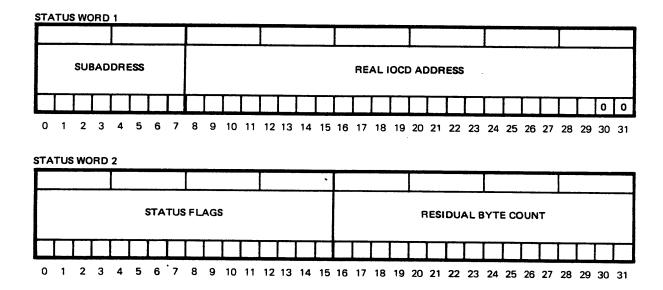

|         |             | 4.2.4     | I/O Status                  | Words            | • • • • • • • • • • |                                       | • • • • | . 4-9           |

|         |             | 4.2.5     | I/O Interru                 | pts              |                     |                                       | • • • • | . 4-10          |

|         |             | 4.2.6     | Blocking of                 | Data             | • • • • • • • • • • |                                       | • • • • | , 4-10<br>1, 11 |

|         | 4.3         |           | ations                      |                  | • • • • • • • • • • |                                       | • • • • | 4-11<br>4-11    |

|         |             | 4.3.1     |                             | Controller       |                     |                                       | • • • • | . τ-11<br>4_11  |

|         |             |           | 4.3.1.1                     | 4.3.1.1.1        | Types of Cont       | trollers                              | • • • • | . 4-17          |

|         |             |           | 4.3.1.2                     |                  | Processor           |                                       |         | 4-12            |

|         |             |           | マッノ・エッム                     | 11100 U OULUUL 1 |                     |                                       |         | ~               |

| Chapter |                |                     |             | E                                 | Page         |

|---------|----------------|---------------------|-------------|-----------------------------------|--------------|

|         |                | 4.3.1.3             | Subchannels | S                                 | 4-12         |

|         | 4.3.2          | System C            |             |                                   | 4-12         |

| 4.4     | I/O Ins        |                     |             |                                   |              |

|         | 4.4.1          | Initial Prog        | gram Load   |                                   | 4-14         |

|         | 4.4.2          | Extended Ì          |             | ns                                |              |

|         |                | 4.4.2.1             | Start I/O . |                                   | 4-17         |

|         |                | 4.4.2.2             |             |                                   | 4-18         |

|         |                | 4.4.2.3             |             |                                   | 4-18         |

|         |                | 4.4.2.4             |             | ••••••                            | 4-19         |

|         |                | 4.4.2.5             |             | inel                              | 4-20         |

|         |                | 4.4.2.6             |             | roller                            | 4-20         |

|         |                | 4.4.2.7             |             | nnel Interrupt                    | 4-21<br>4-21 |

|         |                | 4.4.2.8             |             | annel Interrupt                   |              |

|         |                | 4.4.2.9<br>4.4.2.10 |             | hannel Interrupt                  | 4-22         |

|         | 4.4.3          |                     |             |                                   | 4-23         |

|         | 4.4.4<br>4.4.4 | Device En           | duressing   |                                   | 4-23         |

|         | 4.4.5          |                     |             | ord                               | 4-24         |

|         | T•T•J          | 4.4.5.1             |             |                                   | 4-24         |

|         |                | 4.4.5.2             |             | nat                               | 4-25         |

|         |                | 7.7.7.2             | 4.4.5.2.1   | Data Chain                        | 4-26         |

|         |                |                     | 4.4.5.2.2   | Command Chain                     | 4-27         |

|         |                |                     | 4.4.5.2.3   | Suppress Incorrect Length         | 4-28         |

|         |                |                     | 4.4.5.2.4   | Skip                              | 4-28         |

|         |                |                     | 4.4.5.2.5   | Post Program Controlled Interrupt |              |

|         |                |                     |             | (PPCI)                            | 4-28         |

|         |                | 4.4.5.3             |             | Instructions                      | 4-29         |

|         |                |                     | 4.4.5.3.1   | Write                             | 4-29         |

|         |                |                     | 4.4.5.3.2   | Read                              | 4-30         |

|         |                |                     | 4.4.5.3.3   | Read Backward                     | 4-31         |

|         |                |                     | 4.4.5.3.4   | Control                           | 4-31         |

|         |                |                     | 4.4.5.3.5   | Sense                             | 4-32<br>4-34 |

|         |                |                     | 4.4.5.3.6   | Transfer in Channel               |              |

| 1, 5    | T:             | :f I/C              | 4.4.5.3.7   | Channel Control                   | 4-34<br>4-35 |

| 4.5     | 4.5.1          |                     | •           |                                   | 4-35         |

|         | 4.7.1          |                     |             | n at Operation Instruction        | 4-36         |

|         |                | 4.5.1.2             |             | Operation                         |              |

|         |                | 4.5.1.3             |             | on of Data Transfers              |              |

|         |                | 4.5.1.4             |             | on by an RSCHNL Instruction       | 4-37         |

|         |                | 4.5.1.5             |             | on by an RSCTL Instruction        | 4-38         |

|         |                | 4.5.1.6             |             | on by an HIO Instruction          |              |

|         |                | 4.5.1.7             |             | on by an STPIO Instruction        |              |

|         |                | 4.5.1.8             |             | on Due to Equipment               |              |

|         |                | ,,,,,,,,            | Malfunction | n                                 | 4-38         |

|         | 4.5.2          | I/O Interr          |             |                                   | 4-38         |

|         | 1 +2 +4        | 4.5.2.1             |             | Conditions                        |              |

|         |                | 4.5.2.2             |             | agement                           |              |

|         |                |                     | 4.5.2.2.1   | Status Address                    |              |

|         |                |                     | 4.5.2.2.2   | Status Words                      |              |

|         |                | 4.5.2.3             |             | Conditions                        |              |

| Chapter |                  |            |               |                                    | Page                |

|---------|------------------|------------|---------------|------------------------------------|---------------------|

|         |                  |            | 4.5.2.3.1     | Echo                               | 4-43                |

|         |                  |            | 4.5.2.3.2     | Post Program Controller Interrupt  |                     |

|         |                  |            |               | (PPCI)                             | 4-43                |

|         |                  |            | 4.5.2.3.3     | Incorrect Length                   | 4-44                |

|         |                  |            | 4.5.2.3.4     | Program Check                      | 4-44                |

|         |                  |            | 4.5.2.3.5     | IOP Data Check                     |                     |

|         |                  |            | 4.5.2.3.6     | IOP Control Check                  |                     |

|         |                  |            | 4.5.2.3.7     | Interface Control Check            |                     |

|         | ,                | 4.5.2.4    | 4.5.2.3.8     | Chaining Check                     |                     |

|         |                  | 4.).2.4    | 4.5.2.4.1     | Device Status Conditions           |                     |

|         |                  |            | 4.5.2.4.2     | Busy Status Status Modifier Status |                     |

|         |                  |            | 4.5.2.5.3     | Controller End Status              |                     |

|         |                  |            | 4.5.2.4.4     | Attention Status                   |                     |

|         |                  |            | 4.5.2.4.5     | Channel End Status                 |                     |

|         |                  |            | 4.5.2.4.6     | Device End Status                  |                     |

|         |                  |            | 4.5.2.4.7     | Unit Check Status                  |                     |

|         |                  |            | 4.5.2.4.8     | Unit Exception Status              |                     |

| 4.6     | Operator         | Console P  | rogramming.   |                                    | 4-48                |

|         | 4.6.1            |            |               |                                    |                     |

|         | 4.6.2            |            |               |                                    |                     |

|         | 4.6.3            |            |               |                                    |                     |

|         | 4.6.4<br>4.6.5   | Initialize | Channel (ICH) | Instruction                        | 4-51<br>4-51        |

|         | 4.6.6            |            |               |                                    |                     |

|         | 4.6.7            |            |               |                                    |                     |

|         | 4.6.8            |            |               |                                    |                     |

|         | 4.6.9            |            |               |                                    |                     |

|         | 4.6.10           | CPU State  |               |                                    |                     |

|         |                  | 4.6.10.1   |               | s                                  | 4-53                |

|         |                  | 4.6.10.2   |               | am Controlled Interrupt            |                     |

|         |                  |            |               |                                    |                     |

|         |                  | 4.6.10.3   | Incorrect L   | ength Status                       | . 4-53              |

|         |                  | 4.6.10.4   |               | m Check                            | , 4 <del>-</del> )3 |

|         |                  |            | 4.6.10.4.1    | Invalid IOCS Address Specification | 11 53               |

|         |                  |            | 4.6.10.4.2    | Invalid IOCD Address               |                     |

|         |                  |            | 4.6.10.4.3    | Invalid Command                    |                     |

|         |                  |            | 4.6.10.4.4    | Invalid Count                      | 4-53                |

|         |                  |            | 4.6.10.4.5    | Invalid Data Address               |                     |

|         |                  | 4.6.10.5   | IOP Data      | Check Status                       |                     |

|         |                  | 4.6.10.6   | IOP Contr     | rol Check Status                   | 4-54                |

|         |                  | 4.6.10.7   |               | us                                 |                     |

|         |                  | 4.6.10.8   | Attention     | Status                             | 4-54                |

|         |                  | 4.6.10.9   |               | End Status                         |                     |

|         |                  | 4.6.10.10  |               | nd Status                          |                     |

|         | 1                | 4.6.10.11  |               | ck Status                          |                     |

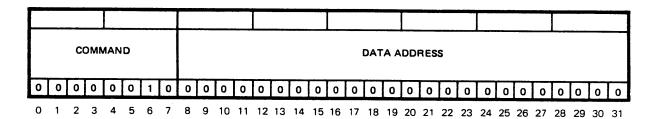

|         | 4.6.11<br>4.6.12 | Dasic I/O  | Command Do    | ubleword                           | , 4-22<br>μ_56      |

|         | 4.0.12           | 4.6.12.1   |               | indius                             |                     |

|         |                  | 7.0.14.1   |               | Data Set Ready                     |                     |

| Chapter      |                        |               |                                | Page   |

|--------------|------------------------|---------------|--------------------------------|--------|

|              |                        | 4.6.12.1.2    | Data Carrier Detected          | . 4-57 |

|              | 4.6.12.2               | Transfer In ( | Channel (TIC)                  | . 4-57 |

|              | 4.6.12.3               | Transmit (W   | rite)                          | . 4-57 |

|              | 4.6.12.4               | Receive (Re   | ad)                            | . 4-57 |

|              | 4.6.12.5               |               | Echo                           |        |

|              | 4.6.12.6               |               |                                |        |

|              | 4.6.12.7               |               | ne                             |        |

|              | 4.6.12.8               | No Operation  |                                | . 4-57 |

|              | 4.6.12.9               | Flags         |                                | . 4-58 |

|              |                        | 4.6.12.9.1    | Data Chain Flag                | . 4-58 |

|              |                        | 4.6.12.9.2    | Command Chaining Flag          | . 4-58 |

|              |                        | 4.6.12.9.3    | Suppress Incorrect Length      |        |

|              |                        |               | Flag                           | . 4-58 |

|              |                        | 4.6.12.9.4    | Suppress Transfer to Memory    |        |

|              |                        |               | (Skip) Flag                    |        |

|              |                        | 4.6.12.9.5    | Post Program Control Interrupt |        |

|              |                        |               | Flag                           | . 4-58 |

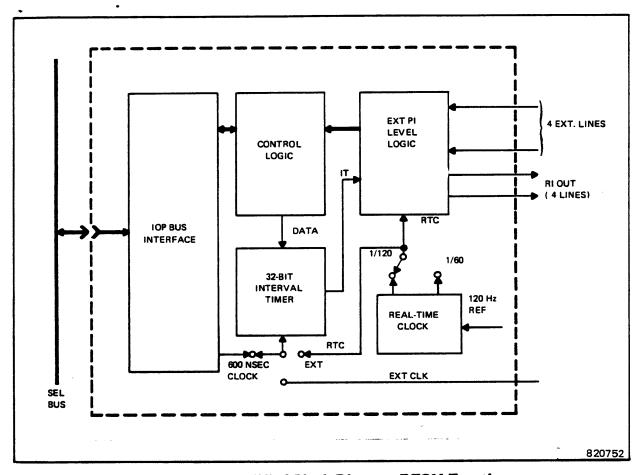

| 5 IOI        | P REAL-TIME OPTION     | MODULE (RTC   | м)                             | 5-1    |

| 5.1<br>5.2   | General Description    | •••••         | •••••••                        | 5-l    |

| 5 <b>.</b> 2 | Functional Description | on            |                                | 5-1    |

## **ILLUSTRATIONS**

| Figure                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                |

|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

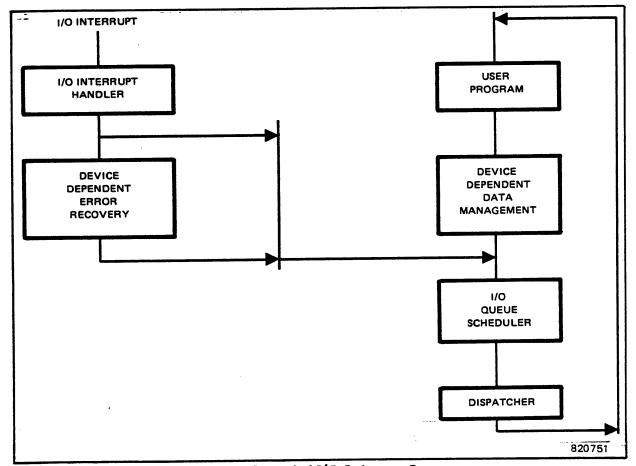

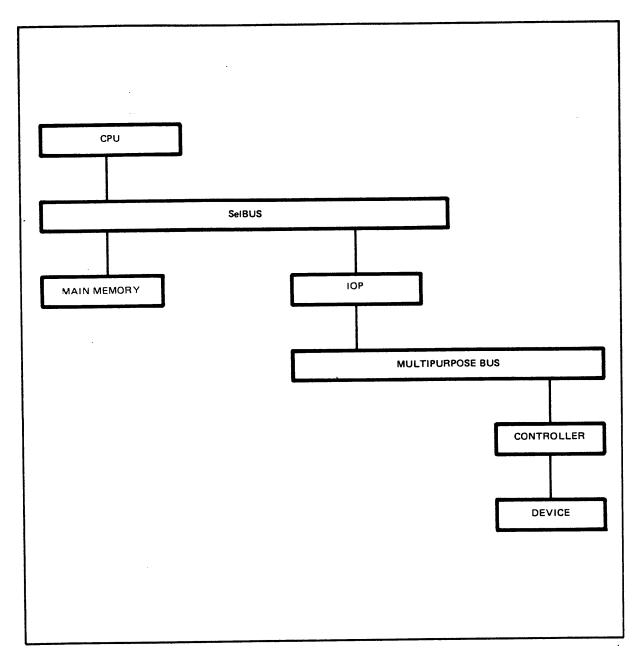

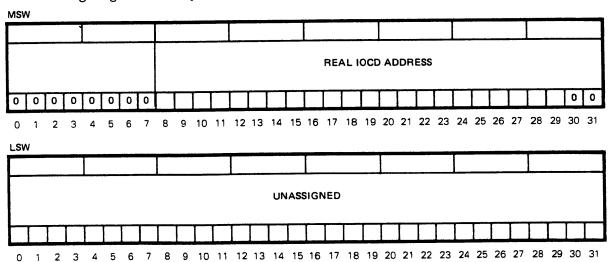

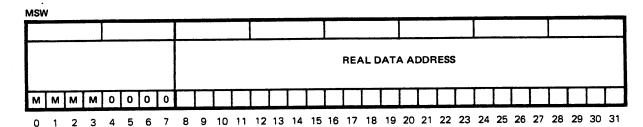

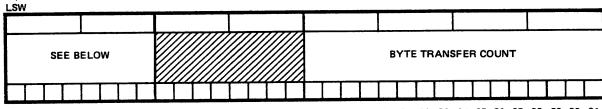

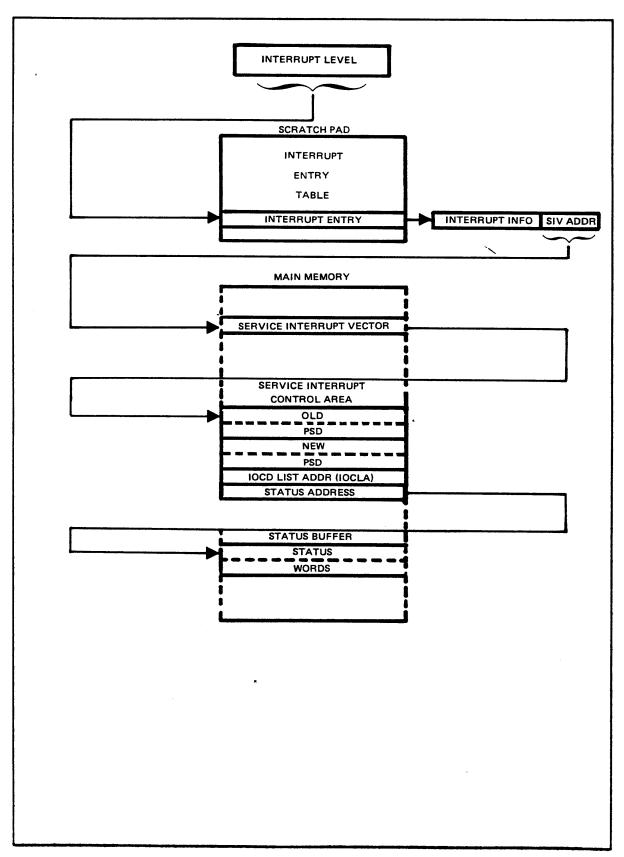

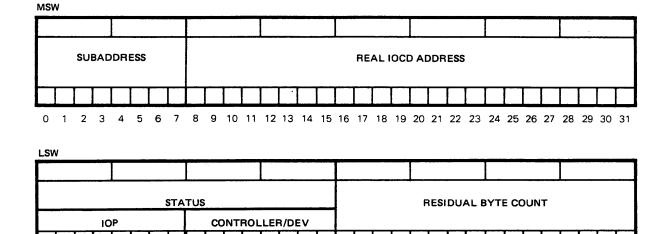

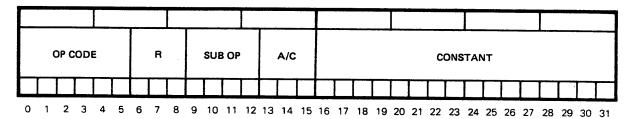

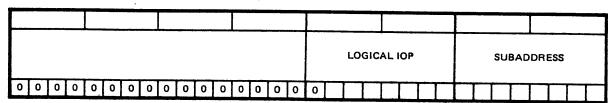

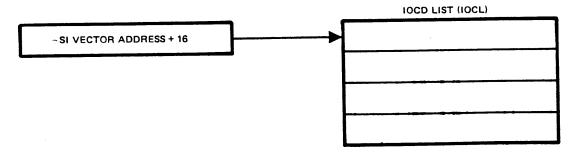

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8 | State Indicator Output-Read GPR or Base Registers State Indicator Format State Indicator Pairs State Indicator Output Pattern GPR Output Pattern GPR Output Display Operator Error Output Pattern Operator Error Message Format SCP Prompt Format Extended I/O Software Structure Basic Components of a Computer System IOCLA Format IOCD Format I/O Status Words Format Device End Command Actions Command Code for the Seven Command Instructions Interrupt Level, Service Interrupt Location, and Parameter List Relationships Simplifies Block Diagram - RTOM Function | 3-3<br>3-5<br>3-6<br>3-6<br>3-6<br>3-6<br>3-6<br>4-2<br>4-7<br>4-10<br>4-25<br>4-29 |

|                                                                                                                     | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                     |

| 1-1<br>3-1<br>3-2<br>5-1                                                                                            | Physical Address Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-4<br>3-9                                                                          |

#### CHAPTER 1

#### GENERAL INFORMATION

#### 1.1 Introduction

This User Reference Manual has been designed to familiarize the operator/user with the configuration conditions, operational characteristics, software programming considerations, and other special aspects of the Model 8000, 8001 Input/Output Processor (IOP) and the IPU Console IOP. They are designed and manufactured by Gould Inc., S.E.L. Computer Systems Division, Fort Lauderdale, Florida.

The primary supporting documents for this user reference manual are the IOP Technical Manual, publication number 303-000170, the IOP User Interface Manual, publication number 310-000890, and the IOP and I/O Expansion Chassis Drawings Manual, publication number 304-000170.

The information contained in this user reference manual is presented in the following order:

Chapter ! - General Information

Chapter ? - Configuration Information

Chapter 3 - Operation

Chapter 4 - Software Programming

Chapter 5 - IOP Real-Time Option Module (RTOM)

In this manual, all references to IOP are applicable to IOP Models 8000, 8001, and IPU Console IOP, except that clock override and IPL panel functions are not supported by the IPU Console IOP.

An input/output processor (IOP) is an I/O multiplexing channel consisting of the following interrelated elements: a SelBUS interface, a multipurpose bus (MPB) interface, the IOP proper, and system control panel (SCP) device dependent logic. The SelBUS interface provides the communications path between the IOP and the CPU, or the IOP and memory. The IOP proper has a control memory that contains the microprogram (firmware) for controlling the SelBUS and MPB interfaces. The IOP circuits consist of control logic for operating the MPB, the SCP interface, and the receiver/drivers necessary to communicate with the MPB controllers.

The IPU Console IOP is part of the IPU Console option (Model 3615). The IPU Console option consists of an alphanumeric CRT, the IPU Console IOP board, and cabling. The primary function of the IPU Console option is to provide an IPU with panel functions. It provides all the panel functions except initial program load (IPL) and clock override. It should be noted that the IPU Console is dedicated for operation with an IPU and cannot be accessed by the CPU. This option is not available for all systems with an IPU.

#### Note

The IPU Console IOP board is not interchangeable with the IOP Models 8000 and 8001.

#### 1.2 Product Description

The IOP is an I/O multiplexing channel, which also includes the functions of a real-time option module (RTOM), system control panel (SCP), and operator console device. These functions all share the same SelBUS interface and microprocessor. The controllers of the IOP are implemented on 12.5 by 15 inch boards. These boards plug into the MPB slot of a split backplane or an I/O expansion chassis. Using this type of board connection, high packing density can be achieved.

The IOP is implemented using 2901 slice processors. This processor and its tri-state bus allows shared processing, for all of the functions and power to control the four interfaces resident on the IOP.

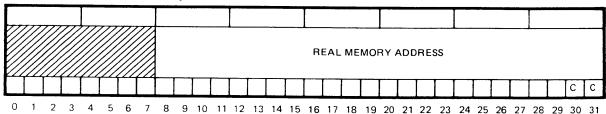

The SelBUS interface is a dual bidirectional interface used for memory and CPU communications. It utilizes two physical addresses on the SelBUS and allows for simultaneous data and command transfers from memory and the CPU respectively. It can also be used for two simultaneous data transfers from memory. This operation increases system throughput by allowing the IOP to prefetch the next Input/Output Command Doubleword (IOCD) during a data-chained operation.

Both the master and slave console ports are identical and have RS-232C and current loop interfaces. Data is formatted and outputted to the cathode ray tube (CRT) terminal in a serial manner. Switching between SCP and operator console modes is achieved using specific commands that are entered into the operator console, via the CRT terminal. Anytime that the system halts, the CRT terminal automatically switches to the SCP mode, the current program status word (PSW) and machine states are outputted. Outputting data in the serial format allows the serial ports to be used for CRT or hard copy SR43 device.

The slave monitor/initial program load (IPL) interface supports a full-duplex RS-232C modem interface. This port may be used locally or through a modem control, monitor, or IPL the system. This action allows maximum flexibility for the master or slave user to exercise the system. Since the IOP may also be the system control panel, macrodiagnostics or software programs may also be loaded and executed using this port. The slave port is activated by the master port so that the slave port can operate in the SCP mode. A command is provided to return control to only the master port. This action provides system protection from the slave user. The IPU Console IOP does not support IPL.

The IOP MPB interface provides a type of first-in, first-out (FIFO) buffering of the data, allowing the IOP microengine time to perform RTOM or SCP functions during a high-speed (1.5-2.0M bytes/sec) burst mode transfer. The MPB protocol allows easy implementation and low cost bus interfaces on each of the 16 possible controllers. Each of the controllers may operate up to 16 separate devices; however, a total of 124 devices are allowed on any one MPB. Multiple IOPs may be used to expand the number of controller devices. Grab controller and IOP to IOP communications are not allowed on the MPB.

#### 1.3 Functional Description

The IOP implements both the SCP and operator console functions in an interleaved manner. These two functions are available to I/O devices at each of the two ports on the IOP.

One port, the master port, is designated for the support of a master device such as a CRT terminal, teletypewriter (TTY), or full-duplex modem.

The other port, the slave port, also supports a complete set of control lines to interface with an asynchronous modem. Using this modem line interface it is possible to perform SCP and operator console functions from a slave I/O device.

In the operator console mode, the displays on each of the CRT terminals (master and slave), are independent and under software control. In the SCP mode, both the master and slave RT terminals display SCP data, unless the slave CRT terminal is deactivated by the system control panel command (PRIP). Activation of the slave CRT terminal causes both the master and slave CRT terminals to display identical information. However, only one mode or the other can be activated at any one time. Automatic switching, form the SCP mode to the operator console mode, occurs when the run command is entered into the SCP. CPU transitions from run to halt cause the CRT terminal to be switched to the SCP mode and current data outputted to the display.

When both terminals are active in the SCP mode they operate in the echo mode. That is, when a character is inputted on a CRT, it is stored by the firmware and then sent to each of the ports. As each CRT receives the eched character it is displayed on the screen. Since the character is echoed to both ports, characters inputted on one terminal appear on both terminals.

If one operator begins to input a message and the other operator inputs a character, the two characters appear sequentially on the screen. Thus the command will be rejected as being incorrectly inputted.

The master and slave ports use a universal synchronous/asynchronous receiver/transmitter (USART) integrated circuit to handle the asynchronous formatting.

The master and slave ports have a choice of RS-232C or current loop interface. Both ports support full-duplex modem controls.

The ports have a set of jumpers to determine operating characteristics. These jumpers are read during the powerup system reset routine and used to initialize the USART. The master and slave ports each have four jumpers dedicated to the selection of baud rate. Note that if only one port is in use, the baud rate for the other port should be set at the same or higher baud rate. This action is necessary, when the IOP is in the SCP mode, because the firmware will attempt to echo (send information) to both ports. A low baud rate on the unused port causes the active port to slow down to the slower baud rate.

An eight-bit American Standard Code for Information Interchange (ASCII) code, with no parity (most-significant bit equal to zero) can be jumper selected into the USART, thus allowing eight-bit binary data to be inputted through the ports. A seven-bit ASCII code, with even parity, allows mechanical TTY terminals to be used.

The SCP, implemented on the IOP, supports the IPL function. The two commands relating to the IPL function are as follows:

IPL IPL device is at default address IPL=XXXX IPL device is at address XXXX

The IPL device may be connected to the SelBUS locally on the MPB, connected to the master terminal port of the IOP, connected to the slave port, or connected at a distance over a modem line to one of the two ports.

Input of one of the IPL commands, given above, causes the IOP firmware to notify the CPU to initiate its IPL routine. This routine sets up an IOCD at memory address 0000 with the command chain and suppress incorrect length flags set. The IOCD calls for a binary read of 120 bytes, beginning at memory address 0000. The CPU performs an initial load RAM with a dummy interrupt level, to communicate with the SCP. A command is then sent to the addressed device to start I/O. The initial records read from the IPL device, writes a predetermined program status doubleword (PSD), beginning at memory address 0000 followed by the necessary number of chained IOCD's to enable loading of the entire IPL block. The PSD indicates where the software control should go at the end of the IPL sequence.

The IPL function is treated as a read operation by the IOP, except for notification of the CPU to intiate the IPL firmware sequence. The IPU Console IOP does not support IPL.

#### 1.4 IPU Console IOP Differences

The differences between the IPU Console IOP and other IOP's are listed below and then mentioned wherever applicable throughout this manual. These differences are as follows:

- 1. The IPL panel function is not available on the IPU Console IOP.

- 2. The clock override function is not supported by the IPU Console IOP.

- 3. The I/O classes associated with an IPU Console IOP have different designations than the standard I/O classes although they are identical in function. The I/O classes for the IPU Console IOP and the corresponding standard I/O class are listed as follows:

| IPU Console IOP Class | Corresponding<br>Standard I/O<br>Class |

|-----------------------|----------------------------------------|

| 7<br>В                | F<br>3<br>E                            |

4. The physical address settings for the panel and RTOM functions are different for an IPU Console IOP. They are defined in Table 1-1.

Table 1-1. Physical Address Settings

|      | Physical Address |                 |

|------|------------------|-----------------|

|      | Standard IOP     | IPU Console IOP |

| RTOM | 7F               | 73              |

| SCP  | 7E               | 72              |

|      |                  |                 |

#### **CHAPTER 2**

#### **CONFIGURATION INFORMATION**

#### 2.1 Software

The real-time option module (RTOM) and system control panel (SCP) functions are implemented using the SelBUS protocol that is defined in the IOP Technical Manual, publication number 303-000170. The multipurpose bus (MPB) uses a subset of extended I/O protocol as it is defined in Chapter 3 of this manual. The serial ports on the IOP are treated as subaddresses FC-FF of the physical address of the IOP. FC and FE are input addresses. FD and FF are output addresses.

#### 2.2 Hardware

A jumper is provided on the Input/Ouput Processor (IOP) to allow selection of the SCP function. The SCP cathode ray tube (CRT) ports may be selected to operate from 110 to 19.2K baud. The IOP contains two physical addresses on the SelBUS (an even and an odd pair).

The MPB is a medium speed asynchronous bus. The MPB protocol allows easy implementation, and low cost bus interfaces, for each of the 16 possible controllers. Each of the controllers may operate up to 16 separate devices; however, a total of 124 devices are allowed on any one MPB. Multiple IOPs may be used to expand the number of devices that are to be controlled.

The MPB is designed so that it may be contained in one computer cabinet. From 1 to 16 controllers can be connected to the MPB. The controllers that are used in a particular system can be distributed in any manner desired along the length of a controller backplane. The number of devices that can be connected to a controller is limited to 16.

The IOP is at one end of the MPB in a slot adjacent to the system's primary central processing unit (CPU), if the system contains more than one CPU. Note that the IOP must be located next to the system CPU if the IOP is to be used as the SCP. Termination resistors are provided on the MPB terminator board at the opposite end of the bus.

Maintaining the integrity of these requirements allows the MPB to vary in length using the necessary controller backplanes.

The MPB interconnect cable is a 50-pin flat cable consisting of 16 data lines, one parity line, three handshake lines, six control lines, and two clock lines.

#### **CHAPTER 3**

#### **OPERATION**

#### 3.1 General Information

The input/output processor (IOP) implements both the system control panel (SCP) and operator console functions in an intereaved manner. These two functions are available to I/O devices at each of the two ports on the IOP.

The local-remote ports will be known as master-slave ports. Both ports support a full-duplex modem control and two wire-20 mA current loop interface.

The master port is designated for the support of a master device such as a cathode ray tube (CRT) terminal, teletypewriter (TTY), or full-duplex modem. The master port can be used to select the slave port when it is required.

The slave port also supports a complete set of control lines to interface with an asynchronous modem. Using this modem line interface, it is possible to perform SCP and operator console functions from a slave I/O device.

In the operator console mode the displays on each of the CRT terminals, (master and slave), are independent and under software control. In the SCP mode, both the master and slave CRT terminals display SCP data, unless the slave CRT terminal is deactivated by the secondary panel (SECP) command. Activation of the slave CRT terminal causes both the master and slave CRT terminals to display identical information. However, only one mode or the other can be activated at any one time. Automatic switching, from the SCP mode to the operator console mode, occurs when the run command is entered into the SCP. CPU transitions from run to halt cause the CRT terminal to be switched to the SCP mode and current data outputted to the display.

#### 3.1.1 System Control Panel Mode

On powerup, baud rate jumpers are read and the appropriate baud rate selected. The ports come up in the SCP mode with a data terminal ready (DTR) indication. The DTR line remains on even if the ports are switched to the operator console mode, as long as a disconnect command has not been executed. Care should be exercised, with certain operator console modems, especially when a ring-in indication is expected to occur. These particular modems give a busy signal indication to an attempted ring-in condition whenever there is a DTR indication. Thus, the operator console port would never receive a ring-in indication and attention status would never be reported.

The system comes up with the SECP enabled (the slave port is also activated as a SCP). This action facilitates using the turnkey panel functions via the CRT terminal. Thus, reset and initial program load (IPL) commands can be executed after powerup.

In the SCP mode, the operator at the master port can input a primary panel (PRIP) command, thus preventing the slave port from being active and inputting commands. The SECP command returns the slave port to the SCP mode. This action allows the slave port to be active in the SCP mode. Note that the SECP and PRIP commands do not affect the operator console mode's operation.

When both terminals are active in the SCP mode they operate in the echo mode. That is, when a character is inputted on a CRT terminal, it it stored by the firmware and sent to each of the ports. As each CRT terminal receives the echoed character, it is displayed on the screen. Since the character is echoed to both ports, characters inputted on one terminal appear on both terminals.

If one operator begins to input a message and the other operator inputs a character, the two characters appear sequentially on the screen. This action serves as an indication that the master operator wishes to take control.

#### 3.1.2 Operator Console Mode

To change from the SCP mode to the operator console mode it is necessary for one of the CRT terminal operators to input @@C[CR]. Upon receipt of the CR command the firmware moves the cursor, on both CRT terminals, to the extreme left margin of the next line.

To return to the SCP mode, enter @@P[CR]. When the SCP mode is selected, // is used as the prompt so that a command can be entered on the CRT terminal. Operator console mode prompt messages are controlled by software.

When the run command is entered while the IOP is in the SCP mode the display is switched to the operator console mode where milestone messages may be outputted.

As the characters are inputted to the CRT terminal, operating in the operator console mode, they are sent to memory and the byte count is decremented. Software must determine when the message is complete so that the information can be decoded.

To exit the operator console mode and return to the SCP mode it is necessary for one of the CRT terminal operators to input QQP[CR]. SCP information is outputted and the cursors on both CRT terminals move to the extreme left. Operator console mode messages, that were currently on the screen, are left in the display. A run-halt transition also causes an automatic switch to the SCP mode. This action causes the program status word (PSW) to also be displayed.

If the CRT terminals are in the SCP mode and software has a message to output to the operator console, the firmware will accept an I/O command to an inactive subchannel, but will not perform the operation until it is in the operator console mode. Any subsequent commands to the subchannel will receive busy status.

#### 3.2 System Control Panel Controls and Indicator

There is no panel lock capability and no power switch associated with the SCP.

The SCP display of state indicators consists of one line, followed by the SCP prompt (//) at the extreme left of the line. The cursor is positioned immediately after the prompt so that operator commands can be inputted. This SCP display occurs in response to certain operator commands, system resets, or run-halt transitions. An alternative display, consisting of eight eight-bit hexadecimal character numbers, is outputted in response to an operator request to read the general purpose central processing unit (CPU) base registers. This output is also followed by the SCP prompt on the next line.

In response to an operator's request to read the general purpose registers (GPRs) or the base registers in the CPU, the SCP outputs one line with all eight registers shown. The display consists of eight eight-digit displays, side-by-side, beginning with register 0 at the left, through register 7 at the right. (See Figure 3-1). Note that NNNNNNNN is an eight-digit numeral field.

ининини инининин инининин инининин инининин инининин инининин

Figure 3-1. State Indicator Output-Read GPR Or Base Registers

For some commands the state indicators are not outputted. When this situation occurs, only the SCP prompt appears on the next line following the input command. The appearance of the prompt // always indicates to the operator, that the previously inputted command has been executed by the SCP. In the event of an error condition, such as a misspelling of a command by the operator, or the inputting of certain commands while the system is in the run mode, the words OPERATOR ERROR are outputted on the line following the command, and the SCP prompt appears on the next line. This indication signifies the readiness of the SCP to accept a new command. Note that the command that was in error will not be executed.

The display parameters are not dynamic (i.e. the indicated states are only true at the time they are outputted). However, an operator can readout current state indicators while the machine is in the run mode by inputting a command that will provide the states (i.e., a memory read command).

If a memory read is indicated by the operator command, and a nonpresent memory indication is sent to the SCP, a NON PRES MEM message appears after the command with the prompt appearing on the next line. If a SelBUS error has occurred in the course of executing an operator command, the words SELBUS ERROR appear followed by the prompt on the next line.

As commands are inputted and executed, they are outputted and scrolled on the screen.

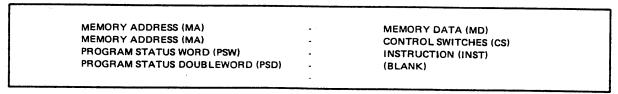

The format for the state indicators is shown in Figure 3-2.

Note that in Figure 3-2 all the alternatives for each field of the line are given. Only one of these fields will appear at any one time.

| MA NNNNNNN<br>PSW<br>PSD | IN MD NNNNNNNN<br>INST<br>EA<br>CS | OVR INT WAIT AS S<br>IS PI<br>RS<br>WS | T RUN<br>E HALT |

|--------------------------|------------------------------------|----------------------------------------|-----------------|

|--------------------------|------------------------------------|----------------------------------------|-----------------|

Figure 3-2. State Indicator Format

The state indicators are paired with other state indicators as shown in Figure 3-3.

Figure 3-3. Status Indicator Pairs

State indicators that are not present when the line is outputted are left blank. The information in the left half of the line, including the two number fields, reflects the information last obtained in response to certain operator commands. For example, if the operator inputs a clock override command, the corresponding change is shown in the appropriate space of the state indicators line; however, the number fields display the previous information that was in these fields. Table 3-1 defines the state indicators.

## Table 3-1 State Indicators

|   | AS CS EA HALT INST INT IS MA MD OVR PE PSD PSW RS RUN ST WAIT | Address stop set (all three stops set) Control switch settings is adjacent display (NNNNNNNN) Effective address in adjacent display (NNNNNNNN) CPU in halt mode Instruction in adjacent display (NNNNNN) Interrupt active Instruction stop set Memory address in adjacent display (NNNNNNNN) Memory data in adjacent display (NNNNNNNN) Clock override on Parity error from memory Program status doubleword in adjacent two displays (NNNNNNNN NNNNNNNN) Program status word 1 in adjacent display (NNNNNNNN) Operand read stop set CPU in run mode Stop (one of the address stop criteria has been met) Instruction execution not in progress |

|---|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | -                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | WS                                                            | Operand write stop set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1 |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Note: Setting of any address stop causes the disable CACHE line to be set on the turnkey panel cable. Resetting the address stop causes the disable CACHE line.

The IOP binary data pattern is shown in the following figures. The state indicators give various number fields and indications. The output pattern of the state indicators is shown in Figure 3-4.

Following the final CR LF indication, either a slash slash (reverse slash, ASCII '2F', for the SCP prompt) or a software message may occur if the system switches to the operator console mode.

The GPR registers display the contents of the general purpose registers. The output pattern of the GPR registers is shown in Figure 3-5.

The GPR readout display is shown in Figure 3-6.

The operator error message is given in response to an incorrectly entered SCP command. The output pattern for the operator error message is shown in Figure 3-7.

The output on the CRT is shown in Figure 3-8.

```

[LF] [NUL]

[NUL]

[NUL]

[CR]

[SP]

MA

or,

PSW

or,

PSD

or,

[SP]

[SP]

[SP]

[SP]

[SP]

NNNNNNN

or,

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

MD

or,

INST

or,

EΑ

[SP]

[SP]

or,

[SP]

[SP]

CS

or,

[SP]

[SP]

[SP]

NNNNNNN

or,

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

OVR

or,

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

INT

or,

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

WAIT

or,

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

AS

or,

IS

or,

RS

or,

WS

or,

[SP]

[SP]

[SP]

[SP]

[SP]

ST

or,

PE

or,

[SP]

[SP]

[SP]

[SP]

[SP]

[SP]

RUN

or,

HALT

[NUL]

[NUL]

[CR] [LF] [NUL]

[NUL]

```

Notes: [SP] = Space, [LF] = Line Feed, [CR] = Carriage returns, NNNNNNNN = an eight-digit numeral field, [NUL] = a Nul character (needed to give time for a [CR] to occur when operating the mechanical Teletypewriter (TTY) carriages).

Figure 3-4. State Indicator Output Pattern

```

RRRRRRRR

[SP]

[CR] [LF] [NUL] [NUL] [NUL]

```

Figure 3-5. GPR Output Pattern

Figure 3-6. GPR Output Display

```

[CR] [LF] [NUL] [NUL] [NUL]

OPERATOR

[SP]

ERROR

[CR] [LF] [NUL] [NUL] [NUL]

//

```

Figure 3-7. Operator Error Output Pattern

OPERATOR ERROR

Figure 3-8. Operator Error Message Format

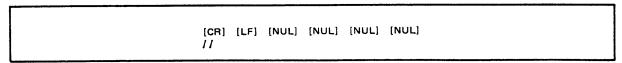

The SCP prompt message indicates that the SCP is ready to receive a new command. The output on the CRT is shown in Figure 3-9.

Figure 3-9. SCP Prompt Format

#### 3.3 System Control Panel Command

Table 3-2 contains the alphabetical list of commands for the SCP. Note that a carriage return (CR) is required after each command. Lock on and lock off commands are not supported by the CRT panel.

The following commands will not be executed and an operator error indication displayed if the CPU is not in the halt mode.

```

CRMA=XXXX

CRMD=XXXXXXXXXXXXX

CLE

EΑ

EXEC

GPR

GPRA=XXXXXXXX

IPL

PL=XXXX

MAV=XXXXXX

PC=XXXXXX

PSD

PSD=XXXXXXXX

PSW

PSW=XXXXXXXX

STEP

RST

```

Note that XXXXXXXX indicates a hexadecimal number field.

When the SCPs are active, they operate in the echo mode. In the echo mode, each character inputted from the CRT is stored in a buffer and echoed (sent) to both terminals. Upon receiving a CR command, the firmware decodes the input characters and executes the command. The display is updated after certain commands are executed. After all the commands are executed and applicable characters displayed, the SCP prompt (//) is outputted. This action indicates, to the operator(s), that this particular command has been executed. If the particular command cannot be executed, an abbreviated error message is outputted on the line following the command.

During the execution of some commands, all states are checked and the display updated. The cursor appears at the extreme left margin to the right of the prompt message (//).

The memory must be cleared (set to zero) before an IPL operation can be performed. To clear memory the clear (CLE) command is used. This command causes zeros to be written into all of the memory locations. After the powerup procedure is completed the CLE command also clears any parity errors. When the memory has been cleared, the // indication appears on the CRT terminal.

Note that in all of the SCP commands, XXXXXX indicates a hexidecimal number field. These number fields are right justified. For example, if an eight-digit field is required and the operator only inputs five characters before the carriage return, these five characters are considered to be the least-significant characters. The most-significant characters are assumed to be zeros. If the operator inputs more than the number of digits required for a particular command, only the last digits that fit into the command field are used.

## 3.3.1 Attention (@@A [CR])

Inputting @@A[CR] while the system is in the operator console mode causes an attention interrupt to occur. Inputting @@A[CR] while the system is in the SCP mode causes an operator error indication to occur with no interrupt.

## 3.3.2 Enter Console Mode (@@C [CR])

The @@C[CR] command causes an immediate switch to the operator console mode.

## 3.3.3 Enter Panel Mode (@@P [CR])

When in the operator console mode the QQP[CR] command causes the ports to switch to the SCP mode and output the SCP prompt //.

#### 3.3.4 Address Stop Commands

The address stop commands (AS[CR], AS=XXXXXXXX[CR], IS[CR], IS=XXXXXXXX[CR], RS [CR], RS=XXXXXXXXX[CR], WS [CR], and WS=XXXXXXXXX [CR]) set and reset the address stop conditions. An AS, IS, RS, or WS output indicates that a specific address stop condition has been set up. These conditions correspond to address stop, instruction stop, operand read stop, and operand write stop respectively. An instruction read stop command causes the CPU to halt and output ST only when an instruction fetch occurs at an address that was previously loaded into the address compare register. Operand read and write stop commands cause the CPU to halt if a read or write occurs at the address previously loaded into the address compare register. ST is outputted to the CRT with every CPU halt condition. All address stop conditions cause the CPU to halt and output ST to the CRT terminal.

The IS [CR] command only relates to an address stop on an instruction fetch operation. The RS [CR] command only relates to an address stop on a read operand operation. The WS [CR] command relates to an address stop on a write operand operation. The AS [CR] command relates to all of the above conditions.

To set an address stop condition, the operator must decide which type of address stop command to use. The appropriate command is then inputted with XXXXXXXX being the actual program stop address. Inputting AS, IS, RS, or WS, followed immediately by a [CR], clears the address stop command. Memory address C bits are ignored and truncated by the SCP. Note that when an address match occurs a stop condition also occurs. When this condition occurs, the address stop condition is not cleared. If that address should occur again, on the address bus, the CPU would halt. Also note that it is not possible to set up a general address stop condition (AS=XXXXXXXXX[CR]) and then clear only a particular stop condition (i.e., IS[CR]) without clearing all address stops. Then an address stop condition has been set up, either AS, RS, IS or WS appears in the CRT display field. The actual stop condition is indicated by ST in the CRT display.

## 3.3.5 Clear Memory (CLE[CR])

The CLE[CR] command clears memory, starting at address 0000 and continuing until the end of the first contiguous block of memory addresses. The end of this operation is signalled by the SCP prompt (//). The purpose of this command is to clear parity errors so that the IPL operation can be performed.

# Table 3-2. Alphabetical List of SCP Commands

| @@A @@C @@P AS[CR] AS=XXXXXXXX[CR] CLE[CR] [CONTROL][H] CRMA=XXXX[CR] CRMD=XXXXXXXXXX[CR] CS[CR] CS=XXXXXXXXXXX[CR] EA[CR] EXEC [CR] GPR [CR] GPR [CR] IPL[CR] IPL[CR] IPL=XXXX[CR] IS[CR] IS=XXXXXXXXX[CR] E[CR] MA=XXXXXX[CR] E[CR] MA=XXXXXX[CR] E[CR] MD=XXXXXXX[CR] E[CR] MD=XXXXXXX[CR] E[CR] MSG[CR] OVR[CR] PC=XXXXXXX[CR] PSD[CR] PSD=XXXXXXXX[CR] PSD[CR] PSD=XXXXXXXX[CR] RS[CR] RS[CR] RS=XXXXXXXXX[CR] RS[CR] RS=XXXXXXXXX[CR] RS[CR] RS=XXXXXXXXXX[CR] RS[CR] RS=XXXXXXXXX[CR] RST[CR] RST[CR] SECP[CR] STEP[CR] STEP[CR] STEP[CR] =[CR] WS[CR] WS=XXXXXXXX[CR] | *** Load CRAM with data and increment address Read control switches Set control switches Read effective address Execute CRAM Read general purpose registers Write general purpose register A Halt IPL from default address IPL from XXXX Clear instruction stop Set instruction stop Repeat command (except RST) Read physical memory address location *** Increment and read memory address Read virtual memory address location *** Increment and read memory address Write memory data Increment and write previous data Message Toggle clock override Load program counter Set primary panel (master terminal only) Read program status doubleword (PSD1) Write program status word (PSD1) Write program status word (PSD1) Clear read operand stop Set read operand stop Set secondary panel (master and slave terminals) Deletes entire command line (Hazeltine terminal only) Instruction step *** Instruction step Clear write operand stop Set write operand stop Set write operand stop |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| [CP] denotes carriage return following the command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| [CR] denotes carriage return following the command.  *** denotes a continuation of the current command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| denotes a constituation of the current commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## 3.3.6 Control RAM (CRAM) Memory Address (CRMA=XXXX[CR])

This command preaddresses the CRAM for a subsequent write into a CRAM location. The SCP prompt is the only output.

###

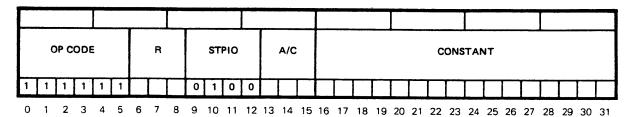

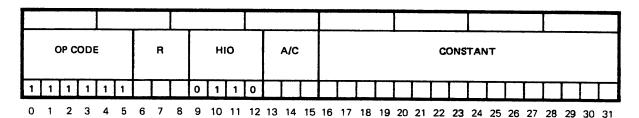

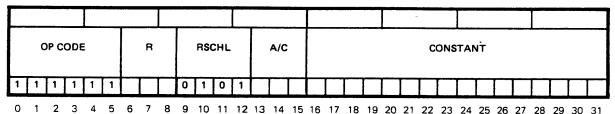

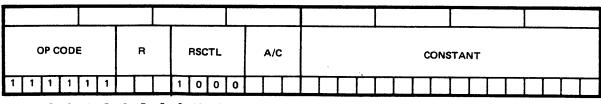

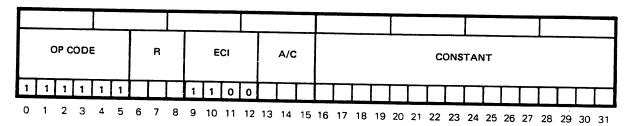

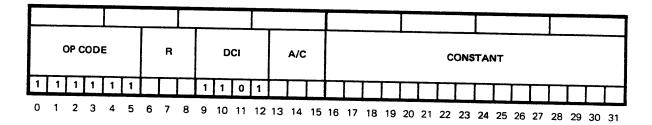

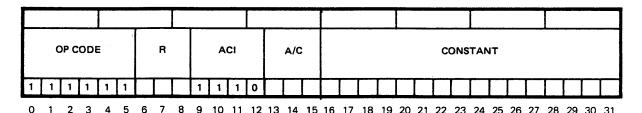

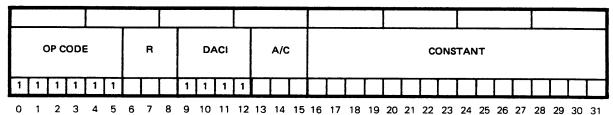

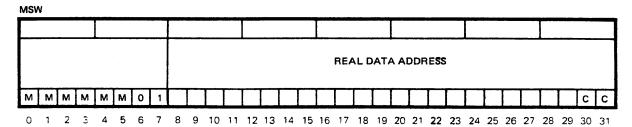

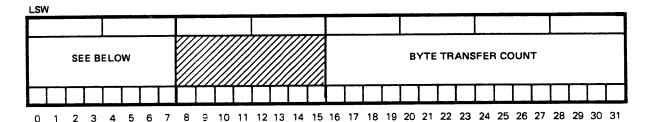

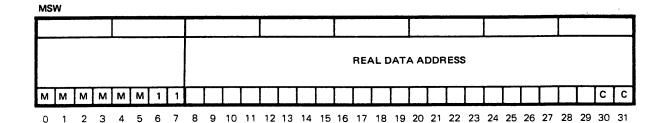

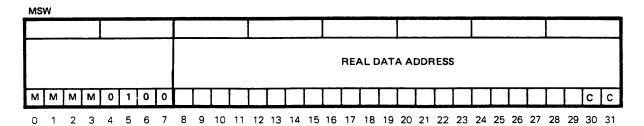

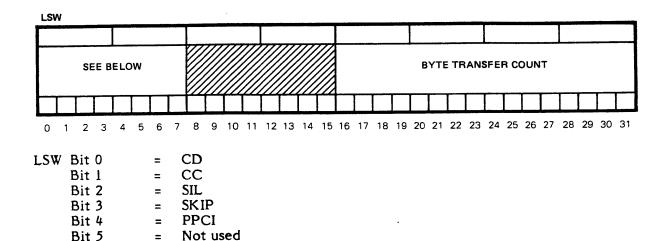

This command writes XXXXXXXXXXX into the CRAM memory address previously selected by the CRAM command. Note that there must be no intervening commands if the CRAM memory write command is to be executed. The SCP prompt is the only output.