## Gould CONCEPT/32

## Floating-Point Accelerator

Model 3611

Technical Manual

March 1983

Publication Order Number: 303-003020-000

This manual is supplied without representation or warranty of any kind. Gould Inc., S.E.L. Computer Systems Division therefore assumes no responsibility and shall have no liability of any kind arising from the supply or use of this publication or any material contained herein.

#### HISTORY

The Gould CONCEPT/32 Floating-Point Accelerator (Model 3611) Technical Manual, Publication Order Number 303-003020-000, was printed March, 1983.

This manual contains the following pages:

Title page Copyright page iii/iv through viii 1-1 through 1-16 2-1 through 2-52 A-1 through A-2 B-1 through B-6 IN-1 through IN-2

## CONTENTS

|   |     |          |                                          | Page                                    |

|---|-----|----------|------------------------------------------|-----------------------------------------|

| 1 | GEN | ERAL DES | CRIPTION                                 |                                         |

|   | 1.1 | Introdu  | ction                                    | 1 – 1                                   |

|   |     |          |                                          |                                         |

|   |     |          | isites                                   |                                         |

|   |     | •        | nt Description                           |                                         |

|   |     |          | nal Description                          |                                         |

|   | ,   | 1.5.1    | FPA File Registers                       |                                         |

|   |     | 1.5.2    | Instruction Formats                      |                                         |

|   |     | 1.5.3    | Operand Formats                          |                                         |

|   |     | 1.5.4    | Operand Entry                            |                                         |

|   |     | 1.5.5    | Input Register Loading                   |                                         |

|   |     | 1.5.6    | Arithmetic Operations                    |                                         |

|   |     | 1.5.7    | Result Normalizing and Rounding          |                                         |

|   |     | 1.5.8    | Result Storage                           |                                         |

|   |     | 1.5.9    | Arithmetic Exception                     |                                         |

|   |     | 1.5.10   | General Purpose Register Busy            |                                         |

|   |     | 1.5.11   | FPA Enable/Disable                       |                                         |

|   |     | 1.3.11   | THE MIGDIC, DIGGORD                      | • • • • • • • • • • • • • • • • • • • • |

| 2 | THE | ORY OF O | PERATION                                 |                                         |

|   |     |          |                                          |                                         |

|   | 2.1 |          | Subtract Unit                            |                                         |

|   |     | 2.1.1    | Floating-point File                      | 2-1                                     |

|   |     | 2.1.2    | Input Registers                          |                                         |

|   |     | 2.1.3    | Scaler                                   |                                         |

|   |     | 2.1.4    | Preadder                                 |                                         |

|   |     | 2.1.5    | Preshifters                              |                                         |

|   |     | 2.1.6    | ALU Sign and Overflow                    | 2-7                                     |

|   |     | 2.1.7    | Special Negative Number and Positive All |                                         |

|   |     |          | Zero Detector                            |                                         |

|   |     | 2.1.8    | Leading Ones and Leading Zeros Detector  |                                         |

|   |     | 2.1.9    | Exponent Corrector                       |                                         |

|   |     | 2.1.10   | Normalizer                               |                                         |

|   |     | 2.1.11   | Overflow and Rounding                    |                                         |

|   |     | 2.1.12   | Normalizer Error Corrector               | .2-11                                   |

|   |     | 2.1.13   | Output Registers                         |                                         |

|   |     | 2.1.14   | Destination Address Control              |                                         |

|   |     | 2.1.15   | Arithmetic Exception Register            |                                         |

|   |     | 2.1.16   | Clock and Microengine                    |                                         |

|   | 2.2 |          | and Divide Unit                          |                                         |

|   |     | 2.2.1    | Floating-point Multiply                  |                                         |

|   |     | 2.2.2    | Floating-point Divide                    |                                         |

|   |     | 2.2.3    | Fixed-point Multiplication               | 2-46                                    |

| Appendix | A - M/D Unit PROM Control Code Definitions | 1   |

|----------|--------------------------------------------|-----|

| Appendix | B - Connector Pin AssignmentsB-            | . 1 |

| Index    | IN-                                        | . 1 |

### **TABLES**

| Table | Page                                          |

|-------|-----------------------------------------------|

| 1-1   | Floating-point Accelerator Specifications1-4  |

| 2-1   | CREG Bits 36-392-5                            |

| 2-2   | Preadder Values2-7                            |

| 2-3   | AE Prediction2-7                              |

| 2-4   | ALU Control Lines2-7                          |

| 2-5   | Overflow State Diagram2-9                     |

| 2-6   | Output Register Contents2-18                  |

| 2-7   | Sequence Control PROM Map - MB84 and MB812-19 |

| 2-8   | Operation Decode2-20                          |

| 2-9   | Sequence Control PROM Coding -                |

|       | Multiply Floating-point Word2-20              |

| 2-10  | Active Sequence Control Signals -             |

|       | Multiply Floating-point Word2-21              |

| 2-11  | Sequence Control PROM Coding -                |

|       | Multiply Floating-point Doubleword2-21        |

| 2-12  | Active Sequence Control Signals -             |

|       | Multiply Floating-point Doubleword2-22        |

| 2-13  | AE Register Contents2-34                      |

|       | Output Register Contents2-36                  |

| 2-15  | Sequence Control SPROM Coding -               |

|       | Divide Floating-point Word2-47                |

| 2-16  | Active Sequence Control Signals -             |

|       | Divide Floating-point Word2-48                |

| 2-17  | Sequence Control PROM Coding -                |

|       | Divide Floating-point Doubleword2-49          |

| 2-18  | Active Sequence Control Signals -             |

|       | Divide Floating-point Doubleword2-50          |

|       | Fixed-point Answer Output2-52                 |

| 2-20  | Sequence Control PROM Coding -                |

|       | Fixed-point Multiply2-52                      |

| 2-21  | Active Sequence Control Signals -             |

|       | Fixed-point Multiply2-52                      |

|       |                                               |

| A-1   | MB84 PROM Control Code Definitions - M/D Unit |

| A-2   | MB81 PROM Control Code Definitions - M/D Unit |

| B-1   | Connector Jl Pin AssignmentsB-1               |

| B-2   | Connector J2 Pin AssignmentsB-1               |

| B-3   | Connector J3 Pin AssignmentsB-2               |

| B-4   | Connector J4 Pin AssignmentsB-2               |

| B-5   | Connector J5 Pin AssignmentsB-3               |

| B-6   | Connector J6 Pin AssignmentsB-3               |

| B-7   | Connector PlA Pin AssignmentsB-4              |

| B-8   | Connector PlC Pin AssignmentsB-4              |

| B-9   | Connector PlB Pin AssignmentsB-5              |

### **ILLUSTRATIONS**

| Figur | re                                                     | Page     |

|-------|--------------------------------------------------------|----------|

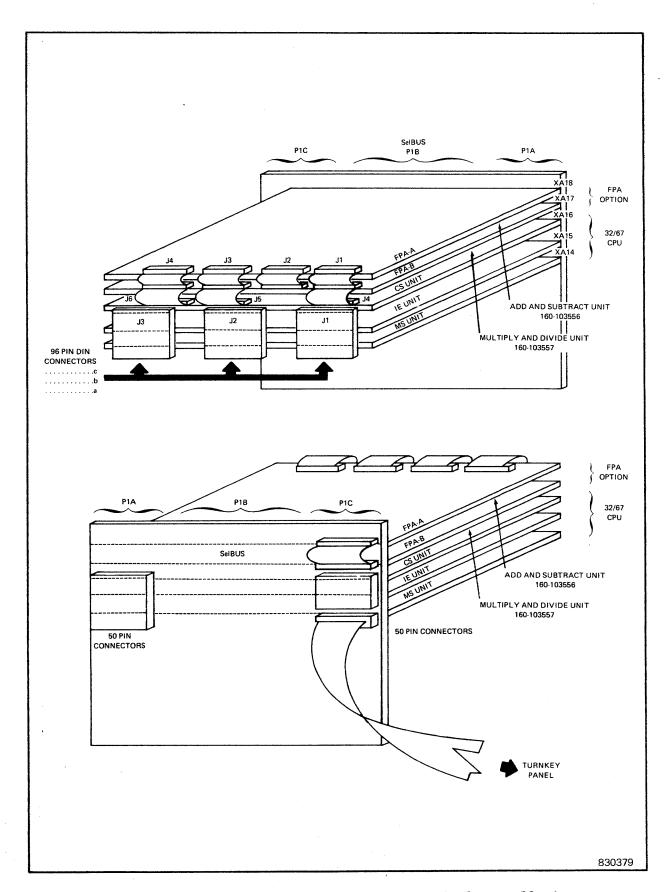

| 1-1   | Floating-point Accelerator Typical Installation        | 1-3      |

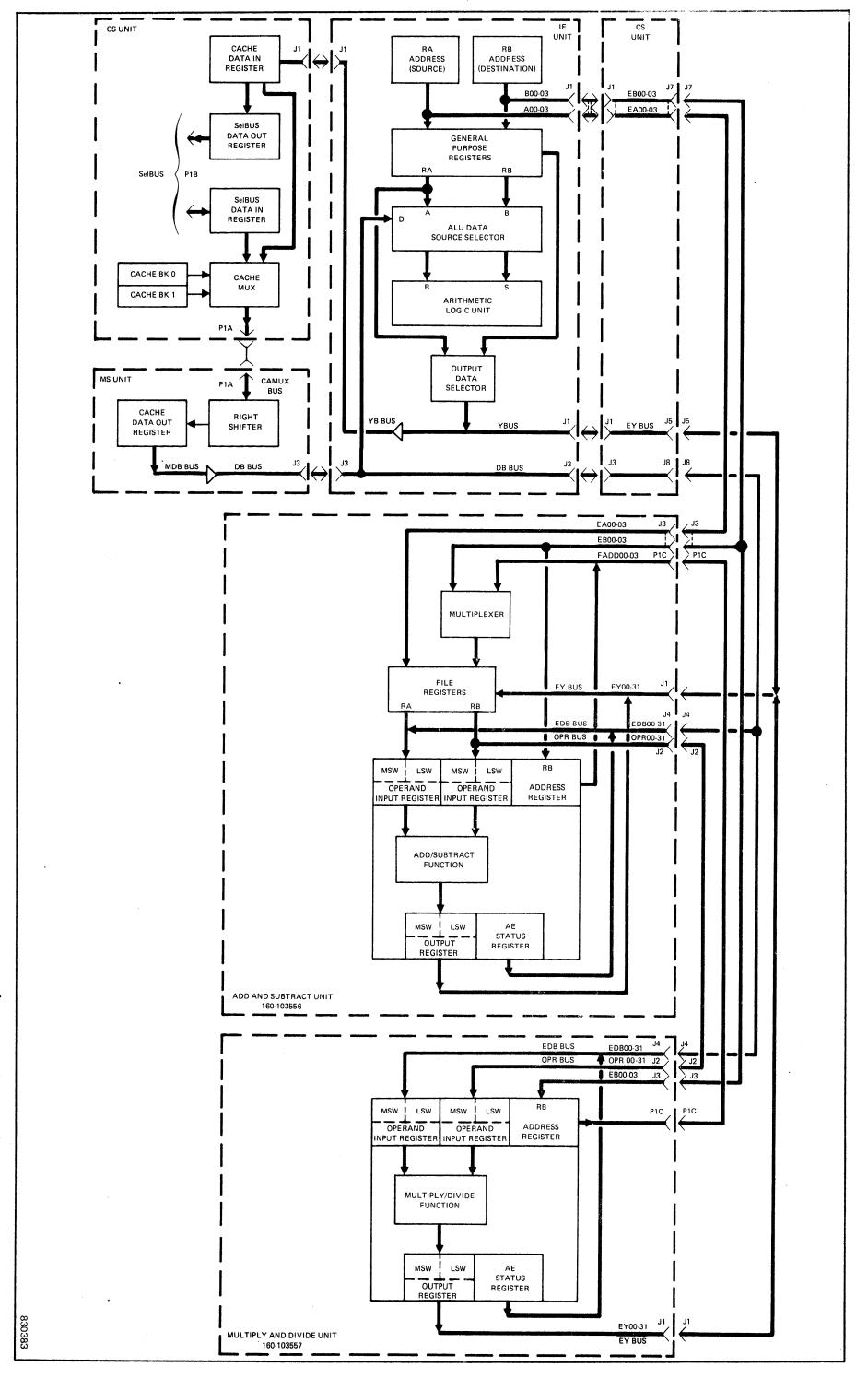

| 1-2   | FPA/CPU Simplified Block Diagram                       | 1-/      |

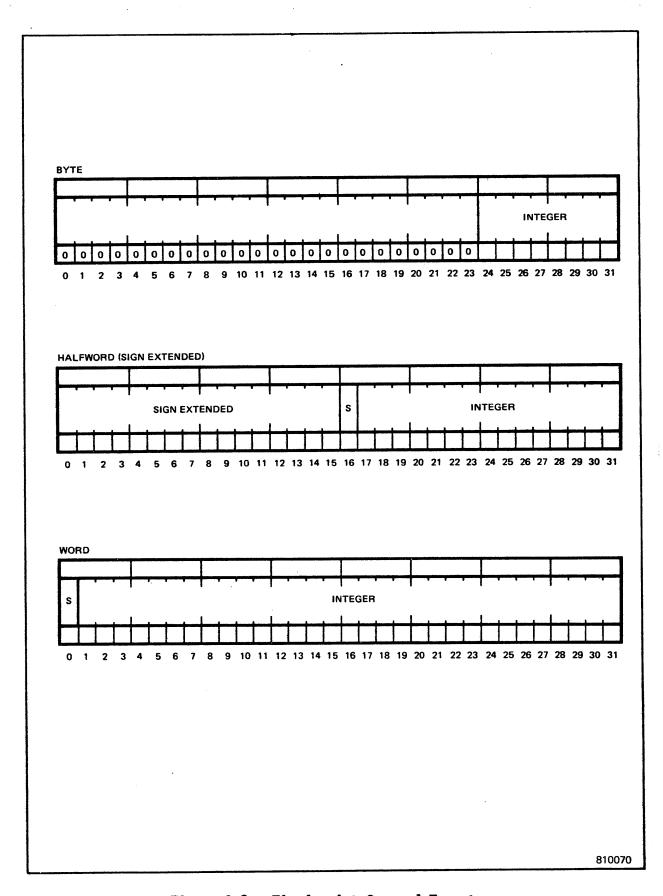

| 1-3   | Fixed-point Operand Formats                            | .1-10    |

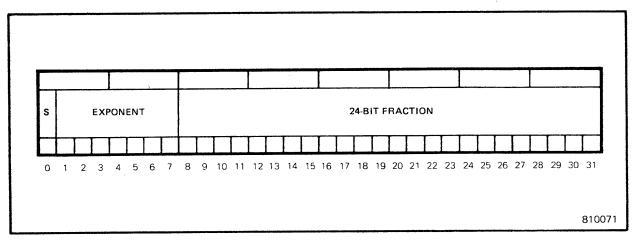

| 1-4   | Single-precision Floating-point Operand Format         | . i-11   |

| 1-5   | Double-precision Floating-point Operand Format         | .1-11    |

| 2-1   | Add and Subtract Unit - Block Diagram                  | 2-3      |

| 2-2   | Simplified Sign and Overflow Function                  | 2-9      |

| 2-3   | Status Word Format                                     | 2-13     |

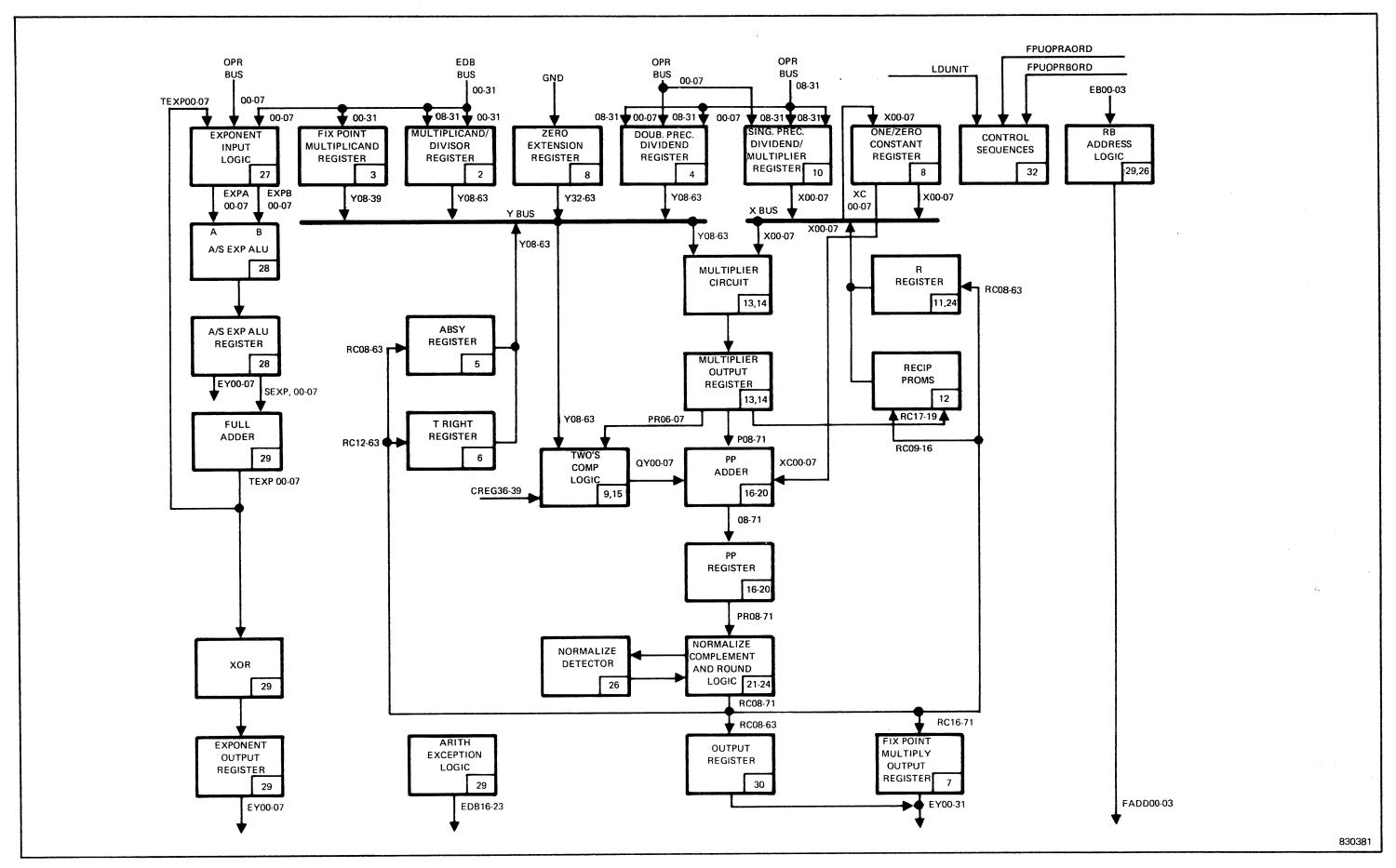

|       | Multiply and Divide Unit-Block Diagram                 | . 2-15   |

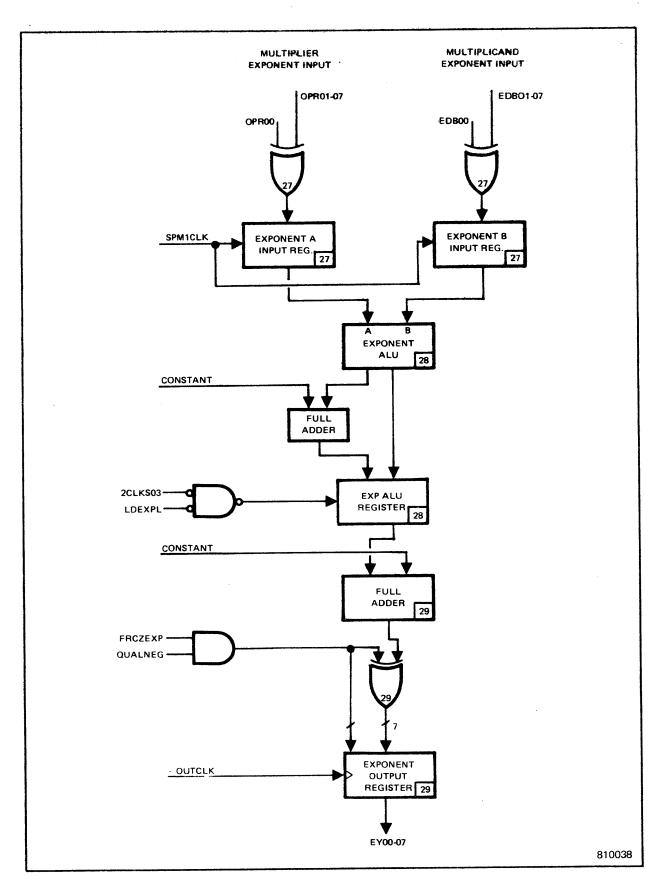

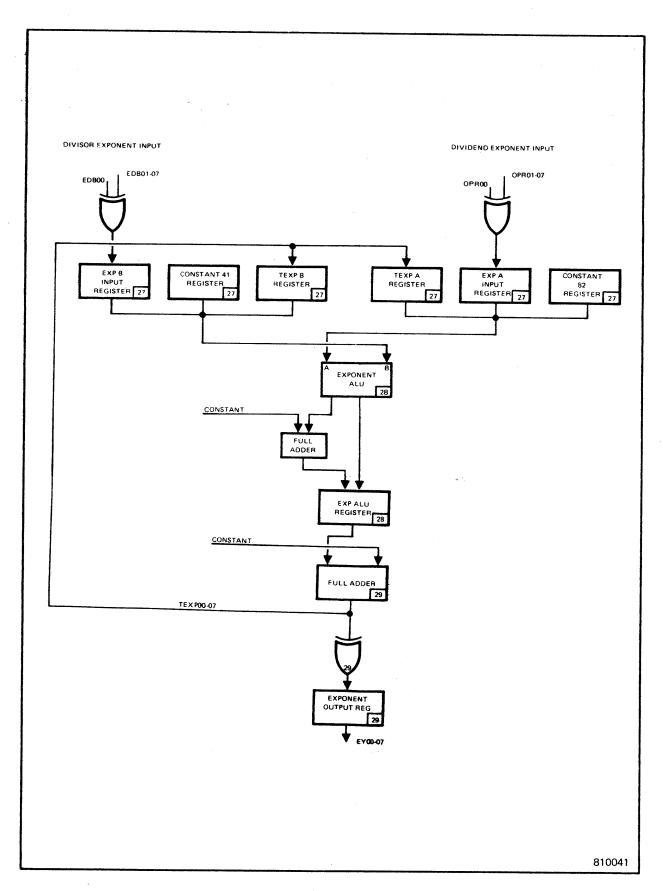

| 2-4   | Exponent Logic Block Diagram (Floating-point Multiply) | 2-24     |

| 2-5   | Exponent Logic Block Diagram (Floating-point Multiply) | 2-27     |

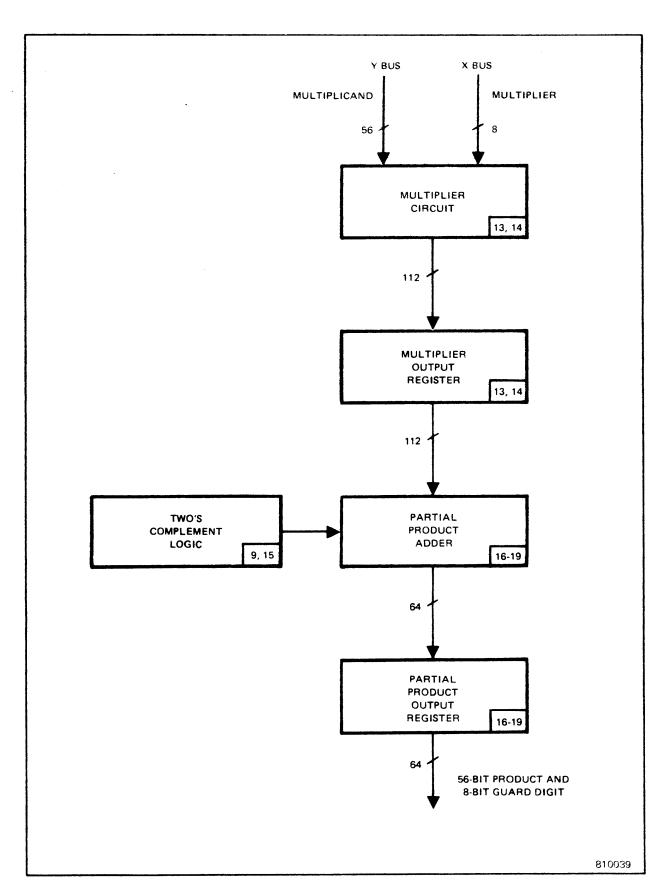

| 2-6   | Multiply Logic - Simplified Block Diagram              | 2_20     |

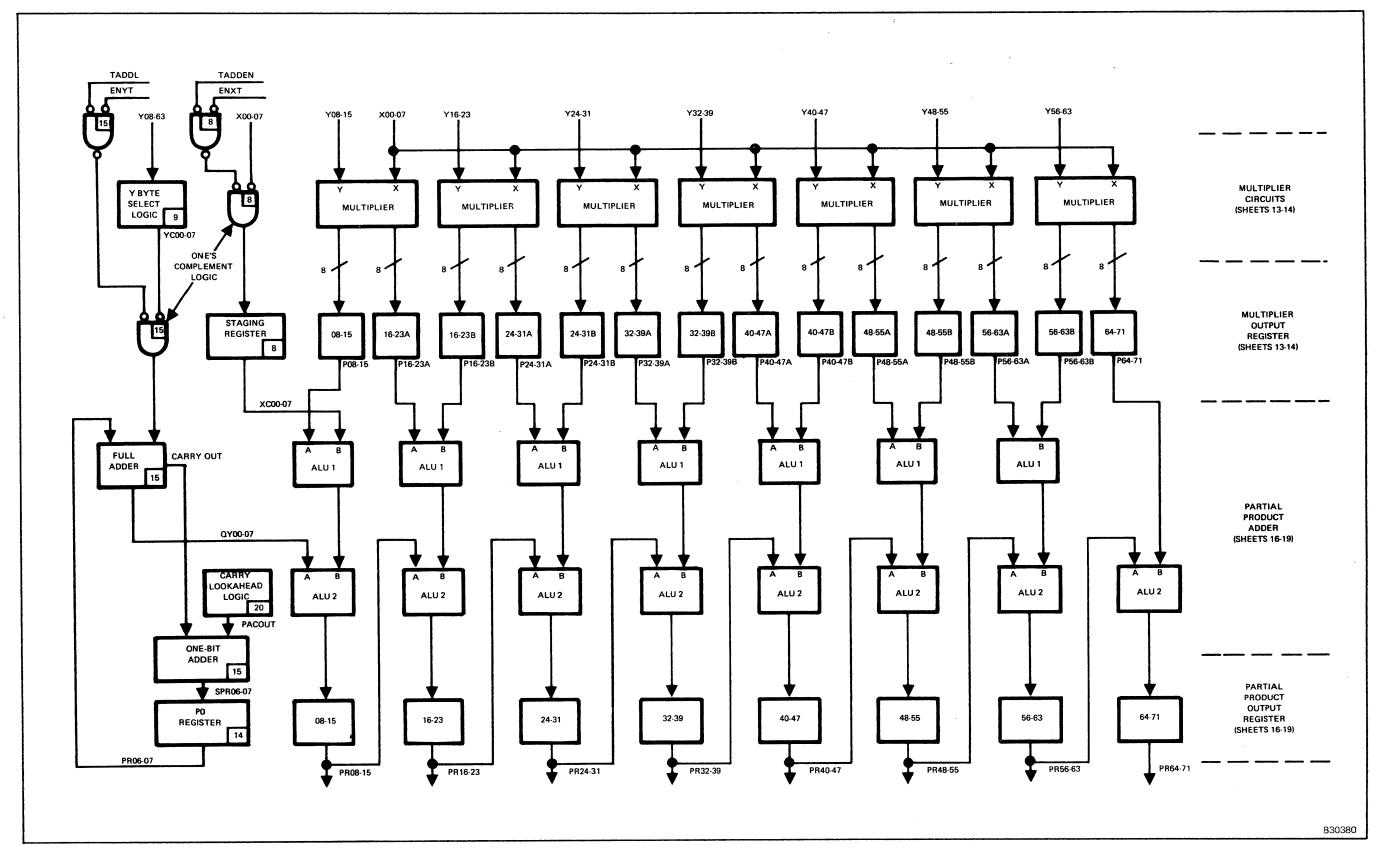

| 2-7   | Multiply Logic - Detailed Block Diagram                |          |

| 2-8   | Exponent Logic Block Diagram (Floating-point Divide)   | 2-41     |

| 2-9   | Single-precision Normalization and                     |          |

|       | Rounding Example                                       | 2-44     |

| 2-10  | Double-precision Normalization and Rounding Example    | • • 2-44 |

#### CHAPTER 1

#### GENERAL DESCRIPTION

#### 1.1 Introduction

The optional floating-point accelerator (FPA) is used by the central processing unit (CPU) to increase the speed of arithmetic operations.

In this manual, unless otherwise specified, the following conventions will apply:

- The term CPU refers to the CONCEPT 32/67 Central Processing Unit.

- The terms add and subtract unit, A/S unit and FPA A board refer to the 160-103556 Add and Subtract Unit.

- 3. The terms multiply and divide unit, M/D unit and FPA B board refer to the 160-103557 Multiply and Divide Unit.

#### 1.2 Purpose

The FPA performs floating-point addition, subtraction, multiplication, and division on single-precision (32-bit) and double-precision (64-bit) operands. The FPA also performs fixed-point multiplication.

The following floating-point arithmetic operations are supported by the FPA:

- 1. Add floating-point word

- 2. Add floating-point doubleword

- 3. Add floating-point word register to register

- 4. Add floating-point doubleword register to register

- 5. Subtract floating-point word

- 6. Subtract floating-point doubleword

- 7. Subtract floating-point word register to register

- 8. Subtract floating-point doubleword register to register

- 9. Multiply floating-point word

- 10. Multiply floating-point doubleword

- 11. Multiply floating-point word register to register

- 12. Multiply floating-point doubleword register to register

- 13. Divide floating-point word

- 15. Divide floating-point word register to register

- 16. Divide floating-point doubleword register to register

The following fixed-point arithmetic operations are supported by the FPA:

- 1. Multiply by memory byte

- 2. Multiply by memory halfword

- 3. Multiply by memory word

- 4. Multiply register by register

- 5. Multiply immediate

#### 1.3 Prerequisites

The FPA requires two SelBUS card slots immediately above, and adjacent to the CPU on a CONCEPT/32 chassis. A typical FPA installation is shown in Figure 1-1.

#### 1.4 Equipment Description

The FPA consists of two, 15 inch by 18.5 inch, logic boards. The add and subtract (A/S) unit performs all floating-point addition and subtraction operations. This unit also contains 16 file registers which are shared by both the multiply and divide unit and the add and subtract unit.

The file registers are used to store operands for the arithmetic operations and to store the results of the operations. The contents of the file registers are a copy of the contents of the general purpose registers in the CPU.

The multiply and divide (M/D) unit performs all floating-point multiplication and division operations and fixed-point multiplication operations. The results of multiply/divide operations are put away in the file registers in the A/S unit.

The two logic boards connect directly to the backplane SelBUS at connector PlB. The SelBUS provides the FPA with power, ground and clock connections only; the FPA does not communicate directly over the SelBUS.

The two-connector, 50 pin cable on the pin side of the backplane at PIC forms the file address (FADD) bus between the two floating-point units. This bus is used to address the file register for storing the arithmetic operation results.

The three-connector 50-pin cable at J1 forms the external Y (EY) bus between the two floating-point units and the CPU. This bus is used to carry 32-bit operands from the CPU, and arithmetic results from the M/D unit, to the file registers in the A/S unit.

The two-connector, 50 pin cable at J2 forms the operand (OPR) bus between the two floating-point units. This

bus carries 32-bit operands from the file registers in the A/S unit to the M/D unit.

The three-connector, 50 pin cable at J3 forms the external A (EA) bus between the A/S unit and the CPU, and the external B (EB) bus between the two floating-point units and the CPU. The EA bus carries A-port addresses from the CPU to the file registers in the A/S unit. The EB bus carries B-port addresses from the CPU to the file registers in the A/S unit, and the RB address registers in both floating-point units. The cable also carries control and test signals between the CPU and the FPA.

The three-connector, 50 pin cable at J4 forms the external buffered data (EDB) bus between the two floating-point units and the CPU. The bus carries the 32-bit memory operand to both floating-point units.

See Appendix B for detailed signal pin assignments for each connector.

Table 1-1 lists the physical, electrical, environmental, and operational specifications of the floating-point accelerator.

### 1.5 Functional Description

The following paragraphs describe the operations performed by the FPA and the different data formats used with the FPA. Figure 1-2 is a simplified functional block diagram of the FPA and its interaction with the CPU.

### 1.5.1 FPA File Registers

FPA file registers 0 through 7 are copies of the CPU (software) general purpose registers and are updated each time the CPU performs a write to the GPRs. All floating-point results are put away in the FPA file registers and the CPU will use the FPA copy of the GPRs for store in

Figure 1-1. Floating-point Accelerator Typical Installation

# Table 1-1 (Sheet 1 of 2) Floating-point Accelerator Specifications

| Characteristic                                                                       | Specification                                                                                                                                     |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| PHYSICAL                                                                             |                                                                                                                                                   |

| Number of PWB Length (each PWB) Width (each PWB) Weigh (total for boards and cables) | Two 18.5 inches (46.99 cm) 15.0 inches (38.10 cm) 8 pounds                                                                                        |

| ELECTRICAL                                                                           |                                                                                                                                                   |

| Voltage Current Unit A Unit B Power Unit A Unit B                                    | 5 vdc <u>+</u> 5%  18 amps 24 amps  90 watts 120 watts                                                                                            |

| Operating Temperature  Relative humidity Storage Temperature                         | +50 degrees to +100 degrees Fahrenheit (+10 degrees to +40 degrees Celsius) 5% to 95%  -40 degrees to +140 degrees Fahrenheit (-40 degrees to +60 |

| Relative humidity                                                                    | degrees Celsius)<br>2% to 95%                                                                                                                     |

# Table 1-1 (Sheet 2 of 2) Floating-point Accelerator Specifications

| Characteristic                                                                                                                                                                                                                                                                                                                                           | Specification                       |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|--|

| OPERATIONAL                                                                                                                                                                                                                                                                                                                                              |                                     |  |  |  |  |

| Instruction execution                                                                                                                                                                                                                                                                                                                                    |                                     |  |  |  |  |

| time (with 600-nanosecond                                                                                                                                                                                                                                                                                                                                |                                     |  |  |  |  |

| memory)                                                                                                                                                                                                                                                                                                                                                  |                                     |  |  |  |  |

| Floating-point instructions                                                                                                                                                                                                                                                                                                                              |                                     |  |  |  |  |

| Add word (ADFW)                                                                                                                                                                                                                                                                                                                                          | 0.90 microseconds                   |  |  |  |  |

| Add doubleword (ADFD)                                                                                                                                                                                                                                                                                                                                    | 1.50 microseconds                   |  |  |  |  |

| Add word register to register (ADRFW)                                                                                                                                                                                                                                                                                                                    | 1.05 microseconds                   |  |  |  |  |

| Add doubleword register to                                                                                                                                                                                                                                                                                                                               |                                     |  |  |  |  |

| register (ADRFD)                                                                                                                                                                                                                                                                                                                                         | 1.80 microseconds                   |  |  |  |  |

| Subtract word (SUFW)                                                                                                                                                                                                                                                                                                                                     | 0.90 microseconds                   |  |  |  |  |

| Subtract doubleword (SUFD)                                                                                                                                                                                                                                                                                                                               | 1.50 microseconds                   |  |  |  |  |

| Subtract word register to                                                                                                                                                                                                                                                                                                                                | 1                                   |  |  |  |  |

| register (SURFW)                                                                                                                                                                                                                                                                                                                                         | 1.05 microseconds                   |  |  |  |  |

| Subtract doubleword register                                                                                                                                                                                                                                                                                                                             |                                     |  |  |  |  |

| to register (SURFD)                                                                                                                                                                                                                                                                                                                                      | 1.80 microseconds                   |  |  |  |  |

| Multiply word (MPFW)                                                                                                                                                                                                                                                                                                                                     | 1.35 microseconds                   |  |  |  |  |

| Multiply doubleword (MPFD)                                                                                                                                                                                                                                                                                                                               | 2.55 microseconds                   |  |  |  |  |

| Multiply word register to                                                                                                                                                                                                                                                                                                                                |                                     |  |  |  |  |

| register (MPRFW)                                                                                                                                                                                                                                                                                                                                         | 1.50 microseconds                   |  |  |  |  |

| Multiply doubleword register                                                                                                                                                                                                                                                                                                                             |                                     |  |  |  |  |

| to register (MPRFD)                                                                                                                                                                                                                                                                                                                                      | 2.85 microseconds                   |  |  |  |  |

| Divide word (DVFW)                                                                                                                                                                                                                                                                                                                                       | 4.95 microseconds                   |  |  |  |  |

| Divide word (DVFD)                                                                                                                                                                                                                                                                                                                                       | 8.10 microseconds                   |  |  |  |  |

| Divide doubleword (DVFD)  Divide word register to                                                                                                                                                                                                                                                                                                        | 0.10 mrer occours                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                          | 5.10 microseconds                   |  |  |  |  |

| register (DVRFW)                                                                                                                                                                                                                                                                                                                                         | J.10 microseconas                   |  |  |  |  |

| Divide doubleword register                                                                                                                                                                                                                                                                                                                               | 8.40 microseconds                   |  |  |  |  |

| to register (DVRFD)                                                                                                                                                                                                                                                                                                                                      | 0.40 microseconds                   |  |  |  |  |

| Fixed-point instructions                                                                                                                                                                                                                                                                                                                                 | 1.95 microseconds                   |  |  |  |  |

| Multiply memory byte (MPMB)                                                                                                                                                                                                                                                                                                                              | 1.95 microseconds                   |  |  |  |  |

| Multiply memory halfword (MPMH)                                                                                                                                                                                                                                                                                                                          | 1.80 microseconds                   |  |  |  |  |

| Multiply memory word (MPMW)                                                                                                                                                                                                                                                                                                                              |                                     |  |  |  |  |

| Multiply register by register (MPR)                                                                                                                                                                                                                                                                                                                      | 1.95 microseconds 1.95 microseconds |  |  |  |  |

| Multiply immediate (MPI)                                                                                                                                                                                                                                                                                                                                 | 1.95 microsecolus                   |  |  |  |  |

| Note: Fixed-point multiply and floating-point add, subtract, and multiply operations will yield identical results when performed by either the FPA or the CPU firmware. However, the result of a floating-point divide operation performed by the FPA will be one bit more accurate than the result of the same operation performed by the CPU firmware. |                                     |  |  |  |  |

memory instructions. For CPU register modification instructions, the CPU will use the FPA copy of a register, or register pair in double precision, if a floating-point operation has been executed by the same register(s).

The remaining eight FPA file registers (8 through 15) may be used as work registers in writable control store (WCS) applications on a per process basis. The eight upper registers cannot be saved during CPU interrupt/trap context switching; however, they can be accessed by CPU microcode that is not a part of the standard microcode set.

## 1.5.1.1 Register Conflict Resolution

The CPU and FPA hardware resolves register conflicts between instructions such that, if a floating-point destination register is specified as a source register to a subsequent instruction, and the floating-point instruction is not complete, the CPU will pause and wait for the floating-point instruction to complete. The result of the floating-point operation is then used as the source operand to the subsequent instruction. The subsequent instruction may be a floating-point, fixed point, or logical instruction.

The register conflict hardware cannot resolve conflicts between pre- or post-indexing registers and floating-point target registers. If a floating-point register is specified as an indexing register to a subsequent instruction, and the floating-point instruction is not complete, the results will be indeterminate.

#### 1.5.2 Instruction Formats

An arithmetic instruction supported by the FPA will conform to one of

three different instruction formats: memory reference, interregister, and immediate. For detailed descriptions of these instruction formats, see the CPU Reference Manual.

## 1.5.2.1 Memory Reference Instruction Format

The memory reference instruction format causes the CPU to fetch one operand from memory and the other operand from a general purpose register. The results of the arithmetic operations are returned to the same general purpose register, overwriting the previously stored contents.

The memory reference format is used by the multiply by memory fixed-point instructions and all floating-point instructions other than the register to register type.

## 1.5.2.2 Interregister Instruction Format

The interregister instruction format causes the CPU to fetch one operand from a source general purpose register and the other operand from a destination general purpose register. The results of the arithmetic operations are returned to the destination general purpose register, overwriting the previously stored contents.

The interregister format is used by the multiply register by register fixed-point instruction and register to register floating-point instructions.

#### 1.5.2.3 Immediate Instruction Format

The immediate instruction format causes the CPU to fetch one operand from a general purpose register. The 16-bit operand portion of the instruction (bits 16 through 31) is sign-extended left, to form the other

32-bit operand, and sent to the FPA. The results of the arithmetic operation are returned to the same general purpose register, overwriting the previously stored contents.

The immediate format is used only by the multiply immediate fixed-point instruction.

#### 1.5.3 Operand Formats

The operands of the arithmetic operation must be stored in memory and/or the general purpose register(s) in the proper format. In addition, floating-point operands must also be normalized. The following paragraphs detail the various operand formats.

#### 1.5.3.1 Fixed-point Operand Formats

Figure 1-3 illustrates the formats for fixed-point operands received by the FPA.

The byte and halfword integers are right justified in a 32-bit word format; the most-significant portion of the byte and halfword operands are zero-filled and sign-extended, respectively. The alignment, zero-fill, and sign-extend functions are performed in the CPU after the operands are fetched from memory.

For every fixed-point multiply instruction executed, the FPA receives two 32-bit operands and returns a 64-bit (doubleword) answer.

## 1.5.3.2 Floating-point Operand Formats

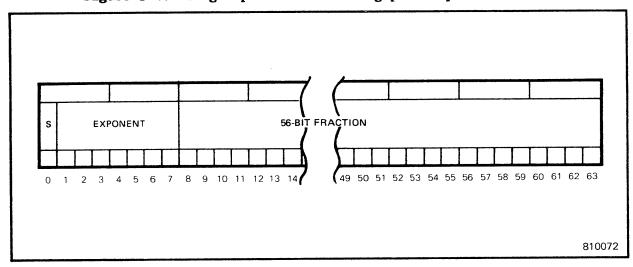

Figures 1-4 and 1-5 show the proper formats for the single- and double-precision floating-point operands. Both formats consist of a sign (S), an exponent, and a fraction. The sign bit (bit 0) represents the positive (0) or negative (1) value of the fraction. The exponent is a

seven-bit (bits 1 through 7) binary number and represents the power to the base 16 of the fraction. The exponent can either be a positive or negative value. The hexadecimal value of 40 represents an exponent of 0 to the base 16. Any hexadecimal value above 40 represents a positive exponent (i.e., hexadecimal of 41 represents the exponent value of positive 1 to the base 16) and any hexadecimal value below 40 represents a negative exponent (i.e., hexadecimal value of 3F represents the exponent value of negative 1 to the base 16).

The fraction is represented by 24 bits (bits 8 through 31) in a single-precision operand and by 56 bits (bits 8 through 63) in a double-precision operand. The radix point of the normalized, binary fraction is assumed to be to the immediate left of its most-significant bit.

When the sign bit represents a negative number, the biased magnitude of the exponent is stored in the one's complement form and the fraction in the two's complement form. Positive numbers are stored in the absolute value.

## 1.5.3.3 Normalized Floating-point Operands

The floating-point operand is considered to be normalized when the absolute value of the most-significant hexadecimal digit of the fraction contains a value less than one and greater than or equal to one-sixteenth. Hexadecimal fractions with magnitudes less than one-sixteenth must be normalized by left shifting the fraction and decrementing the exponent by one accordingly.

#### 1.5.4 Operand Entry

The floating-point accelerator receives single- and double-precision

Figure 1-3. Fixed-point Operand Formats

Figure 1-4. Single-precision Floating-point Operand Format

Figure 1-5. Double-precision Floating-point Operand Format

operands from memory and from a general purpose register. The addend of an addition operation, the subtrahend of a subtraction operation, the multiplicand of a multiplication operation, and the divisor of a division operation are stored in a memory location. The augend, minuend, multiplier and dividend are stored in a general purpose register.

#### 1.5.4.1 Memory Operands

Operands fetched from memory enter the data-in register of the CPU and are enabled onto the DB bus (bits DB00 through DB31). These bits are applied to both floating-point units, via the external DB (EDB) bus, through a cable at J4.

#### 1.5.4.2 File Register Operands

The CPU microword controls the loading of an operand from a general purpose register in the CPU, to a file register in the floating-point accelerator. The CPU microword sets up the arithmetic logic unit of the CPU to place the operand on the internal Y bus (bits YOO through Y31) and enables the external Y bus (bits EY00 through EY31) at J1. The EY bits are applied to the floatingpoint unit A by the cable at Jl. At the same time, the CPU microword activates the register B (RB) address (bits BOO through BO3) in which the operand is to be stored. The register B address is the location of the general purpose register which is designated as the destination

register. The register B address (bits EB00 through EB03) is applied to both floating-point units by a cable at J3. The operand is simultaneously stored in the general purpose register and the file register which has been addressed by the RB address.

Double-precision operands are loaded into two consecutive file register and general purpose register addresses.

#### 1.5.5 Input Register Loading

The CPU microword establishes which floating-point unit is enabled based on the arithmetic operation being performed. The A/S unit is enabled for the addition and subtraction operations and the M/D unit is enabled for the multiplication and division operations.

The RB address is stored in the RB address register of the enabled floating-point unit. The stored RB address is used for storing the results of the arithmetic operation.

#### 1.5.5.1 Single Precision

The input registers of the appropriate floating-point unit are loaded during the CPU memory fetch cycle. At the time the operand from memory is enabled onto the DB bus, the operand from the file registers is enabled onto the OPR bus (bits OPROO through OPR31). The CPU enables the input registers of the unit which is to perform the arithmetic computation, and both operands are loaded simultaneously into the most-significant word (MSW) position of the operand input registers.

The floating-point unit calculations are performed on 64-bit operands. During the loading of single-precision operands, the least-

significant word position is automatically zero extended.

#### 1.5.5.2 Double Precision

Double-precision operands are contained in two consecutive file register locations and memory locations. The most-significant word of the doubleword resides in the even address and the least-significant word resides in the odd address. least-significant words (LSW) of both the memory and register operands are loaded into the least-significant word positions. The CPU then fetches the most-significant operand from memory and simultaneously loads both words into the most-significant word positions of the operand input registers.

## 1.5.6 Arithmetic Operations

The operands are disassembled into their component parts (the sign, the exponent, and the fraction) by the floating-point accelerator prior to the arithmetic operation. Each of the component parts is manipulated and calculated independently. The results are reassembled prior to being stored in the floating-point accelerator file registers.

#### 1.5.6.1 Addition/Subtraction

The addition/subtraction operations are performed by the add and subtract unit. The addition/subtraction instructions cause the CPU microword to enable the input registers of the A/S unit, and the operands are loaded into the input registers as previously described. After the input registers are loaded, the addition or subtraction operation begins.

The exponents of the fractions are compared to each other to determine the smaller of the two. The fraction of the operand with the smaller exponent is shifted right and the exponent is incremented by one for each hexadecimal digit shifted until the two exponents are equalized. If the difference between the two exponents is greater than the maximum allowable difference (6 for singleprecision operands and 13 for doubleprecision operands), the smaller exponent and its fraction are considered insignificant compared to the larger exponent, and the fraction of the operand with the smaller exponent is forced to zero.

The fractions are algebraically added or subtracted and the resulting fraction is normalized or rounded.

The resulting sign, exponent and fraction are assembled and transferred to the output register of the add and subtract unit.

Since all fractional answers are automatically normalized by the A/S Unit, it is possible to use a floating-point add instruction (ADFW or ADFD) simply to normalize an operand. This can be done by adding the unnormalized operand to another operand with a zero value.

#### 1.5.6.2 Multiplication/Division

The multiplication/division operations are performed by the multiply and divide unit. The multiplication/division instructions cause the CPU microword to enable the input registers of the M/D unit and the operands are loaded into the input registers as previously described. After the input registers are loaded, the multiplication/division operation begins.

## 1.5.6.2.1 Multiplication

The floating-point accelerator executes both fixed-point and floating-point multiply instructions.

The multiply operation on the floating-point fraction (or fixedpoint integer) is performed using a multiple-clock operation where partial products are calculated and then added to the sum of all previous partial products. For singleprecision floating-point multiply operations, the summation of partial products may be normalized (if needed) or rounded. For doubleprecision floating-point multiply operations, only normalization may be performed (if needed), never rounding. In fixed-point operations, no normalization or rounding is performed.

The biased exponents of the floatingpoint fractions are algebraically added, and then 40 (hex) is subtracted from the sum. The result is the biased exponent of the answer.

Upon completion of the floating-point or fixed-point multiply, the result is transferred to the file register located on the A/S unit.

#### 1.5.6.2.2 Division

Division of the fraction is accomplished by first performing an algorithm using iterative multiplications to obtain the approximate reciprocal of the divisor and then multiplying the reciprocal by the dividend.

The exponent of the answer is derived by first calculating the exponent of the reciprocal and then adding this value to the exponent of the dividend.

The fraction answer is both normalized (if needed) and rounded. The corrected fraction answer, sign bit, and exponent are assembled and transferred to the file register located on the A/S unit.

## 1.5.7 Result Normalizing and Rounding

The following paragraphs describe the normalizing and rounding operations.

#### 1.5.7.1 Guard Digit

The guard digit is an additional hexadecimal digit of precision which is used in the normalizing and rounding processes of singleprecision arithmetic operations and double-precision division operations. The guard digit of these operations allows the results of the operations to be calculated with a precision of seven hexadecimal digits for single precision and 15 for double precision. The guard digit becomes part of the fraction if normalization is required or is used to determine if the least-significant digit is incremented by one during the rounding process.

#### 1.5.7.2 Normalizing

Left shift normalization of the fractional result of any arithmetic operation is required when its absolute value is less than onesixteenth. The floating-point unit achieves normalization by shifting the hexadecimal fraction to the left until its magnitude is greater than, or equal to, one-sixteenth. exponent is decremented by one for each hexadecimal shift. The guard digit, of the single-precision arithmetic operation and the doubleprecision division operation, is shifted into the least-significant digit position on the first left shift. Subsequent shifts place zeros in the least-significant position of the hexadecimal fraction.

Since the double-precision addition, subtraction and multiplication

operations do not employ the guard digit, zeros are always shifted into the least-significant digit position during the normalizing process.

When the fraction contains all zeros, the exponent is forced to a value of zero.

#### 1.5.7.3 Rounding

The rounding process examines the most-significant bit of the guard digit for a one or a zero. If the most-significant bit of the guard digit is a one (represents a hexadecimal value of 8 or greater), a one is added to the hexadecimal fraction. If the most-significant bit of the guard digit is a zero (represents a hexadecimal value of 7 or less), the fraction is not incremented. Thus, both positive and negative fractions are rounded upwards (i.e., more positive).

#### 1.5.8 Result Storage

The results of the arithmetic operation are transferred from the output register of the floating-point units, via the external Y bus (bits EY00 through EY31), to the file registers. The B address register places the B address (bits FADD00 through FADD03) on the external address bus. The results, which are stored in the file register at the location specified by the B address, overwrite the previously stored contents.

The CPU is informed that the results of the arithmetic operation are available for transfer to the destination general purpose register. The CPU microword addresses the destination file register (B address) via the register A address lines (bits AOO through AO3). This action places the contents of the destination file register, which was designated by the

B address, on the external DB bus (bits EDB00 through EDB31). The result is stored in the general purpose register designated by the RB address. The result overwrites the previously stored contents of the destination general purpose register.

#### 1.5.9 Arithmetic Exception

An arithmetic exception (AE) will occur if the answer to an arithmetic operation results in an exponent underflow or overflow. The AE will cause a trap, within the CPU, if the AE trap is enabled.

If an AE occurs, and the AE trap is not enabled, the CPU firmware will return a full-scale positive result (@ 7FFFFFFF) with a positive overflow, a full-scale negative result (@ 80000001) with a negative overflow, and (@ 00000000) with an underflow.

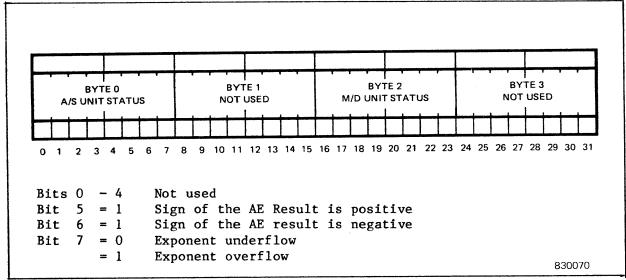

At the time the CPU accepts the results of the arithmetic operation from the file register, the CPU tests the floating-point unit for an AE. If an AE has occurred, the CPU firmware enables the arithmetic exception status word onto the external DB bus. The status word informs the CPU of the sign of the resultant which caused the arithmetic exception and whether it resulted in an underflow or an overflow.

An arithmetic exception will prevent the answer from being stored into the file register. Therefore, the file register and the destination general purpose register will retain the original operand.

### 1.5.10 General Purpose Register Busy

During the arithmetic operation, the destination general purpose register is assigned a busy status.

The CPU requests the transfer of the results from the file register to the destination general purpose register by addressing the file register with the destination address on the RA lines. Addressing the destination register causes the CPU to pause until the results of the operation have been stored into the file register. After the results have been stored, the destination general purpose register is released from its busy status and the CPU is allowed to read the results from the file register and update its general purpose register.

#### 1.5.11 FPA Enable/Disable

Operation of the floating-point accelerator can be enabled or disabled by means of the switch (S1) located on the front edge of the A/S unit circuit board. With the circuit card properly installed, S1 should be switched to the right to enable the FPA.

Operation of the FPA can also be enabled or disabled by the CPU firmware. At power on reset time, an unknown status in the FPA file status register may cause the CPU to stop or perform some error operation. At this time, the CPU firmware will issue a level order (RESET.FPA) to disable the FPA, and a sequence of microcode will clear all the FPA file registers and set the file status register to a known state. At the completion of this reset sequence. the firmware will issue another level order (SET.FPA) to enable the FPA, and the FPA will be ready to resume normal operation.

The SI hardware switch and the firmware set/reset FPA function can override each other. Enabling switch SI will place the FPA under firmware control.

#### CHAPTER 2

#### THEORY OF OPERATION

#### 2.1 Add and Subtract Unit

The add and subtract (A/S) unit contains the logic required to perform floating-point addition and subtraction arithmetic operations. In addition, it contains the floating-point file which provides the interface between the CPU and both floating-point units.

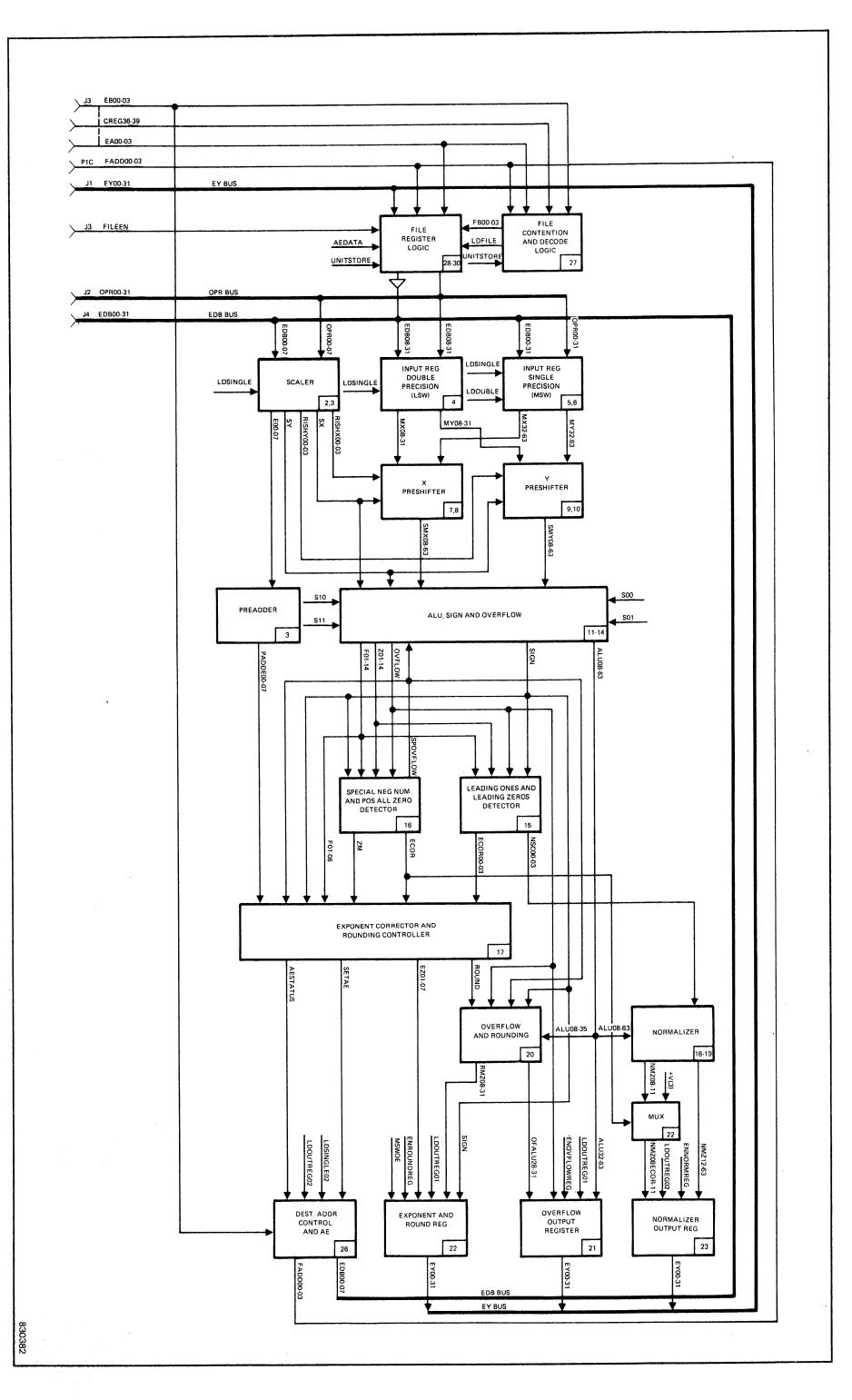

Figure 2-1 is a functional block diagram of the 160-103556 Add and Subtract Unit. The block diagram details the major functional blocks and major signals of the A/S unit. The signal mnemonics shown on the block diagram are similar to those used on the logic diagram. For the add and subtract unit, sheet numbers shown in parentheses in the text, and in the lower right hand corner of each functional block on block diagrams, are the sheet numbers on the A/S unit logic diagram, 130-103556-000, where the circuit details can be found.

#### 2.1.1 Floating-point File

The floating-point file is a major part of the interface between the CPU and the floating-point units. The floating-point arithmetic arguments are passed from the floating-point file registers (FPR) to the operand input registers. The floating-point unit returns the results of the arithmetic operation to the original destination FPR and, subsequently, to the CPU.

The operands from the CPU can be either single-precision or double-precision operands. Both types of

operands contain a sign bit (sign of the fraction), a seven-bit exponent value, and either a 24-bit fraction for single-precision operands or a 56-bit fraction for double-precision operands. The radix point of the fraction is assumed to be immediately before the first bit of the fraction.

The exponents of negative numbers are applied to the floating-point file as one's complement numbers and the fractions as two's complement numbers. The exponents and fractions of positive numbers are applied to the file register as absolute values.

#### 2.1.1.1 File Register Logic

The floating-point file register (sheets 28 through 30) stores operands and results of the arithmetic operations input on the external Y (EY) bus. There are sixteen 32-bit file registers, eight of which correspond directly to the CPU general purpose registers (GPR), addresses 0 through 7. The remaining eight, addresses 8 through F, may be used as work registers in writable control store (WCS) applications.

The output of the file register transfers operands to the operand (OPR) bus for loading the operand input register.

The file register can be loaded with an operand from the CPU or with a result of an arithmetic operation by either floating-point unit.

During the execution of a floatingpoint instruction, the operand in the general purpose register of the CPU will be loaded into the floatingpoint file register of the same address (example: GPRO - FPRO). This is accomplished by the CPU microword which addresses the (file) register (B-port) via the B address lines (EB00 through EB03). Simultaneously, the external destination field (CREG36 through CREG39) of the microword will specify the floating-point file as the external destination. At the end of the same CPU cycle, the contents of the GPR are loaded into the addressed FPR via the external Y bus lines (EY00 through EY31).

The decoding of the external destination field causes the generation of a load file (LDFILE) signal which clocks the operand, from the EY bus, into the file register designated by the GPR address (EBOO through EBO3).

The logic to decode the CPU microword external destination field is contained in the file contention and decode logic.

The results of arithmetic operations are placed on the EY bus from the floating-point unit output register under the control of the microengine. The register B-port address, the same address used for storing the operand, is placed on the file address lines (FADD00 through FADD03) by the unit which performed the arithmetic operation. The microengine issues a unit store (UNITSTORE) signal and the results on the EY bus are stored into the file register designated by the original GPR address.

If, during the arithmetic operation, an arithmetic exception occurs, the arithmetic exception data (AEDATA) signal is generated. This signal inhibits the UNITSTORE, preventing the results from being loaded into the file register, and the file register retains the original operand.

The CPU accesses the contents of the file register by issuing a file enable signal (FILEEN) and applying the file register address, as designated by the destination GPR, to the register A-port (RA) external address lines (EA00 through EA03). The FILEEN signal generates the file output enable (FILEOE) signal which enables the contents of the addressed file register onto the external data bus (EDB00 through EDB31). The CPU GPR is updated with the contents of the file register at the end of the CPU cycle.

#### 2.1.1.2 File Contention Logic

The file contention logic (sheet 27) contains the circuitry for decoding the external destination (ED) field (CREG36 through CREG39) of the CPU microword. The ED field is decoded by the decoder as shown in table 2-1.

The external B lines (EB00 through EB03) are multiplexed with the file address lines (FADD00 through FADD03). When the UNITSTORE signal is not present, the external B lines are selected and generate the file B-port address (FB00 through FB03). When the UNITSTORE signal is present, the file address lines are selected and generate the file B-port address.

#### 2.1.2 Input Registers

The following paragraphs describe the operation of the single- and double-precision input registers.

#### 2.1.2.1 Single Precision

The 24-bit fractions of both operands are loaded simultaneously into the single-precision input register (sheet 4) by the load single (LDSINGLEO1) signal from the microengine. One operand fraction is obtained from the file register's B-port via the operand bus (OPRO8 through OPR31). The other operand

Table 2-1 CREG Bits 36-39

| Syntax  | 36 | CREG<br>37 |   | 39 | Function                                                                                                                                                                                                                                                                                                                             |

|---------|----|------------|---|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FP.FILE | 1  | 0          | 1 | 1  | Floating-point file. This syntax generates the load file (LDFILE) signal. This signal is used to load operands into the file register.                                                                                                                                                                                               |

| A/S.MSW | 1  | 1          | 0 | 0  | Add/subtract most-significant word. This syntax generates the single-precision add (SPADD) signal. The signal controls the loading of a word from a selected file register and a word from the EDB bus into the two single-precision (MSW) input registers. This signal is generated for both single- and double-precision operands. |

| A/S.LSW | 1  | 1          | 0 | 1  | Add/subtract least-significant word. This syntax generates the double-precision add (DPADD) signal. The signal controls the loading of a word from a selected file register and a word from the EDB bus into the two double-precision (LSW) input registers. This signal is generated for double-precision operands.                 |

is prefetched from memory. The CPU microword enables the memory data onto the external data (EDB) bus (EDB00 through EDB31) after the valid memory data is returned to the CPU, via cache multiplexer and right shifter, and clocked into the cache data out register. At the end of the current CPU cycle, both operands are loaded into the most-significant word (MSW) portion (for single-precision operands) of the FPU input register. Simultaneously, the leastsignificant word (LSW) portion (double-precision) of the input register is cleared.

The single operand (SINGLEOPRO1) signal clears the double-precision input register when a single-precision operand is loaded into the single-precision input register.

The latched outputs of the input register are applied to the X and Y preshifters.

## 2.1.2.2 Double Precision

The least-significant 32 bits (LSW) of the 56-bit fractions of both operands are loaded simultaneously into the double-precision input register (sheets 5 and 6) by the load double (LDDOUBLEO1) signal from the microengine. One operand fraction (LSW) is obtained from the file register B-port via the operand bus (OPROO through OPR31). The other operand fraction (LSW) is obtained from the cache data out register via the external data bus (EDBOO through EDB31).

After the least-significant word has been loaded and latched into the double-precision input register, the most-significant word is loaded into the single-precision input register as described in paragraph 2.1.2.1; however, the LSW is not cleared.

The latched outputs of the input register are applied to the X and Y preshifters.

#### 2.1.3 Scaler

The scaler (sheets 2 and 3) contains the logic to determine the rightshift count required and which fraction (the X or the Y) requires right shifting in order to make the two exponents equal.

The load single (LDINGLEO1) signal from the microengine loads the scaler with the sign bits (bit 0) and the exponents (bit 1 through bit 7) of both operands. The external data bus, bits EDBOO through EDBO7, carries the sign and exponent of the X operand. The operand bus, bits OPROO through OPRO7, carries the sign and exponent of the Y operand.

If the sign bit of one or both of the fractions is negative (bit 0 = 1), that fraction's exponent is one's complemented. If the sign bit is positive (bit 0 = 0), the exponent is not altered. The resulting exponent values are simultaneously subtracted from each other using the two's complement method.

The scaler simultaneously subtracts the Y exponent value from the X exponent value and the X exponent value from the Y exponent value and determines which exponent value, the X or the Y, is the greater.

If the X exponent value is the greater, the Y right shift (RISHY00 through RISHY03) count is equal to the difference between the Y exponent value and the X exponent value. The Y right shift count is applied to the Y preshifter.

If the Y exponent value is the greater, the X right shift (RISHX00 through RISHX03) count is equal to the difference between the X exponent value and the Y exponent value. The

X right shift count is applied to the X preshifter.

If the difference between the exponent values is greater than six, for single-precision operands, or 13, for double-precision operands, the smaller fraction is considered insignificant and the maximum shift count of 15 is established. This causes the smaller operand to be replaced with all zeros by the preshifter.

The exponent (X or Y) which has the greater absolute value is applied to the preadder as bits E01 through E07. E00 is always a zero.

#### 2.1.4 Preadder

The preadder (sheet 3) predicts the possibility of an arithmetic exception's occurring during the addition or subtraction of two fractions.

In the scaler, the resulting exponent is applied to the exponent lines (E01 through E07). E00 is always a logical zero. A hexadecimal value (see table 2-2) is added to the exponent. The results of the addition indicate the possibility of an arithmetic exception when PADDE00 = 1.

The preadded exponent (PADDE00 through PADDE07) is applied to the exponent corrector logic.

The exponents that will not have an AE in the preadder are shown in Table 2-3.

#### 2.1.5 Preshifters

The preshifters (sheets 7 through 10) shift the X or Y mantissa to compensate for the equalizing of the exponents.

The X mantissa (MX08 through MX31 for single precision and MX32 through

Table 2-2

Preadder Values

| Decimal<br>Exponent<br>Sign | Precision | Hexadecimal<br>Value<br>Added |  |

|-----------------------------|-----------|-------------------------------|--|

| Positive                    | Single    | 01                            |  |

| Negative                    | Single    | F8                            |  |

| Positive                    | Double    | 01                            |  |

| Negative                    | Double    | F2                            |  |

Table 2-3

AE Prediction

| Decimal<br>Exponent<br>Sign | Precision | Decimal<br>Exponent<br>Value | Hexadecimal<br>Value With<br>40 Bias |  |

|-----------------------------|-----------|------------------------------|--------------------------------------|--|

| Positive                    | Single    | + 62                         | 7E                                   |  |

| Negative                    | Single    | -56                          | 08                                   |  |

| Positive                    | Single    | +62                          | 7E                                   |  |

| Negative                    | Single    | -50                          | 0E                                   |  |

Table 2-4

ALU Control Lines

| Function                        | S11                   | S10              | S01              | S00                   |

|---------------------------------|-----------------------|------------------|------------------|-----------------------|

| OFF ADD SP ADD DP SUB SP SUB DP | 0<br>1<br>1<br>0<br>0 | 0<br>1<br>1<br>1 | 0<br>0<br>1<br>0 | 0<br>0<br>1<br>0<br>1 |

MX63 for double precision) is applied to the inputs of the X preshifter (sheets 7 and 8). The Y mantissa (MY08 through MY31 for single precision and MY32 through MY63 for double precision) is applied to the inputs of the Y preshifter (sheets 9 and 10). Either the X or the Y mantissa is right shifted and sign bit extended as determined by the shift count (RISHX00 through RISHX03 or RISHY00 through RISHX03).

## 2.1.6 ALU Sign and Overflow

Since the arithmetic calculations are performed by the two's complement

method, the sign of the mantissa is part of the calculation. Both sign bits (SX and SY) are applied to the sign portion of the arithmetic logic unit (ALU) (sheets 11 through 14), and both mantissas (SMXO8 through SMX63 and SMY08 through SMY63) are applied to the mantissa portion of the ALU.

The control signals S10, S11, S00 and S01 from the microengine are applied to the ALU. These signals control the functions of the ALU for both single- and double-precision operation. Table 2-4 shows the states of the control lines for the

ALU functions. The S10 and S11 signals control the ALUs associated with the sign bit and the seven most-significant hexadecimal digits and the S00 and S01 signals control the remaining ALUs associated with the seven least-significant hexadecimal digits.

The ALU is turned off during the loading of the input registers and during the preshift operation. The ALU is turned on after the shifted mantissa signals are stable, approximately 110 nanoseconds into the machine cycle.

The seventh hexadecimal digit (least-significant) is the guard digit. The guard digit provides an extra hexadecimal digit of precision for single-precision operations when either of the X and Y mantissas have been right shifted by the preshifter.

The resulting sign is a function of the addition or subtraction operation of the sign bits and the overflow from the most-significant hexadecimal digit.

An overflow condition can be generated by overflow from the most-significant hexadecimal fraction digit or by a special overflow case which is caused by the addition or subtraction of some special numbers.

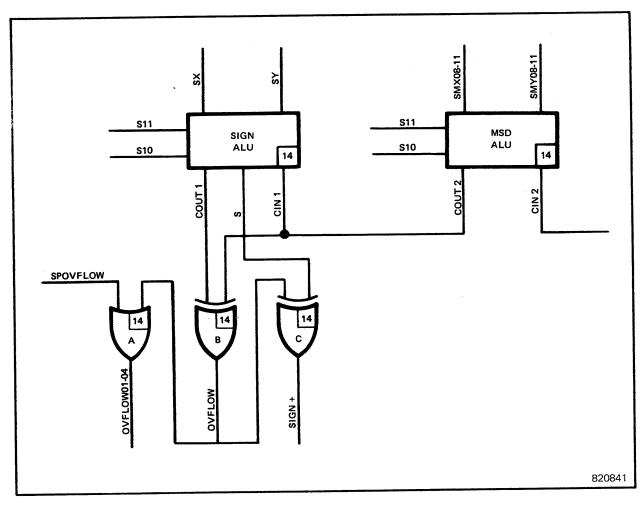

Figure 2-2 is a simplified version of the sign and overflow functions. The sign bits (SX and SY) and the mostsignificant hexadecimal fraction digits (SMX08 through 11 and SMY08 through 11) are applied to the arithmetic logic units. The control lines (S11 and S10) establish the add or subtract function. The carry-out (COUT2) of the most-significant hexadecimal digit ALU is applied to the carry-in (CIN1) of the sign bit ALU (sheet 14) and to the exclusive OR gate B. The carry-out (COUT1) of the sign bit ALU is also applied to the exclusive OR gate B. The sign bit (the result of the addition or

subtraction operation) and the overflow (OVFLOW) are applied to the exclusive OR gate C, the output of which is the SIGN+ signal. The OVFLOW signal is also applied to OR gate A, along with the special overflow signal (SPOVFLOW). The outputs of the A gate are the signals OVFLOWO1 through OVFLOW O4.

The exclusive OR gate B implements the rules for an overflow condition. Table 2-5 is a state diagram for the overflow condition.

The rule for the overflow condition is: an OVFLOW signal will be generated when COUT1 is present and CIN1 is not present or CIN1 is present and COUT1 is not present; an OVFLOW signal will not be generated when COUT1 and CIN1 are both present or neither are present. The OVFLOWO1 through OFVLOWO4 signals are generated when either an OVFLOW signal or an SPOVFLOW signal or both are input to OR gate A.

The special overflow is generated under special conditions; for example: when two negative eights are added or a positive eight is subtracted from a negative eight. These two operations will satisfy the rule CIN1 and COUT1 so as to produce no overflow. In this case, these two operations are detected by the special negative number logic and a special overflow signal (SPOVFLOW) is issued. This causes the overflow signals OVFLOWO1 through OVFLOWO4 to be generated.

The ALU functinal block also contains logic which detects a guard digit value less than, or equal to, seven (hexadecimal) with all other digits equal to zero, for single-precision negative fractions. In this special case, the guard digit is cleared, an F (hexadecimal) is inserted into the most-signficant hexadecimal digit, and the exponent is decremented by one.

Figure 2-2. Simplified Sign and Overflow Function

Table 2-5 Overflow State Diagram

| CIN1                       | COUT1                      | SPOVFLOW                   | ovflow01-04           |

|----------------------------|----------------------------|----------------------------|-----------------------|

| 0<br>0<br>1<br>1<br>1<br>X | 0<br>1<br>0<br>1<br>1<br>X | 0<br>0<br>0<br>0<br>1<br>1 | 0<br>1<br>1<br>0<br>1 |

| X = Don't Care             |                            |                            |                       |

## 2.1.7 Special Negative Number and Positive All Zero Detector

The special negative number and positive all-zero detector logic (sheet 16) detects an all-zeroes result in single- and double-

precision hexadecimal fractions of an arithmetic operation. It also detects a single-precision negative number in which the hexadecimal mantissa is all zeros and the guard digit is equal to, or less than, a hexadecimal 7.

Both of these conditions produce the error correct signal (ECOR) to the exponent correction logic. (Some special single-precision, negative number cases also cause the generation of the special overflow signal (SPOVFLOW) which is used to correct the results.)

## 2.1.8 Leading Ones and Leading Zeros Detector

In the leading ones and leading zeros detector circuitry (sheet 15), leading Fs (hexadecimal) of single—and double—precision negative mantissas (presented in the twos complement form) and leading zeros of single— and double—precision positive mantissas are detected if no overflow condition exists. The number of leading Fs or zeros detected establishes a count on the exponent correct (ECOROO through ECORO3) lines which is used to decrement the exponent.

The normalized shift count (NSC) is used to left shift the mantissa so that a hexadecimal digit other than a zero for a positive mantissa and an F (hexadecimal) for a negative mantissa is to the immediate right of the radix point.

#### 2.1.9 Exponent Corrector

The exponent corrector (sheet 17) adjusts the exponent to compensate for the bit that was added in the preadder, for normalizing of the mantissa, and for special case numbers.

The error correction bits (ECOR00 through ECOR03) are added to the exponent (PADDE00 through PADDE07) from the preadder. The exponent is adjusted based on the conditions that exist.

When there is no overflow, no request for normalization, and the mantissa is either positive or negative, a value of FX (hexadecimal) is added to the preadded exponent. The value of X (hexadecimal) is the one's complement of the mantissa shift count, which in this case is F. This causes the preadded exponent to be decremented by 1 to compensate for the preadded bit.

When there is no overflow, but there is a request for normalizing, and the mantissa is either positive or negative, a value of FX (hexadecimal) is added to the preadded exponent. The value of X (hexadecimal) is the one's complement of the mantissa shift count.

When there is a normal overflow or special overflow (negative mantissa only), no request for normalizing, and the normal overflow mantissa is either a positive or negative, a value of 00 (hexadecimal) is added to the preadded exponent.

The special negative number case where the mantissa contains one or more leading Fs, followed by all zeros, there is no overflow, and a request for normalizing, a value of FX+1 (hexadecimal) is added to the preadded exponent. The value of X (hexadecimal) is the one's complement of the mantissa shift count. The 1 (hexadecimal) is added because the error correct (ECOR) signal is true for the special negative numbers.

When the sign of the mantissa is negative, the corrected exponent is one's complemented before it is transferred to the exponent output register. The corrected exponents of positive mantissas are in their absolute values and are not complemented before being transferred to the exponent output register.

The exponent corrector logic also contains the logic for determining if an arithmetic exception has occurred. The exponent is seven bits wide; however, the output of the preadder is eight bits wide. This allows the most-significant bit (bit 00) of the exponent corrector to be used to indicate the occurrence of an arithmetic exception (SETAE). The set arithmetic exception signal is added with the sign positive (SIGN+) signals to indicate a positive or negative arithmetic exception. arithmetic exception signals are transferred to the arithmetic exception status register. The arithmetic exception status is transferred to the CPU by firmware request.

#### 2.1.10 Normalizer

The normalizer (sheets 18 and 19) receives the mantissa from the arithmetic logic units and the normalized shift count from the leading ones and leading zeros detector. The mantissa is shifted left by the amount specified by the shift count. Both single- and double-precision mantissas can be normalized.

#### 2.1.11 Overflow and Rounding

In the overflow and rounding circuitry (sheet 20), single-precision mantissas are rounded to the next higher hexadecimal digit if the guard digit (ALU32 through ALU35) is equal to, or greater than, eight (hexadecimal). This is accomplished by adding a hexadecimal one (the ROUND signal) to the least-significant mantissa digit. There is an exception to the rounding of the single-precision mantissa. A mantissa which contains all Fs (hexadecimal) is not rounded because it would cause an overflow condition.

There are several overflow conditions which require special handling of the most-significant digit (ALU08 through ALU11). In each case, the digit is placed into the most-significant digit and the mantissa is shifted right by the overflow right shifter (2:1 multiplexers).

When a positive overflow condition exists, a one (hexadecimal) is placed into the most-significant digit.

When a negative overflow condition exists, an E (hexadecimal) is placed into the most-significant digit.

When a special overflow condition exists, an F (hexadecimal) is placed into the most-significant digit.

#### 2.1.12 Normalizer Error Corrector

The normalizer error corrector (sheet 22) is a 2:1 multiplexer which normally selects the normalized bits (NMZO8 through NMZ11); however, in some special cases it will select an F (hexadecimal).

These special cases exist when the result of the ALU operation has a negative sign, the mantissa must be normalized one or more positions, and the normalized mantissa contains all zeros.

An example of this special case is as follows:

Assume the result of the ALU operation is a negative FFFF00. The mantissa requests normalizing because of the four leading Fs. The result of normalizing this mantissa is a negative 000000, which is an invalid negative number. The special negative

number detector detects the special case of negative mantissas with leading Fs followed by all zeros and generates the error correction (ECOR) signal. The ECOR signal causes the multiplexer to select an F instead of the normalized bits (NMZO8 through NMZll) and applies it, via the normalized error corrected lines (MNZO8ECOR through NMZllECOR), to the normalized output register.

#### 2.1.13 Output Registers

The add and subtract unit has two sets of mantissa output registers (sheets 21 through 23). One set contains the sign, the exponent, the results of an ALU overflow, and/or the results of a single-precision rounding request. The other set of output registers contains the sign, the exponent, and the normalized results if an overflow condition does not exist.