# Integrated Storage Module Model 3034

Technical Manual

May 1986

Publication Order Number: 303-003400-000

This manual is supplied without representation or warranty of any kind. Gould Inc., Computer Systems Division therefore assumes no responsibility and shall have no liability of any kind arising from the supply or use of this publication or any material contained herein.

(C) Copyright 1984

Gould Inc., Computer Systems Division

All Rights Reserved

Printed in U.S.A.

#### **HISTORY**

The Integrated Storage Module (ISM), Model 3034, Technical Manual, Publication Order Number 303-003400-000, was printed December, 1984.

Publication Order Number 303-003400-001 (Change 1) was printed April, 1985.

Publication Order Number 303-003400-002 (Change 2) was printed May, 1986.

The updated manual contains the following pages:

| * Change                                                                                                                                                       | * Change        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Number                                                                                                                                                         | Number          |

| Title page          Copyright page          iii (iv Blank) Change 2          iii (iv Blank) Change 1          iii (iv Blank)          vi through ix          x | 1-1 through 1-8 |

On a change page, the portion of the page affected by the latest change is indicated by a vertical bar in the outer margin of the page. However, a completely changed page will not have a full length bar, but will have the change notation by the page number.

<sup>\*</sup> Zero in this column indicates an original page.

#### **HISTORY**

The Integrated Storage Module (ISM), Model 3034, Technical Manual, Publication Order Number 303-003400-000, was printed December, 1984.

Publication Order Number **303-003400-001** (Change 1) was printed April, 1985. The updated manual contains the following pages:

| * Change   | * Change                      |

|------------|-------------------------------|

| Number     | Number                        |

| Title page | 2-7 through 2-15 (2-16 Blank) |

On a change page, the portion of the page affected by the latest change is indicated by a vertical bar in the outer margin of the page. However, a completely changed page will not have a full length bar, but will have the change notation by the page number.

<sup>\*</sup> Zero in this column indicates an original page.

# **HISTORY**

The Integrated Storage Module (ISM), Model 3034, Technical Manual, Publication Order Number 303-003400-000, was printed December 1984.

This manual contains the following pages:

Title page

Copyright page

iii/iv through x

1-1 through 1-8

2-1 through 2-15/(2-16 Blank)

3-1 through 3-15/(3-16 Blank)

4-1 through 4-39/(4-40 Blank)

5-1 through 5-4

A-1 through A-8

IN-1 through IN-2

# TABLE OF CONTENTS

| Ch | apte | r              |                  |                              |                                |                                       |               |                 |           | Page        |

|----|------|----------------|------------------|------------------------------|--------------------------------|---------------------------------------|---------------|-----------------|-----------|-------------|

|    |      |                |                  |                              |                                |                                       |               |                 |           |             |

| _  |      |                |                  |                              |                                | • • • • • • • •                       | • • • • • • • | • • • • • • •   | , <b></b> | ••••        |

| 1  | GEN  | NERAL I        | DESCRIPT         | ION                          |                                |                                       |               |                 |           |             |

|    | 1.1  | Introdu        | ction            | • • • • • • • • •            |                                |                                       |               |                 |           | 1-1         |

|    | 1.2  | Feature        | es               | • • • • • • • • •            |                                |                                       |               |                 |           | 1-1         |

|    |      | 1.2.1          |                  | ess Time                     |                                |                                       |               |                 |           |             |

|    |      | 1.2.2          |                  | ained REfre                  |                                |                                       |               |                 |           |             |

|    |      | 1.2.3          |                  | ained Scrub                  |                                |                                       |               |                 |           |             |

|    |      | 1.2.4          |                  | rror Logger                  |                                |                                       |               |                 |           |             |

|    |      | 1.2.5          | Two-Deep         | o Input Buff                 | ering                          |                                       |               |                 | • • • • • | 1-2         |

|    |      | 1.2.6          |                  | aword Storag                 |                                |                                       |               |                 |           |             |

|    |      | 1.2.7          | Four Meg         | aword Addr                   | essing Capa                    | bility                                | • • • • • • • | • • • • • • • • | • • • • • | 1-2         |

|    |      | 1.2.8<br>1.2.9 | 64KW Ad          | dressing Red<br>erleaving Op | cognition Be                   | oundaries.                            | • • • • • • • | • • • • • • • • | • • • • • | 1 7         |

|    |      | 1.2.10         | Ontional         | erieaving Op<br>Read and Lo  | ok Copobil                     | • • • • • • • • • • • • • • • • • • • | • • • • • • • | • • • • • • •   | • • • • • | <u>i-</u> 2 |

|    |      | 1.2.11         | Solf-Cont        | ained Error                  | Correction                     | Code (EC                              |               | • • • • • • •   | • • • • • | 1_3         |

|    |      | 1.2.12         |                  | le with Exis                 |                                |                                       |               |                 |           |             |

|    | 1.3  |                |                  | iption                       |                                |                                       |               |                 |           |             |

|    | 1.0  | 1.3.1          |                  | terface                      |                                |                                       |               |                 |           |             |

|    |      | 1.3.2          |                  | rection Cod                  |                                |                                       |               |                 |           |             |

|    |      | 1.3.3          |                  | •••••                        |                                |                                       |               |                 |           |             |

|    |      | 1.3.4          |                  | ]                            |                                |                                       |               |                 |           |             |

|    |      | 1.3.5          |                  | Storage                      |                                |                                       |               |                 |           |             |

|    |      | 1.3.6          | Module Ir        | nterleaving                  |                                |                                       |               |                 |           | 1-4         |

|    |      | 1.3.7          | Controls         | and Displays                 | 3                              |                                       |               |                 |           | 1-5         |

|    | 1.4  | Physica        | al Descript      | ion                          | • • • • • • • • •              | • • • • • • • •                       | • • • • • • • | • • • • • • • • | • • • • • | 1-5         |

| 2  | TNIC | TALL AT        | TON AND          | OPERATIO                     | NI.                            |                                       |               |                 |           |             |

| _  | 1173 | IALLA          | ION AND          | OFLINATIO                    | 14                             |                                       |               |                 |           |             |

|    |      |                |                  | • • • • • • • • •            |                                |                                       |               |                 |           |             |

|    |      |                |                  | • • • • • • • • • • •        |                                |                                       |               |                 |           |             |

|    |      |                |                  | • • • • • • • • • •          |                                |                                       |               |                 |           |             |

|    | 2.4  |                |                  | • • • • • • • • •            |                                |                                       |               |                 |           |             |

|    |      | 2.4.1          |                  |                              |                                |                                       |               |                 |           |             |

|    |      |                |                  | Display Er                   | ror Switch (                   | (51)                                  | • • • • • • • | • • • • • • •   | • • • •   | 2-1         |

|    |      |                | 2.4.1.2          |                              | ch (S2)                        |                                       |               |                 |           |             |

|    |      |                | 2.4.1.3          | Error Type                   | : 5WITCH (5 <i>)</i><br>5 (64) | ) • • • • • • •                       | • • • • • • • | • • • • • • •   | • • • • • | Z-J         |

|    |      | 2.4.2          | 2.4.1.4          | ECC Switc                    | п (54)                         | • • • • • • • •                       | • • • • • • • | • • • • • • •   | • • • • • | Z- <i>i</i> |

|    |      | Z.4.Z          | Jumpers 2.4.2.1  | Coft Turns                   | ers                            | • • • • • • • •                       | • • • • • • • | • • • • • • •   | • • • • • | 2.1         |

|    |      |                | ∠• <b>4•</b> ∠•⊥ | 2.4.2.1.1                    |                                |                                       |               |                 |           |             |

|    |      |                |                  | 2.4.2.1.2                    |                                |                                       |               |                 |           |             |

|    |      |                |                  | ~• <del>~</del> •~•          | LU110                          | • • • • • • • •                       | • • • • • • • | • • • • • • • • | • • • • • | . 2-0/      |

# TABLE OF CONTENTS (Continued)

| Ch | apte   | r         |            |              |                                         | Pa                                      | ıge         |

|----|--------|-----------|------------|--------------|-----------------------------------------|-----------------------------------------|-------------|

|    |        |           |            | 2.4.2.1.3    | Starting Address                        | 2-0                                     | 6A          |

|    |        |           |            | 2.4.2.1.4    | Offset Address                          | 2-0                                     | 6A          |

|    |        |           |            | 2.4.2.1.5    | Read and Lock Mode                      | 2-0                                     | 6A          |

|    |        |           |            | 2.4.2.1.6    | Priority Generation                     | 2-6                                     | 6A          |

|    |        |           |            | 2.4.2.1.7    | Priority Recognition                    |                                         |             |

|    |        |           |            | 2.4.2.1.8    | Address Interleave                      | 2                                       | 2-8         |

|    |        |           |            | 2.4.2.1.9    | LDT23 No Error Jumper                   |                                         |             |

|    |        |           |            | 2.4.2.1.10   | Master Slave Enable Jumper              |                                         |             |

|    |        |           |            | 2.4.2.1.11   | SelBUS Clear Display                    |                                         |             |

|    |        |           | 2.4.2.2    |              | rs                                      | 2-                                      | 12          |

|    |        |           |            | 2.4.2.2.1    | DRAM Type Select                        |                                         | 12          |

|    |        |           |            | 2.4.2.2.2    | Memory Bank Decode Select               | 2-                                      | .12         |

|    |        |           |            | 2.4.2.2.3    | RAS Enable                              | 2-                                      | .12         |

|    |        |           |            | 2.4.2.2.4    | HEDCDLSEL                               |                                         |             |

|    |        |           |            | 2.4.2.2.5    | LTONRASSEL1                             |                                         |             |

|    |        |           |            | 2.4.2.2.6    | HTOFFNRASSEL1                           |                                         |             |

|    |        |           |            | 2.4.2.2.7    | LTOFFMRASSEL1                           |                                         |             |

|    |        |           |            | 2.4.2.2.8    | LWESTARTSEL                             |                                         |             |

|    |        |           |            | 2.4.2.2.9    | HTOFFECDPLS                             |                                         |             |

|    |        |           |            | 2.4.2.2.10   | HTONECDPLS                              |                                         |             |

|    |        |           |            | 2.4.2.2.11   | HFDBKINSEL                              |                                         |             |

|    |        |           |            | 2.4.2.2.12   | HFDBKSEL                                | 2-                                      | .14         |

|    |        |           |            | 2.4.2.2.13   | HTONCASSEL                              |                                         |             |

|    |        |           |            | 2.4.2.2.14   | HMUXSEL                                 | 2-                                      | -15         |

|    | 2.5    | Indicato  | ors        |              | ,                                       | 2-                                      | -15         |

|    |        | 2.5.1     | Problem I  | LED          |                                         | 2-                                      | -15         |

|    |        | 2.5.2     |            |              |                                         |                                         |             |

|    |        | 2.5.3     |            |              |                                         |                                         |             |

|    |        | 2.5.4     | Soft SBE   |              |                                         | 2-                                      | -15         |

|    |        | 2.5.5     | Hard SBE   |              |                                         | 2-                                      | -15         |

|    |        | 2.5.6     | DBE LED    |              |                                         | 2-                                      | -15         |

| 7  | C - 1F | . K. TD A | NICEERC    |              | TIONIC                                  |                                         |             |

| 3  |        |           |            | AND OPERA    |                                         |                                         |             |

|    | 3.1    | Introdu   | ction      |              |                                         |                                         | <b>3-</b> 1 |

|    | 3.2    | SelBUS    | Priority T | ransfer Syst | em                                      | • • • • • • • • • • • • • • • • • • • • | <b>5-</b> 1 |

|    | 3.3    |           |            |              |                                         |                                         |             |

|    |        |           |            |              |                                         |                                         |             |

|    |        | 3.3.2     | Priority F | Polling      | • • • • • • • • • • • • • • • • • • • • |                                         | 5-4         |

|    | 3.4    |           | r (TX) Op  | erations     | · · · · · · · · · · · · · · · · · · ·   |                                         | 5-4         |

|    |        | 3.4.1     | Memory I   | Read Transfe | r (MRT)                                 |                                         | 5-4         |

|    |        | 3.4.2     |            |              | er (MWT)                                |                                         |             |

|    |        | 3.4.3     |            |              | k Transfer (MRLT)                       |                                         |             |

|    |        | 3.4.4     |            |              | lock Transfer (MWUT)                    |                                         |             |

|    |        | 3.4.5     | Data Ret   | urn Transfer | (DRT)                                   | • • • • • • • • • • • • • •             | 3-9         |

|    | 3.5    |           | d (E) Tran | sfer Operati | ns                                      | • • • • • • • • • • • • • • • • • • • • | 3-9         |

|    |        | 3.5.1     | Nonprese   | nt Memory A  | ccessed                                 | • • • • • • • • • • • • • • • • • • • • | 5-9         |

|    |        | 3.5.2     | Transfer   | Accepted M   | emory                                   | • • • • • • • • • • • • •               | 5-9         |

|    |        | 3.5.3     | Transfer   | Unsuccessfu  |                                         | ••••• <u>•</u>                          | 5-9         |

|    | _      | 3.5.4     | Error Tra  | ansfer       |                                         |                                         | -11         |

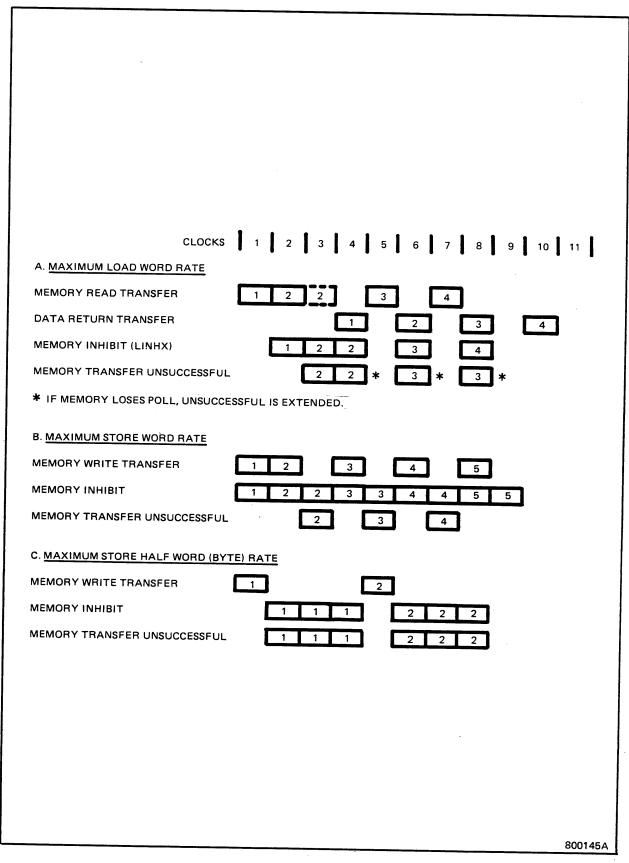

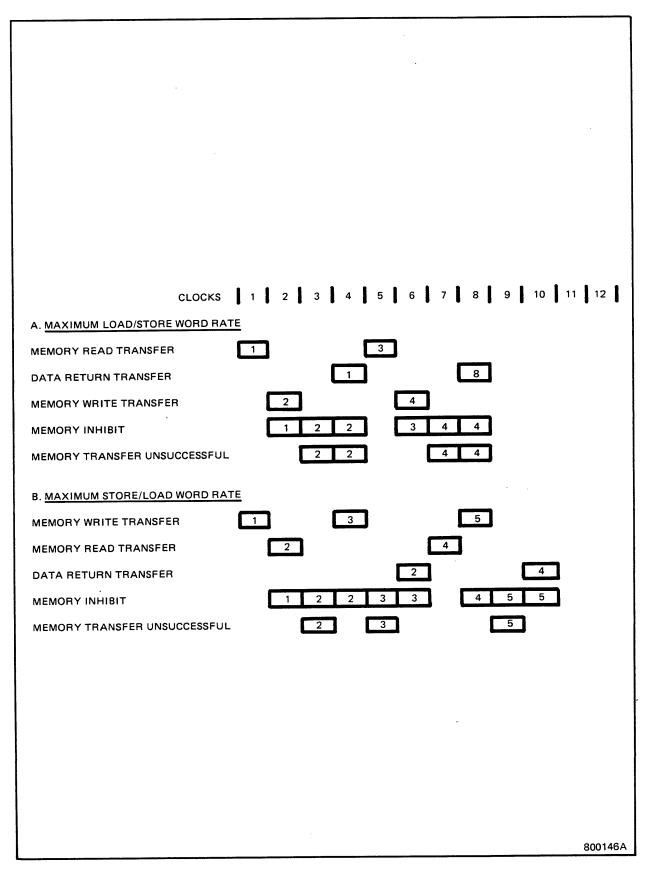

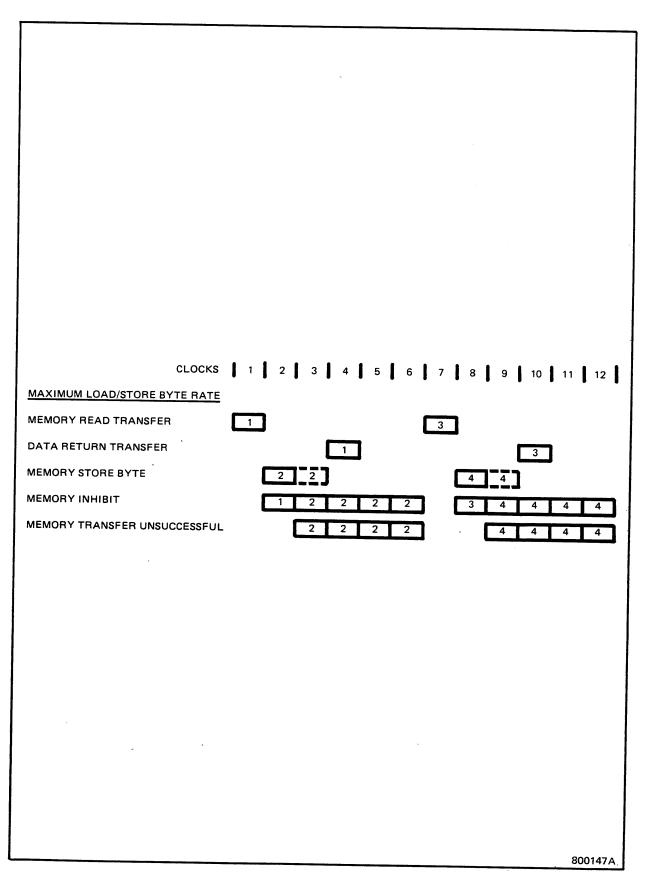

|    | 3.6    | ISM Per   | rformance  | and Timing   |                                         | 3-                                      | -11         |

# TABLE OF CONTENTS (Continued)

| Cha | apter      |                                                                               | Р                                                                                                                                                                                                                                                                                                                | age                                                                  |

|-----|------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 4   | THEC       | RY OF                                                                         | OPERATION                                                                                                                                                                                                                                                                                                        |                                                                      |

|     | 4.2<br>4.3 | Mnemor<br>General<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6       | tion nics Theory SelBUS Interface Data Formatter and Error Corrrection Memory Storage Timing External Error Analysis Connector Control Switches Status Display                                                                                                                                                   | 4-1<br>4-1<br>4-1<br>4-1<br>4-3<br>4-3<br>4-3                        |

|     | 4.4<br>4.5 | Detailed<br>Memory<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.4<br>4.5.5               | d Theory                                                                                                                                                                                                                                                                                                         | 4-3<br>4-3<br>4-4<br>4-4<br>4-4<br>4-4                               |

|     | 4.6        | 4.6.1<br>4.6.2                                                                | Address Structure                                                                                                                                                                                                                                                                                                | 4-4<br>4-9                                                           |

|     | 4.7        | SelBUS<br>4.7.1<br>4.7.2<br>4.7.3                                             | Interface                                                                                                                                                                                                                                                                                                        | 4-15<br>4-15                                                         |

|     | 4.8        | 4.8.1<br>4.8.2<br>4.8.3<br>4.8.4<br>4.8.5<br>4.8.6<br>4.8.7<br>4.8.8<br>4.8.9 | Memory Cycle Accept Refresh Cycle Accept Memory Inhibit Module Reset Phase and Sub-Phase Timing Logic Continuous Clocks and Power Fail Stop Clock Clocks Formatter Timing Display Clear                                                                                                                          | 4-17<br>4-18<br>4-18<br>4-18<br>4-18<br>4-21<br>4-21<br>4-21<br>4-21 |

|     |            | 4.9.1<br>4.9.2<br>4.9.3                                                       | Address Generation                                                                                                                                                                                                                                                                                               | 4-21<br>4-21<br>4-22<br>4-22                                         |

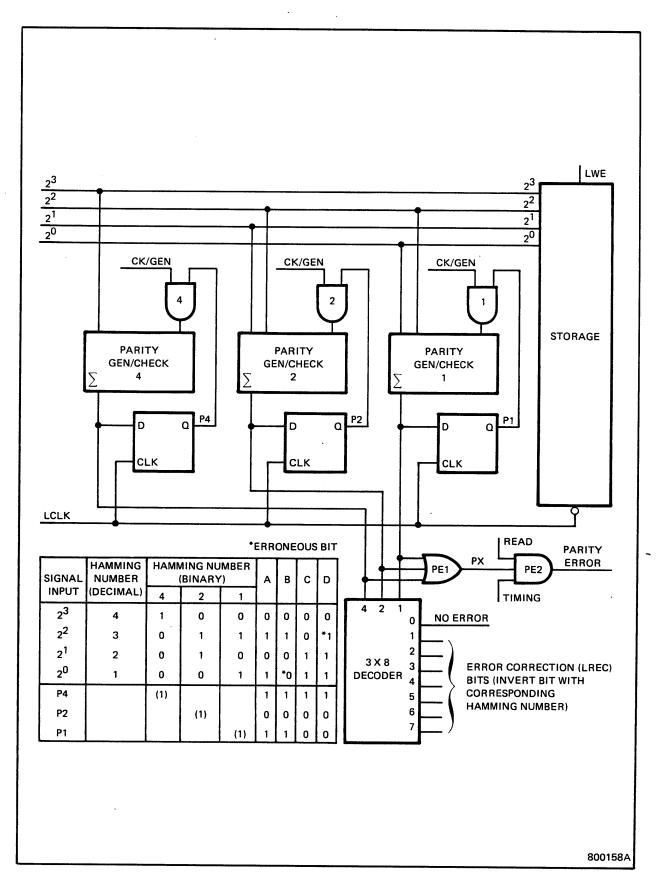

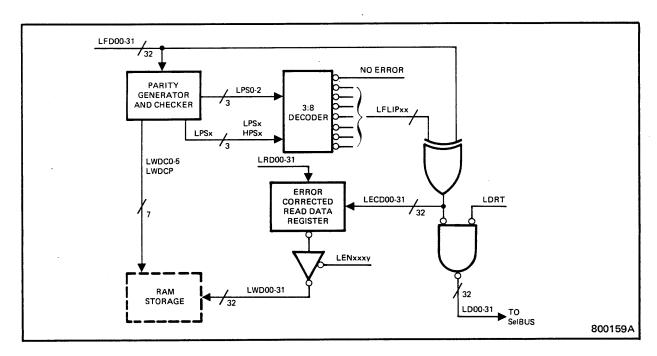

|     | 4.10       |                                                                               | Modified Hamming Code Theory.  Error Correction Code (ECC) Structure  4.10.2.1 Parity Syndrome Check Bits  Error Reporting.  4.10.3.1 Error Logger DS2-DS10  4.10.3.2 Other Status DS11-DS14  4.10.3.3 Sample Display Error Sequence  4.10.3.4 Sample Hamming Code Error Conditions  4.10.3.5 No Error Condition | 4-23<br>4-28<br>4-30<br>4-30<br>4-31<br>4-32<br>4-32<br>4-33         |

# TABLE OF CONTENTS (Continued)

| Chapte                          | r                                                       | Page                       | е           |

|---------------------------------|---------------------------------------------------------|----------------------------|-------------|

|                                 | 4.10.3.6<br>4.10.3.7<br>4.10.3.8                        | Single-Bit Error Condition | 9           |

| 5 <b>MA</b>                     | INTENANCE                                               |                            |             |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Maintenance Phi<br>External Error A<br>Write Check Bits | Ilosophy                   | 1<br>1<br>1 |

| APPEN                           | DIX A                                                   | A-                         | 1           |

| INDEX                           |                                                         | IN-                        | 1           |

# LIST OF ILLUSTRATIONS

| Figure                                               | Title                                                                                                                                                             | Page                                       |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

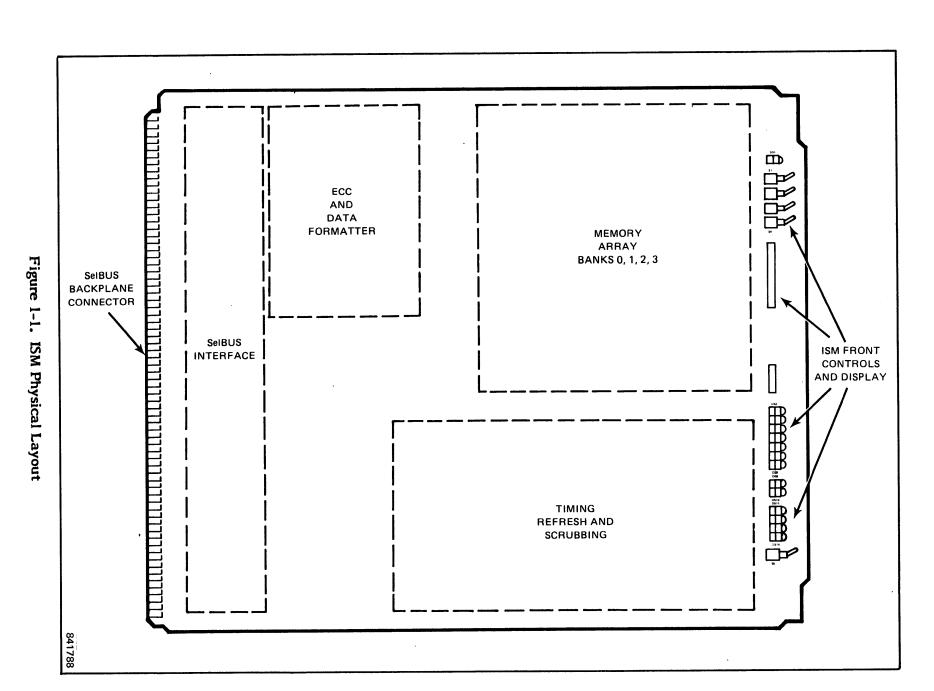

| 1-1                                                  | ISM Physical Layout                                                                                                                                               | 1-6                                        |

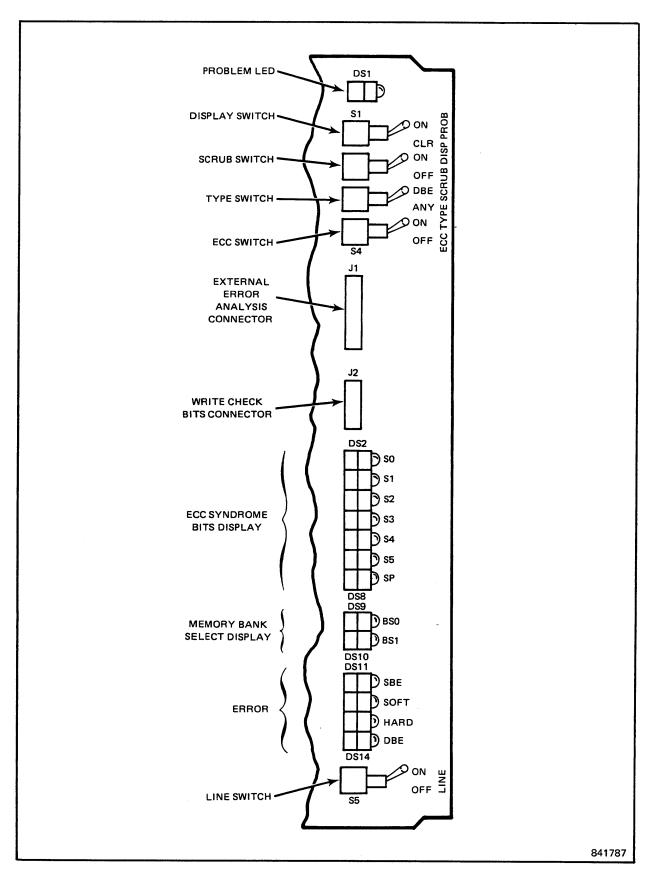

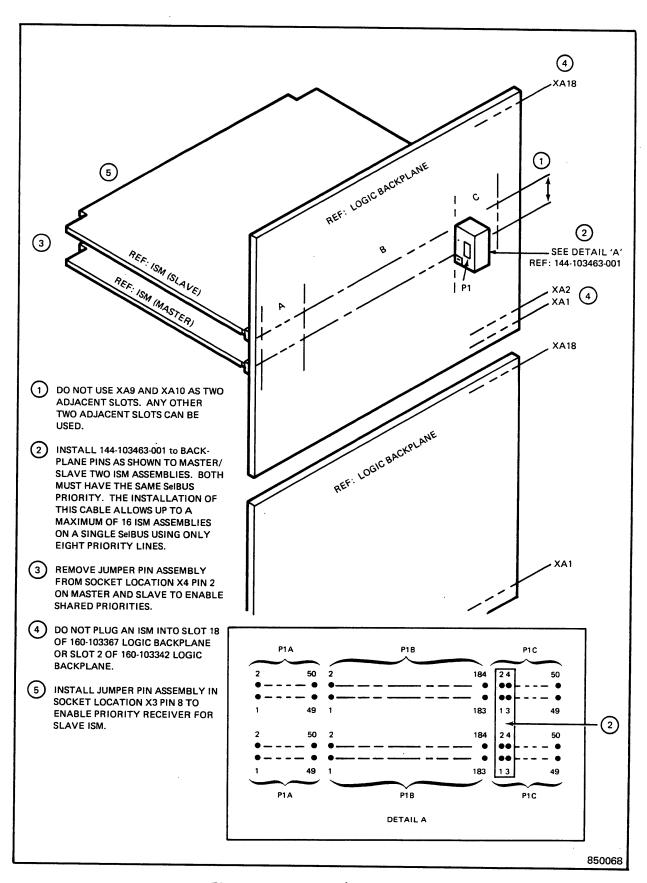

| 2-1<br>2-2                                           | ISM Front Controls and Displays                                                                                                                                   | 2-2<br>2-11                                |

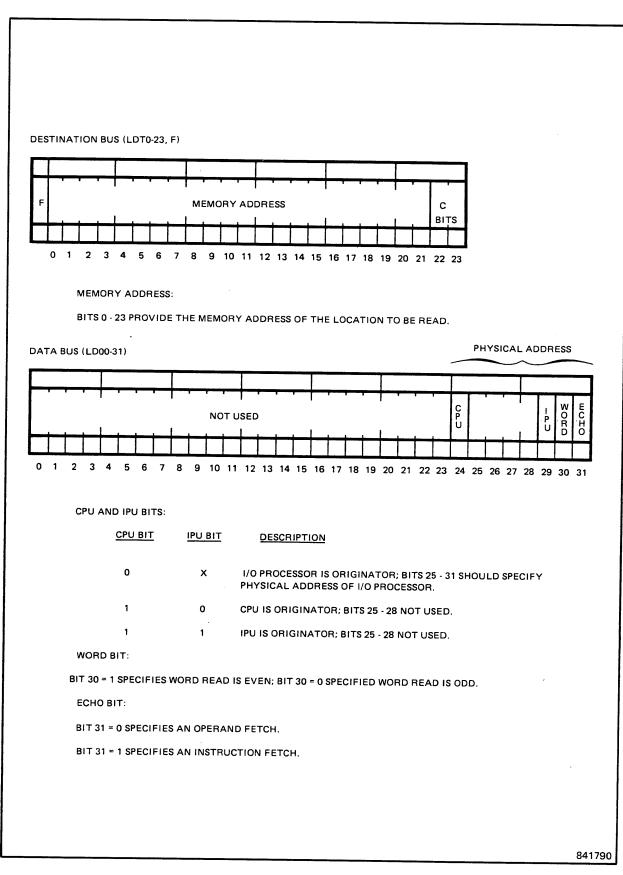

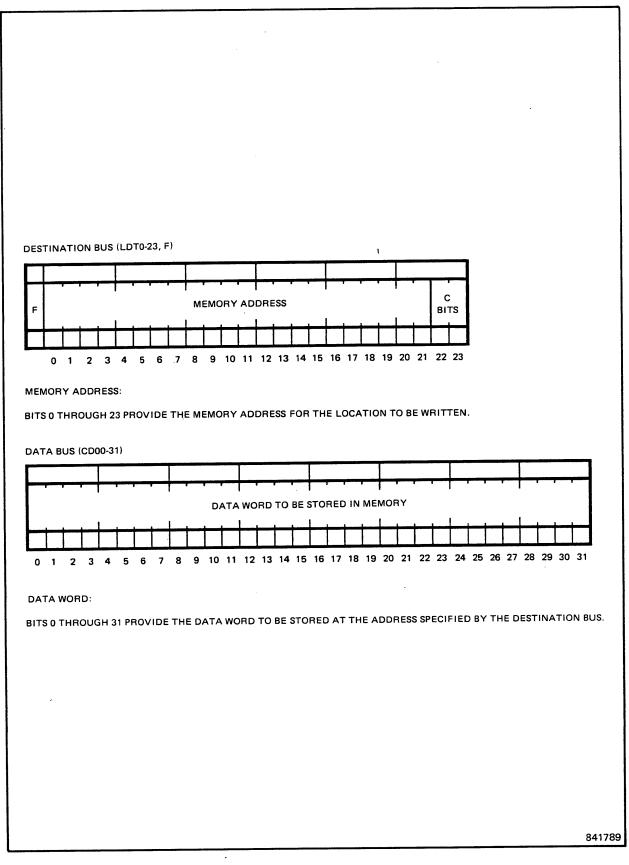

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6               | MRT Format  MWT Format  DRT Format  Performance Transactions Not Mixed  Performance Transactions Mixed Load/Store  Performance Transactions Mixed Load/Store Byte | 3-10<br>3-13<br>3-14                       |

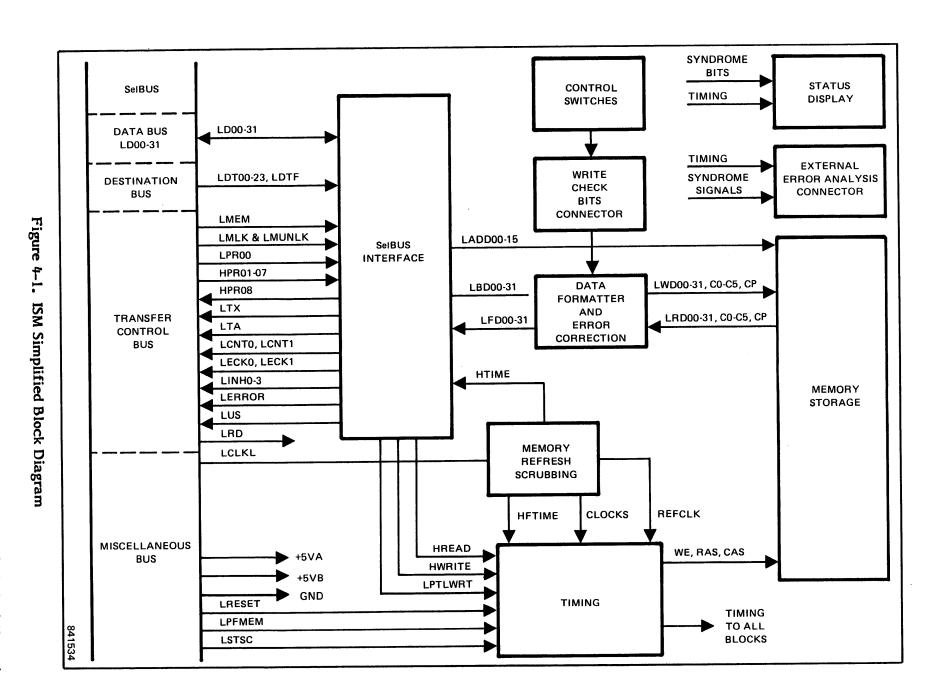

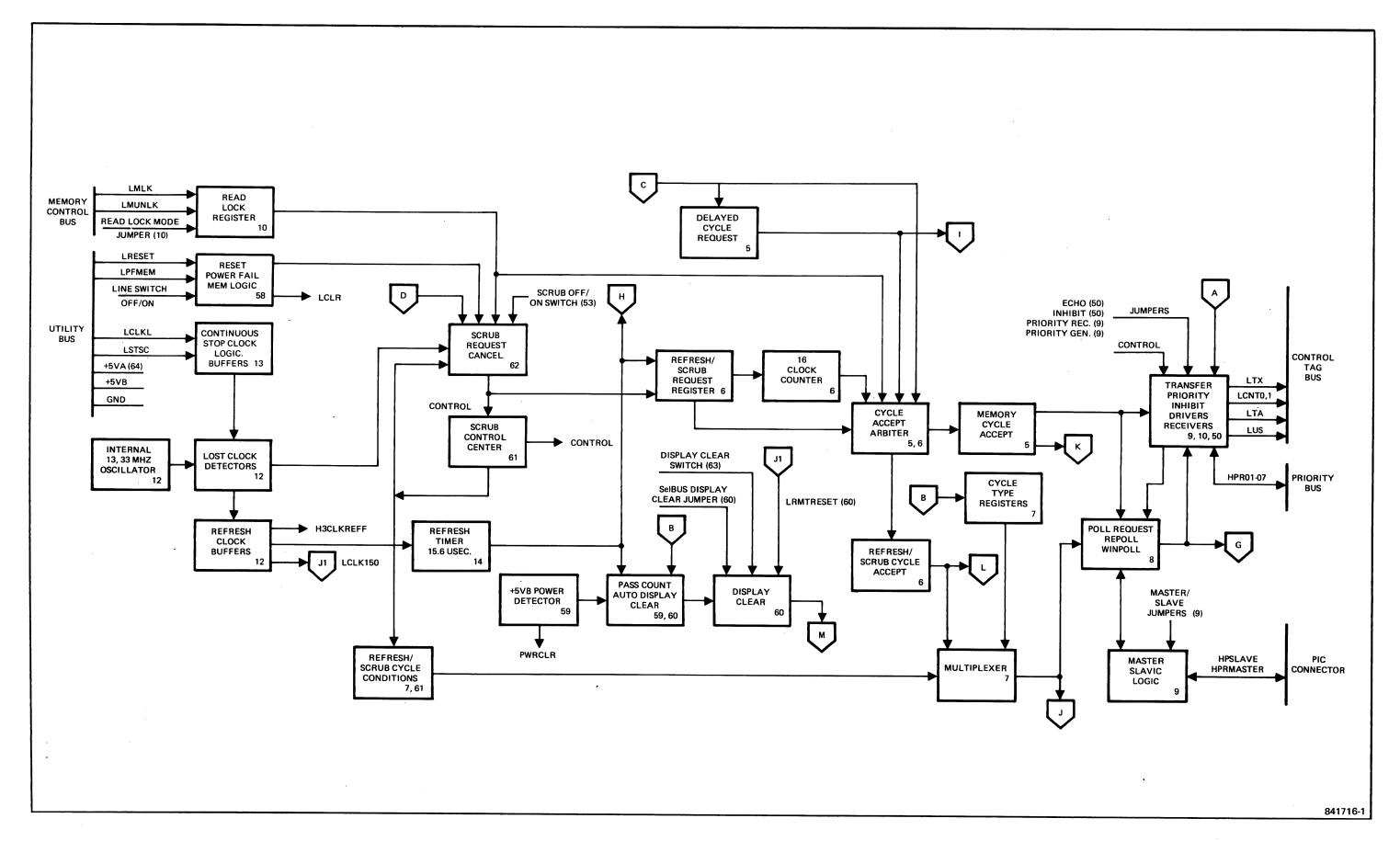

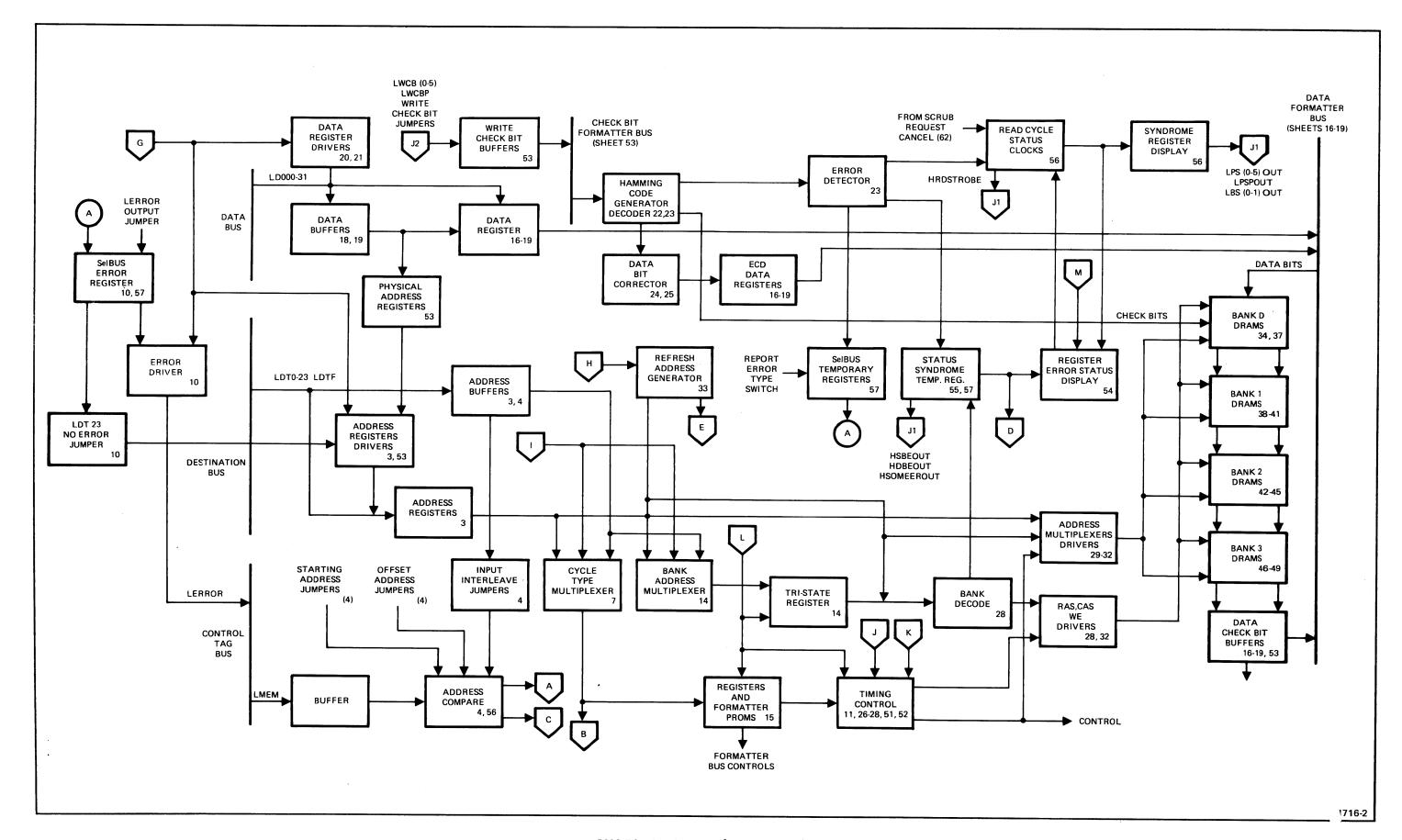

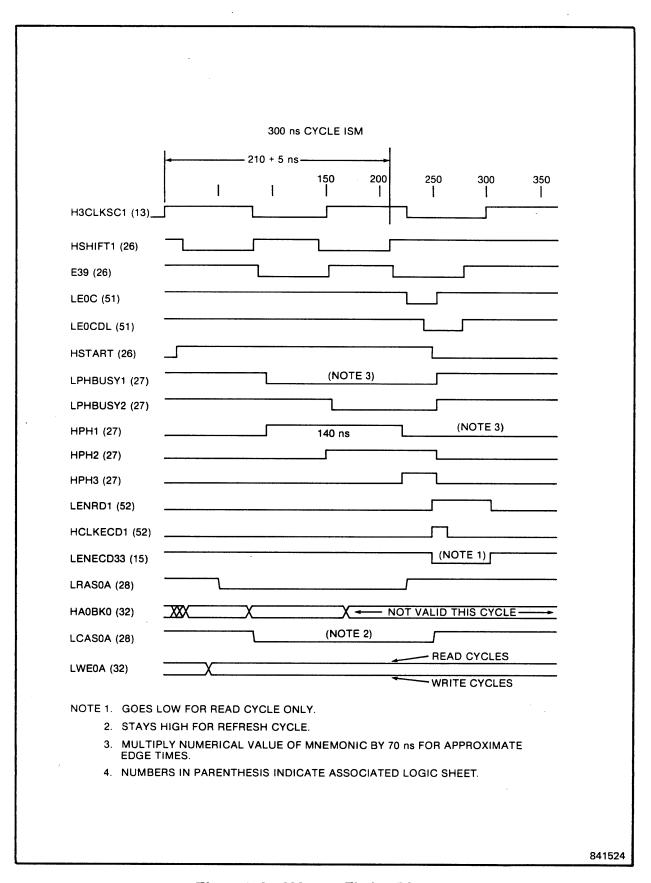

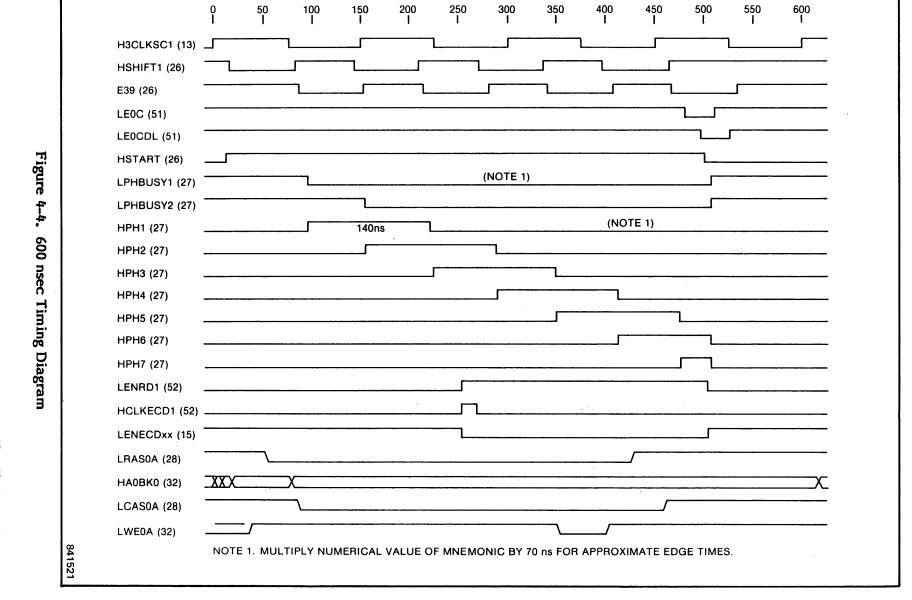

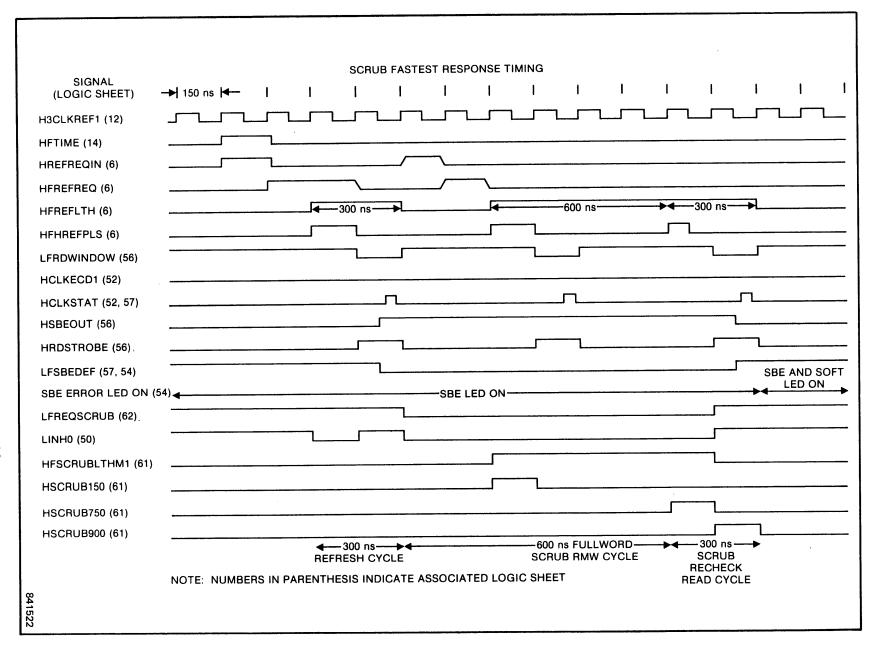

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8 | ISM Simplified Block Diagram                                                                                                                                      | 4-2<br>4-5<br>4-19<br>4-20<br>4-24<br>4-25 |

# LIST OF TABLES

| Table                                                | Title                                                                                                                                                                                                                            | Page                                         |  |  |  |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|

| 1-1<br>1-2                                           | ISM Storage Configurations                                                                                                                                                                                                       |                                              |  |  |  |

| 2-1<br>2-2<br>2-3                                    | Controls/Switches                                                                                                                                                                                                                | 2-4                                          |  |  |  |

| 2-3A<br>2-3B<br>2-3C                                 | Inhibit/Echo Jumper Chart - No Interleaving - Nonshared Inhibit/Echo Jumper Chart - 2-Way Interleaved Nonshared                                                                                                                  | 2-5                                          |  |  |  |

| 2-4                                                  | Inhibit/Echo Jumper Chart - No Interleaving - Shared                                                                                                                                                                             |                                              |  |  |  |

| 2-4A<br>2-4B                                         | Inhibit/Echo Jumper Chart - 2-Way Interleaved - Shared Inhibit/Echo Jumper Chart - 4-Way Interleaved - Shared                                                                                                                    | 2-6                                          |  |  |  |

| 2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11      | Starting Address Jumper Chart Offset Address Jumper Chart SelBUS Priority Jumpers Address Interleave Jumpers. Hard Jumpers. DRAM Type Select Jumpers Memory Bank Decode Select.                                                  | 2-8<br>2-9<br>2-10<br>2-13                   |  |  |  |

| 3-1<br>3-2<br>3-3<br>3-4                             | TX Transfer Operations                                                                                                                                                                                                           | 3-3<br>3-7                                   |  |  |  |

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-7<br>4-8<br>4-9 | Address Range Bank Locator Address Bit Locator SelBUS Pin List (All Signals) SelBUS Pin List (ISM Memory Module) ISM Data Formatter PROM (15E22) Check Parity Matrix Syndrome Word Decoding Matrix Syndrome Error Analysis Guide | 4-10<br>4-11<br>4-13<br>4-16<br>4-29<br>4-31 |  |  |  |

| 5-1                                                  | External Error Analysis Connector                                                                                                                                                                                                | 5-2                                          |  |  |  |

#### CHAPTER 1

#### GENERAL DESCRIPTION

#### 1.1 Introduction

The Integrated Storage Module (ISM), Model 3034, is a high density, low power, one megaword (four megabyte) memory module. It is contained on a single 15 by 18 inch printed circuit board therefore occupying only one SelBUS slot in any CONCEPT Computer System. It is a high performance, self-contained memory system. The ISM provides the capability for single-bit error correction and double-bit error reporting. The ISM is designed and manufactured by Gould Inc., Computer Systems Division, Ft. Lauderdale, Florida.

The information in this manual is presented in the following order:

| Chapter 1 | General Description             |

|-----------|---------------------------------|

| Chapter 2 | Installation and Operation      |

| Chapter 3 | SelBUS Transfers and Operations |

| Chapter 4 | Theory of Operation             |

| Chapter 5 | Maintenance                     |

#### 1.2 Features

The significant ISM features are listed below and a brief description of each feature is provided in the paragraphs that follow.

- o Read access time for 600ns to the SelBUS interface

- o Self-contained refresh logic

- o Scrubbing logic

- o Built-in error logger

- o Two deep input buffering

- o 1 Megaword (4 megabyte) storage capacity using 256K DRAMs

- o 4 MW (16MB) addressing capability

- o 64KW (256KB) address recognition boundaries

- o Optional read and lock capability

- o Three module interleaving options

- o Self-contained error correction code (ECC) logic

- o Compatible with existing battery back-up

#### 1.2.1 Read Access Time

Read access time of 600 nanoseconds to the SelBUS Interface is supported. The ISM also provides the following performance capabilities:

- Internal read memory access time of 300 nanoseconds.

- Internal read cycles initiated every 300 nanoseconds.

- Internal write cycles initiated every 300 nanoseconds.

- Internal write halfword or write byte cycles initiated every 600 nanoseconds.

# 1.2.2 Self-Contained Refresh Logic

A complete refresh cycle is performed every four milliseconds. Each refresh cycle time is 300 nanoseconds.

# 1.2.3 Self-Contained Scrubbing Logic

Scrubbing logic improves reliability by correcting soft correctable single-bit errors as they occur.

## 1.2.4 Built-In Error Logger

Nine on-board LEDs make up the error logger. Seven of the LEDs are used for displaying the error correction code (ECC) syndrome bits, and two LEDs are used to display the bank select bits.

#### 1.2.5 Two-Deep Input Buffering

Two-deep input buffering is provided for all cycles except halfword and byte write cycles.

# 1.2.6 One Megaword Storage Capability Using 256K DRAMs

The maximum storage capacity of the ISM is one megaword (four megabytes). This is achieved by using the 256K dynamic RAM (DRAM).

The 64K DRAM is also supported by the ISM. Maximum storage capacity using the 64K DRAM is 256KW (1MB).

#### 1.2.7 Four Megaword Addressing Capability

The ISM can be programmed to recognize an address range from zero to four megawords (16 megabytes).

#### 1.2.8 64KW Addressing Recognition Boundaries

The ISM can be programmed to recognize addresses in 64KW (256KB) increments over its address range.

# 1.2.9 Three Interleaving Options

There are three interleaving options available: no interleaving, two-way, or four-way interleaving. The interleaved modules must all contain the same memory capacity. Interleaving improves system performance for cache based CPU systems.

# 1.2.10 Optional Read and Lock Capability

The read and lock option allows a processor to lock out another processor while it is modifying data in a memory location. This feature can be disabled for optimum performance in single CPU applications. The option can be enabled for proper ISM operation in multi-processor applications.

# 1.2.11 Self-Contained Error Correction Code (ECC) Logic

On-board Error Correction Code (ECC) circuits correct single-bit errors and detect and/or report double-bit errors.

# 1.2.12 Compatible with Existing Battery Back-up

The ISM is compatible with the existing battery back-up system supported by Gould. The higher memory capacity of the ISM, and the use of low power logic circuits result in increased reliability, and longer back-up times when compared to existing memory modules.

# 1.3 Functional Description

The functional description is divided into seven major functional areas as listed below and briefly described in the paragraphs that follow. Detailed descriptions of these functions are provided in Chapter 4, Theory of Operation, of this manual.

- 1. SelBUS Interface

- 2. Error Correction Logic

- 3. Memory Refresh Logic

- 4. Scrubbing Logic

- 5. Memory Storage

- 6. Module Interleaving Options

- 7. Controls and Indicator Functions

# 1.3.1 SelBUS Interface

The ISM interface to the system is through the SelBUS Interface. The SelBUS is physically part of the chassis backplane, is completely passive, and contains no active electronic parts.

The data bus is 32 bits wide (one word or four bytes). The address bus uses 24 address bits to select up to four megawords (16 megabytes) of memory.

There are five basic memory transfer types supported on the SelBUS as listed below:

- 1. Memory Read Transfer (MRT)

- 2. Memory Write Transfer (MWT)

- 3. Memory Read and Lock Transfer (MRLT)

- 4. Memory Write and Unlock (MWUT)

- 5. Data Return Transfer (DRT)

Each transfer type requires three SelBUS cycles; polling, transfer, and response. By overlapping these cycles the SelBUS attains a transfer rate of one memory transfer every 150 nanoseconds.

## 1.3.2 Error Correction Code (ECC) Logic

The ISM contains Error Correction Code (ECC) circuitry to correct and report single-bit errors and detect and report double-bit errors. The error correction code adds seven bits to each 32 bit data word.

#### 1.3.3 Refresh

The ISM performs a refresh cycle every 15.6 microseconds. A refresh operation consists of a fullword read to one of the four banks in the ISM, and a Row Address Strobe (RAS) refresh cycle to the remaining three banks. The refresh cycle is transparent to the system operation.

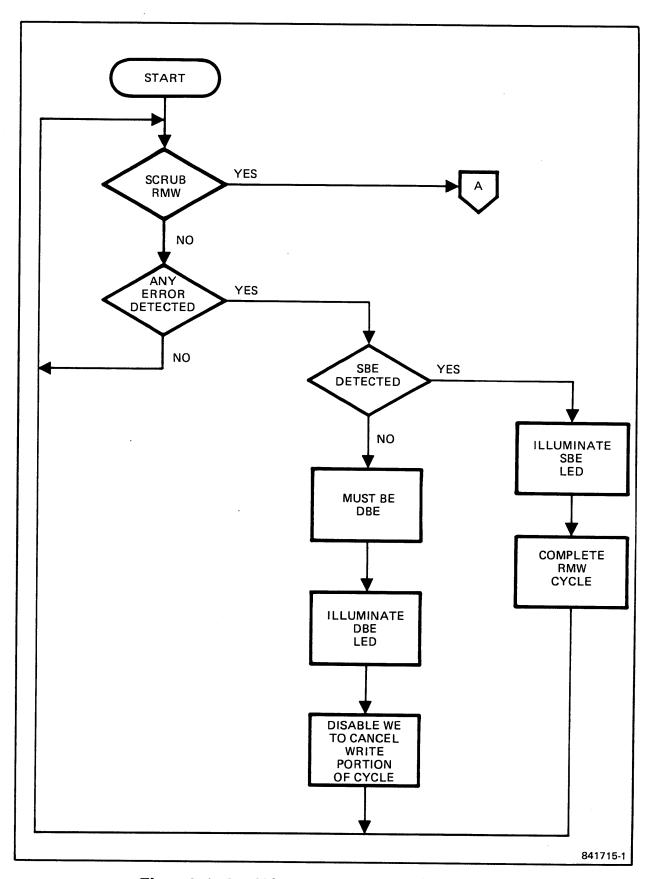

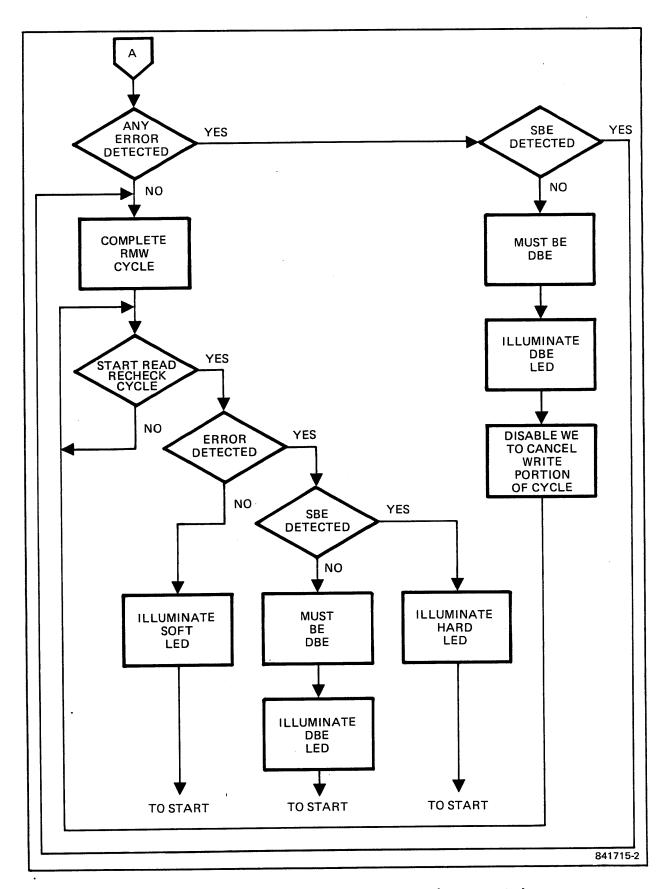

#### 1.3.4 Scrubbing

The scrubbing circuits of the ISM are used only when a refresh operation detects a single-bit error (SBE) condition. The scrubbing circuits perform read and write memory cycles to try to correct the SBE. If the SBE cannot be corrected, the HARD error LED is illuminated. If the SBE can be corrected, the SOFT error LED is illuminated.

## 1.3.5 Memory Storage

Table 1-1 lists the different ISM storage configurations for the ISM assembly 160-103723-XXX. All module types may be used together in the same chassis.

# 1.3.6 Module Interleaving

Module Interleaving is a method of mapping contiguous addresses into separate memory modules to permit overlapped memory operation. The ISM may be installed with no interleaving, two-way, or four-way interleaving. Interleaved modules must all have the same memory capacity. There is no modular interleaving performed within an ISM.

Table 1-1. ISM Storage Configurations

| ASSEMBLY<br>DASH<br>NUMBER | MEMORY<br>CHIP<br>USED | MEMORY<br>MODULE<br>CAPACITY |

|----------------------------|------------------------|------------------------------|

| -001                       | 256K DRAM              | 4MB (1MW)                    |

| -002                       | 256K DRAM              | 2MB (512KW)                  |

| -003                       | 256K DRAM              | 1MB (256KW)                  |

| -004                       | 64K DRAM               | 1MB (256KW)                  |

# 1.3.7 Controls and Displays

The ISM provides individual controls that reset the display, select scrubbing, select the type of error reported, and enable the error correction circuitry.

The ISM contains 14 LED displays. One is used to indicate an incorrect position of several of the controls. An error logger is used to isolate DRAM error conditions. SBE, Soft, Hard, and DBE displays are also provided.

### 1.4 Physical Description

Each ISM is mounted in the SelBUS logic chassis on either 0.6 inch or .75 inch centers depending on the logic chassis used. Figure 1-1 illustrates the physical location of the functional sections of the ISM. Controls and Indicators mounted on the ISM allow the user to control functions and observe the status of the module. Table 1-2 lists the physical, electrical, environmental, and operational specifications of the ISM.

Table 1-2. Integrated Storage Module Specifications

| PHYSICAL                                                               |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

|------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Length<br>Width<br>Height<br>Weight                                    | 18 inches<br>15 inches<br>0.4 inch m<br>4 lbs. | aximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| ELECTRICAL                                                             |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| Voltage                                                                | +5VDC (2:                                      | Supplies)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

| Power Dissipation                                                      | Voltage<br>(Volts)                             | Current<br>(Amps)<br>Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power<br>(Watts)<br>Max. |

| Active                                                                 | +5VA<br>+5VB                                   | 6<br>5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30 –<br>25               |

| Idle                                                                   | +5VA<br>+5VB                                   | 6<br>3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30<br>17 <b>.</b> 5      |

| Battery Backup (+5VB only)                                             | +5VA<br>+5VB                                   | <b>3.</b> 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <br>17.5                 |

| ENVIRONMENTAL                                                          |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ·                        |

| Temperature (Ambient)<br>Operating                                     |                                                | es to +104 degi<br>rees Celsius)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rees Fahrenheit (-10     |

| Storage                                                                |                                                | es to +140 degr<br>rees Celcius)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ees Fahrenheit (-40      |

| Relative Humidity<br>Operating<br>Storage/Transport                    | 20 to 80%<br>5% to 95%                         | (non-condensing (non-condensin (non-condensing (non-condensing (non-condensing (non-condensing | ng)<br>ing)              |

| Heat Dissipation/Active Heat Dissipation/Idle Heat Dissipation/Battery | 188 BTU p<br>162 BTU p                         | er hour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

| Backup<br>Altitude                                                     | 60 BTU pe Up to 10,0                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

Table 1-2. Integrated Storage Module Specifications (Continued)

| OPERATIONAL        |                                                                                                                                                                                                                   |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Word Length        | 39 bits total. 32 data bits plus seven error correction check bits                                                                                                                                                |

| Capacity           | 1MW (4MB) using 256K DRAMs 512KW (2MB) using 256K DRAM 256KW (1MB) using 256K DRAM 256KW (1MB) using 64K DRAMs                                                                                                    |

| Access Mode        | Random                                                                                                                                                                                                            |

| Read Access Time   | Internal 300nsec<br>SelBUS 600nsec                                                                                                                                                                                |

| Cycle Time         | Fullword Read 300nsec Fullword Write 300nsec Write halfword 600nsec Write byte 600nsec Refresh 300nsec                                                                                                            |

| Modes of Operation | Read fullword Read halfword/selected byte Write fullword Write halfword/selected byte Refresh cycle Scrub cycle                                                                                                   |

| Module Addressing  | Jumpers provided for manipulation of the address range.                                                                                                                                                           |

| Error Correction   | Error correction check bits generated and stored. Single-bit errors corrected. Double-bit errors detected and reported during normal operation.                                                                   |

| Refresh            | Each address location refreshed every 4 milliseconds. Sequential address locations refreshed every 15.6 microseconds. A Fullword read used to check for errors. If a SBE is detected, a scrub-cycle is requested. |

| Scrubbing          | Performed when requested. Corrects soft SBE to eliminate accumulation of errors. Reports SBEs as either soft or hard errors.                                                                                      |

#### CHAPTER 2

#### INSTALLATION AND OPERATION

#### 2.1 Introduction

This chapter describes the installation requirements for the Integrated Storage Module (ISM). The various switches and indicators are illustrated in Figure 2-1. Refer to Chapter 4 (Theory of Operation) for a detailed description of the switches and indicators.

#### 2.2 Installation

ISM's are mounted either horizontally or vertically as required SelBUS logic chassis.

#### 2.3 Operation

There are no operating procedures for the ISM, however, the following controls, indicators, and jumpers should be understood. The operating procedures for the CPU, System Control Panel, and the Operators Console are contained in the appropriate manual.

#### 2.4 Controls

The following on board controls are provided as a means of setting the ISM functions and monitoring certain ISM conditions.

A list of the ISM controls together with their on-board locations, associated logic sheet references, and paragraph in which they are explained is contained in Table 2-1.

#### 2.4.1 Switches

Toggle switches (two position) are located on the front of the ISM to control functions. The normal operating position for all toggle switches is the position shown in Figure 2-1.

#### 2.4.1.1 Display Error Switch (S1)

The normal operating position for this switch is the ON position. This switch controls the error detection LED's on the ISM. With the switch in the ON position, the LEDs are illuminated as required. With this switch in the CLR position, the error logger display will be reset.

Figure 2-1. ISM Front Controls and Displays

Table 2-1. Controls/Switches

| DESCRIPTION/<br>NOMENCLATURE<br>(POSITIONS) | IDENTIFIER | BOARD<br>LOCATION | LOGIC<br>SHEET | PARAGRAPH |

|---------------------------------------------|------------|-------------------|----------------|-----------|

| DISPLAY ERROR<br>(CLR/ON)                   | <b>S</b> 1 | FRONT             | 63             | 2.4.1.1   |

| SCRUB SWITCH<br>(OFF/ON)                    | S2         | FRONT             | 63             | 2.4.1.2   |

| ERROR TYPE SWITCH<br>(ANY/DBE)              | <b>S</b> 3 | FRONT             | 63             | 2.4.1.3   |

| ECC SWITCH<br>(OFF/ON)                      | 54         | FRONT             | 63             | 2.4.1.4   |

| LINE SWITCH<br>(OFF/ON)                     | S5         | FRONT             | 50             | 2.4.1.5   |

#### 2.4.1.2 Scrub Switch (S2)

The normal operating mode for this switch is in the ON position. With the switch in the ON position the scrubbing circuits are enabled if the ECC switch is also on. With the switch in the OFF position, the scrubbing circuits are disabled. The Refresh circuits on the ISM continue regardless of the position of this switch.

#### 2.4.1.3 Error Type Switch (S3)

The normal operating mode for this switch is the DBE position. In the DBE position, only double-bit errors are reported. If the switch is in the ANY position, a single-bit or double-bit error will be reported. If an error occurs, the LERROR signal will be sent on the SelBUS if the LERROR report jumper is enabled.

### 2.4.1.4 ECC Switch (S4)

The normal operating mode for this switch is the ON position. In the ON position error correction is enabled. If the Scrub switch is also in the ON position, the scrubbing circuits are also enabled.

With the ECC switch in the OFF position, the error correction is disabled. Also, in the OFF position, the scrubbing circuits are disabled since the Scrubbing feature relies on correction cycles for its operation. While in the OFF position write requests by the SelBUS will continue to write the correct syndrome bits. Read requests from the SelBUS will check the syndrome bits and report errors as selected by the LERROR report jumper. (See jumper section.)

## 2.4.2 Jumpers

There are two basic types of jumpers; hard jumpers and soft jumpers. The following paragraphs describe each type.

# 2.4.2.1 Soft Jumpers

Soft jumpers are either two pin plug-in assemblies or 16 pin IC jumpr modules. These jumpers are used to set up various system parameters and are intended to be changed in the field. Table 2-2 provides a list of soft jumpers.

### 2.4.2.1.1 Inhibit (X5 1-4)