# Gould Eight-Line Asynchronous Communications Multiplexer Model 8512-2 Technical Manual

January 1985

Publication Order Number: 303-006180-000

This manual is supplied without representation or warranty of any kind. Gould Inc., Computer Systems Division therefore assumes no responsibility and shall have no liability of any kind arising from the supply or use of this publication or any material contained herein.

Copyright 1985

Gould Inc., Computer Systems Division

All Rights Reserved

Printed in U.S.A.

# **HISTORY**

The Gould Eight-Line Asynchronous Communications Multiplexer, Model 8512-2 Technical Manual, Publication Order Number 303-006180-000, was printed January 1985.

This manual contains the following pages:

Title page

Copyright page

iii/iv through x

1-1 through 1-12

2-1/2-2

3-1 through 3-18

4-1 through 4-42

A-1 through A-3/A-4

IN-1 through IN-4

# **CONTENTS**

| Chapte                                               | er                                                                                                                                                                |                                          |                                               |                   |                                         |             | <u>P</u> | age                                                                                              |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------|-------------------|-----------------------------------------|-------------|----------|--------------------------------------------------------------------------------------------------|

| 1 INT                                                | RODUCTION                                                                                                                                                         |                                          |                                               |                   |                                         |             |          |                                                                                                  |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8 | Features Applicability Prerequisites Configuration Specification Physical Descriptional D 1.8.1 Cor 1.8.2 Ma: 1.8.3 Eig M 1.8.1 1.8 1.8 1.8 1.8 1.8 1.8 1.8 1.8 1 | nss cription .escription mmunicat        | ion System                                    | munications coder | · · · · · · · · · · · · · · · · · · ·   |             |          | 1-2<br>1-2<br>1-2<br>1-2<br>1-3<br>1-3<br>1-3<br>1-5<br>1-5<br>1-5<br>1-8<br>1-8<br>1-11<br>1-11 |

| 2 OP                                                 | PERATION                                                                                                                                                          |                                          |                                               |                   |                                         |             |          |                                                                                                  |

| 2.1<br>2.2<br>2.3                                    | Initialization                                                                                                                                                    | ,                                        |                                               |                   |                                         | <br>        |          | . Z-i                                                                                            |

| 3 PR                                                 | ROGRAMMINO                                                                                                                                                        |                                          |                                               |                   |                                         |             |          |                                                                                                  |

| 3.1<br>3.2                                           | Basic Instruction Survey                                                                                                                                          | ction For<br>b Op Cod                    | matles                                        |                   | · • • • • • • • • • • • • • • • • • • • | <br>• • • • | • • •    | . 3-1<br>. 3-2                                                                                   |

| 3.3<br>3.4                                           | Status Doub<br>Input/Outpu<br>3.4.1 Wi<br>3.                                                                                                                      | lewords<br>t Comma<br>rite Comi<br>4.1.1 | and Doublewords . mands Write Write with Inpu |                   |                                         | <br>• • • • | • • •    | . 3-2                                                                                            |

|                                                      |                                                                                                                                                                   | 4.1.2<br>4.1.3                           | Monitoring Write with Har                     | dware Flow        |                                         |             |          |                                                                                                  |

|                                                      |                                                                                                                                                                   |                                          | Control Only                                  |                   |                                         | <br>        |          | . 3-5                                                                                            |

| Chapt | <u>er</u> |               |                                       | Page  |

|-------|-----------|---------------|---------------------------------------|-------|

|       | 3.4.2     | Read Comma    | ands                                  |       |

|       |           | 3.4.2.1       | Read                                  | . 3-5 |

|       |           | 3.4.2.2       | Read Echoplex                         |       |

|       |           | 3.4.2.3       | Read with Flow Control                | . 3-6 |

|       |           | 3.4.2.4       | Read with Hardware Flow               |       |

|       |           |               | Control Only                          |       |

|       | 3.4.3     |               | mands                                 |       |

|       |           | 3.4.3.1       | Define ACE Parameters                 |       |

|       |           | 3.4.3.2       | NOP (No Operation)                    |       |

|       |           | 3.4.3.3       | Define Special Character              |       |

|       |           | 3.4.3.4       | Reset Data Terminal Ready (DTR)       |       |

|       |           | 3.4.3.5       | Set Data Terminal Ready (DTR)         |       |

|       |           | 3.4.3.6       | Reset Request to Send (RTS)           |       |

|       |           | 3.4.3.7       | Automatic Handling of RTS and DTR     | . 3-9 |

|       |           | 3.4.3.8       | Set Request To Send (RTS)             | . 3-9 |

|       |           | 3.4.3.9       | Reset Break                           |       |

|       |           | 3.4.3.10      | Set Break                             |       |

|       |           | 3.4.3.11      | Sense Status                          |       |

| 3.5   |           | gramming      |                                       | 3-16  |

|       | 3.5.1     |               | MA Controller                         | 3-16  |

|       | 3.5.2     |               | s Communication Element               |       |

|       |           |               |                                       |       |

|       | 3.5.3     | I/O Processo  | r                                     | 3-18  |

| 4 THI | EORY OF   | OPERATION     |                                       |       |

| 4.1   | MP Bus I  | nterface Info | rmation Transfers                     | . 4-1 |

|       | 4.1.1     | Service Requ  | uest (SRQ) Initiated Information      |       |

|       |           |               |                                       | . 4-1 |

|       | 4.1.2     |               | ated Information Transfers            |       |

| 4.2   | Service ! |               | Protocol Sequence                     |       |

|       | 4.2.1     |               | ing Sequence                          |       |

|       | 4.2.2     |               | g Šequence                            |       |

|       | 4.2.3     |               | g Sequence Termination                |       |

|       | 4.2.4     |               | rotocol Sequence                      |       |

| 4.3   |           |               | Sequences                             |       |

|       | 4.3.1     |               | fer Sequence                          |       |

|       | 4.3.2     | Control Sign  | al Transfer Sequence                  | . 4-9 |

|       | 4.3.3     |               | fer Sequence                          |       |

|       | 4.3.4     |               | ransfer Sequence                      |       |

|       | 4.3.5     |               | Command Transfer Sequence             |       |

|       | 4.3.6     |               | er Sequence                           |       |

|       |           | 4.3.6.1       | Data Output (Write) Transfer Sequence |       |

|       |           |               | Data Input (Read) Transfer Sequence   |       |

|       | 4.3.7     |               | ••••••••••                            |       |

| 4.4   |           | •             | 1                                     |       |

|       | 4.4.1     |               | ce                                    |       |

|       | 4.4.2     |               | Decode                                |       |

|       | 4.4.3     |               | gic                                   |       |

|       | 4.4.4     |               | 5                                     |       |

|       | 4.4.5     |               | ontroller                             |       |

|       | 4.4.6     |               | oller                                 |       |

|       | 4.4.7     |               |                                       |       |

| Chapt | er       |                                                | Page                  |

|-------|----------|------------------------------------------------|-----------------------|

|       | 4.4.8    | Port 0 through 7                               | 4-21                  |

| 4.5   | Detailed | Circuit Description                            | 4-21                  |

| 4.7   | 4.5.1    | MPC Connector (Sheet 2)                        | 4-21                  |

|       | 4.5.2    | Microprocessing Unit (Sheet 3)                 | 4-21                  |

|       |          | Clock Generator                                | 4-22                  |

|       | 4.5.3    | MPU Input Signals                              | 4-22                  |

|       | 4.5.4    |                                                | 4-22                  |

|       |          |                                                | 4-22                  |

|       |          |                                                | 4-22                  |

|       |          |                                                | 4-22                  |

|       |          | 4.5.4.4 Bus Request (BUSREQ)                   | 4-23                  |

|       | 4.5.5    | MPU Output Signals                             | 4-23                  |

|       |          | 4.5.5.1 Input/Output Request (IORQ)            | 4-23                  |

|       |          | 4.5.5.2 Read (RD)                              |                       |

|       |          | 4.5.5.3 Write (WR)                             | 4-23                  |

|       |          | 4.5.5.4 Refresh (RFSH)                         |                       |

|       |          | 4.5.5.5 Machine Cycle One (M1)                 |                       |

|       |          | 4.5.5.6 Memory Request (MREQ)                  | -                     |

|       |          | 4.5.5.7 Bus Acknowledge (BUSAK)                | -                     |

|       |          | 4.5.5.8 Address Bits (A0 through A15)          |                       |

|       | 4.5.6    | Input/Output Signals (Data Bits D0 through D7) |                       |

| 4.6   |          |                                                |                       |

|       | 4.6.1    | Read (RD)                                      | •                     |

|       | 4.6.2    | Write (WR)                                     |                       |

|       | 4.6.3    | Input/Output Request (IOREQ)                   | •                     |

|       | 4.6.4    | Enable                                         |                       |

| 4.7   |          | ver                                            | •                     |

|       | 4.7.1    | Direction (DIR)                                |                       |

|       | 4.7.2    | Enable                                         | •                     |

| 4.8   | I/O Addı | ress Decode (Sheet 4)                          | •                     |

| 4.9   |          | t Logic (Sheet 5)                              | •                     |

|       | 4.9.1    | Clear                                          | •                     |

|       | 4.9.2    | Address Generation                             | -                     |

| 4.10  |          | (Sheet 6)                                      | -                     |

|       | 4.10.1   | Memory Chip Select (Addressing)                | •                     |

|       | 4.10.2   | Memory Data                                    | . 4-29                |

| 4.11  |          | terface (Sheet 7)                              |                       |

|       | 4.11.1   | Service Request (LSRQ)                         | •                     |

|       | 4.11.2   | Address Generator                              | -                     |

|       | 4.11.3   | Parity Generator/Checker                       |                       |

|       |          | 4.11.3.1 Parity Check                          | -                     |

|       |          | 4.11.3.2 Parity Generator                      |                       |

|       | 4.11.4   | Baud Clock Generator                           |                       |

| 4.12  |          | terface (Sheet 8)                              |                       |

|       | 4.12.1   | Data Lines (LDI00 through LDI07)               | -                     |

|       | 4.12.2   | Parity                                         | -                     |

|       | 4.12.3   | MP Bus Controls                                |                       |

|       | 4.12.4   | Interface Clear (LIFC)                         |                       |

| 4.13  |          | alker/Listener                                 |                       |

|       | 4.13.1   | Data Bus Port (D0 through D7)                  |                       |

|       | 4.13.2   | GPIB Data Port (DI01 through DI08)             |                       |

|       | 4.13.3   | Handshake Controls                             |                       |

|       |          |                                                |                       |

|       |          | 4.13.3.2 Not Ready for Data (NRFD)             | , , <del>,</del> -,,, |

| Chapte | <u>er</u>                               |                      |                                       | Page |

|--------|-----------------------------------------|----------------------|---------------------------------------|------|

|        |                                         | 4.13.3.3             | Not Data Accepted (NDAC)              | 4-33 |

|        | 4.13.4                                  | Command Co           |                                       |      |

|        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 4.13.4.1             | Attention (ATN)                       |      |

|        |                                         | 4.13.4.2             | Interface Clear (IFC)                 |      |

|        |                                         | 4.13.4.3             | Service Request (SRQ)                 |      |

|        |                                         | 4.13.4.4             | End or Identify (EOI)                 |      |

|        | 4.13.5                                  |                      | S                                     |      |

|        | 161363                                  | 4.13.5.1             | DMA Request (DREQ)                    | 4-33 |

|        |                                         | 4.13.5.2             | DMA Acknowledge (DACK)                |      |

|        | 4.13.6                                  |                      | Controls                              | 4-34 |

|        | 161360                                  | 4.13.6.1             | Transceiver Control 1 (TR1)           |      |

|        |                                         | 4.13.6.2             | Transceiver Control 2 (TR2)           |      |

|        | 4.13.7                                  | MPU Control          |                                       |      |

|        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 4.13.7.1             | Register Select Inputs                |      |

|        |                                         | 10130701             | (RS0 through RS2)                     | 4-34 |

|        |                                         | 4.13.7.2             | Read Strobe (RD)                      |      |

|        |                                         | 4.13.7.3             | Write Strobe (WR)                     |      |

|        |                                         | 4.13.7.4             | Chip Select (CS)                      |      |

|        |                                         | 4.13.7.5             | Interrupt Request (INT)               |      |

|        | 4.13.8                                  |                      | s Controls                            |      |

|        | 1.13.0                                  | 4.13.8.1             | Clock (CLK)                           |      |

|        |                                         | 4.13.8.2             | Trigger Output (TRIG)                 |      |

|        |                                         | 4.13.8.3             | Reset                                 | 4-35 |

| 4.14   | MPC FOI                                 |                      | heet 9)                               |      |

| 7017   | 4.14.1                                  |                      |                                       |      |

|        | 4.14.2                                  |                      | ct                                    |      |

|        | 4.14.3                                  |                      |                                       |      |

| 4.15   |                                         |                      | 10)                                   |      |

| 7.17   | 4.15.1                                  |                      |                                       |      |

|        | 4.15.2                                  | Active Cycle         |                                       |      |

|        | 4.15.3                                  |                      | ers                                   |      |

|        | 4.15.4                                  |                      | :TS                                   |      |

|        | 4.15.5                                  |                      |                                       |      |

|        | 4.17.7                                  | 4.15.5.1             | Program Condition                     |      |

|        |                                         | 4.15.5.2             | Read/Write Transfers                  |      |

|        | 4.15.6                                  |                      | eration                               |      |

|        | 4.15.7                                  | Clear (Reset)        |                                       |      |

|        | 4.15.8                                  | Orear (recover)      | ,                                     |      |

| 4.16   |                                         |                      | igh 14)                               |      |

| 4.10   | 4.16.1                                  |                      | S Communications Element              |      |

|        | 4.16.2                                  | Input Signals        | · · · · · · · · · · · · · · · · · · · |      |

|        | 4.10.2                                  | 4.16.2.1             | Chip Select (CS2)                     |      |

|        |                                         | 4.16.2.2             | Data Input Strobe (DISTR)             |      |

|        |                                         | 4.16.2.3             | Data Output Strobe (DOSTR)            |      |

|        |                                         | 4.16.2.4             | Register Select (A0 - A2)             |      |

|        |                                         | 4.16.2.4<br>4.16.2.5 | External Clock (XTAL1)                |      |

|        |                                         | 4.16.2.6             | Master Reset (MR)                     |      |

|        |                                         | 4.16.2.7             | Receiver Clock (RCLK)                 |      |

|        |                                         | 4.16.2.8             | Serial Input (SIN)                    |      |

|        |                                         | 4.16.2.9             | Clear to Send (CTS)                   |      |

|        |                                         | 4.16.2.10            | Data Set Ready (DSR)                  |      |

|        |                                         | 4.16.2.11            | Received Line Signal Detect (RLSD)    |      |

|        |                                         | 4.16.2.12            | Ring Indicator (RI)                   | 4-40 |

| Chapt        | er                 |                                            |                                                                                       | Page                       |

|--------------|--------------------|--------------------------------------------|---------------------------------------------------------------------------------------|----------------------------|

|              | 4.16.3             | 4.16.3.1 E<br>4.16.3.2 E<br>4.16.3.3 I     | Data Terminal Ready (DTR)  Baud Out (BAUDOUT) Interrupt (ITRPT)  Serial Output (SOUT) | 4-41<br>4-41<br>4-41       |

|              | 4.16.4             | 4.16.3.5 Enput/Output S                    | Request to Send (RTS)                                                                 | . 4-41<br>. 4-41<br>. 4-41 |

| 4.17         | Buffers/           | Dulinana                                   |                                                                                       | . 4-42                     |

| 4.18         | Distribu<br>4.18.1 | tion Panels<br>RS-232C Distr<br>Model 8580 | ibution Panel                                                                         | • 1- 12                    |

|              | 4.18.2             | 20-Milliamper<br>Panel Model               | e Current Loop Distribution 8582                                                      | . 4-47                     |

| APPE<br>INDE | ENDIX A .<br>X     |                                            |                                                                                       | . A-1                      |

# **ILLUSTRATIONS**

| Figure     | <del>-</del>                                                      | Page   |

|------------|-------------------------------------------------------------------|--------|

| 1-1<br>1-2 | Communication System, Block Diagram                               | . 1-6  |

|            | Diagram                                                           | . 1-7  |

| 1-3        | Eight-Line Asynchronous Communications Multiplexer, Block Diagram | . 1-9  |

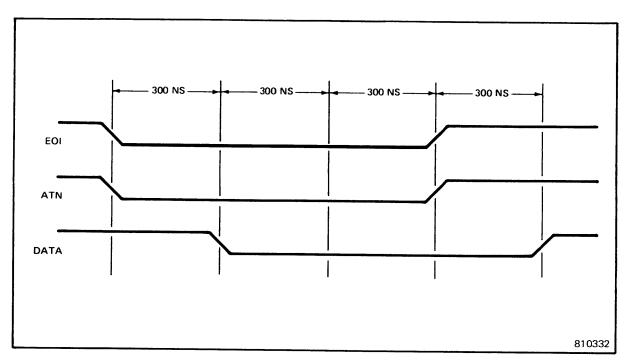

| 4-1        | Parallel Polling Sequence Timing Diagram                          |        |

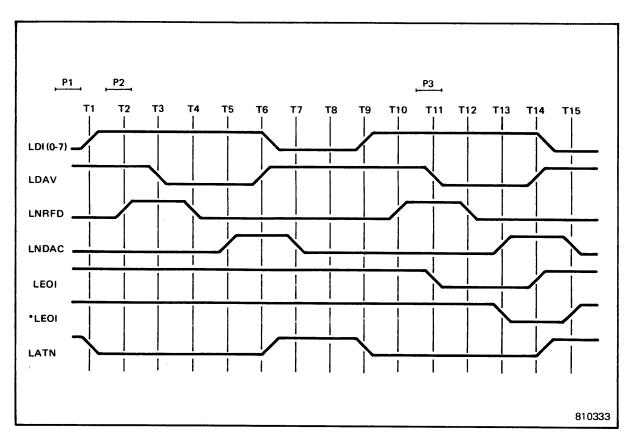

| 4-2        | Handshake Protocol Timing Diagram                                 | . 4-7  |

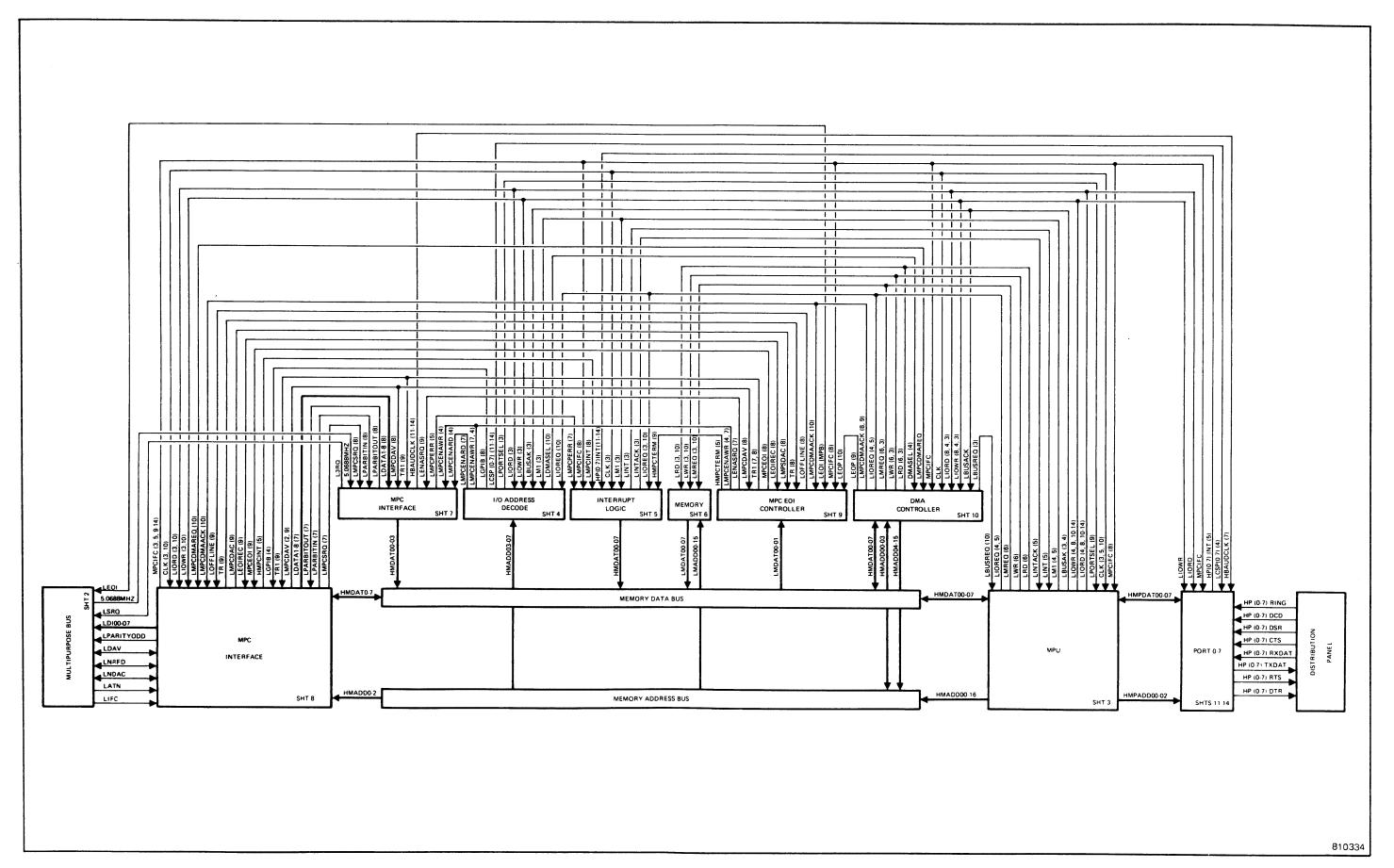

| 4-3        | Functional Block Diagram                                          | . 4-19 |

|            | TABLES                                                            |        |

| 1-1        | Eight-Line Asynchronous Communications Multiplexer                |        |

| 1-1        | Specifications                                                    | . 1-4  |

| 4-1        | Poll Priorities                                                   | . 4-4  |

| 4-2        | Extended I/O Commands                                             | . 4-14 |

| 4-3        | Decoded Address Bits                                              | . 4-26 |

| 4_4        | Interrupt Priority/Address                                        | . 4-28 |

| 4-5        | Memory Chip Select Addresses                                      | . 4-29 |

| 4-6        | Parity Generator/Checker Truth Table                              |        |

| 4-7        | ACE Register Addresses                                            | . 4-41 |

#### CHAPTER 1

#### INTRODUCTION

## 1.1 General Description

The Model 8512-2 Gould Eight-Line Asynchronous Communications Multiplexer controls communication between the central processing unit (CPU) of the Gould 32/7X Series computer, or Gould CONCEPT/32<sup>TM</sup> computers, and up to eight terminals and/or modems. Communication between the CPU and the external I/O device takes place through the Model 8000 or 8001 Input/Output Processor (IOP) via the multipurpose bus (MP Bus).

The multiplexer handles asynchronous data formats with five to eight bits per characters; with one, one and a half, or two stop bits; and even, odd, forced, or no parity.

The Eight-Line Asynchronous Communications Multiplexer interfaces with peripheral devices, with RS-232C or 20-milliampere current loop interfaces, via a distribution panel. Models 8580 and 8582 distribution panels are available to convert the signal levels and pinouts to the RS-232C or the 20-milliampere current loop protocols.

#### 1.2 Features

The Eight-Line Asynchronous Communications Multiplexer has the following features:

- 1. Controls up to eight terminals and/or modems.

- 2. Sixteen data transmission speeds up to 19,200 bits per second.

- 3. Peak aggregate transfer rate of 76,800 bits per second and an average aggregate rate of 40,000 bits per second.

- 4. Selectable controller address.

- 5. Internal loopback mode for diagnostic testing.

- 6. Modem control.

- 7. Type ahead.

- 8. Full or half duplex.

- 9. Software configurable on a per line basis.

# 1.3 Applicability

The Eight-Line Asynchronous Communications Multiplexer can be used on the Gould 32/7X Series computers, and on CONCEPT/32 computers, designed and manufactured by Gould Inc., Computer Systems Division, which meet the required prerequisites.

# 1.4 Prerequisites

The computer must be equipped with the IOP. The Eight-Line Asynchronous Communications Multiplexer requires one multipurpose bus backplane slot.

# 1.5 Configurations

The following configurations are available with the Eight-Line Asynchronous Communications Multiplexer:

- 1. EIA RS-232C physical protocol.

- a. Model 8580 Distribution Panel Assembly.

- b. Model 8590 Cable P/N 145-103020-4XX Interface cable between distribution panel and customer modem.

- c. Cable 145-103020-3XX Interface between the distribution panel and CRT terminal (Televideo 910, Hazeltine 1500, or ADM-3).

- d. Cable 144-103416 Two 60-pin flat cables for interfacing the eight-line asynchronous communications multiplexer and the Model 8580 Distribution Panel.

- e. Cable 145-103071-XXX Flow Control Cables.

- 2. Twenty-milliampere current loop physical protocol.

- a. Model 8582 Distribution Panel Assembly.

- b. Cable 144-103437-001 Power cable between eight-line asynchronous communications multiplexer and distribution panel.

- c. Cable 145-103020-2XX Interface between Model 8582 Distribution Panel and the ADM-3 CRT terminal.

- d. Cable 145-103020-1XX Interface between the Model 8582 Distribution Panel and the Televideo 910 or Hazeltine 1500 CRT terminal.

- e. Cable 144-103004-024 Two 40-pin flat cables for interfacing between eight-line asynchronous communications multiplexer and the Model 8582 Distribution Panel.

# 1.6 Specifications

Table 1-1 lists the physical, electrical, and environmental specifications of the Eight-Line Asynchronous Communications Multiplexer.

## 1.7 Physical Description

The Eight-Line Asynchronous Communications Multiplexer is comprised of the eight-line asynchronous communication multiplexer printed wiring (PW) board, 160-103768 and one of two distribution panels, Model 8580 or Model 8582.

The board contains a Z80<sup>®</sup> CPU, peripheral logic to interface between the multipurpose bus and the peripheral device, programmable read only memories (PROMs) to store the control program, random access memories (RAMs) for data and parameter storage, and eight asynchronous communication elements (ACE) for data and signal control over the output lines. The ACE is also referred to in this manual as a Universal Asynchronous Receiver/Transmitter (UART).

The eight-line asynchronous board occupies one backplane slot in the I/O chassis and is interconnected to the distribution panel by two 40-pin flat ribbon cables and one 14-pin power cable for the 20-milliampere current loop operation, and by two 60-pin flat ribbon cables for the RS-232 operation.

The eight-line asynchronous distribution panel is mounted on the cabinet panel mounting rails and provides eight serial bidirectional ports for connection to peripheral devices.

The Eight-Line Asynchronous Communications Multiplexer is supplied with one of two distribution panels, depending on the physical protocol that is to be supported.

# 1.8 Functional Description

The following is a brief functional description of a communication system using the Eight-Line Asynchronous Communications Multiplexer.

# 1.8.1 Communication System

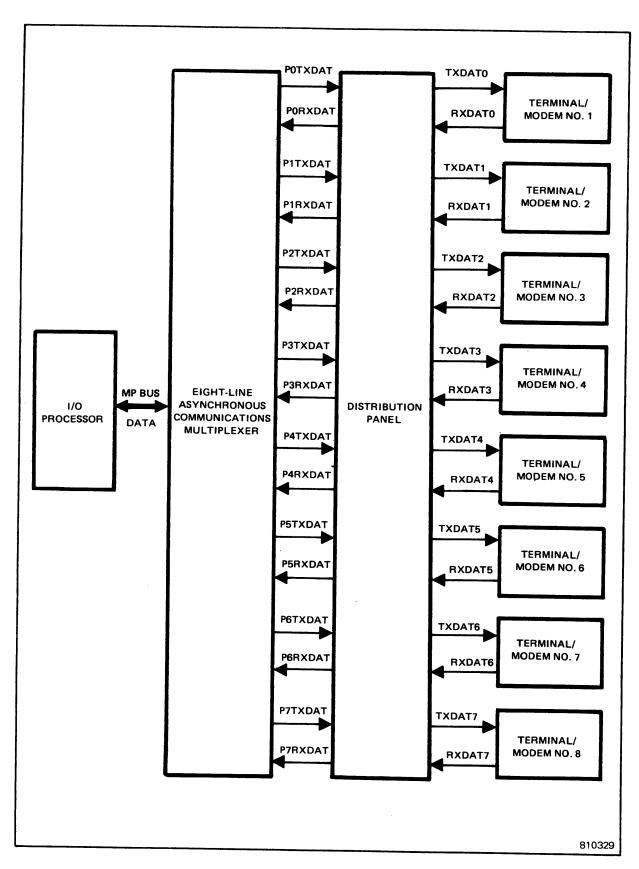

The block diagram of Figure 1-1 shows the data flow of a communication system using the Eight-Line Asynchronous Communications Multiplexer. The MP Bus is the interface between the IOP and the multiplexer. Information from the IOP is applied to eight parallel data lines of the MP Bus. The multiplexer accepts the data using the three-wire handshake protocol and performs a parallel-to-serial conversion. It also transmits the data (P0TXDAT through P7TXDAT) from the selected port (port 0 through port 7) to a distribution panel.

The distribution panel provides the signal levels and pinouts which are compatible with the protocol of the terminal or modem. The information is transferred to the appropriate terminal or modem, as determined by the selected port, using the established protocol. Information transfers can be initiated by the terminal or modem using the established protocol of the device. The distribution panel accepts the serial information on one of the receive data lines (RXDATO through RXDAT7).

The information is sent to the multiplexer on one of the serial port receive data (PORXDAT through P7RXDAT) lines. The multiplexer performs a serial-to-parallel conversion and transmits the information to the IOP on the eight parallel data lines of the MP Bus, using the three-wire handshake protocol.

<sup>®</sup> Z80 is a registered trademark of Zilog, Inc.

Table 1-1

Eight-Line Asynchronous Communications Multiplexer Specifications

| Characteristic                                                                                        | Specification                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical PC Board Length Width Mounting                                                               | 15 in. (38.1 cm)<br>12 3/4 in. (32.2 cm)<br>One backplane slot                                                                                                                                                                              |

| Distribution Panels<br>Length<br>Width<br>Height<br>Mounting                                          | 4 in. (10.2 cm) 19 in. (48.3 cm) 3.5 in. (8.9 cm) Industry standard, 19-inch panel width with EIA hole spacing                                                                                                                              |

| Environmental Operating Temperature Relative humidity Storage Temperature Relative humidity BTUs/Min. | 0° to 50°C (32° to 122° F)<br>20% to 80%, noncondensing<br>-25° to 70°C (-12.8° to 158°F)<br>5% to 95%, noncondensing<br>220                                                                                                                |

| Electrical Voltage  Current                                                                           | +5 vdc -5 vdc +15 vdc, with Model 8582 Distribution Panel 2.5 A at +5 vdc 100 mA at -5 vdc, with Model 8582 Distribution Panel 60 mA at -5 vdc, without Model 8582 Distribution Panel 320 mA at +12 vdc, with Model 8582 Distribution Panel |

| Performance Data Format Characters Stop bits Parity Data throughput Total (eight lines)               | Asynchronous 5, 6, 7, or 8 bits 1, 1.5, or 2 bits Even, odd, forced, or no parity  76,800 bits per second, peak (function of operational mode) 40,000 bits per second, average                                                              |

| Per line                                                                                              | 19,200 bits per second, maximum                                                                                                                                                                                                             |

| Protocol (Interface)                                                                                  | RS-232C and 20-milliampere current loop                                                                                                                                                                                                     |

## 1.8.2 Maximum Configuration

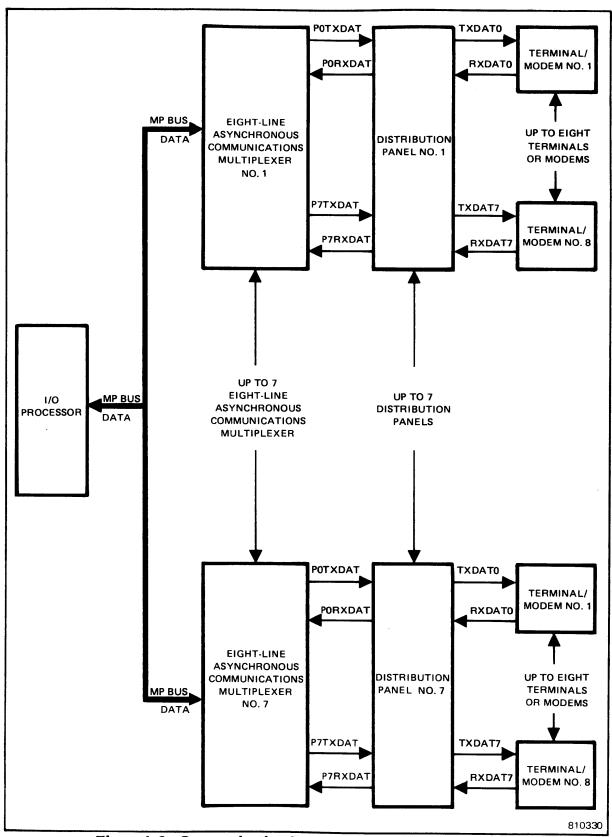

Figure 1-2, the communication system maximum configuration, shows the interconnection between the IOP and the terminals/modems, using up to 7 Eight-Line Asynchronous Communications Multiplexers.

The MP Bus is the interface between the IOP and up to 7 multiplexers. Each multiplexer can support eight port transmit data (POTXDAT through P7TXDAT) lines to the distribution panel. This allows the computer to communicate with up to 56 external devices (terminals and/or modems).

The distribution panel can distribute up to eight transmit (TXDAT0 through TXDAT7) signals and eight receive (RXDAT0 through RXDAT7) signals to terminals or modems. The terminals or modems connected to the same distribution panel must have the same protocol.

# 1.8.3 Eight-Line Asynchronous Communications Multiplexer

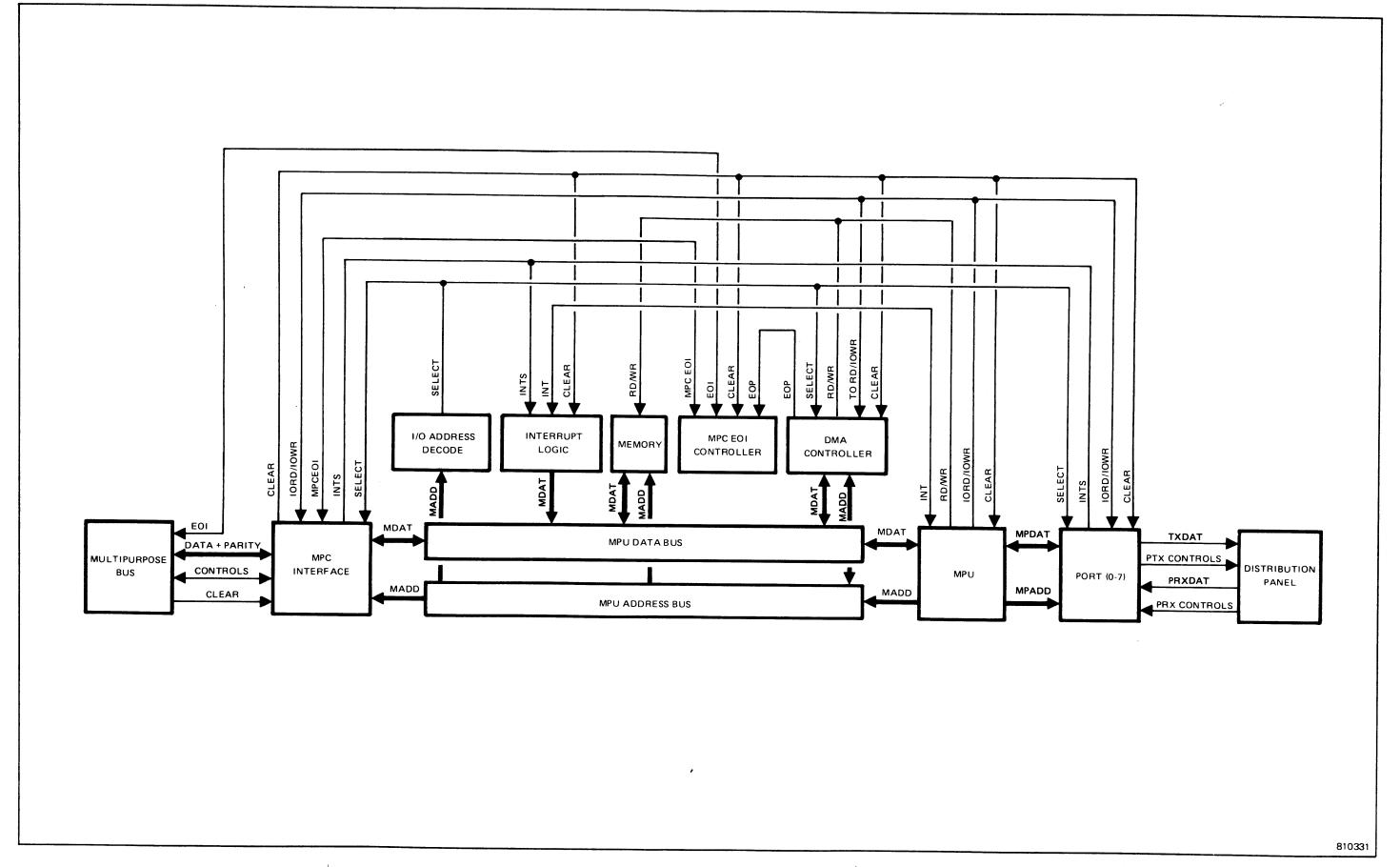

Figure 1-3 is a simplified Eight-Line Asynchronous Communications Multiplexer block diagram that shows the functional blocks of the multiplexer, the major control signals, and the data and address lines.

The functional blocks are as follows:

- 1. MPC interface (interfaces with the MP Bus)

- 2. I/O address decode

- 3. Interrupt logic

- 4. Memory

- 5. MPC EOI controller

- 6. DMA controller

- 7. Microprocessing unit (MPU)

- 8. Port (0 through 7)

The entire operation of the multiplexer is under the control of the microprocessor unit (MPU). The MPU controls the information transfers between the MPC interface and the MPU, between the MPC interface and memory, between the MPU and memory, between the MPU and the direct memory access (DMA) controller, and between the ports (0 through 7) and the MPU. The DMA controller can control the information transfers between the MPC interface and memory when it is programmed by the MPU to do so. The microprocessor has control of the bus (DMA single cycle mode) between DMA transfers.

#### 1.8.3.1 MPC Interface

The mnemonic MPC refers to the nomenclature multipurpose controller. As used in this manual it is synonymous to the I/O Processor (IOP).

The MPC interface, which connects to the MP Bus, contains the logic necessary for information transfers between the MP Bus and the multiplexer. The interface also contains the logic necessary for controlling information transfers between the microprocessor unit (MPU) and the interface and between memory and the interface.

Figure 1-1. Communication System, Block Diagram

Figure 1-2. Communication System, Maximum Configuration, Block Diagram

Eight bidirectional data lines and one parity line effect information transfers between the MP Bus and the interface. The bidirectional handshake controls effect the information transfers.

The MPC interface checks parity (odd) during information transfers from the MP Bus to the interface and generates parity (odd) during information transfers to the MP Bus.

The controls contain the bidirectional three-wire handshake control lines which effect the information transfers from and to the MP Bus. Either the MP Bus or the MPC interface can initiate information transfers.

The MP Bus uses the handshake control lines to initiate and effect information transfers. The MPC interface initiates information transfers requesting service from the MP Bus. The bus then goes through a polling sequence to determine which multiplexer (of a possible 7), with the highest priority, requested the service. The information is then transferred to the MP Bus using the handshake control lines.

The clear line from the MP Bus is used to initialize the multiplexer. The clear signal is received at the MPC interface and distributed to other functional blocks.

The I/O read (IORD) and I/O write (IOWR) signals are generated by the MPU. The MPU uses the read and write signals to transfer information to and from the data bus (DBUS). The particular register in the MPC interface, which is to be read from or written to, is defined by the MPU via the address bus.

The MPC end or identity (EOI) line is bidirectional and comes from the MP Bus controller to indicate the end of a multibyte information transfer sequence. The EOI signal is generated by the MPC interface logic or received from the MP Bus controller.

When the MPC interface logic detects a parity error, an interrupt is generated.

#### 1.8.3.2 I/O Address Decoder

The I/O address decoder receives address bits from the MPU via the MPU address bus. The address bits are decoded to generate a select signal to the MPC interface, the DMA controller, or one of the eight ports.

# 1.8.3.3 Interrupt Logic

The interrupt logic receives interrupts from the MPC interface and from the eight ports. The interrupt logic generates the INT signal to the MPU and places the interrupt vector on the MPU data bus. The MPU uses the vector to locate an interrupt handler which will process the particular interrupt.

# 1.8.3.4 Memory

The memory functional block is comprised of PROMs and RAMs.

Model 8512-2 has a memory consisting of three (2KX8) PROMs and two (2KX8) RAMs.

The PROMs contain the firmware program to control the operation of the multiplexer and are sometimes referred to as the control read only memory (CROM). The RAMs temporary information storage.

The read/write (RD/WR) controls enable reading from and writing to a RAM location, as defined by the address on the MPU address bus. Only the read signal is used to access the PROMs.

# 1.8.3.5 MPC EOI Controller

The MPC interface logic enables and disables the receipt and generation of the EOI to the MP Bus. The MPCEOI signal is generated when the MPC interface receives an EOI signal. Both the EOI and the MPCEOI signals are generated when the end of process (EOP) signal is received from the DMA controller.

The end or identify signals (EOI and MPCEOI) indicate the end of a current multibyte information transfer.

#### 1.8.3.6 DMA Controller

The DMA controller transfers information between memory and the MPC interface without MPU intervention; however, the MPU initiates the transfer operation.

The MPU selects the DMA controller using the I/O address decode logic. By using the IORD/IOWR signals, along with an address, the MPU can establish, change, or inspect internal DMA controller registers. Thus, the DMA controller is programmed to perform the information transfers between memory and the MPC interface.

The information transfers to and from memory are accomplished by the RD/WR signals. When the information transfer is complete the DMA controller issues an EOP signal.

## 1.8.3.7 Microprocessing Unit (MPU)

The MPU controls the operation of the Eight-Line Asynchronous Communications Multiplexer. The MPU accesses the PROM (where the firmware programs are stored) using the read (RD) signal. It also accesses the RAM (for temporary information storage) using both the RD and WR signals.

The MPU reads from or writes to the MPC interface, DMA controller, and ports using the IORD and IOWR signals.

The MPU data (MDAT) lines provide for an eight-bit bidirectional information transfer between the MPU, memory, and the board-mounted I/O device.

The MPU address (MADD) lines access memory locations, for memory read/write operations, and internal registers of the board-mounted I/O devices, for the I/O read/write operations.

The MPU also reads information from or writes information to the internal registers of the ports using the MPU port data (MPDAT) lines and the IORD/IOWR signals. The individual registers are selected by the MPU port address (MPADD) lines.

The interrupt (INT) input informs the MPU that an interrupt has occurred and the interrupt vector address is on the MDAT lines. The MPU uses the vector address to locate the interrupt handler, in memory, which will process the particular interrupt that occurred.

# 1.8.3.8 Port (0 through 7)

The port (0 through 7) functional block represents eight input/output ports (0 through 7). Each port transmits serial data (PTXDAT) and receives serial data (PRXDAT) from an external device (terminal or modem) through the distribution panel, using transmit and receive control signals.

The port performs a serial-to-parallel conversion on data received from the external I/O device and a parallel-to-serial conversion on data transmitted to the external I/O device.

Information transfers between the MPU and a port are accomplished using the MPDAT lines and the IORD and IOWR signals. The register to be read from or written to is selected by the MPADD lines.

The port informs the MPU that it has information to transfer by issuing an INT for that port. The MPU processes the INT, selects the port, and accepts the information on the MPDAT.

#### **CHAPTER 2**

#### **OPERATION**

#### 2.1 Power-on/Power-off

The Eight-Line Asynchronous Communications Multiplexer receives power from the computer backplane. When power is applied to the computer system each multiplexer receives an interface clear (IFC) signal from the I/O processor (IOP). The interface clear causes the elements of the multiplexer to be initialized and the microprocessor unit (MPU) to start the program execution from location zero.

#### 2.2 Initialization

The Eight-Line Asynchronous Communications Multiplexer is initialized during the computer system poweron sequence or when a system RESET is issued from the control panel. During initialization each multiplexer receives an IFC signal from the IOP. The IFC causes the element of the multiplexer to be initialized and the MPU to start the program execution from location zero.

# 2.3 Multiplexer Address

The multiplexer address (and priority) is established by jumpers. The lowest multiplexer address (address 0) has the highest priority during the polling sequence. The multiplexer address is read by the MPU after the receipt of an IFC.

Sheet 7, of the Eight-Line Asynchronous Communications Multiplexer logic diagram, contains a table showing the multiplexer address jumper configurations.

2-1/2-2

# **CHAPTER 3**

## **PROGRAMMING**

#### 3.1 Instructions

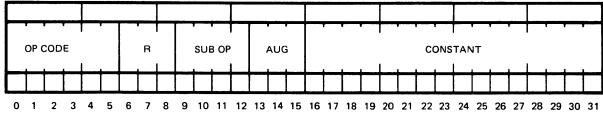

# 3.2 Basic Instruction Format

All extended I/O instructions follow one basic format. Specific details about each instruction can be found in the IOP Reference Manual, publication number 301-000170.

850084

Op code - All ones.

R field - The c

- The constant (bits 16 through 31) is added arithmetically to the contents of the general purpose register specified by "R". A zero in this field results in no change to the constant.

Sub op - Type of operation (defined below).

Aug code - All ones.

Constant - Eight-bit logical channel (bits 16 through 23) and eight-bit subchannel address (bits 24 through 31).

# 3.2.1 Sub Op Codes

| 0010 | SIO           | (Start I/O)                    |

|------|---------------|--------------------------------|

| 0011 | TIO           | (Test I/O)                     |

| 0100 | STPIO         | (Stop I/O)                     |

| 0101 | <b>RSCHNL</b> | (Reset Channel)                |

| 0110 | HIO           | (Halt I/O)                     |

| 1000 | RSCTL         | (Reset Controller)             |

| 1100 | ECI           | (Enable Channel Interrupt)     |

| 1101 | DCI           | (Disable Channel Interrupt)    |

| 1110 | ACI           | (Activate Channel Interrupt)   |

| 1111 | DACI          | (Deactivate Channel Interrupt) |

#### 3.2.2 Condition Codes

Condition codes (CC) indicate the successful or unsuccessful initiation of an I/O instruction as follows:

CC1 - CC4

| 0 | 0 | 0 | 0 | Request accepted will echo status. |  |

|---|---|---|---|------------------------------------|--|

| v | • | • | • | Concer accepted will echo status.  |  |

0 0 0 1 Channel busy.

0 0 1 0 Channel inoperable or undefined.

0 0 1 1 Subchannel busy.

0 1 0 0 Status stored.

1 0 0 0 Request accepted and gueued, no echo status.

## 3.3 Status Doublewords

A status doubleword is returned to main memory after the completion or termination of a command operation. An eight-bit controller/device status byte is transferred from the controller to the channel and merged with an eight-bit channel status byte to form part of the second word. Specific details about each status bit as well as the rest of the status doubleword can be found in the Input/Output Processor (IOP) Reference Manual, publication number 301-000170.

3.3.1 Device Status Bits

850083

| Bit | 8  | Busy            |

|-----|----|-----------------|

|     | 9  | Status modifier |

|     | 10 | Controller end  |

|     | 11 | Attention       |

|     | 12 | Channel end     |

|     | 13 | Device end      |

|     | 14 | Unit check      |

|     | 15 | Unit exception  |

The definition of each device status bit is as follows:

- 1. Busy (XX8C XXXX) This condition indicates that the device or controller cannot execute the command because it is busy executing a previously initiated operation. If a read command is received while a write with input subchannel monitoring condition exists, or if a write command is received while a read echoplex command exists, a busy condition occurs causing an interrupt to be generated.

- 2. Status modifier This bit is not used by the Eight-Line Asynchronous Communications Multiplexer.

- 3. Controller end This bit is not used by the Eight-Line Asynchronous Communications Multiplexer.

- 4. Attention (XXIC XXXX) This condition indicates that the device has detected a device-dependent asynchronous operation. A modem ring wake-up, character ring wake-up or Delta DSR (Data Set Ready) (with no read in progress) signal causes an attention status interrupt.

- 5. Channel end This condition is caused by the completion of the I/O operation involving data transfer or control information between the controller/device and the channel. This condition indicates that the subchannel has become available for use in another operation. This bit is set with one or more of the other bits.

- 6. Device end (XXOC XXXX) This condition is caused by the completion of an I/O operation at the device. The device end (DE) condition indicates that the device has become available for another operation. The channel end (CE) bit will always be set when this bit is set.

- 7. Unit check (XX0E XXXX) This condition indicates that the controller or device has detected an unusual condition. Details about the condition can be found in the sense status (when requested). The DE and CE bits will always be set when this bit is set.

- 8. Unit exception (XX0D XXXX) This bit is only set by a break interrupt signal received while a read operation is in progress. The CE and DE bits are set when this bit is set.

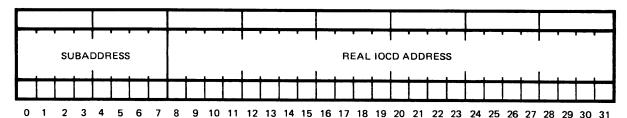

# 3.4 Input/Output Command Doublewords

All control, sense, and I/O commands are placed into doublewords and become part of an I/O Command List (IOCL) in main memory. Chaining is used to link these commands together. After receiving a start I/O (SIO) command, the Input/Output Processor (IOP) fetches these commands and passes them to the proper controller. The transfer count, address, and flags remain with the IOP while the controller receives the command bits from the I/O command doubleword (IOCD) and the subchannel address from the SIO instruction constant.

Only command bits will be covered in this technical manual while information regarding the rest of the IOCD can be found in the IOP Technical Manual, publication number 303-000170.

## 3.4.1 Write Commands

The write commands (bits 0 through 7) are as follows:

| 0 | 0 | 0 | 0 | ( | ) | 0 | 0 | 1 | Write                                  |

|---|---|---|---|---|---|---|---|---|----------------------------------------|

| 0 | 0 | 0 | 0 | ( | ) | 1 | 0 | 1 | Write with input subchannel monitoring |

| 0 | 0 | 0 | 0 | 1 | İ | 1 | 0 | 1 | Write with hardware flow control only  |

#### **NOTES**

- All write commands must use address hexadecimal 8 through F.

- 2. DSR must be true when a write command is issued or the command will be rejected with a unit check. (Exception: When a write is issued to a port that is full duplex with modem ring enabled, the DSR check is bypassed.)

#### 3.4.1.1 Write

This command causes a block of data (1 to 65,535 bytes) to be transferred from main memory to one of eight asynchronous subchannels. Read commands are accepted on the corresponding subchannel. A CE/DE status byte is returned at the completion of the command.

# 3.4.1.2 Write with Input Subchannel Monitoring

This command causes a block of data to be transferred to a device while simultaneously monitoring the corresponding input subchannel for the receipt of a DC3 (X-OFF = 13 hexadecimal), DC1 (X-ON = 11 hexadecimal), or ETX (End of Text = 03 hexadecimal) character.

If a DC3 command is received, the output function is suspended until a DC1 command is received. An ETX command causes an orderly termination of the output function to occur with CE/DE status returned to the Eight-Line Asynchronous Communications Multiplexer.

This command also monitors the clear to send (CTS) line and, should CTS go negative (false), data transmission will be temporarily suspended until CTS again goes positive (true).

This command is only processed in the full-duplex mode with no read operation in progress. A read operation attempted on the input subchannel returns a busy status.

## 3.4.1.3 Write With Hardware Flow Control Only

This command is functionally equivalent to the write with input subchannel monitor mode command with an important exception. The command makes use of the hardware interface lines only to implement flow control. This allows full duplex operation on one port with flow control, as this command does not use the corresponding subchannel for Xon/Xoff transmission. This command monitors CTS as in the write with input subchannel monitor mode command.

#### 3.4.2 Read Commands

The read commands (bits 0 through 7) are as follows:

|   | 0 | Α | S | P | 0 | 0 | 1 | 0 | Read                                 |

|---|---|---|---|---|---|---|---|---|--------------------------------------|

|   | 0 | A | S | P | 0 | 1 | 1 | 0 | Read echoplex                        |

| * | 0 | Α | S | P | 1 | 0 | 1 | 0 | Read with flow control               |

|   | 1 | Α | S | Р | 1 | 1 | 1 | 0 | Read with hardware flow control only |

\*If bit 0 is set in the command byte, DTR is used for flow control.

If bit 0 is reset in the command byte, RTS is used for flow control.

## **NOTES**

- A=ASCII control character detect (7-bit mode only)

S=Special character detect

P=Purge input buffer

- 2. All read commands must use addresses 0 through 7.

- 3. DSR must be true when a read command is issued or the command will be rejected with a unit check. (Exception: when a read is issued to a port that is full duplex with modern ring enable, the DSR check is bypassed).

# 3.4.2.1 Read

This command causes a block of data to be transferred to main memory for one of the eight asynchronous subchannels. If the purge modifier bit is set, any input data held in the buffer by the subchannel will be cleared. Otherwise, this 'type ahead' data is

processed before any new incoming data. The type ahead feature allows input data to be saved before a read command reaches the controller and after the termination of each read operation.

If the special character detect bit is set, the input operation is terminated whenever a previously defined eight-bit character is detected. At this point the input operation is terminated with the special character, written into memory, as the last character.

If the ASCII control character detect bit is set, the input operation is terminated whenever a control character (hexadecimal 00 through 1F) or a delete (hexadecimal 7F) instruction is detected. The last character written into memory is the ASCII control character. The 'type ahead' input buffer is used to hold input data after a read command is completed. This feature allows an uninterrupted flow of input data while waiting for a new read command to reach the controller. The ASCII control character detect applies to 7-bit mode of operation only.

Note that write commands are allowed on the corresponding subchannel with this read instruction.

# 3.4.2.2 Read Echoplex

This command allows a block of data to be read while all printable ASCII characters are outputted to the corresponding subchannel. This command will only be processed in the full-duplex mode with no write command in progress. After this read command is accepted, no write commands will be accepted on the corresponding subchannel.

A write attempted on the Output Subchannel will return busy status. Purge, ASCII Control Character Detect, and special character detect are selectable options.

#### 3.4.2.3 Read With Flow Control

The read with flow control is the complement to the write with input subchannel monitor mode command. The issuance of this command causes the write subchannel to be set busy. The eight-line then monitors the input buffer. If the input buffer reaches the 70% full point (38 bytes remaining), an Xoff character (Hex 13) is sent out on the write subchannel. At the same time either DTR (if bit 0 is set in the command byte) or RTS (if bit 0 is reset) is reset. When the input buffer is nearly empty (8 bytes remaining) an Xon character (Hex 11) is sent out and the DTR or RTS line is set.

## 3.4.2.4 Read With Hardware Flow Control Only

This command is functionally equivalent to the read with flow control command with an important exception. The command makes use of the hardware interface lines only to implement flow control. This allows full duplex operation on one port with flow control, as this command does not use the corresponding subchannel for Xon/Xoff transmission. This command toggles DTR in the same manner as the read with flow control command.

# 3.4.3 Control Commands

The control commands (bits 0 through 7) are as follows:

| 1 | 1 1 1 1 | 1 1 1 | Define ACE (UART) parameters (three bytes follow) |

|---|---------|-------|---------------------------------------------------|

| 0 | 0 0 0 0 | 0 1 1 | No operation (NOP)                                |

| 0 | 0 0 0 1 | 0 1 1 | Define special character (one byte follows)       |

| 0 | 0 0 1 0 | 0 1 1 | Reset data terminal ready                         |

| 0 | 0 0 1 0 | 1 1 1 | Set data terminal ready                           |

| 0 | 0 0 1 1 | 0 1 1 | Reset request to send                             |

| 0 | 0 0 1 1 | 1 1 1 | Set request to send                               |

| 0 | 0 1 1 0 | 1 1 1 | Set break                                         |

| 0 | 0 0 0 0 | 1 0 0 | Sense                                             |

# NOTE

All control commands use either group of addresses (hexadecimal 0 through 7 or 8 through F).

# 3.4.3.1 Define ACE Parameters

This control command precedes a three-byte transfer which defines ACE parameters, wake-up ring, and half-/full-duplex operation as described by byte 1, byte 2 and byte 3.

| 0 |     | • | • | 7 | Byte 1                                                                    |

|---|-----|---|---|---|---------------------------------------------------------------------------|

| - |     | _ | 0 | 0 | Five-bit character length                                                 |

| - |     | - | 0 | 1 | Six-bit character length                                                  |

| - |     | - | 1 | 0 | Seven-bit character length                                                |

| - |     | _ | 1 | 1 | Eight-bit character length                                                |

| - |     | 0 |   | - | One stop bit                                                              |

| - |     | 1 | - | - | Two stop bits or one and one half stop bits for five-<br>character length |

| - | 0   | _ | - | _ | Parity disabled                                                           |

| - | 1   | - | - | - | Parity enabled                                                            |

| - | 0 - | - | - | - | Odd parity                                                                |

| - | 1 - | - | - | - | Even parity                                                               |

| - | - 0 | - | - | - | Normal parity as defined                                                  |

| - | - 1 | - | _ | _ | Force parity to 1 if odd, 0 if even                                       |

| - | 0   | - | - | - | Disable modem ring                                                        |

| - | 1   | - | - | - | Enable modem ring                                                         |

| 0 |     | - | - | - | Full-duplex operation                                                     |

| 1 |     | - | - | - | Half-duplex operation                                                     |

| 0 | • | • | • | • | • | • | 7 | Byte 2                              |

|---|---|---|---|---|---|---|---|-------------------------------------|

| - | _ | _ | _ | 0 | 0 | 0 | 0 | 50 baud                             |

| _ | _ | _ | _ | 0 | 0 | 0 | l | 75 baud                             |

| _ | _ | _ | _ | 0 | 0 | l | 0 | 110 baud                            |

| - | _ | _ | _ | 0 | 0 | 1 | 1 | 134.5 baud                          |

| - | - | _ | _ | 0 | 1 | 0 | 0 | 150 baud                            |

| - | - | _ | _ | 0 | 1 | 0 | 1 | 300 baud                            |

| - | - | - | - | 0 | 1 | 1 | 0 | 600 baud                            |

| - | _ | - | - | 0 | l | 1 | 1 | 1200 baud                           |

| - | - | _ | - | 1 | 0 | 0 | 0 | 1800 baud                           |

| - | _ |   | - | 1 | 0 | 0 | 1 | 2000 baud                           |

| - | _ | _ | _ | 1 | 0 | 1 | 0 | 2400 baud                           |

| _ | _ | _ | _ | 1 | 0 | i | 1 | 3600 baud                           |

| - | _ | _ | - | 1 | 1 | 0 | 0 | 4800 baud                           |

| _ | _ | - | _ | 1 | 1 | 0 | 1 | 7200 baud                           |

| _ | _ | _ | _ | 1 | 1 | 1 | 0 | 9600 baud                           |

| _ | - | _ | _ | 1 | 1 | 1 | 1 | 19200 baud                          |

| _ | _ | _ | 0 | _ | _ | _ | _ | Reset diagnostic loop               |

| _ | _ | _ | 1 | _ | _ | _ | _ | Set diagnostic loop                 |

| _ | _ | 0 | _ | _ | _ | _ | _ | Allow wake-up character detection   |

| - | - | i | - | - | - | - | - | Inhibit wake-up character detection |

|   |   |   |   |   |   |   | _ |                                     |

| 0 | • | • | • | • | • | • | 7 | Byte 3                              |

| С | С | С | С | С | С | С | С | Eight-bit wake-up character         |

# 3.4.3.2 NOP (No Operation)

The NOP command only causes a CE/DE status interrupt. No activity occurs at the controller.

# 3.4.3.3 Define Special Character

This control command causes a one-byte transfer to the controller which contains an eight-bit character used for input termination.

# 3.4.3.4 Reset Data Terminal Ready (DTR)

This control command resets the DTR signal for the addressed port. The DTR signal is automatically reset during a controller clear or power reset operation.

# 3.4.3.5 Set Data Terminal Ready (DTR)

This control command sets the DTR signal for the addressed port.

# 3.4.3.6 Reset Request to Send (RTS)

This control command resets the RTS signal for the addressed port. The RTS signal is automatically reset during device or controller clear or a power reset operation.

If the port is defined half-duplex, this signal is automatically reset at the completion of a write command.

# 3.4.3.7 Automatic Handling of RTS and DTR

Upon initialization of a line (define ACE parameters) the control lines request to send and data terminal ready are set or reset depending on the line parameters. If ring is enabled, the line is assumed to be remote (i.e., modem) and both signals are reset. If ring is not enabled, the line is assumed to be local (i.e., local TTY), DTR is set, and RTS is set if the line is full duplex. If the line is half duplex, RTS is reset.

# 3.4.3.8 Set Request to Send (RTS)

This control command sets the RTS signal for the addressed port.

If the port is defined half-duplex, this signal is automatically set at the start of each write command.

#### 3.4.3.9 Reset Break

This control command disables the break feature, releasing the serial output line from the clamped logic 0 state.

#### 3.4.3.10 Set Break

This control command sets the serial data output line to the spacing logic 0 state until a reset break command is received.

#### 3.4.3.11 Sense Status

This command causes eight bytes of sense information to be transferred to main memory for the addressed port. The first six bits of byte 0 are standard for all controllers.

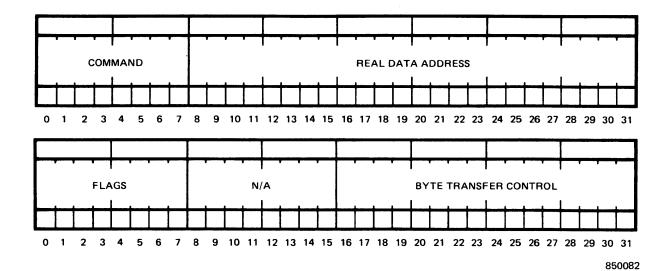

Sense Byte 0: Device status

850081-1

Bit 0 Command reject (program violation)

- 1 Intervention required (not used)

- 2 Bus out check (IOP parity error)

- 3 Equipment check (device error)

- 4 Data check

- 5 Overrun (not used)

- 6 Zero

- 7 Zero

The definition of each device status bit is as follows:

- Command reject (bit 0) This bit indicates that an improper command has been received and ignored. If a port is defined as half-duplex, a command reject command occurs when the write with input subchannel monitoring or a read echoplex command is executed. Note that undefined commands also result in a program violation indication. Unit check status is returned when a program violation is encountered. If a read command is received during a write operation or a write command during a read operation and the controller is operating in the half-duplex mode, a busy condition, not a program violation, is generated.

- 2. Intervention required (bit 1) This bit indicates that the device requires operator intervention (not used with the eight-line asynchronous communications Multiplexer.).

- 3. Bus out check (bit 2) This bit indicates that a parity error has occurred on the I/O channel bus thus generating unit check status.

- 4. Equipment check (bit 3) This bit indicates that an I/O device malfunction has occurred during the last operation. Bit 3 is set when the data set ready or carrier detect lines go low (for 150 ms) while the data terminal ready line is high. An equipment check indication also occurs if the clear to send line goes low (in the full-duplex mode) while the RTS line is high. In either situation, the I/O operation is halted, unit check status posted, and a unit check interrupt is issued.

- 5. Data check (bit 4) This bit indicates that data is in error or lost. An overrun, parity, or framing error must have occurred during input at the ACE for this bit to be set. The I/O operation is halted, unit check status posted, and unit check interrupt issued.

- 6. Overrun (bit 5) This bit is not used with the Eight-Line Asynchronous Communications Multiplexer.

- 7. Bits 6 and 7 are always zero.

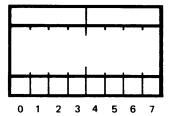

Sense Byte 1: Line Status and Error Conditions

850081-2

Bit 0 ASCII control character detected interrupt

- 1 Special character detected interrupt

- 2 ETX interrupt

- 3 Break interrupt

- 4 ACE framing error interrupt

- 5 ACE parity error interrupt

- 6 ACE overrun error interrupt

- 7 Ring character interrupt

The definition of each line status and error condition bit is as follows:

- 1. ASCII control character detected (bit 0) This bit indicates that an ASCII control character (hexadecimal 00 through 1F or 7F) has been received during the last read operation. The ASCII control character detected bit must be set with the read command to cause this status condition. All buffered data, including the ASCII character, is inputted to main memory. CE/DE status is posted and a CE/DE status interrupt issued.

- 2. Special character detected (bit 1) This bit indicates that the previously defined ASCII character has been received during the last read operation. The special character detect bit must have been set with the read command in order to cause this status condition. All buffered data including the special character will be inputted to main memory. CE/DE status is posted and CE/DE status interrupt is issued.

- 3. ETX detected (bit 2) This bit indicates that an ETX control character has been received during the last input operation, terminating the port's output. The only command which can cause this status is the write with input subchannel monitoring to a full-duplex port. Output data is immediately terminated, CE/DE status is posted, and CE/DE status interrupt is issued.

- 4. Break interrupt (bit 3) This bit indicates that the input data line has been held in the spacing (logic 0) state for longer than a full character time period. If a read operation was in progress, unit exception status is posted and a unit exception status interrupt issued. Framing error (bit 4) is also set. If no I/O operation was in progress, attention status is posted. Only one break interrupt is accepted between read operations.

- 5. ACE framing error (bit 4) This bit indicates that the incoming character did not have valid stop bit(s). If this bit is set without the break interrupt bit (bit 3), unit check status is posted and a unit check status interrupt issued.

- 6. ACE parity error interrupt (bit 5) This bit indicates that an incoming character did not have the correct parity at the ACE. The data check bit in sense byte 0 is also set. Unit check status is posted and a unit check status interrupt issued.

- 7. Overrun error (bit 6) This bit indicates that the internal 128 byte buffer has been overrun or that data has been lost at the ACE due to the controller's failure to read an incoming byte before the reception of the next byte. The data check bit in sense byte 0 is also set. Unit check status is posted and a unit check status interrupt issued.

- 8. Ring character interrupt (bit 7) This bit indicates that a ring character has been received when a read operation was not in progress. Attention status is posted and an attention status interrupt issued.

# Sense Byte 2: Modem Status

Bit

- 0 Received line signal detect status

- 1 Ring indicator line status

- 2 Data set ready line status

- 3 Clear to send line status

- 4 Delta receive line signal detect failure interrupt

- 5 Modem ring interrupt

- 6 Delta data set ready interrupt

- 7 Delta clear to send failure interrupt

#### The definition of each modem status bit is as follows:

- 1. Received line signal detect (bit 0) This bit indicates the logic condition of the RLSD input signal. When this bit is set, the signal is high.

- 2. Ring indicator (bit 1) This bit indicates the logic condition of the RI input signal. When this bit is set, the signal is high.

- 3. Data set ready (bit 2) This bit indicates the logic condition of the DSR input signal. When this bit is set, the signal is high.

- 4. Clear to send (bit 3) This bit indicates the logic condition of the CTS input signal. When this bit is set, the signal is high.

- 5. Delta receive line signal detect failure interrupt (bit 4) This bit indicates that the received line signal detect failure (RLSD) input signal has gone low for at least 150 ms, while a read operation was in progress. The read operation is terminated with unit check status posted and a unit check status interrupt is issued.

- 6. Modem ring interrupt (bit 5) This bit indicates that the ring indicator (RI) signal has changed (trailing edge only). If the modem ring enable bit is set during the initialization of byte 1, the controller will generate attention status. The DTR line must then be set, by software, to "answer the phone." This task is accomplished via the set DTR control command.

- 7. Delta data set ready interrupt (bit 6) This bit indicates that a transition occurred on the data set ready (DSR) input signal. If a read operation was in progress it is terminated, unit check status is posted, and a unit check status interrupt issued. If a read operation was not in progress and the DTR line is high, attention status is posted and an attention status interrupt issued.

8. Delta clear to send failure interrupt (bit 7) - This bit indicates that the clear to send (CTS) input signal shifted from high to low. If a read operation was in progress (full-duplex mode) or a write operation is in progress (half-duplex mode), the read operation is terminated, unit check status is posted, and a unit check status interrupt issued.

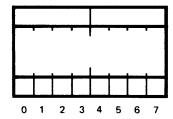

Sense Byte 3: Modem Control/Operation Mode

850081-4

Bit Half-duplex operation set

- Modem ring enabled (1) 1

- 2 ACE parameters defined

- 3 Diagnostic mode set

- 4 Auxiliary output level 2

- 5 Auxiliary output level 1

- Request to send (RTS)

- Data terminal ready (DTR)

The definition of each modem control/operation mode bit is as follows:

- 1. Half-duplex operation set (bit 0) This bit indicates that the port is designated for half-duplex operation. If this bit is not set, the port is designated for full-duplex operation.

- 2. Modem ring enabled (1) (bit 1) If this bit is set the subchannel responds to a modem line ring interrupt, thereby causing an attention status interrupt to be The DTR line is not set by the Eight-Line Asynchronous Communications Multiplexer. Note that it is the responsibility of the software to set or reset the DTR signal using the control commands provided.

- 3. ACE parameters defined (bit 2) This bit indicates that the ACE has been initialized with a control command since it was last cleared.

- Diagnostic mode set (bit 3) This bit indicates that the diagnostic loop-back feature of the ACE is enabled and all data outputted must be read back in with a read command. The read command should be issued before the write command.

- Auxiliary output level 2 (bit 4) This bit indicates the logic condition of auxiliary output level 2.

- 6. Auxiliary output level 1 (bit 5) This bit indicates the logic condition of auxiliary output level 1.

- 7. Request to send (bit 6) This bit indicates the logic condition of the request to send (RTS) output signal. When this bit is set, the signal is high.

8. Data terminal ready (bit 7) - This bit indicates the logic condition of the data terminal ready (DTR) output signal. When this bit is set, the signal is high.

# Sense Byte 4: ACE Parameters

850081-5

Bit 0 Divisor latch enable

0 = disabled

l = enabled

1 Break set

0 = reset

1 = set

2 Forced parity

0 = odd parity

1 = even parity

3 Parity

0 = odd parity

1 = even parity

4 Parity enable

0 = disabled

1 = enabled

Bit 5 Stop bit

0 = 1 stop bit

= 1.5 or 2 stop bits

6-7 Character length

00 = 5

01 = 6

10 = 7

11 = 8

### The definition of each ACE parameter bit is as follows:

- 1. Divisor latch is enabled (bit 0) When this bit is set the ACE's divisor latch (used for loading the baud rate divisor) is accessible. Normal I/O operation cannot take place when this latch is enabled.

- 2. Break is set (bit 1) When this bit is set the data output line is being held in the spacing logic 0 state.

- Forced parity (bit 2) If this bit is set the parity bit will always be a one for odd selected parity, or a zero for even selected parity.

- 4. Even and odd parity (bit 3) When this bit is set, even parity has been selected. The sum total of all ones in the data character (with parity bit) is generated and checked for an even count. If this bit is not set, parity is generated and checked odd.

- 5. Parity enabled (bit 4) - When this bit is set, the proper parity is generated during an output operation, and checked during an input operation by the ACE.

- 6. Stop bits (bit 5) - If this bit is set, two stop bits are transmitted, with each character, and expected to be received with each character. character length has been defined as five bits, then only one and one-half stop bits is transmitted and received. If this bit is not set, one stop bit is transmitted and received.

- Character length (bit 6 and 7) These two bits indicate the character length 7. for transmitted and received data.

If bits 0,1 = 00: character length is five bits. If bits 0,1 = 01: character length is six bits. If bits 0,1 = 10: character length is seven bits. If bits 0,1 = 11: character length is eight bits.

## Sense Byte 5: Baud Rate

850081-6

Bit 0. 1

Zero.

Bit 2

Ring character recognition

0 = enable

1 = inhibit

Bit 3

Bits 4, 5, 6, 7

Define baud rate as in baud rate select command.

The definition of the baud rate bits is as follows:

Zero.

Bits 4, 5, 6, 7 represent the baud rate selected for the port. If the port has not been initialized, these bits will be 0 (this does not mean that the baud rate of 50 has been selected).

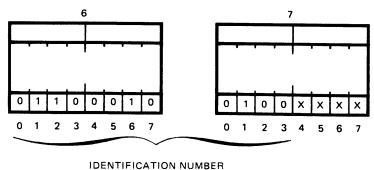

Sense Bytes 6 and 7: Firmware Identification, Revision Level

(CONSTANT)

X=FIRMWARE REVISION LEVEL

850081-7

## 3.5 Microprogramming

The Eight-Line Asynchronous Communications Multiplexer is microprogrammed in Z80 assembly code.