# INPUT/OUTPUT PROCESSOR (IOP) Model 8000 and 8001 USER INTERFACE MANUAL

December 1982

Publication Order Number: 310-000890-000

This manual is supplied without representation or warranty of any kind. Gould Inc., S.E.L. Computer Systems Division therefore assumes no responsibility and shall have no liability of any kind arising from the supply or use of this publication or any material contained herein.

Copyright 1981

Gould Inc., S.E.L. Computer Systems Division

Printed in U.S.A.

# HISTORY

The Input/Output Processor (IOP) User Interface Manual, Publication Order Number 310-000890-000, was printed June, 1981.

Publication Order Number 310-000890-001 (Change 1) was printed December, 1982. The updated manual contains the following pages:

| * Change   | * Change         |

|------------|------------------|

| Number     | Number           |

| Title page | 1-2 through 1-10 |

On a change page, the portion of the page affected by the latest change is indicated by a vertical bar in the outer margin of the page. However, a completely changed page will not have a full length bar, but will have the change notation by the page number.

<sup>\*</sup> Zero in this column indicates an original page.

# Change Record

Insert the latest change pages and dispose of the superseded pages. On a change page, the portion of the page affected by the latest change is indicated by a vertical bar in the outer margin. However, a completely changed page will not have a full length bar; the change number will be next to the page number.

| Rev.<br>Type | Rev.<br>No. | Date<br><u>Issued</u> | Rev.<br><u>Type</u> | Rev.<br><u>No.</u> | Date<br>Issued |

|--------------|-------------|-----------------------|---------------------|--------------------|----------------|

| 0            |             | 06/81                 |                     |                    |                |

|              |             |                       |                     |                    |                |

| O = Original |             | C                     | : = Change          |                    | R = Revision   |

# List of Effective Pages

| Page<br>No.         | Change In <u>Effect*</u> |

|---------------------|--------------------------|

| Title Page          | 0                        |

| Copyright           | 0                        |

| iii/iv through ix/x | 0                        |

| 1-1 through 1-9     | 0                        |

| 2-1 through 2-20    | 0                        |

| 3-1 through 3-3     | 0                        |

| 4-1/4-2             | 0                        |

| A-1 through A-3     | 0                        |

| Index Pages         | 0                        |

<sup>\*</sup>A "0" in this column indicates an original page.

# **CONTENTS**

| Ch | apter |           |               | Pag                                          | e   |

|----|-------|-----------|---------------|----------------------------------------------|-----|

| 1  | FUN   | ICTIONAL  | DESCRIPTION   | ON                                           | -1  |

|    | 1.1   | General   | Information . |                                              | . 1 |

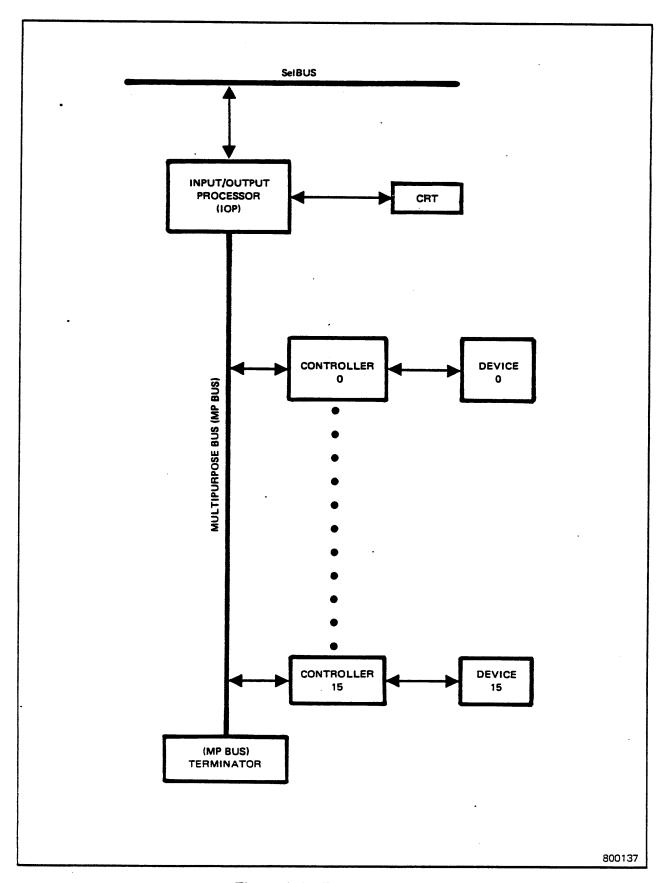

|    | 1.2   | Multipur  | pose Bus Des  | scription                                    | .3  |

|    |       | 1.2.1     |               | tion                                         | .3  |

|    |       |           | 1.2.1.1       | I/O Data Lines                               |     |

|    |       |           | 1.2.1.2       | I/O Control Lines                            |     |

|    |       |           | 1.2.1.3       | Output Control Lines                         |     |

|    |       |           | 1.2.1.4       | Input Control Lines                          |     |

|    |       |           | 1.2.1.5       | Output Timing Lines                          |     |

|    |       | 1.2.2     |               | e Bus Modes of Operation                     |     |

|    |       | 1.2.2     | 1.2.2.1       | Command Transfer Sequence                    |     |

|    |       |           | 1.2.2.2       | Data Transfer Sequence                       |     |

|    |       |           | 1.2.2.3       | End of Message Sequence                      |     |

|    |       |           | 1.2.2.4       |                                              |     |

|    |       |           | 1.2.2.4       | Status Transfer Sequence                     | U   |

| 2  | OPE   | RATIONA   | L DESCRIPT    | ΠΟΝ                                          | . 1 |

|    |       |           |               |                                              |     |

|    | 2.1   |           |               |                                              |     |

|    | 2.2   |           |               | erface 2-                                    |     |

|    |       | 2.2.1     | Extended I/   | O Commands                                   |     |

|    |       |           | 2.2.1.1       | Extended I/O Command Sequence 2-             |     |

|    |       | 2.2.2     | Extended I/   | O Status                                     |     |

|    |       |           | 2.2.2.1       | Busy Status                                  |     |

|    |       |           | 2.2.2.2       | Status Modifier Status 2-                    |     |

|    |       |           | 2.2.2.3       | Controller End Status 2-                     | .3  |

|    |       |           | 2.2.2.4       | Attention Status 2-                          | .4  |

|    |       |           | 2.2.2.5       | Channel End Status                           | .4  |

|    |       |           | 2.2.2.6       | Device End Status 2-                         | .4  |

|    |       |           | 2.2.2.7       | Unit Check Status 2-                         | .5  |

|    |       |           | 2.2.2.8       | Unit Exception Status 2-                     |     |

|    | 2.3   | Interface | Sequences .   |                                              |     |

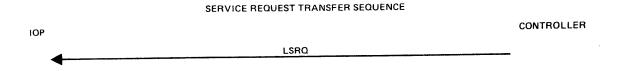

|    |       | 2.3.1     | Service Reg   | quest Sequence                               | -6  |

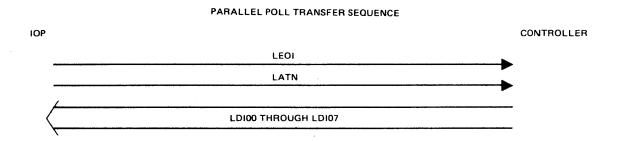

|    |       | 2.3.2     | Parallel Pol  | lling Sequence 2-                            | .7  |

|    |       | 2.3.3     |               | Sequence                                     |     |

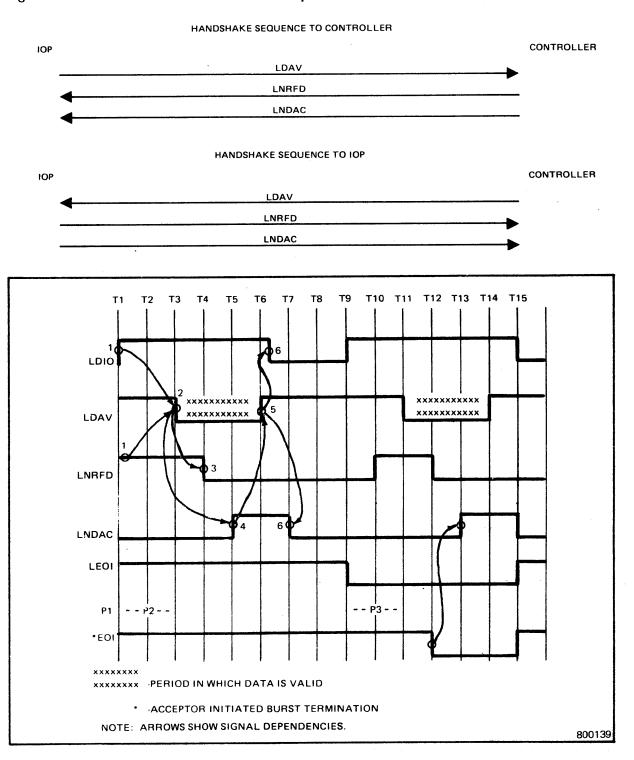

|    |       |           | 2.3.3.1       | List of Events for Handshake Process 2-      |     |

|    |       | 2.3.4     |               | ansfer Sequence                              |     |

|    |       |           | 2.3.4.1       | Addressed Talk Sequence 2-1                  |     |

|    |       |           | 2.3.4.2       | Addressed Listener Sequence 2-1              | ī   |

|    |       |           | 2.3.4.3       | Untalk Sequence                              | ĩ   |

|    |       |           | 2.3.4.4       | Unlisten Sequence                            |     |

|    |       | 2.3.5     |               | nal Sequence                                 | 2   |

|    |       | 21,51,5   | 2.3.5.1       | Addressed Primary Control Signals 2-1        |     |

|    |       |           | 2.5.5.1       | 2.3.5.1.1 Addressed Primary Control Signal   | -   |

|    |       |           |               | ,                                            | 3   |

|    |       |           | 2.3.5.2       | Sequence                                     |     |

|    |       |           | 4.3.3.4       | ,                                            | ر   |

|    |       |           |               | 2.3.5.2.1 Addressed Secondary Control Signal | 3   |

|    |       |           | 2.3.5.3       | Sequence                                     | 2   |

|    |       |           | 4.7.7.3       | Device Address Control Signal                | 1   |

|    |       |           | 2.3.5.4       | 2.3.5.3.1 Device Address Sequence 2-1        |     |

|    |       |           | 7. 7. 1.4     | - CONVERSAL MERBALY CONTOL SIGNAL            |     |

| Chapter      |          |              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |                                         | Page |

|--------------|----------|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------|------|

|              |          |              | 2.3.5.4.1    | Universal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Primary Con       | trol Signal                             |      |

|              |          |              | 2,3,5,4,1    | Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | e                 | ••••••••••••••••••••••••••••••••••••••  | 2-14 |

|              | 2.3.6    | Serial Pol   | Sequence.    | on out of the contract of the |                   |                                         | 2-14 |

|              | 2.5.0    | 2.3.6.1      | Serial Poll  | ing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |                                         | 2-15 |

|              | 2.3.7    | Command      | Transfer Sec | quence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |                                         | 2-16 |

|              | 2.00     | 2.3.7.1      | Addressed    | Listen Seque                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | nce               |                                         | 2-17 |

|              | *        | 2.3.7.2      | Fnable Sec   | Condary Com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mand Sequenc      | e                                       | 2-17 |

|              |          | 2.3.7.3      | Endore sec   | I/O Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Most Signific     | cant                                    |      |

|              |          | 2.3.7.3      | Nibble       | i/O Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                                         | 2-17 |

|              |          | 2.3.7.4      | Evtonded     | I/O Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | l Least Signif    | icant                                   |      |

|              |          | 2.3.7.4      | Nibble       | i/O Commune                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                                         | 2-18 |

|              |          | 2.3.7.5      | Addressed    | Device Segu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ence              |                                         | 2-18 |

|              |          | 2.3.7.6      | Addressed    | Unlisten Sea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | uence             |                                         | 2-18 |

|              | 0.00     | 2.3./.6      | Addi essed   | Oursten sed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | · · · · · · · · · | ,                                       | 2-18 |

|              | 2.3.8    | Data Iran    | Siers        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |                                         | 2-20 |

|              | 2.3.9    | Status ira   | inster Seque | Message Sag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                                         | 2-20 |

|              | 2.3.10   | Terminati    | on by End of | message seq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | uence             |                                         | 2_21 |

|              | 2.3.11   |              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |                                         | 2-21 |

|              |          | 2.3.11.1     | Selected (   | Controller Cle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ear Sequence      |                                         | 2-21 |

|              |          | 2.3.11.2     | Device Ci    | ear Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   | • • • • • • • • •                       |      |

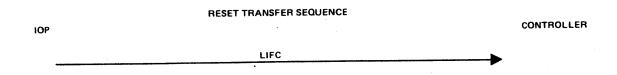

|              |          | 2.3.11.3     | Interface    | Clear Sequen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ce                |                                         | 2-22 |

| 2.4          |          | System Co    | nsiderations | • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   | • • • • • • • • • • • • • • • • • • • • | 2.23 |

|              | 2.4.1    | Intertace    | Timeout      | • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • • • • • • • •   |                                         | 2 22 |

|              | 2.4.2    | Burst Len    | gth          | • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | • • • • • • • •                         | 2 22 |

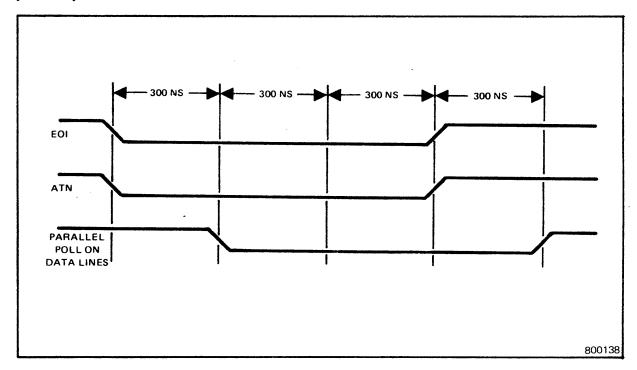

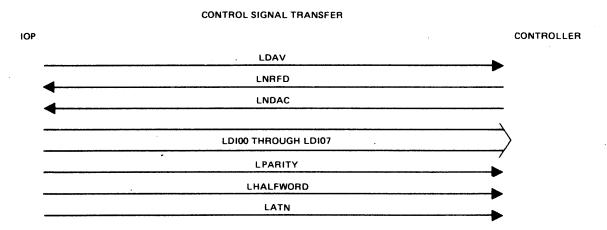

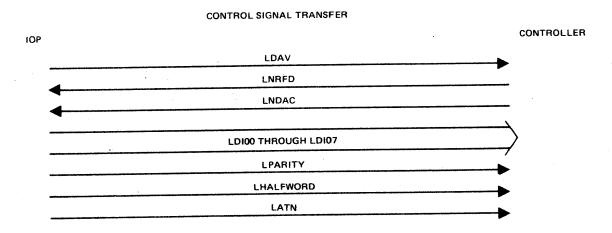

|              | 2.4.3    | Control S    | ignal_Timing | • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • • • • • • • •   | • • • • • • • •                         | 2-23 |

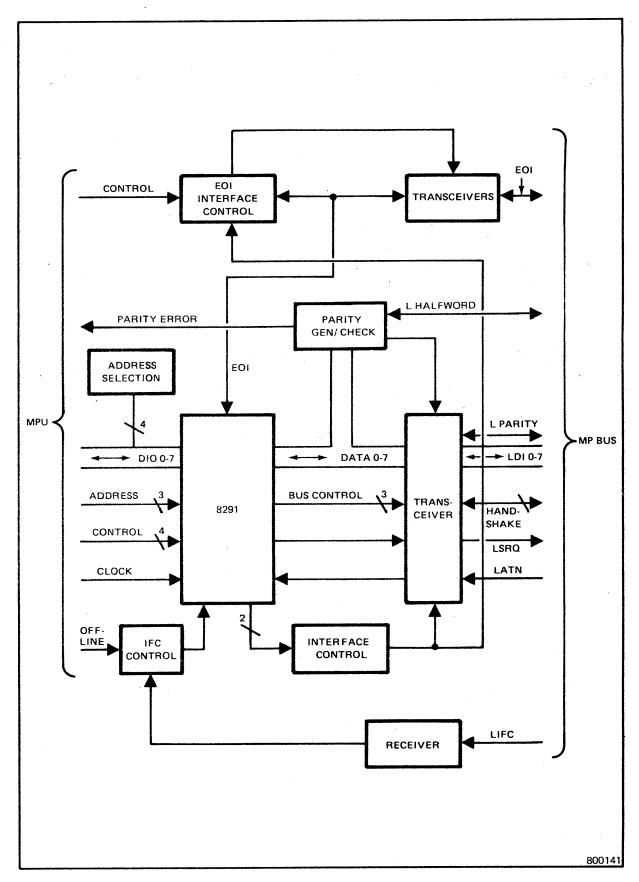

| 2.5          |          | utput Proce  | ssor Feature | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | • • • • • • • •                         | Z-Z9 |

|              | 2.5.1    | Parity Er    | or Reporting | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | • • • • • • • • •                       | 2-29 |

|              | 2.5.2    | Multipurp    | ose Bus Time | eout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • • • • • • • •   | • • • • • • • •                         | 2-24 |

|              | 2.5.3    | IOP Inhib    | it           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   | • • • • • • • •                         | 2-29 |

|              | 2.5.4    | Halfword     | or Byte Tran | nsfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   | • • • • • • • •                         | 2-25 |

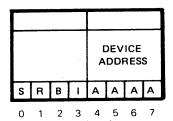

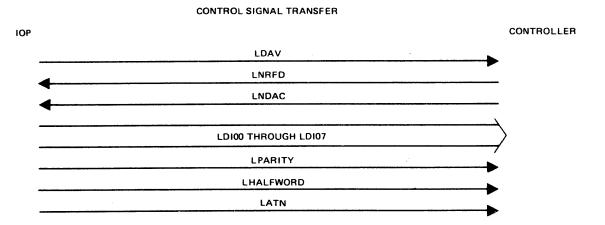

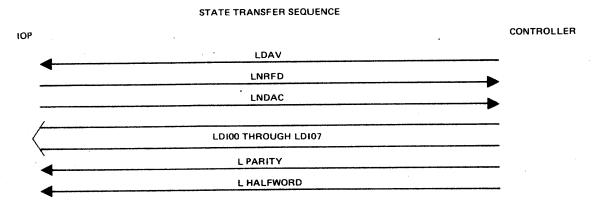

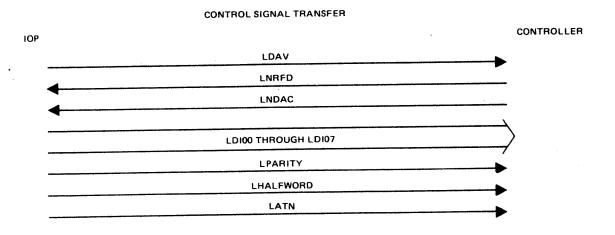

|              | 2.5.5    | Timing Si    | gnals        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   | • • • • • • • •                         | 2-25 |