# Computer Reference Manual SYSTEMS 72 Digital Computer April 1972

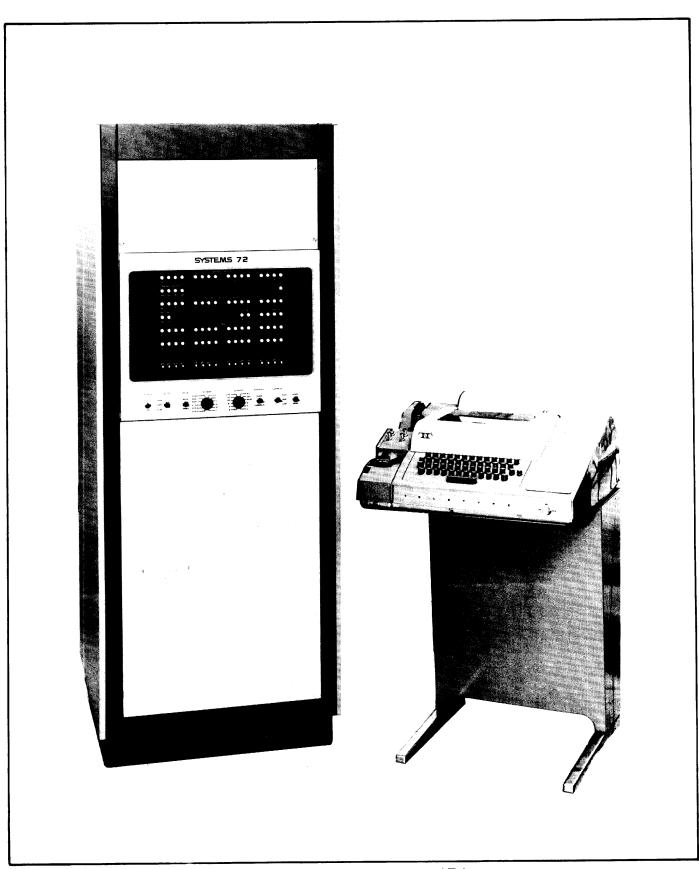

Typical SYSTEMS 72 Digital Computer and Teletype

#### LIST OF EFFECTIVE PAGES

The total number of pages in this manual is 184, consisting of the following pages:

| Page Number      | Issue    |

|------------------|----------|

| Title            | Original |

| A                | Original |

| i through iv     | Original |

| 1-1 through 1-12 | Original |

| 2-1 through 2-54 | Original |

| 3-1 through 3-10 | Original |

| 4-1 through 4-8  | Original |

| A-1 through A-4  | Original |

| B-1 through B-42 | Original |

| C-1 through C-6  | Original |

| D-1 through D-14 | Original |

| E-1 through E-2  | Original |

| F-1 through F-2  | Original |

| G-1 through G-2  | Original |

| H-1 through H-10 | Original |

| I-1 through I-8  | Original |

|                  |          |

#### TABLES OF CONTENTS

| Section | Title                                                       | Page         |

|---------|-------------------------------------------------------------|--------------|

| SECTION | INTRODUCTION AND DESCRIPTION                                |              |

|         | Introduction                                                | 1-1          |

|         | Purpose of Equipment                                        | 1-1          |

|         | Optional Equipment                                          | 1-2          |

|         | Physical Configuration                                      | 1-2          |

|         | Functional Configuration                                    | 1-2          |

|         | Control Panel                                               | 1-8          |

|         | Power Turn on Procedure                                     | 1-8          |

|         | Loading Procedures                                          | 1-10         |

|         | Loading - No Optional Loader                                | 1-10         |

|         | Loading - Optional Loader                                   | 1-11         |

|         | Modifying Memory From the Control Panel                     | 1-11         |

|         | Displaying Memory at the Control Panel Hexadecimal Notation | 1-12<br>1-12 |

|         |                                                             | 1-12         |

| SECTION | II CENTRAL PROCESSOR UNIT                                   |              |

|         | Introduction                                                | 2-1          |

|         | CPU Operational Phases                                      | 2-1          |

|         | Instruction Format                                          | 2-3          |

|         | Addressable Registers                                       | 2-4          |

|         | Program Status Doubleword                                   | 2-5          |

|         | Address Calculation                                         | 2-9          |

|         | Relative Addressing                                         | 2-9          |

|         | Relative Base Addressing                                    | 2-9          |

|         | Indirect Addressing                                         | 2-12         |

|         | Post-Indexing                                               | 2-12         |

|         | Absolute Addressing                                         | 2-12         |

|         | Instruction Repertoire                                      | 2-12         |

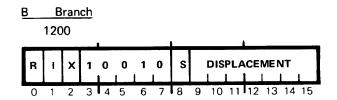

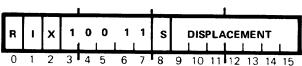

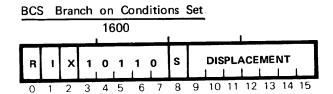

|         | Branch Instructions                                         | 2-14         |

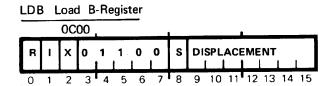

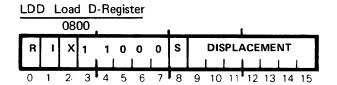

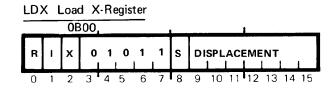

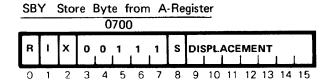

|         | Load Instructions Store Instructions                        | 2-21         |

|         | Arithmetic Instructions                                     | 2-28         |

|         | Logical Instructions                                        | 2-32         |

|         | Compare Instruction                                         | 2-36         |

|         | Shift Instructions                                          | 2-40<br>2-42 |

|         | Call Instructions                                           | 2-42         |

|         | Input/Output Instructions                                   | 2-40<br>2-51 |

|         | Other Instructions                                          | 2-51<br>2-54 |

| SECTION | III CORE/DISC MEMORY SYSTEM                                 | 2-54         |

|         | Introduction                                                | 3-1          |

|         | Basic Core/Disc Memory System                               | 3-1          |

|         | Memory System Functions                                     | 3-1          |

|         | Core Memory                                                 | 3-2          |

|         | Dedicated Core Locations                                    | 3-2          |

|         | Data Guard                                                  | 3-3          |

|         | Memory Parity Check                                         | 3-3          |

|         | Memory Ports                                                | 3-3          |

|         | Disc Memory                                                 | 3.4          |

#### TABLE OF CONTENTS (CONT'D)

| CECTION III | 00 DE /D100 145140 D14 D140 D14                                                                                                                                                                                                          | Page                                                 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| SECTION III | CORE/DISC MEMORY SYSTEM                                                                                                                                                                                                                  |                                                      |

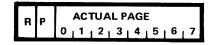

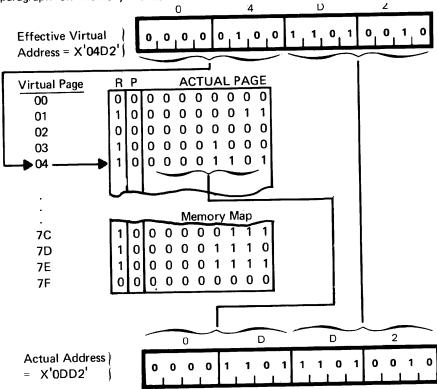

| (Cont'd)    | Actual/Virtual Memory Configuration Memory Map Format Memory Map Operation Memory Map Update Memory Traps Sense Disc Rotational Position Output Disc Track and Sector Address Output Core Bank and Page Address Page Transfer Terminator | 3-4<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8<br>3-9<br>3-9 |

| SECTION IV  | INPUT/OUTPUT SYSTEM                                                                                                                                                                                                                      | 0.0                                                  |

|             | Introduction                                                                                                                                                                                                                             | 4-1                                                  |

|             | Dual Level Interrupt System                                                                                                                                                                                                              | 4-1                                                  |

|             | I/O Priority                                                                                                                                                                                                                             | 4-2                                                  |

|             | Interrupt Inhibit                                                                                                                                                                                                                        | 4-2                                                  |

|             | Interrupt Clear<br>System Interrupts                                                                                                                                                                                                     | 4-2                                                  |

|             | Set System Interrupts                                                                                                                                                                                                                    | 4-2<br>4-3                                           |

|             | Sense System Interrupts                                                                                                                                                                                                                  | 4-4                                                  |

|             | Memory Traps                                                                                                                                                                                                                             | 4-4                                                  |

|             | Input/Output Command List                                                                                                                                                                                                                | 4-4                                                  |

|             | Input/Output Instructions                                                                                                                                                                                                                | 4-6                                                  |

|             | Basic Input/Output Operation                                                                                                                                                                                                             | 4-7                                                  |

|             | PIN/POT I/O Capability                                                                                                                                                                                                                   | 4-8                                                  |

| APPENDIX A  | Glossary of Terms                                                                                                                                                                                                                        | A-1                                                  |

| APPENDIX B  | SYSTEMS 72 Derivative Instructions                                                                                                                                                                                                       | B-1                                                  |

| APPENDIX C  | Sample Input/Output Program                                                                                                                                                                                                              | C-1                                                  |

| APPENDIX D  | Reference Tables                                                                                                                                                                                                                         | D-1                                                  |

| APPENDIX E  | ASCII Character Set and Hexadecimal Codes                                                                                                                                                                                                | E-1                                                  |

| APPENDIX F  | SYSTEMS 72 Instructions - Alphabetical Listing                                                                                                                                                                                           | F-1                                                  |

| APPENDIX G  | SYSTEMS 72 Instructions - Numerical Listing                                                                                                                                                                                              | G-1                                                  |

| APPENDIX H  | Effective Address Calculation Times                                                                                                                                                                                                      | H-1                                                  |

| APPENDIXI   | SYSTEMS 72 Special Derivatives Instructions                                                                                                                                                                                              | I-1                                                  |

#### LIST OF ILLUSTRATIONS

| Figure | Title                                              | Page |

|--------|----------------------------------------------------|------|

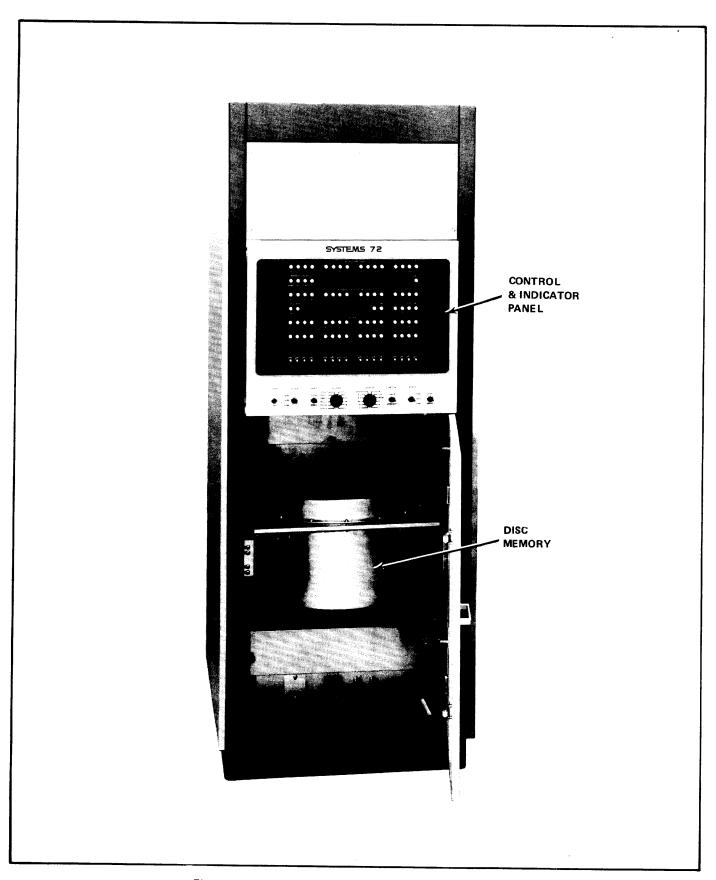

| 1-1    | Basic SYSTEMS 72 Digital Computer, Front View      | 1-6  |

| 1-2    | Simplified Block Diagram - SYSTEMS 72 Digital      |      |

|        | Computer                                           | 1-7  |

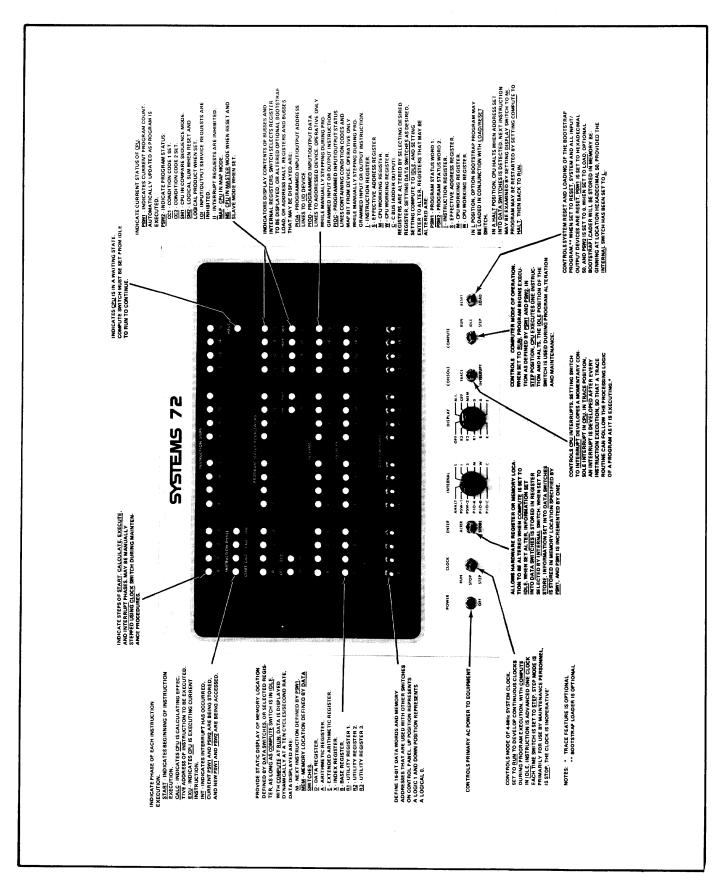

| 1-3.   | Front Panel Controls and Indicators                | 1-9  |

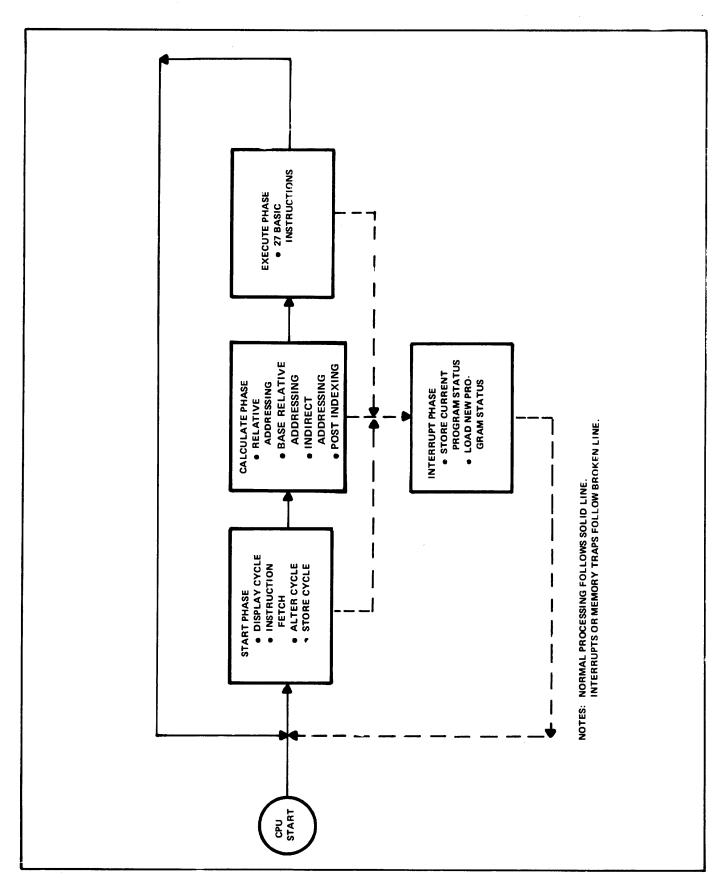

| 2-1    | Block Diagram - CPU Operational Phases             | 2-2  |

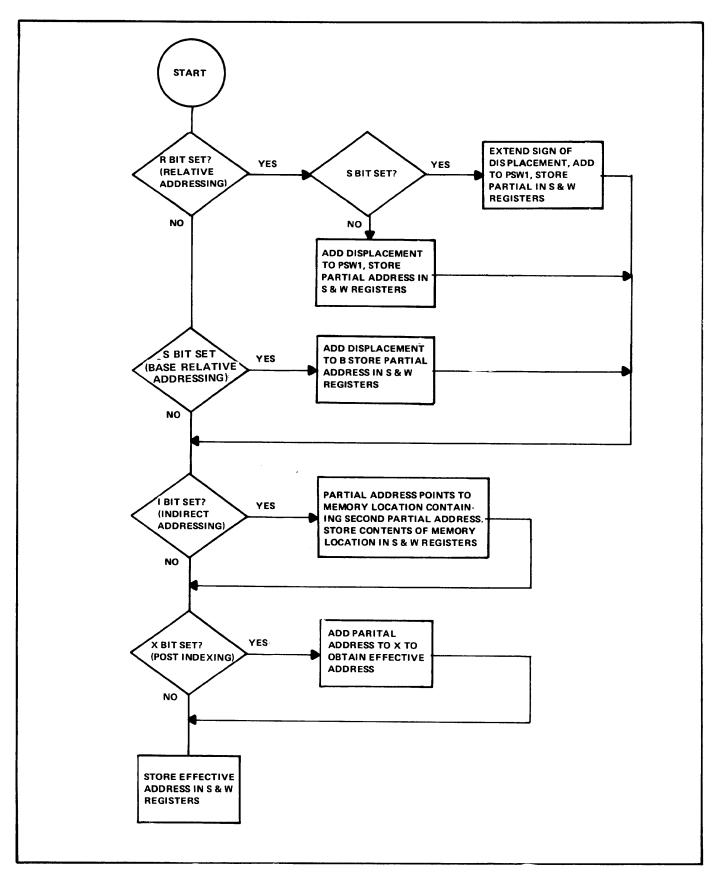

| 2-2    | Sequence Diagram - Effective Address Calculation   | 2-10 |

| 2-3    | Calculation Diagram - Effective Address            | 2-11 |

| 3-1    | Actual/Virtual Memory Configuration (Basic System) | 3-5  |

| 4-1    | Simplified Diagram - Input/Output System           | 4-5  |

#### LIST OF TABLES

| Table | Title                                                | Page |

|-------|------------------------------------------------------|------|

| 1-1   | SYSTEMS 72 Options                                   | 1-3  |

| 1-2   | SYSTEMS 72 Software                                  | 1-4  |

| 2-1   | Condition Code Configurations for Basic Instructions | 2-7  |

| 2-2   | CPU Basic Instructions                               | 2-13 |

#### LIST OF RELATED PUBLICATIONS

The following publications contain information not included in this manual, but necessary for a complete understanding of the SYSTEMS 72 Digital Computer.

| Publication Title                       | Publication No. |

|-----------------------------------------|-----------------|

| MA/10 Operating System Reference Manual | 323-720001      |

| Math Library Reference Manual           | 323-720002      |

| FORTRAN IV Reference Manual             | 323-720003      |

| MA/20 Reference Manual                  | *323-720004     |

| MAP Assembler Reference Manual          | 323-720006      |

| BASIC Reference Manual                  | 323-720007      |

| Interface Design Manual                 | 310-770000      |

| CPU/Memory Maintenance Guide            | 303-780000      |

|                                         |                 |

NOTE

(\* Preliminary)

#### **SECTION I**

#### INTRODUCTION AND DESCRIPTION

#### INTRODUCTION

This manual consists of four sections and three appendicies that describe the SYSTEMS 72 Digital Computer. Detailed reference information is provided for the major functional areas of the equipment, such as the central processor, core/disc memory system, and input/output system. The detailed information describes the instruction set used by the central processor, the actual/virtual memory concept used by the core/disc memory system, and the input/output programming used by the input/output system.

# PURPOSE OF EQUIPMENT

The purpose of SYSTEMS 72 is to offer the user a low-cost computer capable of executing large-scale programs while operating with a variety of input/output (I/O) devices. Modular expansion of core memory from 4096 sixteen-bit words for the basic configuration of the SYSTEMS 72, to 65,536 words in 4096-word increments, offers the user an effective trade-off in the higher cost of core versus the speed and efficiency at which the user's programs are executed.

Major features offered by the SYSTEMS 72 are as follows:

- 4096 word core memory expandable to 65,536 words

- 880-nanosecond core memory cycle time

- 32,768-words of programmable memory, expandable to 65,536 words

- 65,536-word memory extension disc, expandable to 131,072 words or 262,144 words.

- Virtual programmable memory to actual memory map

- Core memory write protection

- Automatic program fragmentation

- Dynamic program relocation

- Power fail safe

- Only single-word instructions

- User-defined instructions

- Privileged instructions

- Five-bit operation field

- Eight addressable registers

- Relative addressing, forward and backward

- Base-relative addressing

- Single-level indirect addressing

- Post-indexing

- Multilevel interrupt system

- Rapid context switching

- IOP-oriented input/output system

- Aysnchronous, demand-multiplexed input/output

- Data and command chaining

- Wide variety of hardware options and I/O devices

#### <u>OPTIONAL</u> EQUIPMENT

A wide variety of hardware options and I/O devices are provided for use with the SYSTEMS 72. Hardware options include priority interrupts, real-time clocks, memory parity, high speed registers, automatic bootstrap loader, high speed multiply/divide, console interrupt and direct access to memory. Peripheral I/O devices include paper tape punch/reader, card reader, various teletypes impact printers, disc drives, 7- and 9-track tape transports, and asynchronous data sets.

Table 1-1 lists the optional equipment available for use with SYSTEMS 72.

#### <u>PHYSICAL</u> CONFIGURATION

The basic configuration of SYSTEMS 72 is illustrated in figure 1-1. A card frame assembly mounted behind the control panel houses the circuit cards that comprise the central processor unit (CPU), core/disc memory system, power fail safe, and teletype controller. The first 4096-word core memory module, which is supplied with the basic system, is also installed in the card frame assembly. The card frame assembly will accomodate an additional Model 7230 Core Memory Module; however, further core memory expansion requires the Model 7231 Memory Extender Chassis.

In addition to the teletype controller and power fail safe, five I/O slots are provided in the card frame assembly to accomodate hardware options or controllers for the various I/O devices. If more than five slots are required for the hardware options or device controllers, the basic system capability is expanded by the Model 7271 I/O Extender Chassis.

The Model 7220 High Speed Multiply/Divide is installed in a dedicated slot in the card frame assembly. The same slot may also be used for other customer-required optional instructions. Another dedicated slot is provided for the Model 7240 Direct Access Channel or the Model 7241 Multiplexed Input/Output Processor.

Disc memory capacity of the SYSTEMS 72 may be increased by installing one of the Model 7235 through 7236 Disc Assemblies in place of the 65,536-word disc supplied with the basic system. Use of a larger disc memory in conjunction with the Model 7232 Memory Map Extension increases the programmable memory capacity of the system to 65,536 words.

The exact rack-mounted configuration of a particular system depends upon the number of rack-mounted peripheral devices, and whether or not the system requires the Model 7231 Memory Extender Chassis and Model 7271 I/O Extender Chassis.

#### <u>FUNCTIONAL</u> CONFIGURATION

The functional configuration of the basic SYSTEMS 72 is illustrated in figure 1-2. Data processing is controlled by the CPU, which receives input data from the control panel, teletype, or other I/O device. The CPU subsequently transfers the information to the core memory by way of the core/disc memory system.

Table 1-1. SYSTEMS 72 Options

| 4005 61-Inch Cabinet 4021 86-Pin Card Extender 4022 60-Pin Card Edge Connector 4023 -Conductor Cable 4024 60/25-Pin Connector Cable Assembly 4103 Paper Tape Punch/Reader and Controller 4211 Card Reader and Controller 4302 ASR-33 Teletype and Controller 4303 KSR-33 Teletype and Controller 4303 KSR-35 Teletype and Controller 4314 KSR-35 Teletype and Controller 4316 Buffered Impact Printer and Controller 4317 ASR Megabyte Disc Drive and Controller 4318 Megabyte Disc Drive and Controller 4319 ASR Megabyte Disc Drive and Controller 4310 ASR Megabyte Disc Drive and Controller 4311 ASR Megabyte Disc Drive and Controller 4312 ASR Megabyte Disc Drive and Controller 4313 ASR Megabyte Disc Drive and Controller 4314 ASR Megabyte Disc Drive and Controller 4315 Memory Extension Chassis | Model                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Model                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4414 4419 4417 24 Megabyte Disc Drive 4419 448 Megabyte Disc Drive 4420 2.4 Megabyte Disc Drive 4481 2.4 Megabyte Disc Pack 4485 4486 4499 4530 4530 4530 4530 4530 4530 4530 4530                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4021<br>4022<br>4023<br>4024<br>4103<br>4211<br>4302<br>4303<br>4313<br>4314<br>4361<br>4412<br>4414<br>4415<br>4417<br>4419<br>4420<br>4481<br>4485<br>4499 | 86-Pin Card Extender 60-Pin Card Edge Connector -Conductor Cable 60/25-Pin Connector Cable Assembly Paper Tape Punch/Reader and Controller Card Reader and Controller ASR-33 Teletype and Controller KSR-35 Teletype and Controller KSR-35 Teletype and Controller KSR-35 Teletype and Controller Buffered Impact Printer and Controller 24 Megabyte Disc Drive and Controller 48 Megabyte Disc Drive and Controller 2.4 Megabyte Disc Drive 48 Megabyte Disc Drive 2.4 Megabyte Disc Drive 2.4 Megabyte Disc Drive 2.4 Megabyte Disc Pack 48 Megabyte Disc Pack 48 Megabyte Disc Pack | 4535<br>4536<br>4590<br>4701<br>4760<br>7200<br>7210<br>7211<br>7212<br>7214<br>7220<br>7230<br>7231<br>7232<br>7235<br>7236<br>7241<br>7242<br>7245<br>7250<br>7251<br>7271 | 7-Track Tape Transport and Controller 7-Track Tape Transport Magnetic Tape Reel Asynchronous Data Set and Controller General Purpose I/O Interface SYSTEMS 72 Basic Computer Memory Parity Trap Card Assembly Real-Time Clock Card Assembly High Speed Register Card Assembly Automatic Bootstrap Loader Card Assembly High Speed Multiply/Divide Card Assembly 4K Core Memory Card Assembly Memory Extension Chassis Long Map Card Assembly 131K-Word Disc Assembly 262K-Word Disc Assembly Multiplexer Input/Output Processor MIOP Expansion Direct Access Interface Card Assembly Console Interrupt Card Assembly Priority Interrupt Pair Card Assembly I/O Extender Chassis |

TABLE 1-2. SYSTEMS 72 SOFTWARE

|      | T        | TABLE 1-2. SYSTEMS 72 SOFTWARE                              |

|------|----------|-------------------------------------------------------------|

| CODE | NUMBER   | TITLE                                                       |

| AAA. | 8000000  |                                                             |

| AAB  | 8000001  | MA/10 Kernel                                                |

| AAC  | 8000002  | MA/10 Programmed IOP                                        |

| AAD  | 8000003  | Loader Text Lister                                          |

| AAE  | 8000004  | Symbolic Editor                                             |

| AAF  | 8000005  | MA/CC1                                                      |

| AAG  | 8000006  | Symbol Concordance                                          |

| AAH  | 8000007  | MA/10 Linking Loader                                        |

| AAI  | 8000008  | MA/10 System Generator                                      |

| AAJ  | 8000009  | MAP Assembler                                               |

| AAK  | 8000010  | BASIC Compiler                                              |

| AAL  | 8000011  | FORTRAN IV Compiler                                         |

| AAM  | 8000012  | MA/10 Virtual Non-Linking Loader (32K)                      |

| AAN  | 8000013  | Debug - Basic                                               |

| AAO  | 8000014  | Debug - EXTENDED                                            |

| AAP  | 8000015  | MA/10 System Loader (32K)                                   |

| DAA  | 8000016  | MA/10 IOCS                                                  |

| AAR  | 8000017  | Card Reader Handler                                         |

| AAS  | 8000018  | Line Printer Handler                                        |

| AAT  | 8000019  | MA/10 Fixed Head Disc                                       |

| AAU  | 8000020  | MA/10 System INITIALIZE                                     |

| AAV  | 8000021  |                                                             |

| AAW  | 8000022  |                                                             |

| AAX  | 8000023  | MA/10 Virtual Non-Linking Loader (65K)                      |

| AAY  | 78000024 | MA/10 System Loader (65K)                                   |

| AAZ  | 8000025  | MA/10 Movable Head Disc Handler                             |

| ABA  | 8000026  | Monitor Services                                            |

| ABB  | 8000027  | MA/10 SYSPAGE                                               |

| ABC  | 8000028  | MA/10 IOCS Dibs/Cibs                                        |

| ABD  | 8000029  | MA/10 Teletype Handler                                      |

| ABE  | 8000030  | MA/10 Cassette & Magnetic Tape                              |

| ABF  | 8000031  | MEDIA                                                       |

| ABG  | 8000032  | D.P. Fixed Pt. Two's Complement and D.P. Fixed Pt. Absolute |

| ABH  | 8000033  | FI. Pt. Load and FI. PTStore                                |

| ABI  | 8000034  | D.P. Fixed Pt. Load & D.P. Fixed Pt.Store                   |

| ABJ  | 8000035  | Floating Point Normalize                                    |

| ABK  | 8000036  | Double Precision Fixed point Add, Subtract                  |

| ABL  | 8000037  | Single Precision Fixed Point Multiply                       |

| ABM  | 8000038  | Single Precision DIV                                        |

| ABN  | 8000039  | Floating Point Overflow                                     |

| ABO  | 8000040  | Floating Point Add, Subtract                                |

| ABP  | 8000041  | FI. Pt. Comp. and D.P. Fixed Pt. Comp                       |

| ABQ  | 8000042  | FI. Pt. Multiply and D.P. Fixed Pt. Multiply                |

| ABR  | 8000043  | FI. Pt. Divide and D.P. Fixed Pt. Divide                    |

| ABS  | 8000044  | Binary Integer to ASCII Conversion                          |

| ABT  | 8000045  | ASCII to Binary Integer Conversion                          |

|      |          |                                                             |

|      | 1        |                                                             |

|      | I.       |                                                             |

TABLE 1-2. SYSTEMS 72 SOFTWARE (Cont'd)

| CODE       | NUMBER                                           | TITLE                                       |

|------------|--------------------------------------------------|---------------------------------------------|

|            | <del>                                     </del> |                                             |

| ABU        | 8000046                                          | ASCII to Floating Point Conversion          |

| ABV        | 8000047                                          | Floating Point to ASCII Conversion          |

| ABW        | 8000048                                          | Floating Point Square Root                  |

| ABX        | 8000049                                          | Floating Point Natural Logarithm            |

| ABY        | 8000050                                          | Floating Point Common Logarithm             |

| ABZ        | 8000051                                          | Floaing Point Exponential (e <sup>X</sup> ) |

| ACA        | 8000052                                          | Floating Point Tangent                      |

| ACB        | 8000053                                          | Floating Point Sine, Cosine                 |

| ACC        | 8000054                                          | Floating Point Arc Tangent                  |

| ACD        | 8000055                                          | Floating Point Hyperbolic Tangent           |

| ACE<br>ACF | 8000056                                          | Random Number Generator                     |

| * <b>1</b> | 8000057                                          | Floating Point to Fixed Point Conversion    |

| ACG        | 8000058                                          | Fixed Point to Floating Point Conversion    |

| ACH        | 8000059                                          | CPU Confidence Test                         |

| ACI        | 8000060                                          | Full Memory Test                            |

| ACJ        | 8000061                                          | TTY Read;Punch Test                         |

| ACK        | 8000062                                          | Disc File Test                              |

| ACL        | 8000063                                          | Map Register Test                           |

| ACM        | 8000064                                          | Upper 4K Memory Test                        |

| ACN        | 8000065                                          | DAC Test                                    |

| ACO        | 8000066                                          | Absolute Dumper                             |

| LIB        | 801000                                           | IOCS' Library                               |

| LIB        | 801001                                           | Math Library                                |

|            |                                                  |                                             |

|            |                                                  |                                             |

| ļ          |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

|            |                                                  |                                             |

Figure 1-1. Basic SYSTEMS 72 Digital Computer, Front View

Information to be processed and transferred to the control panel, teletype, or other I/O device is read from the core memory under control of the core/disc memory system. The information is subsequently transferred to the CPU for output to the control panel or I/O device.

I/O data transfers are accomplished under control of an Input/Output Processor (IOP). The Input/Output Processor (IOP) is provided in the basic system as a Programmed Input/Output Processor (PIOP) or optionally as a hardware Multiplexed Input/Output Processor (MIOP). The PIOP is software-implemented, it appears to be a separate entity to both the user's program and the operating system. To set up a data transfer, the user's program specifies the direction and size of transfer, the appropriate location in virtual memory, and the action to be taken upon termination of the transfer. The Multiplexed Input/Output Processor (MIOP) is a hardware option that can be used to replace the PIOP. It serves to increase the bandwidth to about 700,000 words per second. The addition of this option has no effect on programs already written.

Several busses are used to facilitate transfer of data and address information. Data transfers between the CPU and control panel or I/O device are accomplished by way of the program I/O data bus, while data transferred between the CPU and core/disc memory system is exchanged by way of the memory data bus. The source of the data input to the CPU, or destination of the data output from the CPU, is defined by an effective address, which is calculated by the CPU and output on the associated bus.

Programs stored in the core or disc memory control the processing sequence. The core/disc memory system, under control of a small core-resident program which retrieves information required by the current program from the disc memory and stores the information in core for use by the CPU during processing. Information not required by the current program is transferred from core to disc.

Operator intervention into the processing sequence is by means of the switches located on the control panel, teletype, or other I/O device.

A Direct Access Channel (DAC), or a Multiplexed Input/Output Processor (MIOP) are provided as hardware options. The DAC permits direct data transfers between an I/O device and the core memory, so that the transfer is not under control of the CPU. This transfer rate is 1,000,000 words per second. The MIOP allows for the servicing of up to 64 devices concurrently. The bandwidth here is 700,000 words per second.

#### CONTROL PANEL

The operator control panel contains the controls and indicators necessary to display the current status of the computer, change the status as required, and alter the various registers and memory. Certain switches and indicators are also provided to facilitate maintenance of the computer. Figure 1-3 illustrates the controls and indicators on the operator control panel and provides a brief description of the function of each control and indicator.

#### <u>POWER TURN</u> ON PROCEDURE

To apply power to the basic configuration of SYSTEMS 72, connect the power cord from the system power supply to a source of 115-volt ac, single-phase power. Set the circuit breaker on the ac distribution panel in each rack to ON.

Figure 1-3. Front Panel Controls and Indicators

#### <u>LOADING</u> PROCEDURES

Loading procedures for SYSTEMS 72 depend upon whether the configuration is equipped with a Model 7214 Automatic Bootstrap Loader. If the optional loader is not installed, program information is assumed to originate at the teletype. In systems where the optional loader is installed, the DATA SWITCHES on the control panel are used to select the peripheral device from which the program information will be loaded. The first set of procedures listed below are for systems without the optional loader, and the second set are for systems with the loader.

#### <u>LOADING - NO</u> OPTIONAL LOADER

a. On the computer control panel, set the controls as follows:

| SWITCH      | SETTING               |

|-------------|-----------------------|

| CLOCK       | RUN                   |

| ALTER/STORE | OFF = Center position |

| INTERNAL    | PSW 1                 |

| DISPLAY     | OFF                   |

| CONSOLE     | OFF = Center position |

| COMPUTE     | IDLE                  |

| RESET/LOAD  | OFF = Center position |

| DATA        | OFF                   |

|             |                       |

- b. Momentarily set the RESET/LOAD switch to RESET.

- c. Key in the bootstrap loader by sequentially setting the DATA SWITCHES to the hexadecimal values listed below and momentarily setting the ALTER/STORE switch to STORE.

| MEMORY LOCATION | HEXADECIMAL VALUE |

|-----------------|-------------------|

| 50              | 0B5F              |

| 51              | 0960              |

| *52             | * 0608            |

| 53              | 0803              |

| *54             | *0834             |

| 55              | 1255              |

| 56              |                   |

| 57              |                   |

| 58              | 005A              |

| 59              | 0000              |

| ъ́А             | * 0148            |

| 5B              | 0900              |

| 5C              | 2700              |

| 5D              | 0F03              |

| 5E              | 3756              |

| 5F              | 0200              |

| 60              | 0056              |

|                 |                   |

In this example, the memory locations that have asterisks (52, 54, and 5A) are configured for a device on channel 8. If a device is on another channel, the values of the memory slots would change. Example: Paper reader on channel 'B' 52=060B, 54=8037, and 5A=014B.

- d. Momentarily set the RESET/LOAD switch to RESET.

- e. Install appropriate punched paper tape in the teletype paper tape reader.

- f. Set COMPUTE switch on computer control panel to RIIN.

- g. When tape stops, set COMPUTE switch to IDLE.

- h. Momentarily set RESET/LOAD switch to RESET.

- i. Set DATA SWITCH 7 to the UP position.

- j. Momentarily set ALTER/STORE switch to ALTER.

- k. Set COMPUTE switch to RUN to start program from location X'0100'.

#### <u>LOADING</u> OPTIONAL LOADER

- a. On the computer control panel, set COMPUTE switch to IDLE, and the INTERNAL Switch To L.

- b. Momentarily set RESET/LOAD switch to RESET, then to LOAD, and back to RESET.

- c. Set the appropriate device address into the DATA SWITCHES right justified.

- d. Install punched paper tape, magnetic tape, etc. on appropriate peripheral device.

- e. Set COMPUTE switch on computer control panel to RUN.

- f. When device stops, set COMPUTE TO IDLE.

- g. Momentarily set RESET/LOAD switch to RESET, then to LOAD.

- h. Set COMPUTE switch to RUN to start program from location X'0101'.

#### MODIFYING MEMORY FROM THE CONTROL PANEL

Any programmable register or memory location may be modified by operating the switches on the control panel as follows:

- a. Set the COMPUTE switch to IDLE and the INTERNAL switch to PSW1.

- b. Set DATA SWITCHES to hexadecimal address of desired memory location and momentarily set ALTER/STORE switch to ALTER. This sets program status word 1 (PSW1) to the memory location to be modified.

- c. Set DATA SWITCHES to hexadecimal value to be stored in selected memory location, and momentarily set ALTER/STORE switch to STORE. This stores the selected value in the location defined by PSW1, after which PSW1 is automatically incremented by one. (The MAP indicator in the PROGRAM STATUS DOUBLEWORD on the control panel indicates that the address defined by PSW1 is virtual when the indicator is set and actual when the indicator is reset.)

- d. To store additional hexadecimal values in sequential memory locations, set each new value into the DATA SWITCHES and momentarily set the ALTER/STORE switch to STORE.

#### DISPLAYING MEMORY AT THE CONTROL PANEL

Any core memory location may be displayed on the DISPLAY indicators by operating the switches on the control panel as follows:

- a. Set the desired memory address into the DATA SWITCHES.

- b. Set the DISPLAY switch to MEM to display the contents of the location specified by the DATA SWITCHES. (A toggle switch located inside the control panel determines whether the memory location selected by the DATA SWITCHES is an actual address or a virtual address.)

In addition to the memory display switch setting, there are settings for the display of any hardware registers (memory locations 0 - 7)

#### Note

The DISPLAY indicators are updated at a 10-cycle-per-second rate. This allows the user to change the DATA SWITCHES to any memory address as the program is executing and display the contents of the memory location in the DISPLAY indicators.

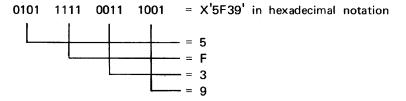

## HEXADECIMAL NOTATION

Throughout this manual and related documents, memory address are referenced in hexadecimal notation, which is indicated by the letter X followed by four characters in single quotation marks. Each character corresponds to a four-bit group of basic 16-bit word used by SYSTEMS 72. An example of hexadecimal code and a coded 16-bit word is provided below.

| <u>HEXADECIMAL</u> |       |      | HEXADECIMAL |  |

|--------------------|-------|------|-------------|--|

| CODE               | VALUE | CODE | VALUE       |  |

| 0000               | 0     | 1000 | 8           |  |

| 0001               | 1     | 1001 | 9           |  |

| 0010               | 2     | 1010 | Α           |  |

| 0011               | 3     | 1011 | В           |  |

| 0100               | 4     | 1100 | С           |  |

| 0101               | 5     | 1101 | D           |  |

| 0110               | 6     | 1110 | E           |  |

| 0111               | 7     | 1111 | F           |  |

#### SECTION II

#### CENTRAL PROCESSOR UNIT

#### INTRODUCTION

The Central Processor Unit (CPU) operates under control of an instruction repertoire consisting of 27 basic instructions. (Five optional instructions are reserved for user-selected functions.) Fifteen of the basic instructions are register-expandable, which allows the CPU to operate directly on eight addressable full-word registers. In addition, the CPU allows the user to make use of features such as: condition codes, master/slave operating modes, double indexing, displacement indexing, indirect addressing, and relative addressing forward and backward.

Rapid context switching, in which the CPU changes from the current program environment to a new program environment, assures efficient handling of interrupts and smooth changes in operating mode.

## CPU OPERATIONAL PHASES

The CPU has four operational phases: start, calculate, execute, and interrupt. These phases correspond to the four INSTRUCTION PHASE indicators located on the control panel. At any given time, the CPU is operating in one of these phases; however, during normal processing more than one indicator may be on due to the speed at which data is being processed.

Figure 2-1 is a general block diagram of the four operational phases. When first intialized, the CPU enters the start phase where it remains until the COMPUTE switch is set to RUN or STEP. This action initiates an instruction fetch cycle, which obtains an instruction from memory, stores the instruction, and causes the CPU to enter the calculate phase.

During the calculate phase, the CPU determines an effective address that is used to define a specific memory location, or provide additional information regarding the operation to be performed. After calculation of the effective address, the CPU enters the execute phase and performs the operation specified in the instruction. When the instruction has been executed, the CPU returns to the start phase; and if the COMPUTE switch is set to RUN, it acquires another instruction. The process is then repeated for the new instruction. (If the COMPUTE switch was initially set to STEP, it must again be set to STEP to execute another instruction.)

The sequence from start, to calculate, to execute, and back to start is the normal processing cycle for the CPU. In the run mode, this cycle will continue until an interrupt is detected, indicating that the CPU is to halt its current operation in order to service the requesting device. A normal interrupt cycle requires the CPU to complete the current instruction, so that the interrupt phase is entered from the execute phase. Two other conditions will also cause the CPU to enter the interrupt phase:

- Receipt of an interrupt request after the CPU has been halted in the start phase.

- Detection of a memory trap by the core/disc memory system. The trap

condition causes the CPU to halt its current operation in the start, calculate,

or execute phase to process the memory trap.

Figure 2-1. Block Diagram - CPU Operational Phases

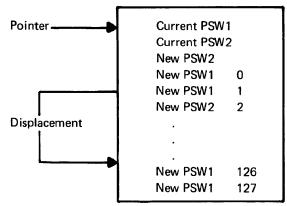

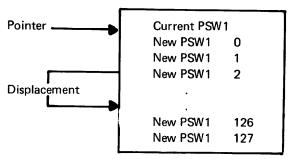

Regardless of the conditions under which the CPU enters the interrupt phase, processing of the interrupt is the same. First the CPU stores the current program environment defined by the program status doubleword, which is displayed by the PROGRAM STATUS DOUBLEWORD indicators on the control panel. A program status doubleword associated with the interrupting device is then transferred from memory to the CPU and the CPU returns to the start phase to begin processing the interrupt.

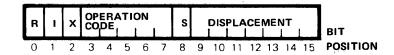

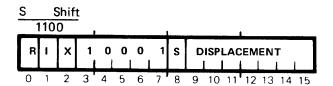

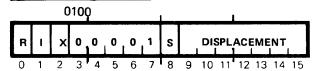

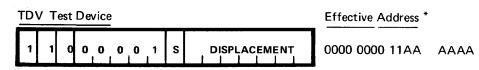

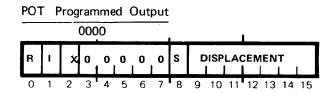

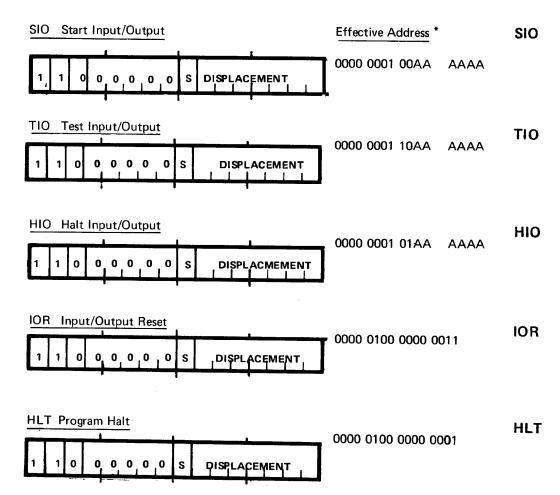

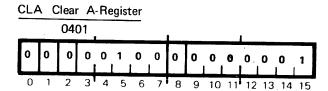

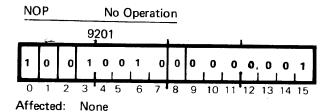

#### INSTRUCTION FORMAT

Processing performed by the CPU is accomplished under control of memory reference instructions, which are in the single-word format indicated below.

The various fields of the memory reference instructions are used to specify the operation to be performed by the CPU and the effective address required during execution of the instruction. Specific functions associated with each field of the instruction are indicated below.

| <u>Field</u> | Function                                                                                                                                                                                                             |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>R</b>     | Relative Addressing - Specifies that the address is relative to the program count in program status word 1 (PSW1). PSW1 is displayed on the front panel by indicators 0 through 15 of the PROGRAM STATUS DOUBLEWORD. |

| <b>1</b>     | Indirect Addressing - Specifies an indirect reference is to be used in calculating the effective address.                                                                                                            |

| X            | Post-Indexing - Specifies calculation of an address relative to the index count stored in the index (X) register. X-Register is displayed by the DISPLAY indicators in conjunction with the DISPLAY switch.          |

| OPERATION    | Operation Code - Specifies the operation next be executed by the CPU. The current contents of the instruction (I) register are displayed by the DISPLAY indicators with the DISPLAY switch in the NI position.       |

|              | Base-Relative Addressing - Specifies the sign of the displacement when the R-bit is set, indicating relative addressing. Specifies pre-indexing by adding the Base Register when the R-bit is reset.                 |

#### **DISPLACEMENT**

Address Displacement - Specifies the displacement to be used in calculation of the effective address.

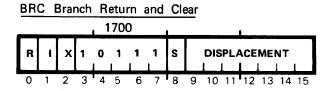

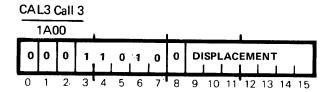

Several instructions executed by the CPU use certain fields for special purposes. For example, conditional branch instructions are incapable of indirect addressing and post-indexing, so for these instructions the I and X fields are used to mask the condition codes. In addition, a branch return and clear instruction does not include post-indexing. In this case, the X field indicates whether the highest active interrupt is to be cleared.

#### ADDRESSABLE REGISTERS

SYSTEMS 72 contains eight full-word addressable registers. In configurations without the Model 7212 High-Speed Register option, the registers occupy the first eight core memory locations. In configurations containing the high-speed register option, the addressable registers consist of eight integrated-circuit, flip-flop registers that increase the speed and efficiency of the CPU. In either case, the registers are always addressable as absolute locations X'0000' through X'0007'. (Effective addresses in this range are not mapped.)

All eight addressable registers have general utility and several perform special functions. A brief summary of each register is provided below:

| Register | Name                    | Address | Special Function                                                                                                                                   |

|----------|-------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| A        | Accumulator             | X'0001' | Store result of arithmetic, logical, compare, and shift operations                                                                                 |

| В        | Base Register           | X'0004' | Base-Relative Addressing                                                                                                                           |

| D        | Data Register           | x'0000' | Store 16-bit data words output to, or input from, the programmed input/output data bus.                                                            |

| E        | Extended<br>Accumulator | x'0002' | Used as the low-order extension of the accumulator (A) register during double register shift operations, and optional Multiply/Divide Instructions |

| X        | Index Register          | X'0003' | Post-indexing and looping                                                                                                                          |

| R1       | Utility Register 1      | X'0005' | None                                                                                                                                               |

| R2       | Utility Register 2      | X'0006' | None                                                                                                                                               |

| R3       | Utility Register 3      | X'0007' | None                                                                                                                                               |

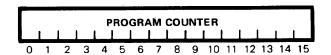

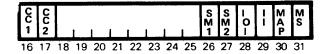

### PROGRAM STATUS DOUBLEWORD

The program status doubleword, which contains the current program environment is displayed on the PROGRAM STATUS DOUBLEWORD indicators on the control panel. The format for the two words is illustrated below:

Program Status Word 1 (PSW1)

Program Status Word 2 (PSW2)

Since the program status doubleword represents a summary of the current program environment, the CPU is able to transfer control rapidly from one program to another. The transfer process, which is referred to as rapid context switching, increases the efficiency of SYSTEMS 72 in processing interrupts and transferring control between user programs and the operating system.

Rapid context switching occurs during the processing of interrupts, memory traps, or execution of a Call 1 or Call 2 instruction. If one of these events is detected, the current program status doubleword is exchanged for a new doubleword pertaining to the routine being called. After the interrupt has been processed, a branch return and clear instruction is used to return control to the original program status doubleword.

As indicated in the diagram of the program status doubleword, PSW1 contains a program count that indicates the memory address of the next instruction to be executed. PSW1 steps sequentially with every instruction execution, unless redirected by a branch instruction, a call instruction, an interrupt, or a memory trap. Program status word 2 (PSW2) defines the program operating environment through a series of status bits. The purpose of each status bit is discussed below:

<u>Bits</u>

**Function**

CC1 and CC2

<u>Condition Codes</u> - Indicate the result of an instruction execution or during programmed input/output operations the status of the peripheral device. Instructions that alter the condition codes are defined in table 2-1. Interrupts also alter the condition codes.

#### **Bits**

#### **Functions**

SM1 and SM2

Compare Sequence Mode - Sequence mode 1 (SM1) places the CPU in the compare sequence mode, in which only the compare instruction is allowed to alter the condition codes. During the compare sequence mode, the result of each comparison combines logically with the current condition code settings as controlled by sequence mode 2 (SM2). If SM2 is set, the bits destined for the condition codes form the logical OR in which logical ONES are developed in those bit positions where either or both inputs are logical ONES. If SM2 is reset, the bits form the logical AND in which logical ONES are developed only in those bit positions where either, but not both, operands contain logical ONES.

101

Input/Output Inhibit - IOI blocks all input/output service requests when set. The software-implemented programmed input/output processor (PIOP) normally allows input/output service requests to take priority over interrupt requests, which signal the end of a data transfer. With IOI set, the low priority interrupt requests are allowed, but all input/output service requests are inhibited. (Refer to Section IV for a discussion of the interrupt system.)

П

Interrupt Inhibit - II blocks all interrupt service requests, but not input/output service requests. Blocking the interrupt request prevents an interrupt from becoming active, but does not prevent an armed interrupt from entering the waiting state. (Refer to section IV for a discussion of the interrupt system.)

MAP

Mapped Mode - MAP allows a memory map in the core/disc memory system to translate program addresses in virtual memory to actual addresses in core memory. All programs are usually mapped. (Refer to section III for a discussion of the core/disc memory system.)

MS

Master/Slave - MS prevents execution of privileged instructions while the CPU is in the slave mode (MS reset). The instruction repertoire contains four privileged instructions; PIN, POT, BRC, and CAL1. The operating systems always operate with MS reset; user programs normally do not.

Table 2-1. Condition Code Configurations for Basic Instructions

| Instruction | Condition Code Configuration                                       |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------|--|--|--|--|--|--|

| POT = 00    | Function of Peripheral Device                                      |  |  |  |  |  |  |

| PIN = 01    | Function of Peripheral Device                                      |  |  |  |  |  |  |

| AND = 02    | CC1 CC2 1 1 A REGISTER < 0 0 0 A REGISTER = 0 1 0 A REGISTER > 0   |  |  |  |  |  |  |

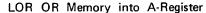

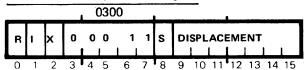

| LOR = 03    | CC1 CC2 1 1 A REGISTER < 0 0 0 A REGISTER = 0 1 0 A REGISTER > 0   |  |  |  |  |  |  |

| EOR = 04    | CC1 CC2 1 1 1 A REGISTER < υ 0 0 A REGISTER = 0 1 0 A REGISTER > 0 |  |  |  |  |  |  |

| LDD = 08    | CC1 CC2 1 1 D REGISTER < 0 0 0 D REGISTER = 0 1 0 D REGISTER > 0   |  |  |  |  |  |  |

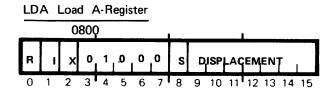

| LDA = 09    | CC1 CC2 1 1 A REGISTER < 0 0 0 A REGISTER = 0 1 0 A REGISTER > 0   |  |  |  |  |  |  |

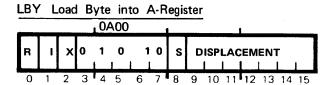

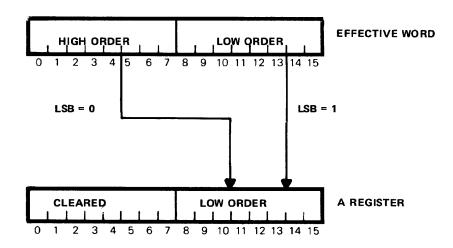

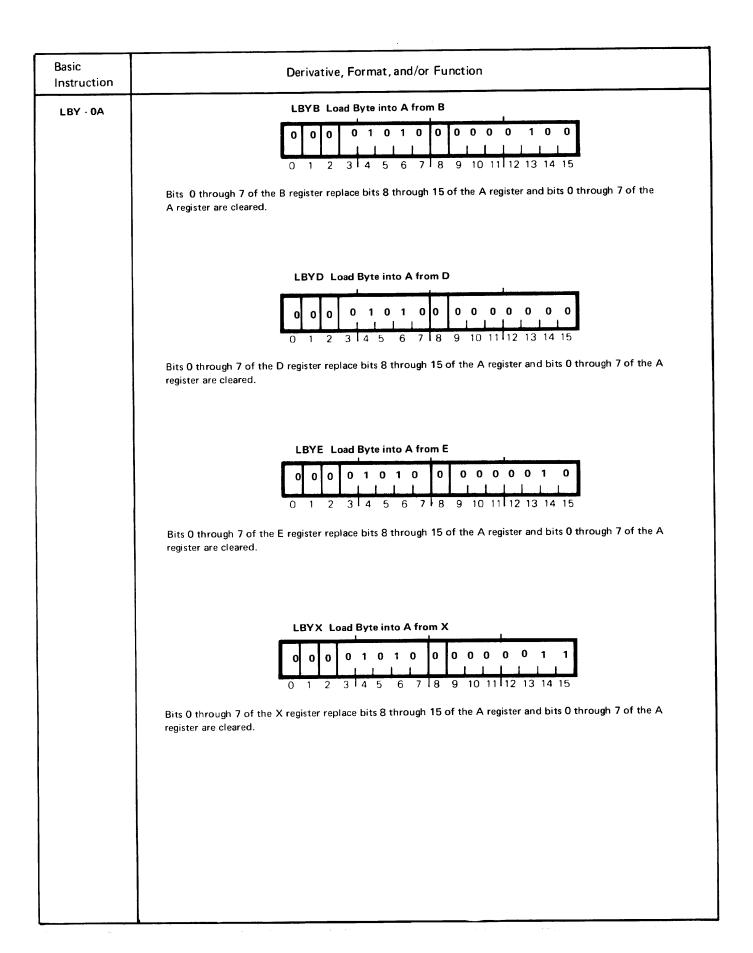

| LBY = 0A    | CC1 CC2<br>0 0 A REGISTER = 0<br>1 0 A REGISTER > 0                |  |  |  |  |  |  |

| LDX = 0B    | CC1         CC2           1         1         X REGISTER < 0       |  |  |  |  |  |  |

| LDB = 0C    | CC1 CC2 1 1 1 B REGISTER < 0 0 0 B REGISTER = 0 1 0 B REGISTER > 0 |  |  |  |  |  |  |

|             |                                                                    |  |  |  |  |  |  |

Table 2-1. Condition Code Configurations for Basic Instructions (Cont'd)

| Instruction | Condition Code Configuration                                                                                                                                                                                                                                                                                                      |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD = 0D    | CC1         CC2           0         0         NO CARRY - NO OVERFLOW           0         1         NO CARRY - OVERFLOW           1         0         CARRY - NO OVERFLOW           1         1         CARRY - OVERFLOW                                                                                                           |

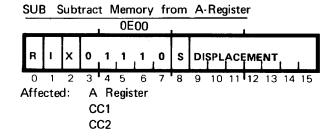

| SUB = 0E    | CC1         CC2           0         0         NO CARRY - NO OVERFLOW           0         1         NO CARRY - OVERFLOW           1         0         CARRY - NO OVERFLOW           1         1         CARRY - OVERFLOW                                                                                                           |

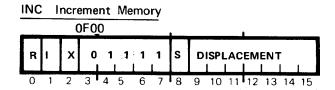

| INC = ÓF    | CC1         CC2           0         0         NO CARRY - NO OVERFLOW           0         1         NO CARRY - OVERFLOW           1         0         CARRY - NO OVERFLOW           1         1         CARRY - OVERFLOW                                                                                                           |

| CMP = 10    | CC1 CC2  1 1 A REGISTER < EFFECTIVE WORD  0 0 A REGISTER = EFFECTIVE WORD  1 0 A REGISTER > EFFECTIVE WORD                                                                                                                                                                                                                        |

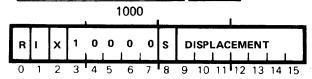

| S = 11      | LEFT SHIFT CC1 CC2  0 O A REGISTER BIT D ORIGINALLY = 0 AND HAS RECEIVED ONLY 0's  0 1 A REGISTER BIT 0 ORIGINALLY = 1 AND HAS RECEIVED AT LEAST ONE 1  1 O A REGISTER BIT 0 ORIGINALLY = 1 AND HAS RECEIVED AT LEAST ONE 0  1 1 A REGISTER BIT 0 WAS 0 AND RECEIVED AT LEAST ONE 1                                               |

|             | RIGHT SHIFT CC1 CC2  0 0 A REGISTER BIT 15 AND E REGISTER BIT 15 HAVE RECEIVED ONLY 0's  0 1 A REGISTER BIT 15 RECEIVED A 0 AT LEAST ONCE AND BIT 15 OF E AT LEAST ONE 1  1 0 A REGISTER BIT 15 RECEIVED A 1 AT LEAST ONCE AND BIT 15 OF E AT LEAST ONE 0  1 1 A REGISTER BIT 15 AND E REGISTER BIT 15 RECEIVED A 1 AT LEAST ONCE |

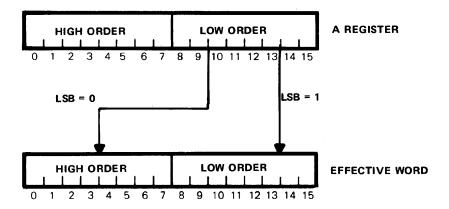

#### ADDHESS CALCULATION

The configuration of the R, I, X, and S bits in the instruction is examined in conjunction with the displacement field to compute the effective memory address. The calculation is performed in exactly the same manner, regardless of whether the effective address will be used to specify a memory location, as in a load instruction, or to specify further details of the instruction as in a shift instruction. Figure 2-2 illustrates the sequence of the address calculation and figure 2-3 indicates the resulting address.

#### <u>RELATIVE</u> ADDRESSING

The CPU first checks the R-bit to determine if an address relative to the current program count is PSW1 is required. If the R bit is set, indicating relative addressing, the S (sign) bit is checked to determine if the address is forward or backward of the current program count.

Relative Backward - When the S-bit is set, indicating a backward address, the CPU extends the sign bit into bits 0 through 7 of the instruction. Extending the sign is accomplished by providing all ONE's in bits 0 through 7, so that the internal adder develops the TWO's complement of the address. The resultant partial address may be up to 128 locations backward from the current program count in PSW1.

Relative Forward - When the S-bit is reset, indicating a forward address, calculation of the partial address takes place in basically the same manner as a relative backward address, except that the sign is not extended into bits 0 through 7 of the instruction. In this case, all ZERO's are provided in bits 0 through 7, so that the internal adder merely adds the displacement to the program count. The resultant partial address may be up to 127 locations forward of the current program count in PSW1.

#### BASE-RELATIVE ADDRESSING

If the R-bit is reset when checked by the CPU, the S-bit is examined to determine if pre-indexing (base addressing) is required. In this case, the CPU reads the contents of the B (base) register, and adds this value to the current program count. The resultant partial address may be up to 127 locations forward of the count in the B-register.

Figure 2-2. Sequence Diagram - Effective Address Calculation

| TYPE OF ADDRESSING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INSTRUCTION FORMAT                OPERATION   S DISPLACEMENT   OPERATION FERFORMED   RESULTANT ADDRESS               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| RELATIVE<br>REMITS ADDRESSING 127 LOCATIONS FORWARD<br>AND 128 BACK FROM CURRENT ADDRESS IN<br>PSWI REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ×                                                                                                                    |

| BASE RELATIVE ADDRESSING PERM TS ADDRESSING 128 LOCATIONS FORWARD FROM CURRENT ADDRESS IN B REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2'S COMPLEMENT IF BACKWARD ADDRESS  0 X X X   1   1   1   1   1   1   1   1                                          |

| INDIRECT     PERMITS ACCESSIVE MENDRY LOCATION CON- TAMING SECOND PARTIAL ADDRESS THAT DEFINES     ANY DESIRED LOCATION IN MENORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | X   1   X                                                                                                            |

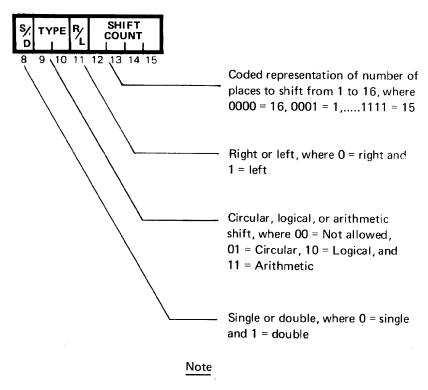

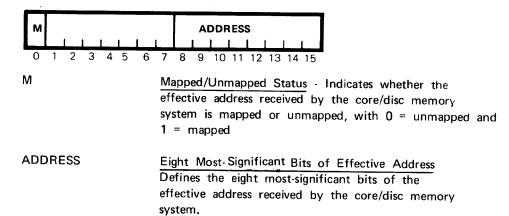

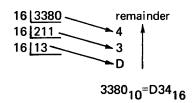

| • POST INDEXING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | X         1                                                                                                          |