# REFERENCE MANUAL SYSTEMS 86 General Purpose Computer

September 1969

ALL SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

301-860000-000 Price: \$10.00

### LIST OF EFFECTIVE PAGES

The total number of pages in this manual is 250, consisting of the following:

| Page Number       | Issue    |

|-------------------|----------|

| Title             | Original |

| A                 | Original |

| i through iv      | Original |

| 1-1 through 1-8   | Original |

| 2-1 through 2-20  | Original |

| 3-1 through 3-10  | Original |

| 4-1 through 4-4   | Original |

| 5-1 through 5-182 | Original |

| A-1 through A-8   | Original |

| B-1 and B-2       | Original |

| C-1 and C-2       | Original |

| D-1 and D-2       | Original |

| E-1 and E-2       | Original |

| F-1 through F-4   | Original |

### TABLE OF CONTENTS

|             |                                                  | Page |

|-------------|--------------------------------------------------|------|

| SECTION I   | SYSTEM CHARACTERISTICS                           |      |

|             | Introduction                                     | 1-1  |

|             | System Structure                                 | 1-1  |

|             | System Characteristics                           | 1-4  |

|             | Physical Characteristics                         | 1-7  |

| SECTION II  | COMPUTER ORGANIZATION                            |      |

|             | Memory Organization                              | 2-1  |

|             | Memory Addressing                                | 2-1  |

|             | Effective Address                                | 2-1  |

|             | No Address Modification                          | 2-1  |

|             | Indexing                                         | 2-5  |

|             | Indirect Addressing                              | 2-5  |

|             | Combined Indexing and Indirect Addressing        | 2-6  |

|             | Instruction Formats                              | 2-6  |

|             | Memory Reference Instructions                    | 2-7  |

|             | Immediate Operand Instructions                   | 2-7  |

|             | Input/Output Instructions                        | 2-8  |

|             | Interrupt Control Instructions                   | 2-8  |

|             | Inter-Register Instructions                      | 2-9  |

|             | Shift Instructions                               | 2-9  |

|             | Operand Formats                                  | 2-9  |

|             | Error Checking                                   | 2-14 |

|             | Undefined Instruction                            | 2-14 |

|             | Non-Present Memory Addressing                    | 2-14 |

|             | Arithmetic Exception                             | 2-15 |

|             | Privilege Violation                              | 2-15 |

|             | Central Processor Options                        | 2-15 |

| SECTION III | INPUT/OUTPUT                                     |      |

|             | Input/Output Organization                        | 3-1  |

|             | Transfer Control Word                            | 3-3  |

|             | Device Controller Channel Types                  | 3-5  |

|             | Device Controller Channel Priority and Parameter |      |

|             | Assignments                                      | 3-5  |

|             | Peripheral Device Control                        | 3-8  |

|             | Block Transfer Sequence                          | 3-9  |

|             | Automatic Reinitialization                       | 3-10 |

|             | Single Transfers                                 | 3-10 |

# TABLE OF CONTENTS (Cont'd)

|            |                                                   | Page       |

|------------|---------------------------------------------------|------------|

| SECTION IV | PRIORITY INTERRUPTS                               |            |

|            | Interrupts and Trap System                        | 4-1<br>4-1 |

|            | Traps                                             | 4-1        |

|            | Input/Output Transfer Interrupts                  | 4-1        |

|            | Basic Interrupts                                  | 4-2        |

|            | Dedicated Memory Locations                        | 4-2        |

|            | Program Control of Interrupts                     | 4-3        |

|            | Interrupt Servicing                               | 4-4        |

| SECTION V  | COMPUTER INSTRUCTIONS                             |            |

|            | Introduction                                      | 5-1        |

|            | Load/Store Instructions                           | 5-4        |

|            | Fixed-Point Arithmetic Instructions               | 5-38       |

|            | Floating-Point Arithmetic Instructions            | 5-72       |

|            | Logical Instructions                              | 5-82       |

|            | Bit Manipulation Instructions                     | 5-101      |

|            | Compare/Branch Instructions                       | 5-111      |

|            | Register Transfer Instructions                    | 5-136      |

|            | Shift Operation Instructions                      | 5-148      |

|            | Control Instructions                              | 5-165      |

|            | Interrupt Instructions                            | 5-174      |

|            | Input/Output Instructions                         | 5-180      |

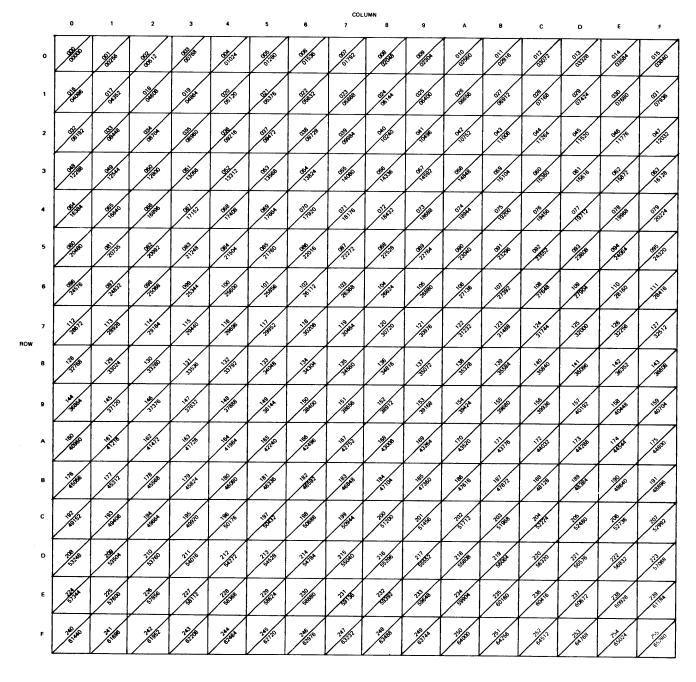

|            | APPENDIX A — Hexadecimal-Decimal Conversion Table | A-1        |

|            | APPENDIX B — Hexadecimal Conversion Table         | B-1        |

|            | APPENDIX C — Hexadecimal Additions                | C-1        |

|            | APPENDIX D — Numerical Information                | D-1        |

|            | APPENDIX E - USASCII Interchange Code Set with    | ٠,         |

|            | Card Punch Codes                                  | E-1        |

|            | APPENDIX F — SYSTEMS 86 Computer Instruction Set  | F-1        |

|            |                                                   |            |

| e.         | LIST OF ILLUSTRATIONS                             |            |

|            |                                                   |            |

| Figure     |                                                   | Page       |

| 1-1        | SYSTEMS 86 Computer Block Diagram                 | 1-3        |

| 1-2        | Data Organization                                 | 1-8        |

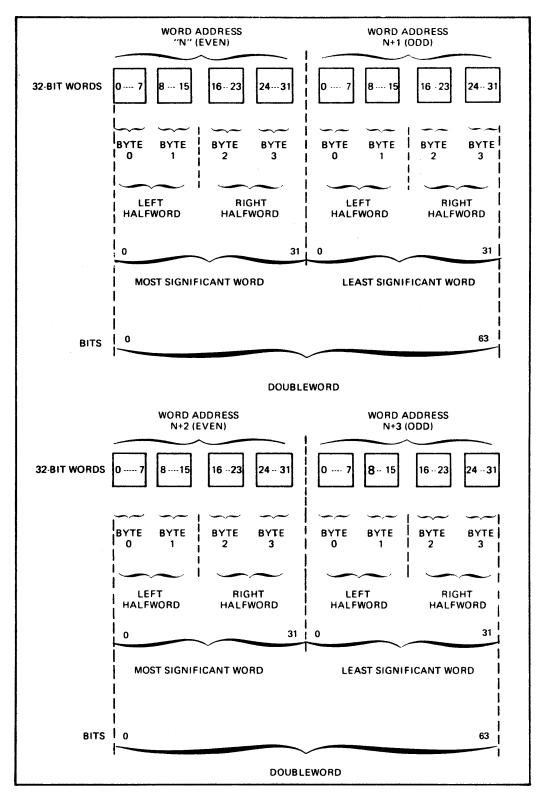

| 2-1        | Information Boundaries in Memory                  | 2-2        |

|            |                                                   |            |

### LIST OF ILLUSTRATIONS (Cont'd)

| Figure |                                                      | Page |

|--------|------------------------------------------------------|------|

| 2-2    | Positioning of Information Transferred Between       |      |

|        | Memory and Registers                                 | 2-3  |

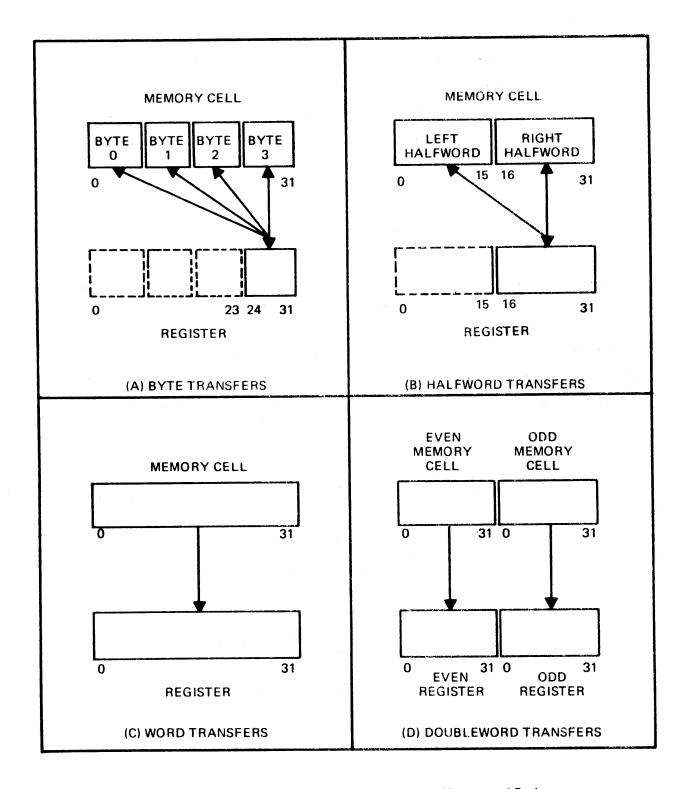

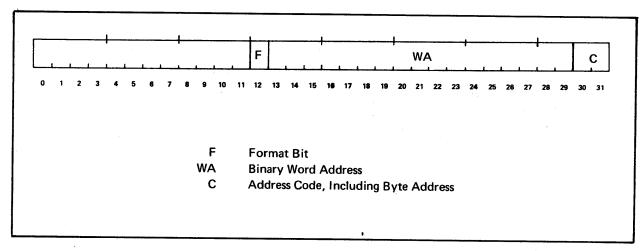

| 2-3    | Memory Address Format                                | 2-4  |

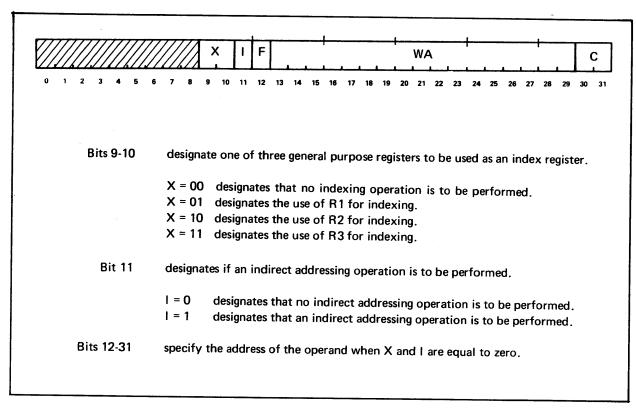

| 2-4    | Effective Address Format                             | 2-4  |

| 2-5    | Indirect Address Format                              | 2-6  |

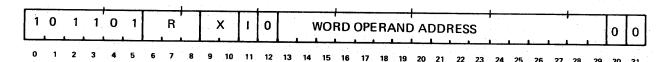

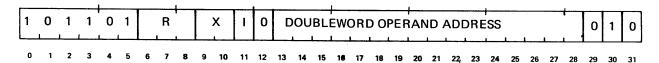

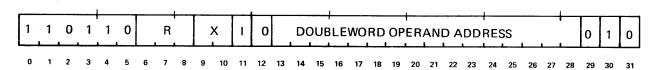

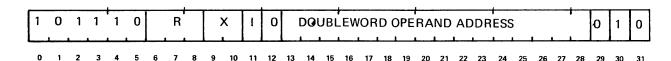

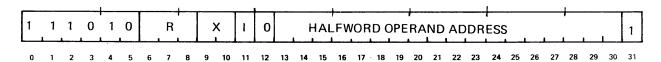

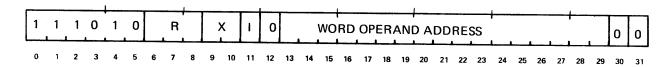

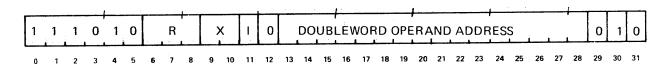

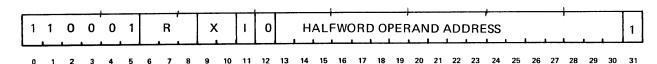

| 2-6    | Memory Reference Instruction Format                  | 2-7  |

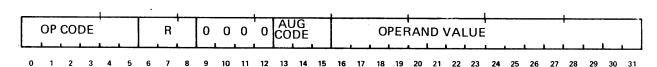

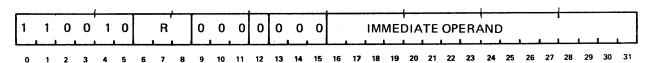

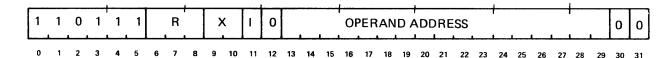

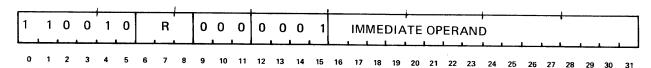

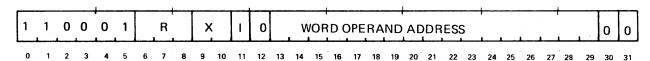

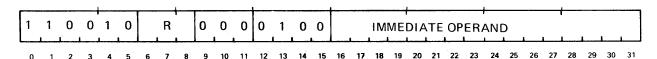

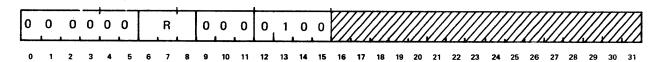

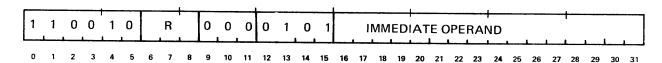

| 2-7    | Immediate Instruction Format                         | 2-7  |

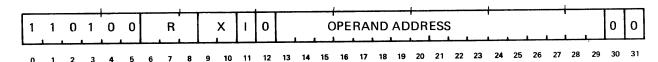

| 2-8    | Input/Output Instruction Format                      | 2-8  |

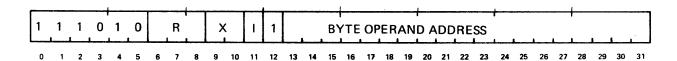

| 2-9    | Interrupt Control Instruction Format                 | 2-8  |

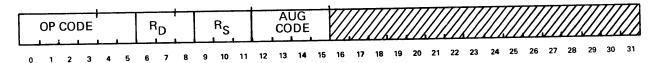

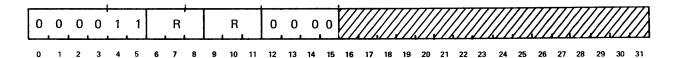

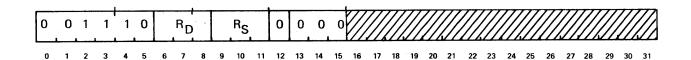

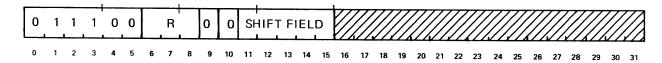

| 2-10   | Inter-Register Instruction Format                    | 2-9  |

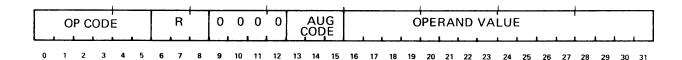

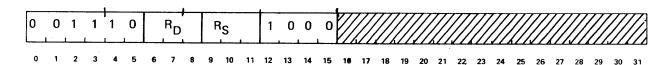

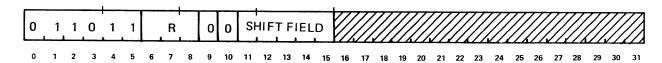

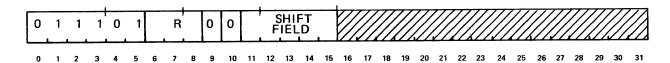

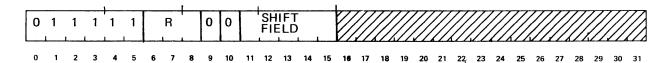

| 2-11   | Shift Instruction Format                             | 2-10 |

| 2-12   | Arithmetic Operation Formats for Fixed-Point Numbers | 2-11 |

| 2-13   | Floating-Point Formats                               | 2-12 |

| 2-14   | Program Status Word Format                           | 2-13 |

| 3-1    | Input/Output Transfer Paths                          | 3-2  |

| 3-2    | Transfer Control Word Format                         | 3-4  |

|        | LIST OF TABLES                                       |      |

| Table  |                                                      | Page |

| 1-1    | SYSTEMS 86 Computer and Options                      | 1-2  |

| 1-2    | Basic Hexadecimal Numbering System                   | 1-8  |

| 2-1    | Operand Format Code                                  | 2-5  |

| 2-2    | Condition Code Definitions                           | 2-13 |

| 2-3    | Privileged Instruction Set                           | 2-17 |

| 2-4    | Memory Protect Page Designations                     | 2-17 |

| 2-5    | Privileged Operating Feature States                  | 2-18 |

| 2-6    | Multiport Memory Protect Register Bit Designations   | 2-19 |

| 2-7    | Multiport Memory Access Control Bit Definitions      | 2-19 |

| 3-1    | Transfer Control Word Format Code                    | 3-5  |

| 3-2    | Device Controller Channel Assignments                | 3-7  |

| 4-1    | Priority Interrupt Dedicated Memory Locations        | 4-2  |

| 5-1    | Symbol Definitions                                   | 5-1  |

Typical SYSTEMS 86 Computer Configuration

### **INSTRUCTION GROUPS**

For ease of reference the mnemonic for each instruction has been placed in the upper outside corner of each page. Also the instructions have been divided into eleven groups with tab designations as follows for each group.

LOAD/STORE

FIXED-POINT ARITHMETIC

FLOATING-POINT ARITHMETIC

LOGICAL

**BIT MANIPULATION**

COMPARE/BRANCH

REGISTER TRANSFER

SHIFT OPERATIONS

CONTROL

INTERRUPT

INPUT/OUTPUT

### SECTION I SYSTEM CHARACTERISTICS

### INTRODUCTION

The SYSTEMS 86 is a 600-nanosecond cycle time, 32-bit general-purpose computer. It is available in a broad and continuous spectrum of configurations. At one end of the spectrum are processors with 8K (K=1024) words of memory and basic card or paper tape input/output devices. The system software supports these configurations with assembler, and basic operating systems. At the other end of the spectrum are processors having up to 128K words of memory. The highest level of system software supports these and intermediate size configurations.

The system hardware and software are designed, in particular, to respond to the expanding need for computers capable of performing substantial computational loads in real-time environments. The computational capability is designed in with a set of 152 basic instructions; direct addressing capability for any bit, byte, halfword, word, or doubleword in 128K words of memory; general-purpose registers; and high internal processing speeds. The real-time capability is designed into the input/output and interrupt systems and the instruction set which has an extensive group of logical, bit manipulation and control instructions. The two capabilities are combined in the multiprogramming software system which features fast external environment response, task scheduling, resource allocation; and multilanguage processing capabilities.

### SYSTEM STRUCTURE

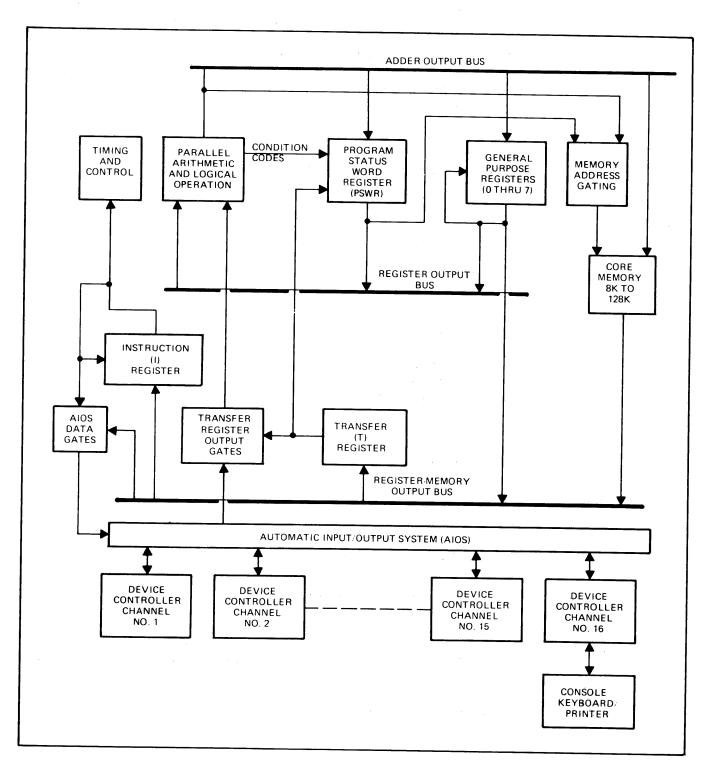

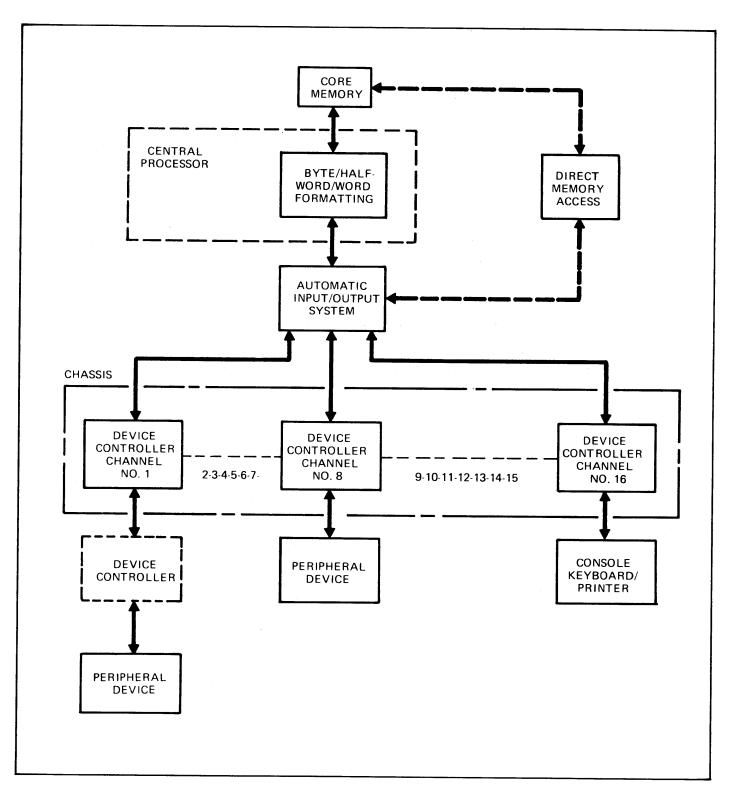

The principal components of the SYSTEMS 86 Computer are a Central Processor (CP), Core Memory, Automatic Input/Output System (AIOS), and Device Controller Channels (DCC's).

Table 1-1 lists the options offered with the SYSTEMS 86 Computer.

The internal organization of the Central Processors and the interconnections between them and other system components are shown in figure 1-1. The CP basically consists of registers; control, timing, and execution logic; and information transfer buses.

The eleven 32-bit registers in the CP consist of the eight general-purpose registers (R0 through R7), the Instruction Register, the Transfer Register, and the Program Status Word Register. The eight registers, R0 through R7, are general purpose in that the contents of any of these registers can be addressed and operated on by most instructions. For example, all arithmetic, logical, and shift instructions can use any of the general purpose registers. In addition to being general purpose, some of these registers are assigned a specific function, Register R0 is used as the Link Register, and registers R1, R2, and R3 are used as index registers. R4 is used for masking operations.

The Instruction Register stores the full word or two halfword instructions currently being executed. The Transfer Register stores operands acquired from memory during the execution phase of the instructions. The Program Status Word Register always contains the current Program Status Word, including the program count.

TABLE 1-1. SYSTEMS 86 COMPUTER AND OPTIONS

| Model Number | Description                                                                                                    |

|--------------|----------------------------------------------------------------------------------------------------------------|

| 8600         | Central Processor with the KSR-33 Console K/P and the highest Interrupt Module                                 |

| 8610         | Real Time Monitor features (system protect, privileged instruction execution, and common memory protect logic) |

| 8618         | Remote Control Console                                                                                         |

| 8619         | KSR-37 Console K/P instead of the standard KSR-33 Console K/P                                                  |

| 8620         | Floating Point Arithmetic Unit                                                                                 |

| 8630         | 8K x 36 Bit Memory Module with one port and byte parity                                                        |

| 8631         | 8K x 36 Bit Memory Module with one port, page protect and byte parity                                          |

| 8632         | 8K x 36 Bit Memory Module with two ports and byte parity                                                       |

| 8633         | 8K x 36 Bit Memory Module with two ports, page protect and byte parity                                         |

| 8634         | $8\mbox{K} \times 36\mbox{ Bit Memory Module with two ports, page protect, port protect and byte parity}$      |

| 8640         | Direct Memory Access                                                                                           |

| 8650         | Highest 6 External Interrupts                                                                                  |

| 8651         | External Interrupt Module, 16 levels                                                                           |

| 8670         | Interfaces for nine additional Device Controller Channels                                                      |

| 8671         | Interval Timer                                                                                                 |

Figure 1-1. SYSTEMS 86 Computer Block Diagram

The Timing and Control Section translates machine instructions into signals which control the flow of information over the buses and through the execution logic specified by each instruction. The Parallel Arithmetic and Logical Operation Section contains the adder and other execution logic for arithmetic and logical operations. It also contains the data formatting gates, which permit the reading from and writing into memory of bytes, halfwords, words, and doublewords. The execution logic for all arithmetic and logical instructions operates on all specified bits in parallel to expedite machine operation.

All data transfers are also performed in bit parallel format over the information buses. All paths over which instructions or operands are transferred are 32 bits wide. Some paths for peripheral device controller channels are eight bits and 16 bits wide.

# SYSTEM CHARACTERISTICS

Word Length - 32 bits

Cycle Time - 600 nanoseconds

Instruction Execution Times (microseconds)

|                                                     | 32 bit word                             | 64 bit doubleword                       |

|-----------------------------------------------------|-----------------------------------------|-----------------------------------------|

| Load, store                                         | 1.2                                     | 1.8                                     |

| Add, subtract fixed point floating point (optional) | 1.2<br>2.4 minimum<br>to<br>3.6 maximum | 1.8<br>3.0 minimum<br>to<br>4.8 maximum |

| Multiply fixed point floating point (optional)      | 6.6<br>6.6                              | n/a<br>11.4                             |

| Divide<br>fixed point<br>floating point (optional)  | 10.8<br>11.4                            | n/a<br>19.8                             |

Memory Size

The memory size can be 8,192 to 131,072 words, expandable by 8K word modules. (K = 1024)

Memory Addressing

Memory is addressable by bit, byte, halfword, word, and doubleword. All locations up to 128K words are directly addressable without requiring the use of base registers, index registers, or indirect addressing.

Memory Parity

A parity bit is stored with each eight-bit byte.

Indirect Addressing

Capability for multilevel indirect addressing is provided in all memory reference instructions. Both pre-indexing and post-indexing operations can be performed in conjunction with indirect addressing.

Immediate Addressing

Capability for immediate addressing of operands is provided to reduce execution time and storage requirements.

General Purpose Registers Eight addressable general purpose registers are provided.

Index Registers

Three of the eight general purpose registers can be used as index registers.

Index Formats

Memory addresses can be indexed by byte, halfword, word, or doubleword.

Instruction Set

A total of 47 halfword instructions (16-bit instruction length) and 105 word instructions (32-bit instruction length) are included in the SYSTEMS 86 Computer instruction set. The word instructions primarily reference bits, bytes, halfwords, words, or doublewords stored in memory. The halfword instructions primarily reference operands stored in registers. The halfword set, in particular, results in very efficient memory utilization due to the high percentage of instructions that can be stored two per location.

Register File Loading and Storing Load File and Store File instructions are provided to expedite context switching as well as computation. The contents of from one to eight registers can be transferred to or from memory by executing either of these instructions.

Bit Manipulation

A set of bit manipulation instructions is provided to enable individual bits in memory or a register to be tested and modified. In addition, the capability for direct evaluation of logical functions is provided.

Masking Operations

The result of many register-to-register arithmetic, logical, and transfer operations can be masked as part of the execution of the instruction. In addition, masking operations can be performed on operands transferred between memory and registers. These masking features result in outstanding data formatting and logical operation capabilities.

Call Monitor Instructions An instruction is provided to enable the currently active program to communicate readily with the system monitor.

Condition Code

A four-bit condition code is stored at the completion of the execution of instructions which modify operands. This code enables the result of operations to be tested quickly and conveniently.

Program Status Word This word contains the current value of all machine conditions which must be preserved prior to context switching. The current Program Status Word is automatically stored in memory each time a priority interrupt occurs, and is restored when the interrupt routine is exited.

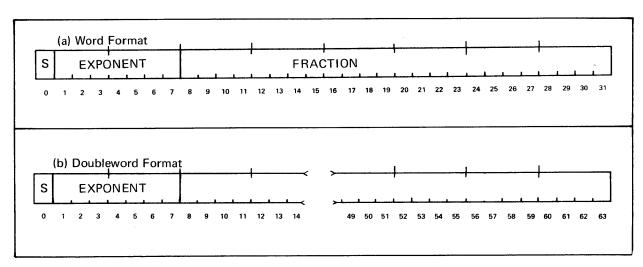

Floating Point Arithmetic The floating point hardware option enables the SYSTEMS 86 Computer to perform either word or doubleword floating-point add, subtract, multiply, and divide operations. The word format consists of a 24-bit fraction, plus sign and a seven-bit exponent. The first word of the doubleword format consists of the 31 most significant bits, plus sign, and the second word contains the 25 least significant bits of the fraction and the seven-bit exponent.

### Automatic Input/Output System

The basic input/output structure is designed to eliminate Central Processor delays caused by peripheral device response time. The Central Processor can initiate transfers of blocks of data for any combination of up to 16 Device Controller Channels and then proceed with internal operations while the transfers occur in a simultaneous, interleaved manner.

### Device Controller Channels

These input/output channels contain the controllers for peripheral devices as well as the required computer transfer logic. This enables high-speed command and data transfers between the computer and device controllers to be confined within the computer cabinet. The transfers between controllers and devices are performed independently of Central Processor operation. As a result, a minimum number of machine cycles is used for input/output operations.

### Direct Memory Access

This option enables the Automatic Input/Output System to be connected to a second memory port to permit input/output transfers to be performed without stealing program execution cycles.

### Priority Interrupts

The SYSTEMS 86 Computer is supplied with twelve levels of priority interrupts and traps. Minimum interrupt response time is achieved by making long instructions interruptable, providing for automatic storage of the current program status, and providing register file load and store instructions. The high degree of program control provided for handling of the interrupt system offers new capabilities to real-time system users and improves monitor performance.

#### Machine Traps

Extensive checking of both hardware and program operation is performed. Traps are generated when abnormal conditions occur.

### Multiprogramming Features

Hardware as well as software features are supplied with SYSTEMS 86 Computers which enable multiple programs to time-share computer operation. A privileged operation feature is available which includes both memory protection and privileged instruction trapping capabilities.

#### Real-Time Clock

SYSTEMS 86 Computers are supplied with a real-time clock. This clock is useful in all real-time system control and time allocation or accounting applications. In addition an interval timer is optionally available.

#### Power Fail-Safe

This standard feature prevents the contents of core memory from being modified by power turn-on or turn-off. An interrupt level is also supplied which enables machine status and volatile register contents to be preserved when power failure is detected and to be restored when power is again applied to the computer.

#### Control Panel

The SYSTEMS 86 Computer control panel is designed to facilitate manual machine control. It contains an automatic program load feature and an addressable program halt feature in addition to all necessary controls and displays for loading and displaying register or memory contents and performing all required machine control functions. An Optional Remote Control Console is also available.

### Keyboard/Printer

A choice of keyboard/printer is available. Either the Teletype Model 33 or 37 can be supplied.

### Real Time Monitor Features

The optional Real Time Monitor Features include System Protect, Memory Page Protect and Privileged Operation. System Protect consists of a console keyswitch which may be used to prevent manual intervention with computer operation. It also includes two special interrupt levels which override all other machine functions. One is connected to the power failure and restoration detection circuits. The other is connectable to an external controller or monitor such as a watchdog timer. Memory Page Protect causes the privilege violation trap to be generated if the Central Processor is operating in the unprivileged state, and attempts execution of an instruction which modifies the contents of any protected memory location. Privileged Operation provides safeguards against attempts by two or more programs to use the same computer resources.

### PHYSICAL CHARACTERISTICS

SYSTEMS 86 Computers are packaged in cabinets approximately 66 inches high, 51 inches wide, and 31 inches deep. A single cabinet can contain a Central Processor with an Automatic Input/Output System and up to 16 Device Controller Channels plus 8K to 32K words of memory. The memory may have one or two ports. Any combination of computer options including Direct Memory Access, and floating point arithmetic can be contained in the single cabinet. This packaging design enables SYSTEMS 86 Computers to be expanded readily at the customer's facility, since space is provided for all combinations of options.

### DATA FORMATS

USASCII eight-bit character coding (shown in the Appendix) is used as the internal character code by the SYSTEMS 86 software. Characters are stored in memory four per word in byte format.

All character-oriented peripheral devices, except card handling equipment, produce or accept USASCII-coded characters. Some devices, such as line printers, accept only truncated USASCII (six least significant bits of USASCII). The card equipment transfers eight-bit bytes. It operates either in the binary or code translate modes.

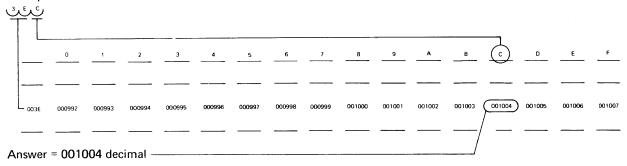

The basic hexadecimal numbering system and its binary and decimal equivalents are specified in table 1-2. The hexadecimal system has a base of 16. The first 10 digits are represented by decimal numbers zero through nine; the last six digits are represented by the letters A through F.

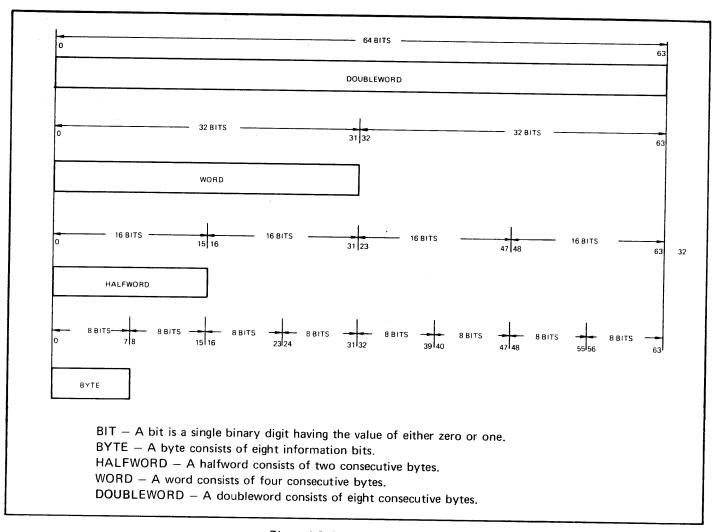

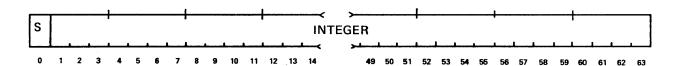

Figure 1-2 gives a functional description and format of the data organization used with SYSTEMS 86 Computers.

TABLE 1-2. BASIC HEXADECIMAL NUMBERING SYSTEM

| Hexadecimal<br>(Base 16) | Binary<br>(Base 2) | Decimal<br>(Base 10) | Hexadecimal<br>(Base 16) | Binary<br>(Base 2) | Decimal<br>(Base 10) |

|--------------------------|--------------------|----------------------|--------------------------|--------------------|----------------------|

| 0                        | 0000               | 0                    | 8                        | 1000               | 8                    |

| 1                        | 0001               | 1                    | 9                        | 1001               | 9                    |

| 2                        | 0010               | 2                    | А                        | 1010               | 10                   |

| 3                        | 0011               | 3                    | В                        | 1011               | 11                   |

| 4.                       | 0100               | 4                    | С                        | 1100               | 12                   |

| 5                        | 0101               | 5                    | D.                       | 1101               | 13                   |

| 6                        | 0110               | 6                    | E                        | 1110               | 14                   |

| 7                        | 0111               | 7                    | F                        | 1111               | 15                   |

Figure 1-2. Data Organization

#### SECTION II COMPUTER ORGANIZATION

### MEMORY ORGANIZATION

The SYSTEMS 86 Computer is a 32-bit, word-organized machine. All core memory cells as well as registers store 32 bits. A full word is always read from, or stored into, memory each time memory is accessed; however, memory is designed to permit replacement of a byte, halfword, or word in any addressed cell. A word can be read from a cell into the Memory Data Register and then partially replaced in the register by bits transferred from the Parallel Arithmetic and Logical Operation Section in the Central Processor. The modified word can then be stored back into the memory cell. The entire operation, which consists of read, selective replace, and restore, is performed in one memory cycle time.

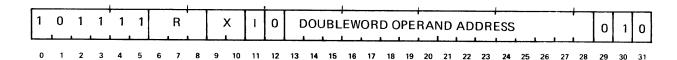

The definition of the position in memory for all the basic information formats is given in figure 2-1. Any of these units of information except the doubleword can be accessed by either the Central Processor or Automatic Input/Output System. Doublewords are accessible by the Central Processor as pairs of words that always start with an even memory location. The least significant bit of a doubleword address is actually forced to zero by the Central Processor. Therefore, an odd doubleword address contained in an instruction causes the same operand to be acquired as the next lower even address.

Information is transferred between memory and registers with the initial and final positioning shown in figure 2-2. All information transferred from memory to a register is right-justified in the register, and all information transferred from a register to a memory cell is assumed to be right-justified in the register. When doublewords are transferred, the contents of the specified even memory cell are always transferred to the specified even register (R0, R2, R4, or R6), and the contents of the odd cell are transferred to the next higher numbered odd register. The least significant bit of both the register address and the memory address is treated as zero.

### MEMORY ADDRESSING

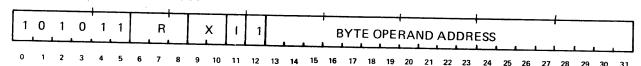

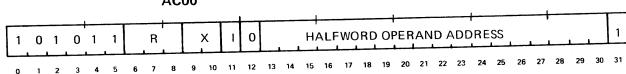

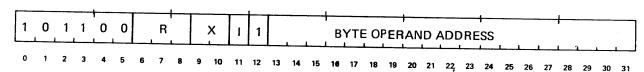

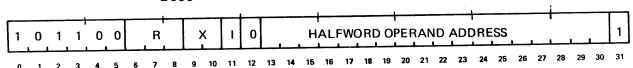

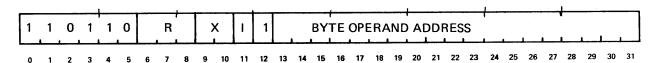

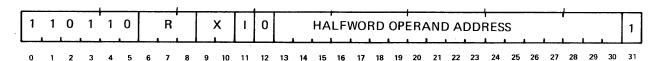

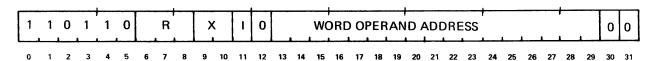

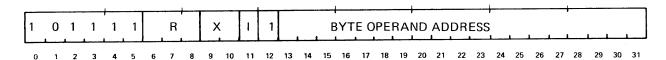

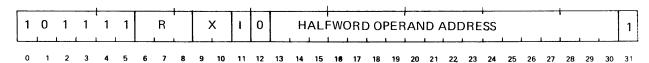

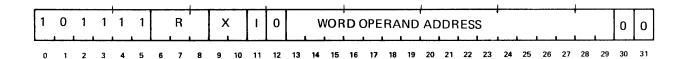

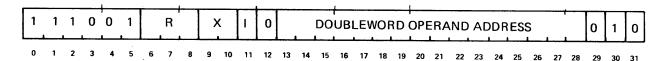

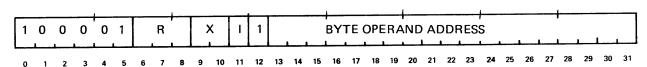

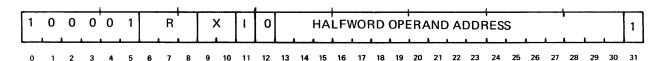

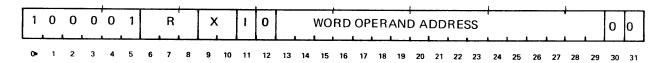

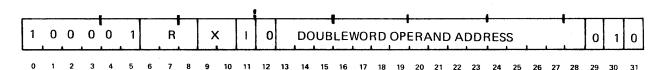

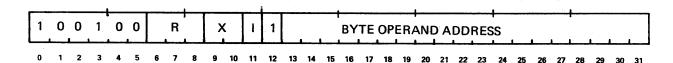

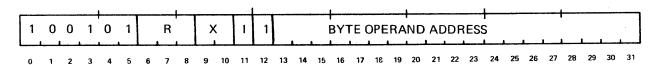

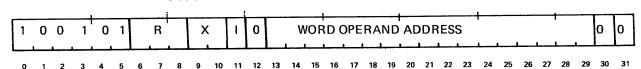

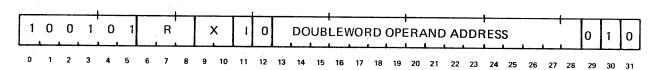

A 20-bit address is used to specify any byte, halfword, word, or doubleword in memory. The format and the bit positioning of this address are shown in figure 2-3.

This format enables all cells in memory to be addressed directly without use of any paging, sectorizing, mapping, or other address modification operations.

The coding of the F and C fields, which when combined are called the operand format code, is defined in table 2-1.

### EFFECTIVE ADDRESS

The effective address of the operand is derived from the value of bits 9 through 31 contained in the instruction. The format and bit position of the effective address is defined in figure 2-4.

### NO ADDRESS MODIFICATION

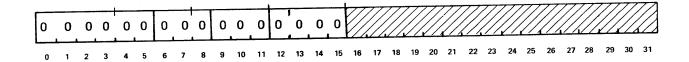

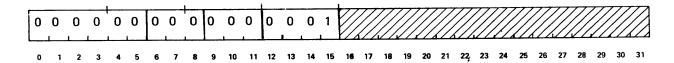

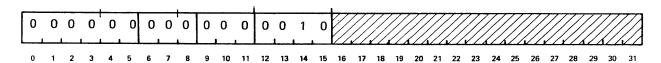

When X and I are equal to zero, the effective address is defined by bits 12 through 31. Any byte, halfword, word, or doubleword in memory can be specified.

Figure 2-1. Information Boundaries in Memory

Figure 2-2. Positioning of Information Transferred Between Memory and Registers

Figure 2-3. Memory Address Format

Figure 2-4. Effective Address Format

TABLE 2-1. OPERAND FORMAT CODE

| F | С   | Designated Format |

|---|-----|-------------------|

| 0 | 0 0 | Word              |

| 0 | 0 1 | Left Halfword     |

| 0 | 1 0 | Doubleword        |

| 0 | 1 1 | Right Halfword    |

| 1 | 0 0 | Byte 0            |

| 1 | 0 1 | Byte 1            |

| 1 | 1 0 | Byte 2            |

| 1 | 1 1 | Byte 3            |

#### **INDEXING**

When X is not equal to zero and I is equal to zero, the effective address is formed by adding the contents of bit positions 13 through 31 of the specified index register to the corresponding bit positions of the address contained in the instruction.

The index register is assumed to contain a 32-bit positive or negative displacement value. This displacement value may be any integral number of bytes, halfwords, words, or doublewords which, when added to the address contained in the instruction, produces a resulting address within the memory boundaries of the machine. If the addition produces a resulting address larger than the memory boundaries of the machine, a non-present memory trap is generated. The bit position corresponding to the displacement value for each type of operand format is given below:

| Format     | Bit Position |

|------------|--------------|

| Byte       | 31           |

| Halfword   | 30           |

| Word       | 29           |

| Doubleword | 28           |

The instruction that increments the contents of the index register is capable of specifying which of these four bits is to be incremented. Therefore, indexing operations can be performed with any of the defined operand formats. The address format code is designed such that indexing operations, as defined, do not change the specified format for the operand. For example, when a sequence of bytes is accessed by successive indexing operations, incrementing bit 31 of the index count causes bytes to be accessed in the sequence — Byte 0, Byte 1, Byte 2, Byte 3, Byte 0—, where the second Byte 0 indicated in the sequence is accessed from the next higher word location in memory than the first.

### INDIRECT ADDRESSING

When X equals zero and I equals one, the value of the Word Address (WA) is interpreted as the address of the address of the operand. The contents of the location specified by the WA are accessed to obtain the address of the operand. This accessing of an indirect address word adds one cycle time to instruction execution time. The format for an indirect address word is defined in figure 2-5. As seen in the figure, the

Figure 2-5. Indirect Address Format

indirect address format is the same as the memory reference instruction format in bit positions 9 through 31. The values of bits 0 through 8 are ignored in indirect addressing operations to permit instruction words to be used as indirect address words for other instructions.

Presence of the X and I fields in the indirect address format permits multilevel indirect addressing plus indexing at any level desired.

The address modification logic is designed to permit the operand format to be specified at any indirect address level. The rule for format code specification in indirect address levels is as follows:

Format Code Specification Rule — The effective operand format code in each indirect address level replaces the format code from the previous level, provided that the format code is not equal to zero in the new level. If the format code is equal to zero at any indirect address level, the value from the previous level is retained. The effective value of C at any level is the value resulting after any specified indexing operation is performed. The value of F is not modified by indexing operations.

The result of providing the above-described flexibility in operand format specification is that, in instructions such as Load and Store, the operand format can be specified in the instruction word, and in other instructions such as an Indirect Branch, the format (left or right instruction) can be specified in the final indirect address level. In addition, indirect address words containing the wrong format code can be used, provided the correct nonzero format code is specified in a later indirect level.

COMBINED INDEXING AND INDIRECT ADDRESSING

When X is not equal to zero and I is equal to one, both indexing and indirect addressing operations are performed. Indexing is performed first, which means that the indirect address is obtained from the cell specified by the sum of the address contained in the instruction word and the value stored in the specified index register. If post-indexing rather than pre-indexing is desired, the value of X=0 is placed in the instruction word and the value of X=1, 2, or 3 (as desired) is placed in the indirect address word. This flexible indexing scheme enables any one, two, or three-dimensional indexing operation desired to be performed.

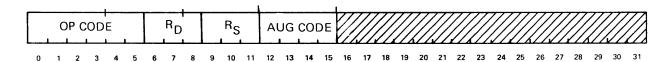

INSTRUCTION FORMATS

The SYSTEMS 86 instruction set contains both halfword and word instructions. The general distinction between these two types of instructions is that word instructions either contain operands or reference operands stored in memory, and halfword instructions only reference operands stored in registers. The principal classes of formats for both word and halfword instructions are described individually.

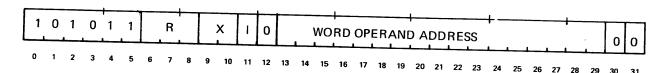

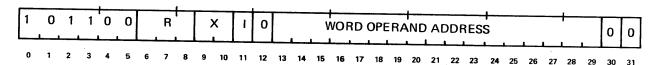

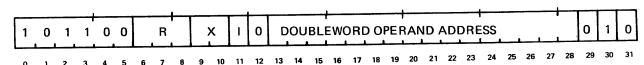

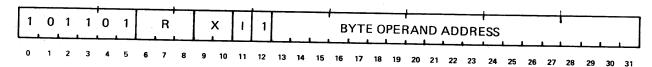

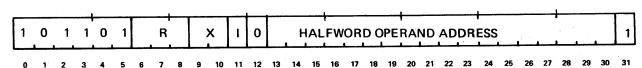

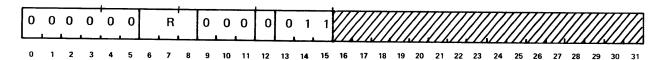

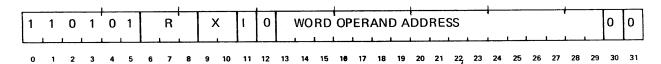

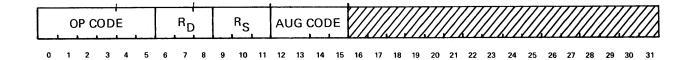

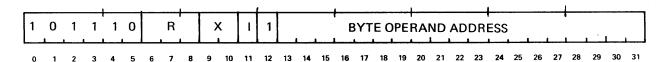

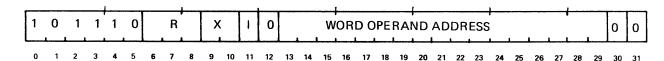

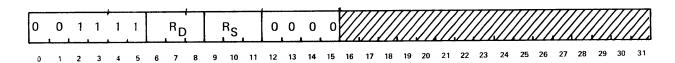

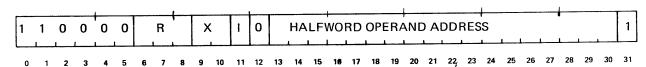

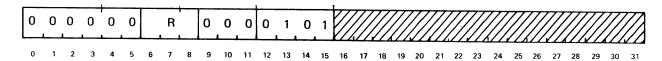

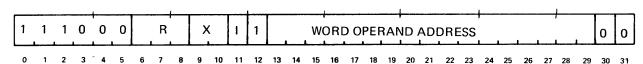

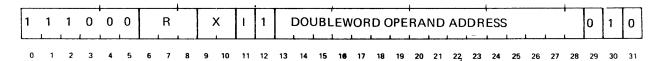

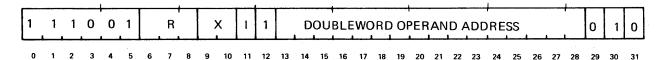

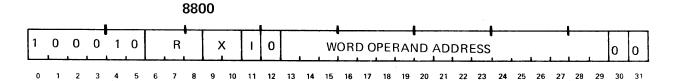

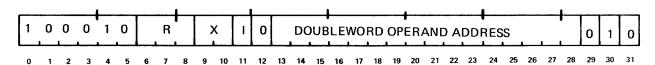

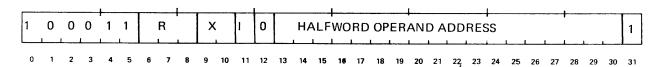

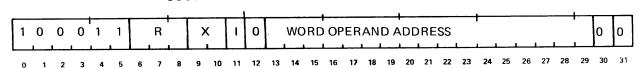

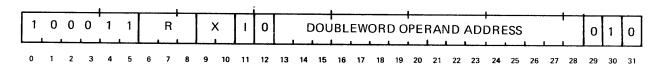

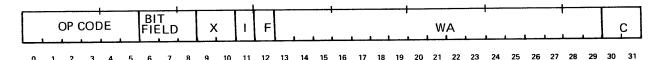

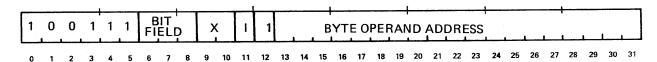

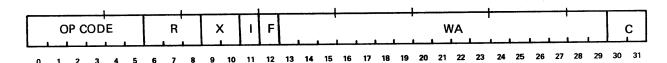

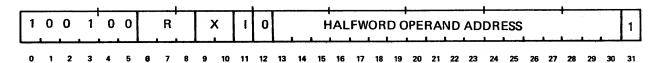

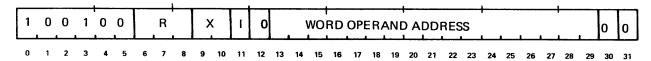

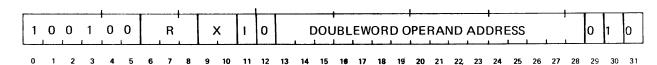

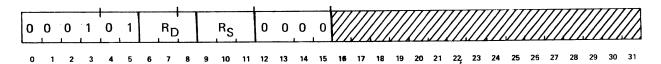

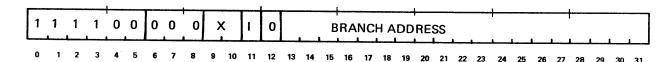

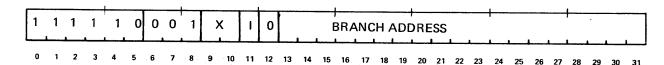

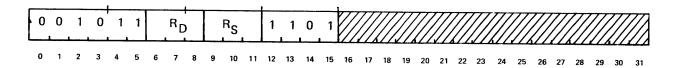

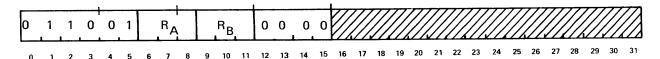

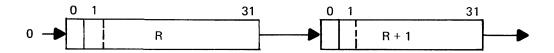

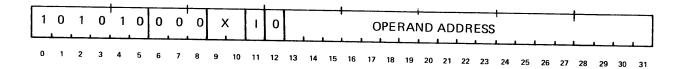

MEMORY REFERENCE INSTRUCTIONS The format for most memory reference instructions is defined in figure 2-6. These instructions contain two addresses: a register address R, and a memory address having the 20-bit format previously described.

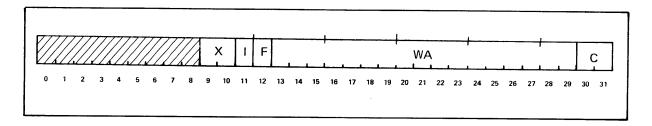

Figure 2-6. Memory Reference Instruction Format

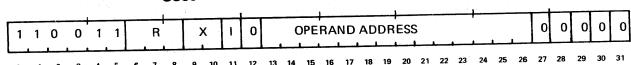

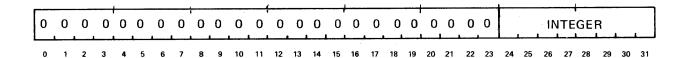

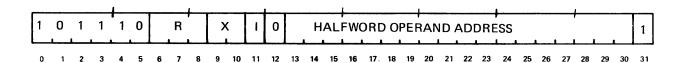

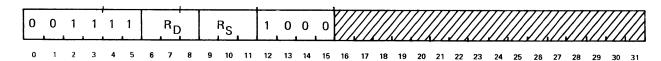

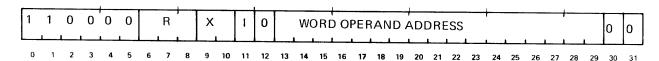

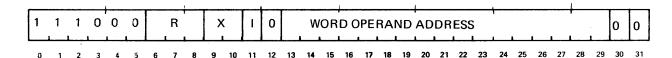

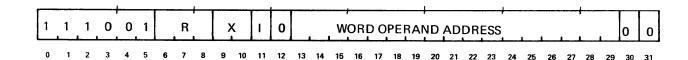

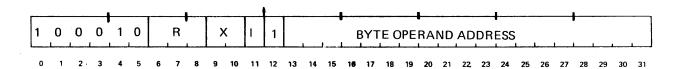

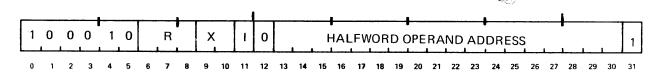

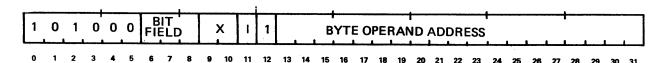

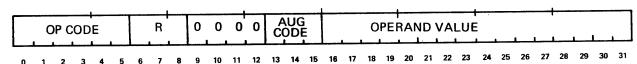

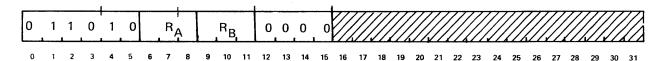

IMMEDIATE OPERAND INSTRUCTIONS

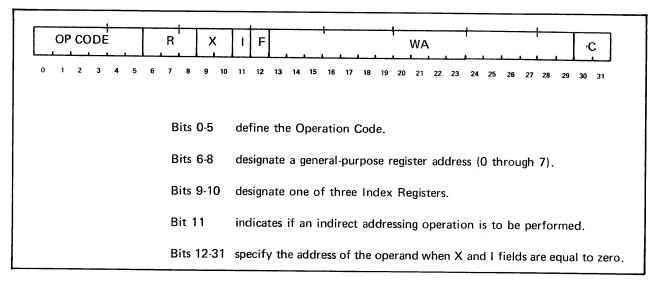

In immediate operand instructions, the right halfword of the instruction contains the 16-bit operand, rather than the address of the operand. The format for these instructions is given in figure 2-7.

Figure 2-7. Immediate Instruction Format

Arithmetic operands are assumed to be represented in the two's complement format, with the sign specified in bit 16. The sign is automatically extended to the left to convert the halfword operand into a fullword operand prior to performing arithmetic operations.

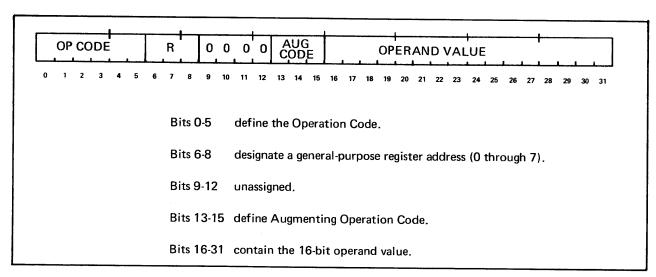

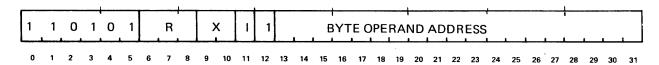

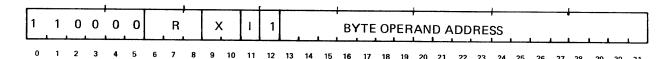

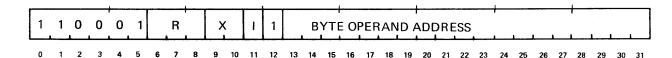

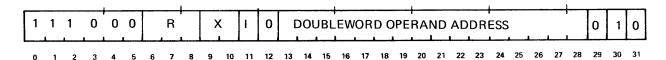

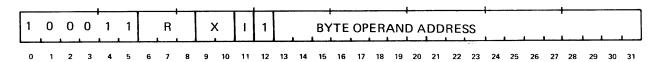

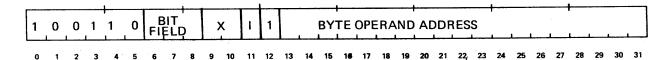

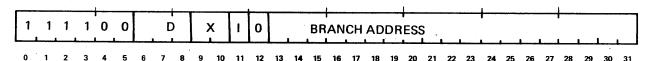

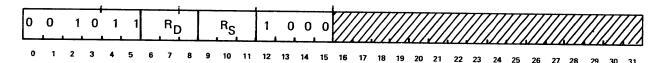

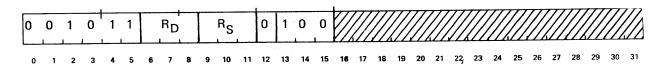

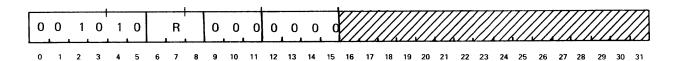

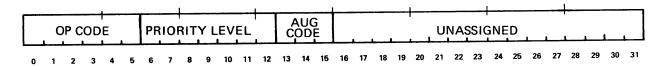

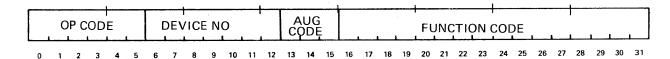

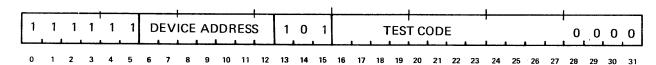

### INPUT/OUTPUT INSTRUCTIONS

The format for input/output instructions is given in figure 2-8. Input/output instructions include peripheral device command and test instructions. Both types of these instructions cause a 16-bit function code, contained in the instruction right halfword, to be sent to a device controller. The device number is specified within the instruction format as shown.

Figure 2-8. Input/Output Instruction Format

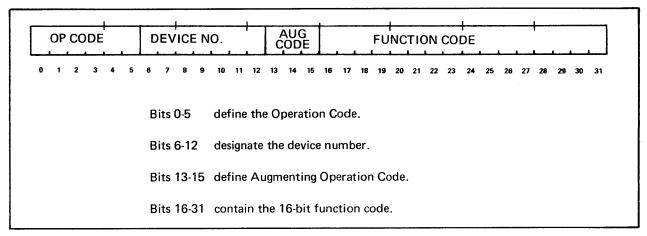

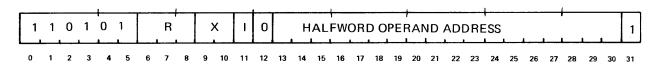

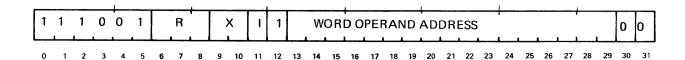

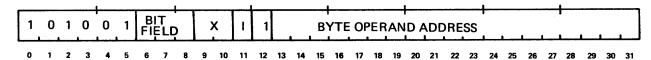

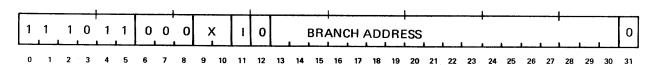

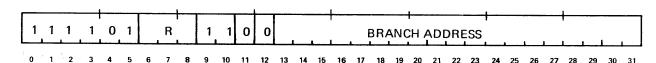

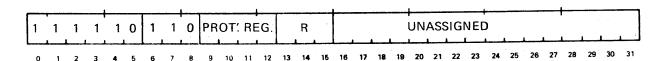

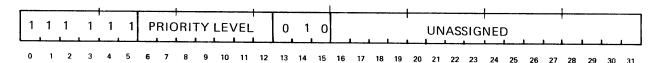

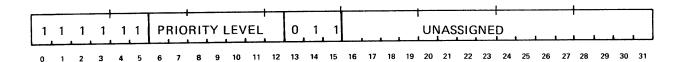

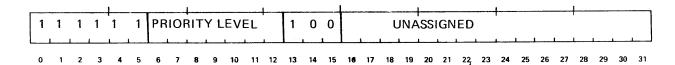

### INTERRUPT CONTROL INSTRUCTIONS

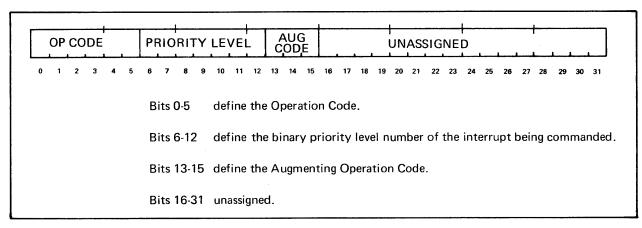

Interrupt control instructions permit selective enable, disable, and other control operations to be performed on any addressed interrupt level. The binary priority level number is specified in bits 6 through 12 of the instruction which specifies that the corresponding level is to be operated on by the instruction (for example, enabled). The instruction format is shown in figure 2-9.

Figure 2-9. Interrupt Control Instruction Format

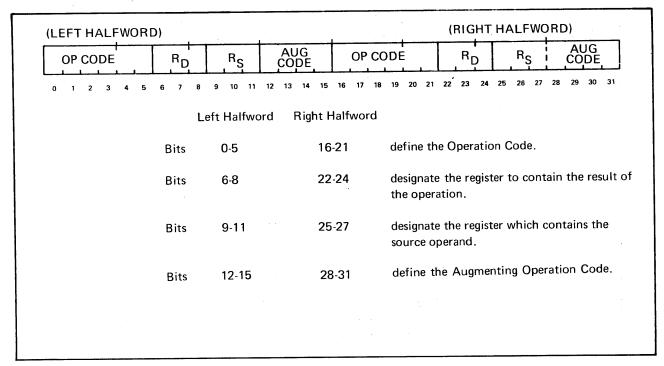

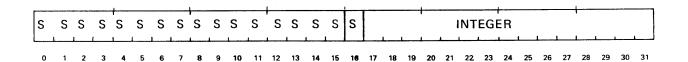

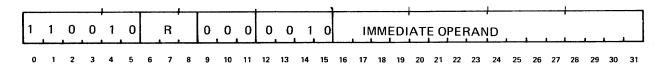

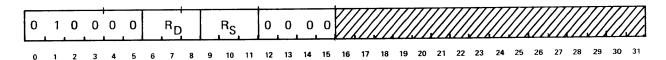

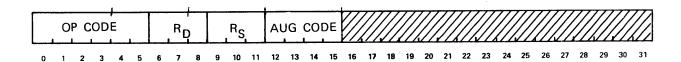

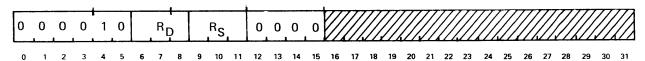

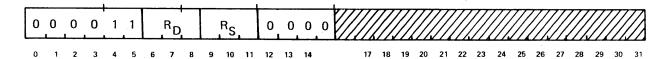

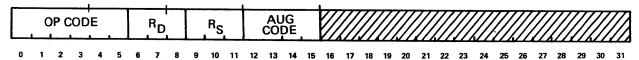

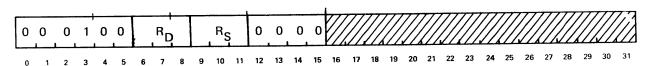

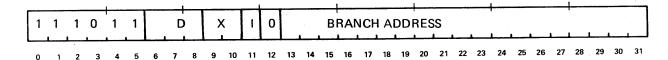

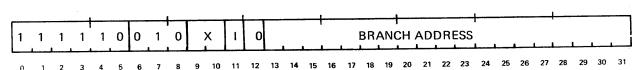

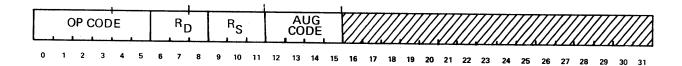

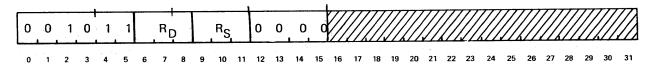

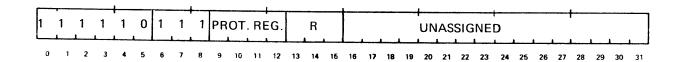

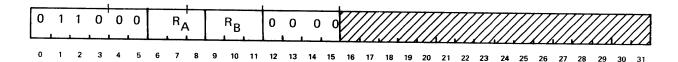

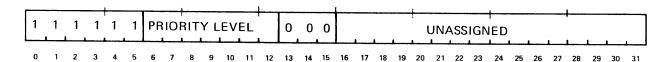

### INTER-REGISTER INSTRUCTIONS

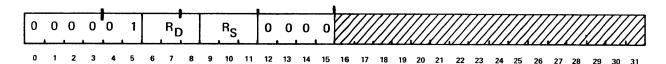

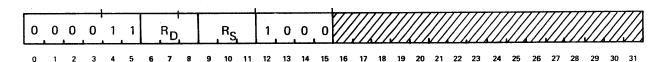

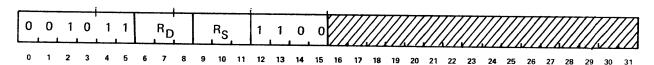

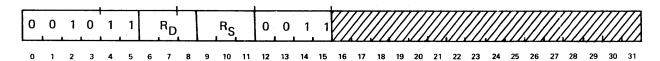

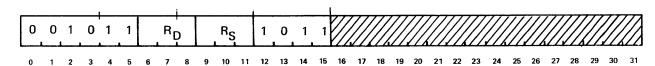

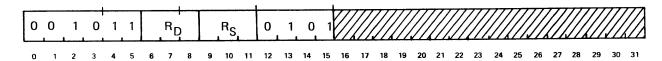

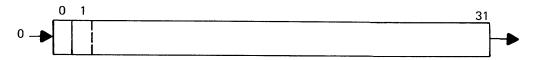

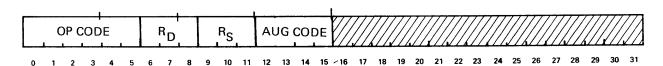

These halfword instructions provide the capability for manipulating operands stored in general purpose registers R0 through R7. The format for these instructions is shown in figure 2-10.

Figure 2-10. Inter-Register Instruction Format

Many inter-register instructions mask the result of the operation prior to storage in the destination register ( $R_D$ ). When the instruction specifies masking, the result is masked by the contents of the mask register so that zeros will be stored in the destination register in the positions corresponding to the zeros in the mask register. A one bit will be stored in the destination register for each bit position that has a corresponding one in the result and mask register.

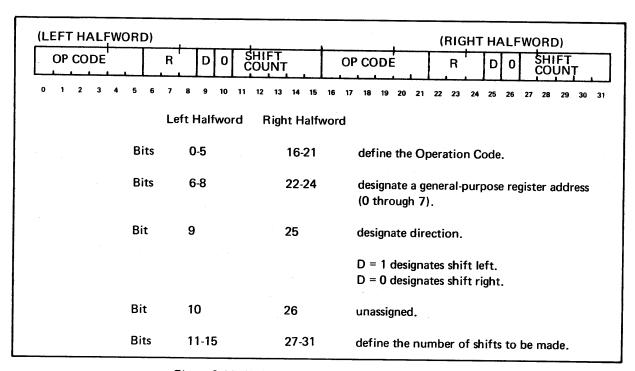

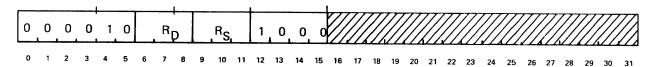

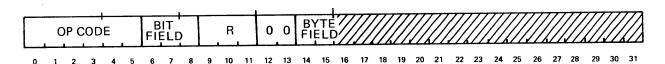

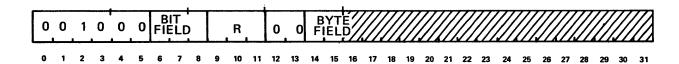

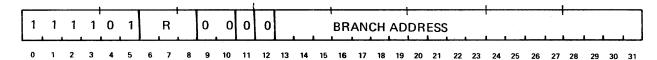

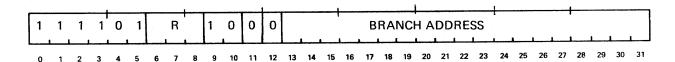

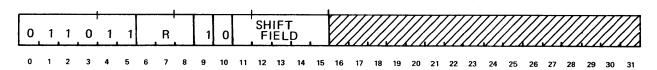

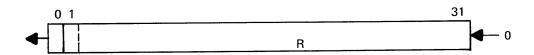

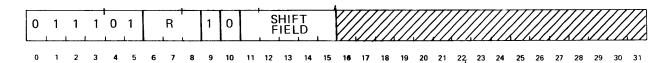

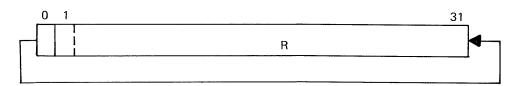

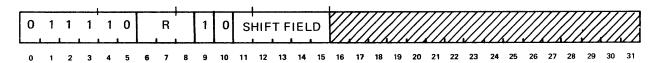

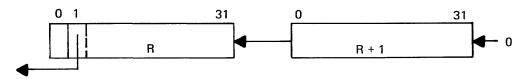

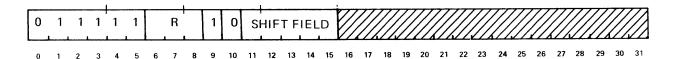

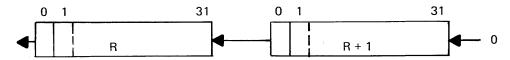

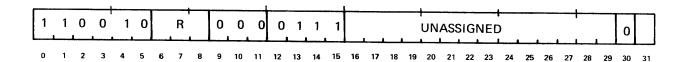

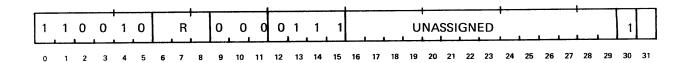

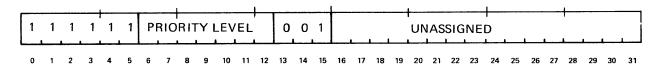

### SHIFT INSTRUCTIONS

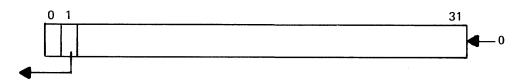

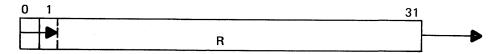

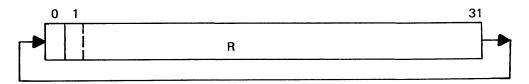

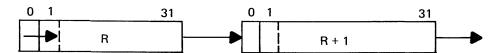

Shift instructions contain a register address, shift count, and shift direction bit, as shown in figure 2-11. In double register shift instructions, the R address specifies an even-odd pair, with the even register always on the left as in all other double register operations.

### OPERAND FORMATS

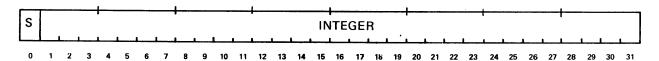

### Fixed-Point Arithmetic Operands

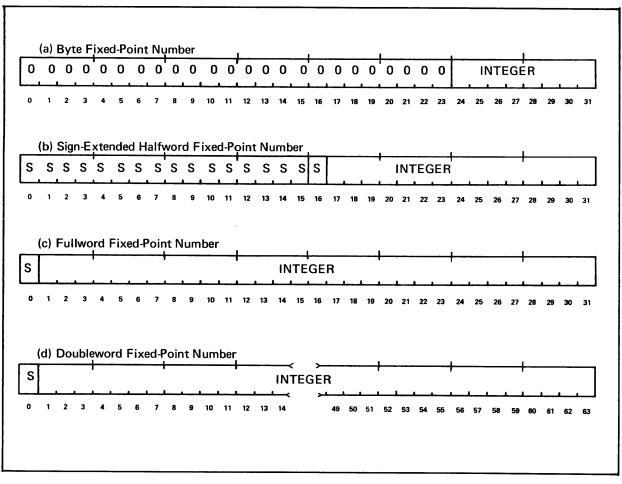

Fixed-point numbers are represented by a sign bit followed by a binary-coded integer. Negative numbers are represented in the two's complement format. Arithmetic operations are performed on bytes and halfwords after these operands are right justified and converted into words. Byte conversion is accomplished by the appending of 24 leading zeros, and halfword conversion consists of extending the halfword sign bit 16 positions to the left. Arithmetic operations are performed on words and doublewords in the format stored in memory, as shown in figure 2-12.

Figure 2-11. Shift Instruction Format

The range of numbers which can be represented in the two's complement format is:

| + Full Scale - 1 | 011 11 |

|------------------|--------|

| Zero             | 000 00 |

| Full Scale       | 100 00 |

Where Full Scale equals  $2^{31}$  for fullword operands. The negative Full Scale value requires special treatment because it is the only number, other than zero, that does not change sign when complemented.

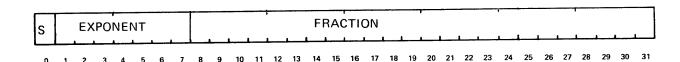

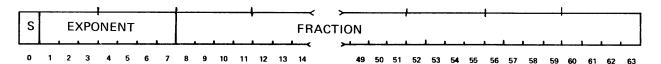

Floating-Point Arithmetic Operands

The formats for floating-point operands are shown in figure 2-13. Both the word and the doubleword formats consist of a signed fraction and a seven-bit, base 16 exponent. The exponent is weighted as shown on page 2-12. A negative number is represented as the two's complement of its absolute value, so that the execution of the compare and negate operations is valid with fixed-point or floating-point operands. The letter H indicates hexadecimal number representation.

Figure 2-12. Arithmetic Operation Formats for Fixed-Point Numbers

Figure 2-13. Floating-Point Formats

| Exponent Value (H) | Weight            |

|--------------------|-------------------|

| <b>7</b> F         | 16 <sup>63</sup>  |

| 40                 | 16 <sup>0</sup>   |

| 00                 | 16 <sup>-64</sup> |

The resulting magnitude of the range of numbers N that can be represented by the floating-point format is shown below.

/F/ is the magnitude of the fraction contained in the format. [(/F/16<sup>-64</sup>  $\leq$  /N/  $\leq$  /F/16<sup>63</sup>) the number is equal to or greater than F times 16<sup>-64</sup> or equal to or less than F times 16<sup>63</sup>]. The range of /F/ provided in the normalized word format is [(2<sup>-4</sup>  $\leq$  /F/  $\leq$  (1-2<sup>-24</sup>) the magnitude is equal to or greater than 2<sup>-4</sup> or equal to or less than 1 minus 2<sup>-24</sup>].

And in the doubleword format is  $[(2^{-4} \le /F)] \le (1-2^{-56})$  the magnitude is equal to or greater than  $2^{-4}$  or equal to or less than 1 minus  $2^{-56}$ ].

### Condition Code

A four-bit condition code is stored at the completion of the execution cycle of most instructions. This code contains the information regarding the result of the operation for which tests are most often made. The meaning of the condition code bits after the execution of arithmetic and many other instructions is defined in table 2-2.

The specific meanings of the condition code bits are defined in Section V with each instruction description. In addition to having a condition code stored automatically at the end of the execution cycle of most instructions, a group of compare instructions is provided that enables two operands to be compared in a variety of ways without

**TABLE 2-2. CONDITION CODE DEFINITIONS**

| Condition Code | Bit Position | Meaning               |

|----------------|--------------|-----------------------|

| CC1            | 1000         | Arithmetic exception  |

| CC2            | 0100         | Result greater than 0 |

| ссз            | 0010         | Result less than 0    |

| CC4            | 0001         | Result equals 0       |

modification of the stored operands. The result of the comparison is stored as the current condition code. A peripheral device test instruction is also provided that causes a condition code to be stored, which is the response of the device to the execution of the test instruction.

Three instructions, Branch Condition True, Branch Condition False, and Branch Function True, enable the condition code to be tested for any of the 16 possible states. The Branch Function True instruction also provides a means of evaluating any logical function having up to four independent variables.

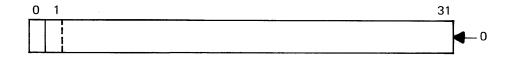

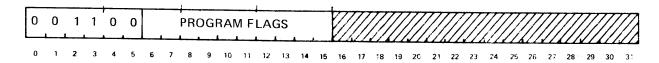

Program Status Word The Program Status Word (PSW) contains all machine conditions that must be preserved prior to context switching. The format of the PSW is shown in figure 2-14.

Figure 2-14. Program Status Word Format

Execution of any Branch or Branch-and-Link instruction replaces the contents of bit positions 13 through 30 of the PSW Register with the effective address specified by the instruction. In addition, if the Branch instruction contains an indirect address bit (bit 11), the contents of bits 1 through 8 are also replaced by the contents of the corresponding bit positions in the indirect address location.

The PSW is automatically stored in the Link register (R0) each time a Branch-and-Link instruction is executed. An instruction is provided to enable a new PSW to be established by transferring the contents of any register to the PSW register.

#### **ERROR CHECKING**

### Memory Parity

A separate parity bit is stored in memory with each byte. This permits selective replacement of individual bytes in memory with no added time penalty. Each time a word is read from memory, the parity of all four bytes is checked.

There are two basic categories of memory parity errors: (1) those that can occur during input/output transfers and (2) those that can occur on instruction fetch, indirect calls in the process of fetching an operand, fetching the operand itself, or fetching a dedicated interrupt location.

If a parity error occurs during an I/O transfer, a testable condition is set in the associated Device Controller Channel to indicate the parity error occurrence, but no parity error trap is generated in the Central Processor.

If a parity error is detected during the operations outlined in the second category, the instruction execution is terminated before any register, memory location, or machine status is changed (except a parity error detected in the operand of an indirect call initiated by a Load Byte, Load Halfword, Load Word, or Load Doubleword instruction). In this case, the operand is loaded into the specified register regardless of the parity error. When the instruction execution is terminated, the parity error trap processing routine is entered, provided that the trap level is enabled and no higher priority routine is being processed. If the trap level is not enabled, or a higher priority interrupt routine is being processed, the trapped instruction is treated as a No Operation instruction and the priority interrupt assigned to the trap is not requested; however, an error indicator is lighted.

The timing of any terminated instruction is one cycle if the parity error is located in the instruction word. If the error is contained in an indirect call, the timing is two cycles plus the number of cycles of indirect calls successfully completed before the indirect call containing the parity error. If the parity error is contained in the operand, the timing is that specified for the instruction.

### UNDEFINED INSTRUCTION

If execution of an undefined or nonpresent optional operation code is attempted, the instruction execution is terminated before any register, memory location, or machine status is changed. The trap processing routine is entered provided the trap level is enabled and no higher priority routine is being processed. If the trap level is not enabled, or a higher priority interrupt routine is being executed, the trapped instruction is treated as a No Operation instruction and the priority interrupt assigned to the trap is not requested.

### NON-PRESENT MEMORY ADDRESSING

When non-present memory is addressed by the Central Processor, the instruction execution is terminated before any register, memory location, or machine status is changed. The trap processing routine is entered provided the trap level is enabled and no higher

priority routine is being processed. If the trap level is not enabled, or a higher priority interrupt routine is being executed, the trapped instruction is treated as a No Operation instruction and the priority interrupt assigned to the trap is not requested. In Multiprocessor applications, the nonpresent memory trap occurs when a Central Processor addresses a memory module in which its port access bits are set to 00.

When a Device Control Channel addresses nonpresent memory, the Illegal Memory Access test condition is set in the Device Control Channel.

### ARITHMETIC EXCEPTION

An Arithmetic Exception occurs whenever the result of an arithmetic operation exceeds the word length of the machine. In all floating point operations, Arithmetic Exceptions occur whenever the value of the exponent of the result cannot be contained in the seven-bit exponent field.

An Arithmetic Exception is detected during a fixed-point add operation if the register and memory signs are the same but the sum sign is different. During a fixed-point subtract, it is detected if register and memory signs are different and the register and difference signs are different. An Arithmetic Exception cannot occur in a fixed-point Multiply Instruction. However, it is detected after a Divide Instruction, if the quotient cannot be represented as a 32-bit integer. In left shift arithmetic operations, an Arithmetic Exception occurs if the sign and most significant bit differs; then one or more additional shifts are performed. When a negate (two's complement) operation is performed, an Arithmetic Exception is detected if the operand equals minus full scale.

In all cases, the presence of an Arithmetic Exception causes the Condition Code bit CC1 to be set, and the Arithmetic Exception interrupt request signal to be generated.

## PRIVILEGE VIOLATION

If a privilege violation occurs, the instruction execution is aborted before the contents of any register, memory location, or machine status is changed. The trap processing routine is entered provided the trap level is enabled and no higher priority routine is being processed. If the trap level is not enabled, or a higher priority interrupt is being executed, the trapped instruction is treated as a No Operation and the priority interrupt assigned to the trap is not requested.

# CENTRAL PROCESSOR OPTIONS

### Teletype KSR-37

A Teletype model KSR-37 is offered as an optional replacement for the KSR-33. The KSR-37 operates at data input/output rates of up to 15 characters per second, and is provided for applications of high performance and continuous operation.

### Remote Control Console

The Remote Control Console option provides for mounting the Computer Control Panel on a convenient desk type console. This console also acts as a stand for the teletype. Both KSR-33 and KSR-37 teletypes can be used with the Remote Control Console.

### Interval Timer

The Interval Timer option includes a high resolution clock and a 32 bit register for counting machine cycles. The 32 bit register is under program control and may be loaded from memory or transferred to memory. A down count to zero in this register results in interrupt.

### Floating Point Hardware

When this option is present, the computer is capable of executing the floating point instruction set:

Add Floating-Point Word

Add Floating-Point Doubleword

Subtract Floating-Point Word

Subtract Floating-Point Doubleword

Multiply Floating-Point Word

Multiply Floating-Point Doubleword

Divide Floating-Point Word

Divide Floating-Point Doubleword

The execution of these instructions is described in Section V. The floating-point word and doubleword formats used are shown in figure 2-13.

### System Protect Feature

The system protect feature provides a maximum degree of assurance that the system will continue to operate regardless of external conditions or partial system failure. It consists of three elements: power fail-safe/auto start interrupt, system override interrupt and a console keylock switch. The power fail-safe/auto start feature causes an interrupt/trap (see interrupts description) to be generated each time the ac power is turned on or off. This interrupt can be used to save the machine status in the non-volatile core memory when power fails and to restart the program at the same, or perhaps some recovery, position when power is reapplied.

The system override interrupt can be connected to a second Central Processor in the system, or to a program controlled watchdog timer external to the system. If the program ever fails to reset the timer before the countdown interval elapses, the override interrupt signal can be used to restart program execution at a preassigned location. This feature can also be used to enable one Central Processor to control other Central Processors, or to enable the system to recover from "hangups" caused by either program or hardware problems.

A console keylock is included with the System Protect feature to provide a means of disabling the computer control switches. This three-position switch has the positions of "OFF," "Interrupts Enabled," and "Console Disabled." In the "OFF" position the computer operates as if the protect feature were absent. In the center position the two System Protect interrupts are enabled as are the console switches. In the third position the interrupts remain enabled and the console is disabled.

# Privileged Operation Feature

This optional feature provides safeguards against attempts by two or more programs to use the same computer resources. The Central Processor can be switched to operate in the "Privileged," "Semi-Privileged," or "Unprivileged" state and thereby have different degrees of control of computer memory and input/output resources. Two features are provided for limiting resource control. These are the capability to trap the execution of privileged instructions and to protect memory areas from unauthorized modification.

### Instruction Trap

This feature causes the privilege violation trap to be generated if the Central Processor is operating in the unprivileged state, and attempts execution of any of the privileged instruction set defined in table 2-3. If execution of a privileged instruction is attempted, it is aborted before any changes are made in memory content or machine status, and the privilege violation trap is generated.

**TABLE 2-3. PRIVILEGED INSTRUCTION SET**

| Enable Interrupt Disable Interrupt Request Interrupt Activate Interrupt Deactivate Interrupt | Transfer Register to Protect Register Branch and Reset Interrupt Command Device Halt Test Device |  |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

### Memory Page Protect

This feature causes the privilege violation trap to be generated if the Central Processor is operating in the unprivileged state, and attempts execution of an instruction which modifies the contents of any protected memory location. The Central Processor can continue to read and execute the contents of all memory locations, provided no instruction attempts to modify the contents of a protected location.

The memory protect quantum is a 512-word page. A sixteen-bit register associated with each 8K memory module stores the protect status of each of the sixteen pages in the module. Therefore, any combination of memory pages can be protected in each memory module. Instructions are provided to modify the contents of the protect registers.

Table 2-4 defines the protect bit positions and the corresponding memory areas protected.

TABLE 2-4. MEMORY PROTECT PAGE DESIGNATIONS

| Computer Bit<br>Designation | Page<br>Number | Memory Page (512 Words)<br>Protected (1st Module) <sub>H</sub> |  |  |

|-----------------------------|----------------|----------------------------------------------------------------|--|--|

| 31                          | 0              | 0-7FC                                                          |  |  |

| 30                          | 1              | 800-FFC                                                        |  |  |

| 29                          | 2              | 1000-17FC                                                      |  |  |

| 28                          | 3              | 1800-1FFC                                                      |  |  |

| 27                          | 4              | 2000-27FC                                                      |  |  |

| 26                          | 5              | 2800-2FFC                                                      |  |  |

| 25                          | 6              | 3000-C400                                                      |  |  |

| 24                          | 7              | 3800-3FFC                                                      |  |  |

| 23                          | 8              | 4000-47FC                                                      |  |  |

| 22                          | 9              | 4800-4FFC                                                      |  |  |

| 21                          | 10             | 5000-57FC                                                      |  |  |

| 20                          | 11             | 5800-5FFC                                                      |  |  |

| 19                          | 12             | 6000-67FC                                                      |  |  |

| 18                          | 13             | 6800-6FFC                                                      |  |  |

| 17                          | 14             | 7000-77FC                                                      |  |  |

| 16                          | 15             | 7800-7FFC                                                      |  |  |

Input/output transfers are not affected by the memory protect status or the Central Processor operating state. Since all I/O instructions are privileged, I/O transfers can only be initiated by programs which are executed when the processor is operating in the privileged state. However, it is often desirable to switch state from privileged to unprivileged during the time of completion of an I/O block transfer. Therefore, I/O transfers are performed independently of the operation of the privileged operation feature.

Table 2-5 summarizes the degree of resource control available to the Central Processor when operating in each of the privileged states.

The Central Processor state is initially set by the operation of a three-position keyswitch on the processor control panel. Any time this switch is operated from any position, the state is set to privileged. Operation continues in the privileged state until the first instruction is fetched from an unprotected memory location. Before this instruction is executed, the Central Processor is placed in the state corresponding to the current keyswitch position. The three positions are privileged, privileged and semi-privileged, unprivileged. The Central Processor continues operating in the new state until the

TABLE 2-5. PRIVILEGED OPERATING FEATURE STATES

| State Executable Instructions                |                   | Permissible<br>Memory<br>Operations                         | Trapped<br>Operations        |  |

|----------------------------------------------|-------------------|-------------------------------------------------------------|------------------------------|--|

| Privileged                                   | All               | Read, Write None Execute Contents                           |                              |  |

| Semi-<br>Privileged                          | All Except<br>TRP | Read, Execute<br>Contents                                   | Write in Protected Page, TRP |  |

| Unprivileged All Except<br>Privileged<br>Set |                   | Read, Execute Contents  Page, Execute Privileged Institions |                              |  |

keyswitch is operated again, or any interrupt other than a transfer interrupt occurs. When an interrupt occurs, the Central Processor is automatically switched to the privileged state. The current state is preserved in the Program Status Word, which is stored in memory each time an interrupt is processed. Execution of the Branch and Reset Interrupt (indirect) instruction used to exit from the interrupt routine automatically restores the Central Processor state present at the time the interrupt routine processing began.

### Multiport Memory Protect

Multiport Memory Protect enables the access of memory modules to be restricted to either the Central Processor or Direct Memory Access unit in systems having both of these units. Since each of these units is connected to memory via one memory port, the protection feature is actually made to operate on a memory port basis.

With this feature, the protect register associated with each memory module is extended in size from sixteen to twenty-four bits, as shown in table 2-6.

TABLE 2-6. MULTIPORT MEMORY PROTECT REGISTER BIT DESIGNATIONS

| Bits  | Function                    |  |

|-------|-----------------------------|--|

| 0-7   | Unused                      |  |

| 8-9   | Port 1 access control (DMA) |  |

| 10-11 | Port 2 access control (CP)  |  |

| 12-15 | Unused                      |  |

| 16-31 | Page Protect Control        |  |

Two access control bits per port are used to permit four levels of access, as defined in table 2-7.

TABLE 2-7. MULTIPORT MEMORY ACCESS CONTROL BIT DEFINITIONS

| Access Bits | Permissible CP Operations                              |                             |                     |                                                           | Permissible DMA Operations |                                    |

|-------------|--------------------------------------------------------|-----------------------------|---------------------|-----------------------------------------------------------|----------------------------|------------------------------------|

|             | Execute TRP<br>Instruction?                            | Execute TPR<br>Instruction? | Read and Execute?   | Write?                                                    | Read?                      | Write?                             |

| 00          | Yes, transfers 8 access<br>and 16 page protect<br>bits | No, generates N-PMV         | No, generates N-PMV | No, generates N-PMV                                       | No, generates IMA          | No, generates IMA                  |

| 01          | Yes, transfers 8 access<br>and 16 page protect<br>bits | Yes, transfers 24 bits      | Yes                 | No, generates PV                                          | Yes                        | No, generates IMA                  |

| 10          | Yes, transfers 8 access<br>and 16 page protect<br>bits | Yes, transfers 24 bits      | Yes                 | Yes, transfer under control of page protect feature       | Yes                        | Yes, unrestricted write capability |

| 11          | Yes, transfers 8 access<br>and 16 page protect<br>bits | Yes, transfers 24 bits      | Yes                 | Yes, transfer under<br>control of page protect<br>feature | Yes                        | Yes, unrestricted write capability |

TRP - Transfer Register to Protect Register TPR - Transfer Protect Register to Register

N-PMV - Non-Present Memory Violation Trap

P-V - Privilege Violation Trap

From the table it is seen that the 00 state prohibits all access to a given memory module through a given port. This capability is provided both to safeguard memory from the standpoint of privacy and also to insure that only designated units will be granted access cycles in a given module or group of modules. Therefore, in critical timing applications, the central processor or direct memory access can be assured of having all cycles in a given group of memory modules.

State 01 operates much like the page protect feature, except that the page size is 8K instead of 512 words. It allows read and execute operations but not write operations.

States 10 and 11 provide identical and unrestricted operation in SYSTEMS 86 Computers. Port 2 access to the first memory module (0-8K) is always forced by the hardware to keep the CP from locking itself out of this one module. Therefore, the value of bit 10 stored in the protect register is ignored and always treated as having the value of one.

#### SECTION III INPUT/OUTPUT

# INPUT/OUTPUT ORGANIZATION

Input/output (I/O) operations consist of transferring blocks of bytes, halfwords, or words between core memory and peripheral devices. Transfers are possible at rates up to 1,666,666 bytes, halfwords, or words per second, and are performed in an automatic manner which requires minimum Central Processor involvement.

All system components which participate in the execution of an I/O operation are illustrated in figure 3-1. The peripheral devices shown may be either data processing-type devices such as disc files, magnetic tape units, line printers, card readers, and card punches; or they may be real-time system devices such as data acquisition subsystems, communication control units, or system control units. In all cases, these devices are connected by a cable to a Device Controller Channel (DCC) in the Central Processor cabinet.

The Device Controller Channel is an Input/Output channel which performs fully buffered transfers of information concurrently with the transfer operations of other Device Controller Channels. There may be a total of 16 Device Controller Channels, all of which can perform block transfers concurrently at combined rates of up to 1,666,666 transfers per second.

Some Device Controller Channels are designed to handle single devices and others multiple devices. One is dedicated to the console keyboard/printer (DCC No. 16) and is supplied with the basic SYSTEMS 86 Computer. An additional Device Controller Channel is supplied with each peripheral device, except in cases such as magnetic tape units which operate with multi-device controllers. Under these conditions, a Device Controller Channel is supplied with the device controller.

Many devices, such as the console keyboard/printer, paper tape reader, paper tape punch, and card reader, are connected directly to a Device Controller Channel. The control electronics for these devices are incorporated into the Device Controller Channel. This implementation technique has been selected because it results in the Central Processor being buffered from delays caused by the I/O cable and the response time of the peripheral device. As a result, all peripheral device command instructions are executed in a single computer cycle time and all device test instructions are executed in two cycle times.

Multi-device controllers such as magnetic tape control units and single device controllers requiring a considerable amount of electronics, such as disc files and line printers, are contained in a cabinet other than the Central Processor cabinet. However, the Device Controller Channels to which these controllers are connected contain all of the command, test, and data buffering required to isolate the Central Processor from I/O cable and remote controller response delays. The execution time for device command and test instructions is also one and two computer cycles, respectively.

Figure 3-1. Input/Output Transfer Paths

The Automatic Input/Output System (AIOS) directs all I/O transfers between core memory and the Device Controller Channels. Transfer of a block of information is initiated by execution of a Command Device instruction in the Central Processor. This instruction specifies the device, the direction of transfer, and other control parameters required to condition the device to produce or accept data. The Automatic Input/Output System accepts these parameters from the Central Processor, routes the device control parameters to the Device Controller Channel specified in the instruction, and initializes the transfer of a block of data. The starting memory address and the number of transfers to be made are contained in a memory location dedicated to each Device Controller Channel.

Each transfer made is requested by the Transfer Interrupt (TI), which is produced by the Device Controller Channel to which the device is connected. The repetition rate of the Transfer Interrupt signal is determined by the device, if it contains some form of internal clock, or by the device controller, if it is an asynchronous device. The Automatic Input/Output System processes all Transfer Interrupt signals by initiating a transfer to/from memory and then updating the memory address and transfer count.

Finally, when the transfer count has been decremented to zero, indicating that the specified number of transfers have been made, the Automatic Input/Output System causes a Service Interrupt (SI) to be generated. This interrupt signifies the completion of transfer for the block of information.

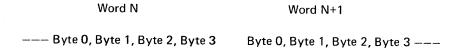

The Central Processor is capable of automatic assembly of bytes or halfwords into words during input operations and disassembly of words into bytes or halfwords during output operations. These functions, when required, are performed partially by the device controllers and partially by the formatting logic in either the Central Processor or in the Direct Memory Access. Low speed byte or character-oriented devices such as console keyboard/printer, paper tape reader and punch, and line printer transfer one byte per I/O transfer. In the case of input transfers, a word is read from memory, the input byte is inserted in the proper location, and the word is restored in memory during the same computer cycle time. Output transfers consist of reading a word from memory, transferring the proper byte to the specified Device Controller Channel, and then restoring the unaltered word into memory.

Intermediate speed devices such as disc files and magnetic tape units transfer halfwords to/from memory. The assembly/disassembly process is the same as for byte-oriented devices, except for the number of bits contained in each transfer.

High speed devices, such as external core memories and very high speed data acquisition systems, can transfer 32 bits at a time to/from core memory. These transfers, like all others, can occur at a rate of one per computer cycle.

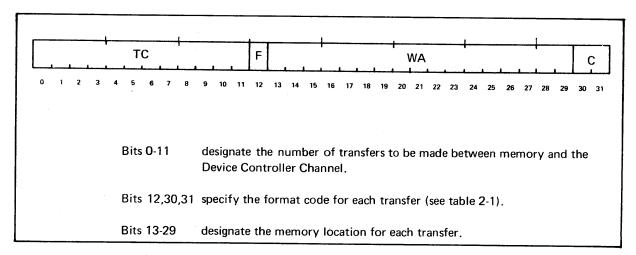

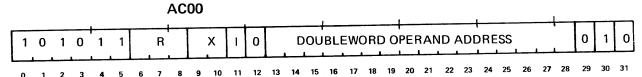

# TRANSFER CONTROL WORD

The key to all transfer processing by the Automatic Input/Output System is the Transfer Control Word assigned to each Device Controller Channel. The Transfer Control Word contains a 20-bit address which defines the memory location for each transfer. It also contains a positive 12-bit binary transfer count (TC). The transfer count plus the format code (FC) permit transfers of blocks of information having any number of bytes, halfwords, or words up to 4,096. The format of the Transfer Control Word is shown in figure 3-2.

Figure 3-2. Transfer Control Word Format

The processing of each transfer interrupt by the Automatic Input/Output System consists of incrementing the address and decrementing the transfer count each time a transfer interrupt occurs. The End-of-Block (EOB) signal is generated by the Device Controller Channel when the transfer count is equal to zero. This level is connected to the service interrupt level assigned to the Device Controller Channel.

The presence of the format code in the Transfer Control Word permits transfers of bytes, halfwords, or words. The format code is designed such that when F is equal to one in a given transfer control word, the address is incremented in bit position 31 each time a transfer occurs. Therefore, each transfer is stored in or read from a consecutive byte in memory in the order:

The proper binary value of format code for accessing consecutive halfwords in memory is F equal to 0, C equal to Y1, where Y equal to zero designates left halfword and Y equal to one designates right halfword. With this value of format code, the address is incremented in bit position 30 each time a transfer is made. This results in the desired accessing of consecutive halfwords.

The proper value of format code for consecutive word accessing is FC equal to 000. When this value is present in a given transfer control word, the Automatic Input/Output System increments the Transfer Control Word in bit position 29 each time a transfer occurs.

The format code values discussed above are summarized in table 3-1.

Each time the address is incremented, the transfer count is decremented. Therefore, the block length is always defined by the number of memory accesses and not by the number of words transferred.

TABLE 3-1. TRANSFER CONTROL WORD FORMAT CODE

| Information Format                                                              | FC                |  |  |

|---------------------------------------------------------------------------------|-------------------|--|--|

| Byte<br>Halfword<br>Word                                                        | 1XX<br>0Y1<br>000 |  |  |

| XX = Byte number Y = 0 designates left halfword Y = 1 designates right halfword |                   |  |  |

DEVICE CONTROLLER CHANNEL TYPES Two types of Device Controller Channels are available with SYSTEMS 86 Computers: high priority and low priority. High priority Device Controller Channels contain a 32-bit hardware register which stores the current transfer control word. These Device Controller Channels also contain one or more data registers, which buffer information between the Central Processor and the peripheral device. Therefore, high priority Device Controller Channels are provided to minimize the amount of time taken from Central Processor operation by I/O transfers. Only one cycle is stolen per transfer. Disc files, magnetic tape units, and high speed data acquisition systems are connected to the Central Processor through high priority Device Controller Channels.

Low priority Device Controller Channels are used to connect keyboard/printer, paper tape, line printer, card equipment, low-speed data acquisition systems, and similar equipment to the Central Processor. A data register is also provided in each of these channels so that the Central Processor will not be delayed by peripheral device response time and cable delays. However, the Transfer Control Word is stored in the memory location dedicated to the Device Controller Channel transfer interrupt level rather than in a hardware register (see table 4-1). Therefore, a total of three computer cycles are stolen per transfer, since the transfer control word must be read, processed, and written back into memory each time a transfer is made. This function requires two cycle times in addition to the one required for the I/O transfer.

DEVICE CONTROLLER CHANNEL PRIORITY AND PARAMETER ASSIGNMENTS A significant feature of the I/O structure is the ability to connect Device Controller Channels in a highly flexible and yet program-transparent manner. The Device Controller Channels are constructed of functional printed circuit cards that are inserted in a chassis, as shown in figure 3-1. This chassis can contain up to 16 Device Controller Channels, although it is wired for only seven in the basic SYSTEMS 86 Computer. Each position has a unique transfer priority, with position one having the highest priority and position 16 the lowest. Therefore, devices with higher transfer rates are connected to the higher priority positions.

The connector wiring is the same for all positions in the chassis, except the fixed position of the console keyboard/printer (position 16). For this reason, any Device Controller Channel can be inserted in any position in the chassis other than position 16. This provides the system with a flexibility of containing multiple Device Controller Channels of the same type, or of being able to move channels to new priority positions to permit additional Device Controller Channels to be connected.

The program transparency feature results from the fact that all parameters which affect Central Processor programming directly are implemented on the cards which make up the Device Controller Channel. Therefore, no program change need be made when a Device Controller Channel is moved from one chassis position to another, since the parameters move with the cards. The parameters which do change when a move is made are the actual priorities of the Transfer and Service Interrupt levels. The virtual priorities used by the interrupt control instructions remain unchanged.

Because the service interrupt level used in interrupt control instructions is a function of the card and may differ from the actual priority level which is a function of the card position, it is necessary that a virtual and an actual priority concept be introduced. The actual priority level is used by the Central Processor hardware interrupt structure, and the virtual priority level is used by the interrupt control instruction group. The service interrupt priority levels are unique in this respect. The transfer interrupt priority levels are not program controllable and are wired to have fixed priorities.

The standard Device Controller Channel numbers, device addresses, transfer interrupt, and service interrupt parameters are defined in table 3-2. The devices are listed in the order of descending transfer rate, except possibly for the system device controller channels which are discussed later.

TABLE 3-2. DEVICE CONTROLLER CHANNEL ASSIGNMENTS

| Rel<br>Prio | ative<br>ority | Device                   | DCC<br>Number | Device<br>Addresses | Maximum<br>Number<br>of | T1<br>Dedicated<br>Location | S1<br>Dedicated<br>Location | T1<br>Level<br>(H) | S1<br>Virtual<br>Level | Std. S1<br>Actual<br>Level<br>(H) * |

|-------------|----------------|--------------------------|---------------|---------------------|-------------------------|-----------------------------|-----------------------------|--------------------|------------------------|-------------------------------------|

| Std         | Opt            |                          | (H)           | (H)                 | Devices                 | (H)                         | (H)                         | ····               | (H)                    | (n)                                 |