OSG - V30/35(7/92)

United States

Australia

United Kingdom

#### Contributors

Written by Lawrence Ertel Illustrated by Keith Granger

Engineering contributions by Bob Abbott, Tore Kellgren, Larry Lewis, Todd Nordland, Edward (Ted) Wilcox, and Ken Williams

#### © Copyright 1992, Silicon Graphics, Inc.— All Rights Reserved

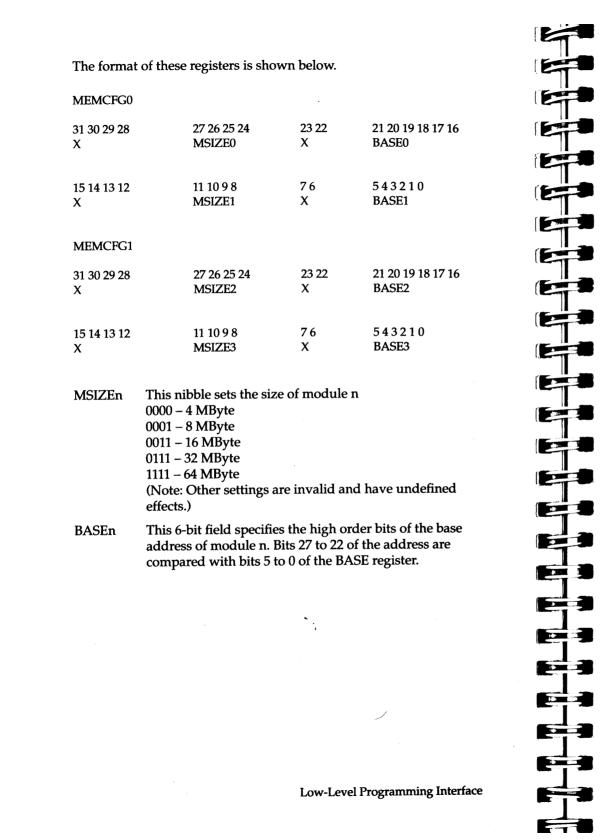

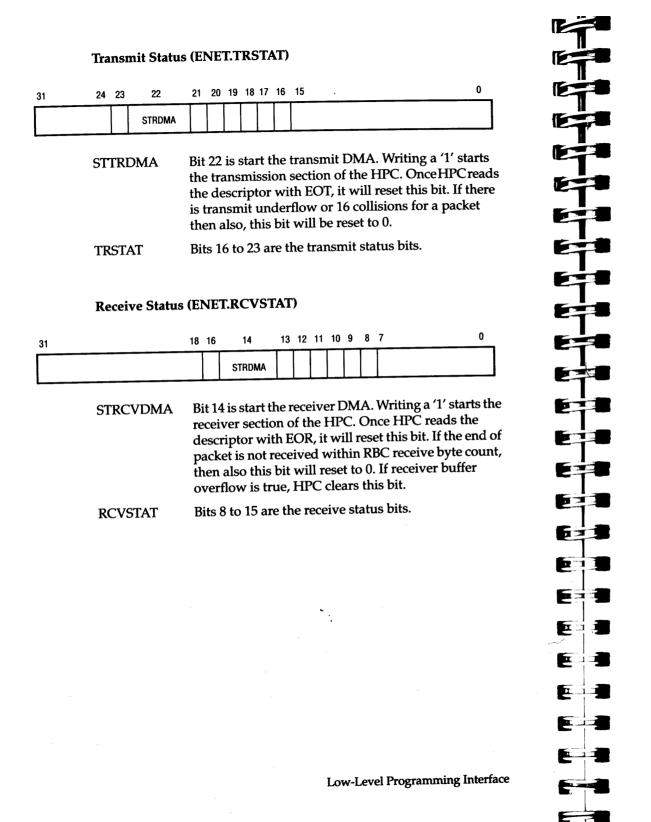

This document contains proprietary and confidential information of Silicon Graphics, Inc. The contents of this document may not be disclosed to third parties, copied, or duplicated in any form, in whole or in part, without the prior written permission of Silicon Graphics, Inc.

#### **Restricted Rights Legend**

Use, duplication, or disclosure of the technical data contained in this document by the Government is subject to restrictions as set forth in subdivision (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 52.227-7013 and/or in similar or successor clauses in the FAR, or in the DOD or NASA FAR Supplement. Unpublished rights reserved under the Copyright Laws of the United States. Contractor/manufacturer is Silicon Graphics, Inc., 2011 N. Shoreline Blvd., Mountain View, CA 94039-7311. The information in this guide is subject to change without notice.

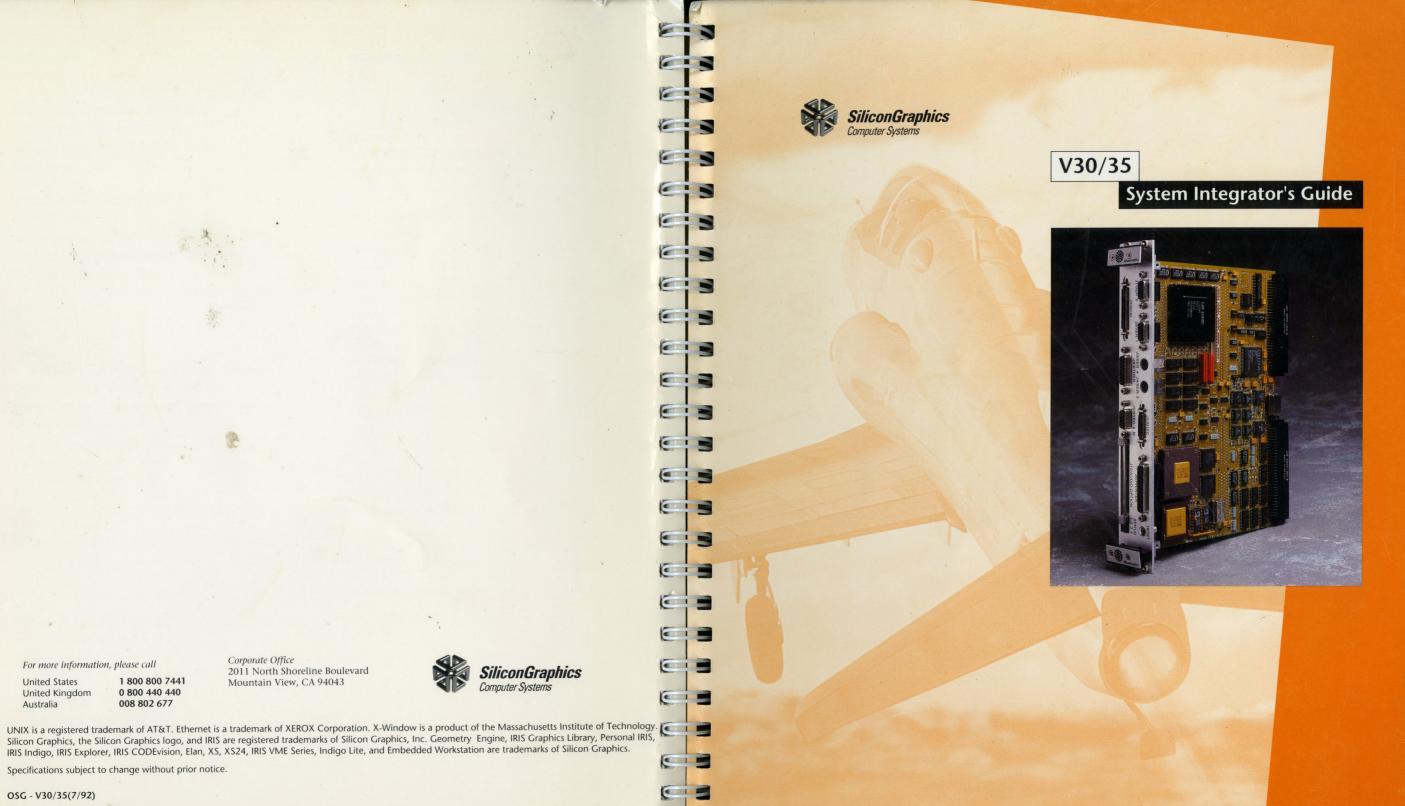

#### V30/35 System Integrator's Guide Document Number 007-5015-020

#### Silicon Graphics, Inc. Mountain View, California

Silicon Graphics and IRIS are registered trademarks and Personal IRIS, IRIS Indigo, IRIX, Graphics Engine, Private Bus, GIO Bus, and Graphics Library are trademarks of Silicon Graphics, Inc. MIPS is a registered trademark of MIPS Computer Systems, Inc. Centronics is a registered trademark of Centronics Data Computer Corporation. Ethernet is a registered trademark of Xerox Corporation. NFS is a trademark of Sun Microsystems, Inc. UNIX is a registered trademark of Unix Systems Laboratories. X Window System is a trademark of the Massachusetts Institute of Technology. Motif is a trademark of the Open Software Foundation. Duracell is a registered trademark of Duracell, Inc.

### To The Reader

Your V30/35 CPU subsystem came with a standard set of manuals. The set includes the V30/35 System Integrator's Guide, the Personal System Administration Guide, the IRIS Software Installation Guide and the IRIX Device Driver Programming Guide. Below you'll find a brief description of each book. For more detailed information on a particular book, please refer to the first chapter in that book.

*V30/35 System Integrator's Guide* — Explains how to install and maintain your CPU subsystem, install the necessary software, and run interactive diagnostics.

8

53

Personal System Administration Guide — Explains how to create and modify a login account, set up your V30/35 as part of a network, back up your work, and more. If you are responsible for managing many workstations or a large network, also see the IRIX Site Administrator's Guide.

*IRIS Software Installation Guide* — Explains how to install Silicon Graphics software products. It covers basic installation procedures, customization techniques, and troubleshooting. Also serves as a complete reference for the installation program, *inst*.

dev dev

*IRIX Device Driver Programming Guide* — Explains how to write a device driver for your CPU subsystem.

і. З.

iv

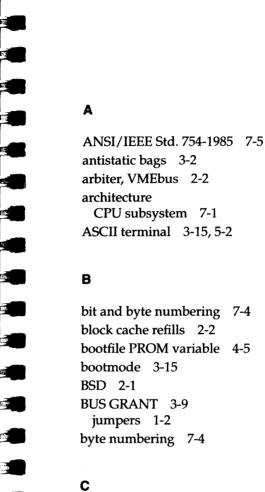

# Contents

|    | To The Readeriii                              |

|----|-----------------------------------------------|

| 1. | Introduction1-1                               |

|    | Conventions1-2                                |

| 2. | The V30/35 CPU Subsystem2-1                   |

|    | CPU Subsystem Features                        |

|    | Memory Expansion2-3                           |

| 3. | Hardware Installation3-1                      |

|    | Service and Support Information               |

|    | Electrostatic Discharge (ESD) Precautions     |

|    | Electromagnetic Interference (EMI) Compliance |

|    | General Guidelines for Installing Handause    |

|    | General Guidelines for Installing Hardware    |

|    | Preparations                                  |

|    | Power Supply3-5                               |

|    | Unpacking                                     |

|    | Installing the CPU Subsystem                  |

|    | Installing the Graphics Subsystem             |

|    | Installing Additional VMEbus Devices          |

|    | Installing Airflow Restrictors                |

|    | Connecting Peripheral Devices                 |

|    | Supported Devices                             |

|    | Checking the Installation3-14                 |

|    | Powering Up the System3-15                    |

V

| Installing System Software            |      |

|---------------------------------------|------|

| Installing Additional Software        |      |

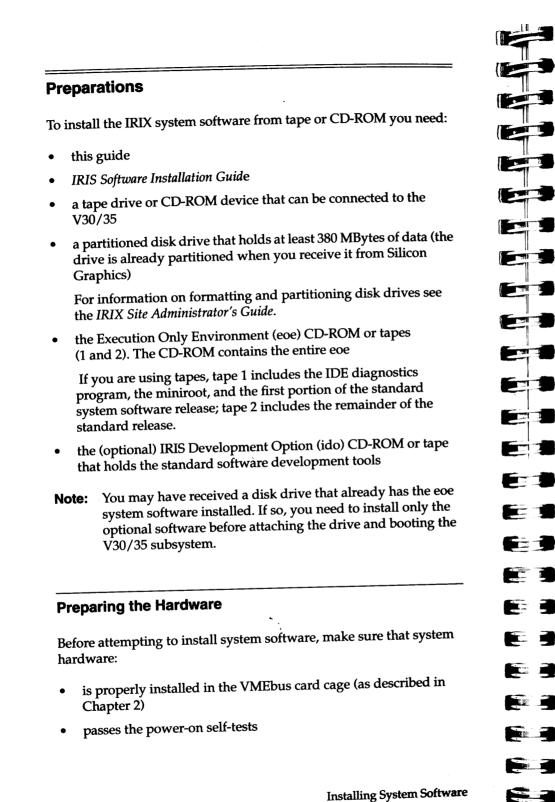

| Preparations                          |      |

| Preparing the Hardware                |      |

| Preparing the Standalone Environment  |      |

| Installing the System Software        | 4-6  |

| Diagnostics                           | 5-1  |

| Power-on Tests                        | 5-1  |

| Test Failure                          | 5-2  |

| Using IDE Diagnostics                 | 5-4  |

| Starting IDE in Terse or Verbose Mode | 5-4  |

| IDE Standard Tests                    | 5-5  |

| IDE Interactive Commands              | 5-6  |

| General Commands                      | 5-6  |

| CPU Subsystem Tests                   | 5-7  |

| The VMEbus                            | 6-1  |

| VMEbus History                        | 6-1  |

| VMEbus Signals                        | 6-2  |

| DTB Bus                               | 6-4  |

| Bus Arbitration                       | 6-8  |

| Interrupt Handling                    | 6-10 |

| Utility Bus                           |      |

| VMEbus Specifications                 |      |

| VMEbus Pinouts                        | 6-12 |

| CPU Subsystem Architecture            |      |

| CPU Subsystem                         |      |

| Processor Core                        |      |

| MIPS R3000A CPU                       |      |

| MIPS R3010A FPU                       |      |

| Instruction and Data Caches           |      |

| Main Memory                           | 7-10 |

|                                       |      |

8.

| I/O System                                 |  |

|--------------------------------------------|--|

| Ethernet Port7-13                          |  |

| SCSI-II                                    |  |

| Parallel Port7-14                          |  |

| Serial Ports7-14                           |  |

| GIO32 Bus7-14                              |  |

| VMEbus Interface7-15                       |  |

| Local (V30/35) to VMEbus Memory Access     |  |

| VMEbus-to-Local (V30/35) Memory Access7-17 |  |

| VMEbus Arbiter7-18                         |  |

| VMEbus System Clock7-18                    |  |

| VMEbus Watchdog Timer7-18                  |  |

| CPU Address Space7-19                      |  |

|                                            |  |

|                                            |  |

| Low-Level Programming Interface            |  |

| Low-Level Programming Interface            |  |

|                                            |  |

| CPU, Memory, Boot PROM, VME Registers8-1   |  |

| CPU, Memory, Boot PROM, VME Registers      |  |

| CPU, Memory, Boot PROM, VME Registers      |  |

| CPU, Memory, Boot PROM, VME Registers      |  |

| CPU, Memory, Boot PROM, VME Registers      |  |

| CPU, Memory, Boot PROM, VME Registers      |  |

| CPU, Memory, Boot PROM, VME Registers      |  |

| CPU, Memory, Boot PROM, VME Registers      |  |

| CPU, Memory, Boot PROM, VME Registers      |  |

| CPU, Memory, Boot PROM, VME Registers      |  |

.

vi

; ; ,

vii

|    | Ethernet Controller Register8-14       |  |

|----|----------------------------------------|--|

|    | SCSI Controller Registers8-18          |  |

|    | Centronics Controller Registers        |  |

| Α. | Operating Conditions A-1               |  |

| в. | Routine Maintenance                    |  |

|    | Replacing the Clock Battery B-1        |  |

| C. | Pinouts for Peripheral ConnectorsC-1   |  |

| D. | Cultabas Jumpers and Nemery Nens       |  |

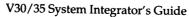

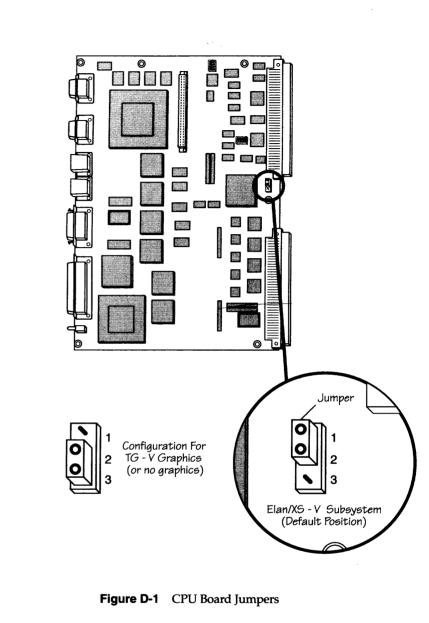

|    | Switches, Jumpers, and Memory Maps D-1 |  |

|    | Jumpers D-1                            |  |

|    | Jumpers D-2                            |  |

|    |                                        |  |

| E. | Jumpers D-2<br>Oscillator              |  |

Figures

63

E

ES

EI

EB

ÊJ

e j

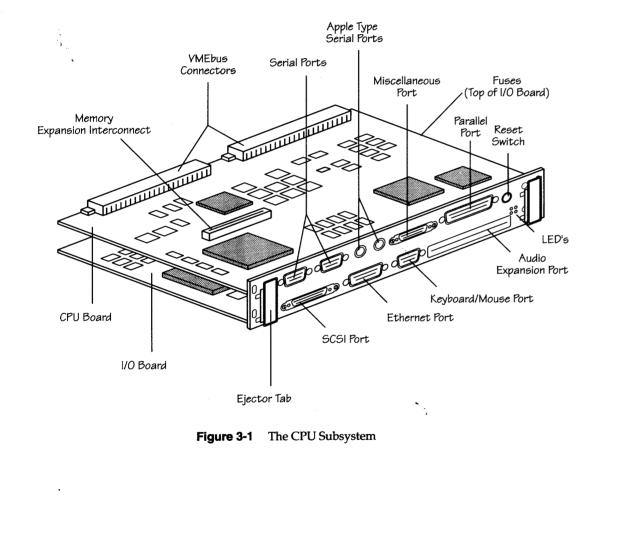

| Figure 3-1 | The CPU Subsystem3-6                                              |

|------------|-------------------------------------------------------------------|

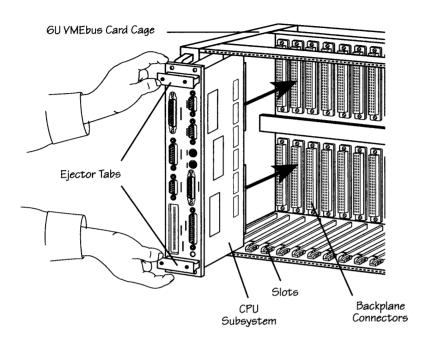

| Figure 3-2 | Installing the CPU Subsystem                                      |

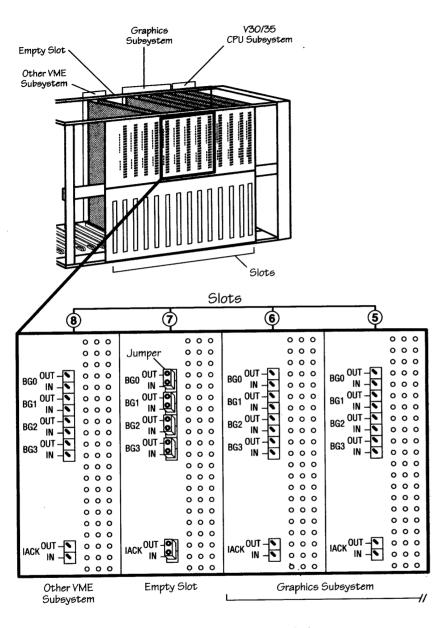

| Figure 3-3 | Configuring the VMEbus Backplane3-10                              |

| Figure 3-4 | Connectors for Peripheral Devices                                 |

| Figure 4-1 | Installing Software with External<br>SCSI Tape and Disk Drives4-3 |

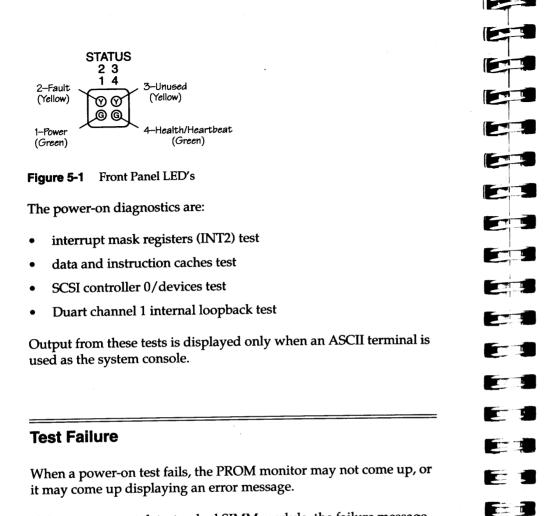

| Figure 5-1 | Front Panel LED's5-2                                              |

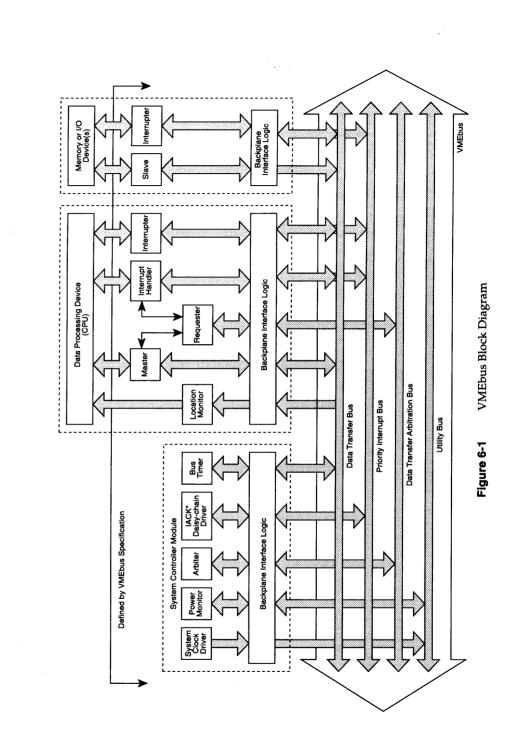

| Figure 6-1 | VMEbus Block Diagram6-3                                           |

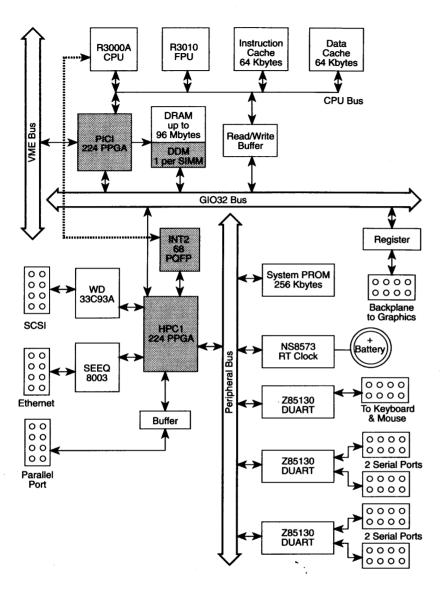

| Figure 7-1 | CPU Board Block Diagram7-2                                        |

| Figure 7-2 | Bit and Byte Numbering7-5                                         |

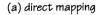

| Figure 7-3 | Cache Operation7-6                                                |

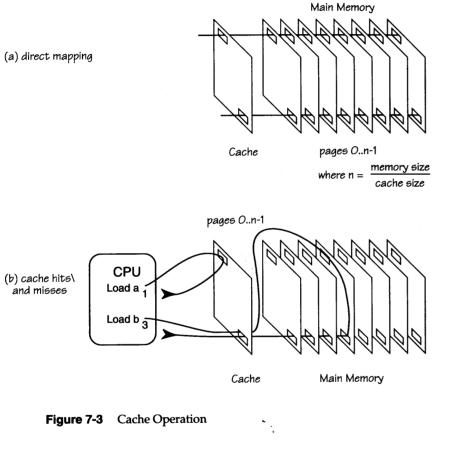

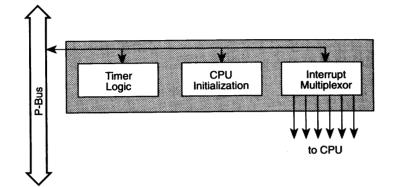

| Figure 7-4 | PIC1 ASIC7-7                                                      |

| Figure 7-5 | INT2 ASIC7-10                                                     |

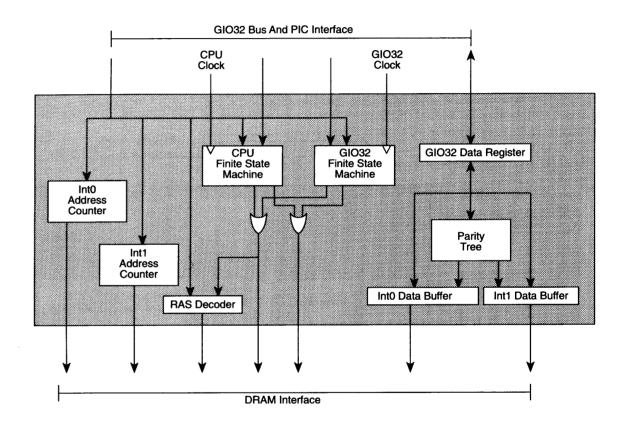

| Figure 7-6 | DDM ASIC7-11                                                      |

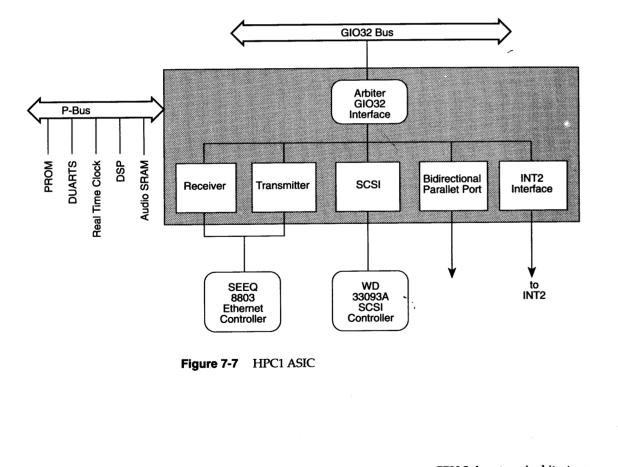

| Figure 7-7 | HPC1 ASIC7-12                                                     |

| Figure B-1 | Removing the Clock BatteryB-1                                     |

| Figure C-1 | SCSI Connector Pin Numbering (front view)C-2                      |

| Figure D-1 | CPU Board JumpersD-3                                              |

| Figure D-2 | I/O Board JumpersD-4                                              |

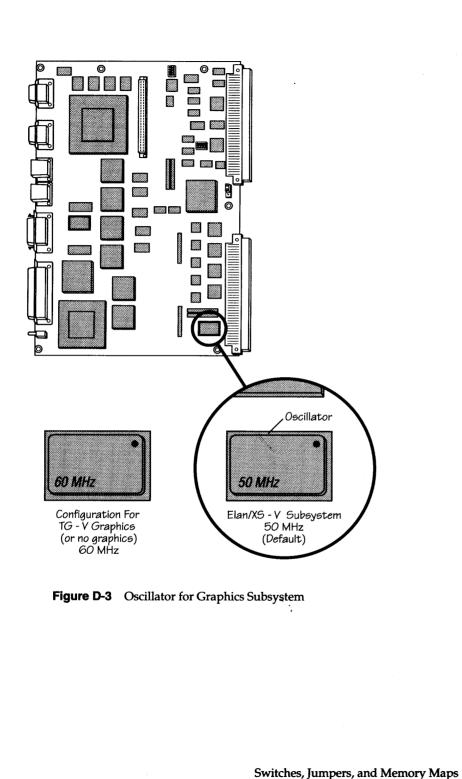

| Figure D-3 | Oscillator for Graphics SubsystemD-6                              |

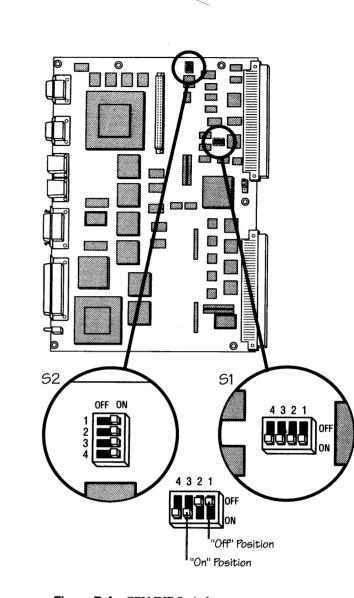

| Figure D-4 | CPU DIP SwitchesD-9                                               |

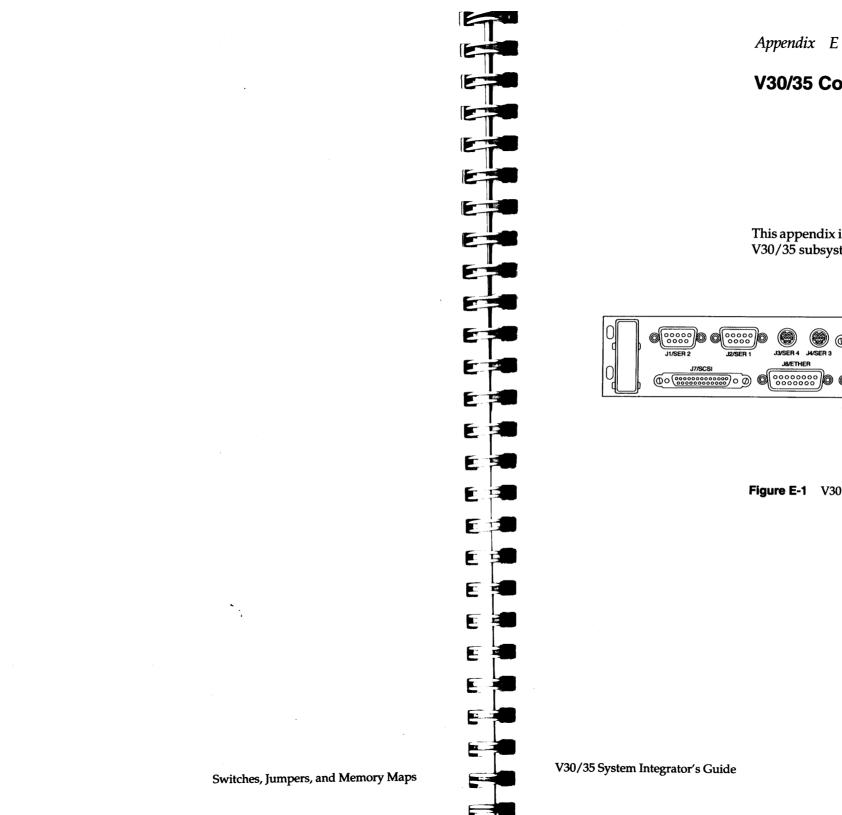

| Figure E-1 | V30/35 Front Panel E-1                                            |

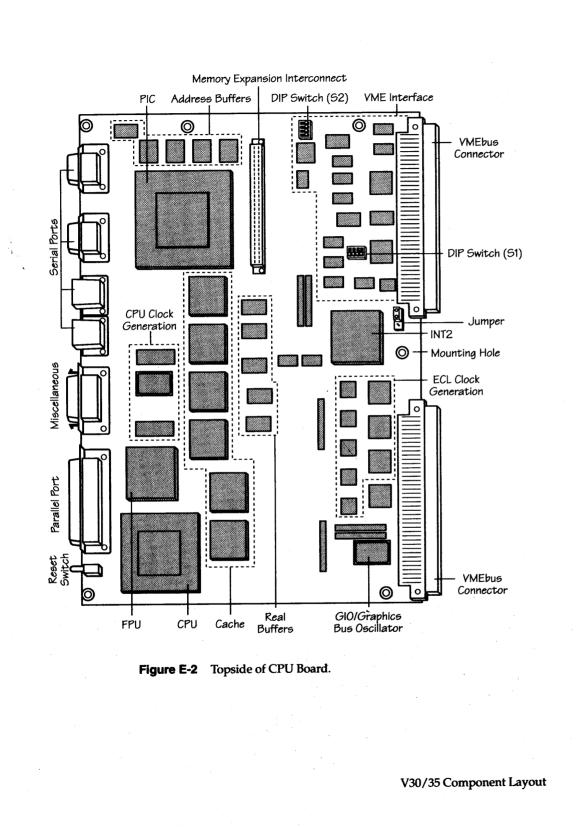

| Figure E-2 | Topside of CPU Board E-2                                          |

| Figure E-3 | Bottom of CPU Board E-3                                           |

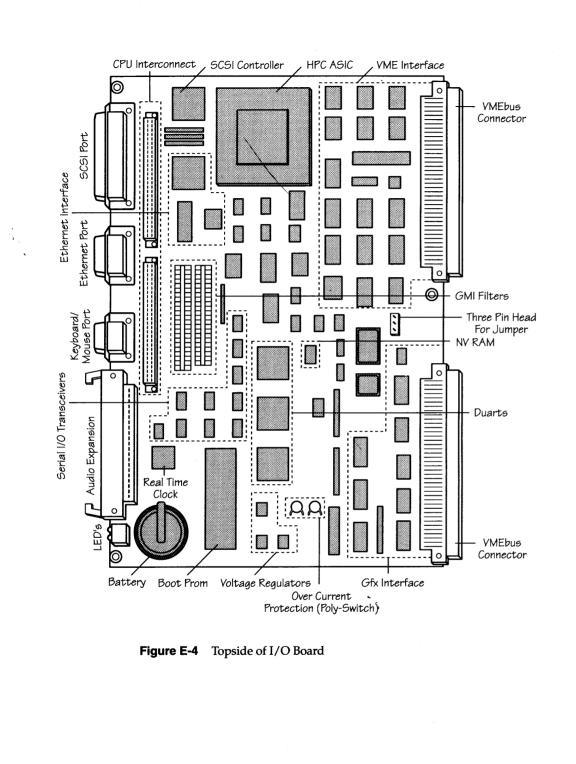

| Figure E-4 | Topside of I/O Board E-4                                          |

ix

| · |     |  |

|---|-----|--|

|   |     |  |

|   |     |  |

|   |     |  |

|   | e 3 |  |

| • | E J |  |

|   | EJ  |  |

|   |     |  |

|   | EB  |  |

|   | EJ  |  |

|   |     |  |

5

X

•

Tables

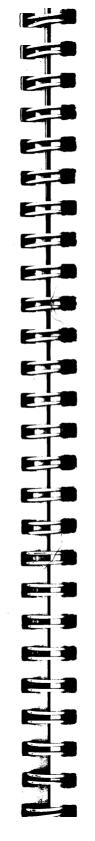

| Table 3-1 | Silicon Graphics Peripheral Devices3-13 |

|-----------|-----------------------------------------|

| Table 5-1 | IDE SIMM Failure Symbols5-3             |

| Table 6-1 | VMEbus Address Modifiers6-5             |

| Table 6-2 | VMEbus P1 Pin Assignments6-13           |

| Table 6-3 | VMEbus P2 Pin Assignments6-15           |

| Table 6-4 | VMEbus Pin Assignment Names6-17         |

| Table 7-1 | V30/35 VMEbus Master Address Map7-16    |

| Table 7-2 | Global Address Map7-19                  |

| Table 7-3 | Normally Inaccessible Addresses         |

| Table 7-4 | Local I/O Segment Map7-20               |

| Table 7-5 | HPC Address Map7-21                     |

| Table 8-1 | CPU, Main Memory, Boot PROM,            |

|           | and VMEbus Registers8-1                 |

| Table 8-2 | GIO Bus Registers8-8                    |

| Table 8-3 | Graphics Channel Registers8-9           |

| Table 8-4 | 3-Way Transfer Registers8-11            |

| Table 8-5 | Serial Port DUART Registers8-13         |

| Table 8-6 | Ethernet Control Registers8-14          |

| Table 8-7 | SCSI control Registers8-18              |

| Table 8-8 | Centronics Control Registers            |

| Table C-1 | Pinouts for Peripheral ConnectorsC-1    |

| Table C-2 | I/O Board P2 VMEbus ConnectorC-3        |

| Table D-1 | Jumper positionsD-2                     |

| Table D-2 | DIP Switch PositionsD-7                 |

| Table D-3 | Switch Bank S1 FunctionalityD-8         |

|           | •                                       |

.

xi

.

### Chapter 1

### Introduction

This guide tells you how to install the V30 and V35 CPU subsystems and the IRIX<sup>™</sup> operating system software. It also explains how to operate the interactive diagnostic environment (IDE) hardware diagnostics program. Later chapters provide detailed information about system architecture and the low-level programming interface.

This guide contains the following chapters:

- Chapter 1, "Introduction," explains how to use this guide.

- Chapter 2, "The V30/35 CPU Subsystem," summarizes product features.

- Chapter 3, "Hardware Installation," provides instructions for unpacking and installing the CPU.

- Chapter 4, "Software Installation," provides instructions for installing the IRIX<sup>™</sup> operating system.

- Chapter 5, "Diagnostics," provides instructions for operating the IDE diagnostics program.

- Chapter 6, "The VMEbus," gives background information on the VMEbus.

- Chapter 7, "CPU Subsystem Architecture," offers a detailed description of the CPU subsystem.

- Chapter 8, "Low-Level Programming Interface," lists the various registers that provide low-level access to the system.

- Appendix A, "Operating Conditions," gives power requirements of the V30/35 subsystem.

- Appendix B, "Routine Maintenance," provides instructions for changing the clock battery.

- Appendix C, "Pinouts for Peripheral Connectors," outlines the pinouts for all of the V30/35 peripheral connectors.

- Appendix D, "Switches, Jumpers, and Memory Maps," shows you how to locate the V30/35 DIP switches and jumpers and explains how to set them correctly.

- Appendix E, "V30/35 Component Layout," illustrates the front panel and circuit boards used in the V30/35.

- **Note:** For information on installing a graphics subsystem, please refer to the system integrator's guide included with the product.

### Conventions

This V30/35 System Integrator's Guide uses the following conventions:

- References to other documents are in *italics*.

- References to other chapters and sections within this guide are in quotation marks.

- Step-by-step instructions used to perform a task are shown as numbered sentences. These may be followed by additional instructions, marked with a small box, that further explain the step. For example:

- 1. Make sure the VMEbus backplane is properly jumpered.

- If necessary, remove any coverings or enclosures to get access to the rear of the VMEbus backplane. (Some VMEbus backplanes may be jumpered from the front.)

- With the backplane exposed, replace the single IACK and the four BUS GRANT jumpers from each of the empty slots between the CPU subsystem and your other cards.

- Programming variables are shown in italics.

- Text that appears on screen is shown in a typewriter (courier) font.

- Individual keyboard commands are shown in boldface within angle brackets.

• Keyboard user input is shown in a boldface typewriter (courier) font.

Introduction

ES

ES

12.0

1-2

5

Introduction

### Chapter 2

### The V30/35 CPU Subsystem

The V30/35 CPU subsystem provides the processing power of the Silicon Graphics<sup>®</sup> 4D/30 or 4D/35 Personal IRIS<sup>™</sup> workstation for any standard 6U VMEbus card cage with P2 backplane connectors. The V30/35 hardware package consists of a central processing unit (CPU) subsystem which supports multiple optional graphics subsystems. The CPU and graphics subsystems each come prepackaged and ready to install.

The V30/35 is compatible with Silicon Graphics' entire product line of reduced instruction set computing (RISC) systems. It is an ideal solution for applications that require the functionality and performance of a Personal IRIS or IRIS Indigo<sup>™</sup> in a VMEbus-based embedded system. The V30/35 is also ideal for hardware configurations that require additional VMEbus expansion.

Like the 4D/30 and 4D/35 workstations, the V30 and V35 CPU subsystems are particularly suited to applications that require intensive visual processing, such as medical imaging, mission planning, and air traffic control. The optional graphics subsystem and on-board I/O controllers use the Silicon Graphics GIO Bus<sup>™</sup> to communicate with the CPU, allowing better throughput of data from VMEbus devices.

The V30/35 provides full support for the IRIX operating system (UNIX<sup>®</sup> System V Release 3 with BSD extensions), as well as the X Window System<sup>™</sup> and Motif<sup>™</sup> window manager. The Silicon Graphics industry-standard Graphics Library<sup>™</sup> can be used to calculate and display three-dimensional objects.

The system can support up to four standard TG - V graphics subsystems with each subsystem monitor displaying multiple windows. The system can also support the Elan/XS - V graphics subsystem; however, it can not support both types of graphics subsystems at the same time. 63

EI

63

E

E

EJ

EI

The V30/35 CPU Subsystem

### **CPU Subsystem Features**

The CPU subsystem assembly consists of two Institute of Electrical and Electronic Engineers (IEEE) Std. 1014-1987 double-height VMEbus EuroCards: a CPU board and an input/output (I/O) interface board. These boards *must* reside in the first two slots as they are serving as the VMEbus system controller (arbiter).

#### The V35 CPU board features:

- the MIPS<sup>®</sup> R3000A 32-bit RISC 36 MHz CPU delivering 33 MIPs

- the MIPS R3010A 36 MHz floating point coprocessor delivering 6 MFLOPs

The V30 CPU board features:

- the MIPS R3000A 32-bit RISC 30 MHz CPU delivering 27 MIPs

- the MIPS R3010A 30 MHz floating point coprocessor delivering 4.7 MFLOPs

Both the V30 and V35 CPU boards feature:

- full support for R3000A features including block cache refills and partial cache writes

- a 64 KByte direct mapped instruction cache and a 64 KByte direct mapped, write-through (one-deep, write buffer) data cache

- up to 32 MBytes of main memory (using SIMMs), expandable to 96 MBytes with the optional memory expansion board

- one Centronics<sup>®</sup>-compatible bi-directional parallel port

Both the V30 and V35 I/O interface boards feature:

- a GIO Bus that supports:

- transfers at sustained rates of up to 100 MB/sec.

- I/O transfers for up to four TG V graphics subsystems

- I/O transfers for a single Elan/XS V graphics subsystem

- Real Time Clock (RTC)

- four general-purpose RS423 type serial ports with full modem control at a transfer rate of 38.4 Kbaud

- dedicated serial ports for the Personal IRIS keyboard and mouse

- a standard 32-bit VMEbus interface

- a graphics interface (rows P2A and P2C of VMEbus)

- one Ethernet<sup>®</sup> port with Transmission Control Protocol/Internet Protocol (TCP/IP) support, yielding peak data transfer rates of up to 10 Mbits/sec.

- one single-ended Small Computer System Interface (SCSI) port, with peak data transfer rates of up to 5 MBytes/sec.

#### Memory Expansion

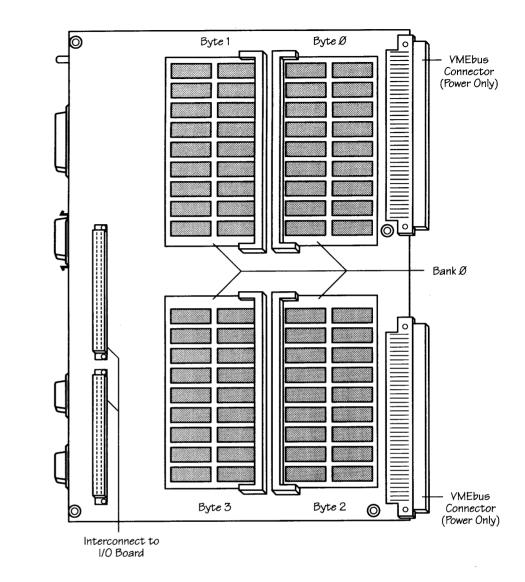

An optional memory expansion board occupies one additional 6U slot and supports up to 64 MBytes of additional memory in 2 memory banks.

## Hardware Installation

This chapter explains how to install the V30/35 CPU subsystem into the VMEbus card cage. The steps involved include:

- 1. preparations

- 2. unpacking

- 3. installing the CPU subsystem

- 4. installing additional VMEbus device

- 5. connecting peripheral devices

- 6. checking the installation

- 7. powering up the system

Be sure to read and understand the complete contents of any procedure described in this chapter before attempting it. If something is not clear to you or if you encounter problems, be sure to get help from your support provider.

Note: Your VMEbus system configuration must conform to industry standard VMEbus specifications in order to ensure proper operation of your V30/35 CPU and graphics subsystems.

### Service and Support Information

When you purchased your system you may have purchased a support program from either Silicon Graphics, Inc., or a software vendor. Whenever you encounter any problems that you cannot solve using the methods described in this document, contact the organization from which you purchased the support program.

If you did not purchase a support program, contact your sales representative to arrange for support.

### **Electrostatic Discharge (ESD) Precautions**

This equipment is extremely sensitive and may be susceptible to damage caused by Electrostatic Discharge (ESD). ESD is an electrical discharge (spark) caused by the build-up of electrical charge on clothing and other materials.

You must use proper ESD preventative measures:

- Connect a ground strap to your wrist and to the metal frame of the VMEbus card cage.

- You and all the electrical equipment that you handle during this installation must be at ground potential to avoid damage from ESD.

- Keep the boards in the antistatic bags provided.

- Remove a board from its antistatic bag only when you are properly grounded to the card cage with a ground strap.

- Do not use an ohmmeter on the boards.

- The card cage should be powered down and grounded until the installation is complete and ready for testing. The AC power cord provides a ground for the card cage and should be left plugged in unless some other ground is provided.

### **Electromagnetic Interference (EMI) Compliance**

To make this system comply with FCC, VDE, and VCCI emission requirements, follow these guidelines:

- Ensure that the VMEbus chassis and power supply meet FCC, CISPR-22, and VDE specifications.

- Securely tighten screws holding the VMEbus cards.

- Install blanking panels over unused slots.

- Connect all peripheral devices with shielded cables.

- Ensure the internal and external unshielded cables that connect to Input/Output connectors have EMI suppression components such as ferrite cable, cable clamps, filters, etc.

### **General Guidelines for Installing Hardware**

Remember the following guidelines whenever you install or handle the electronic equipment described in this guide:

- In addition to electrostatic discharge, this equipment is also susceptible to damage from physical impact, exposure to excessive temperatures, moisture, solvents, and other conditions known to damage electronic equipment. Please handle with care!

- This equipment has been carefully designed and manufactured to fit properly into the VMEbus card cage. While moderate force is necessary to seat a subsystem in the card cage, you should not have to struggle. If you experience any difficulty whatsoever, remove the subsystem from the card cage and inspect both subsystem and backplane for bent connector pins, obstructions, or other damage. Do not apply impact or excessive force to seat a subsystem into the card cage; never use tools or other implements to seat a board into a card cage.

- Use only AC outlets that are properly grounded.

- Make sure that the power supply is adequate for the number of slots being used; typically 30W at 5V for each slot.

- Make sure the card cage has adequate air flow for cooling purposes; use covers and airflow restrictors on all empty slots.

- Warning: Never expose the card cage power supply. Power supplies generate high voltages, even when not plugged in! Contact with an exposed or improperly grounded power supply can deliver a severe electrical shock. The power supply must remain grounded and shielded. If you are not certain which coverings prevent access to the power supply, refer to the documentation for your card cage before removing any of its coverings.

#### Preparations

Both CPU and graphics subsystems arrive assembled and ready to install. Before you begin, make sure that you have the proper items on hand and that the operating conditions described in Appendix B, "Operating Conditions" have been met.

Before removing the board assemblies from their packaging, make sure that the ambient temperature is between 0°C and 55°C. The work area should be free of excessive dust, airborne fumes, solvents or other possible contaminants, and any other conditions that might result in damage to electronic equipment.

In addition to this guide, you will need the items listed below to install this equipment successfully:

- an electrostatic discharge grounding strap for each person who may need to handle the PC-board assemblies

- a small standard (flat-head) screwdriver

- any other tools needed to remove covers or enclosures surrounding your VMEbus card cage

- ork her in tall

A set

**Note:** Before installing the CPU or graphics subsystem, check the ground pins on the P1 and P2 connectors of the slots in which you intend to place it. These pins must be present to ground the subsystem properly.

### **Power Supply**

Be sure your power supply is adequate to support the number of slots in your backplane.

The CPU and subsystem consists of two boards and the graphics subsystems each consist of between two and four boards, depending on the configuration. When installing multiple subsystems, it is especially important to be sure that the power supply is adequate for the number of slots taken up. The VMEbus standard of 30 watts (6 amps at 5 volts) per slot is sufficient. (Refer to Appendix A, "Operating Conditions," for information on power requirements for this CPU.)

### Unpacking

While unpacking your V30/35, remember to inspect each assembly and any accompanying materials for damage. When it is not in the card cage, place the new equipment on a clean, stable surface that is safely insulated from electrostatic discharge. If possible, leave the V30/35 board assemblies in their conductive plastic wrappings when they are not in the card cage.

Your packages should contain:

- the CPU subsystem as shown in Figure 3-1

- a single CD-ROM or several installation tapes

V30/35 System Integrator's Guide

Hardware Installation

Depending on the options you ordered, the installations tapes include the following:

- Execution Only Environment tape, Part 1 (eoe1)

- Execution Only Environment tape, Part 2 (eoe2)

- optional Development Environment tape (*dev*)

There may also be an additional tape or CD-ROM accompanied by an errata sheet explaining its usage.

**1**.7

3

ý -

Hardware Installation

**Note:** Your V30/35 may include an optional graphics subsystem in a separate package. Instructions on the installation and operation of the graphics subsystem can be found in the system integrator's guide included with the product.

### Installing the CPU Subsystem

The CPU subsystem occupies two slots on the VMEbus.

To install the CPU subsystem:

1. Set the switches and jumpers to configure the CPU operation and VMEbus-to-local memory maps.

The V30/35 CPU subsystem *must* be used as the VMEbus system controller and is set up for this purpose by default with the appropriate mappings for the IRIX operating system. See Appendix D, "Switches, Jumpers, and Memory Maps," for additional information.

2. Verify that the CPU subsystem is configured for your graphics subsystem (if any) with the appropriate oscillator and jumpers.

For information on the proper configurations, see Appendix D, "Switches, Jumpers, and Memory Maps."

- 3. Insert the CPU subsystem into the card cage.

- Remove any coverings or enclosures to access the front opening of the VMEbus card cage. If you are also installing the optional graphics assembly, remove additional coverings or enclosures as needed to get access to the rear of the VMEbus backplane.

- The CPU must be used as the VMEbus system controller. Remove any boards from the leftmost slots as the CPU subsystem must reside in those slots.

- Orient the CPU subsystem so that the component side (top) faces toward the right with respect to the front panel. Align each board in its respective slot. (See Figure 3-2.)

Pull back the captive screws located on the front panel near the ejector tabs so that the screws do not get caught when you slide in the subsystem. - H -

Hardware Installation

Figure 3-2 Installing the CPU Subsystem

- Slide the subsystem back along the slots and seat it into the backplane with a firm, steady pressure. The subsystem should slide smoothly along the slots and fit snugly into the backplane connectors.

- Secure the subsystem to the card cage using the captive screws located near the extractor tabs at the top and bottom of the faceplate.

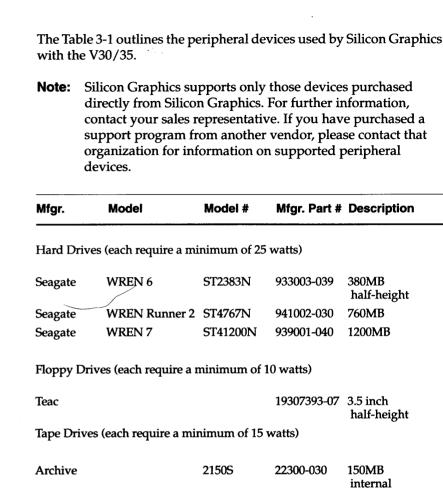

- 4. Make sure the VMEbus backplane is properly jumpered. (See sample configuration in Figure 3-3)

- If necessary, remove any coverings or enclosures to get access to the rear of the VMEbus backplane. (Some VMEbus backplanes may be jumpered from the front.)

- With the backplane exposed, replace the single IACK and the four BUS GRANT jumpers from each of the empty slots between the CPU subsystem and your other cards.

Hardware Installation

### Installing the Graphics Subsystem

Keep the backside VMEbus backplane accessible if you are going to install a graphics subsystem.

The graphics subsystem should be installed when the installation of the CPU subsystem is completed and before you load the operating software. Please refer to the system integrator's guide included with your graphics subsystem for additional information.

### **Installing Additional VMEbus Devices**

At this time you can install any additional VMEbus-resident devices by following the manufacturer's instructions.

### **Installing Airflow Restrictors**

Be sure to properly install airflow restrictors in any empty VMEbus slot after you have installed all your VMEbus devices. The airflow restrictors are needed to maintain a sufficient airflow within the card cage.

### **Connecting Peripheral Devices**

With the power to the card cage still off, you are now ready to connect peripheral devices to your V30/35. In order to install the software, you need a SCSI hard disk and a CD-ROM device or a SCSI tape drive.

If you have already installed a graphics subsystem, you also need the following devices to install and boot the IRIX operating system:

- a Silicon Graphics graphics keyboard and mouse

- a high-resolution 1280 by 1024 monitor

If you have not installed a graphics subsystem, you need an ASCII terminal connected to serial port 1 for the power-on tests.

At this time you can also connect the Ethernet and a printer or other Centronics-compatible device. (The Ethernet port may be used to load the software across a network.)

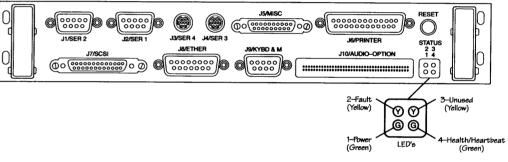

The proper ports and connectors for these peripherals are shown in Figure 3-4. For pinout information, see Appendix C, "Pinouts for Peripheral Connectors."

| ( |                                                                                                                                       | <b>O</b> |

|---|---------------------------------------------------------------------------------------------------------------------------------------|----------|

| ( | J/SCSI         J&ETHER         JANYED & M         J10/AUDIO-OPTION         23<br>1 4           (0 0 000000000000000000000000000000000 | ļ        |

Figure 3-4 Connectors for Peripheral Devices

### **Supported Devices**

The V30/35 works with any Personal IRIS workstation peripheral device sold by Silicon Graphics. SCSI devices not provided by Silicon Graphics as part of its standard product line may require a new driver and are not guaranteed to work with the V30/35.

|                              | 19307393-07    | 3.5 inch<br>half-height          |

|------------------------------|----------------|----------------------------------|

| ives (each require a minimur | n of 15 watts) |                                  |

| 2150                         | S 22300-030    | 150MB<br>internal<br>half-height |

| 2150                         | E 21525-125    | 150MB                            |

380MB

760MB

1200MB

half-height

external 1300MB Archive 4320NT 27245-006 DAT half-height

Table 3-1 Silicon Graphics Peripheral Devices

Archive

### **Checking the Installation**

When all of the desired boards are installed, you are ready to inspect the card cage. After verifying that the installation is correct, you can replace any coverings or enclosures to secure the cage. (Depending on the physical layout of your VMEbus card cage, you may need to replace covers or enclosures before connecting your peripheral devices.) ES

E 3

ES

ES

12

21

When inspecting the card cage, ensure that:

- Assemblies and boards are seated properly and secured.

- Unoccupied slots between VMEbus cards are correctly jumpered.

- For each graphics subsystem, the GE board is connected to the appropriate CPU subsystem.

- Connections and jumpers are tight and solid.

- Peripheral connectors are securely attached.

- CPU jumpers and switches are properly configured for your environment.

- Air flow inhibitors are properly installed (where appropriate) in unoccupied slots.

- You follow the guidelines for maintaining EMI compliance as outlined under the heading "Electromagnetic Interference (EMI) Compliance" earlier in this chapter.

Once you verify that the hardware is properly installed, you can power up the VMEbus card cage.

### Powering Up the System

Connect the card cage and any peripherals that require it to a grounded source of AC power, and switch on the card cage to power up the system.

When the system first comes up, the CPU performs a number of diagnostic tests on itself. The CPU diagnostics are displayed on the ASCII terminal if the *bootmode* remains on its default value, *bootmode=d*.

The CPU diagnostics are not displayed if the *bootmode* has been reset so that *bootmode=c*.

After the CPU diagnostic tests are completed, a series of graphics subsystem tests are run if a graphics subsystem is present. The results of the graphics diagnostic tests appear on an attached graphics monitor if the *console* value remains on its default value, *console=g*.

If no graphics monitor is attached, the results of the graphics test appear on the ASCII terminal. The test results also appear only on the ASCII terminal if the console value has been reset so that *console=d*.

**Note:** See "Preparing the Standalone Environment" in Chapter 4 for information on setting the *console* and *bootmode* variables.

These tests take a minute or two to complete. In case of error or failure, contact your support representative or the organization from which you purchased your support program. If you have not purchased a support program, contact your sales representative to arrange for support. Do not attempt to correct or repair any boards or components. Refer to Chapter 4, "Diagnostics" for an explanation of the power-on self-tests.

V30/35 System Integrator's Guide

When the self-test completes successfully, you see the following message on the system console:

Starting up the system ...

To perform system maintenance instead, press <Esc>

Press <BBC> to bring up the System Maintenance menu. At this point, the hardware installation is complete; you are ready to install software.

Chapter 4

## **Installing System Software**

This chapter explains how to install system software onto the V30/35 CPU subsystem directly from tape or CD-ROM. The procedure takes about an hour to complete.

Standard software for the V30/35 includes the IRIX Execution Only Environment and the optional IRIS Development Option (ido). The installation process involves loading the system software onto disk using the standalone inst(1M) program. For additional background information about the inst program and the installation process in general, see the IRIS Software Installation Guide.

Alternatively, you can install system software over a network using a tape drive or CD-ROM attached to a remote host. For multiple installations, you can copy the software onto a remote host's disk using *distcp*(1M), and then install it over the network. See the *Personal* System Administration Guide for information on installing software over a network.

# Installing Additional Software

You may want to install additional software that you receive from Silicon Graphics or another company that writes application software or device drivers. Always follow the instructions that come with the software to make sure you install new software correctly.

•

14 555

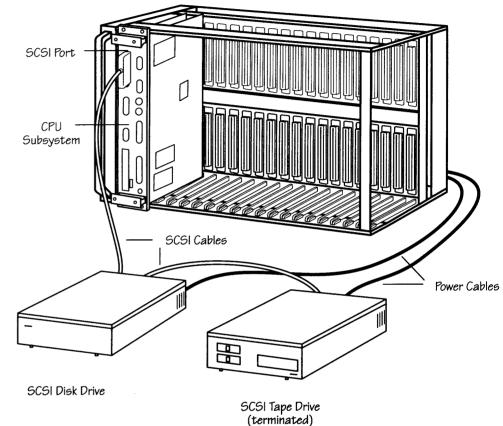

Figure 4-1 shows one possible system configuration using external SCSI disk and tape drives. Remember to power down the card cage before connecting or disconnecting the drives.

Figure 4-1 Installing Software with External SCSI Tape and Disk Drives

4-3

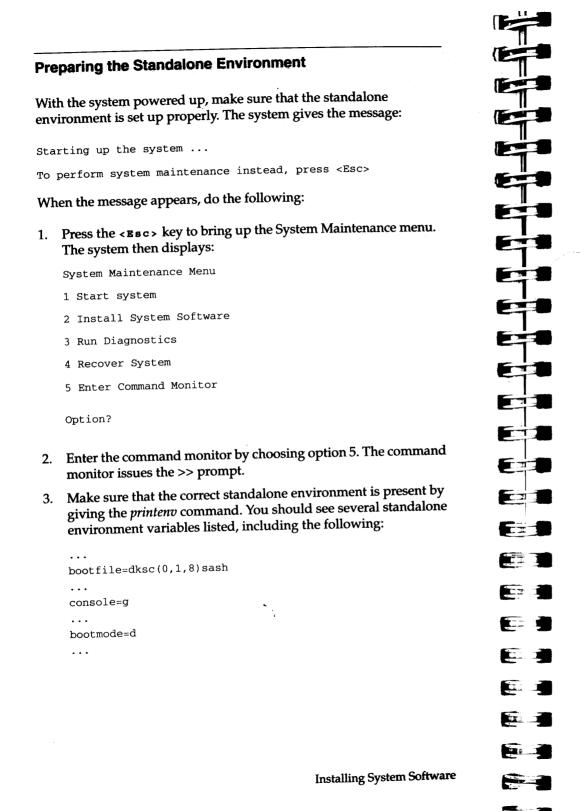

4. The *bootfile* variable determines the device from which the system is to boot. In order to install system software using a local tape drive or CD-ROM device, this variable must have the value shown. If the *bootfile* variable is not correct, use the *setenv* command to assign the correct value to this variable:

setenv bootfile dksc(0,1,8)sash

- **Note:** For additional information on the *bootfile* variable and other issues pertaining to the PROM monitor see the *IRIX Site Administrator's Guide.*

- 5. The *console* environment variable indicates that the system console is either the graphics monitor (g or G) or an ASCII terminal (d); this means that the console is attached to the graphics (g) port or the diagnostics (d) port. The graphics monitor is the default setting; however, if you do not have a graphics subsystem in operation, the software automatically switches to an ASCII terminal.

If you wish to manually set the console variable, type:

setenv console g

for a graphics monitor, or type

setenv console d

for an ASCII terminal.

- **Note:** The upper-case graphics monitor variable *G* displays a Silicon Graphics logo in the upper left corner of the screen, the lower-case *g* does not; this is the only difference between the two.

- 6. The *bootmode* variable determines whether the CPU diagnostics are displayed when the system is booted. The default variable, *bootmode=d*, displays the diagnostics. You can manually set this variable by typing:

setenv bootmode d

If you do not want the diagnostics displayed, type:

setenv bootmode c

7. When these variables are set to the correct values, type init to return to the System Maintenance menu. You are now ready to begin installing system software.

### Installing the System Software

You can install the system software from a local drive attached directly to the V30/35 subsystem or from a remote drive over a network.

E

Installing System Software

#### To install the system software:

- 1. Insert the eoe1 tape into the tape drive, or the CD-ROM into the CD-ROM drive.

- 2. Choose option 2, "Install System Software," from the System Maintenance menu. When you do, the system displays:

Installing System Software ... Press <Esc> to return to the menu.

Insert the installation tape, then press <enter>:

- Press the <Enter> key to load the miniroot and *inst* program. This takes about 10 minutes. When *inst* is installed and ready, the system displays:

- Inst Main Menu

- from [source]

list [keywords]

go

install [keywords] [names]

remove [keywords] [names]

keep [keywords] [names]

step [keywords] [names]

versions [args]

help [topic]

admin

quit

- Inst>

- Choose option 3 to automatically install the entire eoel distribution. If you are installing from CD-ROM, skip steps 5 and 6.

- 5. If you are installing from tape, in about 20 minutes you are asked:

- Is there more software to install?

Answer y to this question to proceed with the next tape.

6. You next see the prompt:

Insert the next tape, then press <enter>:

Replace the eoel tape with the eoel tape and press<Bnter>. This tape takes about 15 minutes to install. Repeat this process for the dev tape (about 5 minutes).

7. When you are done, answer n when *inst* asks:

Is there more software to install?

When you answer n to this question, *inst* may ask if it should automatically reconfigure the kernel. Answer y if so prompted.

The software is now installed.

8. Answer y when *inst* asks if you want to start the operating system. This reboots the system.

For additional information on installing the system software, please refer to the *IRIS Software installation Guide*.

### Chapter 5

### **Diagnostics**

The V30/35 provides extensive support for testing both CPU and graphics subsystems. The system comes with two sets of diagnostics:

- a basic set of power-on tests ensures that the system can bootstrap and run standalone programs

- the interactive diagnostics environment (IDE), a standalone program that runs in the PROM monitor through the standalone shell (*sash*)

This chapter describes both sets of diagnostics and the various tests they perform. If you need general information about the PROM monitor and the standalone shell, please refer to the *Personal System Administration Guide* that came with your system.

### **Power-on Tests**

Power-on diagnostics are performed automatically whenever the system is powered up. The "Fault" (yellow) light-emitting diode (LED) flashes while these tests are under way. The LED's located on the front panel of the V30/35 are illustrated in Figure 5-1.

If the memory test detects a bad SIMM module, the failure message displays an IDE alphanumeric symbol to indicate the specific byte that needs replacing as well as the SIMM bank in which it's located. The SIMM bank can be located on either the CPU board or the optional Memory Expansion Board. Table 5-1 outlines the IDE symbols and the physical location of the byte they represent.

| IDE<br>Symbol | Bank   | Byte   | Board                  |

|---------------|--------|--------|------------------------|

| A1            | bank 0 | byte 3 | CPU board              |

| A2            | bank 0 | byte 2 | CPU board              |

| A3            | bank 0 | byte 1 | CPU board              |

| A4            | bank 0 | byte 0 | CPU board              |

| B1            | bank 1 | byte 3 | memory expansion board |

| B2            | bank 1 | byte 2 | memory expansion board |

| B3            | bank 1 | byte 1 | memory expansion board |

| B4            | bank 1 | byte 0 | memory expansion board |

| C1            | bank 2 | byte 3 | memory expansion board |

| C2            | bank 2 | byte 2 | memory expansion board |

| C3            | bank 2 | byte 1 | memory expansion board |

| C <b>4</b>    | bank 2 | byte 0 | memory expansion board |

#### Table 5-1IDE SIMM Failure Symbols.

To locate the correct SIMM module for replacement on the CPU board, refer to Appendix E, "V30/35 Component Layout." To locate the SIMM modules on the optional Memory Expansion Board, please refer to the documentation that came with the memory upgrade.

L D

ŭ.

Diagnostics

### **Using IDE Diagnostics**

The interactive diagnostics environment includes comprehensive tests for all of the I/O interface controllers and ports, the graphics subsystem (subsystem 0 only) and its various components, main memory, and other system components.

You can use the IDE program to verify that your system hardware is performing properly or to isolate hardware malfunctions. The IDE program must be loaded into the monitor from disk, from tape, or over the network before you can run it. If you have installed the operating system as described in Chapter 4, the IDE program is on disk and ready to run.

### Starting IDE in Terse or Verbose Mode

You can run the IDE program in either terse or verbose mode. To start the diagnostics program in terse mode select option 3, "Run Diagnostics," from the System Maintenance menu. While in terse mode, the program first reports on the hardware configuration and then runs silently, displaying error messages only when a diagnostic fails on an installed board or component.

When IDE runs in terse mode, you cannot interrupt the test suite. You must let it run to completion or reset the system.

You must run IDE in verbose mode if you wish to use it interactively. In verbose mode, you can interrupt the standard test suite at any time by pressing <ctrl-c>; the program then issues the ide>> prompt and accepts the commands described in the next section, "IDE Interactive Commands."

#### To start IDE in verbose mode:

- 1. Enter the command monitor by selecting option 5 on the System Maintenance menu.

- 2. Type ide fe in response to the command monitor's >> prompt.

In verbose mode, the IDE program reports on each test it attempts, along with the success or failure of that test.

#### **IDE Standard Tests**

In either terse or verbose mode, IDE first performs an initial inventory of subsystems that are present (the equivalent of the *hinv* PROM monitor command). The initial output you see looks something like this:

Memory size:xx MBytes Instruction cache size:xxxxx Data cache size:xxxxx CPU board:xxxxx System options:xxxxx

Graphics: xxxxx SCSI disk:dksc(0,1)

Once the program starts, it runs a standard test suite. These tests cover all major subsystems and components, taking about 25 minutes to complete.

The standard test suite has two parts. The first part tests the CPU subsystem. The second part tests the graphics subsystem if one is present. Some tests apply only to specific models or options; if IDE attempts to access a piece of hardware that is not supported on this system, IDE reports the device as missing and continues with the next test.

**Note:** Certain tests take over the graphics display monitor. When these tests are running, the graphics monitor may go black or display various shapes and patterns. This is no cause for alarm. When the tests finish running, the monitor resumes the console display.

#### V30/35 System Integrator's Guide

Diagnostics

E

EI

1983

CPU tests can fail with any of the following errors. If IDE reports one of these errors, contact your support provider.

53

Diagnostics

Failure detected on CPU board. Failure detected on FPU. Failure detected on VME device. Failure detected on SCSI device[s].

### **IDE Interactive Commands**

The interactive commands available under IDE allow you to check the operation of the boards and components that make up the system.

The IDE interactive commands are classified by subsystem. Those that pertain to the CPU subsystem are listed below. The IDE commands for the graphics subsystem are listed in the integrator's guide that came with it.

#### **General Commands**

The following general commands are used to modify more specific commands pertaining to either the CPU or graphic subsystem:

{*cmd*; *cmd* ... }

Command may be grouped between { }.

? Provides on-line help for each IDE command.

exit Exit IDE.

if [expr] cmdl [else cmd2] [fi] Execute cmdl if expr is true, cmd2 otherwise; fi is optional.

### repeat n cmd

Repeat cmd n times.

**report** [*n*] Set verbose level, where *n* represents a scale of one to four, with four being the most verbose. wait ["message"] Display the indicated message, if any, and wait for an <Enter> to be typed in on the keyboard. while [expr] cmd Repeat *cmd* while *expr* is true. **CPU Subsystem Tests** audio DSP audio diagnostics (run only if the audio option is present). buffoff Turn off message buffering. Messages are not displayed when running IDE on a graphics terminal. *buffon* stores the messages which are then displayed when IDE is completed and the graphics terminal is automatically reset as a console window; otherwise, messages are discarded. buffon Turn on message buffering. cache2 Instruction/data caches data test. cache3 Instruction/data caches tag test. cache4 Instruction/data caches random refill test. cdsio1 CDSIO data loopback test. cdsio2 CDSIO interrupt test. checksum range

Calculate checksum for the specified range of addresses.A range can be specified in one of two forms:start:endstarting address up to but not including<br/>the ending addressstart#countstarting address up through count words

V30/35 System Integrator's Guide

|              | decimal, with th<br>K<br>P                       | e specified in either hexadecimal or<br>e following scaling abbreviations:<br>1024 bytes<br>4096 bytes (page)<br>1048576 bytes (10242 bytes) |

|--------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| clock        | Real-time clock                                  | counters carry test.                                                                                                                         |

|              | <b>m</b><br>CPU DSP SRAN<br>present).            | I data test (runs only if audio option is                                                                                                    |

| dram [–p] [1 | range]<br>Walking bit and<br>- <b>p</b><br>range | address uniqueness tests:<br>Perform parity test instead<br>Same as for checksum command; must<br>be greater than 4MB                        |

| dsp56        | DSP560001 diag                                   | gnostics.                                                                                                                                    |

| duart [ –ieX | (]<br>DUART interna<br>X<br>-i<br>-e             | l/external loopback test:<br># of DUART port tested ( 0 – 6)<br>Internal loopback (the default)<br>External loopback                         |

| emfail       | Produce "Elect                                   | ronics Module" failure message.                                                                                                              |

| enet1        | Ethernet data/a                                  | address port register test.                                                                                                                  |

| enet2 [–ie]  | Ethernet intern<br>–i<br>–e                      | al/external loopback test:<br>Internal loopback (the default)<br>External loopback                                                           |

| finflgs      | Test the DK3 fi                                  | nish flags.                                                                                                                                  |

| fpu          | Run floating-p                                   | oint unit diagnostics.                                                                                                                       |

| -            | Print memory                                     | diagram.                                                                                                                                     |

| hinv         |                                                  | entory (same as <i>hinv</i> PROM monitor                                                                                                     |

| hpc1         | HPC1 registers                                   | s and fifos.                                                                                                                                 |

|              |                                                  |                                                                                                                                              |

|              |                                                  |                                                                                                                                              |

| iganop [ ik | <pre>  -W] [-c   -r] Instruction cache galloping column/row test:</pre>                                        |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

|             | -R Read only                                                                                                   |  |  |  |

|             | -W     Read-write       -c     Column test                                                                     |  |  |  |

|             | -r Row test                                                                                                    |  |  |  |

| initgr      | Initialize graphics board (includes microcode<br>downloading - runs only if graphics subsystem is<br>present). |  |  |  |

| int2        | Init2 interrupt mask registers.                                                                                |  |  |  |

| ldram [–p]  | Lower (0-4Mbyte) DRAM walking bit and address uniqueness tests:                                                |  |  |  |

|             | -p Perform parity test instead.                                                                                |  |  |  |

| led 0 1 2   | Turn health LED on or off.                                                                                     |  |  |  |

| memtest     | CPU memory test.                                                                                               |  |  |  |

| nvram1      | EEPROM address test.                                                                                           |  |  |  |

| nvram3      | EEPROM data test.                                                                                              |  |  |  |

| nvram4      | EEPROM ID test.                                                                                                |  |  |  |

| nvram5      | EEPROM pin signals test.                                                                                       |  |  |  |

| parity      | Parity test.                                                                                                   |  |  |  |

| print1      | Centronics printer connection test.                                                                            |  |  |  |

| print2      | Centronics printer interface DMA test.                                                                         |  |  |  |

| print3      | Centronics printer loop back test.                                                                             |  |  |  |

| resetcons   |                                                                                                                |  |  |  |

|             | Reset graphics console (runs only if graphics subsystem is present).                                           |  |  |  |

| scope [men  | nory   icache   dchace   scsi  <br>enet   rtc   duart0   duart1   duart2]                                      |  |  |  |

|             | CPU scope loop.                                                                                                |  |  |  |

| sdma        | Stride DMA test.                                                                                               |  |  |  |

| scsi        | Test SCSI interface controller.                                                                                |  |  |  |

V30/35 System Integrator's Guide

E .

EI

ES

E

EI

EI

Diagnostios

#### test subcmd

| md         |                                               |  |

|------------|-----------------------------------------------|--|

| Memory     | tests; <i>subcmd</i> is one of:               |  |

|            | wiuf] range                                   |  |

|            | Walking bit test                              |  |

| parity [-l | bhwiuf] range                                 |  |

|            | Parity test                                   |  |

| addr (-w   | iuf] range                                    |  |

|            | Address uniqueness test                       |  |

| wire [gr   | nnpv] index page frame                        |  |

|            | Set up address mapping for addresses in       |  |

|            | the ranges 0x0–0x7fffffff and                 |  |

|            | 0xc0000000-0x0ffffffff                        |  |

| Argumer    | its to the data, parity, and addr subcommands |  |

| are:       |                                               |  |

| -b         | Load and store bytes.                         |  |

| -h         | Load and store halfwords.                     |  |

| -w         | Load and store words (the default).           |  |

|            | (The –b, –h, and –w options do not apply      |  |

|            | to address ranges for other commands          |  |

|            | such as checksum, dram, or ldram.)            |  |

| -i         | Invert the binary sense of the test; use      |  |

|            | walking zero instead of walking one; use      |  |

|            | complemented address uniqueness               |  |

|            | instead of uncomplemented                     |  |

| -u         | Repeat test until an error occurs             |  |

| -f         | Continue repeating (forever), despite         |  |

|            | errors                                        |  |

|            |                                               |  |

• .

Diagnostics

range

a range of addresses taking one of two forms: start addr:end addr

(Specifies a range from start\_addr through,but not including, end\_addr.)

start\_addr#count

Specifies a range from start\_addr through that address plus the number of units specified by count; unit size is determined by -b, -h, or -w.

An address can be specified in either hexadecimal or decimal, with the following scaling abbreviations:

**K** 1024 units

P 4096 units (page)

M 10242 units

For instance, the command: test addr 0xa01M#0x1M

performs an address uniqueness test over the one megaword (4Mbyte) range starting at address 0xa0100000

Arguments to the **wire** subcommand are:

.

| 0          |                                           |

|------------|-------------------------------------------|

| -g         | Global mapping (don't compare             |

|            | TLBPIDs).                                 |

| -m         | Allow writes at virtual addresses         |

|            | given by <i>page</i> .                    |

| <b>-</b> n | Do not look in cache after translating an |

|            | address.                                  |

| - <b>p</b> | Purge page map of entries.                |

| - <b>v</b> | Mark map entry as valid for address       |

|            | translations.                             |

| index      | A map entry index between 0 and 63.       |

| page       | A page number (five hexadecimal digits).  |

| frame      | A page frame number (five hex. digits)    |

|            | into which addresses beginning with       |

|            | page's five digits are to be translated.  |

|            |                                           |

V30/35 System Integrator's Guide

٦.

For instance, the following commands set up a walking bit test on two pages of mapped memory using pages 0 and 1:

> test wire -pvm 0 0 0x18 test wire -vm 1 10x19 test data -b 0#2p

| timer | Timer frequency test.                          |

|-------|------------------------------------------------|

| tlb   | Translation lookaside buffer (TLB) tests.      |

| utlb  | UTLB miss exception test.                      |

| vme1  | VME interrupt test using ESDI disk controller. |

| vme2  | VME DMA test using ESDI disk controller.       |

| xscsi | Exercise all SCSI disk drives found.           |

### Chapter 6

### **The VMEbus**

The VMEbus is an asynchronous bus supporting a large variety of computer peripherals and CPUs. Originally designed in Europe as a primary computer bus for the Motorola MC68000 series microprocessor, the VMEbus is used today as a peripheral bus by many manufacturers, including Silicon Graphics.

The V30/35 uses the VMEbus as a peripheral bus; however, not all *modes* of the VMEbus are supported.

This chapter provides an overview of VMEbus definitions and functionality. It is not intended to be used as a VMEbus specification, but rather as a source of general information about the VMEbus and its capabilities.

**Note:** VMEbus functionality supported by the V30/35 is described in Chapter 7, "CPU Subsystem Architecture."

### **VMEbus History**

With the introduction of the MC68000 family of processors in the early 1980's, Motorola introduced the VERSAbus which matched the different address and data modes of the MC68000. However, the VERSAbus suffered from some important design flaws: the card sizes and connectors to the bus were very large and awkward.

Meanwhile, Motorola offices in Germany had developed a different bus for the MC68000. The sizes of the cards, form factors, and the bus connectors were considered better than those designed for the VERSAbus. The form factor from Europe (EuroCard) was married with the electrical specifications of the VERSAbus and the VMEbus (Versa Module Eurocard) was born.

The VMEbus

Since that time the VMEbus has had two revisions and is now at Revision C. The IEEE has given the number of IEEE-P1404-1987 for the VMEbus. The IEC number is IEC-821BUS.

Note: As the V30/35 System Integrator's Guide goes to print Revision D of the VMEbus is anticipated but has not yet been released. Several new capabilities expected in Revision D will be referred to in this chapter.

### **VMEbus Signals**

The signals of the VMEbus can be divided into 4 groups:

- data transfer bus (DTB)

- arbitration of the DTB ٠

- interrupt bus ٠

- utility bus ٠

The DTB performs data transfers and defines the protocols necessary to deal with access timing, address space, and data size considerations. The arbitration of the DTB is based on a MASTER/SLAVE concept and supports several bus scheduling algorithms. The interrupt bus is prioritized into seven levels. The utility bus handles power and control lines such as ACFAIL and SYSRESET.

Figure 6-1 illustrates the VMEbus signal pathways.

V30/35 System Integrator's Guide

### **DTB Bus**

The VMEbus uses a master/slave concept. The MASTER initiates data transfers. Only the MASTER actually moves data across the bus. The SLAVE is passive and responds to the MASTER.

67

ГЪ.,

6

The VMEbus

The DTB is a non-multiplexed bus consisting of:

- 24 or 32 address lines

- 16 or 32 data lines

- two data strobe lines

- an address strobe line

- a write line

- a long word line

- a data transfer acknowledge line

The DTB supports three address widths: A32, A24, and A16. The address space sizes are 4 GBytes, 16 MBytes and 64 KBytes respectively.

These address spaces are referred to as "extended" for A32, "standard" for A24, and "short" for A16. The DTB also uses six address modifier lines which determine the access type.

**Note:** Rev D of the VMEbus supports A64 using data lines.

| Modifier Code | Function                          |

|---------------|-----------------------------------|

| 0x3f          | A24 supervisory block transfer    |

| 0x3e          | A24 supervisory program access    |

| 0x3d          | A24 supervisory data access       |

| 0x3b          | A24 non-privileged block transfer |

| 0x3a          | A24 non-privileged program access |

| 0x39          | A24 non-privileged data access    |

| 0x2d          | A16 supervisory access            |

| 0x29          | A16 non-privileged access         |

| 0x0f          | A32 supervisory block transfer    |

| 0x0e          | A32 supervisory program access    |

| 0x0d          | A32 supervisory data access       |

| 0x0b          | A32 non-privileged block transfer |

| 0x0a          | A32 non-privileged program access |

| 0x09          | A32 non-privileged data access    |

#### Table 6-1 VMEbus Address Modifiers

The VMEbus supports two operation modes: supervisory and non privileged. The two modes allow a multi-tasking operating system to have access protection by employing the concept of protected memory regions. Program text and data sections could be separated and bus signals would produce an error if an incompatible access occurred. The VMEbus modifier codes reflect this concept with supervisory and non-privileged access along with block, program, and data access.

The DTB supports three data path sizes: D8, D16, and D32 which provide 8 bits, 16 bits and 32 bits of data transfer in each address space.

**Note:** Revision D of the VMEbus will support A64 providing 64 bits of address space. The additional 32 bits are gained by using the data lines (multiplexing) to present the address.

The DTB also has the ability to access non-aligned bytes and do three byte (tri-byte) transfers.

The DTB supports read, write, address only, and read-modify-write operations. Read-Modify-Write allows a MASTER to read data, modify it and write it back without releasing the bus.

Since the VMEbus is asynchronous, a non-responsive SLAVE could hang the bus, so the system controller usually incorporates a watch dog timer to timeout the bus causing a bus error. A mismatch between data transfer size of the SLAVE and the MASTER can also cause a bus error. In either case, the bus error (BERR\*) line is asserted.

**Note:** A \* indicates that low level logic is true.

Descriptions of the various DTB cycles are outlined in the following subsections. These descriptions are provided as general reference information; they are not intended to provide specific VMEbus protocols and specifications.

#### Write Cycle

The write cycle begins when the MASTER gains control of the bus. The MASTER places the address and the address modifier on the address bus to indicate the type of access and address space (i.e. A32, A24, or A16). The address strobe (AS\*) is asserted to indicate a stable address.

The MASTER specifies data direction, in this case driving WRITE\* low. The MASTER places the data on the data bus and then asserts the data strobes DS0\* and DS1\*. The combination of DS0\*, DS1\*, A01, and LWORD\* determines the data size (i.e. D32, D16, or D8). (Note that DS0\*, DS1\*, A01, and LWORD are used to select which byte location(s) within the 4 byte word are accessed during the data transfer.)

The SLAVE reads the data and responds by driving the DTACK\* line low. The MASTER then releases the address lines, modifier line, data lines, and LWORD\* line and drives DS0\*, DS1\* and AS\* to high. Finally, when the SLAVE receives DS0\*, DS1\*, and AS\*, it releases DTACK\* to complete the cycle. If a mismatch in the data transfer size or other errors occur, the SLAVE asserts BERR\* and the bus error terminates the cycle.

24

. .

### Unaligned Transfer (UAT) Cycles

the data lines and DTACK\* to complete the cycle.

Unaligned transfer cycles occur in the same way as the read and write cycles described above. Data bytes for unaligned transfers are selected by the DS0\*, DS1\*, A01, and LWORD\* combination. Unaligned transfers include:

The read cycle is the same as the write cycle except the MASTER drives WRITE\* high to indicate a read cycle and the SLAVE places the

data on the data bus in response to the data strobes (DS0\*and DS1\*).

The SLAVE asserts DTACK\* when the data is stable and the MASTER

reads it. The MASTER then releases the address lines and drives DS0\*, DS1 and AS\* high. Finally, the SLAVE receives these lines and releases

- double byte (1-2)

- triple byte (0-2)

**Read Cycle**

• triple byte (1-3)

### Read Modify Write (RMW) Cycle

The Read-Modify-Write cycle starts as a normal read cycle. When the SLAVE asserts DTACK\* the MASTER only releases the data strobes (DS0\*-DS1\*) while the assertion on address strobe (AS\*) is maintained. This indicates a RMW cycle. The MASTER then, after modification, writes the data back with a normal write cycle.

### **Block Transfer (BLT) Cycles**

The block transfer cycle starts as a normal read or write cycle. When the first data transfer is complete the MASTER does not allow address strobe (AS\*) to go high. Instead it repeatedly drives data strobes(s) (DS0\* and DS1\*) low in response to the data transfer acknowledge (DTACK\*) from the SLAVE. It then transfers data to and from sequential memory locations in ascending order in blocks of up to 256 bytes for D32.

| <b>Note:</b> Revision D of the VMEbus will support D64 providing data transfers of up to 2048 byte blocks.                                       |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                  |    |

| Address Only (AO) Cycles                                                                                                                         |    |

| An Address Only cycle allows slow peripherals to prefetch data.                                                                                  |    |

| This case is like the write or read cycle except no data is transferred<br>and the data strobes are never asserted. Only the address and address | 63 |

| strobes are used. The MASTER releases the bus without receiving a BERR* or DTACK*. This allows the MASTER's local memory decoder                 |    |

| to work in parallel with the SLAVES's address decoder and thereby, in some cases, speed up the transfer.                                         |    |

|                                                                                                                                                  |    |

| Bus Arbitration                                                                                                                                  | 23 |

| The VMEbus is a multi-master system and supports bus arbitration to:                                                                             |    |

| • Prevent simultaneous use of the bus by two masters.                                                                                            |    |

| • Schedule requests for multiple masters for optimum use of the bus.                                                                             |    |

| There are four bus request lines BR0* to BR3* with BR3* used as the                                                                              |    |

| highest priority. When the bus is granted to a particular request level (0-3,) the bus grant signal is daisy-chained down the backplane via the  | EJ |

| BGxIN and BGxOUT* (where x is 0-3). The bus grant for a particular                                                                               | EI |

| level "x" is brought into the card via BGxIN* and is sent on to the nearest neighbor (the next slot to the right) via BGxOUT. If a MASTER        |    |

| requires the bus and is a requester at level "x", it does not pass<br>BGxOUT* but instead asserts the bus busy line (BBSY*). This daisy          |    |

| chain system means that for each bus request level, the requesting<br>MASTER closest to the arbiter (system controller) gains control of the     | EI |

| bus.                                                                                                                                             |    |

| The MASTER will relinquish the bus based on a policy of Release On Request (ROR) or Release When Done (RWD). ROR requires the                    |    |

| MASTER to relinquish the bus only when another request is pending.<br>RWD causes the MASTER to release the bus when it has finished its          |    |

| current operation. This policy is built into the VMEbus MASTER.                                                                                  |    |

Modern VMEbus MASTERS often offer the ability to select RWD or ROR.

The policy of ROR or RWD can impact system performance. ROR MASTERs tend to hold the bus and monitor the bus request lines (BR0\*-BR3\*) even if they don't need the bus. ROR is a good policy for MASTERs which make frequent bus accesses and do not want to spend the time arbitrating for the bus on each access. This of course means that other MASTERs in the system will normally find the bus busy and will have to wait for arbitration by the system controller.

RWD MASTERs tend to release the bus to allow rearbitration on each bus access. This policy is good for MASTERs which may make fewer bus accesses or with systems where multiple MASTERs need more equal access to the bus.

There are many algorithms that can be used to arbitrate the bus; only two are addressed here: round robin arbitration and priority arbitration. Round Robin (RRS) arbitration assigns the bus on a rotating priority basis. When the bus is granted to the requester on the bus request line BRx\*, the highest priority for the next arbitration is assigned to bus request line BR(x-1)\*. The bus is rotated from BR3\* through BR0\* and then back to BR3\* again.

Prioritized (PRI) arbitration assigns the bus according to a fixed priority scheme where each of the four bus request lines has a priority from highest (BR3\*) to lowest (BR0\*). This means the higher priority devices could potentially "lock-out" lower priority devices.

Another priority scheme which is a subset of PRI is single level (SGL). SGL only accepts request on BR3\* and relies on the daisy-chain (BG3IN\*, BG3OUT) as the arbitration mechanism for the requests. Many system controllers offer the ability to select between RRS and PRI or other arbitration schemes.

### Interrupt Handling

The VMEbus allows seven prioritized interrupt request levels (IRQx). These are IRQ1\* to IRQ7\* with IRQ1\* the lowest and IRQ7\* the highest. Once an interrupt is asserted and the bus is granted to a handler, a 3 bit code, which identifies the interrupt level being acknowledged, is placed on address bits 1-3 and IACK\* and AS\* are asserted. The handler also indicates the status data size (D32, D16, or D8) via the data strobes. IACK\* runs the full length of the backplane and is connected to IACKIN\* on slot 1. When driven low the IACKIN\* line causes the daisy-chain driver located in slot 1 to propagate a falling edge down the backplane via the interrupt acknowledge daisy-chain (IACKIN\* AND IACKOUT\*).

Each board compares the interrupt level with the interrupt level it asserted and IACKIN\*. If the board does not have an interrupt outstanding or does not match the interrupt level, the IACKIN\* is passed to the next board via IACKOUT\*. If the interrupting board matches the interrupt level, it does not pass on IACKOUT\* and places a status on the data bus.

The size of the status word is determined by the interrupt handler. Note that even though the VMEbus definition allows D8, D16, or D32 size status, most systems only use D8. Even if an interrupting board can use D16 or D32 it must respond to the size declared by the interrupt handler or declare a bus error (BERR\*).

VMEbus boards have two methods of interrupt acknowledge:

- release on acknowledge of interrupt

- release on register access.

With release on acknowledge, the interrupting device de-asserts the IRQ when the controller acknowledges the interrupt. That is, when the interrupting device transfers its interrupt vector, the assertion on IRQ is released.

With release on register access, the interrupting device does not remove its IRQx request until a register on the board has been accessed or modified. Therefore, after the interrupt vector has been transferred, the device still asserts IRQx. The utility bus supplies power, system reset signals, system clock, power fail signals, and I/O pins. The VMEbus specifies voltages of: +5V, +12V, -12V, and a standby +5V.