# SA4000 Fixed Disk Drive

# **Table of Contents**

| 1.0 | Introd | uction                                                            | 1  |

|-----|--------|-------------------------------------------------------------------|----|

| 1.0 | 1.1    | General Description                                               | 1  |

|     | 1.2    | Specifications Summary                                            | 2  |

|     | 1.2.1  | Performance and Function Specifications                           | 2  |

|     | 1.2.1  | Physical Specifications                                           | 2  |

|     |        | Reliability Specifications                                        | 2  |

|     | 1.2.3  | Reliability Specifications                                        | _  |

| 2.0 | 2.0    | This section will functionally describe the major circuits of the |    |

|     |        | SA4000. For interface timing. Refer to the SA4000 0EM manual      | _  |

|     |        | Part Number 39005                                                 | 3  |

|     | 2.1    | Power on Reset (POR)                                              | 3  |

|     | 2.2    | Stepping                                                          | 4  |

|     | 2.3    | Read Operation                                                    | 7  |

|     | 2.4    | Write Operation                                                   | 9  |

|     | 2.5    | Error Circuit                                                     | 10 |

| 3.0 | 3.0    | Troubleshooting Techniques                                        | 11 |

| 4.0 | 4.0    | Test Points and Pin Locations                                     | 19 |

| 5.0 | 5.0    | Component Locations                                               | 23 |

| 6.0 | 6.0    | Schematic Diagrams                                                | 28 |

|     |        | LIST OF FIGURES                                                   |    |

| 4   | ο.     | •                                                                 | 6  |

| 1.  |        | ing Sequence                                                      |    |

| 2   | Piook  | Diagram                                                           |    |

#### 1.0 INTRODUCTION

#### 1.1 General Description

The Shugart Model 4000 Disk Drive is a random access storage device with one or two fixed 14 inch disks as the storage media. Each disk surface has two read/write heads and contains up to 404 data tracks. The drive provides up to 29 megabytes of on-line storage on 1616 addressable tracks. An option is available which allows 8 fixed heads (one per track) to be selected, providing 144 kilobytes of fast access storage. Up to 4 drives may be daisy chain connected in one system.

Low cost and reliability of the unit is achieved with a unique actuator design. The inherent simplicity of mechanical construction and electronic controls of the assembly allows maintenance free operation for the life of the drive.

Mechanical and contamination protection for the head, actuator, and disk is provided by an impact-resistant plastic enclosure. A self-contained recirculating system supplies clean air through absolute filters that are designed to last through the life of the drive.

A single track of clock information is written on the disk and is read by a single fixed head. These clock pulses are used to synchronize the Phase Locked Oscillator in the data separation circuitry and provide Index, Sector and Write Clocking information from the disk. A jumper programmable counter is provided that converts the clock pulse into any number of sectors per track.

A data separator PCB is mounted in the drive enclosure. In addition to data separation of MFM Read Data, this PCB MFM encodes and write precompensates standardized Write Data.

The drive can be mounted in any 19 inch rack. It occupies 5.25 inches of vertical space and is 22 inches long.

# 1.2 Specifications Summary

# 1.2.1 Performance and Functional Specifications

| MODEL                    | 4004                             | 4008  |

|--------------------------|----------------------------------|-------|

| No. of Disk Surfaces     | 2                                | 4     |

| No. of Heads             | 4                                | 8     |

| No. of Cylinders         | 202                              | 202   |

| No. of Tracks            | 808                              | 1616  |

| Gross Capacity (M bytes) | 14.54                            | 29.08 |

| Access Time (ms)         |                                  |       |

| One Track                | 20                               | 20    |

| Average                  | 65                               | 65    |

| Maximum                  | 140                              | 140   |

| Disk Speed               | 2964 RPM ±2%                     |       |

| Recording Mode           | MFM                              |       |

| Recording Density        | 5534 BPI                         |       |

| Flux Density             | 5534 FCI                         |       |

| Track Capacity           | 18000 Bytes                      |       |

| Track Density            | 172 <b>TPI</b>                   |       |

| Transfer Rate            | 7.11 x 10 <sup>6</sup> bits/sec. |       |

|                          | 889 x $10^{3}$ bytes/sec.        |       |

| Sectors                  | Programable                      |       |

| Start Time               | 1.5 minutes                      |       |

#### 1.2.2 Physical Specifications

Environmental Requirements

| Environmental Requirements                                         |                       |                     |               |  |  |

|--------------------------------------------------------------------|-----------------------|---------------------|---------------|--|--|

|                                                                    | Operating             | Shipping            | Storage       |  |  |

| Temperature (host ambient) - F                                     | 50 to 105             | -40 to 144          | -8 to 117     |  |  |

| Relative humidity $-\%$                                            | (10 to 41°C)          | (-40 to 62°C)       | (-22 to 47°C) |  |  |

|                                                                    | 8 to 80               | 1 to 95             | 1 to 95       |  |  |

| Maximum wet bulb                                                   |                       | 78°F non-condens    | sing          |  |  |

| AC Power Requirements                                              |                       |                     |               |  |  |

| 50/60 Hz ± 0.5 Hz                                                  |                       |                     |               |  |  |

| 100/115 VAC Installations = 90                                     | to 127 V @ 2.         | 9A maximum          |               |  |  |

| 200/230 VAC Installations = 180                                    | to 253 V @ 1.         | 9A maximum          |               |  |  |

| DC Voltage Requirements                                            |                       |                     |               |  |  |

| +24 V ± 10% @ 3A maximum                                           |                       |                     |               |  |  |

| +5V ± 5% @ 3A maximum                                              | +5V ± 5% @ 3A maximum |                     |               |  |  |

| -7 to -16 V @ 0.15A maximum (option -5 V $\pm$ 5% @ 0.10A maximum) |                       |                     |               |  |  |

| Physical Dimensions                                                |                       |                     |               |  |  |

| Height                                                             |                       | naximum (132.6 r    | · ·           |  |  |

| Width                                                              | 16.7 inches i         | naximum (424 mr     | n)            |  |  |

| Depth                                                              | 21.9 inches r         | naximum (556.3 n    | nm)           |  |  |

| Weight                                                             | 35 pounds             | (15.9 kg            | )             |  |  |

| Heat dissipation                                                   | 880 BTU/H             | r. typical (235 Wat | tts)          |  |  |

# 1.2.3 Reliability Specifications

| MTBF:                   | 8000 power on hours              |

|-------------------------|----------------------------------|

| MTTR:                   | 30 minutes                       |

| Component life:         | 5 years normal usage             |

| Acoustic noise level:   | less than NR 55                  |

| Error Rates:            |                                  |

| Soft read errors:       | 1 per 1010 bits read             |

| Hard read errors:       | 1 per 10 <sup>12</sup> bits read |

| Seek errors:            | 1 per 10 <sup>7</sup> seeks      |

| Preventive Maintenance: | none required                    |

|                         |                                  |

This section will functionally describe the major circuits of the SA4000. For interface timing, refer to the SA4000 OEM manual Part Number 39005.

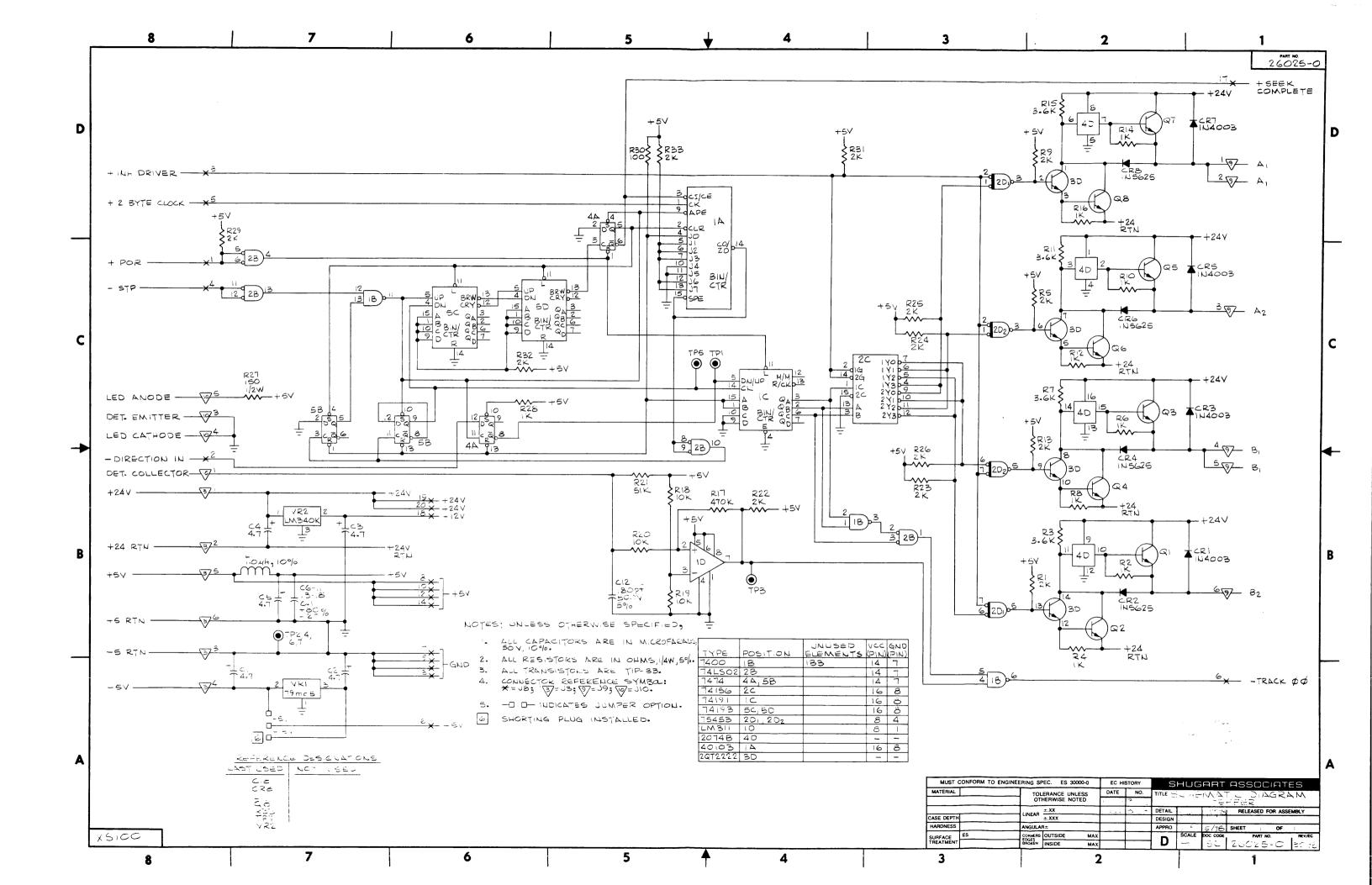

#### 2.1 POWER ON RESET (POR)

When DC voltages are applied to the SA4000, C44 on the Control board charges up momentarily, preventing Q4 from turning on. From the time +5 goes high until Q4 turns on is approximately 15 msec, thus IC 5G will output a 15 msec -POR pulse. This low pulse has several functions.

It resets the IN LOCK circuit (IC's IB, ID, and 2E) and the WRITE FAULT DETECT circuit (IC 7F) on the Control PCB. —POR then becomes +POR and is transferred to the Actuator PCB, where it loads the step count buffers (IC's 5C and 5D), disables the step-count timer (IC 1A) and loads the AC motor phase counter (IC 1C) so that on DC power up, phase A will be energized. SEEK COMPLETE is generated and with IC 5B set, the step circuit will wait for a step pulse.

#### 2.2 STEPPING

#### **Control PCB**

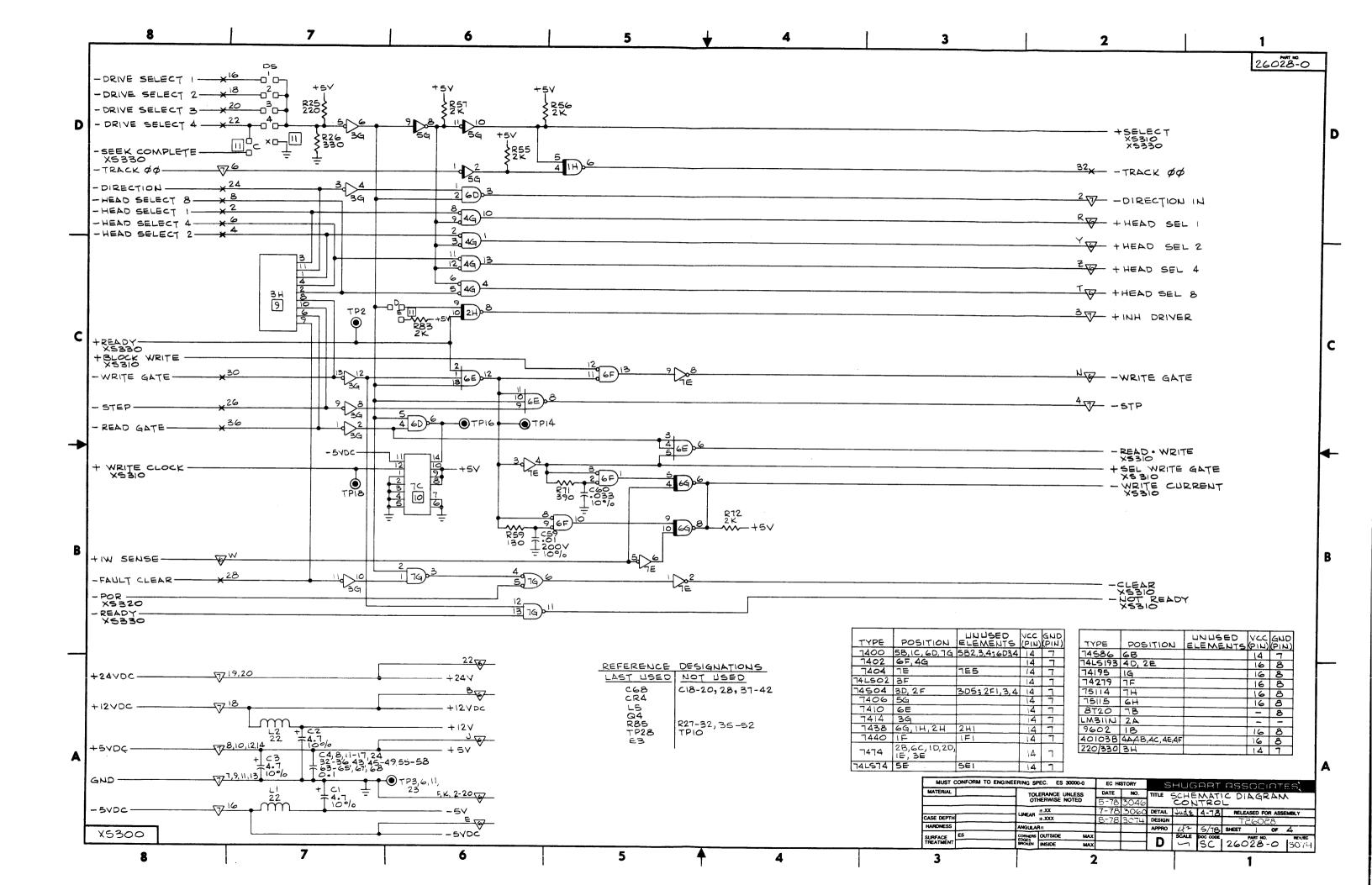

To initiate a seek operation, the controller issues the required number of step pulses and also sets the DIRECTION line at least 200 nsec before the trailing edge of the step pulse.

If the drive is SELECTED and a WRITE operation is not in progress, the step pulses (-STP) and direction of seek (-DIRECTION IN) will be gated through the Control PCB to the Actuator PCB via pins 4 and 2 respectively of connector J7.

#### **Actuator PCB**

In order to be valid, step pulses must be at one of two rates. In the Normal mode there will be 1.1 msec or more time delay between incoming step pulses. In the Buffered mode there will be less than 350 usec time delay between them. If step pulses are incoming 600 µsec apart for example, then every other pulse would be lost causing the heads to move only half the required number of tracks. The reason for this is that the step count timer located at position 1A which counts down to zero in approximately 500 µsec would output a low pulse. This pulse then clocks chip 5B blocking out incoming step pulses for another 500 µsec while chip 1A once again counts down to zero generating a single track step and a SEEK COMPLETE signal. At this time another step pulse is allowed to enter, but the previous one was lost.

In the Normal step mode, pulses are gated through chip 1B incrementing the step count buffers (IC 5C and 5D) by 1 and starting the step rate timer (IC 1A). In approximately 500  $\mu$ sec the timer,

which was preset by the last step pulse, counts down to zero. The low pulse generated at that time does the following: 1) clocks IC 5B pin 3 preventing any more step pulses from being processed until the heads have stepped 1 track, 2) Clocks IC 5B pin 11 dividing the step rate timer outputs by 2 lengthening the time between steps to 1 msec, and 3) presets itself for the next step pulse input. The step rate timer now counts down, once more outputting a low pulse when count zero is reached. This second timer clocks IC 5B pin 11 again, this time decrementing the step count buffers by 1 and clocking the DIRECTION through the phase counter to the decoder at 2C.

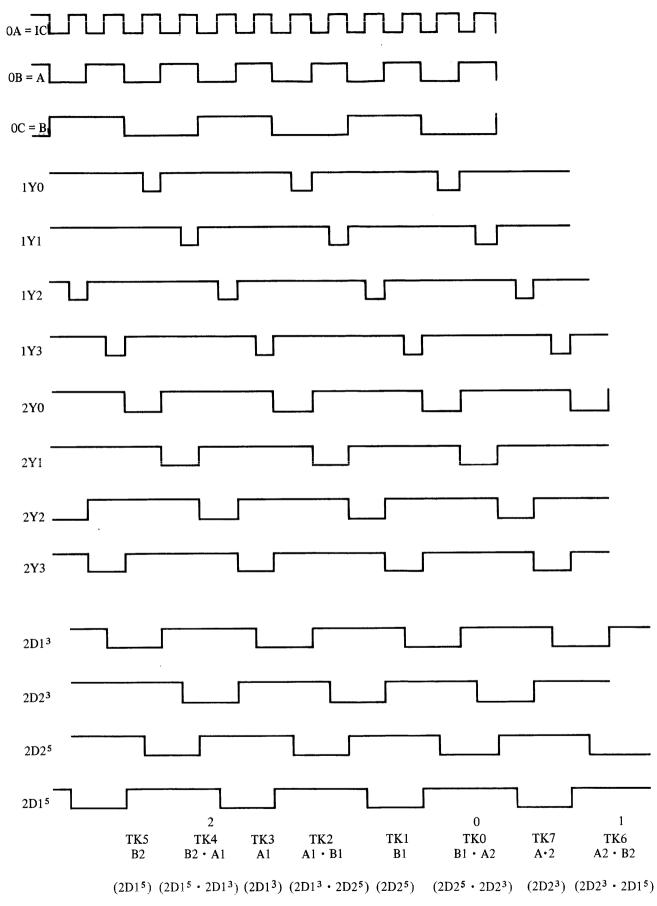

The phase counter, which is always set to phase A on DC power up, increments or decrements according to the level of the DIRECTION line. For example, a phase count of 3 ( $Q_A$  high  $\cdot$   $Q_B$  high  $\cdot$   $Q_C$  low) would be decoded by chip 2C to become 1Y1 and 2Y1 low, energizing both coils B1 and A2 simultaneously. For a complete sequencing chart refer to Figure 1.

Since the step pulse counters were decremented, a borrow output in generated, clocking IC 4A. This results in chips 5B, 5C, and 5D being reset for any further step pulses and also generates SEEK COMPLETE.

Buffered seeking entails exactly the same sequence of events with the only difference being that all of the step pulses are loaded into the step pulse buffers before chip 1A is allowed to clock them out to the stepper motor. In this mode the step rate is accelerated and decelerated for the first/last 16 steps. Refer to table 1 showing the acceleration/deceleration step values.

# STEPPER ACCELERATION/DECCELERATION VALUES

| STEP # | STEP TIME ( µ SEC) |

|--------|--------------------|

| 1      | 984                |

| 2      | 1050               |

| 3      | 884                |

| 4      | 812                |

| 5      | 755                |

| 6      | 708                |

| 7      | 671                |

| 8      | 641                |

| 9      | 617                |

| 10     | 598                |

| 11     | 583                |

| 12     | 572                |

| 13     | 564                |

| 14     | 558                |

| 15     | 554                |

| 16     | 552                |

Table 1

Figure 1. Stepping Sequence

# 2.3 READ OPERATION

When the controller desires to initiate a read operation, it will select the appropriate head and drop the -READ GATE line. If the drive has been selected, -READ GATE goes to the VFO PCB via socket 7C and the -HEAD SELECT signal goes to the R/W PCB via connector J6.

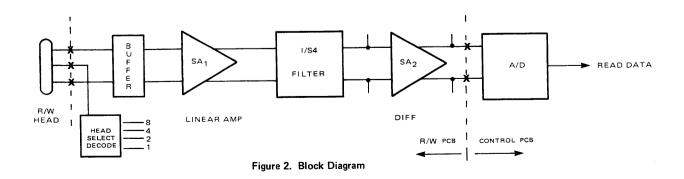

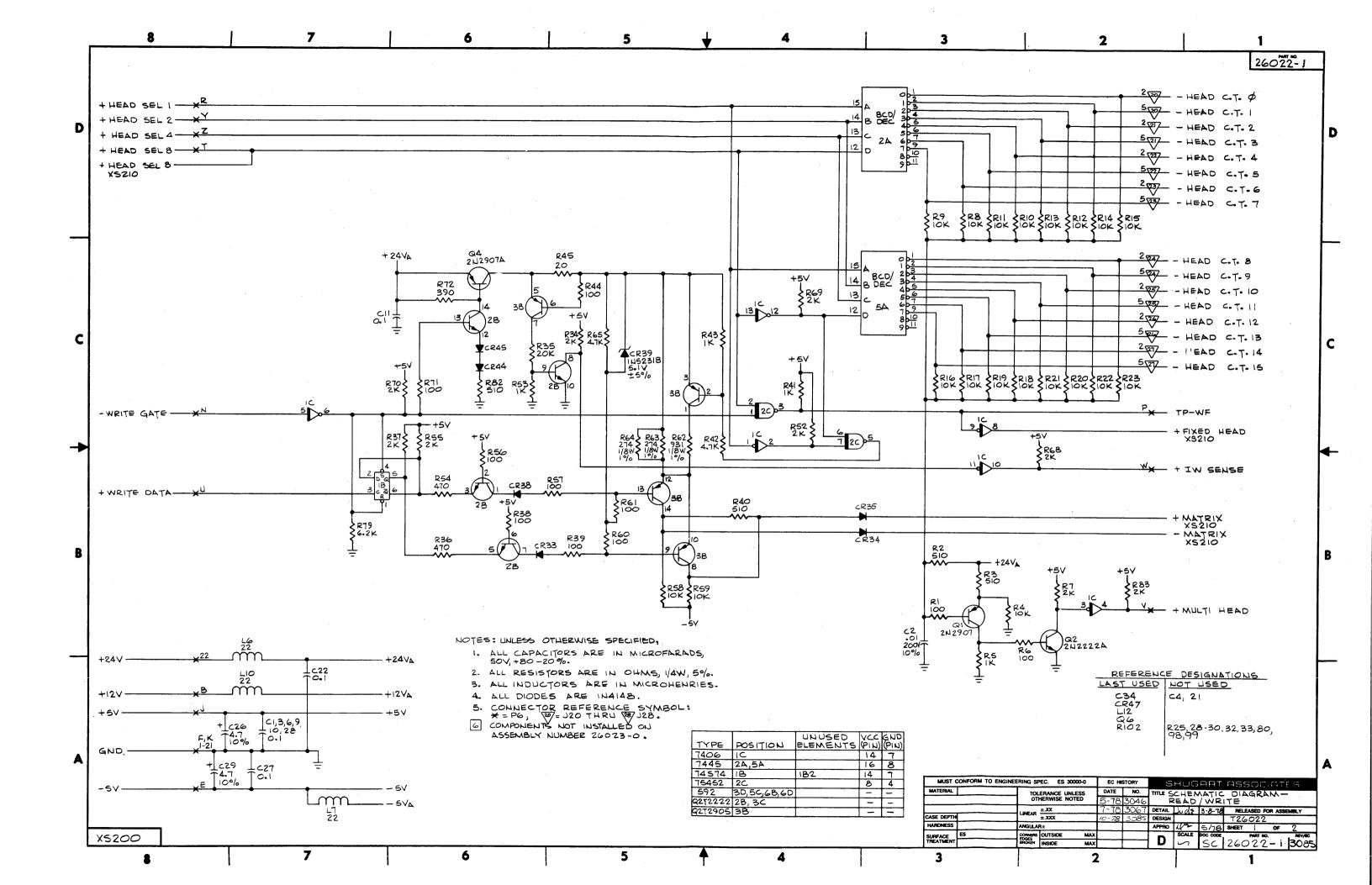

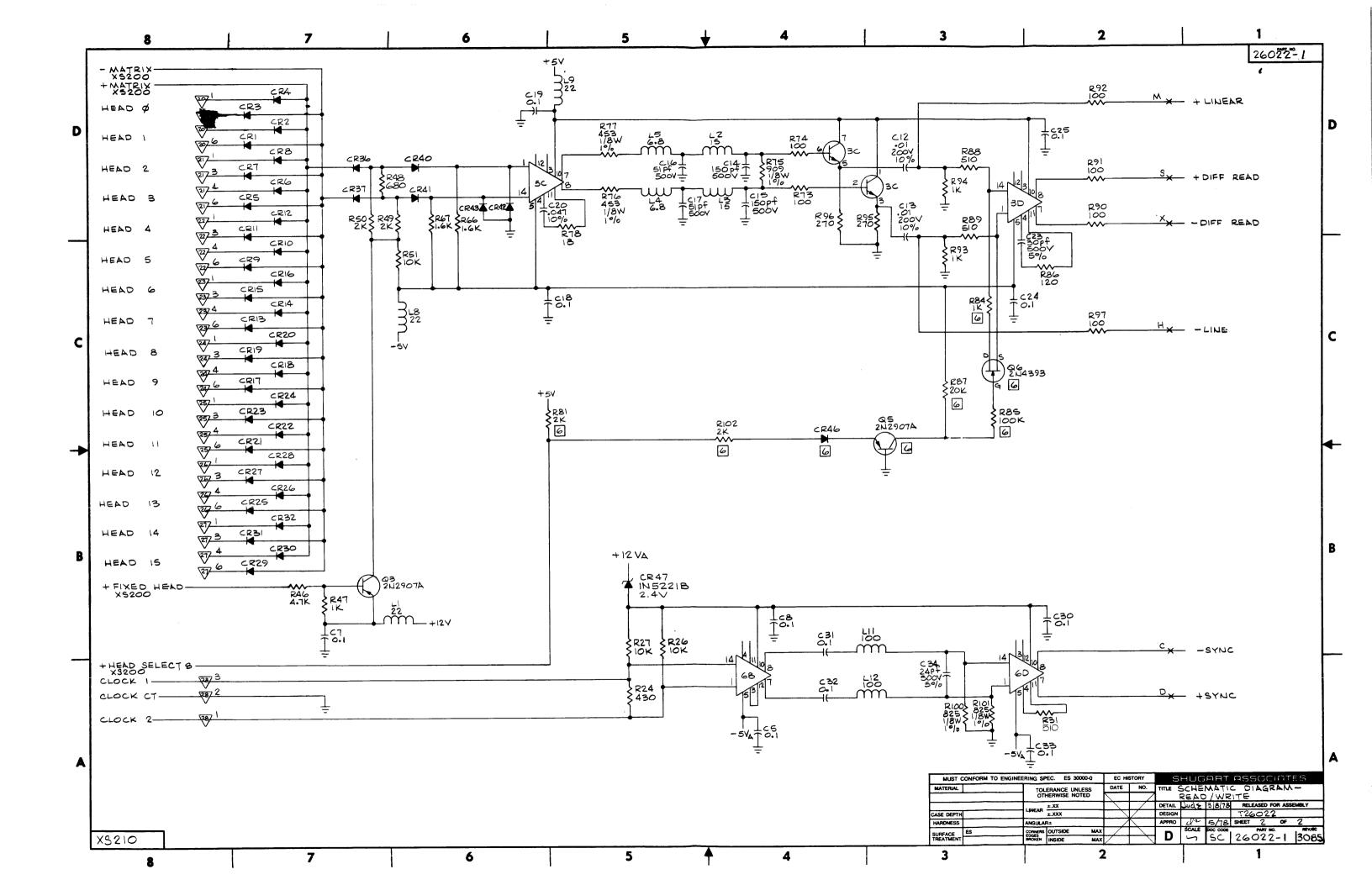

#### R/W PCB (Refer to Figure 2)

The head select lines are decoded by chips 5A and 2A who choose the appropriate head, by grounding its center tap. Flux transitions are now passed through the head core into the isolation stage of the read channel. This stage isolates the head from the read channel during the write mode, provides the necessary damping for detection of flux transitions, and affords the requisite impedance matching between the selected head and the first stage of amplification.

The first amplification stage is a high pass network with a pole located at 76.9 KHz. It removes all DC offset as well as provides a linear high pass for frequencies greater than 1 MHz. Midband amplification at this stage is 312 (50 dB).

Next the four pole bessel type filter network increases the signal to noise ratio and linearizes the phase by having a constant time delay. Load impedance for the first amplification stage is also provided.

Raw data is differentiated and amplified once more by chip 3D which is a high pass linear amp providing a midband voltage gain of 96. Total gain for the two amplification stages equals 9 for 1F frequency and 5 for 2F frequency.

#### **Control PCB**

Amplified raw data then goes to the Control board via connector J6 as ±DIFF READ ±LINEAR signal is not used. The analog to digital converter chip 7B is a bidirectional one shot device whose outputs correspond to any flux transitions detected by the

read head. A head with very high resolution will occasionally translate droop into a flux change. All of the flux transitions, including any invalid droop conditions, are scrutinized by the droop ignore circuit whose 30 nsec delay allows invalid transitions to be filtered out. Droop ignored raw data then goes to the VFO PCB via socket 7D.

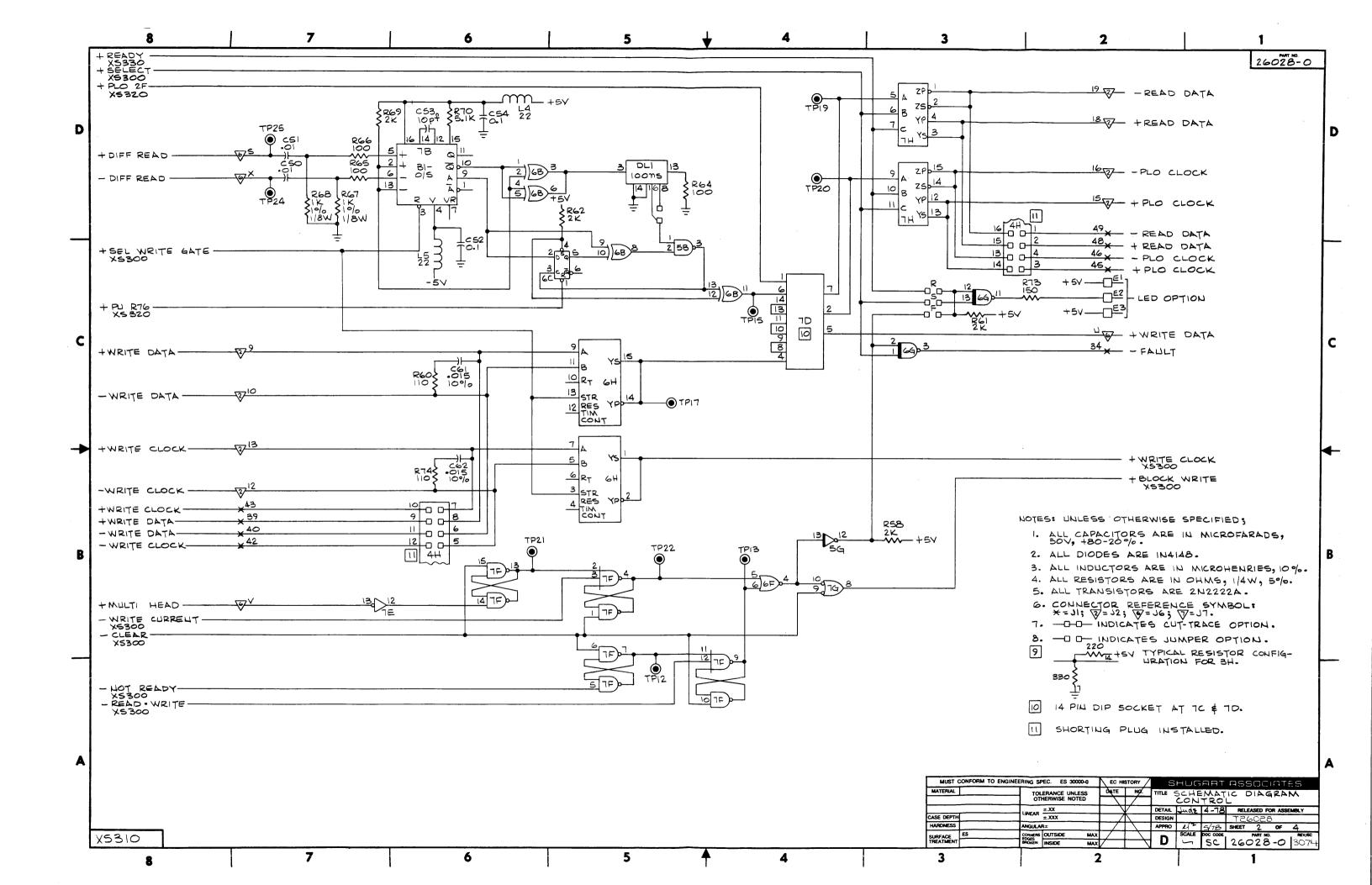

#### **VFO PCB**

-READ GATE is active when a read operation is in progress. Chip 1B will be clocked by raw data, counting up. [After 4 bits, 1B will enable NRZ READ DATA to be sent to the controller.] At the same time it disables chip 1E activating the window generator chip 2E. VCO 2F is now compared to the stream of raw delayed data. This stream consists of clock and data bits 20 nsec wide delayed by 30 nsec.

If raw data bits are early with respect to VCO 2F, the top half of the window generator chip 2E pin 7 goes low turning on Q2 charging up C13, who then generates a positive going DC error voltage. If data bits are late with respect to VCO 2F, the bottom half of chip 2E pin 5 goes high turning on Q4 discharging C13, who then generates a negative going DC error voltage. Chip 2D pin 9 is always high between raw data pulses locking up the window generator. Without this condition VCO 2F which is twice the frequency of the data bit stream would cause a large false DC error voltage to be produced whenever no data was present.

DC ERROR voltage, if it is a high going signal, will cause the varicap CR3 to decrease its capacitance, speeding up the frequency of the VCO 2F oscillator CK+, thus VCO 2F which was lagging behind the raw data stream will speed up. This cycle always continues during the read operation as the VCO 2F frequency tracks the data bit frequency, i.e., the disk's rotational speed.

Corrected VCO 2F is divided by 2 at chip 4E becoming VCO 1F. Each alternate cycle of the VCO 2F frequency, according to jumper D/C (sync on all 0's or all 1's) will put all of the data

bits into pin 4 of chip 5E and all of the clock bits into pin 10 of chip 5E. 5E acts as an R/S flip flop and latches on the data bits, clears on the clock bits. By latching in this manner the data window is extended so that delayed data will be centered in the window to prevent late data bits from "slivering" and appearing in both data and clock window. The output of chip 5D then is centered, delayed data bits only. They are stored in 6D until clocked out of pin 5 by 5 VCO 1F. Chip 6D pin 9 then outputs a low whenever no data is present and a high if data is present, i.e., NRZ READ DATA.

#### **Control PCB**

This data is then transferred to the Control PCB via socket 7D where it is input to the line drivers at 7H and transmitted to the controller as NRX READ DATA.

#### 2.4 WRITE OPERATION

#### **Control PCB**

When the controller desires to write data to the disk, it will activate-head select, -WRITE GATE, WRITE CLOCK, and NRZ WRITE DATA.

If the drive is in the READY condition, is SELECTED, and there are no FAULT conditions, -WRITE GATE will be gated to the R/W PCB via connector J6, and will allow the write operation to begin.

+WRITE CLOCK, -WRITE CLOCK, +WRITE DATA, and -WRITE DATA all enter the differential amplifiers at chip 6H, becoming +WRITE DATA and +WRITE CLOCK +WRITE DATA passes to the VFO PCB via socket 7D and +WRITE CLOCK goes to the VFO PCB via socket 7C.

#### **VFO PCB**

+WRITE DATA and +WRITE CLOCK are mixed at chip 6C and enter the precompensation circuit

composed of chips 4A, 4B, 5A, 5B, and 5C. Depending on the pattern of this clock and data stream, an appropriate amount of precompensation is added. The early line, (pin. 3 of chip 4A) delays the raw data stream by 8 nsec, the on time line (pin 5 of chip 4A) delays it by 16 nsec, and the late line (pin 9 of chip 4A) delays it by 24 nsec. At this point the + MFM WRITE DATA goes back through the Control PCB via socket 7D and to the R/W PCB via connector J6.

#### R/W PCB

+ WRITE DATA (actually composite clock and data bits) is converted from digital to analog by chips 1B, 2B, and 3B and associated circuitry. + MATRIX or – MATRIX is selected by chip 3B depending on whether or not a one or a zero is to be written. the HEAD SELECT lines are decoded by chips 2A and 5A choosing one of the possible 16 heads by grounding its center tap. Current flows through the appropriate matrix diodes to the selected head and flux transitions are imposed on the media surface.

#### 2.5 ERROR CIRCUIT

The error circuit is located on the Control PCB and its function is to prevent writing on the media at improper times. + MULTI HEAD, - WRITE CURRENT, -NOT READY, or -READ\*WRITE condition will cause a +BLOCK WRITE and a -FAULT to be issued. +BLOCK WRITE will prevent -WRITE GATE from being active, -FAULT will be sent to the controller who must toggle the -FAULT CLEAR line in order to reset the fault circuit.

- +MULTI HEAD is the result of the R/W PCB circuit selecting in more than one head.

- -WRITE CURRENT occurs when -WRITE GATE is active but no write current (IW SENSE) is sensed in the R/W PCB write circuit, or -WRITE GATE is inactive and write current is present in the R/W PCB write circuit.

- -NOT READY is active if -WRITE GATE is on, but the drive is not in the READY condition.

- -READ WRITE happens if both -READ GATE and -WRITE GATE are active concurrently.

#### 3.0 TROUBLESHOOTING TECHNIQUES

#### Philosophy

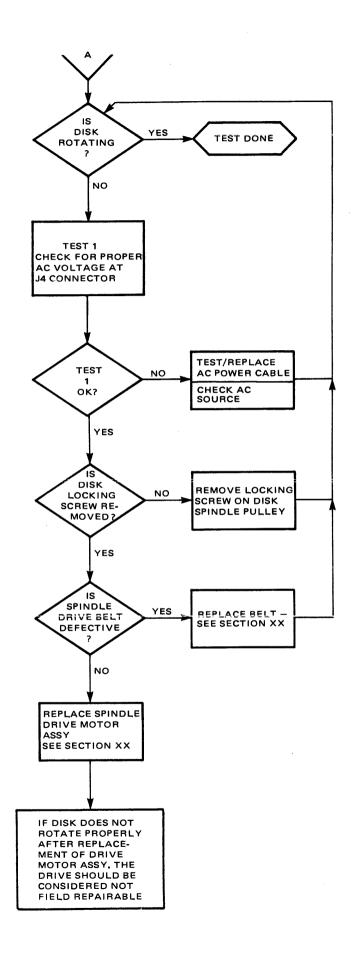

The following troubleshooting techniques are designed to aid field service personnel in locating a drive fault down to the PCB level (modular replacement) or to determine that the drive is not field repairable, in which case the drive must be repaired at a depot facility.

# **Equipment Required**

- 1. A power supply capable of generating the following voltages:

- a. +5 volts at 3 amps maximum

- b. +24 volts at 3 amps maximum

- c. -5 volts at 0.1 amps maximum or -7 to -16 volts at 0.15 amps maximum.

- 2. Oscilloscope Tektronix 464 or equivalent.

- a. Probes: X10 2 each X1 1 each

#### **Troubleshooting Flowcharts**

The interface signals utilized by the various flow-charts may be generated by the host system/controller through its own diagnostic routines, or by the SA4000 suitcase tester available from Shugart.

#### Flowchart Symbols

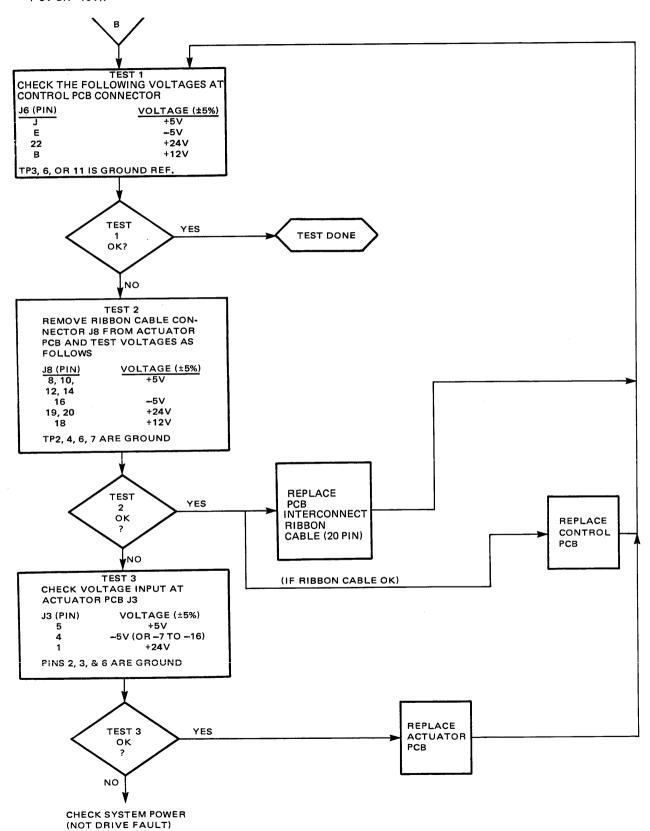

#### D.C. POWER TEST

#### PRELIMINARY NOTES:

1. CHECK REGULATOR JUMPER OPTION ON ACTUATOR PCB FOR CORRECT POSITION (-5V OR -15V).

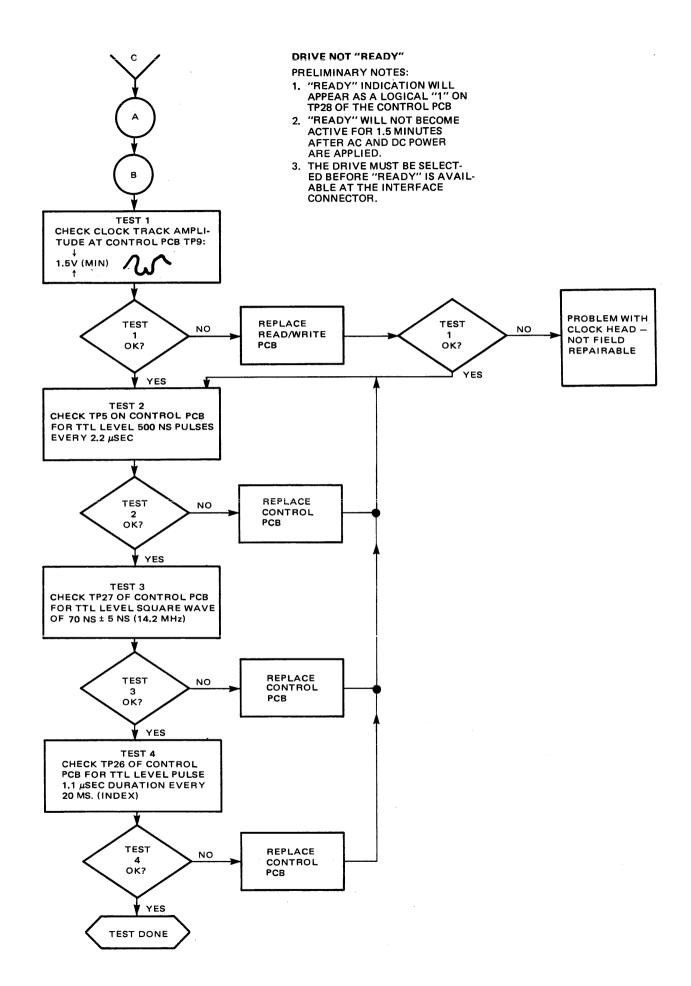

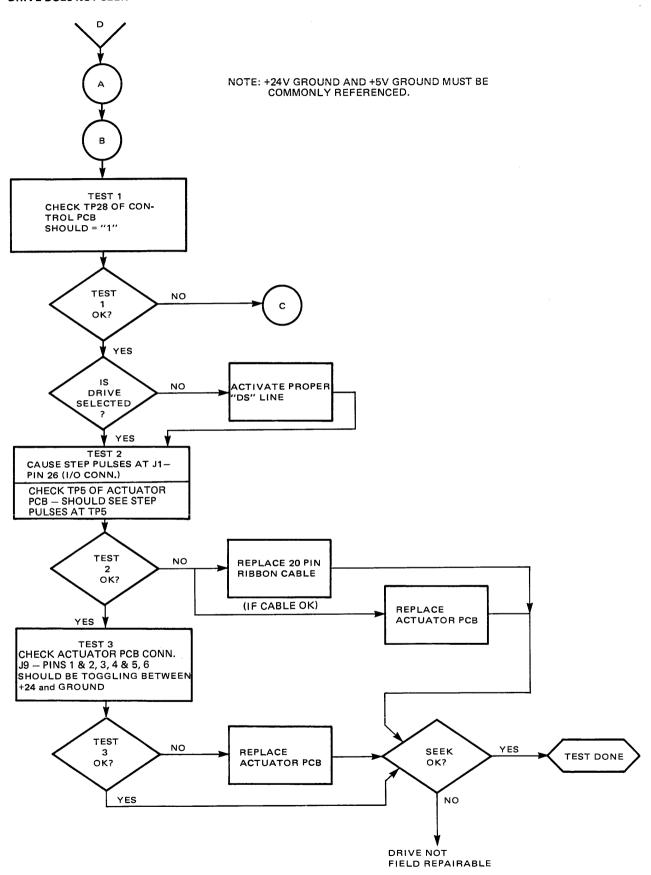

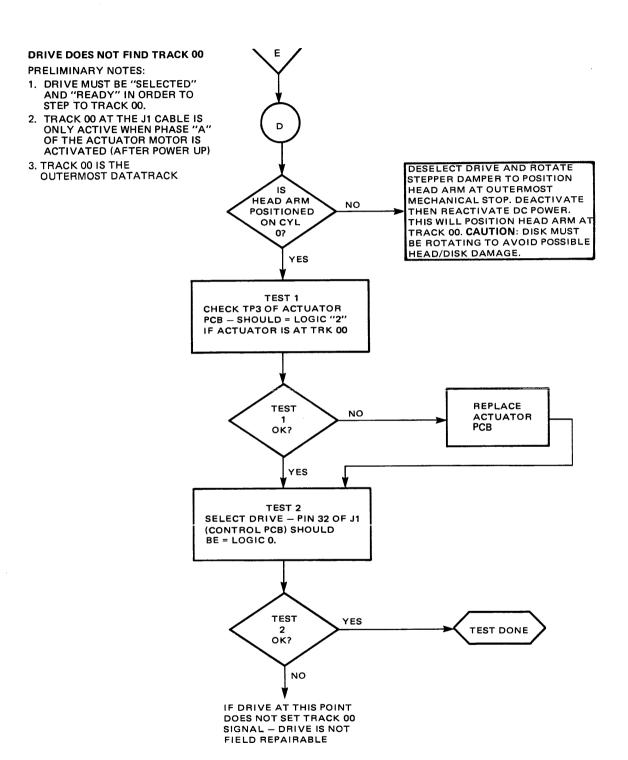

#### DRIVE DOES NOT SEEK

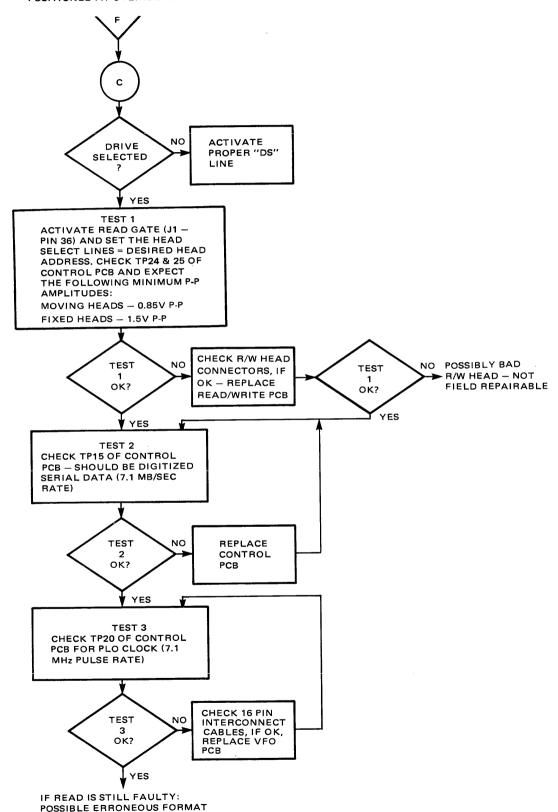

#### **DRIVE DOES NOT READ**

#### PRELIMINARY NOTES:

1. FOR THESE TESTS, THE READ/ WRITE HEADS SHOULD BE POSITIONED AT CYLINDER 201.

OR DATA - POSSIBLE FAULTY I/O

CABLE.

AND A DATA PATTERN OF ALL ZERO'S ORONE'S SHOULD BE WRITTEN TO ALL READ/WRITE HEADS.

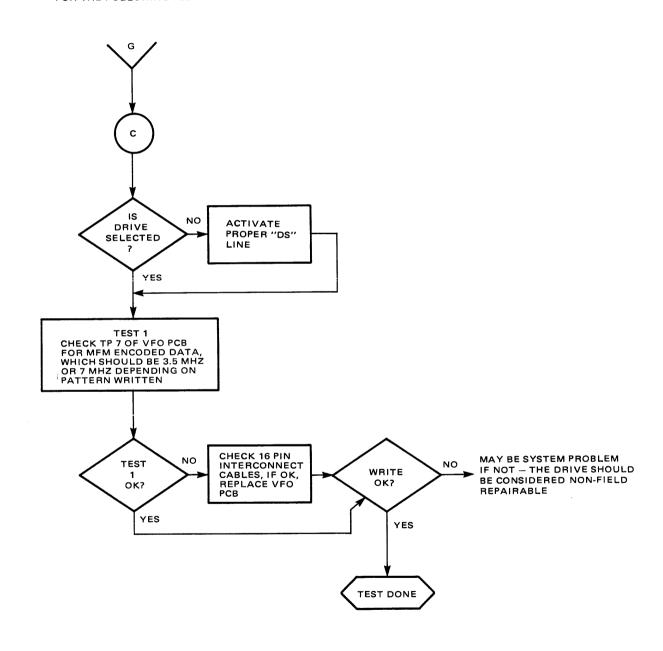

#### **DRIVE DOES NOT WRITE**

#### PRELIMINARY NOTES:

WRITE GATE MUST BE ACTIVATED FOR THE FOLLOWING TESTS.

# 4.0 TEST POINTS AND PIN LOCATIONS

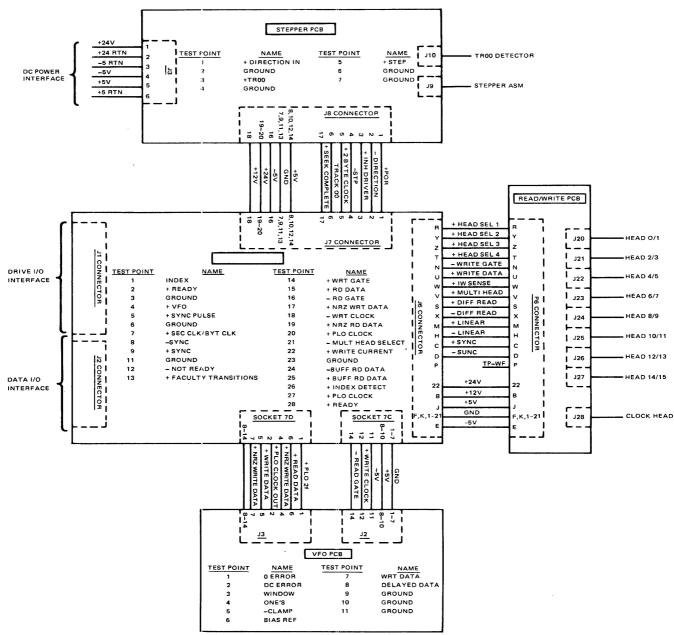

**SA4000 INTERCONNECT DIAGRAM**

**Test Points**

**CONTROL BOARD**

- 1 INDEX \_\_\_, 20 msec period, 1.1 μs pulse width

- 2 LOGIC 1 = READY, LOGIC 0 = NOT READY

- 3 GND

- 4

2.2 µsec period (PLO clock derivative)

5

2.2 µsec period (digitized clock track)

- 6 GND

- 7 Sector Count or Byte Clock e.g., 32 sector = \_\_\_\_\_ 600 μsec period, 1.1 μs pulse width

- 8 + SYNC

- $\sim$

- 2.2 µsec

- 9 SYNC

- 2.2 µsec

- 10 GND

- 11 GND

- 12 ↓ = NOT READY ↑ READY

- NOT READY or READ•WRITE fault condition = ↑ no fault = ↓

- 14 WRITE GATE READY DRIVE SELECT ↓ = Writing ↑ Reading

- 15 digitized read data

- 16 READ GATE DRIVE SELECT ↓ = READING ↑ = WRITING

- 17 WRITE DATA BIT CELL PERIOD = 140 nsec

- 18 WRITE CLOCK PERIOD PLO CLOCK = 140 nsec PERIOD

- 19 NRZ READ DATA \_\_\_\_\_\_\_ BIT CELL PERIOD = 140 nsec

- 20 PLO CLOCK PLO CLOCK = 140 nsec PERIOD

| 21 | MULTI HEADS selected = ↓                                   |

|----|------------------------------------------------------------|

| 22 | MULTI HEADS · WRITE CURRENT = ↑                            |

| 23 | GND                                                        |

| 24 | -DIFF READ 1F -\                                           |

| 25 | +DIFF READ 1F -/                                           |

| 26 | INDEX DETECT 20 msec period, 1.1 $\mu$ s pulse width       |

| 27 | PLO 2F 70 nsec                                             |

| 28 | READY = ↑                                                  |

|    | STEPPER BOARD                                              |

| 1  | DIRECTION IN $-\uparrow$ OUT = $\downarrow$                |

| 2  | GND                                                        |

| 3  | TK00 detected = ↑                                          |

| 4  | GND                                                        |

| 5  | STEP CLOCK 0.5 to 1.0 msec rate while stepping             |

| 6  | GND                                                        |

| 7  | GND                                                        |

|    | VFO BOARD                                                  |

| 1  | intermediate VCO correction signal                         |

| 2  | DC error – typical VCO correction signal NRZ 1F = 280 nsec |

| 3  | VFO data window                                            |

| 4  | decoded read data                                          |

| 5  | CLAMP VCO ↑ = clamped after 5 bits of data                 |

| 6  | DC ERROR                                                   |

| 7  | MFM WRITE DATA 1F = 280 nsec                               |

| 8  | 1F 280 nsec data window                                    |

| 9  | GND                                                        |

| 10 | GND                                                        |

| 11 | GND                                                        |

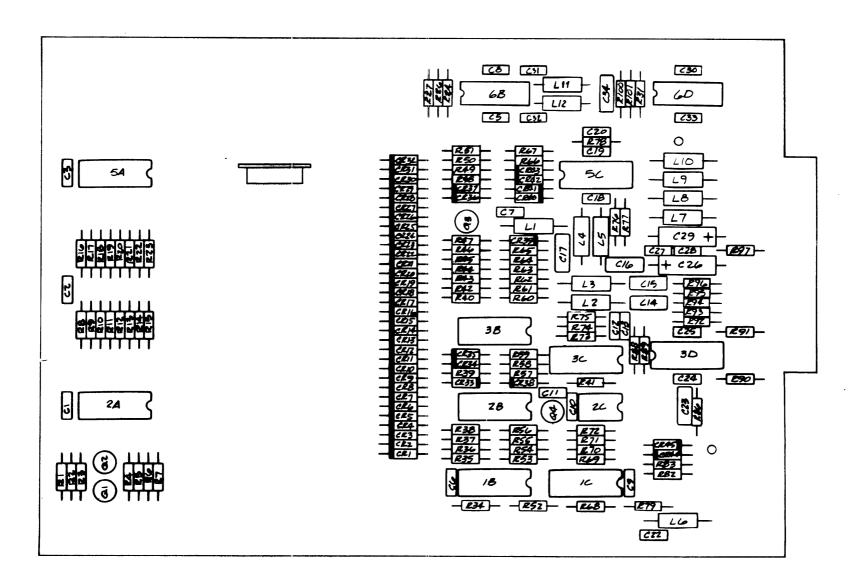

# **5.0 PCB COMPONENT LOCATIONS**

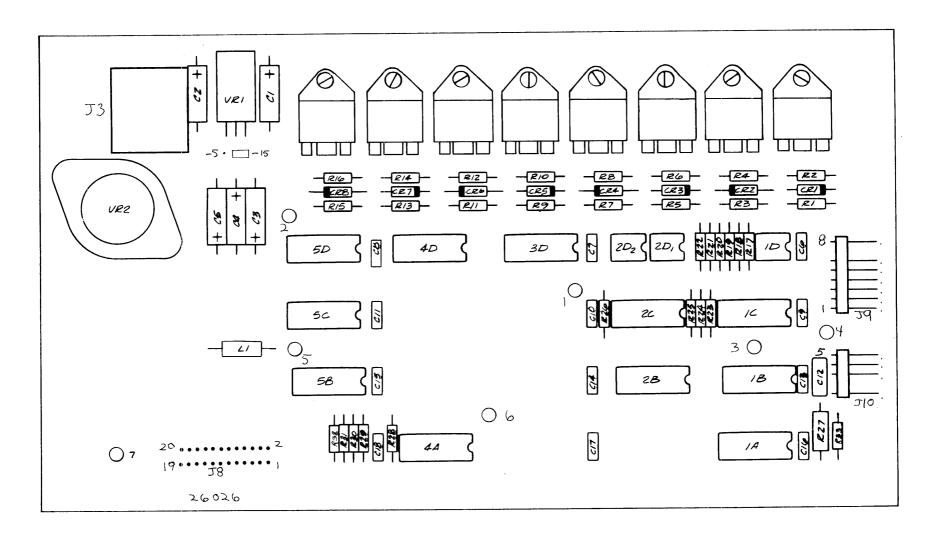

**READ/WRITE PCB**

Stepper PCB

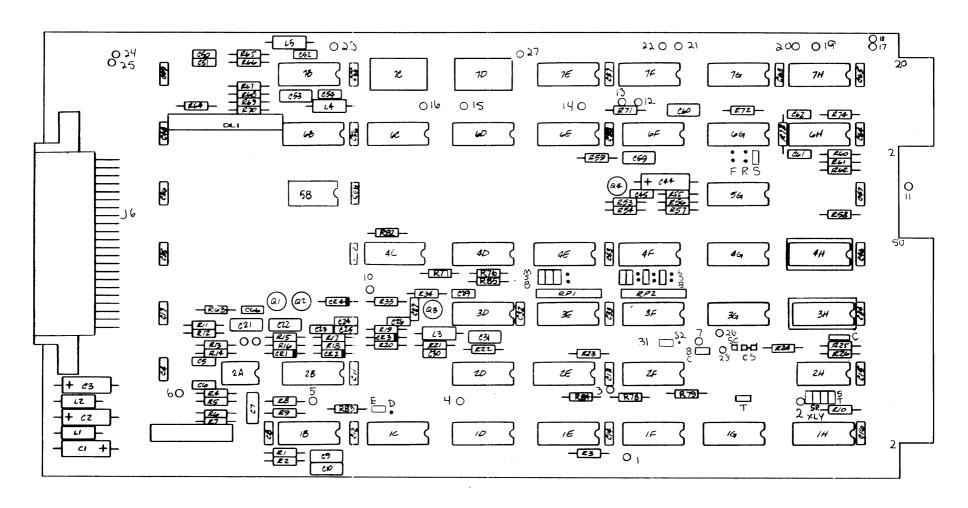

Control PCB

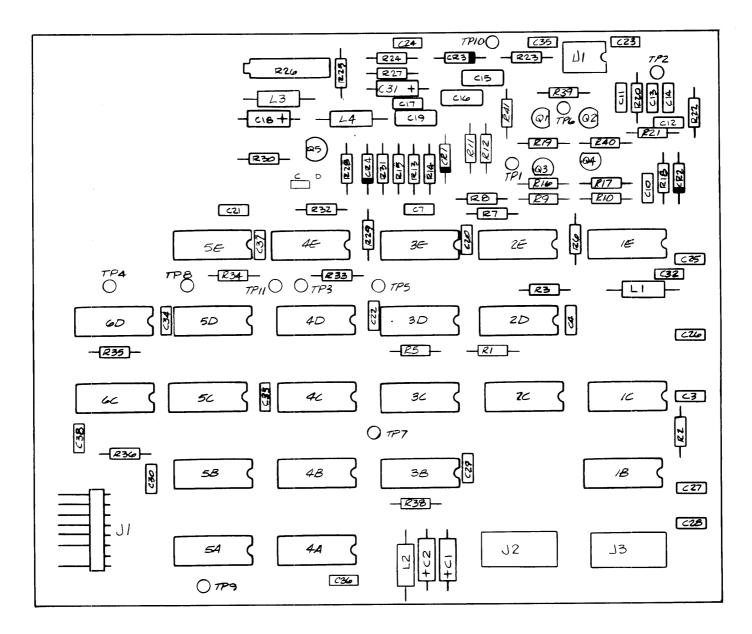

VFO PCB

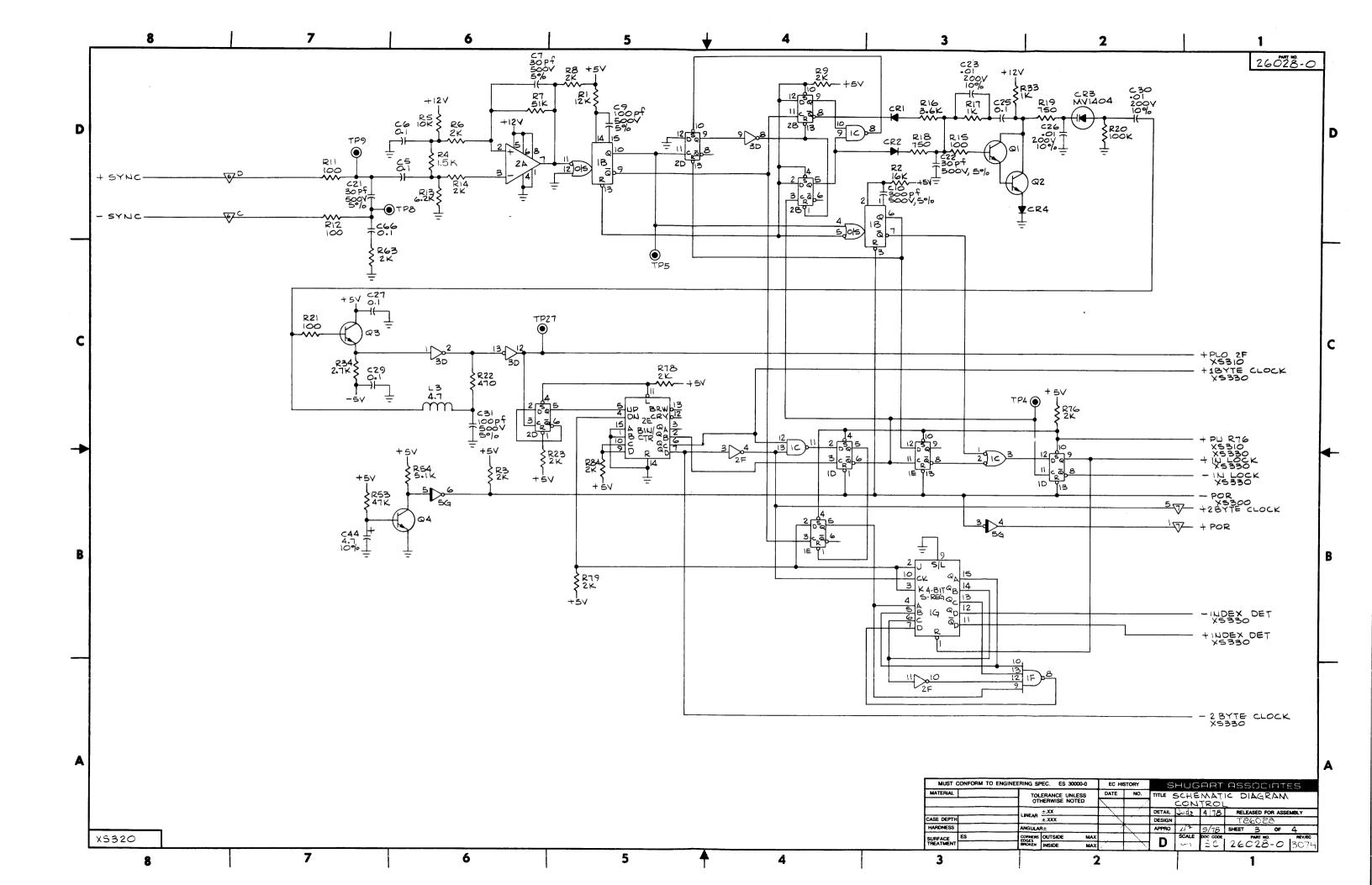

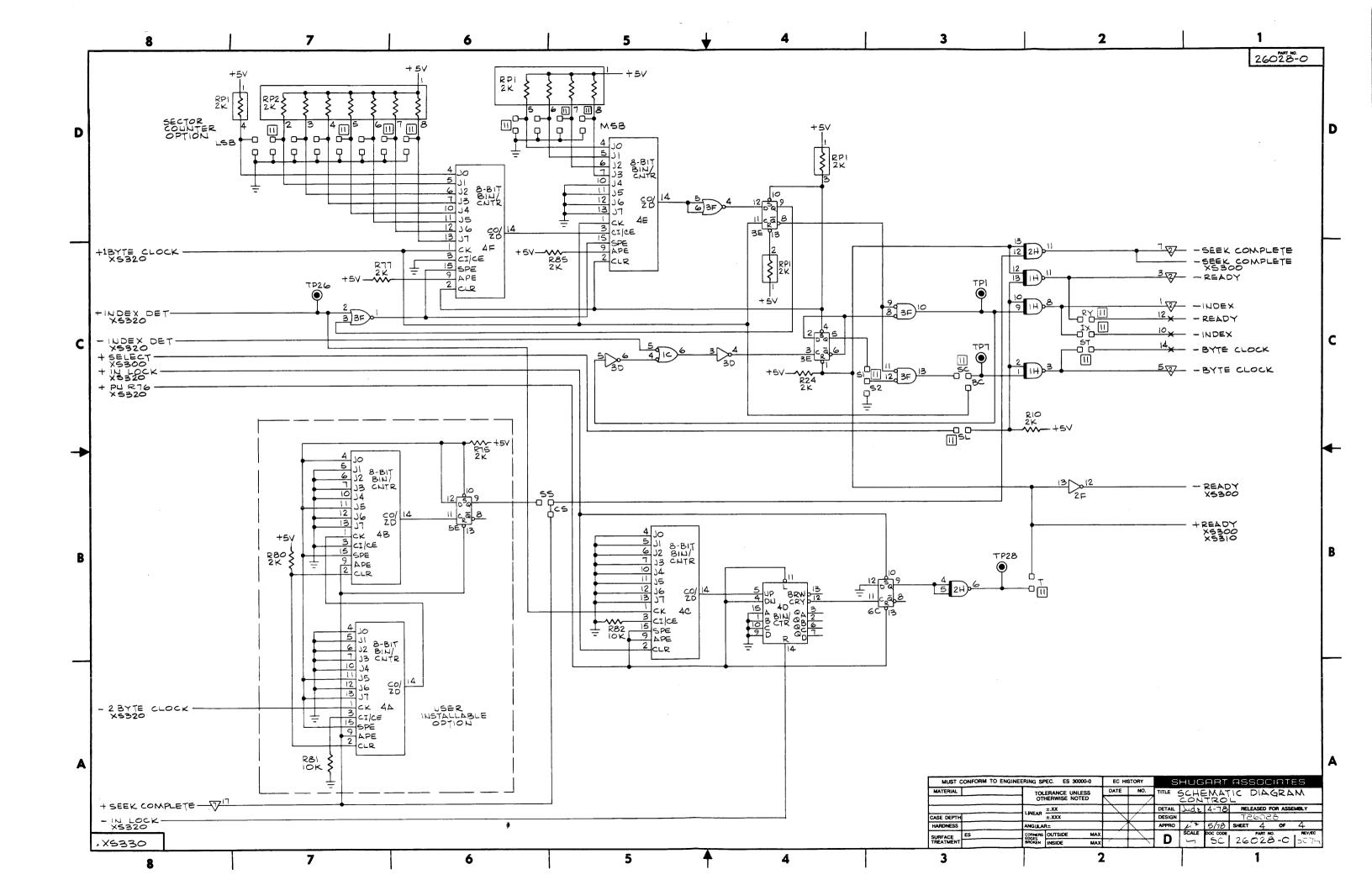

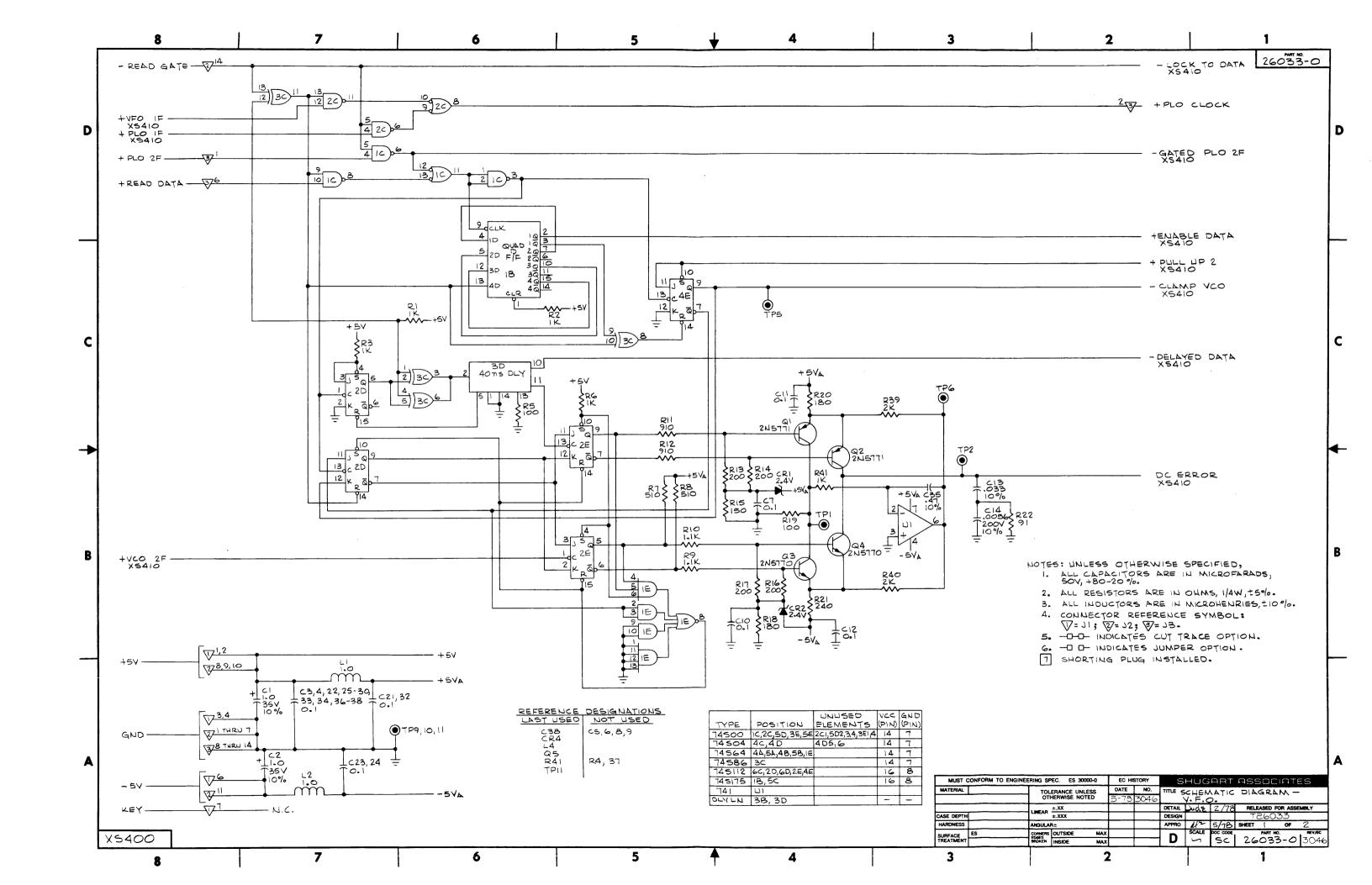

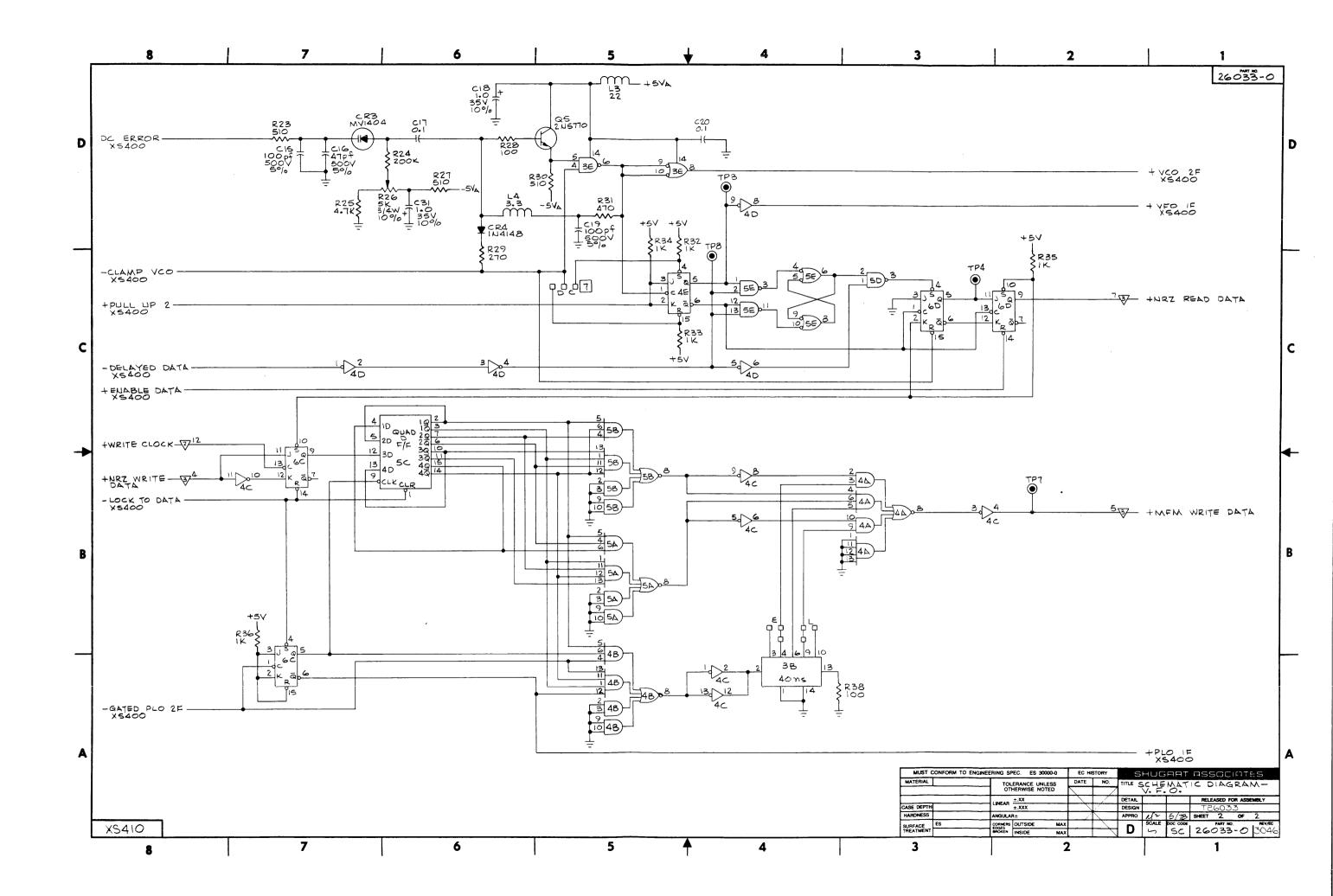

# **6.0 SCHEMATIC DIAGRAMS**

435 Oakmead Parkway, Sunnyvale, California 94086 Telephone: (408) 733-0100 TWX: 910 339-9355 SHUGART SUVL