# SCD - DHV11/16 16-Line Asynchronous Multiplexer Manual

# SCD - DHV11/16 16-Line Asynchronous Multiplexer Manual

COPYRIGHT © SIGMA INFORMATION SYSTEMS

ANAHEIM, CALIFORNIA - JUNE 1986

MA400470 REV D

# Contents

| Section 1 - General Information                          |                |

|----------------------------------------------------------|----------------|

| 1.1 INTRODUCTION                                         | 4              |

| Section 2 - Installation                                 | -              |

| 2.1 UNPACKING AND INSPECTION                             | 8              |

| 2.3 MODULE INSTALLATION AND CABLING                      | 11             |

| Section 3 - Programming Considerations                   | 15             |

| 3.3 RECEIVE BUFFER (RBUF)                                | 16             |

| 3.5 LINE PARAMETER REGISTER (LPR)                        | 20<br>21<br>22 |

| 3.9 TRANSMIT BUFFER ADDRESS REGISTER NUMBER 2 (TBUFFAD2) | 24             |

| Appendices                                               | 27             |

| APPENDIX B ADDRESS ASSIGNMENTS VIA SWITCH SW1            |                |

| APPENDIX D STAGGERED LOOPBACK CONNECTOR PINS             | ٦              |

# Figures/Tables

| Figure 1-1 | 3.5" Distribution Panel Hardw | ıar | ·e |   |  |   |     | 3  |

|------------|-------------------------------|-----|----|---|--|---|-----|----|

| Figure 1-2 | 5.18" Distribution Panel Hard | lwa | re | • |  |   |     | 4  |

| Figure 2-1 | Component Locations           |     |    |   |  |   |     | 8  |

| Figure 2-2 | Address Selection             |     |    |   |  |   |     | 8  |

| Figure 2-3 | Interrupt Vector Selection .  |     |    |   |  |   |     |    |

| Figure 2-4 |                               |     |    |   |  |   |     |    |

| Table 2-1  | J1 Connector Pin Assignments  |     |    |   |  | • | • , | 10 |

#### Section 1 - General Information

#### 1 1 INTRODUCTION

This manual provides general installation and programming information for the SCD-DHV11/16 16-line asynchronous communication multiplexer manufactured by Sigma Information Systems, Anaheim, California. The material in this manual is arranged into the following sections.

Section 1 - GENERAL INFORMATION. This section provides a general description of the SCD-DHV11/16. Specifications are included.

Section 2 - INSTALLATION. This section describes the procedures for setting up and installing the 16-line multiplexer. Device address and vector interrupt switch selections are included, along with cabling to I/O devices.

Section 3 - PROGRAMMING CONSIDERATIONS. This sections contains a detailed description of the SCD-DHV11/16 registers. Diagnostic testing is included

APPENDICES. The appendices contains Q bus signals and a complete list of switch configurations for the device address and the vector interrupts.

REF: DHV11.WPS/DM4

#### 1 2 GENERAL DESCRIPTION

The SCD-DHV11/16 is a 16-line asynchronous communication multiplexer. Sigma's dual-wide module is addressed as two separate 8-line devices that emulate two of DEC's DHV11 quad-wide boards. The SCD-DHV11/16 is software compatible with operating systems and diagnostics designed for the DEC\* module All lines are compatible with EIA RS-232-C and CCITT V 24 standard (data leads only)

Each communication line is independently programmable for word format and hardware character echo. Each line is also independently programmable for split transmit and receive baud rates up to 38 4K baud and for full or half duplex or auto echo operation.

Optional 19" rackmount communication panels are available for convenient cabling to user I/O devices. One panel contains 16 subminiature D-type RS-232-C connectors. The other panel contains 16 RJ11 connectors with DEC's\* H3173-A layout.

## 1 3 FEATURES

- 16 asynchronous serial lines on one dual wide module.

- Emulates two of DEC's DHV11s without requiring patches when interfacing with DEC LSI-11 and MicroVAX CPUs

- Compatible with EIA RS-232-C and CCITT V 24

- Programmable parameters individually set for each channel: baud rate word format, and character echo.

- Two contiguous switch selectable device addresses for lines 0-7 and lines 8-15.

- Optional rackmount panels available for convenient connection to I/O devices

- Two 256 character buffers for received characters.

- DMA for transmitted data

- Hardware or program-controlled break generation.

\*DEC and Q bus are registered trademarks of Digital Equipment Corporation

## 1.4 OPTIONAL DISTRIBUTION PANELS

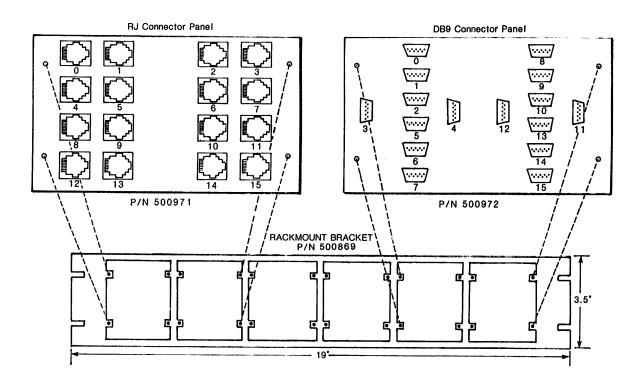

Two optional 19" rackmount brackets are available for convenient cabling to user's external I/O devices.

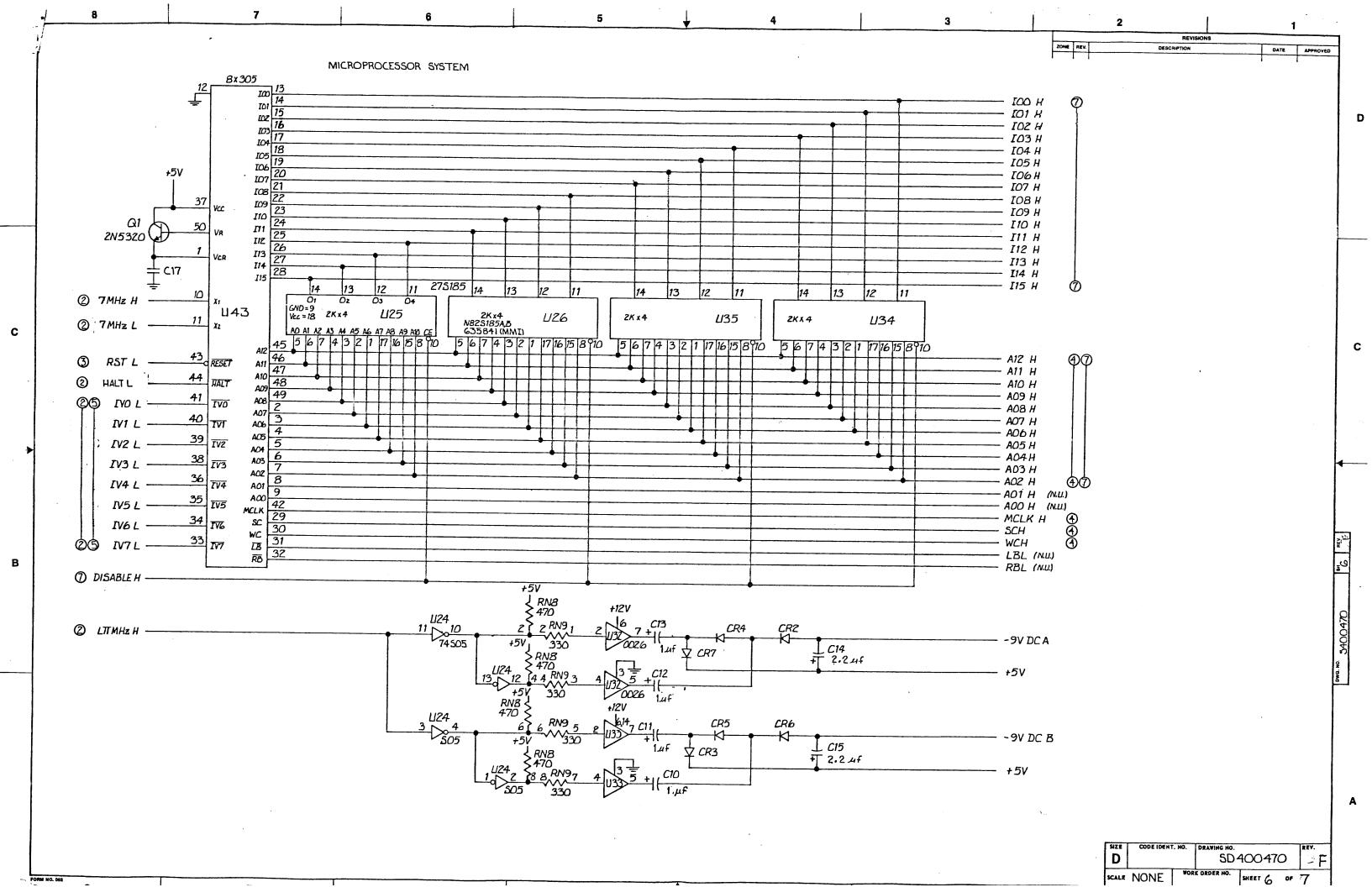

The rackmount bracket shown in Figure 1-1 accepts one or two optional distribution panels. Each distribution panel distributes signals from each SCD-DHV11/16 line to I/O connectors. The I/O connectors can be either subminiature DB9 connectors or RJ connectors.

FIGURE 1-1: 3.5" DISTRIBUTION PANEL HARDWARE

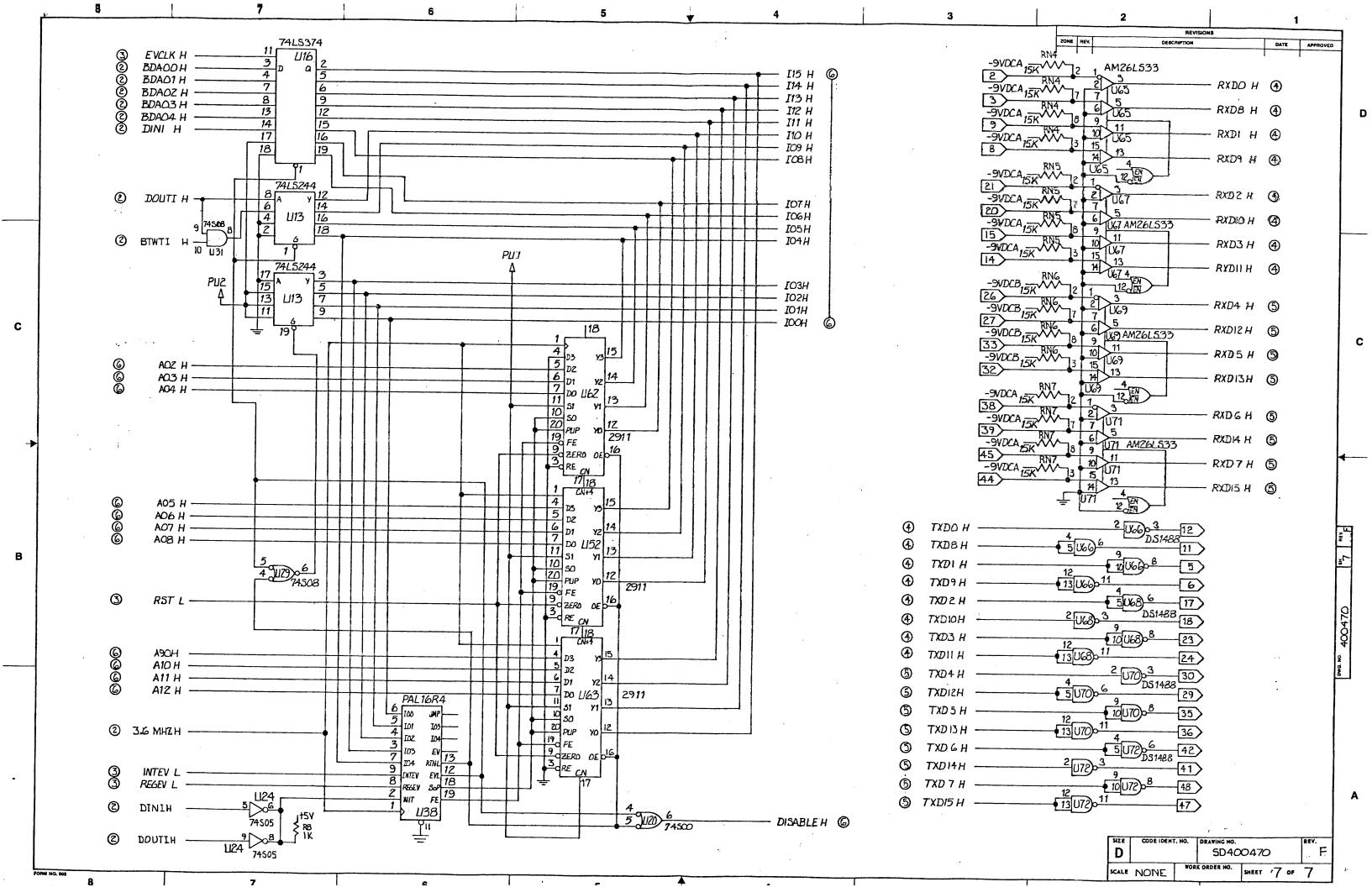

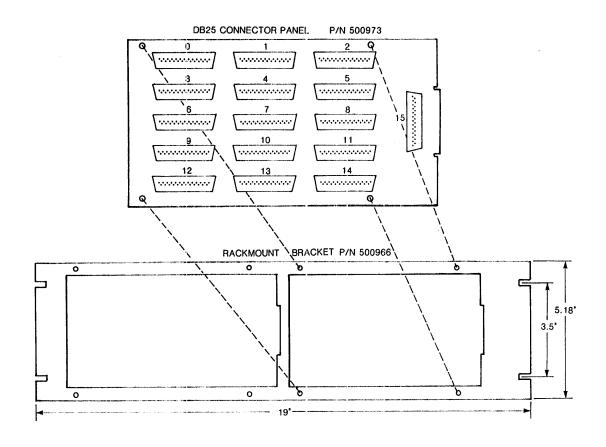

The rackmount bracket shown in Figure 1-2 accepts an optional distribution panel that distributes signals from each SCD-DHV11/16 line to DB25 I/O connectors.

FIGURE 1-2: 5.18" DISTRIBUTION PANEL HARDWARE

#### 1 5 **SPECIFICATIONS**

Size:

Standard dual-wide Q bus module

Power Requirements: +5V @ 3.5A

+12V @ 200mA

Interface:

EIA RS-232-C and CCITT V.24 standard (data leads

only)

Cables (Optional): Ribbon cable terminated with 16 D-type RS-232-C

connectors or to RJ11 connectors.

Distribution Panel: Optional 19" rackmount distribution panel contains four B I/O panels that distribute each line to a

subminiature D-type RS-232-C connector

alternately, to RJ11 connectors.

Full duplex or half duplex Operating Modes:

Each channel independently program controlled: 50, Baud Rates:

75, 110, 134.5, 150, 300, 600, 1200, 1800, 2000, 2400, 4800, 7200, 9600, 19.2K, and 38.4K baud.

Two contiguous addresses for lines 0-7 and lines 8-15 Device Address:

are switch selectable from 17760000 to 17770000

Two contiguous interrupts for lines 0-7 and lines Vector Interrupt:

8-15 are switch selectable from 000 to 760

Asynchronous. Serial by bit. Each line individually Data Format:

program controlled.

One start and 1, 1-1/2 (5 level code only), or 2 stop Stop/Start bits:

bits.

Character Bits: 5, 6, 7 or 8

Parity: Odd, Even, or None

Temperature:

0°C to 50°C Operating:

Storage: -45°C to 85°C

Humidity: 0% to 95% noncondensing

Altitude:

0 ft. to 10,000 ft. Operating: 0 ft. to 30,000 ft. Storage:

## Section 2 - Installation

## 2.1 UNPACKING AND INSPECTION

The SCD-DHV11/16 is shipped in a special packing carton designed to keep the module from vibrating and to give it maximum protection during shipment. The packing carton should be retained in case the unit requires reshipment.

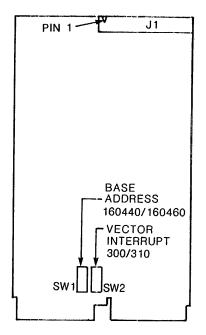

#### 2.2 FACTORY-SET SWITCHES

The SCD-DHV11/16 multiplexer is shipped configured with DEC standard address 160440 and vector interrupt 300. The location of the switches that determine these parameters is shown in Figure 2-1. Before installing modules, verify that the switches are set properly. The following sections describe the procedures to verify and/or reconfigure device address and vector interrupt.

FIGURE 2-1: COMPONENT LOCATIONS

#### 2.2.1 Device Address Selection

The device address for the SCD-DHV11/16 is set by switch SW1 shown in Figure 2-1. The address can range from 160000 to 177740. Figure 2-2 shows the relationship between the address bits and the switch positions.

The factory set address of 160440 is shown in Figure 2-2. A list of the complete address range with associated switch settings can be found in Appendix B.

|                   |     |         |          |         |         | -0FF    | = : | l, ON       | = 0     | <br>     |   |         |         |         |         |

|-------------------|-----|---------|----------|---------|---------|---------|-----|-------------|---------|----------|---|---------|---------|---------|---------|

| ADDRESS<br>BITS   |     | 14<br>1 |          |         |         |         |     | 08<br>3Y SW |         | 05       |   | 03<br>0 | 02<br>0 | 01<br>0 | 00<br>0 |

| SW1 POSI          | TIO | NS      |          | 1<br>ON | 2<br>0N | 3<br>ON |     | 5<br>OFF    | 6<br>0N | 8<br>0FF |   |         |         |         |         |

| BINARY<br>ADDRESS | 1   | 1       | 1        |         | •       |         |     | 1           |         | <br>1    | 0 | 0       | 0       | 0       | 0       |

| OCTAL<br>ADDRESS  | 1   |         | <b>-</b> |         |         | 0       |     |             | 4       | <br>     | 4 |         |         | 0       |         |

FIGURE 2-2: ADDRESS SELECTION

#### NOTE

The SCD-DHV11/16 can be considered as two of DEC's DHV11s. Lines 0 through 7 will have the device address selected by switch SW1. Lines 8 through 15 will have the selected device address +20 (octal).

#### 2.2.2 Interrupt Vector Selection

The interrupt vector for the SCD-DHV11/16 is set by switch SW2 shown in Figure 2-1. The vector interrupt can range from 000 to 770. Figure 2-3 shows the relationship between the interrupt vector bits and the switch positions.

The factory set interrupt of 300 is shown in Figure 2-3. A list of the complete interrupt range with associated switch settings can be found in Appendix C.

|                     |          | 0FF | = 0     | , ON | = 1.     |          |   |         |    |

|---------------------|----------|-----|---------|------|----------|----------|---|---------|----|

| VECTOR<br>BITS      | 08       |     |         |      | -        | 03       |   | 01<br>0 | 00 |

| SW2 POSITIONS       | 3<br>OFF |     | 5<br>0N |      | 7<br>OFF | 8<br>0FF |   |         |    |

| BINARY<br>INTERRUPT | 0        | 1   | 1       | 0    | 0        | 0        | 0 | 0       | 0  |

| OCTAL<br>INTERRUPT  |          | 3   |         |      | 0        |          |   | 0       |    |

FIGURE 2-3: INTERRUPT VECTOR SELECTION

#### NOTE

Lines 0 through 7 will have the interrupt vector selected by SW2. Lines 8 through 15 will have that vector +10 (octal).

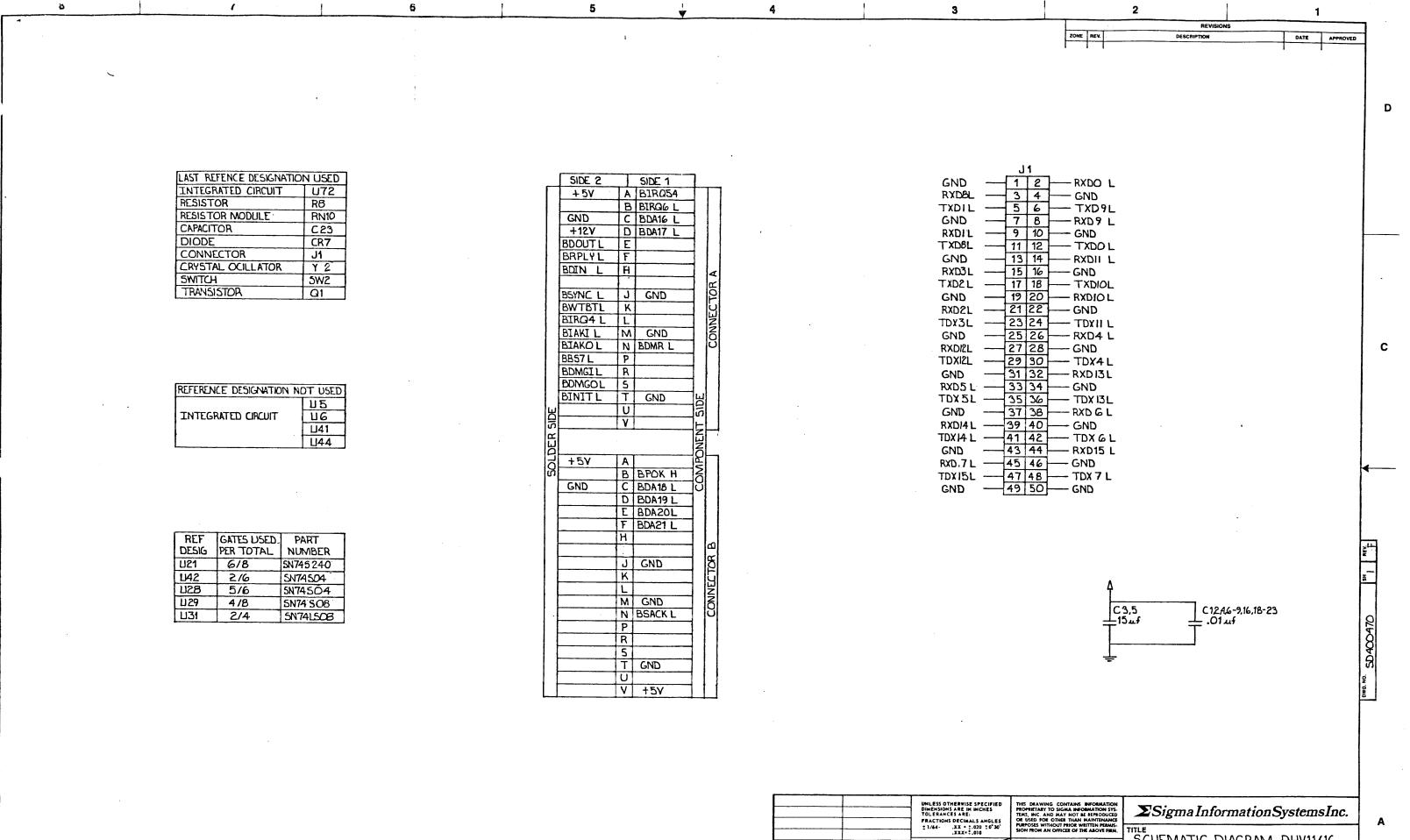

#### 2.3 MODULE INSTALLATION AND CABLING

The SCD-DHV11/16 plugs directly into an LSI-11 backplane dual slot (see Figure 2-2). The J1 connector provides the interface signals for the I/0 panels described in Figure 1-1. Pin assignments for the 50-pin connector are listed in Table 2-1.

|    | LINE<br>NUMBEI |     | SIG<br>RECEIVE<br>J1 PIN | NALS-<br>TRAN<br>NUME | ISMIT ]    |

|----|----------------|-----|--------------------------|-----------------------|------------|

| Ę  | 0              |     | 2<br>9                   | 12<br>5               |            |

|    | 1<br>2         |     | 21                       | 17                    | -          |

| Ĺ  | 3              |     | 15                       | 23                    | 3          |

|    | 4<br>5         |     | 26<br>33                 | 30<br>35              | ) <u> </u> |

|    | 7              |     | 38                       | 42                    |            |

| Ē  | 7              |     | 45                       | 48                    |            |

| Ĺ  | 8              |     | 3                        | 11                    | : ]        |

| L  | 9<br>10        |     | 8<br>20                  | 18                    | ) ]        |

| Ē  | 11             |     | 14                       | 24                    | í j        |

|    | 12             |     | 27                       | 29                    | j          |

|    | 13<br>14       |     | 32<br>39                 | 36<br>41              | j<br>1     |

| Ë  | 15             |     | 44                       | 41                    | ;          |

| Ĺ- | Pins           | not | listed                   | are                   | ground     |

TABLE 2-1: J1 CONNECTOR PIN ASSIGNMENTS

The cables from J1 plug into the PCBA of the I/O connector panels. The PCBA distributes J1 signals to each of the I/O lines specified on the connector side of the panels described in Figures 1-1 and 1-2.

#### 2.4 TESTING

Diagnostic testing can be run using DEC's VDHA??, VDHB??, and VDHC?? functional verification tests. Only parts of these tests are used for the SCD-DHV11/16.

VDHA?? \*TESTS 1-27 VDHB?? TESTS 1-15 AND 24-26 VDHC?? TESTS 1-4

Use the following procedure to run the functional verification tests.

1. Run the tests in the internal loopback mode (staggered loopback connector not installed). Run the diagnostics for one error-free pass. Any fault message indicates a defective SCD-DHV11/16. The underlined parameters below are keyboard entries.

#### RUNNING VDHA??

(\*Test 11 does not run on LSI-11/23 due to timing differences)

;run VDHA test .RUN VDHA?? ;system response VDHABO.BIC :Start tests 1 through 27 DR>START/FLAG:HOE<CR> ;with Halt on Error (HOE) flag ;Change hardware configuration CHANGE HW (L) ? Y<CR> # UNITS (D) ? 2<CR> ;Specify two DHV11 emulation ;Specify SCD-DHV11/16 address UNIT O CSR ADDRESS: (0) 160460 ? 160440 CR> ;for lines 0-7 (unit 0) INTERRUPT VECTOR ADDRESS: (0) 300 ? Y<CR> ; Specify vector interrupt ACTIVE LINE BIT MAP: (0) 377 ? <CR> INTERRUPT LEVEL: (0) 4 ? 5<CR> :Specify level 5 ;Repeat for CSR address 160460, UNIT 1 ;interrupt vector 310 (unit 1 ;= lines 7-15) :Test will begin. CHANGE SW (L) ? N<CR>

CTRL C

;Terminate test with CTRL C.

2. To run the test in the staggered loopback mode requires removal of the 50-conductor cable from the SCD-DHV11/16 module. A staggered loopback connector, shown in Figure 2-4, is installed into the 50-pin connector on the module. The pin assignments for the staggered loopback connector are shown in Appendix D.

FIGURE 2-4: STAGGERED LOOPBACK CONNECTOR

3. Run the tests in the staggered loopback mode for two error-free passes. Any fault message indicates a defective SCD-DHV11/16 or cable. The underlined parameters below are keyboard entries.

#### RUNNING VDHB??

```

.RUN VDHB??

;run VDHB test

VDHBCO.BIC

:system response

DR>START/FLAG:HOE/TEST:1-15:24-26<CR>

:Start tests 1-15 and 24-26

;with Halt on Error (HOE) flag

CHANGE HW (L) ? Y<CR>

:Change hardware configuration

;Specify two DHV11 emulation

# UNITS (D) ? 2<CR>

;Specify SCD-DHV11/16 address

UNIT 0

for lines 0-7 (unit 0)

CSR ADDRESS: (0) 160460 ? 160440 CR>

INTERRUPT VECTOR ADDRESS: (0) 300 ? Y<CR> ; Specify vector interrupt

ACTIVE LINE BIT MAP: (0) 377 ? <CR>

TYPE OF LOOPBACK (1 = INTERNAL, 2 =

;Specify staggered loopback

H3277, 3 = H325: (0) 2<CR>

:test (H3277 installed)

INTERRUPT LEVEL: (0) 4?5<CR>

;Specify level 5

:Repeat for CSR address 160460.

UNIT 1

;interrupt vector 310 (unit 1

:= lines 7-15)

;Test will begin.

CHANGE SW (L) ? N<CR>

CTRL C

:Terminate test with CTRL C.

```

## RUNNING VDHC??

| RUN VDHC??                                                                                                                                                                                                                                                                                                                           | ;run VDHC test                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDHCBO.BIC<br>DR>START/FLAG:HOE/TEST:1-4 <cr></cr>                                                                                                                                                                                                                                                                                   | ;system response<br>;Start tests 1 through 4<br>;with Halt on Error (HOE) flag                                                                                                                                       |

| •                                                                                                                                                                                                                                                                                                                                    | •                                                                                                                                                                                                                    |

| CHANGE HW (L) ? Y <cr> # UNITS (D) ? 2<cr> UNIT 0 CSR ADDRESS: (0) 160460 ? 160440<cr> INTERRUPT VECTOR ADDRESS: (0) 300 ? Y<cr> ACTIVE LINE BIT MAP: (0) 377 ? <cr> TYPE OF LOOPBACK (1 = INTERNAL, 2 = H3277, 3 = H325, 4 = MODEM, 5 = KEYBOARD ECHO): (0) 2<cr> INTERRUPT LEVEL: (0) 4 ? 5<cr></cr></cr></cr></cr></cr></cr></cr> | ;Change hardware configuration;Specify two DHV11 emulation;Specify SCD-DHV11/16 address;for lines 0-7 (unit 0);Specify vector interrupt;Specify staggered loopback;test (H3277 equivalent;installed);Specify level 5 |

| UNIT 1                                                                                                                                                                                                                                                                                                                               | ;Repeat for CSR address 160460,<br>;interrupt vector 310 (unit 1                                                                                                                                                     |

| CHANGE SW (L) ? N <cr></cr>                                                                                                                                                                                                                                                                                                          | ;= lines 7-15)<br>;Test will begin.                                                                                                                                                                                  |

| •                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                      |

| CTRL C                                                                                                                                                                                                                                                                                                                               | ;Terminate test with CTRL C.                                                                                                                                                                                         |

# Notes

# **Section 3 - Programming Considerations**

#### 3.1 INTRODUCTION

There are two sets of registers for the SCD-DHV11/16. The registers listed below are associated with channels 0-7. A set of the same registers with "Base + 20 (octal) addresses is associated with channels 8-15. The term "Base" is the address selected by switch SW1 (Section 2.2.1).

| Control/Status Register   | CSR       | Base      | Read/Write |

|---------------------------|-----------|-----------|------------|

| Receive Buffer            | RBUF      | Base + 2  | Read Only  |

| Transmit Character        | TXCHAR*   | Base + 2  | Write Only |

| Line Parameter Register   | LPR*      | Base + 4  | Read/Write |

| Line Status               | STAT*     | Base + 6  | Read Only  |

| Line Control              | LNCTRL*   | Base + 10 | Read/Write |

| Transmit Buffer Address 1 | TBUFFAD1* | Base + 12 | Read/Write |

| Transmit Buffer Address 2 | TBUFFAD2* | Base + 14 | Read/Write |

| Transmit Buffer Count     | TBUFFCT*  | Base + 16 | Read/Write |

<sup>\*</sup>There are eight indirect address registers associated with each of these registers: one for each channel. When the indirect address registers are accessed, the address is indexed by the contents of CSR bits 03-00.

The SCD-DHV11/16 clears MASTER RESET when initialization and self-test are complete; the red LED is turned on and the module is then operational with the following default register parameters.

Send and receive 9600 bits/s Eight data bits One stop bit No parity Parity odd Auto-flow off No loopback

RX disable TX enabled No break on line DMA character counters zero DMA start addresses zero TX.DMA.START cleared TX.DMA.ABORT cleared.

#### CONTROL AND STATUS REGISTER (CSR) 3.2

|      |     | 15   | !  | 14    | 13         | 12  | !   | 11   | 10 | 09        | ! | 80 | 07    | 06!  | 05  | 04  | 03  | ! 02 | 01  | 00   |

|------|-----|------|----|-------|------------|-----|-----|------|----|-----------|---|----|-------|------|-----|-----|-----|------|-----|------|

|      | !   | R    | !  | R/W   | R          | R   | !   | R    | R  | R         | ! | R  | R     | R/W! | R/W | /// | R/2 | !R/W | R/W | R/W! |

|      |     | !    |    | !     | !          | !   |     | !    |    |           |   | !  | <br>! | !    | !   |     | !   |      |     | !    |

| Tran | s-  | . !  |    | !     | !          | !   |     |      |    | !         |   |    | !     | !    | !   |     |     |      | !   |      |

| mitt | er  | . !  |    | į     | į.         | !   |     |      |    | ļ         |   |    | i     | !    | !   |     |     |      | !   |      |

| Acti | on  | -!   |    | !     | ļ          | !   |     |      |    | !         |   |    | ļ     | !    | i   |     |     |      | !   |      |

| Tran | sm  | ii t |    | !     | !          | !   |     |      |    | !         |   |    | !     | !    | į   |     |     |      | !   |      |

| Inte | rr  | upt  | t  | !     | !          | !   |     |      |    | !         |   |    | !     | !    | !   |     |     |      | !   |      |

| Enab | 1e  | ·    |    | !     | !          | !   |     |      |    | !         |   |    | !     | !    | !   |     |     |      | !   |      |

| Diag | no  | st   | ic | Fai   | <b> -!</b> | !   |     |      |    | !         |   |    | !     | !    | !   |     |     |      | !   |      |

| Tran | SIT | ıi t | DI | MA E  | rror       | !   |     |      |    | !         |   |    | !     | !    | !   |     |     |      | !   |      |

| Tran | SIT | ii t | L  | ine   |            |     |     |      |    | <b>-!</b> |   |    | i     | !    | !   |     |     |      | !   |      |

| Rece | iv  | ed   | D  | ata A | \vai       | lab | le. |      |    |           |   |    | !     | į    | !   |     |     |      | !   |      |

| Rece | iv  | er   | I  | nter  | rupt       | In: | te  | rrup | t  |           |   |    |       | !    | !   |     |     |      | !   |      |

| Mast |     |      |    |       |            |     |     |      |    |           |   |    |       |      | !   |     |     |      | !   |      |

| Indi | re  | ct   | A  | ddre  | ss R       | egi | s t | er   |    |           |   |    |       |      |     |     |     |      | !   |      |

| BIT | MNEMONIC   | DESCRIPTION                                                                                                                                                                                                                                                |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | TX.ACTION  | This bit is set by SCD-DHV11/16 when (1) the last character of a DMA buffer has left the DUART or (2) A DMA transfer has been aborted or terminated by the SCD-DHV11/16. Cleared by MASTER.RESET.                                                          |

| 14  | TXIE       | When set, this bit allows the SCD-DHV11/16 to interrupt the host if CSR bit 15 becomes set. CLEARED BY BINIT (bus initialize), power up or down, but not by MASTER.RESET.                                                                                  |

| 13  | DIAG.FAIL  | This bit is set when the internal diagnostics detects an error (LED off). Clear is indicated when LED is on.                                                                                                                                               |

| 12  | TX.DMA.ERR | If this bit, along with TX.ACTION, is set, there is a memory parity error or else the channel indicated by CSR bits 11-08 has failed to transfer DMA data within the time allotted for the bus request to be acknowledged. TBUFFAD1 and TBUFFAD2 registers |

contain the address of the memory location that could not be accessed. TBUFFCT will be cleared.

11-08 TX.LINE

If TX.ACTION is set, these its contain the binary number of the channel which has (1) completed a DMA block transfer, (2) accepted a single character for transmission, or (3) aborted a DMA block transfer.

If TX DMA ERR is also set, these bits contain the binary number of the channel that failed during a DMA transfer.

7 RX.DATA.AVAIL

When set, this bit indicates that a received character is available. This bit is cleared when the FIFO is empty It is used to request and RX interrupt

Set after MASTER RESET because the FIFO contains diagnostic information.

6 RXIE

When set, this bit allows the SCD-DHV11/16 to interrupt the host when RX DATA AVAIL is set. An interrupt is generated if (1) RXIE is set and a character is placed into an empty FIFO and (2) the FIFO is not empty and RXIE is changed from 0 to 1. Cleared by BINIT, power up or down, but not by MASTER RESET.

5 MASTER RESET

Set by the host to reset SCD-DHV11/16. Cleared after self-test and initialization sequence.

Set by BINIT (bus initialization) or by CPU setting CSR bit 5. The host should not write to this bit when it is already set.

03-00 IND.ADDR.REG

These bits specify the channel to be used for accessing a block of indexed register (Section 3.1). They form the binary number of the channel to be accessed.

| Bit     | Cha     | nnel     |                                     |

|---------|---------|----------|-------------------------------------|

| 3 2 1 0 | (DHV A) | *(DHV B) | *DHV B Base Address<br>= DHV A Base |

| 0 0 0 0 | 0       | 8        | Address + 20 <sub>8</sub>           |

| 0 0 0 1 | 1       | 9        | 9                                   |

| 0 0 1 0 | 2       | 10       |                                     |

| 0 0 1 1 | 3       | 11       |                                     |

| 0 1 0 0 | 4       | 12       |                                     |

| 0 1 0 1 | 5       | 13       |                                     |

| 0 1 1 0 | 6       | 14       |                                     |

| 0 1 1 1 | 7       | 15       |                                     |

#### 3.3 RECEIVE BUFFER (RBUF)

|       | 1                                                                    | 5   | !  | 14   | 13 | 12 | ! | 11 | 10 | 09 | ! | 80 | 07 | 06 | 1 | 05 | 04 | 03 | ! | 02 | 01 | 00 |

|-------|----------------------------------------------------------------------|-----|----|------|----|----|---|----|----|----|---|----|----|----|---|----|----|----|---|----|----|----|

|       | !                                                                    | R   | !  | R    | R  | R  | ! | R  | R  | R  | ! | R  | R  | R  | ! | R  | R  | R  | ! | R  | R  | R! |

|       |                                                                      | !   |    | !    | !  | !  |   | !  |    |    |   | !  | !  |    |   |    |    |    |   |    |    | !  |

| Data  |                                                                      | ļ   |    | !    | !  | !  |   |    |    | !  |   |    |    |    |   |    | !  |    |   |    |    |    |

| Valid | l                                                                    | !   |    | ļ.   | !  | !  |   |    |    | !  |   |    |    |    |   |    | !  |    |   |    |    |    |

| Actio | n-                                                                   | .!  |    | ļ.   | !  | !  |   |    |    | !  |   |    |    |    |   |    | !  |    |   |    |    |    |

| 0verr | ur                                                                   | 1   |    | !    | ļ  | !  |   |    |    | !  |   |    |    |    |   |    | !  |    |   |    |    |    |

| Error | ·                                                                    |     |    | !    | !  | !  |   |    |    | !  |   |    |    |    |   |    | !  |    |   |    |    |    |

| Frami | no                                                                   | 1 6 | rı | ror- | !  | !  |   |    |    | !  |   |    |    |    |   |    | !  |    |   |    |    |    |

| Parit |                                                                      |     |    |      |    | !  |   |    |    | !  |   |    |    |    |   |    | !  |    |   |    |    |    |

|       | -                                                                    |     |    |      |    |    |   |    |    | !  |   |    |    |    |   |    | !  |    |   |    |    |    |

| Recei | Receive Line Number! ! Received Character OR Diagnostic Information! |     |    |      |    |    |   |    |    |    |   |    |    |    |   |    |    |    |   |    |    |    |

| BII | MNEMONIC    | DESCRIPTION                                                                                                                                                                      |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | DATA.VALID  | Set if FIFO is not empty. Cleared by MASTER.RESET or by the FIFO becoming empty. Always set after a successful MASTER.RESET since self-test information is loaded into the FIFO. |

| 14  | OVERRUN.ERR | Set if one or more previous characters of the channel (bits 11-08) were lost due to a full FIFO or failure to service the UARTs (see RX.CHAR).                                   |

## NOTE

The all 1s code for bits 14-12 indicates that diagnostic information is held in RBUF bits 07-00.

| 13    | FRAME.ERR  | Set if the first stop bit of the received character was not detected (see RX.CHAR).                                                                            |

|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12    | PARITY.ERR | Set if a character has a parity error and if parity is enabled for the channel specified by bits $11\text{-}08$ (see RX.CHAR).                                 |

| 11-08 | RX.LINE    | These bits contain the binary number of the channel on which the character of RBUF bits 07-00 was received. See CSR bits 03-00 for channel binary definitions. |

07-00 RX.CHAR

If RBUF bits 14-12 = 000, these bits contain the oldest character in the FIFO and the character is good.

If RBUF bits 14-12 = 001, 010, or 011. the oldest character in the FIFO is bad.

If RBUF bits 14-12 = 111, these bits contain diagnostic information.

If there is an overrun condition, the data buffer for the selected channel will be cleared and data will be lost.

## 3 4 TRANSMIT CHARACTER REGISTER (TXCHAR)

| 1                | 15 !  | 14   | 13   | 12  | !        | 11  | 10   | 09  | ! | 80  | 07 | 06 | ! | 05 | 04 | 03 | ! | 02 | 01 | 00 |

|------------------|-------|------|------|-----|----------|-----|------|-----|---|-----|----|----|---|----|----|----|---|----|----|----|

| !                | W !   | ///  | //// | /// | !        | /// | //// | /// | ! | /// | W  | W  | ! | W  | M  | W  | ! | W  | W  | W! |

|                  | <br>! |      |      |     |          |     |      |     |   |     | !  |    |   |    |    |    |   |    |    | !  |

| Transmi<br>Valid | it D  | ata  |      |     |          |     |      |     |   |     |    |    |   |    |    | !  |   |    |    |    |

| Transmi          | it C  | hara | cter |     |          |     |      |     |   |     |    |    |   |    |    | !  |   |    |    |    |

|                  |       |      |      |     | <b>.</b> |     |      | OM. |   |     |    |    |   |    |    |    |   |    |    |    |

| BIT | MNEMONIC   | DESCRIPTION     |

|-----|------------|-----------------|

|     | LUALITONIA | DE201/11 11/01/ |

TX.DATA.VALID When set, this bit instructs the SCD-DHV11/16 to transmit the character contained in bits 07-00. The bit is sensed by the SCD-DHV11/16, which then transfer the character, clears the bit, and sets TX.ACTION.

07-00 TX.CHAR These bits contain the character to be transmitted. The LSB is bit 0 for 7-, 6-, or 5-bit characters. Unused bits must be 0.

#### 3 5 LINE PARAMETER REGISTER (LPR)

15 ! 14 13 12 ! 11 10 09 ! 08 07 06 ! 05 04 03 ! 02 01 00 !R/W!R/W R/W R/W !R/W R/W R/W !R/W R/W R/W R/W R/W !///////// \_\_\_\_\_\_

| !! !.            | ! | !  | ! | ! | !! |

|------------------|---|----|---|---|----|

| !                | ! | !  | ! | ! | !  |

| Transmit !       | ! | ļ. | ļ | ļ | !  |

| Speed!           | ! | !  | ! | ! | !  |

| Receive Speed    | ! | !  | ! | ! | !  |

| Stop Code        |   | !  | į | ! | !  |

| Even Parity      |   |    | ! | ! | !  |

| Parity Enable    |   |    |   | ! | !  |

| Character Length |   |    |   |   | !  |

BIT MNEMONIC DESCRIPTION

15-12 TX SPEED

Defines the transmit data rate as shown below. Notice that the rates are associated with either Group A or Group B

|    | B <b>i</b> 1 | t  |    | Baud    | Rate    |

|----|--------------|----|----|---------|---------|

| 15 | 14           | 13 | 12 | Group A | Group B |

| 0  | 0            | 0  | 0  | 50      |         |

| 0  | 0            | 0  | 1  |         | 75      |

| 0  | 0            | 1  | 0  | 110     | 110     |

| 0  | 0            | 1  | 1  | 134 5   | 134.5   |

| 0  | 1            | 0  | 0  |         | 150     |

| 0  | 1            | 0  | 1  | 300     | 300     |

| 0  | 1            | 1  | 0  | 600     | 600     |

| 0  | 1            | 1  | 1  | 1200    | 1200    |

| 1  | 0            | 0  | 0  |         | 1800    |

| 1  | 0            | 0  | 1  |         | 2000    |

| 1  | 0            | 1  | 0  | 2400    | 2400    |

| 1  | 0            | 1  | 1  | 4800    | 4800    |

| 1  | 1            | 0  | 0  | 7200    |         |

| 1  | 1            | 0  | 1  | 9600    |         |

| 1  | 1            | 0  | 0  |         | 19200   |

| 1  | 1            | 1  | 1  | 38400   |         |

NOTE

The SCD-DHV11/16 uses dual-channel ICs Channels 0-8, 1-9, 2-10, 3-11, 4-12, 5-13, 6-14, 7-15 are paired. Baud rates for paired channels (e g , channel 1 and channel 9) must belong to the same group. It is the responsibility of the user to select transmit and receive data rates of the same group (A or B) for any pair of channels

| 11-08 | RX.SPEED    | Defines the receive data rate the same as TX.SPEED. Restrictions are the same; paired channels must have baud rates within the same group.                  |

|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |             | Set to 1101 by MASTER.RESET.                                                                                                                                |

| 07    | STOP.CODE   | Defines the length of the transmitted stop bit.                                                                                                             |

|       |             | <pre>0 = 1 stop bit for 5-, 6-, 7-, or 8-bit     characters 1 = 2 stop bits for 6-, 7-, or 8-bit characters     OR 1.5 stop bits for 5-bit characters</pre> |

|       |             | Cleared by MASTER.RESET.                                                                                                                                    |

| 07    | EVEN.PARITY | If LPR bit 5 is set, this bit defines the type of parity.                                                                                                   |

|       |             | 1 = even parity, 0 = odd parity                                                                                                                             |

|       |             | Cleared by MASTER.RESET.                                                                                                                                    |

| 05    | PARITY.ENAB | Causes a parity bit to be generated on transmit, and checked and stripped on receive.                                                                       |

|       |             | 1 = parity enabled, 0 - parity disabled                                                                                                                     |

|       |             | Cleared by MASTER.RESET.                                                                                                                                    |

| 04-03 | CHAR.LGTH   | Defines the length of characters.                                                                                                                           |

|       |             | 00 = 5 bits                                                                                                                                                 |

# 3.6 LINE STATUS REGISTER (LPR)

| 15 ! 14 |   |   |   |   |   |   |    |   |   |   |   |   |   |    |

|---------|---|---|---|---|---|---|----|---|---|---|---|---|---|----|

| ! 0 ! 0 | 0 | 0 | 0 | 0 | 0 | ! | 0! | 0 | 0 | 0 | ! | 0 | 0 | 0! |

The Line Status Register is not used in the SCD-DHV11/16. All bits are read as Os.

#### 3.7 LINE CONTROL REGISTER (LNCTRL)

|       | 15  | !  | 14  | •   | 13 |    | 12 | !  | 1  | 1  | 1  | 0  | 0  | 9  | !           | 80  | 07    | 06  | !  | 05     | 04    | 03       | !   | 02    | 01    | 00    |

|-------|-----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|-------------|-----|-------|-----|----|--------|-------|----------|-----|-------|-------|-------|

|       | !// | /! | /// | //  | // | // | // | /! | // | // | // | // | // | // | <u>'!</u> , | /// | R/W   | R/W | !  | R/W    | R/W   | R/W      | ! F | R/W   | R/W   | R/W   |

|       |     |    |     |     |    |    |    |    |    |    |    |    |    |    |             |     | <br>! |     | -! | :<br>! | <br>! | <br>!    |     | <br>! | <br>! | <br>! |

| Maint | ena | nc | e M | lod | e  |    |    |    |    |    |    |    |    |    | . <b></b> . |     |       | !   |    | 1      | !     | 1        |     | 1     | !     | İ     |

| Force |     |    |     |     |    |    |    |    |    |    |    |    |    |    |             |     |       |     |    |        |       |          |     |       |       |       |

| Outgo |     |    |     |     |    |    |    |    |    |    |    |    |    |    |             |     |       |     |    |        |       |          |     |       |       |       |

| Break | (   |    |     |     |    |    |    |    |    |    |    |    |    |    | <b>.</b>    |     |       |     |    |        |       | <u>!</u> |     | į     | ĺ     | Ì     |

| Recei |     |    |     |     |    |    |    |    |    |    |    |    |    |    |             |     |       |     |    |        |       |          |     |       |       |       |

| Incom |     |    |     |     |    |    |    |    |    |    |    |    |    |    |             |     |       |     |    |        |       |          |     |       |       |       |

| Trans |     |    |     |     |    |    |    |    |    |    |    |    |    |    |             |     |       |     |    |        |       |          |     |       |       |       |

BIT MNEMONIC DESCRIPTION

07-06 MAINTENANCE

These bits can be written by the driver or test programs with codes are follows:

00 = Normal operation

- 01 = Automatic echo mode. Received data is retransmitted (regardless of TX.ENA state) at the receiver baud rate. Received characters are processed and placed in the received character FIFO. The SCD-DHV11/16 does not transmit any characters including internally generated flow-control characters). bit must be set when operating in this mode.

- 10 = Local loopback The UART channel output is internally connected to the input. Normal received data is ignored and the transmit data line is held marking. Flow-control characters are looped back. Transmit baud rate is used both for transmission and reception. TX.ENA bit controls transmission.

- 11 = Remote loopback -Received data is retransmitted at the received baud rate. Data is not placed in the receiver FIFO. TX.ENA is ignored.

Cleared by MASTER.RESET.

| 05 | FORCE.XOFF   | Set by the program to indicate that the selected channel is congested at the host (e.g., typeahead buffer full). The SCD-DHV11/16 sends an X-OFF code. Until the bit is reset, X-OFF is sent after every alternate character received on the channel. When the bit is reset, an X-ON is sent unless IAUTO is set and the FIFO is critical. |

|----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04 | OAUTO        | When set (if RX.ENA is also set) the SCD-DHV11/16 automatically responds to X-ON and X-OFF codes received from a channel. The SCD-DHV11/16 uses the TX.ENA bit in TBUFFAD2 to stop and start the flow. Cleared by MASTER.RESET.                                                                                                            |

| 03 | BREAK        | When set, this bit forces the transmitter of the selected channel to the spacing state. Transmission is restarted when the bit is cleared. Cleared by MASTER.RESET.                                                                                                                                                                        |

| 02 | RX.ENA       | If set, the receiver channel is enabled. Cleared by MASTER.RESET.                                                                                                                                                                                                                                                                          |

| 01 | IAUTO        | If set, the SCD-DHV11/16 controls incoming characters by transmitting X-ON and X-OFF codes. If the FIFO becomes congested, the SCD-DHV11/16 send X-OFF code to channels. X-ON is sent when the congestion is reduced. Cleared by MASTER.RESET.                                                                                             |

|    |              | X-ON code = 21 (octal) = DC1 = CTRL Q<br>X-OFF code = 23 (octal) = DC3 = CTRL S                                                                                                                                                                                                                                                            |

| 00 | TX.DMA.ABORT | Set by the driver program to halt transfer of DMA buffer. The transfer can be continued by clearing TX.DMA.ABORT and then setting TX.DMA.START. No characters are lost.                                                                                                                                                                    |

|    |              |                                                                                                                                                                                                                                                                                                                                            |

$\mathsf{TX.DMA.ABORT}$  must be clear before setting  $\mathsf{TX.DMA.START}$  or else the transfer is aborted before characters are transmitted.

Cleared by MASTER.RESET.

24

#### 3.8 TRANSMIT BUFFER ADDRESS REGISTER NUMBER 1 (TBUFFAD1)

15 ! 14 13 12 ! 11 10 09 ! 08 07 06 ! 05 04 03 ! 02 01 00 !R/W!R/W R/W R/W !R/W R/W !R/W R/W !R/W R/W R/W !R/W R/W !R/W R/W! \_\_\_\_\_

Transmit DMA Address----!

BIT MNEMONIC DESCRIPTION

15-00 TBUFFAD

Contains the low byte of the Transmit DMA buffer address. Cleared by MASTER.RESET. See Section 3.9.

#### TRANSMIT BUFFER ADDRESS REGISTER NUMBER 2 (TBUFFAD2) 3.9

15 ! 14 13 12 ! 11 10 09 ! 08 07 06 ! 05 04 03 ! 02 01 00 !R/W! /////// ! /////// ! /// R/W ///!R/W R/W R/W !R/W R/W! ! Trans-! mit Enable Transmit DMA Start----!

Transmit DMA Address (High Order)-----!

DESCRIPTION BIT MNEMONIC

15 TX.ENA When cleared, the SCD-DHV11/16 will transmit only internally generated flow-control character. In the OAUTO mode, this bit is used by the SCD-DHV11/16 to control outgoing characters. Set by MASTER.RESET.

07 TX.DMA.START Set by the host to start a DMA transfer. SCD-DHV11 resets the bit before returning TX.ACTION. Cleared by MASTER.RESET.

After setting this bit, the host must not write to TBUFFCT, TBUFFAD1 or TBUFFAD2 bits 07-00 until the TX.ACTION report is returned.

05-00 TBUFFAD

These bits contain the high order byte (bits 21-16) of the DMA address.

Before a DMA transfer, TBUFFAD1 and the low byte of TBUFFAD2 are loaded with the start address of the DMA buffer. This address is not valid during a DMA transfer. When TX.ACTION is returned, the address is valid. Cleared by MASTER.RESET.

#### 3.10 TRANSMIT DMA BUFFER COUNTER (TBUFFCT)

Transmit Character Count-----!

BIT MNEMONIC

DESCRIPTION

15-00 TX.CHAR.CT

Loaded with the number of characters to be transferred by DMA. The number of character is specified as a 16-bit unsigned integer.

After a DMA transfer is aborted, this location holds the number of characters left to be transferred.

Notes

| !<br>!<br>! DIN | CTCMAL        |         |         | LSI-        | !!         |     | CTONAL  |     | LSI-  |         |

|-----------------|---------------|---------|---------|-------------|------------|-----|---------|-----|-------|---------|

| ! PIN           | SIGNAL        | VAX     | 11//3   | 11/23       | : :<br>    |     | SIGNAL  | VAX | 11/73 | 11/23   |

| ! AA1           | BIRQ5L        |         |         |             | :<br>! !   | AA2 | +5٧     |     |       |         |

| ! AB1           | BIRQ6L        |         |         |             |            | AB2 | -12V    | N/U | N/U   |         |

| ! AC1           | BDAL16L       |         |         |             | !!         |     | GND     |     | -     |         |

| ! AD1           | BDAL17L       |         |         |             | !!         | AD2 | +12V    |     | N/U   |         |

| ! AE1           | *SSPARE1      | N/U     | N/U     | SINGLE STEP | !          | AE2 | BDOUTL  |     |       |         |

| ! AF1           | *SSPARE2      | SRUNL   | SRUNL   | SRUNL       | !!         | AF2 | BRPLYL  |     |       |         |

| ! AH1           | *SSPARE3      | N/U     | N/U     | SRUNL       | !!         | AH2 | BDINL   |     |       |         |

| ! AJ1           | GND           |         |         |             | !!         |     | BSYNCL  |     |       |         |

| ! AK1           | *MSPAREA      | N/U     | N/U     | N/U         | !!         |     | BWTBTL  |     |       |         |

| ! AL1           | *MSPAREB      | N/U     | N/U     | N/U         | !!         | AL2 | BIRQ4L  |     |       |         |

| ! AM1           | GND           |         |         |             | !!         | AM2 | *BIAK1L |     | N/U   | MMUSTRH |

| ! AN1<br>!      | BDMRL         |         |         |             | ! !<br>! ! | AN2 | *BIAKOL |     | BIAKL |         |

| ! AP1           | BHALTL        |         |         |             | !!         | AP2 | BBS7L   |     |       |         |

| ! AR1           | BREFL         |         | N/U     | N/U         | !!         | AR2 | *BDMG1L |     | N/U   | UBMAAPL |

| ! AS1           | +12VB         | N/U     | N/U     |             | !!         | AS2 | *BDMGOL |     |       |         |

| ! AT1           | GND           |         |         |             | !!         | AT2 | BINITL  |     |       |         |

| ! AU1           | PSPARE1       | N/U     | N/U     |             | !!         | AU2 | BDALOL  |     |       |         |

| ! AV1           | +5 <b>V</b> B | N/U     |         |             | !!<br>!!   | AV2 | BDAL1L  |     |       |         |

| ! BA1           | BDCOKH        |         |         |             | !!         | BA2 | +57     |     |       |         |

| ! BB1           | BPOKH         |         |         |             | !!         | BB2 | -12V    | N/U | N/U   |         |

| ! BC1           | *SSPARE4      |         |         | MMUDAL18H   |            |     | GND     |     |       |         |

| ! BD1           | *SSPARE5      |         |         | MMUDAL19H   |            |     | +12V    |     | N/U   |         |

| ! BE1           | *SSPARE6      |         |         | MMUDAL20H   |            | BE2 | BDAL2L  |     |       |         |

| ! BF1<br>!      | *SSPARE6      | BUALZIL | BDALZIL | MMUDAL21H   | ! !<br>! ! | BF2 | BDAL3L  |     |       |         |

| ! BH1           | *SSPARE8      | N/U     | N/U     | CLKDISL     | !!         | BH2 | BDAL4L  |     |       |         |

| BJ1             | GND           |         |         |             | !!         | BJ2 | BDAL5L  |     |       |         |

| ! BK1           | *MSPAREB      | N/U     | N/U     | N/U         | !!         | BK2 | BDAL6L  |     |       |         |

| ! BL1           | *MSPAREB      | N/U     | N/U     | N/U         | !!         |     | BDAL7L  |     |       |         |

| ! BM1           | GND           |         |         |             | !!         | BM2 | BDAL8L  |     |       |         |

| ! BN1<br>!      | BSACKL        |         |         |             | :          | BN2 | BDAL9L  |     |       |         |

| BP1             | BIRQ7L        |         |         |             | !!         | BP2 | BDAL10L |     |       |         |

| ! BR1           | BEVNTL        |         |         | 4615        | !!         | BR2 | BDAL11L |     |       |         |

| ! BS1           | PSPARE4       | N/U     | N/U     | +12VB       | !!         | BS2 | BDAL12L |     |       |         |

| ! BT1           | GND           | N / O   | NI /11  |             | !!         | BT2 | BDAL13L |     |       |         |

| ! BU1           | PSPARE2       | N/U     | N/U     |             | : !        | BU2 | BDAL14L |     |       |         |

| ! BV1           | +5V           |         |         | •           | : :<br>    | BV2 | BDAL15L |     |       |         |

\*NOT BUSSED N/U = NOT USED

## NOTE

C-D slots for LSI-11/73 and LSI-11/23 are the same as A-B slots. Pin assignments for MicroVAX C-D slots are defined on the next page.

| 1. |      |            |      |           |     |            |     |           | . 1        |

|----|------|------------|------|-----------|-----|------------|-----|-----------|------------|

| !  | CA1  | NOT USED   | CA2  | +5V       | DA1 | NOT USED   | DA2 | +57       | į          |

| !  | CB1  | *MAA<0>L   | CB2  | MAA<9>L   | DB1 | *MAA<7>L   | DB2 | MAA<7>L   | !          |

| !  | CC1  | NOT USED   | CC2  | GND       | DC1 | NOT USED   | DC2 | GND       | !          |

| !  | CD1  | *RAS<5>H   | CD2  | RAS<1>H   | DD1 | *MAA<5>L   | DD2 | MAA<5>L   | !          |

| !  | CE1  | *BMCAS<0>H | CE2  | BMCAS<0>L | DE1 | *MAA<4>L   | DE2 | MAA<4>L   | !          |

| !  | CF1  | *RAS<1>H   | CF2  | NOT USED  | DF1 | *MAA<3>L   | DF2 | MAA<3>L   | !          |

| !  | CH1  | *BMCAS<1>H | CH2  | BMCAS<1>H | DH1 | *MAA<6>L   | DH2 | MAA<6>L   | ļ          |

| !  | CJ1  | *MSID<0>L  | CJ2  | MSID<2>L  | DJ1 | *MSID<2LL  | DJ2 | NOT USED  | !          |

| !  | CK 1 | *MSWT<1>H  | CK2  | MSWT<1>H  | DK1 | *RAS<3>H   | DK2 | NOT USED  | l          |

| Ī  | CL1  | *RAS<4>H   | Cl_2 | RAS<0>H   | DL1 | *RAS<7>H   | DL2 | RAS<3>H   | ļ          |

| !  | CM1  | *MSID<1>L  | CM2  | MSID<3>L  | DM1 | *MSID<3>L  | DM2 | NOT USED  | i          |

| !  | CN1  | *MAA<1>L   | CN2  | MAA<1>L   | DN1 | *RAS<2LH   | DN2 | NOT USED  | ļ          |

| !  | CP1  | *MAA<2>L   | CP2  | MAA<2>L   | DP1 | *BMCAS<2>H | DP2 | BMCAS<2>H | !          |

| !  | CR1  | *MAA<0>L   | CR2  | MAA<0>L   | DR1 | *BMCAS<3>H | DR2 | BMCAS<3>H | !          |

| !  | CS1  | *MAA<8>L   | CS2  | MAA<8>L   | DS1 | *MSWT<2>H  | DS2 | MSWT<2>H  | !          |

| !  | CT1  | GND        | CT2  | MSID<4>L  | DT1 | GND        | DT2 | *MSID<4>L | ļ          |

| !  | CU1  | *RAS<0>H   | CU2  | NOT USED  | CU1 | *RAS<6>H   | DU2 | RAS<2>H   | !          |

| !  | CV1  | NOT USED   | CV2  | NOT USED  | DV1 | NOT USED   | DV2 | NOT USED  | !          |

| !. |      |            |      |           |     |            |     |           | , <u>İ</u> |

<sup>\*</sup>Used by MSA32 memory module. Not used by CPU.

MicroVAX C-D Slot Definitions

29

| ADDRESS                    | 1              | SI<br>2        | 3                 | 4              | 1 POS          | 6                 | ONS<br>7         | 8                | ADDRESS                    | 1              | SV<br>2           | 3                 | 4              | 1 POS<br>5<br>SS B1 | 6                 | ONS<br>7         | 8                |

|----------------------------|----------------|----------------|-------------------|----------------|----------------|-------------------|------------------|------------------|----------------------------|----------------|-------------------|-------------------|----------------|---------------------|-------------------|------------------|------------------|

|                            | A12            | A11            | A10               |                | SS B1<br>A08   |                   | A06              | A05              |                            | A12            | A11               | A10               |                |                     |                   | A06              | A05              |

| 160000<br>160040<br>160100 | ON<br>ON<br>ON | ON<br>ON<br>ON | ON<br>ON<br>ON    | ON<br>ON<br>ON | ON<br>ON<br>ON | ON<br>ON<br>ON    | ON<br>ON<br>OFF  | ON<br>OFF<br>ON  | 162400<br>162440<br>162500 | ON<br>ON<br>ON | ON                | OFF<br>OFF<br>OFF | ON<br>ON<br>ON | OFF<br>OFF<br>OFF   | ON<br>ON<br>ON    | ON<br>ON<br>OFF  | ON<br>OFF<br>ON  |

| 160140<br>160200           | ON<br>ON       | ON<br>ON       | ON<br>ON          | ON<br>ON       | ON<br>ON       | ON<br>OFF         | OFF<br>ON        | OFF<br>ON        | 162540<br>162600           | ON<br>ON       | ON                | OFF<br>OFF        | ON<br>ON       | OFF<br>OFF          | ON<br>OFF         | OFF<br>ON        | OFF<br>ON        |

| 160240<br>160300           | ON<br>ON       | ON<br>ON       | ON<br>ON          | ON<br>ON       | ON<br>ON       | OFF<br>OFF        | ON<br>OFF<br>OFF | OFF<br>ON<br>OFF | 162640<br>162700<br>162740 | ON<br>ON<br>ON | ON<br>ON<br>ON    | OFF<br>OFF        | ON<br>ON<br>ON | OFF<br>OFF          | OFF<br>OFF        | ON<br>OFF<br>OFF | OFF<br>ON<br>OFF |

| 160340<br>160400           | ON<br>ON       | ON<br>ON       | ON<br>ON          | ON             | ON<br>OFF      | OFF               | OFF              | OFF              | 163000                     | ON             | ON                | OFF               |                | OFF                 | OFF               | OFF              | ON               |

| 160440<br>160500           | ON<br>ON       | ON<br>ON       | ON<br>ON          | ON<br>ON       | 0FF            | ON<br>ON          | ON<br>OFF        | OFF<br>ON        | 163040<br>163100           | ON<br>ON       | ON<br>ON          |                   | 0FF            | ON<br>ON            | ON<br>ON          | ON<br>OFF        | OFF<br>ON        |

| 160540<br>160600           | ON<br>ON       | 0N<br>0N       | ON<br>ON          | ON<br>ON       | 0FF            | ON<br>OFF         | OFF<br>ON        | OFF<br>ON        | 163140<br>163200           | ON<br>ON       | ON<br>ON          | 0FF               | OFF<br>OFF     | ON<br>ON            | ON<br>OFF         | OFF<br>ON        | OFF<br>ON        |

| 160640<br>160700<br>160740 | ON<br>ON<br>ON | ON<br>ON<br>ON | ON<br>ON<br>ON    | ON<br>ON<br>ON |                | OFF<br>OFF<br>OFF | ON<br>OFF<br>OFF | OFF<br>ON<br>OFF | 163240<br>163300<br>163340 | ON<br>ON<br>ON | ON<br>ON<br>ON    | OFF<br>OFF<br>OFF | 0FF            | ON<br>ON<br>ON      | OFF<br>OFF<br>OFF | ON<br>OFF<br>OFF | OFF<br>ON<br>OFF |

| 161000<br>161040           | ON<br>ON       | ON<br>ON       | ON<br>ON          | OFF<br>OFF     | ON<br>ON       | ON<br>ON          | ON<br>ON         | ON<br>OFF        | 163400<br>163440           | ON<br>ON       | ON<br>ON          | OFF<br>OFF        | OFF<br>OFF     | OFF<br>OFF          | ON<br>ON          | ON<br>ON         | ON<br>OFF        |

| 161100<br>161140           | ON<br>ON       | ON<br>ON       | ON<br>ON          |                | ON<br>ON       | 0N<br>0N          | OFF<br>OFF       | ON<br>OFF        | 163500<br>163540           | ON<br>ON       | ON<br>ON          | OFF<br>OFF        | OFF            | OFF<br>OFF          | ON<br>ON          | OFF<br>OFF       | ON<br>OFF        |

| 161200<br>161240<br>161300 | ON<br>ON<br>ON | ON<br>ON<br>ON | ON<br>ON<br>ON    | OFF<br>OFF     | ON<br>ON<br>ON | OFF               | ON<br>ON<br>OFF  | ON<br>OFF<br>ON  | 163600<br>163640<br>163700 | ON<br>ON<br>ON | ON<br>ON<br>ON    | OFF<br>OFF        | OFF<br>OFF     | OFF<br>OFF          | OFF<br>OFF        | ON<br>ON<br>OFF  | ON<br>OFF<br>ON  |

| 161340                     | ON             | ON             | ON                | 0FF            |                | 0FF               |                  |                  | 163740                     | ON             | ON                |                   |                |                     |                   | 0FF              |                  |

| 161400<br>161440           | ON<br>ON       | ON<br>ON       | ON                | OFF<br>OFF     | OFF<br>OFF     | ON<br>ON          | ON<br>ON         | ON<br>OFF        | 164000<br>164040           | ON             | OFF<br>OFF        | ON<br>ON          | ON<br>ON       | ON<br>ON            | ON<br>ON          | ON               | ON<br>OFF        |

| 161500<br>161540<br>161600 | ON<br>ON<br>ON | ON<br>ON<br>ON | ON<br>ON          | OFF<br>OFF     | OFF<br>OFF     | ON<br>ON          | OFF<br>OFF<br>ON | ON<br>OFF<br>ON  | 164100<br>164140<br>164200 |                | OFF<br>OFF        | ON<br>ON<br>ON    | ON<br>ON<br>ON | ON<br>ON            | ON<br>ON<br>OFF   | OFF<br>OFF<br>ON | ON<br>OFF<br>ON  |

| 161640<br>161700           | ON<br>ON       | 0N<br>0N       | ON                | OFF            | OFF<br>OFF     | OFF               | ON               | OFF<br>ON        | 164240<br>164300           | ON             | OFF<br>OFF        | ON<br>ON          | ON<br>ON       | ON                  | OFF<br>OFF        | ON               | OFF<br>ON        |

| 161740                     | ON             | ON             | ON                |                | 0FF            |                   |                  | ¥                | 164340                     |                | 0FF               | ON                | ON             | ON                  |                   | 0FF              |                  |

| 162000<br>162040<br>162100 | ON<br>ON<br>ON |                | OFF<br>OFF        | ON<br>ON<br>ON | 0N<br>0N<br>0N | ON<br>ON<br>ON    | ON<br>ON<br>OFF  | ON<br>OFF<br>ON  | 164400<br>164440<br>164500 | ON             | OFF<br>OFF        | ON<br>ON<br>ON    | ON<br>ON       | OFF<br>OFF          | ON<br>ON<br>ON    | ON<br>ON<br>OFF  | ON<br>OFF<br>ON  |

| 162140<br>162200           | ON<br>ON       | ON<br>ON       | OFF<br>OFF        | ON<br>ON       | ON<br>ON       | ON                |                  | OFF<br>ON        | 164540<br>164600           | ON             | OFF<br>OFF        | ON<br>ON          | ON<br>ON       | OFF<br>OFF          | ON                |                  | OFF<br>ON        |

| 162240<br>162300<br>162340 | ON<br>ON<br>ON | ON<br>ON<br>ON | OFF<br>OFF<br>OFF | ON<br>ON<br>ON | ON             | OFF<br>OFF<br>OFF | ON<br>OFF<br>OFF | OFF<br>ON<br>OFF | 164640<br>164700<br>164740 | ON             | OFF<br>OFF<br>OFF | ON<br>ON<br>ON    | ON<br>ON<br>ON |                     | 0FF               | ON<br>OFF<br>OFF | ON               |

| ADDRESS          | 1     | SI<br>2 | W1 SI<br>3 | WITCI<br>4 | H POS<br>5 | SITI(<br>6 | ONS<br>7   | <br>8     | ADDRESS          | <br>1      | SI<br>2    | W1 SI<br>3 | WITCI<br>4 | H POS<br>5 | SITI(<br>6 | ONS       | <br>8     |

|------------------|-------|---------|------------|------------|------------|------------|------------|-----------|------------------|------------|------------|------------|------------|------------|------------|-----------|-----------|

|                  |       |         |            |            | SS B       |            |            |           |                  |            |            | -          | DDRE:      | SS B:      | -          | ·<br>     |           |

|                  | A12 / | A11     | A10        | A09        | 80A        | A07        | A06        | A05       |                  | A12        | A11        | A10        | A09        | 80A        | A07        | A06       | A05       |

| 165000           | ON (  |         |            | 0FF        | ON         | ON         | ON         | ON        | 167400           |            |            | 0FF        |            |            | ON         | ON        | ON        |

| 165040           | ON (  |         |            | OFF        | ON         | ON         |            | 0FF       | 167440           | ON         |            | 0FF        |            | 0FF        | ON         | ON        | OFF       |

| 165100<br>165140 | ON (  | -       |            | OFF<br>OFF | ON         | ON<br>ON   | OFF<br>OFF | ON<br>OFF | 167500           | ON         |            | OFF        |            | 0FF        | ON         | OFF       | ON        |

| 165200           | ON (  |         |            | 0FF        | ON<br>ON   | 0FF        | OFF        | OFF       | 167540<br>167600 | ON<br>ON   | OFF<br>OFF | OFF<br>OFF |            | OFF<br>OFF | ON<br>OFF  | OFF<br>ON | OFF<br>ON |

| 165240           | ON (  |         |            | OFF        | ON         |            |            | OFF       | 167640           | ON         | 0FF        | 0FF        | 0FF        | 0FF        | OFF        | ON        | OFF       |

| 165300           | ON (  |         |            | OFF        | ON         | OFF        | OFF        | ON        | 167700           | ON         | 0FF        | OFF        |            | 0FF        | OFF        | OFF       | ON        |

| 165340           | ON (  |         |            | 0FF        |            | OFF        |            |           | 167740           | ON         | -          | 0FF        |            |            |            | OFF       |           |

| 165400           | ON (  |         |            | 0FF        |            | ON         | ON         | ON        | 170000           | 0FF        | ON         | ON         | ON         | ON         | ON         | ON        | ON        |

| 165440           | ON (  |         |            | 0FF        |            | ON         | ON         | 0FF       | 170040           | 0FF        | ON         | ON         | ON         | ON         | ON         | ON        | 0FF       |

| 165500           | ON (  |         |            | OFF        |            | ON         | OFF        | ON        | 170100           | 0FF        | ON         | ON         | ON         | ON         | ON         | 0FF       | ON        |

| 165540<br>165600 | ON (  |         |            | OFF<br>OFF |            | ON<br>OFF  | OFF<br>ON  | OFF       | 170140           | OFF        | ON         | ON         | ON         | ON         | ON         | 0FF       | 0FF       |

| 165640           | ON (  |         |            |            | OFF        | OFF        | ON         | ON<br>OFF | 170200<br>170240 | OFF<br>OFF | ON<br>ON   | ON<br>ON   | ON<br>ON   | ON<br>ON   | OFF<br>OFF | ON<br>ON  | ON<br>OFF |

| 165700           | ON (  |         |            |            | OFF        |            | OFF        | ON        | 170240           | 0FF        | ON         | ON         | ON         | ON         | OFF        | OFF       | ON        |

| 165740           | ON (  |         |            |            | OFF        |            |            |           | 170340           | OFF        | ON         | ON         | ON         |            | -          |           |           |

| 166000           | ON (  | 0FF     | 0FF        | ON         | ON         | ON         | ON         | ON        | 170400           | 0FF        | ON         | ON         | ON         | 0FF        | ON         | ON        | ON        |

| 166040           |       | -       | 0FF        | ON         | ON         | ON         | ON         | 0FF       | 170440           | OFF        | ON         | ON         | ON         |            | ON         | ON        | 0FF       |

| 166100           | ON (  |         |            | ON         | ON         | ON         | OFF        | 0N        | 170500           | OFF        | ON         | ON         |            | OFF        | ON         | OFF       | ON        |

| 166140<br>166200 | ON (  |         |            | ON<br>ON   | ON<br>ON   | ON<br>OFF  | OFF<br>ON  | OFF<br>ON | 170540<br>170600 | OFF<br>OFF | ON<br>ON   | ON<br>ON   | ON<br>ON   | OFF<br>OFF | ON<br>OFF  | OFF<br>ON | OFF<br>ON |

| 166240           | ON (  |         |            | ON         | ON         | OFF        | ON         | 0FF       | 170640           | 0FF        | ON         | ON         | ON         | 0FF        | OFF        | ON        | 0FF       |

| 166300           | ON (  |         |            | ON         |            | 0FF        | 0FF        | ON        | 170700           | 0FF        | ON         | ON         | ON         | 0FF        | OFF        | OFF       | ON        |

| 166340           | ON (  | OFF     | 0FF        | ON         | ON         | 0FF        | 0FF        | 0FF       | 170740           | 0FF        | ON         | ON         | ON         |            | 0FF        | 0FF       | OFF       |

| 166400           | ON (  |         |            |            | OFF        | ON         | ON         | ON        | 171000           | 0FF        | ON         | ON         | OFF        | ON         | ON         | ON        | ON        |

| 166440           | ON (  |         |            |            | 0FF        | ON         | ON         | 0FF       | 171040           | OFF        | ON         | ON         | OFF        | ON         | ON         | ON        | OFF       |

| 166500           | ON (  |         |            |            | OFF<br>OFF | ON         | OFF<br>OFF | ON        | 171100           | 0FF        | ON         | ON         | 0FF        | ON         | ON         | OFF       | 0N        |

| 166540<br>166600 | ON (  |         |            |            | OFF        |            | ON         | OFF<br>ON | 171140<br>171200 | OFF<br>OFF | ON<br>ON   |            | OFF<br>OFF | ON         | ON<br>OFF  | OFF<br>ON | OFF<br>ON |

| 166640           | ON (  |         |            |            | 0FF        |            | ON         | OFF       | 171240           | 0FF        | ON         |            | 0FF        |            | 0FF        | ON        | 0FF       |

| 166700           | ON C  |         |            |            | 0FF        |            |            | ON        | 171300           | 0FF        | ON         |            | OFF        |            | OFF        |           | ON        |

| 166740           | ON (  |         |            |            | OFF        |            |            |           | 171340           | 0FF        | ON         |            | OFF        | ON         |            | OFF       |           |

| 167000           |       |         | 0FF        |            | ON         | ON         | ON         | ON        | 171400           | 0FF        | ON         |            | 0FF        |            | ON         | ON        | ON        |

| 167040           |       |         | OFF        |            | ON         | ON         |            | UFF       | 171440           | 0FF        | ON         |            | OFF        |            | ON         |           | 0FF       |

| 167100           |       |         | OFF        |            | ON         |            | OFF        | ON        | 171500           | 0FF        | ON         |            | OFF        |            |            | OFF       |           |

| 167140<br>167200 |       |         | OFF<br>OFF |            | ON         | ON<br>OFF  | OFF<br>ON  | OFF<br>ON | 171540<br>171600 | OFF<br>OFF | ON<br>ON   |            | OFF        | OFF        | ON         | OFF<br>ON | OFF       |

| 167240           |       |         | 0FF        |            |            | OFF        | ON         | 0FF       | 171600           | 0FF        | ON         |            |            | OFF        |            | ON        |           |

| 167300           |       |         | 0FF        |            |            | 0FF        |            | ON        | 171700           | 0FF        | ON         |            |            | 0FF        |            |           | ON        |

| 167340           |       |         | 0FF        |            |            | 0FF        |            |           | 171740           | OFF        | ON         |            |            | OFF        |            |           |           |

| ADDRESS                                                                      | SW1 SWITCH POSITIONS 1 2 3 4 5 6 7 8ADDRESS BITS A12 A11 A10 A09 A08 A07 A06 A05             | ADDRESS 1 2 3 4 5 6 7 8ADDRESS BITS A12 A11 A10 A09 A08 A07 A06 A05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 172000<br>172040<br>172100<br>172140<br>172200<br>172240<br>172300<br>172340 | OFF ON OFF ON ON ON ON ON ON OFF ON OFF ON ON ON ON ON OFF ON ON ON OFF ON OFF ON ON OFF OFF | 174400         OFF OFF         ON         ON OFF         ON         ON ON         ON         ON         ON         ON         ON         ON         ON         ON         ON         ON         OFF         ON         ON         OFF         ON         ON         OFF         ON         ON         OFF         ON         OFF         ON         ON         OFF         ON         OFF         OFF         ON         ON         OFF         OFF         OFF         ON         ON         OFF         OFF |

| 172400<br>172440<br>172500<br>172540<br>172600<br>172640<br>172700<br>172740 | OFF ON OFF ON OFF ON ON ON OFF ON OFF ON OFF ON OFF ON OFF ON OFF ON OFF ON OFF OFF          | 175000 OFF OFF ON OFF ON ON ON ON 175040 OFF OFF ON OFF ON ON ON ON OFF 175100 OFF OFF ON OFF ON OFF ON OFF ON OFF OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 173000<br>173040<br>173100<br>173140<br>173200<br>173240<br>173300<br>173340 | OFF ON OFF OFF ON ON ON ON OFF OFF ON OFF OFF                                                | 175400         OFF OFF         ON OFF OFF         ON ON ON ON ON ON ON OFF OFF OFF OFF OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |