OMTI 5050 PROGRAMMABLE DATA SEQUENCER REFERENCE MANUAL JUNE 20th, 1986

Scientific Micro Systems, Inc.

OMTI 5050 PROGRAMMABLE DATA SEQUENCER REFERENCE MANUAL JUNE 20th, 1986

PUBLICATION NUMBER: 3001222

# OMTI 5050

# PROGRAMMABLE DATA SEQUENCER

## REFERENCE MANUAL

SCIENTIFIC MICRO SYSTEMS, INC.

339 North Bernardo Avenue

P.O. Box 7777

Mountain View

CALIFORNIA 94039

TEL: 415-964-5700 TWX: 910-379-6577 TLX: 172555 SMS MNTV FAX: 415-968-4861

Copyright 1986 SCIENTIFIC MICRO SYSTEMS, INC. All Rights Reserved

PRINTED IN THE UNITED STATES OF AMERICA

The information in this publication is subject to change without notice. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Scientific Micro Systems, Inc.

## (PART #20505)

| REV         | REVISION HISTORY                                   | PRINT DATE                                                       |

|-------------|----------------------------------------------------|------------------------------------------------------------------|

| 1<br>2<br>B | Original Issue<br>Revision<br>Revision<br>Revision | May 18, 1984<br>Sept.11, 1985<br>Feb. 6, 1986<br>June 20th, 1986 |

DOCUMENT NUMBER: 3001222

REVISION: B

DATE OF THIS REVISION: JUNE 20th 1986

# TABLE OF CONTENTS

| CTION 1: INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D.C. Information 1.3.1. Absolute Maximum Ratings 1.3.2. Standard Test Conditions 1.3.3. D.C. Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-5<br>1-5<br>1-5<br>1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A.C. Characteristics 1.4.1 WRITE Operation, Z8 Mode Timing Characteristics 1.4.2 READ Operation, Z8 1.4.3 WRITE Operation, 8051 Mode Timing Characteristics 1.4.4 READ Operation, 8051 1.4.5 SEQUENCER Register Load 1.4.6 DMA Request / Acknowledge Handshake 1.4.7 Disk / MPU to DMA Memory 1.4.8 Disk Interface Signals 1.4.8.1 Read Data Signals 1.4.8.2 Write Data Signals                                                                                                                                                                                                                                                                               | 1-6<br>1-6<br>1-7<br>1-8<br>1-9<br>1-1(<br>1-1<br>1-1;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TION 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Interfaces 2.2.1 Micro-Processor Interface 2.2.2 DMA Interface 2.2.3 State Control Register Interface 2.2.4 Serial Disk Interface 2.2.5 Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-2<br>2-2<br>2-2<br>2-2<br>2-2<br>2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PIN Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

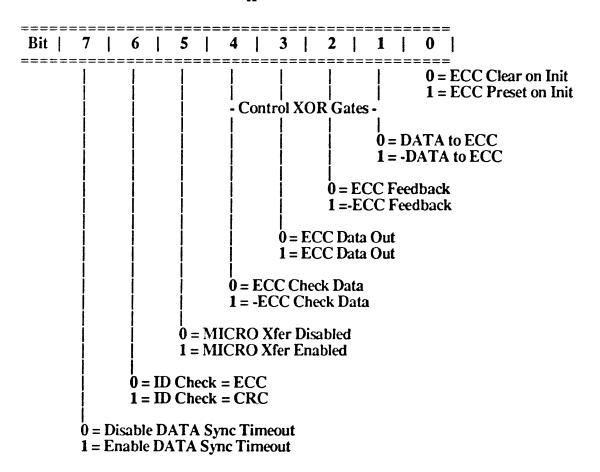

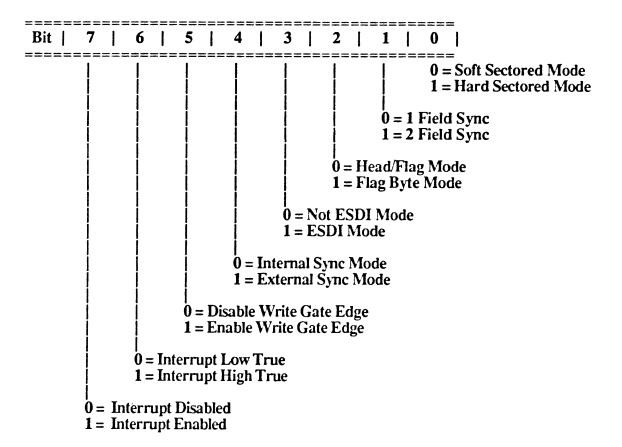

| Registers  2.4.1.1 Write Register 20H: Command  2.4.1.2 Write Register 21H: Sequencer Loop Count  2.4.1.3 Write Register 22H: Index Time-Out  2.4.1.4 Write Register 23H: Sub-Block Count  2.4.1.5 Write Registers 24 through 27H: ID Registers  2.4.1.6 Write Registers 28H: Micro to Memory  2.4.1.7 Write Register 29H: Sequencer Start/Re-Start  2.4.1.8 Write Register 2AH: Sequencer Loop State  2.4.1.9 Write Register 2BH: Bit Ring Control  2.4.1.10 Write Register 2CH: ECC Control  2.4.1.11 Write Register 2DH: Configuration Control  2.4.1.12 Write Register 2EH: External Count Register  2.4.1.13 Write Register 2FH: External Value Register | 2-8<br>2-10<br>2-10<br>2-11<br>2-12<br>2-12<br>2-13<br>2-14<br>2-15<br>2-15<br>2-15<br>2-17<br>2-18<br>2-19<br>2-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Peatures  D.C. Information 1.3.1. Absolute Maximum Ratings 1.3.2. Standard Test Conditions 1.3.3. D.C. Characteristics  A.C. Characteristics 1.4.1 WRITE Operation, Z8 Mode Timing Characteristics 1.4.2 READ Operation, Z8 1.4.3 WRITE Operation, 8051 Mode Timing Characteristics 1.4.4 READ Operation, 8051 1.4.5 SEQUENCER Register Load 1.4.6 DMA Request / Acknowledge Handshake 1.4.7 Disk / MPU to DMA Memory 1.4.8 Disk Interface Signals 1.4.8.1 Read Data Signals 1.4.8.2 Write Data Signals 1.4.8.2 Write Data Signals 1.4.8.2 Write Data Signals 1.4.8.2 Write Data Signals 1.4.8.1 Write Register Interface 2.2.1 Micro-Processor Interface 2.2.2 DMA Interface 2.2.3 State Control Register Interface 2.2.4 Serial Disk Interface 2.2.5 Clock  PIN Descriptions  Registers 2.4.1.1 Write Register 20H: Command 2.4.1.2 Write Register 21H: Sequencer Loop Count 2.4.1.3 Write Register 21H: Mex Time-Out 2.4.1.4 Write Register 22H: Index Time-Out 2.4.1.5 Write Register 23H: Sub-Block Count 2.4.1.6 Write Register 28H: Micro to Memory 2.4.1.7 Write Register 29H: Sequencer Loop State 3.4.1.8 Write Register 29H: Sequencer Loop State 3.4.1.9 Write Register 2BH: Bit Ring Control 3.4.1.10 Write Register 2CH: ECC Control 3.4.1.11 Write Register 2CH: Configuration Control 3.4.1.11 Write Register 2CH: ECC Control 3.4.1.11 Write Register 2CH: ECC Control 3.4.1.11 Write Register 2CH: External Count Register |

| 2.4.2 Read Registers                                  | 2-20 |

|-------------------------------------------------------|------|

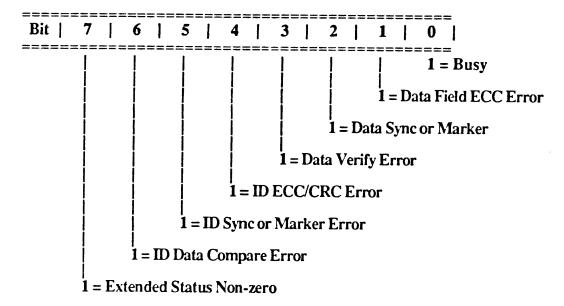

| 2.4.2.1 Read Register 20H: Status                     | 2-20 |

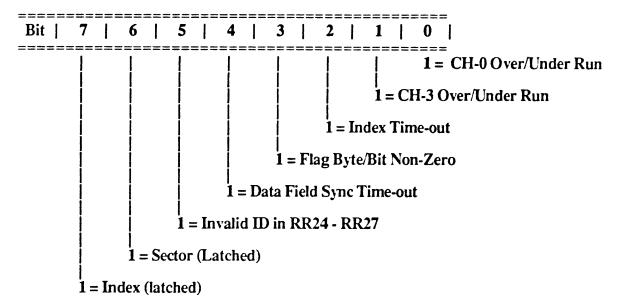

| 2.4.2.2 Read Register 21H: Extended Status            | 2-21 |

| 2.4.2.3 Read Register 22H: Retry Count/State Address  | 2-23 |

| 2.4.2.4 Read Register 23H: Flag Byte (Header Byte 5)  | 2-23 |

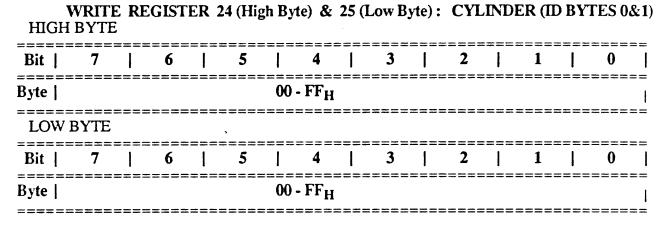

| 2.4.2.5 Read Register 24 (High Byte) & 25 (Low Byte)  | 2-23 |

| 2.4.2.6 Read Register 26H: Head (ID Byte 2)           | 2-24 |

| 2.4.2.7 Read Register 27H: Sector Number              | 2-24 |

| 2.4.2.8 Read Register 28H: Memory to Micro            | 2-24 |

| 2.4.2.9 Read Register 29H: Sequencer Loop Count       | 2-25 |

| 2.4.2.10 Read Register 2EH: External Count Register   | 2-25 |

| 2.4.2.11 Read Register 2FH: Exrternal Value Register  | 2-26 |

| 2.4.3 State Control Registers                         | 2-26 |

| 2.4.4 Strobe Logic                                    | 2-27 |

| 2.4.5 List of OMTI 5050 Commands                      | 2-28 |

| 2.4.5.1 Command Description                           | 2-29 |

| Appendix A Initialization of the Register File        | A-1  |

| Appendix B Sequencer State Flow Chart (Soft Sectored) | B-1  |

#### SECTION 1

### INTRODUCTION

#### 1.1 DESCRIPTION

The OMTI 5050 Programmable Data Sequencer is an application specific CMOS/VLSI integrated circuit mounted in a 68-pin plastic leaded chip carrier. The OMTI 5050 manages the flow of block-level information between serial disk interfaces and a host or buffer memory in advanced Winchester disk controller designs.

A dual-bus structure is used so the disk data transfers and the micro-processor can be operating at the same time without impacting the disk transfer rate or the performance of the micro-processor.

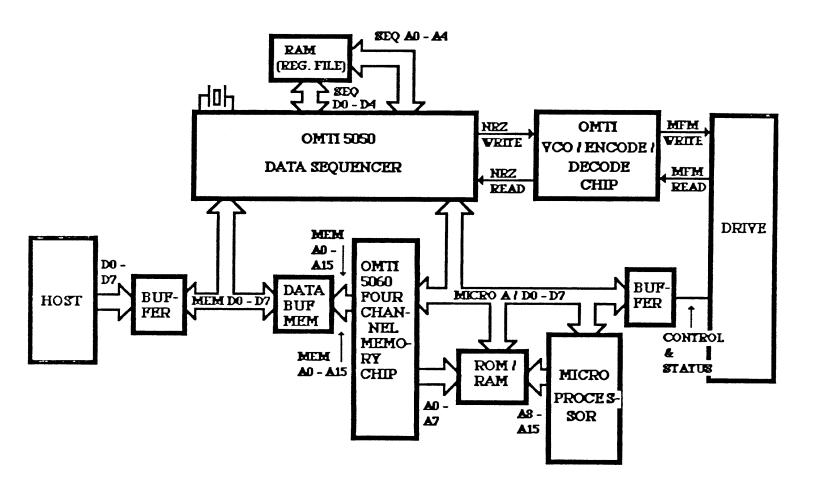

The OMTI 5050 is designed to be used with the OMTI 5060 Direct Memory Access Controller (DMAC), a RAM buffer, a byte oriented micro-processor, and appropriate drivers and receivers. The Data Sequencer can also be used with the OMTI 5070 MFM/Encode/Decode/VCO chip or the OMTI 5027 2-7/Encode/Decode/VCO chip to provide all the functions needed to interface to disk drives using MFM or 2-7 encoded data.

The Data Sequencer provides the bit-serial data management, format control, error detection, and serialization/de-serialization functions normally associated with data controllers. The chip is designed to be used directly with NRZ interfaces such as ESDI. (Enhanced Standard Drive Interface) When used with the OMTI 5070 or OMTI 5027 chips, it provides all the control lines required for MFM or 2-7 interfaces such as ST-506 or ST-412 and ST-238 drives.

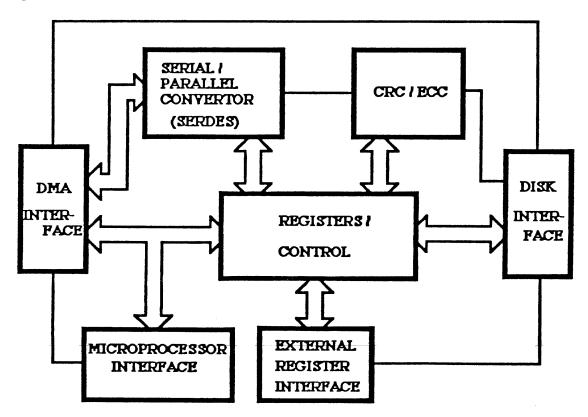

# CONCEPTUAL BLOCK DIAGRAM

OMTI 5050 - Page 1-1

## 1.2 FEATURES

- \* High Performance Dual-Bus Architecture.

- \* High-level Instruction Set including:

- Individual Sector Formatting.

- Track Formatting.

- Read ID.

- Read/Write Long.

- Read Syndrome.

- Verify (with data in buffer).

- Check Data ECC.

- Check Track Format

- \* 10 MHz bit rate--up to 10 Mbit/sec Drive Data Transfer Rate.

- \* Programmable Disk Format.

- Programmable Sector Size up to 65,536 bytes/sector.

- Programmable ID Data and Size.

- Programmable Gap Sizes and Fill Characters.

- User-definable Header Flag Byte or Nibble.

- Up to 64-bit Programmable (ECC) Polynomial and ID CRC or ECC.

- \* Hard or Soft Sector Modes.

- \* NRZ Serial Disk Interface.

- \* Direct Interface to ESDI Type Drives.

- \* Multi-sector Transfer capability with Automatic Sector Increment.

- \* Programmable Automatic ID Retries.

- \* Surface-mount Plastic 68-pin Leaded Chip Carrier Package.

- \* Low Power Consumption.

- \* Strobe Logic to access External Registers on the Micro Bus.

- \* Logic to Transfer Data between the Micro Bus and Buffer Memory.

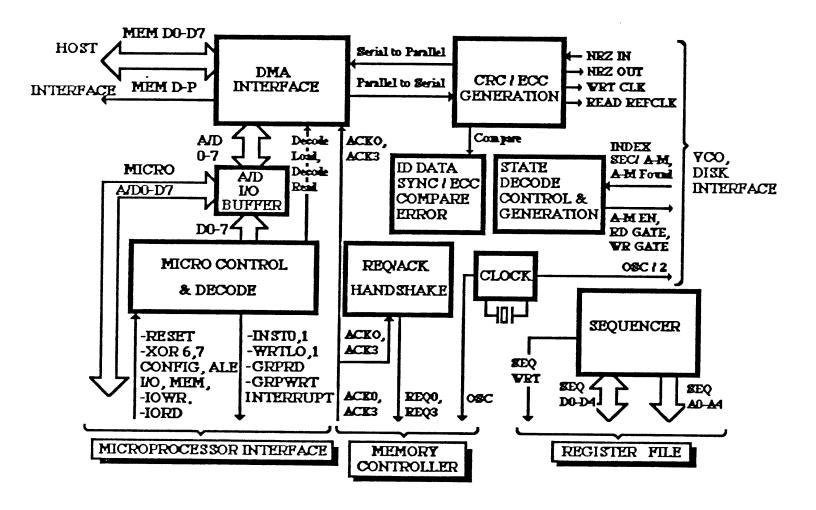

FUNCTIONAL BLOCK DIAGRAM

TYPICAL SYSTEM CONFIGURATION

### 1.3 D. C. INFORMATION

## 1.3.1 Absolute Maximum Ratings:

- \* Voltages on all pins with respect to GND range from -0.3 V to +7.0 V.

- \* Ambient operating temperature is 0 degrees C. to +70 degrees C.

- \* Storage temperature ranges from -65 degrees C. to +150 degrees C.

Note that stresses greater than those indicated may cause permanent damage. Operation of the chip at conditions above those shown is not implied. Exposure to absolute maximum rating conditions for extended periods may affect the chip's reliability.

## 1.3.2 Standard Test Conditions:

The characteristics shown below apply for the following test conditions, unless otherwise noted. Voltages are referenced to GND. Positive current flows into the reference pin. Standard conditions are as follows.

- \* +4.50 V < VCC < +5.50 V

- \* GND = 0 V

- \* 0 degrees C. < TA < +70 degrees C.

## 1.3.3 D. C. Characteristics:

| Parameter                                                                                                                                                          | Min                                    | Max                                        | Unit                                | Condition | Notes |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------|-------------------------------------|-----------|-------|

| Input High Voltage Input Low Voltage Output High Voltage Output Low Voltage Output Low Current Output High Current Input Leakage Output Leakage VCC Supply Current | 2<br>-0.3<br>2.4<br>4.0<br>-4.0<br>-30 | VCC<br>0.8<br>VCC<br>0.4<br>10<br>10<br>50 | V<br>V<br>V<br>MA<br>mA<br>uA<br>uA |           |       |

## 1.4 A.C. CHARACTERISTICS

The two relevant timing diagrams and A.C. characteristics for interfacing the 5050 Data Sequencer are given below. (For more information about these chips, the reader is referred to: - Zilog's Z8681/82 ROMless Z8 Microcomputer Product Specification - or Intel's 8051 Single Chip 8-Bit N-Channel Microprocessor Data Sheet.

# 1.4.1 WRITE Operation, Z8 Configuration (Configuration = 1)

| Signal     | I/O Pin  |                                     |                  |

|------------|----------|-------------------------------------|------------------|

| -DM        | I (65)   |                                     | /                |

| -DS        | I (66)   |                                     | <t1></t1>        |

|            |          |                                     |                  |

| R∕₩        | I (67)   | > T2 <                              |                  |

| -AS        | I (68)   |                                     |                  |

|            |          | >   T3   <<br> ->   T4   <<br>  <-> | T5               |

| A/D 0-7    | I (2-9)  |                                     | >                |

| ribui 0 /1 | 0 /55/56 | 17>                                 | T8>              |

| -WRTL0/1   | 0 (55/56 | ) )                                 | /                |

| Symbol     | I<br>    | VCC = 5.0V, TA = 25oC               | min typ max unit |

| m 1        |          |                                     | 100              |

| Symbol     | Item                                    | min | typ | max | unit |

|------------|-----------------------------------------|-----|-----|-----|------|

|            |                                         |     |     |     |      |

| Tl         | -DS Low Pulse Width                     | 100 |     |     | ns   |

| T2         | -AS Low Pulse Width                     | 50  |     |     | ns   |

| Т3         | Address Setup to -AS Low to High        | 25  |     |     | ns   |

| <b>T4</b>  | Address Hold after -AS Low to High      | 25  |     |     | ns   |

| Т5         | Data Setup to -DS High to Low           | 25  |     |     | ns   |

| <b>T6</b>  | Data Hold After -DS Low to High         | 25  |     |     | ns   |

| <b>T</b> 7 | -DS High to Low to -WRLTO/1 High to Low |     | 25  |     | ns   |

| T8         | -DS Low to High to -WRLTO/1 Low to High |     | 25  |     | ns   |

# 1.4.2 READ Operation, **Z8** Configuration (Configuration = 1)

| Signal              | I/O Pin   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -DM                 | I (65)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                     |           | <t1></t1>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -DS                 | I (66)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>κ</b> / <b>₩</b> | I (67)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| -AS                 | I (68)    | > T2 <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A/D 0-7             | I (2-9)   | >   T3   <  >   T6   <   T5   <   T7  >   T7  >   T7  >   T7  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >  >   - |

| -INSTO/1            | 0 (53/54) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | VCC = 5.0V, $TA = 250C$                 |     |     |     |      |

|-----------|-----------------------------------------|-----|-----|-----|------|

| Symbol    | Item                                    | min | typ | max | unit |

|           |                                         |     |     |     |      |

| Tl        | -DS Low Pulse Width                     | 100 |     |     | ns   |

| Т2        | -AS Low Pulse Width                     | 50  |     |     | ns   |

| Т3        | Address Setup to -AS Low to High        | 25  |     |     | ns   |

| <b>T4</b> | Address Hold after -AS Low to High      | 25  |     |     | ns   |

| Т5        | Data Valid from -DS High to Low         |     |     | 50  | ns   |

| Т6        | Data Float After -DS Low to High        |     | 35  |     | ns   |

| T7        | -DS High to Low to -INSTO/1 High to Low |     | 25  |     | ns   |

| <b>T8</b> | -DS Low to High to -INSTO/1 Low to High |     | 25  |     | ns   |

# 1.4.3 WRITE Operation, 8051 Configuration (Configuration = 0)

| Signal   | I/O Pin  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOMEM    | I (65)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -IORD    | I (66)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -IOWR    | I (67)   | <t1></t1>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ALE      | I (68)   | > T2 <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A/D 0-7  | I (2-9)  | T3   <   T6   <   T6   <   T7   <   T7   <   T7   <   T7   <   <   T8>   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   < |

| -WRTL0/1 | 0 (55/56 | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | VCC = 5.0V, TA = 250C                     |     |     |     |      |

|-----------|-------------------------------------------|-----|-----|-----|------|

| Symbol    | Item                                      | min | typ | max | unit |

|           |                                           |     |     |     |      |

| Tl        | -IOWR Low Pulse Width                     | 100 |     |     | ns   |

| Т2        | ALE High Pulse Width                      | 50  |     |     | ns   |

| Т3        | Address Setup to ALE High to Low          | 25  |     |     | ns   |

| T 4       | Address Hold after ALE High to Low        | 25  |     |     | ns   |

| Т5        | Data Setup to -IOWR High to Low           | 25  |     |     | ns   |

| Т6        | Data Hold After -IOWR Low to High         | 25  |     |     | ns   |

| т7        | -IOWR High to Low to -WRLTO/1 High to Low |     | 25  |     | ns   |

| <b>T8</b> | -IOWR Low to High to -WRLTO/1 Low to High |     | 25  |     | ns   |

# 1.4.4 READ Operation, 8051 Configuration (Configuration = 0)

| Signal   | 1/0 | ) Pin   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOMEM    | I   | (65)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| -IOWR    | I   | (66)    | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| -IORD    | I   | (67)    | <t1></t1>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ALE      | I   | (68)    | > T2 <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0 – 7    | I   | (2-9)   | >   T3   <  >   T6   <  >   T74   <  >   T5   <  >   T7>   <  >   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   <   < |

| -INSTO/1 | 0   | (53/54) | T7>  <   <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Symbol   |     | Item    | VCC = 5.0V, TA = 25oC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | VCC = 5.0V, TA = 250C                     |     |     |     |      |

|--------|-------------------------------------------|-----|-----|-----|------|

| Symbol | Item                                      | min | typ | max | unit |

|        | ** ** ** ** ** ** ** ** ** ** ** ** **    |     |     |     |      |

| Tl     | -IORD Low Pulse Width                     | 100 |     |     | ns   |

| Т2     | ALE High Pulse Width                      | 50  |     |     | ns   |

| Т3     | Address Setup to ALE High to Low          | 25  |     |     | ns   |

| T 4    | Address Hold after ALE High to Low        | 25  |     |     | ns   |

| T5     | Data Valid from -IORD High to Low         |     |     | 50  | ns   |

| Т6     | Data Float After -IORD Low to High        |     | 35  |     | ns   |

| T7     | -IORD High to Low to -INSTO/1 High to Low |     | 25  |     | ns   |

| T8     | -IORD Low to High to -INSTO/1 Low to High |     | 25  |     | ns   |

# 1.4.5 SEQUENCER REGISTER LOAD Operation

**T6**

| Signal                     | I/O Pin<br>                                                                                                                                                                                                                                                                               |   |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| -DM                        | I (65)                                                                                                                                                                                                                                                                                    | • |

| -DS                        | I (66)                                                                                                                                                                                                                                                                                    | - |

| R/W                        | I (67)                                                                                                                                                                                                                                                                                    |   |

| -AS                        | I (68)                                                                                                                                                                                                                                                                                    |   |

| A/D 0-7                    | I (2-9)                                                                                                                                                                                                                                                                                   |   |

| -SEQ WRT                   | O (21)                                                                                                                                                                                                                                                                                    |   |

| SEQ ADD 4                  | T3>                                                                                                                                                                                                                                                                                       |   |

| SEQ D 0-7                  | 0 (27-33)                                                                                                                                                                                                                                                                                 |   |

| Symbol                     | VCC = 5.0V, TA = 25oC Item min typ max unit                                                                                                                                                                                                                                               |   |

| T1<br>T2<br>T3<br>T4<br>T5 | -DS High to Low to -SEQ WRT High to Low 40 ns -DS Low to High to -SEQ WRT Low to High 40 ns -DS High to Low to SEQ A 4 Address Valid 40 ns -DS Low to High to SEQ A 4 Address Invalid 40 ns -DS High to Low to SEQ D 0-7 data Valid 35 ns -DS Low to High to SEQ D 0-7 Data Invalid 35 ns |   |

35

ns

-DS Low to High to SEQ D 0-7 Data Invalid

# 1.4.6 DMA REQUEST / ACKNOWLEDGE HANDSHAKE

| -REQ 0/3 O (44/46)                                                                         | Signal    |

|--------------------------------------------------------------------------------------------|-----------|

|                                                                                            |           |

| mı si                                                                                      | -REQ 0/3  |

|                                                                                            |           |

| -ACK 0/3 I (45/47)                                                                         | -ACK 0/3  |

| T2>                                                                                        | MEM D 0 7 |

| MEM D 0-7 I (36-43)                                                                        | MEM D U-7 |

| T4>     <>     <t5< td=""><td></td></t5<>                                                  |           |

| MEM D P O (63)                                                                             | MEM D P   |

|                                                                                            |           |

| VCC = 5.0V, TA = 250C                                                                      |           |

| Symbol Item min typ max unit                                                               | Symbol    |

| Tl -ACK High to Low to -REQ Low to High 45 ns                                              |           |

| T2 MEM D 0-7 Setup to -ACK Low to High 15 ns                                               |           |

| T3 MEM D 0-7 Hold from -ACK Low to High 10 ns T4 MEM D 0-7 Valid to MEM D P Valid 40 ns    |           |

| T4 MEM D 0-7 Valid to MEM D P Valid 40 ns<br>T5 MEM D 0-7 Invalid to MEM D P Invalid 10 ns |           |

# 1.4.7 DISK/MPU TO DMA MEMORY

| Signal    | I/O Pin   |                 |

|-----------|-----------|-----------------|

| -REQ 0/3  | 0 (44/46) |                 |

|           |           | T1>   <         |

| -ACK 0/3  | I (45/47) | 1               |

|           |           | T2>   < T3>   < |

| MEM D 0-7 | 0 (36-43) |                 |

|           |           | T4>   < T5>   < |

| MEM D P   | 0 (63)    | >< ><           |

| VCC = 5.0V, $TA = 250C$ |                                       |     |     |     |      |  |  |  |  |

|-------------------------|---------------------------------------|-----|-----|-----|------|--|--|--|--|

| Symbol                  | Item                                  | min | typ | max | unit |  |  |  |  |

|                         | *                                     |     |     |     |      |  |  |  |  |

| Tl                      | -ACK High to Low to -REQ Low to High  |     | 45  |     | ns   |  |  |  |  |

| Т2                      | -ACK High to Low to MEM D 0-7 Valid   |     | 15  |     | ns   |  |  |  |  |

| Т3                      | -ACK Low to High to MEM D 0-7 Invalid |     | 10  |     | ns   |  |  |  |  |

| T4                      | MEM D 0-7 Valid to MEM D P Valid      |     | 40  |     | ns   |  |  |  |  |

| T5                      | MEM D 0-7 Invalid to MEM D P Invalid  |     | 10  |     | ns   |  |  |  |  |

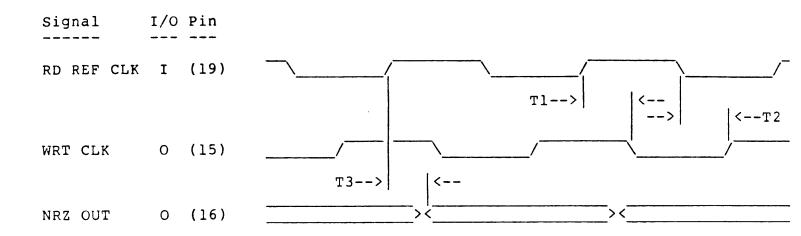

# 1.4.8 DISK INTERFACE SIGNALS

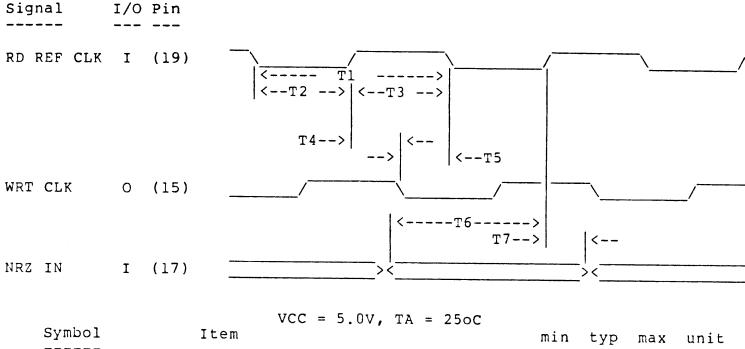

# 1.4.8.1 READ DATA SIGNALS

|        |           | 2.00                        |     |     |     |      |  |

|--------|-----------|-----------------------------|-----|-----|-----|------|--|

| Symbol | I         | tem                         | min | typ | max | unit |  |

|        |           |                             |     |     |     |      |  |

| Tl     | RD REF CL | K Period                    | 100 |     |     | ns   |  |

| T 2    | RD REF CL | K Low Width                 | 50  |     |     | ns   |  |

| Т3     |           | K High Width                | 50  |     |     | ns   |  |

| T4     |           | K High to WRT CLK Low Delay |     | 45  |     | ns   |  |

| T5     |           | K Low to WRT CLK High Delay |     | 45  |     | ns   |  |

| Т6     |           | ta Setup to RD REF CLK      | 20  |     |     | ns   |  |