OMTI 5080 SCSI MULTIFUNCTIONAL DEVICE REFERENCE MANUAL September 1985

Scientific Micro Systems, Inc.

OMTI 5080 SCSI

MULTIFUNCTIONAL DEVICE

REFERENCE MANUAL

September 1985

# OMTI 5080 MULTIFUNCTIONAL DEVICE REFERENCE MANUAL

SCIENTIFIC MICRO SYSTEMS, INC.

339 North Bernardo Avenue

P.O. Box 7777

Mountain View

CALIFORNIA 94039

TEL: 415-964-5700 TWX: 910-3379-6577 TLX: 172555 SMS INC. MNTV

Copyright 1985 SCIENTIFIC MICRO SYSTEMS, INC.

All Rights Reserved

PRINTED IN THE UNITED STATES OF AMERICA

# TABLE OF CONTENTS

| Page                                                                                                                                                                          | Number                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| CHAPTER 1. GENERAL DESCRIPTION                                                                                                                                                |                                               |

| Introduction Applications Features Architectural Overview Registers/Control Logic Host Interface DMA Interface Local Microprocessor Interface Input Port System Configuration | 1-1<br>1-2<br>1-3<br>1-4<br>1-4<br>1-4<br>1-4 |

| CHAPTER 2. FUNCTIONAL DESCRIPTION                                                                                                                                             |                                               |

| Introduction                                                                                                                                                                  | 2-1<br>2-2<br>2-12                            |

| CHAPTER 3. INTERFACING                                                                                                                                                        |                                               |

| Signal Descriptions                                                                                                                                                           | 3-20<br>3-28<br>3-28<br>3-28<br>3-28<br>3-28  |

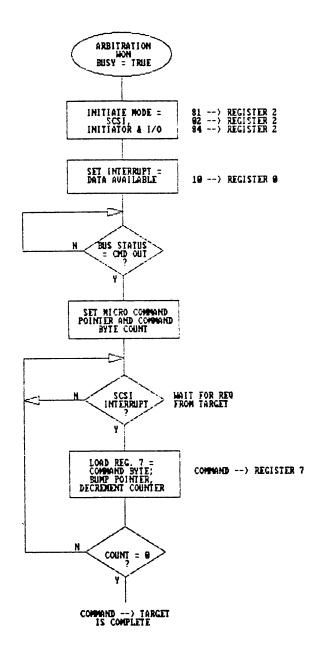

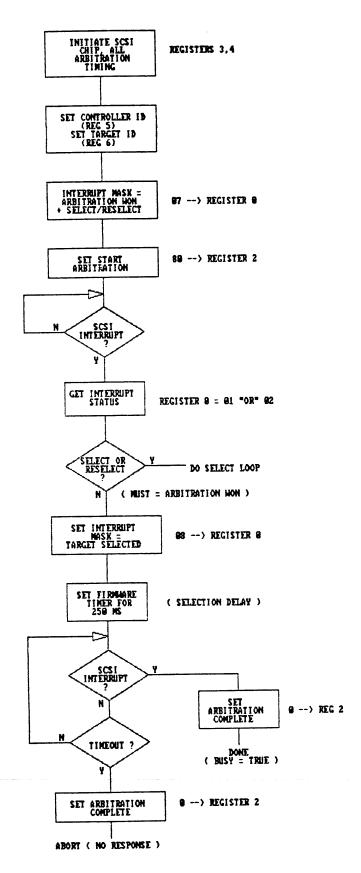

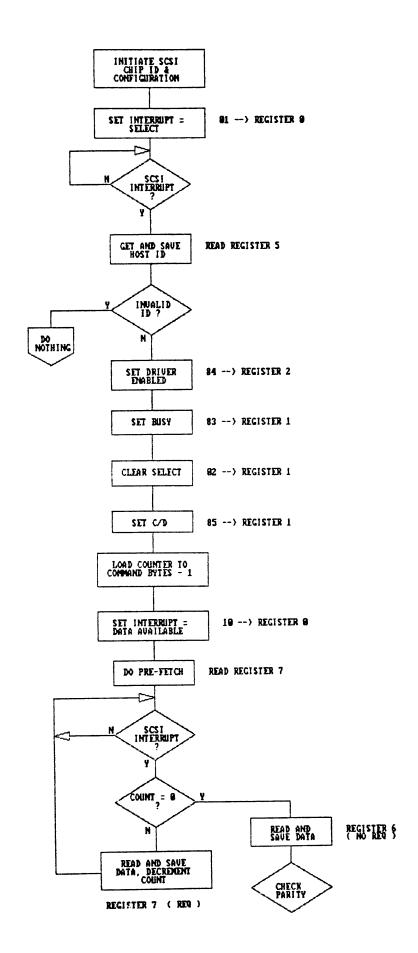

# APPENDIX A SCSI IMPLEMENTATION FLOW CHARTS

# LIST OF ILLUSTRATIONS

Page Number

| Figure Figure Figure Figure Figure Figure Figure Figure         | 2.<br>3.<br>4.<br>5.<br>6.<br>7. | Application Examples Diagram                                                                  | 1-3<br>1-3<br>1-5<br>1-6<br>3-1<br>3-2<br>3-3 |

|-----------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------|

|                                                                 |                                  | LIST OF TABLES                                                                                |                                               |

|                                                                 |                                  | Page                                                                                          | Number                                        |

| Table 1 Table 2 Table 3 Table 4 Table 5 Table 6 Table 7 Table 8 | •                                | Register Assignments and Addressing                                                           | 2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9 |

| Table 9<br>Table 1<br>Table 1                                   | 0.                               | Register 5 - Controller ID/Host Data                                                          | 2-10                                          |

| Table 1                                                         |                                  | Settings, SCSI Mode                                                                           |                                               |

|                                                                 |                                  | Settings, QIC 02 Mode                                                                         | 2-13                                          |

| Table 1                                                         | 5.                               | Pin Descriptions, Signals Common to All Modes Pin Descriptions, Signals Specific to SCSI Mode | 3 – 4                                         |

|                                                                 |                                  | Pin Descriptions, Signals Specific to QIC 02 Mode                                             | 3-11                                          |

|                                                                 |                                  | Mode                                                                                          |                                               |

|                                                                 |                                  | Mode                                                                                          | 3-18<br>3-19                                  |

#### CHAPTER 1

#### GENERAL DESCRIPTION

#### INTRODUCTION

The OMTI 5080 is designed to be used for three separate interface support functions. Used as an SCSI Controller, the 5080 provides interfacing in both Initiator and Target roles with arbitration and disconnect/reconnect support. As a disk I/O interface, the 5080 will support up to four drives. Additionally, the 5080 can be configured to support a QIC 02 interface.

The 5080 is optimized for use with the OMTI disk controller chip family, which includes the 5050 Data Sequencer and the 5060 DMA Controller, to provide a minimum hardware design with no sacrifice in performance or features.

#### **APPLICATIONS**

- \* SCSI or SASI Host Adapters

- \* Computers with SCSI or SASI ports

- \* SCSI Controllers

- \* SCSI Drives

- \* DISK Interface Control

- \* QIC 02 Interface Control

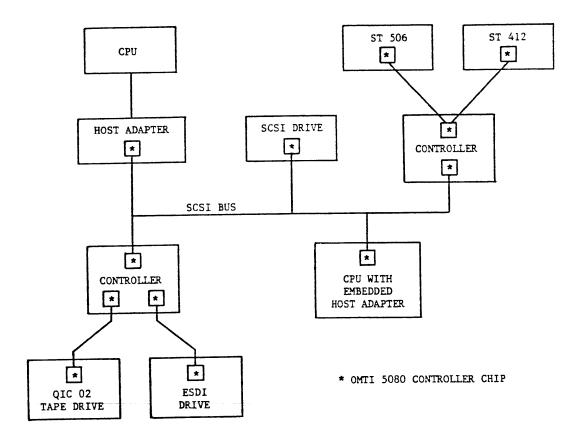

Figure 1. Application Examples Diagram

#### FEATURES

- \* Various interface support capability. Programmable to be used for one of the following three types of interface:

- 1) SCSI (Small Computer System Interface) or SASI.

- 2) QIC 02 Tape Interface (or ANSC X3T9.6 device level interface for Streaming Tape drives).

- Winchester disk drive interface (ST506/412, EDSI, 412HP, etc.)

- \* Includes single-ended drivers and receivers

- \* Microprocessor direct control of bus signals

- \* Programmable I/O or DMA transfer modes

- \* Programmable microprocessor interrupt mode

- \* Programmable SCSI Initiator and Target roles

- \* Supports SCSI disconnect/reconnect functions

- \* Programmable SCSI arbitration delay from clock input

- \* Programmable SCSI Initiator and Target ID

- \* Programmable parity check

- \* High Performance dual-bus architecture

- \* Includes six bus driver ground pins

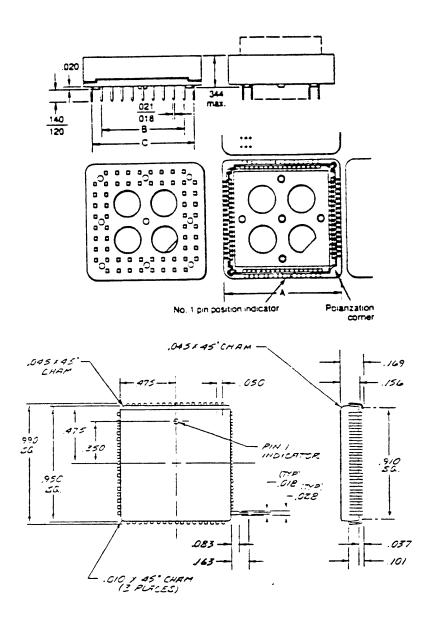

- \* 68-pin plastic leaded chip carrier

- \* Low power consumption (CMOS technology)

#### ARCHITECTURAL OVERVIEW

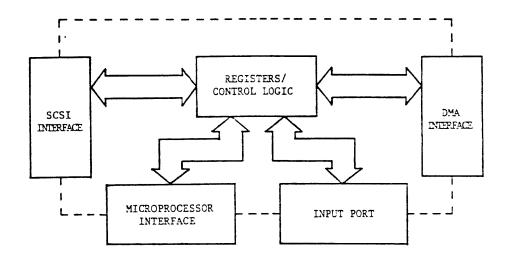

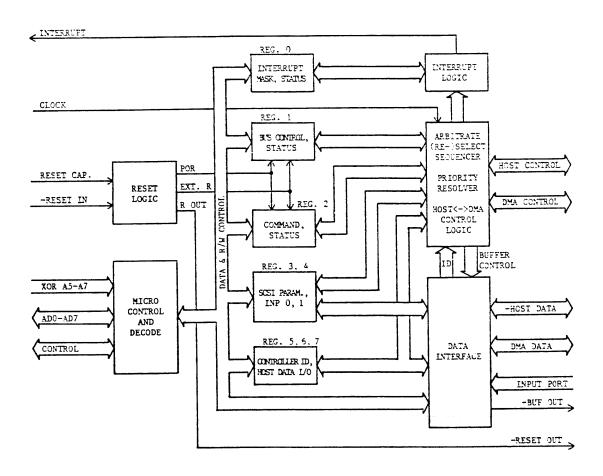

The following drawings are the Conceptual and Functional Block Diagrams of the 5080 SCSI Multifunctional Device.

Figure 2. Conceptual Block Diagram

Figure 3. Functional Block Diagram

# Registers/Control Logic

The Registers/Control block contains eight 8-bit internal registers and associated control logic. The write registers may be individually written to initialize the parameters that control data transfer, and for data transfer to the host bus. The read registers may be individually read to obtain status information about command execution, and for data transfer from the host bus.

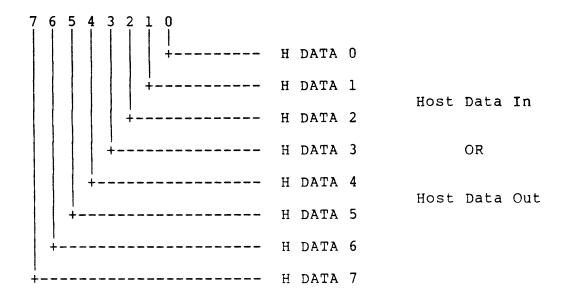

# Host Interface

Communication with the host is via an 8-bit bidirectional port. The host interface circuit contains the logic to transfer data between the host I/O port and either the DMA interface or the microprocessor interface.

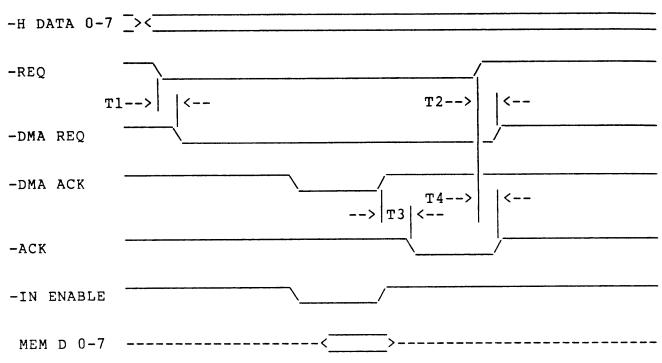

#### DMA Interface

The DMA interface circuit contains the logic to transfer data to and from the 5060 DMA Memory Controller or equivelent logic. The 5060 DMA Memory Controller provides the addresses in the buffer to which this data is to be transfered. Communication with the DMA controller is over an 8-bit bidirectional bus, with request/acknowledge handshake signals for control.

# Local Microprocessor Interface

This block contains the logic which allows the local microprocessor to read and write the internal registers, and communicate with the host and DMA interfaces. Address decoding for all interfaces and internal registers is contained within this block.

#### Input Port

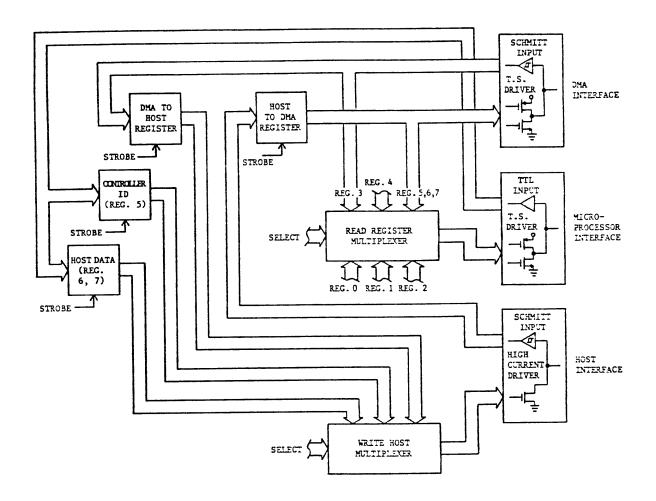

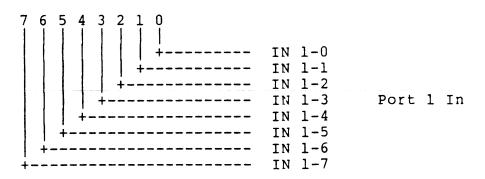

This block provides a path for the microprocessor to read jumperselectable options, or any other data input. The following diagram illustrates the main data paths within the 5080, and the type of I/O driver/receiver on each interface. Multiple source data outputs are individually selected with a multiplexer, with select lines generated by logic input from registers and control interface signals.

Figure 4. Internal Data Path and Interface Diagram

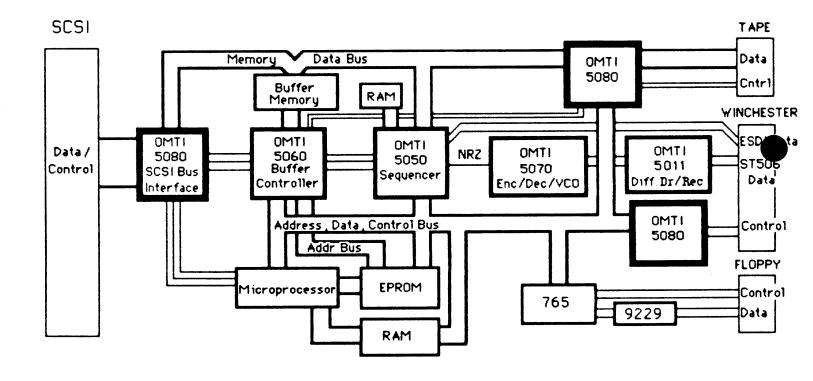

Figure 5. Typical System Configuration

Illustrated above is a typical system configuration, incorporating three 5080's in three modes of operation. Also included in the diagram is the 5050 Data Sequencer, the 5060 Four Channel DMA Controller, the 5070 VCO/Encode/Decode, and the 5011 Driver/Receiver chip.

#### CHAPTER 2

# FUNCTIONAL DESCRIPTION

#### INTRODUCTION

The 5080's basic function is to provide a versatile interface to the SCSI bus. The 5080 device can serve in either target or initiator role, depending on it's initialization. Selection/reselection and arbitration are handled by the 5080 device after the associated parameters have been entered into it's internal registers. The 5080 device provides the logic to interface the SCSI bus to a DMA data transfer device such as the OMTI 5060 DMA Controller. Microprocessor data transfers can also be performed through the 5080 device, either with automatic control of SCSI handshake or by direct microprocessor control via the 5080's Bus Control Register.

Additional functions provided in the 5080 device are support for QIC 02 and disk I/O interfaces. The QIC 02 support functions are similar to the SCSI support functions, with the exception of the selection/reselection and arbitration. Disk I/O interface can be accomplished by microprocessor access to the 5080's Bus Control Register.

The 5080 is designed to be used with a microprocessor having the proper control signals, such as the Z8 or 8051. Refer to the timing diagrams and pin descriptions for specific details.

#### REGISTERS

Registers in the 5080 provide a wide range of control over the device. They allow for selection of interrupting conditions, control of the SCSI bus and initiation/termination of commands. They provide programmable timing for the SCSI Selection/Reselection and Arbitration phases, as well as logic for arbitration. Various status bytes can be read for proper device control. Data transfer is initiated by reading and writing certain 5080 device registers. Refer to Table 1 for a list of the registers, and Tables 2 through 10 for the bit conditions associated with these registers.

# 5080 Register Organization

Table 1. Register Assignments and Addressing

| ADDRESS   | REGISTER | REGISTER FUNCTION              |                                          |  |  |  |  |  |  |

|-----------|----------|--------------------------------|------------------------------------------|--|--|--|--|--|--|

| 4 3 2 1 0 | NUMBER   | WRITE                          | READ                                     |  |  |  |  |  |  |

| 0 0 0 0 0 | 0        | Interrupt mask                 | Interrupt Status                         |  |  |  |  |  |  |

| 0 0 0 0 1 | 1        | Bus Control                    | Bus Status                               |  |  |  |  |  |  |

| 0 0 0 1 0 | 2        | Command                        | Status                                   |  |  |  |  |  |  |

| 0 0 0 1 1 | 3        | SCSI Arbitration<br>Timing     | Input Port 0                             |  |  |  |  |  |  |

| 0 0 1 0 0 | 4        | SCSI Arbitration<br>Timing     | Input Port 1                             |  |  |  |  |  |  |

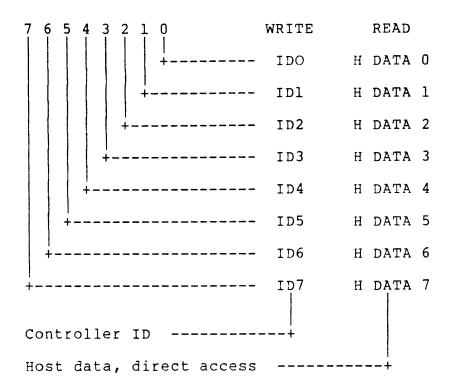

| 0 0 1 0 1 | 5        | Controller ID                  | Host data<br>(direct)                    |  |  |  |  |  |  |

| 0 0 1 1 0 | 6        | Host Data out (no handshake)   | Host data<br>(latch - no<br>handshake)   |  |  |  |  |  |  |

| 0 0 1 1 1 | 7        | Host data out (with handshake) | Host data<br>(latch - with<br>handshake) |  |  |  |  |  |  |

Address bits 5-7 = Chip Select

Table 2. Register 0 - Interrupt Mask/Status

Table 3. Register 1 - Bus Control/Status, SCSI Mode

|                            |                                 | $\mathbf{D}^{\mathbf{A}}$ | AT?                        | A E                        | 3U.S                            | 5                               | SCSI                            |                                                                                                      |

|----------------------------|---------------------------------|---------------------------|----------------------------|----------------------------|---------------------------------|---------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------|

| 7                          | 6                               | 5                         | 4                          | 3                          | 2                               | 1                               | 0                               | FUNCTION                                                                                             |

| 0<br>0<br>0<br>0<br>0<br>0 | 0 0 0 0 0 0                     | 0 0 0 0 0 0 0             | 0 0 0 0 0 0                | 0 0 0 0 0 0                | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | Clear REQ<br>Clear ACK<br>Clear SEL<br>Clear BSY<br>Clear I/O<br>Clear C/D<br>Clear MSG<br>Clear ATN |

| 1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 0 0 0 0 0 0               | 0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | * Set REQ ** Set ACK Set SEL Set BSY * Set I/O Set C/D Set MSG Set ATN                               |

- \* Can only be set in I/O and Target mode.

- \*\* Can only be set in I/O and Initiator mode.

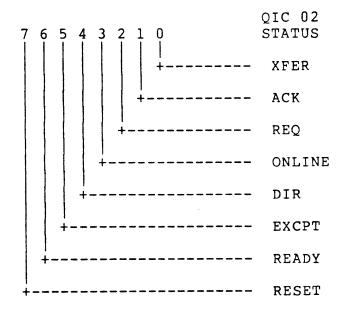

Table 4. Register 1 - Bus Control/Status, QIC 02 Mode

|   |   | DA | TA | A E | BUS | 3 |   | QIC 02       |  |  |  |

|---|---|----|----|-----|-----|---|---|--------------|--|--|--|

| 7 | 6 | 5  | 4  | 3   | 2   | 1 | 0 | FUNCTION     |  |  |  |

|   |   |    |    |     |     |   |   |              |  |  |  |

| 0 | 0 | 0  | 0  | 0   | 0   | 0 | 0 | Clear XFER   |  |  |  |

| 0 | 0 | 0  | 0  | 0   | 0   | 0 | 1 | Clear ACK    |  |  |  |

| 0 | 0 | 0  | 0  | 0   | 0   | 1 | 0 | Clear REQ    |  |  |  |

| 0 | 0 | 0  | 0  | 0   | 0   | 1 | 1 | Clear ONLINE |  |  |  |

| 0 | 0 | 0  | 0  | 0   | 1   | 0 | 0 | Clear DIR    |  |  |  |

| 0 | 0 | 0  | 0  | 0   | 1   | 0 | 1 | Clear EXCPT  |  |  |  |

| 0 | 0 | 0  | 0  | 0   | 1   | 1 | 0 | Clear READY  |  |  |  |

| 0 | 0 | 0  | 0  | 0   | 1   | 1 | 1 | Clear RESET  |  |  |  |

|   |   |    |    |     |     |   |   |              |  |  |  |

| 1 | 0 | 0  | 0  | 0   | 0   | 0 | 0 | * Set XFER   |  |  |  |

| 1 | 0 | 0  | 0  | 0   | 0   | 0 | 1 | ** Set ACK   |  |  |  |

| 1 | 0 | 0  | 0  | 0   | 0   | 1 | 0 | Set REQ      |  |  |  |

| 1 | 0 | 0  | 0  | 0   | 0   | 1 | 1 | Set ONLINE   |  |  |  |

| 1 | 0 | 0  | 0  | 0   | 1   | 0 | 0 | * Set DIR    |  |  |  |

| 1 | 0 | 0  | 0  | 0   | 1   | 0 | 1 | Set EXCPT    |  |  |  |

| 1 | 0 | 0  | 0  | 0   | 1   | 1 | 0 | Set READY    |  |  |  |

| 1 | 0 | 0  | 0  | 0   | 1   | 1 | 1 | Set RESET    |  |  |  |

- Can only be set in I/O and Target mode. Can only be set in I/O and Initiator mode.

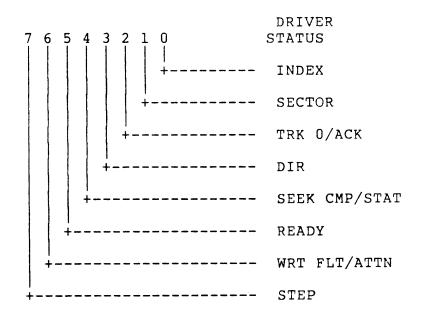

|                            |                                 | DA            | AT <i>I</i>      | A E         | 3US | 3           |                                 | DISK I/O                                                                                                         |  |  |  |

|----------------------------|---------------------------------|---------------|------------------|-------------|-----|-------------|---------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7                          | 6                               | 5             | 4                | 3           | 2   | 1           | 0                               | FUNCTION                                                                                                         |  |  |  |

| 0<br>0<br>0<br>0           | 0 0 0 0 0                       | 0 0 0 0       | 0<br>0<br>0<br>0 | 0           | 0   | 1           | 0<br>1<br>0<br>1                | Clear INDEX<br>Clear SECTOR<br>Clear TRK 0<br>Clear DIR<br>Clear SEEK CMP                                        |  |  |  |

| 0 0                        | 0 0                             | 0 0           | 0 0              | 0           | 1   | _           | 1 0                             | Clear READY<br>Clear WRT FLT<br>Clear STEP                                                                       |  |  |  |

| 1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0    | 0<br>0<br>0 | 0   | 1<br>1<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | * Set INDEX * Set SECTOR * Set TRK 0 Set DIR/CMD DATA * Set SEEK CMP * Set READY * Set WRT FLT Set STEP/XFER REQ |  |  |  |

<sup>\*</sup> These functions SHOULD NOT be SET while in DISK I/O mode.

Table 6. Register 2 - Command/Status

|                       |                       | DZ                    | T               | A E                   | 3US                        | 3                          |                       |                                                                                                                                                               |

|-----------------------|-----------------------|-----------------------|-----------------|-----------------------|----------------------------|----------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                     | 6                     | 5                     | 4               | 3                     | 2                          | 1                          | 0                     | FUNCTION                                                                                                                                                      |

| 0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0 | 0000000         | 0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>1<br>1      | 0<br>1<br>1<br>0<br>0      | 0<br>1<br>0<br>1<br>0 | Set Arbitration Complete Set Target Mode Set I/O Mode Set Select Arbitration Set Driver I/O Disable Set SCSI Mode Set Interrupt High Set Parity No-Check      |

| 1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0 | 0 0 0 0 0 0 0 0 | 0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0 | Set Arbitration Sart Set Initiator Mode Set DMA Mode  * Set Re-Select Arbitration Set Driver I/O Enable  * Set QIC 02 Mode Set Interrupt Low Set Parity Check |

<sup>\*</sup> QIC 02 and RE-SELECT both set=DISK I/O mode.

Table 7. Register 3 - SCSI Arbitration Timing O/Input Port O

WRITE (10 MHZ Clock)

| + | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | + |

|---|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |   |   |

| DELAY ENABLE BUSY | BUS FREE PHASE    |

|-------------------|-------------------|

| 0 0 0 0 not valid | 0 0 0 0 not valid |

| 0 0 0 1 200 ns    | 0 0 0 1 200 ns    |

| 0 0 1 0 300       | 0 0 1 0 300       |

| 0 0 1 1 400       | 0 0 1 1 * 400     |

| 0 1 0 0 500       | 0 1 0 0 500       |

| 0 1 0 1 600       | 0 1 0 1 600       |

| 0 1 1 0 700       | 0 1 1 0 700       |

| 0 1 1 1 * 800     | 0 1 1 1 800       |

| 1 0 0 0 900       | 1 0 0 0 900       |

| 1 0 0 1 1000      | 1 0 0 1 1000      |

| 1 0 1 0 1100      | 1 0 1 0 1100      |

| 1 0 1 1 1200      | 1 0 1 1 1200      |

| 1 1 0 0 1300      | 1 1 0 0 1300      |

| 1 1 0 1 1400      | 1 1 0 1 1400      |

| 1 1 1 0 1500      | 1 1 1 0 1500      |

| 1 1 1 1 1600      | 1 1 1 1 1600      |

<sup>\*</sup> Values defined by SCSI specification.

Table 8. Register 4 - SCSI Arbitration Timing 1/Input Port 1

WRITE (10 MHZ Clock)

| + | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | + |

|---|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |   |   |

| DELAY ENABLE SELECT | AR | BITE | RATION | DELAY |       |

|---------------------|----|------|--------|-------|-------|

| 0 0 0 0 not valid   | 0  | 0 0  | 0      | not   | valid |

| 0 0 0 1 400 ns      | 0  | 0 0  | 1      | 400   | ns    |

| 0 0 1 0 600         | 0  | 0 1  | 0      | 600   |       |

| 0 0 1 1 800         | 0  | 0 1  | 1      | 800   |       |

| 0 1 0 0 1000        | 0  | 1 0  | 0      | 1000  |       |

| 0 1 0 1 * 1200      | 0  | 1 0  | 1      | 1200  |       |

| 0 1 1 0 1400        | 0  | 1 1  | 0      | 1400  |       |

| 0 1 1 1 1600        | 0  | 1 1  | 1      | 1600  |       |

| 1 0 0 0 1800        | 1  | 0 0  | 0      | 1800  |       |

| 1 0 0 1 2000        | 1  | 0 0  | 1      | 2000  |       |

| 1 0 1 0 2200        | 1  | 0 1  | 0 *    | 2200  |       |

| 1 0 1 1 2400        | 1  | 0 1  | 1      | 2400  |       |

| 1 1 0 0 2600        | 1  | 1 0  | 0      | 2600  |       |

| 1 1 0 1 2800        | 1  | 1 0  | 1      | 2800  |       |

| 1 1 1 0 3000        | 1  | 1 1  | 0      | 3000  |       |

| 1 1 1 1 3200        | 1  | 1 1  | 1      | 3200  |       |

<sup>\*</sup> Values defined by SCSI specification.

Table 9. Register 5 - Controller ID/Host Data

Table 10. Register 6 - Host Data I/O (no handshake) Register 7 - Host Data I/O (with handshake)

I/O Port Signals -vs- Command Register Mode Settings

Table 11. SCSI Mode

|              | PIN<br>NO. | DRIVER<br>DIS. | SCSI<br>DRIVER<br>EN.<br>TARGET<br>I/O | SCSI<br>DRIVER<br>EN.<br>TARGET<br>DMA | SCSI<br>DRIVER<br>EN.<br>INIT.<br>I/O | SCSI<br>DRIVER<br>EN.<br>INIT.<br>DMA |

|--------------|------------|----------------|----------------------------------------|----------------------------------------|---------------------------------------|---------------------------------------|

| -REQ         | 54         |                | Х                                      |                                        |                                       |                                       |

| –ACK         | 47         |                |                                        |                                        | Х                                     |                                       |

| -BSY         | 45         | X              | Х                                      | X                                      | X                                     | X                                     |

| -SEL         | 51         | X              | X                                      | X                                      | X                                     | X                                     |

|              | 55         |                | X                                      |                                        |                                       |                                       |

| -I/O<br>-C/D | 53         |                | X                                      | X                                      | X                                     | X                                     |

| -MSG         | 50         |                | X                                      | X                                      | Х                                     | Х                                     |

| -ATN         | 44         | Х              | X                                      | Х                                      | х                                     | X                                     |

Note: "X" indicates I/O Port Signal -vs- Modes that can be asserted by a microprocessor write to the Bus Control Register (Reg. 1). In certain cases it may not be applicable to assert these signals.

Table 12. QIC 02 Mode

|                                       | PIN<br>NO.                 | DRIVER<br>DIS. | QIC 02<br>DRIVER<br>EN.<br>TARGET(2)<br>I/O | QIC 02<br>DRIVER<br>EN.<br>TARGET(2)<br>DMA | QIC 02<br>DRIVER<br>EN.<br>INIT.(2)<br>I/O | QIC 02<br>DRIVER<br>EN.<br>INIT.(2)<br>DMA |

|---------------------------------------|----------------------------|----------------|---------------------------------------------|---------------------------------------------|--------------------------------------------|--------------------------------------------|

| -XFER -ACK -TONLINE -TREQUEST -DIRECT | 54<br>47<br>45<br>51<br>55 | X<br>X         | X<br>X<br>X<br>X                            | X<br>X<br>X                                 | X<br>X<br>X                                | X<br>X                                     |

| -TEXCPT<br>-RDY<br>-TRESET            | 53<br>50<br>44             | x              | X<br>X<br>X                                 | X<br>X<br>X                                 | Х<br>Х<br>Х                                | X<br>X<br>X                                |

Notes: 1. "X" indicates I/O Port Signal -vs- Modes that can be asserted by a microprocessor write to the Bus Control Register (Reg. 1). In certain cases it may not be applicable to assert these signals.

2. In QIC 02 terminology, TARGET = DEVICE and INIT. = HOST.

Table 13. Disk I/O Mode

|                                                            | PIN<br>NO.                                   | DRIVER<br>DIS. | DISK I/O<br>DRIVER<br>EN.<br>TARGET<br>I/O | DISK I/O<br>DRIVER<br>EN.<br>TARGET<br>DMA | DISK I/O<br>DRIVER<br>EN.<br>INIT.<br>I/O | DISK I/O<br>DRIVER<br>EN.<br>INIT.<br>DMA |

|------------------------------------------------------------|----------------------------------------------|----------------|--------------------------------------------|--------------------------------------------|-------------------------------------------|-------------------------------------------|

| -INDEX -SECTOR -DIR -TRK 0 -SEEK CMP -READY -WRT FLT -STEP | 54<br>47<br>45<br>51<br>55<br>53<br>50<br>44 | X<br>X         | X<br>X<br>X<br>X<br>X                      | X<br>X<br>X<br>X<br>X                      | X<br>X<br>X<br>X<br>X                     | X<br>X<br>X<br>X                          |

Note: "X" indicates I/O Port Signal -vs- Modes that can be asserted by a microprocessor write to the Bus Control Register (Reg. 1). In certain cases it may not be applicable to assert these signals.

Register Descriptions

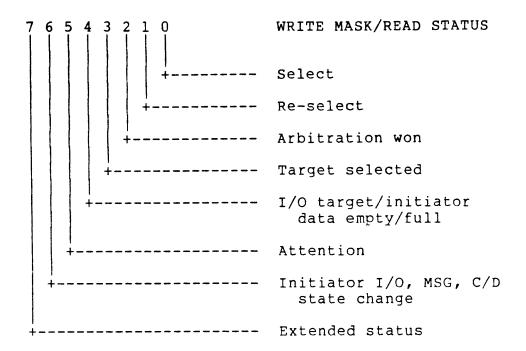

#### REGISTER 0 INTERRUPT MASK/INTERRUPT STATUS

This register gives the user control over the condition(s) causing an interrupt, and access to a byte indicating status of all interrupt conditions.

# WRITE Operation (INTERRUPT MASK)

This register allows the user to select the condition(s) by which INTERRUPT (pin 60) will become asserted. The bit condition for the mask to disable an interrupt is cleared (0). A set (1) bit will enable that condition to activate the interrupt pin. Interrupting conditions are described in the next section.

Power-on or external resets have no effect on this register.

#### READ Operation (INTERRUPT STATUS)

A read of this register allows the user to determine what condition caused INTERRUPT (pin 60) signal to become asserted. A description of the conditions for each bit of this register is as follows:

#### Bit 0 - Select

Indicates that the SCSI bus is in the Selection Phase. The following conditions exist:

-SEL is asserted

-BSY is deasserted

-I/O is deasserted

Target ID is on the SCSI bus and at least one bit completes a logical "AND" with Controller ID (Reg. 5, write).

No parity error if parity is enabled.

This bit is cleared when any of these conditions are no longer met.

# Bit 1 - Reselect

Indicates that the SCSI bus is in the Reselection Phase. The following conditions exist:

-SEL is asserted

-BSY is deasserted

-I/O is asserted

Target ID is on the SCSI bus and at least one bit completes a logical "AND" with Controller ID (Reg. 5, write).

No parity error if parity is enabled.

This bit is cleared when any of these conditions are no longer met.

#### Bit 2 - Arbitration won

Indicates that this bus device has completed the Arbitration Phase and has won arbitration. The following conditions exist:

-SEL is asserted

-BSY is deasserted (by this device)

-I/O is asserted (if Reselect)

-I/O is deasserted (if not Reselect)

The logical "OR" of the Target & Initiator ID is on the SCSI bus (Reg. 5 & 6, write).

This bit is cleared when a Set Arbitration Complete command is issued.

Bit 3 - Target selected Indicates that the Selection Phase is complete and the Target has control of the SCSI bus. The following conditions exist:

> -SEL is asserted -BSY is asserted (Asserted by Target) -I/O is asserted (If Reselect) -I/O is deasserted (if not Reselect) The logical "OR" of the Target & Initiator ID is on the SCSI bus (Reg. 5 & 6, write).

This bit is cleared when a Set Arbitration Complete command is issued or -BSY is not asserted.

Bit 4 - I/O Target/Initiator data empty/full

This bit indicates the status of the I/O data

transfer during the -REQ/-ACK handshake cycle. The

5080 device Command/Status Register (Reg. 2) must

be set up in the following way:

Driver I/O Enable SCSI Mode I/O Mode

If the 5080 device is in Target Mode, this bit will be set when -ACK becomes deasserted. In the Initiator Mode, this bit will be set when -REQ becomes asserted. It will be reset by any of the following conditions:

A microprocessor read of the Host Data Registers 6 or 7.

A microprocessor write to the Host Data Register 7. If any of the following command register modes are changed:

Driver I/O Enable SCSI Mode I/O Mode

This bit is cleared when any of these conditions are no longer met.

- Bit 5 Attention

This bit being set is an indication that the -ATN signal is in the asserted state.

- Bit 6 Initiator I/O, MSG, C/D state change.

If the Command Register (Reg. 2) is set up in

Initiator or Disk I/O Mode, then a state change on

the -I/O, -MSG, or -C/D (or their QIC 02/Disk I/O

counterpart) signals will cause this bit to be set.

This bit will be reset on the trailing edge of a

microprocessor read of the Interrupt Status Register

(Reg. 0), or any type of 5080 device reset.

Bit 7 - Extended Status

The Extended Status bit is an indication of a reset

or parity error condition. It will be set if any of

the following conditions occur:

-RST (pin 48) asserted Power On Reset Parity Error on the Host Bus (if parity is enabled)

This bit will be cleared on the trailing edge of a microprocessor read of the Status Register (Reg. 2).

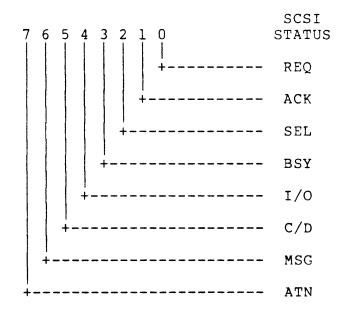

# REGISTER 1 BUS CONTROL/BUS STATUS

There are three main modes that the 5080 device can be used in. These are SCSI Mode, QIC 02 Mode, and Disk I/O Mode. All of these modes have access to one 8 bit I/O port, which will be used for the signals specific to the mode selected. The I/O port, with certain exceptions, can be accessed by a microprocessor write/read operation on the Bus Control/Bus Status Register.

# WRITE Operation (BUS CONTROL)

Most individual bits on this port can be set or cleared by writing a specific byte to the Bus Control Register (Reg. 1). Refer to Tables 11, 12, and 13, and the Register 1 table (Tables 3, 4, and 5) specific to the mode you will be using for a list of these bytes, and mode-specific exceptions.

This register is cleared by a power-on or external reset.

# READ Operation (BUS STATUS)

A status of the port signals specific to the 5080 device mode selected can be obtained by a microprocessor read of the Bus Status Register (Reg. 1). Each "1" bit in the Bus Status byte indicates an asserted state of that signal. Refer to the Register 1 table specific to the mode you will be using for a list of the Bus Status bits.

#### REGISTER 2 COMMAND/STATUS

Register 2 is the main command/status register for the 5080 device. As a command register, it is used to set modes, submodes, and conditions by which the 5080 device operates. As a status register, it is used to verify mode settings, host parity, parity errors, and reset status.

# WRITE Operation (COMMAND)

A microprocessor write to Register 2 allows the user to select the modes and conditions for the application desired. There are sixteen options to be selected, the first eight being the complement of the second eight. Therefore, the user may select one option from each complement pair (bit 0 through 2 selects the option pair, bit 7 selects the option). Refer to Tables 11, 12, and 13, and the Register 2 - Command/Status table (Table 6) for additional information.

This register is cleared by a power-on or external reset.

A description of each complement pair of commands and its hexadecimal byte is as follows:

00 H - Set Arbitration Complete 80 H - Set Arbitration Start

Set Arbitration Start is the command to start the SCSI Arbitration Phase. When a SCSI Bus Free Phase is detected by -SEL and -BSY being deasserted, the 5080 device initiates a SCSI Arbitration Phase. The arbitration phase continues until one of the following conditions occur:

Arbitration has been won by this bus device. A Set Arbitration Complete command is issued.

The 5080 device continues arbitration attempts after -SEL is found to be asserted (another device has captured the bus) or another device with a higher priority ID is found to be on the bus. The Set Arbitration Complete command must be used to disable any further arbitration attempts by the 5080 device.

01 H - Set Target Mode

81 H - Set Initiator Mode

Set Target Mode configures the 5080 device to react as a SCSI Target when in SCSI Mode, and as a QIC-02 Device when in QIC-02 Mode.

Set Initiator Mode configures the 5080 device to react as a SCSI Initiator when in SCSI Mode, and as a QIC-02 Host when in QIC-02 Mode.

02 H - Set I/O Mode 82 H - Set DMA Mode

I/O Mode is used to allow the microprocessor to transfer data directly to and from the -Host Data Bus (0-7) without using DMA channels. More information on access to the -Host Data Bus can be obtained in the description of Registers 5, 6, and 7.

DMA Mode allows for a DMA controller to have access to the -Host Data Bus and control of the SCSI/QIC 02 handshake signals. Data is transfered to and from the -Host Data Bus by way of the Memory Data Bus.

Note: If the 5080 device is set up in SCSI and Initiator Mode, a state change on the -I/O, -C/D, or -MSG signals will put the device in I/O Mode. To resume in DMA Mode, a Set DMA Mode command must be reissued.

03 H - Set Select Arbitration 83 H - Set Reselect Arbitration

The Select or Reselect Arbitration command is set in SCSI Mode to provide the correct -I/O condition on the SCSI bus during the Arbitration phase. For Select Arbitration, -I/O will be deasserted, and for Reselect Arbitration, -I/O will be asserted. To select Disk I/O Mode, QIC 02 Mode and Reselect Arbitration must be set. See the description of "Set SCSI Mode/Set QIC 02 Mode" for additional information on Disk I/O Mode.

04 H - Set Driver I/O Disable 84 H - Set Driver I/O Enable

Driver I/O Disable/Enable gives the user the capability of disabling certain pins as output drivers. Refer to Tables 11, 12, and 13 for additional information.

05 H - Set SCSI Mode 85 H - Set QIC 02 Mode

SCSI Mode and QIC 02 Mode are two of the main operating modes of the 5080 device. However, a third mode, Disk I/O Mode, can be entered by selecting QIC 02 Mode and Re-Select Arbitration. This mode is also described in this section.

SCSI Mode configures the 5080 device to mantain control of the SCSI bus as either a Target or Initiator bus device.

QIC 02 Mode configures the 5080 device to handle the QIC 02 handshake signals, control signals, and data transfers.

Disk I/O Mode configures the 5080 device as an I/O interface to an ST 506/412, or ESDI type drive. Control/status signal communication is carried out by microprocessor write/read operations on the Bus Control/Status Register (Reg. 1).

06 H - Set Interrupt High 86 H - Set Interrupt Low

> Interrupt High/Low allows the user to select the polarity of the interrupting signal on the Interrupt pin (pin 60).

07 H - Set Parity No-check 87 H - Set Parity Check

Parity No-check/Check allows the user to disable/enable the parity checking logic for the -Host Data Bus. If parity checking is disabled, no interrupts are created by parity errors and no parity error is indicated in a microprocessor Read of the Command/Status Register (Reg. 2).

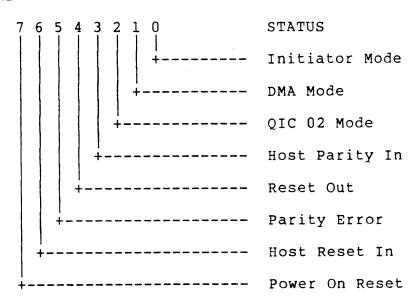

READ Operation (STATUS)

A read of this register provides the user with an 8-bit status of various mode settings and signal conditions. A description of these status bits is as follows:

Bit 0 - Initiator Mode

High - Initiatior Mode set

Low - Target Mode set

Bit 1 - DMA Mode

High - DMA Mode set Low - I/O Mode set

Bit 2 - QIC 02 Mode

High - QIC 02 Mode set Low - SCSI Mode set

Bit 3 - Host Parity In

High - Host Parity asserted

Low - Host Parity deasserted

Bit 4 - Reset Out

High - Reset in progress

Low - No reset in progress

Bit 5 - Parity Error

High - Host Data Parity error has occured Low - No Host Data Parity error latched

Bit 6 - Host Reset In

High - Host Reset signal has occured

Low - No Host Reset signal latched

Bit 7 - Power On Reset

High - Power On Reset internal to the 5080 has occured

Low - No Power On Reset status latched

Bits 0 - 3, and 5 are cleared by a power-on or external reset. Bits 5 - 7 are cleared after a read of this register takes place. Bit 4 is a direct reflection (inverted) of the condition of the -RESET OUT signal.

# REGISTER 3 SCSI ARBITRATION TIMING 0 / INPUT PORT 0

WRITE Operation (SCSI ARBITRATION TIMING 0)

Register 3, in a microprocessor write operation, consists of two 4-bit timing value registers used by the 5080's arbitration/selection logic for SCSI delay timing. A list of the delay options can be found in the Register 3 - SCSI Arbitration Timing 0/Input Port 0 table (Table 7).

Bits 0 - 3 are for the Bus Settle Delay after -SEL and -BSY are deasserted. The delay range for Bus Settle Delay is from 200 ns to 1600 ns, in increments of 100 ns.

Bits 4-7 are for the Bus Clear Delay before this bus device asserts -BSY. The delay range for Bus Clear Delay is from 200 ns to 1600 ns, in increments of 100 ns.

Power-on or external resets have no effect on this register.

READ Operation (INPUT PORT 0)

A microprocessor read of Register 3 will provide the user with direct access to the MEM D(0-7) bus (inverted), with input buffered through Schmitt Triggers. This register can be accessed independant of any Command Register settings or other conditions. No other registers or signals are affected.

# REGISTER 4 SCSI ARBITRATION TIMING 1 / -INPUT PORT 1

WRITE Operation (SCSI ARBITRATION TIMING 1)

Register 4, in a microprocessor write operation, consists of two 4-bit timing value registers used by the 5080's arbitration/selection logic for SCSI delay timing. A list of the delay options can be found in the Register 4 - SCSI Arbitration Timing 1/Input Port 1 table (Table 8).

Bits 0 - 3 are for the Arbitration Delay after -BSY is asserted. During this time, the -Host Data Bus is monitored for a higher priority ID, and -SEL is monitored for assertion by another bus device. If the delay times out prior to these conditions, -SEL will be asserted. The delay range for Arbitration Delay is from 400 ns to 3200 ns, in increments of 200 ns.

Bits 4-7 provide the Bus Settle delay value after -SEL is asserted by this bus device. The -BSY signal is deasserted upon completion of this delay. The delay range for the Bus Settle Delay is from 400 ns to 3200 ns, in increments of 200 ns.

Power-on or external resets have no effect on this register.

READ Operation (-INPUT PORT 1)

Register 4 provides the user with access to an 8-bit input port. Data is recieved through Schmitt Triggers, with input pull-ups. A microprocessor read operation on this register will put bits 0 - 7 on the data bus in an inverted state. Bits 0 - 4 are from Input Port 1 (pins 24 - 28). Bits 5, 6, and 7 are from -BUF IN (pin 29), -IN ENABLE (pin 30), and -OUT CLK (pin 31), respectively. This register can be accessed independant of any Command Register settings or other conditions. Bit 5 will appear as -BUF OUT (non-inverted) on pin 22 of the 5080 device. No other registers or signals are affected.

This port can be used to provide a SCSI bus device ID or other options from a set of jumpers.

# REGISTER 5 CONTROLLER ID/HOST DATA

WRITE Operation (CONTROLLER ID)

A microprocessor write to this register provides the 5080 device with this Initiator/Target bus device's ID, for use during the SCSI Arbitration Phase and Selection/Reselection Phase. For the Arbitration Phase, it will be placed on the -Host Data Bus after the Bus Free Phase along with -BSY being asserted. For the Selection/Reselection Phase, the contents of this register and the -Host Data Bus are logically "ANDed". If the result of the "AND" is true, the Select or Reselect Interrupt Status bit will be set.

Power-on or external resets have no effect on this register.

READ Operation (HOST DATA)

A microprocessor read operation to this register provides direct access to the contents of the -Host Data Bus (inverted). Data can be transferred from the -Host Data Bus without the 5080 device directly controlling the SCSI signals.

# REGISTER 6 HOST DATA I/O (no handshake)

A microprocessor write to this register serves two purposes, depending on the mode and phase of operation. In SCSI Mode, during arbitration, this register holds the target's ID to be logically "OR"ed with the initiator's ID in Register 5. It is then placed on the -Host Data Bus after -SEL is asserted and at least two Bus Settle Delays have occured. The other purpose, involving both Write and Read operations, is to transfer data to and from the -Host Data Bus without the 5080 device directly controlling the SCSI handshake signals. Handshake can be provided by the microprocessor through a write to the Bus Control Register (Reg. 1). In Disk I/O Mode, this register can be used as an output port for head and drive select signals.

Power-on or external resets have no effect on this register.

#### REGISTER 7 HOST DATA I/O (with handshake)

Register 7 also transfers data to and from the -Host Data Bus, except that the 5080 device handles the -REQ/-ACK handshake when a microprocessor write or read to this register occurs. The device must be set in SCSI Mode, Driver I/O Enable, and I/O Mode. When Target Mode is set, the 5080 device will control the -REQ signal. When Initiator Mode is set, it will control the -ACK signal. No other signals are directly controlled by the 5080 device when accessing this register.

Power-on or external resets have no effect on this register.

# CHAPTER 3

#### INTERFACING

# SIGNAL DESCRIPTIONS

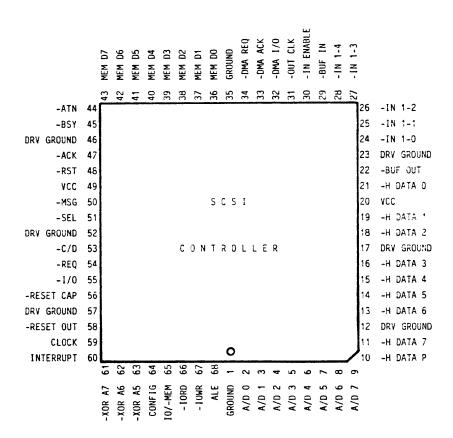

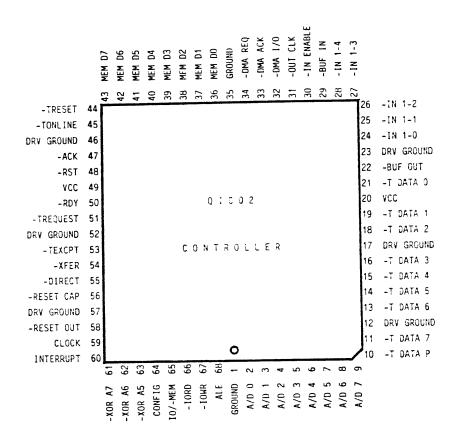

Figure 6. Pin Configuration, SCSI Controller Application

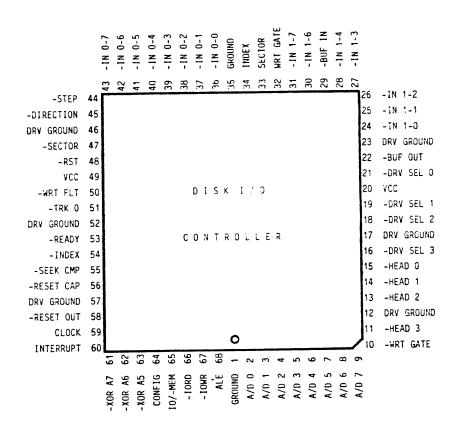

Figure 7. Pin Configuration, QIC 02 Controller Application

Figure 8. Pin Configuration, Disk I/O Controller Application

Table 14. Pin Descriptions, Signals Common to All Modes

| Symbol          | Туре | Pin<br>#  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

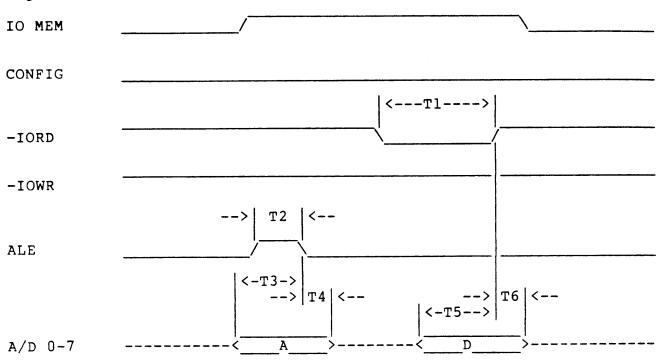

| A/D 0-<br>A/D 7 |      | 2-<br>9   | Address/Data Bus. (Active High, 3-state.) These Three-state address/data lines inter face with the microprocessor lower 8-bit address/data bus. The addresses are latched into the address latch on the falling edge of ALE. The 8-bit data is either written into or read from the SCSI controller register, depending on -IOWR or -IORD input control lines, if the address is within the range of the internal chip select. |

| -BUF OUT        | r o  | 22        | Buffer Out. (Active Low.) This open drain output driver may be used to provide a reset to the SCSI bus under external microprocessor control.                                                                                                                                                                                                                                                                                  |

| -IN 1<br>0-4    | I    | 24-<br>28 | Input Port 1. (Active Low.) These internally pulled-up inputs may be used for default setup information. For example, the SCSI default controller ID may be set with the bits of this port. These bits are accessible to the microprocessor in an Input Port 1 read operation (Register 4, read).                                                                                                                              |

| -BUF IN         | I    | 29        | Buffer In. (Active Low.) This input provides direct control of the -BUF OUT signal on pin 22. It may be read as bit 5 of Input Port 1 (Register 4, read).                                                                                                                                                                                                                                                                      |

| -RST            | I    | 48        | Reset. (Active Low.) This input is asserted by the host to abort any operation in progress and return the bus to the idle state. It provides Interrupt Status (Register 0, read) with an asserted bit 7, and Status Register (Register 2, read) with an asserted bit 6.                                                                                                                                                        |

| Symbol        | Type  | Pin<br># | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -RESET<br>CAP | 1/0   | 56       | Reset Capacitor. (Active Low.) The -RESET CAP pin is to be connected to an external capacitor to provide a power-on reset signal of externally controllable pulse width. The capacitor is discharged by either a power-on condition to the 5080 or a -RST signal. (pin 48). The -RESET OUT time is determined by the RC time constant of an internal ≡100K resistor and the external capacitor. When the capacitor charges to a 3.0v threshold, the -RESET OUT signal is deasserted. If an external open collector reset signal is applied to pin 56, the 5080 will react as it would to a -RST signal or power-on reset, except no reset status bits or reset interrupt will be set. |

| -RESET<br>OUT | 0     | 58       | Reset Out. (Active Low.) This output is asserted on power up or when the SCSI reset input is asserted. It remains asserted until the RC time constant of pin 56 reaches the 3.0v threshold, as stated by the -RESET CAP description.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CLOCK         | I     | 59       | Clock. (Active High.) This input is for a free running clock used for the internal arbitration logic. All timing is calculated with a 10 MHz clock frequency. In order to meet SCSI specifications, any change in this frequency should be kept within a range of 2.5 MHz - 13.75 MHz.                                                                                                                                                                                                                                                                                                                                                                                                |

| INTERR        | UPT O | 60       | Interrupt. (Active High on Reset, Programmable.) This output, if enabled, is asserted when any enabled interrupting sequence is detected, and is cleared when the microprocessor reads status or the interrupting event is disabled or deasserted. Refer to the Register Descriptions section under Register O, READ Operation for specific information on clearing an interrupting condition.                                                                                                                                                                                                                                                                                        |

| Symbol 5       | <br>Type | Pin<br>#  | Name and Function                                                                                                                                                                                                                                                                                                                                              |

|----------------|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -XOR A5-<br>A7 | I        | 61-<br>63 | Exclusive-OR Address 5-7. (Active Low.) These internally pulled-up inputs are used for the internal chip select. Grounding one or more of these inputs will enable the corresponding A/D 5 - A/D 7 address high signal(s) to select the 5080 device. Therefore, if another group chip select is required, ground the appropriate line(s).                      |

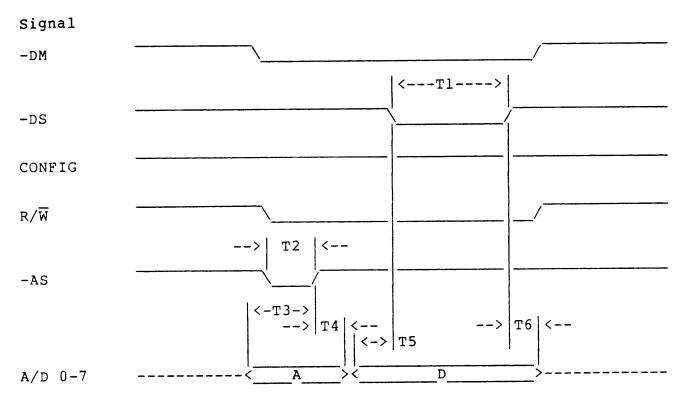

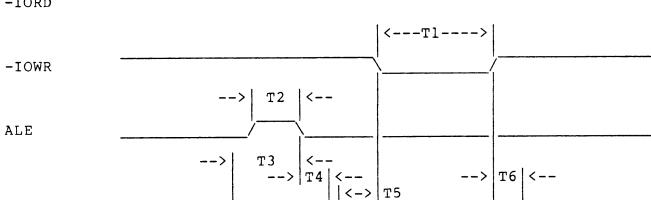

| CONFIG         | I        | 64        | Configuration. (Active High.) This internally pulled-up line is used to select the microprocessor strobe inputs. When this input is grounded, the chip is configured for an 8051 type microprocessor using individual read and write strobes. When left open, the chip is configured for a Z8 type microprocessor with separate strobe and read/write signals. |

| VCC            | I        | 20,<br>49 | VCC. +5 Vdc                                                                                                                                                                                                                                                                                                                                                    |

| GND            | I        | 1,<br>35  | Ground.                                                                                                                                                                                                                                                                                                                                                        |

| DRV GND        | ]        |           | Drive Ground (isolated from circuit ground plane).                                                                                                                                                                                                                                                                                                             |

Table 15. Pin Descriptions, Signals Specific to SCSI Mode

| Symbol         | Type | Pin<br>#               | Name and Function                                                                                                                                                                                                                                                                                                                                                          |

|----------------|------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -H DATA<br>P   | 1/0  | 10                     | Host Data Parity. (Active Low.) This driver/receiver I/O line in output mode is odd parity of the host data bus. In input mode the host must generate odd parity of the bus and the SCSI controller will check for valid parity if internally enabled.                                                                                                                     |

| -H DATA<br>0-7 | 1    | 21,<br>9,18,<br>.6-13, | Host Data 0-7. (Active Low.) These driver/ receiver input/output signals are the 8-bit data bus from/to the SCSI data bus. As inputs, they provide data to the internal Host-to-DMA Register. As outputs, they transfer data from the internal Write Host Multiplexer to this bus. Refer to Figure 5, Internal Data Path and Interface Diagram for additional information. |

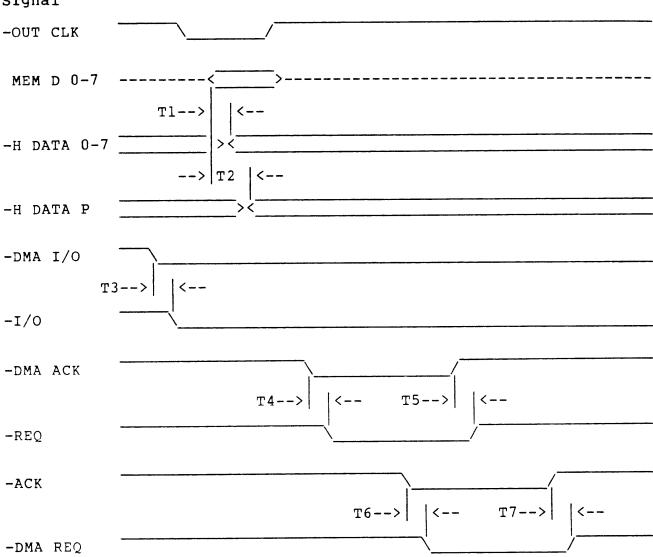

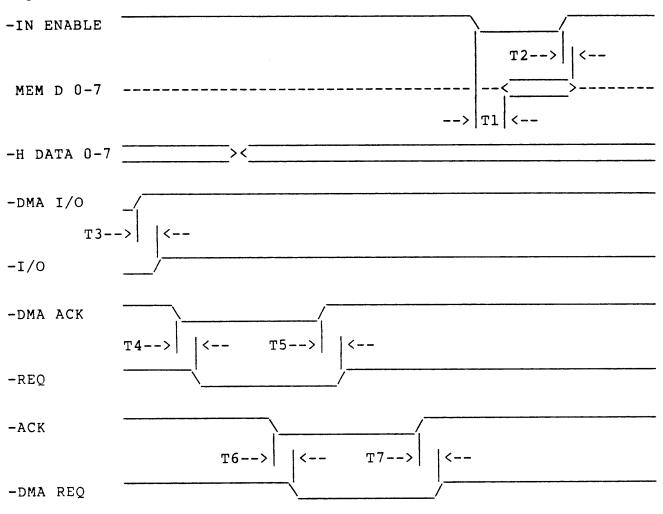

| -IN<br>ENABL   |      | 30                     | Input Enable. (Active Low.) This input enables data from the -H DATA 0-7 bus (latched) to the MEM D0-D7 bus for DMA write.                                                                                                                                                                                                                                                 |

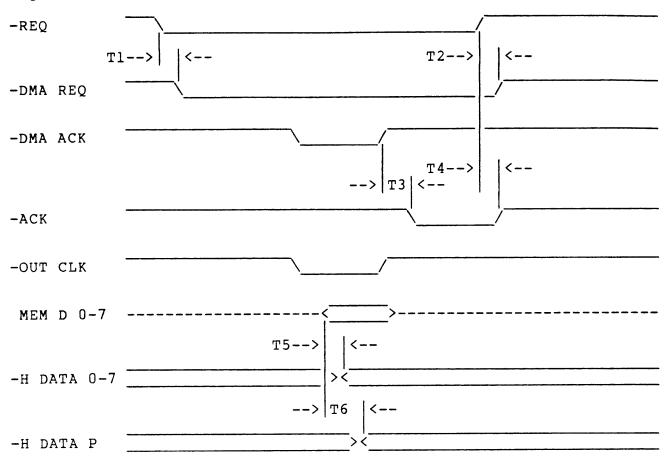

| -OUT CL        | K I  | 31                     | Output Clock. (Active Low.) This input strobes data from the MEM D0-D7 bus to the internal DMA-to-Host Register. Refer to Figure 5, Internal Data Path and Interface Diagram for additional information.                                                                                                                                                                   |

| -DMA I/        | O I  | 32                     | DMA I/O (Active Low.) This input, in DMA and Target Mode, provides direct control of the -I/O signal (pin 55) by the DMA controller.                                                                                                                                                                                                                                       |

| -DMA AC        | K I  | 33                     | DMA Acknowledge. (Active Low.) This input, in DMA and Initiator Mode, clocks the -ACK (pin 47) asserted on its trailing edge. In DMA and Target Mode, it provides direct control of the -REQ signal (pin 54).                                                                                                                                                              |

| -DMA RE        | Q 0  | 34                     | DMA Request. (Active Low.) This output, in DMA and Target Mode, is directly controlled by the -ACK input (pin 47). In DMA and Initiator Mode, it is directly controlled by the -REQ input (pin 54).                                                                                                                                                                        |

| Symbol        | Type | Pin<br>#  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

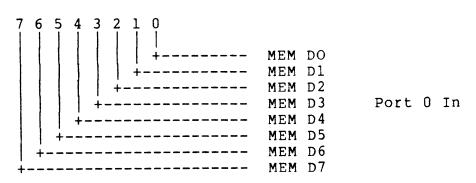

| MEM DO-<br>D7 | 1/0  | 36-<br>43 | Memory Data Bus. (Active High.) These input/output signals are the 8-bit data bus from/to the DMA buffer memory. As inputs, they provide data to the internal DMA-to-Host Register, and to a Register 3, read operation. As outputs, they transfer data from the internal Host-to-DMA Register to this bus. Refer to Figure 5, Internal Data Path and Interface Diagram for additional information.                                                  |

| -ATN          | 1/0  | 44        | Attention. (Active Low.) This driver/ receiver I/O line allows direct micro- processor control of/access to the -ATN signal through a write/read of Register 1, Bus Control/Status.                                                                                                                                                                                                                                                                  |

| -BSY          | 1/0  | 45        | Busy. (Active Low.) This driver/receiver I/O signal indicates that the bus is in use.  In Initiator Mode, (for selection) it is received, asserted, then deasserted by the 5080 device under control of the internal state generator. In Initiator Mode, (for reselection) it is received, asserted/deasserted (depending on the SCSI phase required) through a write/read of Register 1, Bus Control/Status.  In Target Mode, (for selection) it is |

|               |      |           | received, asserted/deasserted (depending on the SCSI phase required) through a write/read of Register 1, Bus Control/Status In Target Mode, (for reselection) it is received, asserted, then deasserted by the 5080 device under control of the internal state generator.                                                                                                                                                                            |

| -ACK          | 1/0  | 47        | Acknowledge. (Active Low.) This driver/ receiver I/O signal is an indication that data is available from, or has been received by, the initiator.  In Target Mode, this signal is received by                                                                                                                                                                                                                                                        |

In Target Mode, this signal is received by the 5080 device. If DMA Mode is set, -ACK has direct control of the -DMA REQ signal (pin 34).

| Symbol | Туре | Pin<br># | Name and Function                                                                                                                                                                                                                                                                                                                                                                      |

|--------|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |      |          | In Initiator Mode, this signal is asserted by the 5080 device. If DMA Mode is set, then -DMA ACK (pin 33) clocks this signal to asserted, and -REQ (pin 54) clears it to deasserted. If I/O Mode is set, then -ACK is either under the control of the Bus Control Register (Register 1, write) or the Host Data I/O Port (Register 7, automatic control of -ACK upon data write/read). |

| -MSG   | 1/0  | 50       | Message. (Active Low.) This driver/receiver I/O signal indicates that a SCSI Message Phase is in progress. The microprocessor has direct control of, or access to, the -MSG signal through the Bus Control/Status Register (Register 1, write/read).                                                                                                                                   |

| -SEL   | 1/0  | 51       | Select. (Active Low.) This driver/receiver I/O signal is an indication that the SCSI Bus is in the Selection or Reselection Phase.                                                                                                                                                                                                                                                     |

|        |      |          | In Target Mode and Selection Phase, this signal is received by the 5080 device through the Bus Status Register (Register 1, read). In Target Mode and Reselection Phase, this signal is asserted by this 5080 device, under control of it's internal state generator.                                                                                                                  |

|        |      |          | In Initiator Mode and Selection Phase, this signal is asserted by this 5080 device, under control of it's internal state generator. In Initiator Mode and Reselection Phase, this signal is received by this 5080 device to control it's internal state generator.                                                                                                                     |

| -C/D   | 1/0  | 53       | Control/Data. (Active Low.) This driver/receiver I/O signal indicates whether Control or Data information is on the databus.                                                                                                                                                                                                                                                           |

|        |      |          | In Target Mode, it is asserted by the 5080 device for all command data transfers.                                                                                                                                                                                                                                                                                                      |

|        |      |          | In Initiator Mode, this line is received to indicate that the target has command/data to transfer.                                                                                                                                                                                                                                                                                     |

| Symbol | Type | Pin<br># | Name and Function                                                                                                                                                                                                                                                                                                            |

|--------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -REQ   | 1/0  | 54       | Request. (Active Low.) This driver/ receiver I/O signal is an indication that data is to be transfered to, or received from, the initiator.                                                                                                                                                                                  |

|        |      |          | In Target Mode, this signal is asserted by the 5080 device. If DMA Mode is set, then -DMA ACK has direct control of this signal. If I/O Mode is set, then -REQ is either controlled by the Bus Control Register (Register 1, write), or the Host Data I/O Port (Register 7, automatic control of -REQ upon data write/read). |

|        |      |          | In Initiator and DMA Mode, this signal is received by the 5080 device and has direct control of the -DMA REQ signal (pin 34).                                                                                                                                                                                                |

| -1/0   | 1/0  | 55       | Input/Output. (Active Low.) This driver/receiver I/O signal controls data transfer direction with respect to the initiator. During the Reselection Phase, this signal asserted indicates that the winning bus device is a target.                                                                                            |

|        |      |          | In Target and DMA Mode, this signal is asserted by the 5080 device under direct control of the -DMA I/O signal (pin 32). In Target and I/O Mode, this signal is under the control of the Bus Control Register (Register 1, write).                                                                                           |

|        |      |          | In Initiator Mode, this signal is available to the Bus Status Register (Register 1, read).                                                                                                                                                                                                                                   |

Table 16. Pin Descriptions, Signals Specific to QIC 02 Mode

| Symbol         | Type | Pin<br>#      | Name and Function                                                                                                                                                                                                                                                                                                                                                           |

|----------------|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -T DATA<br>P   | 1/0  | 10            | Tape Data Parity. (Active Low.) Generates odd-parity of the tape data bus on output, expects odd-parity on bus on input. Controller checks for valid parity if internally enabled.                                                                                                                                                                                          |

| -T DATA<br>0-7 | 19   | ,18,<br>,-13, | Tape Data 0-7. (Active Low.) These driver/receiver input/output signals are the 8-bit data bus from/to the QIC-02 data bus. As inputs, they provide data to the internal Host-to-DMA Register. As outputs, they transfer data from the internal Write Host Multiplexer to this bus. Refer to Figure 5, Internal Data Path and Interface Diagram for additional information. |

| -IN<br>ENABL   |      | 30            | Input Enable. (Active Low.) This input enables data from the -T DATA 0-7 bus (latched) to the MEM D0-D7 bus for DMA write.                                                                                                                                                                                                                                                  |

| -OUT CL        | K I  | 31            | Output Clock. (Active Low.) This input strobes data from the MEM D0-D7 bus to the internal DMA-to-Host Register. Refer to Figure 5, Internal Data Path and Interface Diagram for additional information.                                                                                                                                                                    |

| -DMA I/        | 0 I  | 32            | DMA I/O (Active Low.) This input, in QIC-02 Mode, serves no purpose and would normally be grounded.                                                                                                                                                                                                                                                                         |

| -DMA AC        | K I  | 33            | DMA Acknowledge. (Active Low.) This input, in DMA and Device (Target) Mode, provides direct control of the -ACK signal (pin 54).                                                                                                                                                                                                                                            |

| -DMA RE        | Q O  | 34            | DMA Request. (Active Low.) This output, in DMA Mode, is directly controlled by the -ACK/-XFER input (pin 47).                                                                                                                                                                                                                                                               |

| Symbol        | Type  | Pin<br>#  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEM DO-<br>D7 | 1/0   | 36-<br>43 | Memory Data Bus. (Active High.) These input/output signals are the 8-bit data bus from/to the DMA buffer memory. As inputs, they provide data to the internal DMA-to-Host Register, and to Input Port 0 (Register 3, read). As outputs, they transfer data from the internal Host-to-DMA Register to this bus. Refer to Figure 5, Internal Data Path and Interface Diagram for additional information. |

| -TRESET       | 0     | 44        | Reset. (Active Low.) This driver/receiver I/O signal, in Host (Initiator) Mode, is asserted by the Bus Control Register (Register 1, write) to initiate a device initialization. In Device (Target) mode, the Bus Status Register (Register 1, read) receives the reset signal.                                                                                                                        |

| -TONLIN       | E I/O | 45        | Online. (Active Low.) This driver/receiver I/O line, in Host (Initiator) Mode, is assert by the Bus Control Register (Register 1, write prior to transferring a read or write command. It is deasserted to terminate that read or write command. In Device (Target) mode, the Bus Status Register (Register 1, read) receive the online signal.                                                        |

| -ACK<br>-XFER | I     | 47<br>47  | (Host Application.) (Device Application.)  Acknowledge/Transfer. (Active Low.) This driver/receiver I/O line, in QIC 02 Mode, operates as a receiver only.  In DMA mode, it is in direct control of -DMA REQ (pin 34) whether in Host (Initiator) or Device (Target) mode. In I/O mode, the Bus Status Register (Register 1, read) receives                                                            |

REQ (pin 34) whether in Host (Initiator) or Device (Target) mode. In I/O mode, the Bus Status Register (Register 1, read) receives this signal.

In Host (Initiator) Mode, this pin receives

In Host (Initiator) Mode, this pin receives the -ACK bus signal to indicate that data has been taken in a write operation, or that data is available in a read operation. In Device (Target) Mode, this pin receives the -XFER bus signal to indicate that data is available in a write operation, or that data has been taken in a read operation.

| Symbol        | Туре<br> | Pin<br>#<br>             | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|----------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -RDY          | 1/0      | 50                       | Ready. (Active Low.) This driver/receiver I/O line, in Device (Target) Mode, is asserted by the Bus Control Register (Register 1, write) when a command is completed or when the device is ready to receive/transmit the next block or receive the next command. In Host (Initiator) Mode, the Bus Status Register (Register 1, read) receives the ready signal.                                                                                                                      |

| -TREQ         | 1/0      | 51                       | Tape Request. (Active Low.) This driver/ receiver I/O line in Host (Initiator) Mode is asserted by the Bus Control Register (Register 1, write) to indicate that command data has been placed on the data bus for a Command operation, or that status has been taken from the bus in a Status Input operation. This line is asserted only when -RDY or -EXC is asserted by the tape device. In Device (Target) mode, the Bus Status Register (Register 1, read) receives this signal. |