OMTI 5098

AT COMPATIBLE

INTERFACE CHIP

REFERENCE MANUAL

FEBRUARY 1988

# OMTI 5098 AT COMPATIBLE INTERFACE CHIP

# REFERENCE MANUAL

# (PART #20516)

| REV. | REVISION              | HISTORY | PRI | T D | ATE          |

|------|-----------------------|---------|-----|-----|--------------|

|      | Original<br>First rev |         | -   |     | 1987<br>1988 |

Copyright 1987, 1988 by Scientific Micro Systems, Inc.

The information in this publication is subject to change without notice.

Scientific Micro Systems, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Scientific Micro Systems, Inc. product. No other circuit patent licenses are implied.

# TABLE OF CONTENTS

Page Number:

| SECTION | N 1. INTRODUCTION                                                 | 1-1                         |

|---------|-------------------------------------------------------------------|-----------------------------|

| 1.1     | General Description                                               |                             |

| 1.2     | OMTI 5098 "AT" Compatable Interface Chip                          | 1-1                         |

| 1.3     | Functional Overview                                               | 1-2                         |

| 1.3.1   | Host Interface and Decode                                         | 1-3                         |

| 1.3.2   | Host Data Bus                                                     | 1-3                         |

| 1.3.3   | Winchester Interface Logic                                        | 1-3                         |

| 1.3.4   |                                                                   | 1-3                         |

| 1.3.5   | Memory Data Interface                                             | 1-3                         |

| 1.3.6   |                                                                   | 1-3                         |

| 1.4     |                                                                   | $\overline{1}-\overline{4}$ |

| 1.4     | Controller Block Diagram                                          | _                           |

| SECTION | N 2. INTERFACING                                                  | 2-1                         |

| 2.1     | Pin Descriptions                                                  | 2-1                         |

| 2.2     | Pin Assignment                                                    | 2-6                         |

|         | •                                                                 |                             |

|         | N 3. INTERFACE REGISTER                                           |                             |

| 3.1     |                                                                   | 3-1                         |

| 3.2     | 11000 1109101 11001 11111 11111 11111 11111 11111 11111 1111      | 3-1                         |

| 3.3     |                                                                   | 3-1                         |

| 3.3.1   |                                                                   | 3-1                         |

| 3.3.2   |                                                                   | 3-1                         |

| 3.3.3   | Dadda dama kajiara man (in in i  | 3-3                         |

| 3.3.4   |                                                                   | 3-3                         |

| 3.3.5   |                                                                   | 3-3                         |

| 3.3.6   |                                                                   | 3-3                         |

| 3.3.7   | Size/Head/Drive Register 1F6 (176)                                | 3-3                         |

| 3.3.8   |                                                                   | 3 - 4                       |

| 3.3.9   | FDC 765 Main Status Register (OPTIONAL)                           | 3-5                         |

| 3.3.10  | FCC 765 Data Register (OPTIONAL)                                  | 3-5                         |

| 3.3.11  | Secondary Status Register 3F6 (376)                               | 3-5                         |

| 3.3.12  | Head/Select Status Register 3F7 (377)                             | 3-6                         |

| 3.4     | Host Write Register Description                                   | 3-6                         |

| 3.4.1   | Write Precomp/RWC Register 1F1 (171)                              | 3-6                         |

| 3.4.2   |                                                                   | 3-6                         |

| 3.4.3   | 000001 00001 110 120 200 200 100 100 100                          | 3-7                         |

| 3.4.4   | Cylinder Register (LSB) 1F4 (174)                                 | 3-7                         |

| 3.4.5   | Cylinder Regioed (100) ii (1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/ | 3-7                         |

| 3.4.6   | Size/Head/Drive Register 1F6 (176)                                |                             |

| 3.4.7   | Command Register 1F7 (177)                                        | 3-8                         |

| 3.4.8   |                                                                   | 3-8                         |

| 3.4.8   |                                                                   | 3-8                         |

| J.4.7   | ruc 100 pata Register (Orlional)                                  | 2-0                         |

| 3.7<br>3.7.1<br>3.7.2<br>3.7.3<br>3.7.4<br>3.7.5<br>3.7.6<br>3.7.7<br>3.7.8<br>3.8                                    | Microc<br>Microc<br>INTR<br>Writ<br>Sect<br>Sect<br>Cyli<br>Cyli<br>Size<br>Comm<br>Microc | ller Read/Writomputer Registomputer Read RQ/CONTROLLER Se Precomp Regior Count Regisor Number Reginder Register nder Register /Head/Drive Reand Register Fomputer Write                                                                                                   | er Assignmegister Detatus register Flter F2ter F3(LSB) F4.(MSB) F5.gister F6.7Register I | nent escription ister F0 Description |          | 3-8<br>3-8<br>3-8<br>3-9<br>3-9<br>3-9<br>3-9<br>3-9<br>3-10<br>3-10                 |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------|----------|--------------------------------------------------------------------------------------|

| 3.8.1<br>3.8.2<br>3.8.3<br>3.8.4<br>3.8.5<br>3.8.6<br>3.8.7<br>3.8.8<br>3.8.9<br>3.8.10<br>3.8.11<br>3.8.12<br>3.8.13 | Erro<br>Sect<br>Sect<br>Cyli<br>Size<br>Stat<br>Exte<br>Driv<br>Busy<br>Iden<br>Addi       | Select Register Floor Count Register Floor Number Register Inder Register Inder Register Register Fous Register Fous Register Fous Control Register Command Compatifier Register Inder Register Inder Register Inder Register Inder Register Inder Register Index Control | ster F2 ster F3 (LSB) F4 (MSB) F5 egister F6 Register F9 ster F9 rator Reg               | 8                                    | NLY)     | 3-10<br>3-10<br>3-10<br>3-10<br>3-10<br>3-10<br>3-11<br>3-11<br>3-11<br>3-11<br>3-12 |

| \$ECTION<br>4.1<br>4.2<br>4.3                                                                                         | Absolu<br>Standa                                                                           | C. CHARACTERING MAXIMUM Rater of Test Conditions of the Characteristics                                                                                                                                                                                                   | ings                                                                                     |                                      |          | 4-1 $4-1$                                                                            |

|                                                                                                                       |                                                                                            | LIST                                                                                                                                                                                                                                                                      | OF ILLUST                                                                                | RATIONS                              | Page Nur | mber:                                                                                |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure                                                                        | 2.<br>3.<br>4.<br>5.                                                                       | Internal Block<br>Controller Block<br>Pin Assignment<br>Pin Assignment<br>Pin Assignment<br>Pin Assignment                                                                                                                                                                | ock Diagra<br>: 5098B <b>84</b><br>: 5098B <b>80</b><br>: 5098C <b>84</b>                | m                                    |          | 1-4<br>2-6<br>2-7<br>2-8                                                             |

|                                                                                                                       |                                                                                            | L                                                                                                                                                                                                                                                                         | ST OF TAB                                                                                | LES                                  | Page Nur | mber:                                                                                |

| Table<br>Table                                                                                                        |                                                                                            | Host Register<br>Microcomputer                                                                                                                                                                                                                                            | Assignmen<br>Register                                                                    | t                                    |          | 3-1<br>3-8                                                                           |

|                                                                                                                       |                                                                                            | LI                                                                                                                                                                                                                                                                        | ST OF APPE                                                                               | NDIX                                 | Page Nu  | mber:                                                                                |

| Append                                                                                                                | ix A                                                                                       | AT Compatable                                                                                                                                                                                                                                                             | Logic Dia                                                                                | gram                                 |          | A-1                                                                                  |

#### SECTION 1

#### INTRODUCTION

### 1.1 GENERAL DESCRIPTION

The OMTI 5098 "AT" Compatible Interface chip provides all the function required for a winchester controller to interface to an AT compatible system when used with the OMTI 5055 Kombo Controller Chip. This chip provides a compatible 8 bit register set for all command, control and status along with a 16 bit data path to and from the host to the Winchester controller. The OMTI 5098 chip also includes the floppy decode logic required for a combination Winchester and floppy controller.

# 1,2 OMTI 5098 "AT" COMPATIBLE INTERFACE CHIP

- \* Direct Interface to "AT" Compatible systems

- \* No external logic required with OMTI 5055

- \* Support for external floppy controller

- \* High current drivers for host interface

- \* SCHMITT trigger inputs form host interface

- Configurable primary or secondary address

- \* 3 micron SLM CMOS Standard Cell Technology

- \* 84-Pin PLCC Package or 80-Pin PFP package

# 1.3 FUNCTIONAL OVERVIEW

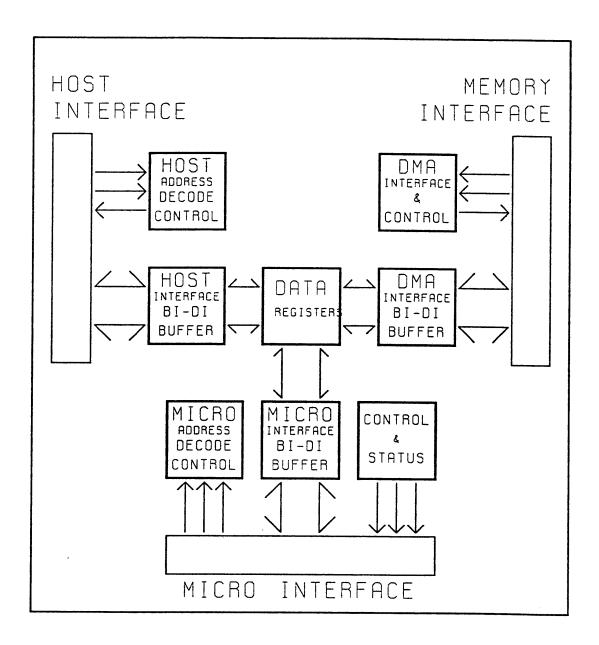

Figure 1 illustrates the internal block diagram of the OMTI 5098 "AT" Compatible Interface Chip. Each logic block is discussed in the following sections.

Figure 1. Internal Block Diagram

- 1.3.1 Host Interface and Decode

- This block contains all the logic to interface an AT compatible computer to a winchester controller. This includes all the I/O address decode logic along with all the host read write registers.

- 1.3.2 Host Data Bus

This blocks contains the 16 bit bi-directional registers used to interface the Host to the microcomputer on the controllers microcomputer and also the memory data bus.

- 1.3.3 Winchester Interface Logic

- section controls the select logic for the external This winchester, along with directing the disk drive status to the host computer.

- 1.3.4 Floppy Interface Logic

- This section controls the select logic for the external floppy controller chip along with the control of the external floppy speed control logic.

- 1.3.5 Memory Data Interface

This section controls the transfer of data to and from the external eight bit buffer memory to and from the sixteen bit host computer. It is in this block that the 8 bit to 16 bit packing and unpacking in accomplished.

1.3.6 Microcomputer Interface and Decode

This blocks interfaces the microcomputer on the controller to the read write registers in which the host interfaces and also allows the microcomputer to initialize the OMTI 5098 Interface chip.

### 1.4 CONTROLLER BLOCK DIAGRAM

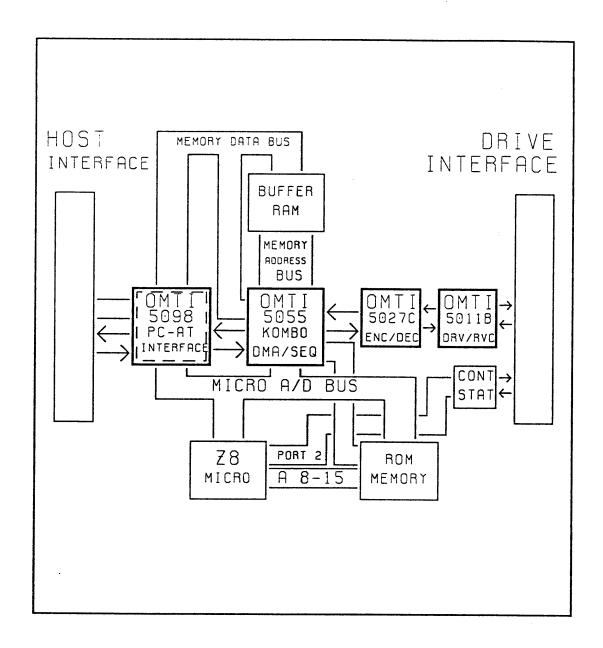

Figure 2 illustrates a complete controller block diagram using the OMTI 5098 "AT" Compatible Interface Chip along with an OMTI 5055 Kombo controller chip and an OMTI 5070 or OMTI 5027 Encode / Decode / VCO chip.

Figure 2. Controller Block Diagram

# SECTION 2

# INTERFACING

# 2.1 PIN DESCRIPTIONS

| Symbol '   | Type | Pin # | Name and Function                                                                                                                                                                                                                                 |

|------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AEN        | I    | 2     | ADDRESS ENABLE (HOST): This signal is asserted during a DMA cycle. It is used to disable the decoding of the HOST I/O ADDRESS BUS during DMA cycles.                                                                                              |

| ~IOWR      | ·I   | 3     | I/O WRITE (HOST): This input signal is asserted to write data from an I/O address (A9 - A0, AEN is de-asserted).                                                                                                                                  |

| ~IORD      | I    | 4     | I/O READ (HOST): This input signal is asserted to read data from an I/O address (A9 - A0, AEN is de-asserted).                                                                                                                                    |

| D_(7:0)    | 1/0  | 5-11  |                                                                                                                                                                                                                                                   |

| -WRITE_DAT | A O  | 12    | WRITE DATA (CONTROLLER, REV C ONLY): This output signal is asserted during a HOST write to the DATA REGISTER 1F0(170).                                                                                                                            |

| ALE        | Ţ    | 14    | ADDRESS LATCH ENABLE (HOST): This input signal is asserted to indicate that the HOST I/O ADDRESS is valid on the falling edge.                                                                                                                    |

| TDS_0      | 0    | 15    | DRIVE SELECT ZERO: This open drain output is asserted when a '0' is written to BIT 4 of WRITE REGISTER 1F6(176). If the 5098 is in the NON-SELECT MODE, this output is only asserted during reads to REGISTER 1F7(177) or the controller is BUSY. |

| IO_CH_RDY  | 0    | . 16  | I/O CHANNEL READY (HOST): This open drain, 24 MA. output signal is deasserted to lengthen an I/O data cycle. This signal is only active during WORD MODE data transfers at I/O ADDRESS 1FO(170).                                                  |

| Symbol T   | уре | Pin # | Name and Function                                                                                                                                                                                                                                                              |

|------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -10_CS_16  | 0   | 18    | I/O CHIP SELECT 16 BIT (HOST): This open drain, 24 ma. output signal is asserted to indicate that the present HOST data transfer is a 16-bit, 1 wait-state I/O cycle. It is derived from the 5098 DATA REGISTER 1F0(170) decode.                                               |

| ~DS_1      | 0   | 19    | DRIVE SELECT ZERO: This open drain output is asserted when a 'l' is written to BIT 4 of WRITE REGISTER 1F6(176). If the 5098 is in the NON-SELECT MODE, this output is only asserted during reads to REGISTER 1F7(177) or the controller is BUSY.                              |

| RESET_IN   | I   | 20    | RESET IN (HOST): This input signal is asserted to indicate that a power-up or low voltage condition exist.                                                                                                                                                                     |

| ~RESET_OUT | 0   | 21    | RESET OUT: This output is an inverted copy of the RESET_IN signal or is asserted for a minimum of 1 microsecond indicating that the 5098 has an internal power-on reset.                                                                                                       |

| RESET_SOFT | 0   | 23    | SOFT RESET: This output signal is asserted as long as BIT 2 of WRITE REGISTER 3F6(376) is asserted.                                                                                                                                                                            |

| -READY     | I   | 24    | READY: This input signal is available on BIT 6 of READ REGISTER 1F7(177).                                                                                                                                                                                                      |

| -INDEX     | I   | 25    | INDEX: This input signal is available on BIT 1 of READ REGISTER 1F7(177).                                                                                                                                                                                                      |

| DMA_INTRO  | I   | 26    | DMA INTERRUPT REQUEST: When enabled, this level sensitive input causes the 5098 to become BUSY. The polarity of this signal is programmable and should be connected to the DMA INTERRUPT signal of the DMA controller.                                                         |

| DECODE_A   | I   | 27    | ADDRESS DECODE A (HOST): This internally pulled-up signal specifies the 5098 HOST I/O address range. If no connection is made to this signal the 5098 HOST REGISTER A range is 1F0 - 1F7 (HEX). If this signal is grounded, the 5098 HOST REGISTER A range is 170 - 177 (HEX). |

| Symbol     | Type | Pin # | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DECODE_B   | I    | 28    | ADDRESS DECODE B (HOST): This internally pulled-up signal specifies the 5098 HOST I/O address range. If no connection is made to this signal the 5098 HOST REGISTER B range is 3FO - 3F7 (HEX). If this signal is grounded, the 5098 HOST REGISTER B range is 370 - 377 (HEX).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CONFIG     | I    | 29    | PROCESSOR CONFIGURATION (CONTROLLER): This internally pulled-up signal specifies the controller processor strobe inputs. If no connection is made to this signal, the 5098 is configured for a Z8-type processor. In this case, ALE_AS = AS, IORD_DS = DS, IOWR_RW = RW and IO_MEM_DM = DM. If this signal is grounded, the 5098 is configured for an 8051-type processor. In this case, ALE_AS = ALE, IORD_DS = IORD, IOWR_RW = IOMR_ARM = IOMR_DMEM_DM = IOMR_DMEM_DM = IOMR_DMEM_DM = IOMR_DMEM_DM = IOMR_DMEM_DM = IOMR_DMEM_DMEM_DM = IOMR_DMEM_DM = IOMR_DM |

| DMA_ACK    | I    | 30    | DMA ACKNOWLEDGE: This input signal, initiated by the DMA controller, indicates that a DMA transfer is taking place.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DMA_REQ    | 0    | 31    | DMA REQUEST: In conjunction with DMA_ACK, this output signal is asserted by the 5098 on the trailing edge of an IORD or IOWR to HOST ADDRESS 1F0(170) during data transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| READ_DATA  | 0    | 32    | READ DATA (CONTROLLER, REV C ONLY): This output signal is asserted during a HOST read to the DATA REGISTER 1F0(170).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ~INENA     | I    | 33    | INPUT ENABLE: This input signal is asserted by the DMA controller to enable the 5098 to drive the MEMORY Data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -OUTCLK    | I    | 34    | OUT CLOCK: This input signal is asserted by the DMA controller to save data into the 5098 form the MEMORY Data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MEM_D(7:0) | 1/0  | 35-42 | MEMORY DATA: These bi-directional signals are used to transfer data between the HOST and the Controller DMA Buffer Memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Symbol     | Type | Pin # | Name and Function                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD_(7:0)   | 1/0  | 44-51 | ADDRESS/DATA BUS (CONTROLLER): These bidirectional, tri-state signals are used to transfer address and data between the 5098 and the controller processor. The processors ADDRESS is latched on the falling edge (8051-mode) or the rising edge (Z8-mode) of the ALE_AS signal. the processors DATA is either read from or written to the 5098 (if selected) on the processors TORD_DS/TOWR_RW data strobes. |

| ALE_~AS    | I    | 52    | ADDRESS LATCH ENABLE/ADDRESS STROBE (CONTROLLER): This input signal is asserted to latch the controller microcomputers address into the 5098. In 8051 mode, this input is active high. In Z8 mode, this input is active low.                                                                                                                                                                                 |

| ~IOWR_RW   | I    | 53    | I/O WRITE (8051) READ/WRITE (Z8) (CONTROLLER): This input signal is asserted in 8051 mode, to gate data from the controller to the 5098 (if selected). If the Z8-mode is selected, this input signal is low to indicate a write function and high to indicate a read function.                                                                                                                               |

| SYS_CLK    | I    | 54    | SYSTEM CLOCK (HOST, REV C ONLY): This input is used to synchronize the IO_CH_RDY output to the system clock.                                                                                                                                                                                                                                                                                                 |

| ~IORD_~DS  | I    | 55    | I/O READ (8051) DATA STROBE (Z8) (CONTROLLER): This input signal is asserted to gate data from the 5098 (if selected) to the ADDRESS/DATA BUS of controller processor (8051-mode). If the Z8-mode is selected, this input signal is used to gate data from (READ) or to (WRITE) the 5098 (if selected).                                                                                                      |

| IO_~MEM_~I | OM I | 56    | I/O ~MEMORY (8051) ~DM (Z8) (CONTROLLER): This input signal is used for as a chip select for the 5098. In 8051 mode, this input is active high. In Z8 mode, this input is active low.                                                                                                                                                                                                                        |

| Symbol    | Туре | Pin # | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ~COMMAND  | 0    | 57    | COMMAND: This output signal is asserted to indicate that a command has been written into WRITE REGISTER 1F7(177) It is de-asserted by writing the INTERNAL CONTROL REGISTER bit 2 with a '1' or a RESET.                                                                                                                                                                                                                                                                                                       |

| -WRT_GATE | I    | 58    | WRITE GATE: This input signal is available on BIT 6 of READ REGISTER 3F7(377).                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ~DCHG     | I    | 59    | DISK CHANGED: This internally pulled-up signal is available on BIT 7 of READ REGISTER 3F7(377). If this signal is not used, BIT 7 of READ REGISTER 3F7(377) can be TRI-STATED by writing a 'l' to BIT 4 of the INTERNAL CONTROL REGISTER F8.                                                                                                                                                                                                                                                                   |

| RATE_1    | 0    | 60    | FLOPPY DATA RATE 1: This output signal along with RATE_0 determine the flexible disk data rate.                                                                                                                                                                                                                                                                                                                                                                                                                |

| RATE_0    | 0    | 61    | FLOPPY DATA RATE 0: This output signal along with RATE_1 determine the flexible disk data rate.                                                                                                                                                                                                                                                                                                                                                                                                                |

| ~FDD_REG  | 0    | 62    | FLOPPY DATA REGISTER: This output signal is asserted during an IOWR to HOST ADDRESS 3F2(372).                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ~CS_FDC   | 0    | 63    | FLOPPY CONTROLLER SELECT: This output signal is asserted during an IOWR or IORD to HOST ADDRESS 3F4-3F5(374-375).                                                                                                                                                                                                                                                                                                                                                                                              |

| INTRQ     | 0    | 65    | INTERRUPT REQUEST: This TRI-STATE output signal indicates that the 5098 needs attention. It is enabled or disabled by writing a '0' or '1' respectively to BIT 1 of WRITE REGISTER 3F6(376). It is asserted by writing a '1' to BIT 0 of the INTERNAL CONTROL REGISTER F8 and is de-asserted by writing a '0' to BIT 0 of the INTERNAL CONTROL REGISTER F8, reading SYSTEM REGISTER 1F7(177) or writing SYSTEM REGISTER 1F7(177).  REV C: Writing a '0' to BIT 0 of the INTERNAL CONTROL REGISTER will not de- |

| Symbol   | Type Pin # | Name and Function                                                                                                                                                                 |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D_(15:8) | I/O 66-73  | DATA BUS (HOST): These bi-directional, tri-state signals are used to transfer the most significant byte of HOST data to or from the 5098 DATA REGISTER.                           |

| A_(9:0)  | I 75-84    | I/O ADDRESS BUS (HOST): These input signals constitute the 10 BIT 5098 HOST I/O ADDRESS BUS and are internally decoded for the selection of internal and external 5098 registers. |

| VSS      |            | GROUND: Pins 1,17,43,74                                                                                                                                                           |

| VDD      |            | POWER: Pins 22,64                                                                                                                                                                 |

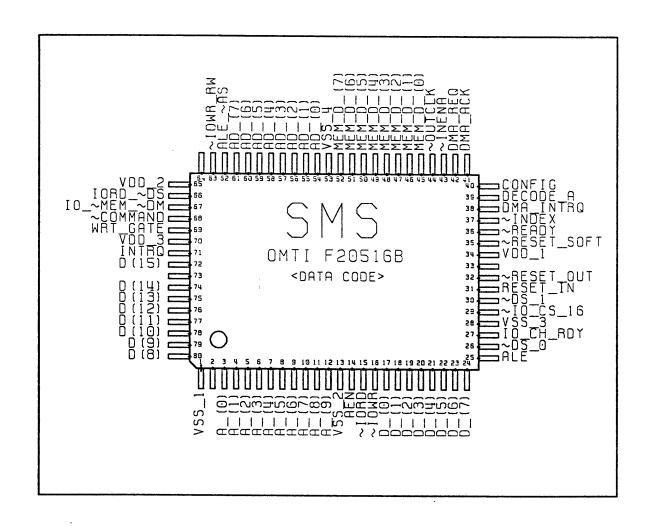

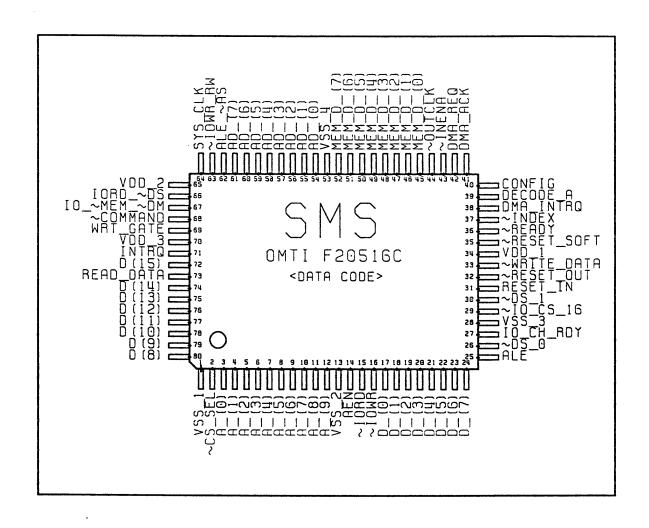

Figure 3. Pin Assignment 5098B 80 Pin PFP

Figure 3. Pin Assignment 5098C 84 Pin PLCC

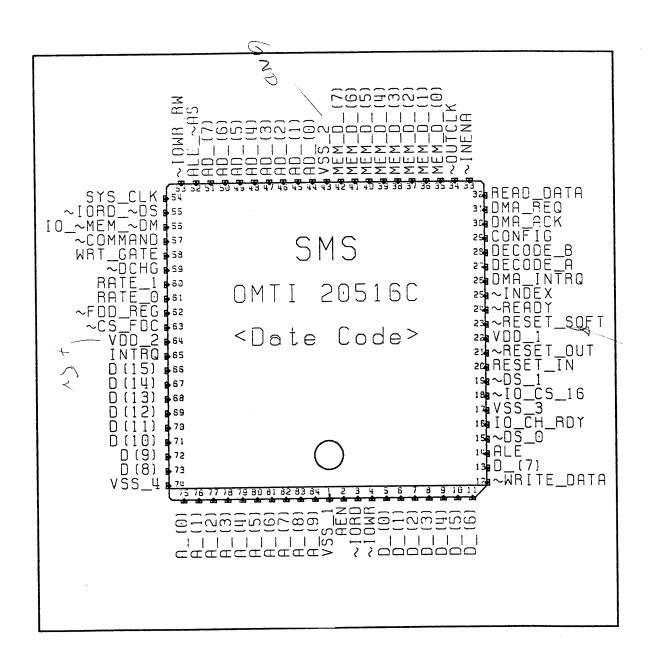

Figure 3. Pin Assignment 5098C 80 Pin PFP

# SECTION 3

#### INTERFACE REGISTERS

### 3.1 HOST INTERFACE REGISTERS

The OMTI 5098 contains 10 registers by which the HOST can communicate with the controller. The register organization described in this document relate to an 'AT' compatible Winchester/Floppy Controller application. However, these registers are general purpose READ/WRITE registers and except for some hardware specific bits, can be defined to suit other applications. Decoding for an optional FLOPPY SELECT/CONTROL REGISTER and a FDC 765 FLOPPY DISK CONTROLLER is also available.

### 3.2 HOST REGISTER ASSIGNMENT

PRIMARY (SECONDARY) READ

I/O ADDRESS

3F6(376)

3F7(377)

| 1F0(170) | DATA REGISTER           | DATA REGISTER            |

|----------|-------------------------|--------------------------|

| 1F1(171) | ERROR REGISTER          | PRECOMPENSATION REGISTER |

| 1F2(172) | SECTOR COUNT REGISTER   | SECTOR COUNT REGISTER    |

| 1F3(173) | SECTOR NUMBER REGISTER  | SECTOR NUMBER REGISTER   |

| 1F4(174) | CYLINDER REGISTER (LSB) | CYLINDER REGISTER (LSB)  |

| 1F5(175) | CYLINDER REGISTER (MSB) | CYLINDER REGISTER (MSB)  |

| 1F6(176) | SDH REGISTER            | SDH REGISTER             |

| 1F7(177) | STATUS REGISTER         | COMMAND REGISTER         |

| 3F2(372) |                         | FLOPPY SELECT/CONTROL    |

| 3F4(374) | FDC MAIN STATUS         | ·                        |

| 3F5(375) | FDC DATA                | FDC DATA                 |

|          |                         |                          |

TABLE 1 HOST REGISTER ASSIGNMENT

SECONDARY STATUS

HEAD/SELECT STATUS

### 3.3 HOST READ REGISTER DESCRIPTION

# 3.3.1 DATA REGISTER 1F0(170)

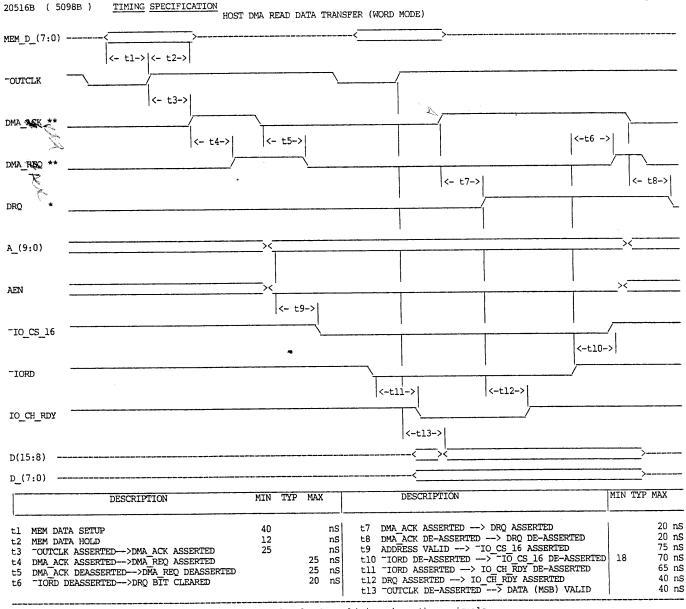

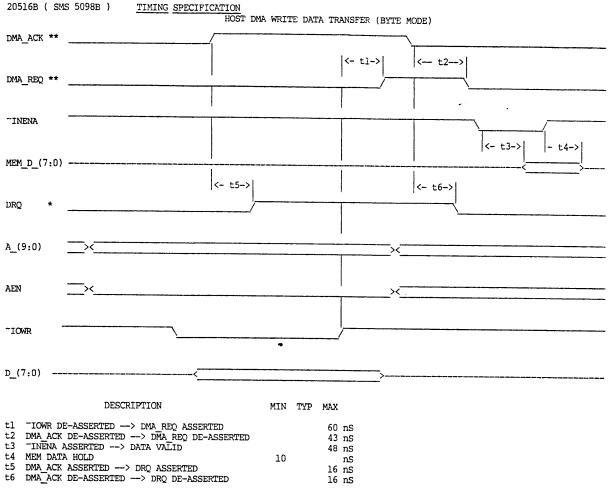

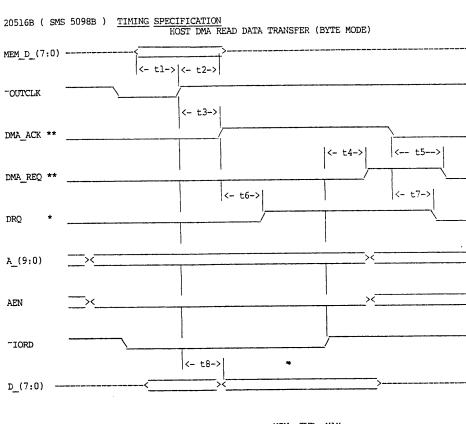

This register transfers controller data between the 5098 and the HOST. In WORD MODE, 16 bits of data are transferred requiring TO\_CS\_16 to be asserted and possibly de-asserting TO\_CH\_RDY. In BYTE MODE, 8 bits of data are transferred leaving  $\overline{-10}$   $\overline{CS}$  16 de-asserted and 10 CH RDY asserted.

WRITE

CONTROL REGISTER

FLOPPY RATE SELECT

#### **3.3.2** ERROR REGISTER 1F1(171)

This register contains the ERROR STATUS of the last command executed by the controller. It can only be accessed while the controller is in the NOT BUSY state. This register is not affected by RESET. The bit definitions are:

BIT 7 - BAD BLOCK FOUND.

This indicates that the specified track has previously been formatted with the BAD TRACK flag set in the ID field. It is not possible to access data on this track and the command will be terminated.

BIT 6 - ECC ERROR.

This indicates that a NON-ZERO syndrome was detected in a specified data field. If the data error was corrected by ECC, BIT 2 of the STATUS REGISTER will also be SET and the command will continue if more sectors are specified. If the data error was NOT corrected by ECC, BIT 0 of the STATUS REGISTER will be SET and the command terminated.

BIT 5 - NOT USED.

Set to zero.

BIT 4 - ID NOT FOUND.

This indicates that the controller was able to locate the correct cylinder and head numbers but was unable to locate the correct sector number. An ID CRC error can also generate this error condition.

BIT 3 - NOT USED.

Set to zero.

BIT 2 - ABORTED COMMAND.

The current command issued by the HOST has been aborted due to an undefined COMMAND OPCODE, or a WRITE FAULT/NOT READY condition exist on the selected drive.

BIT 1 - NO CYLINDER ZERO.

This indicates that during a RECALIBRATION command or if retries are enabled no CYLINDER 000 was detected. This error occurs after the controller issues 2048 step pulses towards cylinder 000 and the selected drive does not respond with the TRACK 000 signal.

BIT 0 - NO DATA MARK FOUND.

This indicates that the controller was able to locate the sector but was unable to locate the data mark associated with it.

# 3.3.3 SECTOR COUNT REGISTER 1F2(172)

This register contains the number of sectors to be processed and is decremented as each sector is processed. It can only be accessed while the controller is in the NOT BUSY state. register is set to 1 after a RESET.

# 3.3.4 SECTOR NUMBER REGISTER 1F3(173)

This register contains the current sector number being processed by the controller. It can only be accessed while the controller is in the NOT BUSY state. If an error condition exist, this register contains the sector number in error. It is set to 1 after a RESET.

# 3.3.5 CYLINDER (LSB) REGISTER 1F4(174)

This register contains the least significant byte of current cylinder number. It can only be accessed while the controller is in the NOT BUSY state. If an error condition exist, this register contains the least significant byte of cylinder number in error. This register is set to  $ar{0}$  after a RESET.

# 3.3.6 CYLINDER (MSB) REGISTER 1F5(175)

This register contains the most significant byte of current cylinder number. It can only be accessed while the controller is in the NOT BUSY state. If an error condition exist, this register contains the most significant byte of the cylinder number in error. This register is set to 0 after a RESET.

### 3.3.7 SDH REGISTER 1F6(176)

This register contains the controller ERROR CODE/SECTOR SIZE parameters along with the current DRIVE/HEAD select. It can only be accessed while the controller is in the NOT BUSY state. register is set to 0 after a RESET. The bit definitions are:

BIT 7 - ERROR CODE.

This bit indicates the error code selected. If this bit is set to ONE, the data field will appended with an ECC field. If set to ZERO, the data field will be appended with a CRC field.

BITS 6, 5 - SECTOR SIZE. These bits indicate the sector size selected. Their definitions are:

BIT 6 5

0 0 - 256 BYTE SECTOR

0 1 - 512 BYTE SECTOR

1 0 - 1024 BYTE SECTOR

1 1 - 128 BYTE SECTOR

BIT 4 - DRIVE SELECT.

This bit reflects the selected drive. If this bit is set to ZERO, drive 0 is selected. If set to ONE, drive 1 is selected.

BITS 3-0 - HEAD SELECT.

These bits indicate the selected head.

### 3.3.8 STATUS REGISTER 1F7(177)

This register contains the CONTROLLER/DRIVE STATUS. Reading this register de-asserts the INTRQ signal. The bit definitions are:

BIT 7 - BUSY.

This bit indicates the state of the controller. If SET, the controller is busy executing the specified command and is NOT in a DATA TRANSFER state. While set, the STATUS REGISTER is gated on the BUS during any READ to the HOST READ/WRITE REGISTERS. Any WRITE to the HOST READ/WRITE REGISTERS while this bit is set will be ignored. If CLEARED, the controller either in a NOT BUSY or a DATA TRANSFER state. The DRQ bit will SET if the controller is in the DATA TRANSFER state.

BIT 6 - READY.

This bit is an inverted copy of the TREADY signal of the selected drive.

BIT 5 - WRITE FAULT.

This bit is an inverted copy of the TWRITE FAULT signal of the selected drive.

BIT 4 - SEEK COMPLETE.

This bit is an inverted copy of the TSEEK COMPLETE signal of the selected drive.

BIT 3 - DATA REQUEST.

This bit indicates that controller is in a DATA TRANSFER mode. While this bit is SET, the BUSY bit will be CLEARED and the controller will wait for data to be transferred to or from the HOST.

BIT 2 - CORRECTED.

This bit indicates if a DATA ERROR was corrected. If SET, an ECC error occurred but was corrected. A corrected ECC error will NOT terminate a multiple sector transfer. If CRC is selected, this bit has no meaning and is set to ZERO.

BIT 1 - INDEX.

This bit is an inverted copy of the ~INDEX signal of the selected drive.

BIT 0 - ERROR.

This bit indicates if UNRECOVERABLE ERROR has occurred. If SET, an error condition exist STATUS REGISTER must be and the read to determine the error type. - ERROR

# 3.3.9 FDC 765 MAIN STATUS REGISTER (OPTIONAL)

Reading this register selects the FDC 765 MAIN STATUS register (if available). For more information, consult the FDC 765 data sheet.

# 3.3.10 FDC 765 DATA REGISTER (OPTIONAL)

Reading this register selects the FDC 765 DATA register (if available). For more information, consult the FDC 765 data sheet.

# 3.3.11 SECONDARY STATUS REGISTER 3F6 (376)

This register contains the CONTROLLER/DRIVE STATUS. It is identical to the STATUS REGISTER at address 1F7(177). See section 3.3.8 for bit definitions.

# 3.3.12 HEAD/SELECT STATUS REGISTER 3F7(377)

This register contains the HEAD/DRIVE SELECT STATUS. The bit definitions are:

This bit indicates the state of the BIT 7 - DISKETTE CHANGE. floppy ~DCHG signal. If SET, diskette, door open or drive NOT READY condition exist.

This bit indicates the state of the BIT 6 - WRITE GATE. winchester ~WRITE GATE signal.

BIT 5 - HEAD SELECT 3/RWC. This bit indicates the state of HEAD SELECT 3/RWC.

BIT 4 - HEAD SELECT 2. This bit indicates the state of HEAD SELECT 2.

This bit indicates the state BIT 3 - HEAD SELECT 1. of HEAD SELECT 1.

BIT 2 - HEAD SELECT 0. This bit indicates the state HEAD SELECT 0.

This bit indicates the state BIT 1 - DRIVE SELECT 1. DRIVE SELECT 1. If set to ZERO, DRIVE 1 is selected. If set to ONE, DRIVE 1 is de-selected.

This bit indicates the state of BIT 0 - DRIVE SELECT 0. DRIVE SELECT O. If set to ZERO, DRIVE 0 is selected. If set to ONE, DRIVE 0 is de-selected.

### 3.4 HOST WRITE REGISTER DESCRIPTION

### 3.4.1 DATA REGISTER 1F0(170)

This register transfers controller data between the HOST and the 5098. In WORD MODE, 16 bits of data are transferred requiring TO CS 16 to be asserted and possibly de-asserting IO\_CH\_RDY. In BYTE MODE, 8 bits of data are transferred leaving  $\overline{-10}$  CS 16 de-asserted and 10 CH RDY asserted.

# 3.4.2 WRITE PRECOMPENSATION/RWC REGISTER 1F1(171)

This register determines the cylinder at which WRITE PRECOMPENSATION will be applied. The value written is 1/4 the actual precompensation cylinder. A value of 255 will result in no write precompensation/reduce write current. This register should be written prior to the COMMAND REGISTER being written with a WRITE/FORMAT command. It is set to 32 (128) after a RESET.

### 3.4.3 SECTOR COUNT REGISTER 1F2(172)

This register specifies the number of sectors to processed. A value of 0 indicates 256 sectors. It should be written prior to the COMMAND REGISTER being written. This register is set to 1 after a RESET.

# 3.4.4 SECTOR NUMBER REGISTER 1F3(173)

This register specifies the starting sector number. should be written prior to the COMMAND REGISTER being written. This register is set to 1 after a RESET.

# 3.4.5 CYLINDER (LSB) REGISTER 1F4(174)

This register specifies the least significant byte of starting cylinder number. It should be written prior to the COMMAND REGISTER being written. This register is set to 0 after a RESET.

### 3.4.6 CYLINDER (MSB) REGISTER 1F5(175)

This register specifies the most significant byte of starting cylinder number. It should be written prior to the COMMAND REGISTER being written. This register is set to 0 after a RESET.

# 3.4.7 SDH REGISTER 1F6(176)

This register specifies the controller ERROR CODE/SECTOR SIZE parameters along with the DRIVE/HEAD select. This register should be written prior to the COMMAND REGISTER being written. This register is set to 0 after a RESET. The bit definitions are:

BIT 7 - ERROR CODE.

This bit specifies the error code to be selected. If this bit is SET the data field will be appended with an ECC field. If CLEARED, the data field will be appended with a CRC field.

BITS 6, 5 - SECTOR SIZE.

These bits specify the sector size to be selected. The sector size definitions are:

> 6 5 BIT 0 0 - 256 BYTE SECTOR 0 1 - 512 BYTE SECTOR 1 0 - 1024 BYTE SECTOR 1 1 - 128 BYTE SECTOR

BIT 4 - DRIVE SELECT.

This bit selects the drive. this bit is set to ZERO, drive 0 is selected. If set to ONE, drive 1 is selected.

BITS 3-0 - HEAD SELECT. These bits select the head.

### 3.4.8 COMMAND REGISTER 1F7(177)

This register specifies the command to be executed by the controller. It is set to 0 after a RESET. Writing to this register asserts the ~COMMAND signal.

# 3.4.9 FLOPPY SELECT/CONTROL REGISTER (OPTIONAL)

Writing this register selects the floppy select/control register (if available). This register is external to the OMTI 5098 and is selected by the "FDD REG signal.

# 3.4.10 FDC 765 DATA REGISTER (OPTIONAL)

Writing this register selects the FDC 765 DATA register (if available). For more information, consult the FDC 765 data sheet.

# 3.5 CONTROLLER READ/WRITE REGISTERS

The OMTI 5098 contains 8 registers by which the microcomputer can communicate with the HOST and 4 WRITE ONLY registers which control the internal/external special functions.

### 3.6 MICROCOMPUTER REGISTER ASSIGNMENT

| ADDRESS                                                                                                                                                                                            | READ                                                                                                                                                                      | WRITE                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F0<br>F1<br>F2<br>F3<br>F4<br>F5<br>F6<br>F7<br>F8<br>F7<br>F8<br>F7<br>F8<br>F7<br>F8<br>F7<br>F8<br>F7<br>F8<br>F7<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8<br>F8 | INTRQ STATUS REGISTER PRECOMPENSATION REGISTER SECTOR COUNT REGISTER SECTOR NUMBER REGISTER CYLINDER REGISTER (LSB) CYLINDER REGISTER (MSB) SDH REGISTER COMMAND REGISTER | HEAD SELECT REGISTER ERROR REGISTER SECTOR COUNT REGISTER SECTOR NUMBER REGISTER CYLINDER REGISTER (LSB) CYLINDER REGISTER (MSB) SDH REGISTER STATUS REGISTER INTERNAL CONTROL REGISTER DRIVE CONTROL REGISTER BUSY CONTROL REGISTER 5098 IDENTIFIER REGISTER |

|                                                                                                                                                                                                    |                                                                                                                                                                           |                                                                                                                                                                                                                                                               |

REV C ONLY

FC ADDITIONAL CONTROL REGISTER

TABLE 2 MICROCOMPUTER REGISTER ASSIGNMENT

# 3.7 MICROCOMPUTER READ REGISTER DESCRIPTION

# 3.7.1 INTRO STATUS REGISTER FO

This one bit register (BIT 0 ONLY) contains the status of the INTRQ bit. If this bit is SET, INTRQ is asserted. If CLEARED, INTRQ is de-asserted.

#### REV C:

This register has been expanded to include drive and command interface status. The bit definitions are:

BIT 2 - COMMAND.

This bit is an inverted copy of the external "COMMAND input signal. When this status bit is set to 'l', a write to HOST WRITE REGISTER 1F7(177) has occurred. This bit is set to '0' by writing the INTERNAL CONTROL REGISTER bit 2 with a 'l' or a RESET.

BIT 1 - READY.

This bit is an inverted copy of the external READY input signal. When this status bit is set to 'l', the selected drive is ready. When set to '0' the selected drive is NOT ready.

### 3.7.2 WRITE PRECOMPENSATION REGISTER F1

This register contains the cylinder at which WRITE PRECOMPENSATION will be applied. The value read must be multiplied by 4. A value of 255 will result in no write precompensation/reduce write current. It is read by the controller processor only after a command has been written into the COMMAND REGISTER (HOST).

### 3.7.3 SECTOR COUNT REGISTER F2

This register contains the number of sectors to be processed. It is read by the controller processor only after a command has been written into the COMMAND REGISTER (HOST).

# 3.7.4 SECTOR NUMBER REGISTER F3

This register contains the starting sector number to be processed. It is read by the controller processor only after a command has been written into the COMMAND REGISTER (HOST).

### 3.7.5 CYLINDER (LSB) REGISTER F4

This register contains the starting (least significant byte) cylinder number to be processed. It is read by the controller processor only after a command has been written into the COMMAND REGISTER (HOST).

# 3.7.6 CYLINDER (MSB) REGISTER F5

This register contains the starting (most significant byte) cylinder number to be processed. It is read by the controller processor only after a command has been written into the COMMAND REGISTER (HOST).

#### 3.7.7 SDH REGISTER F6

This register contains the controller ERROR CODE/SECTOR SIZE parameters along with the current DRIVE/HEAD select. It is read by the controller processor only after a command has been written into the COMMAND REGISTER (HOST). The bit definitions are:

BIT 7 - ERROR CODE.

This bit specifies the error code to be used. If this bit is set to ONE, the data field will appended with an ECC field If set to ZERO, the data field will be appended with a CRC field.

BITS 6, 5 - SECTOR SIZE.

These bits specify the sector size The sector size be used. definitions are:

BIT 6 5

0 0 - 256 BYTE SECTOR 0 1 - 512 BYTE SECTOR

1 0 - 1024 BYTE SECTOR

1 1 - 128 BYTE SECTOR

BIT 4 - DRIVE SELECT.

This bit specifies the drive to be selected. If this bit is set to ZERO, drive 0 is selected. If set to ONE, drive 1 is selected.

BITS 3-0 - HEAD SELECT.

These bits specify the head to be selected.

# 3.7.8 COMMAND REGISTER F7

This register contains the command to be executed by the controller. It is read only after the "COMMAND signal has been asserted.

### 3.8 MICROCOMPUTER WRITE REGISTER DESCRIPTION

### 3.8.1 HEAD SELECT REGISTER FO

This registers upper nibble (BITS 7,6,5,4) is written with current head select (BIT 7 - HEAD 2^3, BIT 4 - HEAD 2^0) during head changes on multiple sector reads or writes. BIT 0 of this register enables or disables the 5098 identifier register. If a 'l' is written to this bit, the identifier register will be accessed at HOST READ ADDRESS 3F1(371). If a '0' is written, the register is disabled.

### 3.8.2 ERROR REGISTER F1

This register is written with ERROR STATUS of the last command executed. The bit definitions are:

BIT 7 - BAD BLOCK FOUND.

This indicates that the specified track has previously been formatted with the BAD TRACK flag set in the field. It is not possible to access data on this track and the command will be terminated.

BIT 6 - ECC ERROR.

This indicates that a NON-ZERO syndrome was detected in specified data field. If the data error was corrected by ECC, BIT 2 of the STATUS REGISTER will also be SET and the command will continue if more sectors are specified. the data error was NOT corrected by ECC, BIT 0 of the STATUS REGISTER will be SET and the command terminated.

BIT 5 - NOT USED.

Set to zero.

BIT 4 - ID NOT FOUND.

This indicates that the controller was able to locate the correct cylinder and head numbers but was unable to locate the correct sector number. An ID CRC error can also generate this error condition.

BIT 3 - NOT USED.

Set to zero.

BIT 2 - ABORTED COMMAND.

The current command issued by the HOST has been aborted due to an undefined COMMAND OPCODE. WRITE FAULT/NOT READY condition exist on the selected drive.

BIT 1 - NO CYLINDER ZERO.

This indicates that during a RECALIBRATION command or if retries are enabled no CYLINDER 000 was detected. This error occurs after the controller issues 2048 step pulses towards cylinder 000 and the selected drive does not respond with the TRACK 000 signal.

BIT 0 - NO DATA MARK FOUND.

This indicates that the controller was able to locate the sector but was unable to locate the data mark associated with it.

### 3.8.3 SECTOR COUNT REGISTER F2

This register is written with the number of sectors processed. It is read by the host only after a command has been executed by the controller.

# 3.8.4 SECTOR NUMBER REGISTER F3

This register is written with the sector number that has an error by the controller. It is read by the host only after a command has been executed by the controller.

## 3.8.5 CYLINDER (LSB) REGISTER F4

This register is written with the cylinder LSB number that has an error by the controller. It is read by the host only after a command has been executed by the controller.

# 3.8.6 CYLINDER (MSB) REGISTER F5

This register is written with the cylinder MSB number that has an error by the controller. It is read by the host only after a command has been executed by the controller.

# 3.8.7 SDH REGISTER F6

This register is written with the size/drive/head number that has an error by the controller. It is read by the host only after a command has been executed by the controller. The bit definitions are:

BIT 7 - ERROR CODE.

This bit indicates the error code selected. If this bit is set to ONE, the data field will be appended with an ECC field. If set to ZERO, the data field will be appended with a CRC field.

BITS 6, 5 - SECTOR SIZE. These bits indicate the sector size selected. Their definitions are:

BIT 6 5

0 0 - 256 BYTE SECTOR

0 1 - 512 BYTE SECTOR

1 0 - 1024 BYTE SECTOR

1 1 - 128 BYTE SECTOR

BIT 4 - DRIVE SELECT.

This bit reflects the selected drive. If this bit is set to ZERO, drive 0 is selected. If set to ONE, drive 1 is selected.

BITS 3-0 - HEAD SELECT.

These bits indicate the selected head.

# 3.8.8 STATUS REGISTER F7

This register is written with the status by the controller. It is read by the host only after a command has been executed by the controller. The bit definitions are:

### 3.8.9 INTERNAL CONTROL REGISTER F8

This register is written by the controller and is used to control of the internal operations of the 5098. This register is set to 0 after a RESET. The bit definitions are:

BIT 7 - DMA BUSY.

This bit controls if DMA\_INTRQ will cause BUSY status. Writing a 'l' to this bit will enable DMA INTRO to cause the 5098 BUSY status. Writing a '0' will disable the DMA\_INTRQ signal. Disabling DMA INTRQ will not affect the BUSY state.

BIT 6 - SELECT.

This bit controls the TDS 0 or ~DS l output enable. If the DIS SELECT (BIT 5) is not set, this bit has no meaning. Writing a 'l' to this bit will enable the drive select signals. Writing a '0' will disable them.

BIT 5 - DIS\_SELECT.

This bit enables or disables the drive select function. Writing a 'l' to this bit will enable the drive select function. This causes the drive to be selected only during STATUS reads or the SELECT bit is set. Writing a '0' to this bit disables the drive select function leaving the drive select signals active at all times.

BIT 4 - DIS MSB.

This bit enables or disables the most significant bit (MSB) of HOST REGISTER 3F7(377) during reads. Writing a 'l' to this bit disables (tri-states) BIT 7 of HOST REGISTER 3F7(377). Writing a '0' enables (drives) it.

BIT 3 - DIS\_WORD.

This bit enables or disables word (16 bit) data transfers. Writing a '1' to this bit enables word data transfers during read or writes to HOST REGISTER 1F0(170). While in WORD MODE, the TO\_CS\_16 and TO\_CH\_RDY signal are enabled. Writing a '0' causes byte (8 bit) data transfers during read or writes to HOST REGISTER 1F0(170). In this case, the TO\_CS\_16 and TO\_CH\_RDY signals are disabled.

BIT 2 - COMMAND

This bit is used to reset the COMMAND signal. Writing a '1' to this bit deasserts the COMMAND signal. Writing a '0' leaves the COMMAND signal in its current state.

BIT 1 - BUSY

This bit is used to set or reset the 5098 BUSY STATUS. Writing a '1' to this bit will set the BUSY STATUS. Writing a '0' will clear it.

BIT 0 - INTERRUPT

This bit is used to set or reset the INTRQ signal. Writing a 'l' to this bit will set the INTRQ signal. Writing a '0' will clear it.

REV C: Writing a 0 to this bit has no effect on the INTRQ signal

# 3.8.10 DRIVE STATUS CONTROL REGISTER F9

This register is written by the controller and is used to control both the 5098 and the drive status. The bit definitions are:

BIT 7 - POLARITY.

This bit specifies the polarity of the DMA INTRO input. Writing a 'l' to this bit causes (if enabled) the 5098 BUSY STATUS to be set when DMA INTRQ is a 'l'. Writing a '0' causes BUSY STATUS when DMA\_INTRQ is a '0'.

BITS 6 - DIS BUSY.

This bit enables or disables the 5098 BUSY STATUS. Writing a 'l' to this bit disables BUSY. Writing a '0' enables BUSY.

BIT 5 - NOT RDY 1.

This bit allows the controller to override the TREADY signal for drive select 1. Writing a 'l' to this bit will cause the 5098 to indicate DRIVE NOT READY status for drive select 1 regardless of the "READY signal. Writing a '0' will allow the "READY signal to indicate DRIVE NOT READY STATUS.

BIT 4 - WF 1.

This bit specifies the WRITE FAULT status for drive select 1. Writing a '1' to this bit will cause the 5098 to indicate WRITE FAULT status. Writing a '0' will signal no WRITE FAULT.

BIT 3 - SC 1.

This bit specifies the SEEK COMPLETE status for drive select 1. Writing a 'l' to this bit will cause the 5098 to indicate SEEK COMPLETE status. Writing a '0' will indicate NO SEEK COMPLETE status.

BIT 2 - NOT RDY 0.

This bit allows the controller to override the TREADY signal for drive select 0. Writing a 'l' to this bit will cause the 5098 to indicate DRIVE NOT READY status for drive select 0 regardless of the TREADY signal. Writing a '0' will allow the TREADY signal to indicate DRIVE NOT READY STATUS.

BIT 1 - WF 0.

This bit specifies the WRITE\_FAULT status for drive select 0. Writing a '1' to this bit will cause the 5098 to indicate WRITE FAULT status. Writing a '0' will signal no WRITE FAULT.

BIT 0 - SC 0.

This bit specifies the SEEK COMPLETE status for drive select 0. Writing a '1' to this bit will cause the 5098 to indicate SEEK COMPLETE status. Writing a '0' will indicate NO SEEK COMPLETE status.

# 3.8.11 BUSY COMMAND COMPARATOR REGISTER FA

This register is written by the controller and is used to allow for two commands that will not cause the 5098 to indicate BUSY status. It is organized into two nibbles. Bits 7,6,5,4 represent the first command, bits 3,2,1,0 represent the second. These nibbles correspond to bits 7,6,5,4 of HOST REGISTER 1F7(177). This register must be initialize prior to writing a command to the 5098.

### 3.8.12 5098 IDENTIFIER REGISTER FB