Scientific Micro Systems, Inc.

### OMTI 5098 AT COMPATIBLE INTERFACE CHIP

#### REFERENCE MANUAL

#### (PART #20516)

| REV. | REVISION | HISTORY | PRINT DATE   |

|------|----------|---------|--------------|

|      | Original | Issue   | May 19, 1987 |

Copyright 1987 by Scientific Micro Systems, Inc.

The information in this publication is subject to change without notice.

Scientific Micro Systems, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Scientific Micro Systems, Inc. product. No other circuit patent licenses are implied.

### TABLE OF CONTENTS

Page Number:

| 1.3.3 Winchester Interface Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-1<br>1-2<br>1-3<br>1-3<br>1-3<br>1-3                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1.4 Controller Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-3<br>1-4                                                                       |

| SECTION 2. INTERFACING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-1                                                                              |

| Host Register Assignment  Host Read Register Description  Host Read Register 1F0 (170)  Tror Register 1F1 (171)  Sector Count Register 1F2 (172)  Cylinder Register (LSB) 1F4 (174)  Cylinder Register (MSB) 1F5 (175)  Size/Head/Drive Register 1F6 (176)  Size/Head/Drive Register 1F6 (176)  Total Status Register 1F7 (177)  The status Register 1F7 (177)  Host Write Register (OPTIONAL)  Head/Select Status Register 3F6 (376)  Host Write Register Description  Host Write Register Description  Host Write Register Description  Sector Count Register 1F2 (172)  Sector Count Register 1F3 (173)  Cylinder Register (LSB) 1F4 (174)  Cylinder Register (MSB) 1F5 (175) | 3-1<br>3-1<br>3-1<br>3-3<br>3-3<br>3-3<br>3-3<br>3-5<br>3-6<br>3-7<br>3-7<br>3-8 |

| 3.6<br>3.7<br>3.7.1<br>3.7.2<br>-3.7.3<br>3.7.4<br>3.7.5<br>3.7.6<br>3.7.7<br>3.8<br>3.8.1<br>3.8.3<br>3.8.4<br>3.8.5<br>3.8.6 | Microco<br>Write<br>Secto<br>Secto<br>Cylin<br>Size<br>Commo<br>Microco<br>Head<br>Sect<br>Sect | ller Read/Writomputer Registomputer Registor Count Registor Number Register Register Register Property Register Register Select Registor Count Registor Count Registor Number Register | er Assignmedister Dester 20F1 ter 20F2 ster 20F3 (LSB) 20F (MSB) 20F gister 20 Register 20F0 ter 20F0 ster 20F2 ster 20F3 (LSB) 20F (MSB) 20F | ment escripti 4 Descript | on    |         | 3-8<br>3-8<br>3-9<br>3-9<br>3-9<br>3-10<br>3-10<br>3-10<br>3-10<br>3-10 |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|---------|-------------------------------------------------------------------------|

| 3.8.7<br>3.8.9<br>3.8.10<br>3.8.9                                                                                              | Comm                                                                                            | /Head/Drive Reland Register 2<br>ernal Control Register 2<br>ernal Control Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20F7<br>Register 2                                                                                                                            | OF8                      |       |         | 3-10                                                                    |

| SECTION<br>4.1<br>4.2<br>4.3                                                                                                   | Absolu                                                                                          | C. CHARACTER<br>te Maximum Rai<br>rd Test Condi<br>Tharacteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tings                                                                                                                                         |                          |       |         | 4-1                                                                     |

|                                                                                                                                |                                                                                                 | LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OF ILLUST                                                                                                                                     | TRATIONS                 |       | Page Nu | mber:                                                                   |

| Figure<br>Figure<br>Figure                                                                                                     | 2.                                                                                              | Internal Bloc<br>Controller Bl<br>Pin Assignmen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ock Diagra                                                                                                                                    | am                       |       |         | 1-4                                                                     |

|                                                                                                                                |                                                                                                 | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IST OF TAI                                                                                                                                    | BLES                     |       |         |                                                                         |

|                                                                                                                                |                                                                                                 | ٠.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                               | • •                      |       | Page Nu | mber:                                                                   |

| Table<br>Table                                                                                                                 |                                                                                                 | Host Register<br>Microcomputer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Assignmen<br>Register                                                                                                                         | nt<br>Assignm            | ent   |         | 3-1<br>3-8                                                              |

|                                                                                                                                |                                                                                                 | LI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ST OF APP                                                                                                                                     | ENDIX                    |       | Page Nu | ımber:                                                                  |

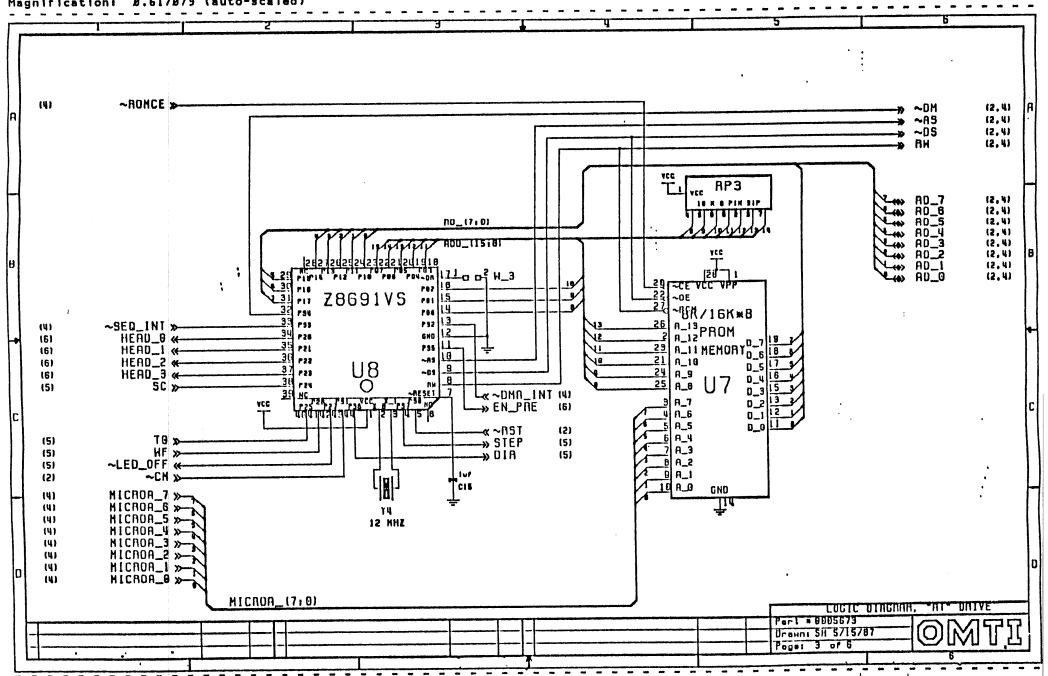

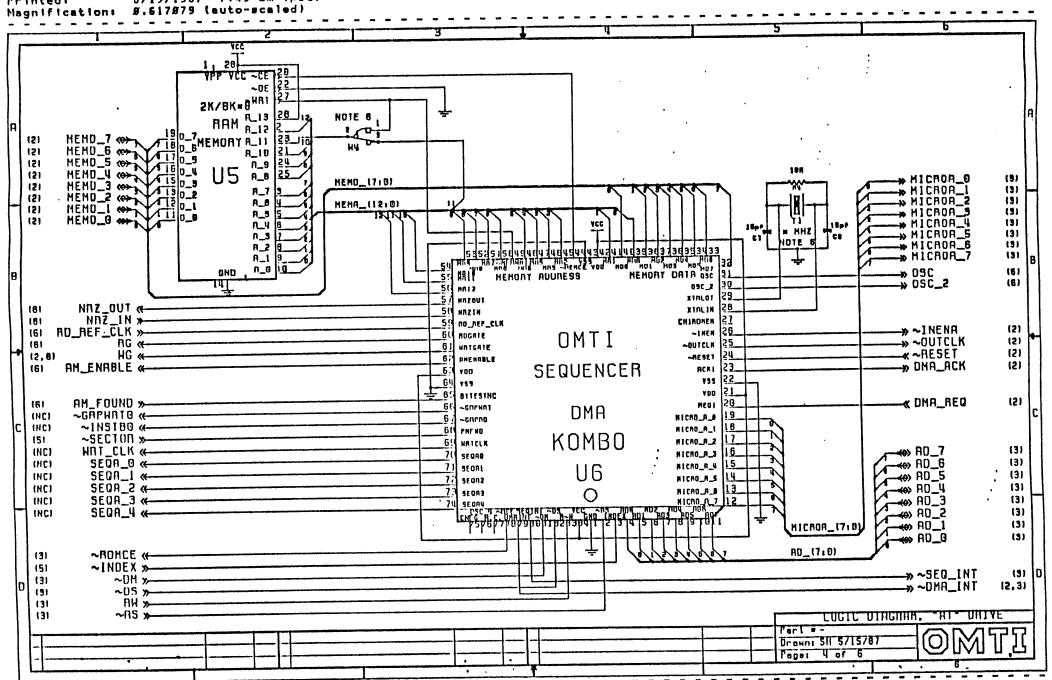

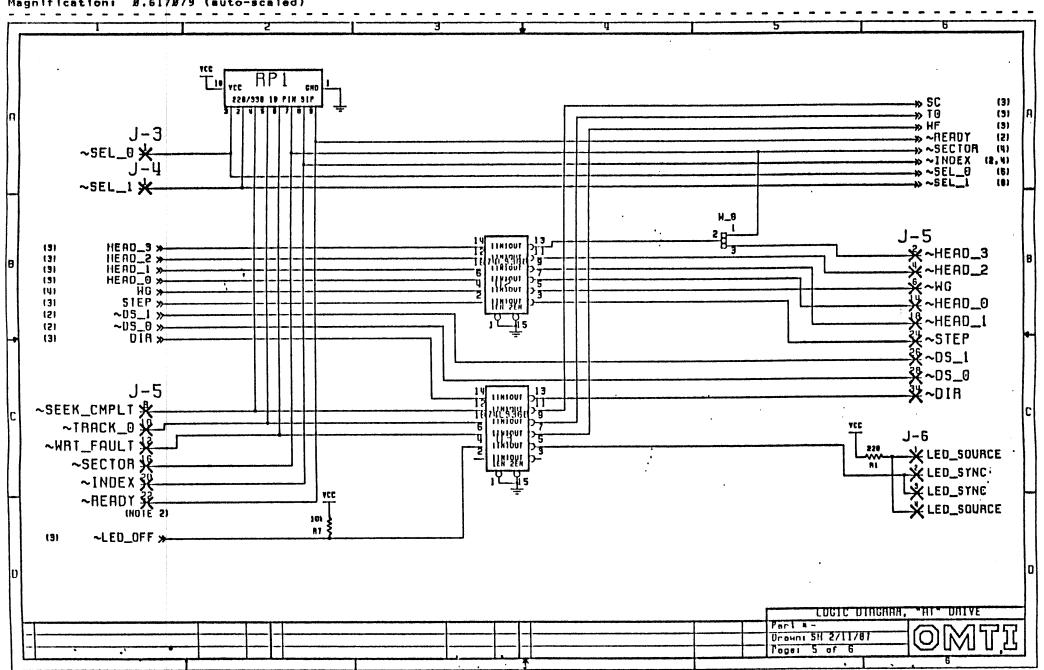

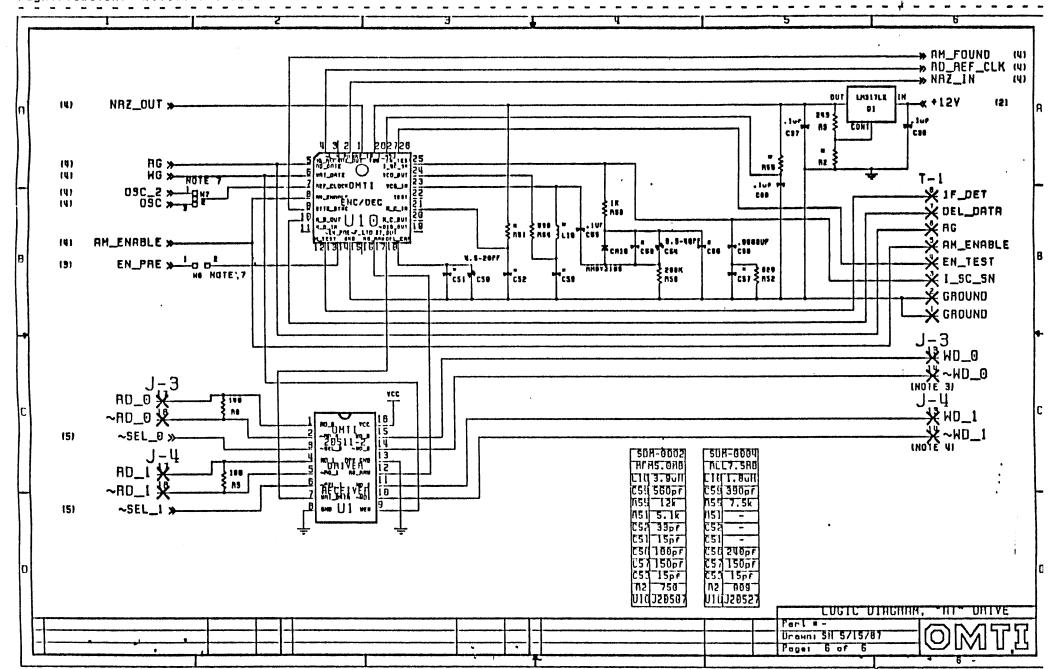

| Append                                                                                                                         | lix A                                                                                           | AT Compatable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Logic Di                                                                                                                                      | agram                    | ••••• |         | A-1                                                                     |

#### SECTION 1

#### INTRODUCTION

#### 1.1 GENERAL DESCRIPTION

The OMTI 5098 "AT" Compatiable Interface chip provides all the function required for a winchester controller to interface to an AT compatiable system when used with the OMTI 5055 Kombo Controller Chip. This chip provides a compatiable 8 bit register set for all command, control and status along with a 16 bit data path to and from the host to the Winchester controller. The OMTI 5098 chip also includes the floppy decode logic required for a combination Winchester and floppy controller.

### 1.2 OMTI 5098 "AT" COMPATIABLE INTERFACE CHIP

- \* Direct Interface to "AT" Compatiable systems

- \* No external logic required with OMTI 5055

- \* Support for external floppy controller

- \* High current drivers for host interface

- \* Schmidt trigger inputs form host interface

- Configurable primary or secondary address

- \* 3 micron SLM CMOS Standard Cell Technology

- \* 84-Pin PLCC Package or 80-Pin PFP package

## 1.3 FUNCTIONAL OVERVIEW

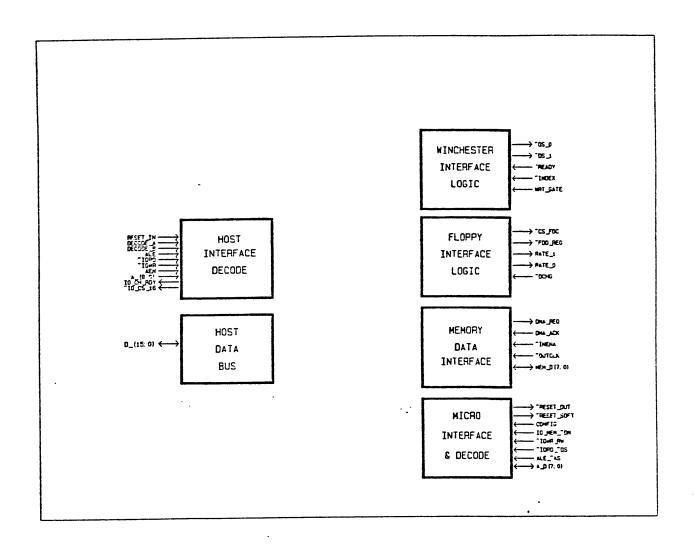

Figure 1 illustrates the internal block diagram of the OMTI 5098 "AT" Compatiable Interface Chip. Each logic block is discussed in the following sections.

Figure 1. Internal Block Diagram

- 1.3.1 Host Interface and Decode

This block contains all the logic to interface an AT compatiable computer to a winchester controller. This includes all the I/O address decode logic along with all the host read write registers.

- 1.3.2 Host Data Bus

This blocks contains the 16 bit bi-directional registers used to interface the Host to the microcomputer on the controllers microcomputer and also the memory data bus.

- 1.3.3 Winchester Interface Logic

This section controls the select logic for the external winchester, along with directing the disk drive status to the host computer.

- 1.3.4 Floppy Interface Logic

This section controls the select logic for the external floppy controller chip along with the control of the external floppy speed control logic.

- 1.3.5 Memory Data Interface

This section controls the transfer of data to and from the external eight bit buffer memory to and from the sixteen bit host computer. It is in this block that the 8 bit to 16 bit packing and unpacking in accomplished.

- 1.3.6 Microcomputer Interface and Decode

This blocks interfaces the microcomputer on the controller to the read write registers in which the host interfaces and also allows the microcomputer to initialize the OMTI 5098 Interface chip.

## 1.4 CONTROLLER BLOCK DIAGRAM

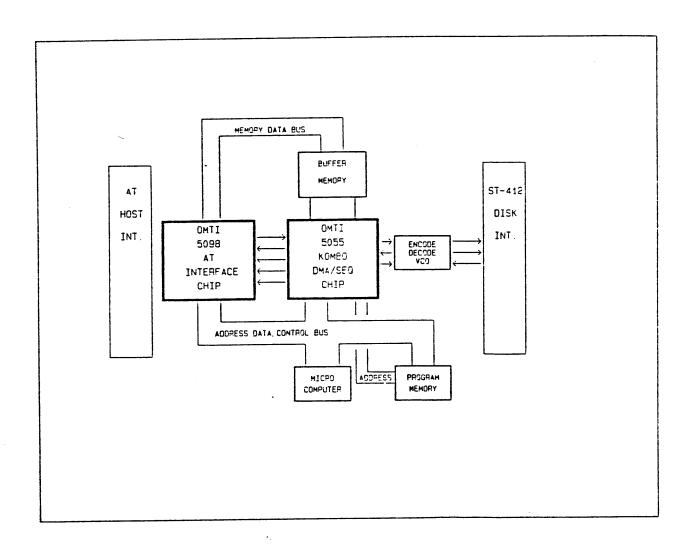

Figure 2 illustrates a complete controller block diagram using the OMTI 5098 "AT" Compatiable Interface Chip along with an OMTI 5055 Kombo controller chip and an OMTI 5070 or OMTI 5027 Encode / Decode / VCO chip.

Figure 2. Controller Block Diagram

### SECTION 2

#### INTERFACING

### 2.1 PIN DESCRIPTIONS

| Symbol    | Type       | Pin # | Name and Function                                                                                                                                                                                                                                 |

|-----------|------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AEN       | I          | 2     | ADDRESS ENABLE (HOST): This signal is asserted during a DMA cycle. It is used to disable the decoding of the HOST I/O ADDRESS BUS during DMA cycles.                                                                                              |

| ~IOWR     | I          | 3     | I/O WRITE (HOST): This input signal is asserted to write data from an I/O address (A9 - A0, AEN is de-asserted).                                                                                                                                  |

| ~IORD     | I          | 4     | I/O READ (HOST): This input signal is asserted to read data from an I/O address (A9 - A0, AEN is de-asserted).                                                                                                                                    |

| D_(7:0)   | 1/0        | 5-11  | DATA BUS (HOST): These bi-directional, tri-state signals are used to transfer data between the HOST and the 5098 internal/external registers. During WORD data transfers, these signals are the least significant byte of the data word.          |

| ALE       | I          | 14    | ADDRESS LATCH ENABLE (HOST): This input signal is asserted to indicate that the HOST I/O ADDRESS is valid on the falling edge.                                                                                                                    |

| ~DS_0     | 0          | . 15  | DRIVE SELECT ZERO: This open drain output is asserted when a '0' is written to BIT 4 of WRITE REGISTER 1F6(176). If the 5098 is in the NON-SELECT MODE, this output is only asserted during reads to REGISTER 1F7(177) or the controller is BUSY. |

| IO_CH_RDY | • <b>o</b> | 16    | I/O CHANNEL READY (HOST): This open drain, 24 MA. output signal is deasserted to lengthen an I/O data cycle. This signal is only active during WORD MODE data transfers at I/O ADDRESS 1FO(170).                                                  |

| Symbol    | Type  | Pin # | Name and Function                                                                                                                                                                                                                                                              |

|-----------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -10_CS_16 | 0     | 18    | I/O CHIP SELECT 16 BIT (HOST): This open drain, 24 ma. output signal is asserted to indicate that the present HOST data transfer is a 16-bit, 1 wait-state I/O cycle. It is derived from the 5098 DATA REGISTER 1F0(170) decode.                                               |

| -DS_1     | 0     | 19    | DRIVE SELECT ZERO: This open drain output is asserted when a 'l' is written to BIT 4 of WRITE REGISTER 1F6(176). If the 5098 is in the NON-SELECT MODE, this output is only asserted during reads to REGISTER 1F7(177) or the controller is BUSY.                              |

| RESET_IN  |       | 20    | RESET IN (HOST): This input signal is asserted to indicate that a power-up or low voltage condition exist.                                                                                                                                                                     |

| -RESET_OU | T O   | 21    | RESET OUT: This output is an inverted copy of the RESET_IN signal or is asserted for a minimum of 1 microsecond indicating that the 5098 has an internal power-on reset.                                                                                                       |

| -RESET_SC | OFT O | 23    | SOFT RESET: This output signal is asserted as long as BIT 2 of WRITE REGISTER 3F6(376) is asserted.                                                                                                                                                                            |

| -READY    | I     | 24    | READY: This input signal is available on BIT 6 of READ REGISTER 1F7(177).                                                                                                                                                                                                      |

| -INDEX    | γ 'I  | . 25  | INDEX: This input signal is available on BIT 1 of READ REGISTER 1F7(177).                                                                                                                                                                                                      |

| DAL INTRO | Q I   | 26    | DMA INTERRUPT REQUEST: When enabled, this level sensitive input causes the 5098 to become BUSY. The polarity of this signal is programmable and should be connected to the DMA INTERRUPT signal of the DMA controller.                                                         |

| decode_a  |       | I 27  | ADDRESS DECODE A (HOST): This internally pulled-up signal specifies the 5098 HOST I/O address range. If no connection is made to this signal the 5098 HOST REGISTER A range is 1F0 - 1F7 (HEX). If this signal is grounded, the 5098 HOST REGISTER A range is 170 - 177 (HEX). |

| Symbol    | Type            | Pin #       | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|-----------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DECODE_B  | I               | 28          | ADDRESS DECODE B (HOST): This internally pulled-up signal specifies the 5098 HOST I/O address range. If no connection is made to this signal the 5098 HOST REGISTER B range is 3FO - 3F7 (HEX). If this signal is grounded, the 5098 HOST REGISTER B range is 370 - 377 (HEX).                                                                                                                                                                                               |

| CONFIG    | I               | 29          | PROCESSOR CONFIGURATION (CONTROLLER): This internally pulled-up signal specifies the controller processor strobe inputs. If no connection is made to this signal, the 5098 is configured for a Z8-type processor. In this case, ALE TAS = TAS, TIORD TDS = TDS, TIOWR RW = RW and IO MEM TDM = TDM. If this signal is grounded, the 5098 is configured for an 8051-type processor. In this case, ALE TAS = ALE, TIORD TDS = TIORD, TIOWR RW = TIOWR and IO MEM TDM = IO MEM. |

| DMA_ACK   |                 | 30          | DMA ACKNOWLEDGE: This input signal, initiated by the DMA controller, indicates that a DMA transfer is taking place.                                                                                                                                                                                                                                                                                                                                                          |

| DMA_REQ   | <b>W</b><br>ARQ | <b>©</b> 31 | DMA REQUEST: In conjuction with DMA_ACK, this output signal is asserted by the 5098 on the trailing edge of an IORD or IOWR to HOST ADDRESS 1F0(170) during data transfers.                                                                                                                                                                                                                                                                                                  |

| -INENA    | ·I              | 33          | INPUT ENABLE: This input signal is asserted by the DMA controller to enable the 5098 to drive the MEMORY Data bus.                                                                                                                                                                                                                                                                                                                                                           |

| -OUTCLK   | I               | 34          | OUT CLOCK: This input signal is asserted by the DMA controller to save data into the 5098 form the MEMORY Data bus.                                                                                                                                                                                                                                                                                                                                                          |

| MEM_D(7:0 | )) I/O          | 35-42       | MEMORY DATA: These bi-directional signals are used to transfer data between the HOST and the Controller DMA Buffer Memory.                                                                                                                                                                                                                                                                                                                                                   |

| Symbol          | Type | Pin # | Name and Function                                                                                                                                                                                                                                                                          |

|-----------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD_(7:0)        |      |       |                                                                                                                                                                                                                                                                                            |

| ALEAS           | I    | 52    | ADDRESS LATCH ENABLE/ADDRESS STROBE: This input signal is asserted to latch the controller microcomputers address into the 5098. In 8051 mode, this input is active high. In Z8 mode, this input is active low.                                                                            |

| -IOWR_RW<br>W √ | I    | · 53  | I/O WRITE (8051) READ/WRITE (28): This input signal is asserted in 8051 mode, to gate data from the controller to the 5098 (if selected). If the Z8-mode is selected, this input signal is low to indicate a write function and high to indicate a read function.                          |

| -IORDDS         | I    | 55    | I/O READ (8051) DATA STROBE (Z8): This input signal is asserted to gate data from the 5098 (if selected) to the ADDRESS/DATA BUS of controller processor (8051-mode). If the Z8-mode is selected, this input signal is used to gate data from (READ) or to (WRITE) the 5098 (if selected). |

| IOMEM           | DM I | 56    | I/O TMEMORY (8051) TDM (Z8): This input signal is used for as a chip select for the 5098. In 8051 mode, this input is active high. In Z8 mode, this input is active low.                                                                                                                   |

| -command        | O    | 57    | COMMAND: This output signal is asserted to indicate that a command has been written into WRITE REGISTER 1F7(177) It is de-asserted by writing the INTERNAL CONTROL REGISTER bit 2 with a 'l' or a RESET.                                                                                   |

| Symbol         | Type | Pin # | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -wrt_gate<br>₩ | I    | 58    | WRITE GATE: This input signal is available on BIT 6 of READ REGISTER 3F7(377).                                                                                                                                                                                                                                                                                                                                                          |

| -DCHG          | I    | 59    | DISK CHANGED: This internally pulled-up signal is available on BIT 7 of READ REGISTER 3F7(377). If this signal is not used, BIT 7 of READ REGISTER 3F7(377) can be TRI-STATED by writing a '1' to BIT 4 of the INTERNAL CONTROL REGISTER (F8).                                                                                                                                                                                          |

| RATE_1         | 0    | 60    | FLOPPY DATA RATE 1: This output signal along with RATE_0 determine the flexible disk data rate.                                                                                                                                                                                                                                                                                                                                         |

| RATE_0         | 0    | 61    | FLOPPY DATA RATE 0: This output signal along with RATE_1 determine the flexible disk data rate.                                                                                                                                                                                                                                                                                                                                         |

| FDC_           | 0    | 62    | FLOPPY DATA REGISTER: This output signal is asserted during an IOWR to HOST ADDRESS 3F2(372).                                                                                                                                                                                                                                                                                                                                           |

| -CS_FDC        | 0    | 63    | FLOPPY CONTROLLER SELECT: This output signal is asserted during an IOWR or IORD to HOST ADDRESS 3F4-3F5(374-375).                                                                                                                                                                                                                                                                                                                       |

| INTRQ          | Ο    | 65    | INTERRUPT REQUEST: This TRI-STATE output signal indicates that the 5098 needs attention. It is enabled or disabled by writing a '0' or '1' respectively to BIT 1 of WRITE REGISTER 3F6(376). It is asserted by writing a '1' to BIT 0 of the INTERNAL CONTROL REGISTER (F8) and is de-asserted by writing a '0' to BIT 0 of the INTERNAL CONTROL REGISTER (F8), reading SYSTEM REGISTER 1F7 (177) or writing SYSTEM REGISTER 1F7 (177). |

| D_(15:8)       | 1/0  | 66-73 | DATA BUS (HOST): These bi-directional, tri-state signals are used to transfer the most significant byte of HOST data to or from the 5098 DATA REGISTER.                                                                                                                                                                                                                                                                                 |

| A_(9:0)        | I    | 75-84 | I/O ADDRESS BUS (HOST): These input signals constitute the 10 BIT 5098 HOST I/O ADDRESS BUS and are internally decoded for the selection of internal and external 5098 registers.                                                                                                                                                                                                                                                       |

GROUND: Pins 1,17,43,74 VSS

POWER: Pins 22,64 VDD

```

E

M

M

2<muutantee</pre>2

x 32 NC_ (32)

~IORD_~DS $551

№3 La DMA_REQ

⊁₃₲ DMA_ACK

IO_~MEM_~DM $50*

☆z蚰 CONF I G

~COMMAND $57*

SMS

⊁≥畸 DECODE_

WRT_GATE $58 X

ス~2をDECODE A

~DCHG $59×

RATE_1 $60×.

>≥6 DMA INTRQ

OMTI 20516

RATE_0 $ 51 %

*z蜎~ⅠNDEX

~FDD_REG $62 X

×z岫~READY

~CS_FDC 653X

╲≥┪~RESET_SOFT

<Date Code>

sap VDD

VDD

*21 ~ RESET_OUT

INTRO 65-X

-×26 RESET_IN

D(15) $66*

×19√0S_1

(14) $67×

*18 ~ IO_CS_16

13 VSS_3

12)

₽ 69 ×

서화 I O_CH_RDY

[] [] b 70 x

*15√0\\

0

D.(10) $71 ×

~1貼 日LE

D(9) $72 >

№13₽D_(7)

D(8) $73×

<u>* 1회</u> NC_ (12)

76 77 78 79 80 81 82 83 84

11118

\mathcal{M}

J- 00

```

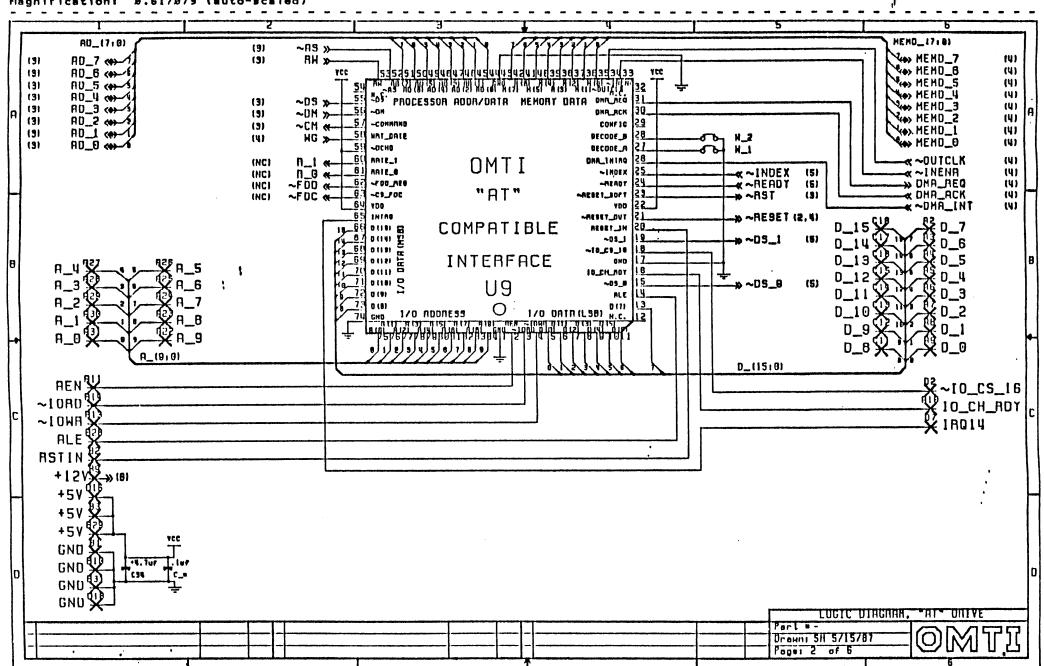

Figure 3. Pin Assignment

#### SECTION 3

#### INTERFACE REGISTERS

### 3.1 HOST INTERFACE REGISTERS

The OMTI 5098 contains 10 registers by which the HOST can communicate with the controller. Decoding for an optional FLOPPY SELECT / CONTROL REGISTER and a FDC 765 FLOPPY DISK CONTROLLER is also available.

### 3.2 HOST REGISTER ASSIGNMENT

The following is a list of primary and (secondary) address along with there read or write function.

| I/O AD                                               |                                                                      |                                                                                                     |                                                                                                              |

|------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| PRIMARY                                              | SECONDARY                                                            | READ REGISTER                                                                                       | WRITE REGISTER                                                                                               |

| 1F0<br>1F1<br>1F2<br>1F3<br>1F4<br>1F5<br>1F6<br>1F7 | (170)<br>(171)<br>(172)<br>(173)<br>(174)<br>(175)<br>(176)<br>(177) | DATA (16 BIT) ERROR SECTOR COUNT SECTOR NUMBER CYLINDER (LSB) CYLINDER (MSB) SIZE/DRIVE/HEAD STATUS | DATA (16 BIT) WRITE PRECOMP SECTOR COUNT SECTOR NUMBER CYLINDER (LSB) CYLINDER (MSB) SIZE/DRIVE/HEAD COMMAND |

| 3F2<br>3F4<br>3F5<br>3F6<br>3F7                      | (372)<br>(374)<br>(375)<br>(376)<br>(377)                            | FDC MAIN STATUS FDC DATA SECONDARY STATUS HEAD/SELECT STATUS                                        | FLOPPY SELECT/CONTROL  FDC DATA  CONTROL  FLOPPY RATE SELECT                                                 |

TABLE 1 HOST REGISTER ASSIGNMENT

#### 3.3 HOST READ REGISTER DESCRIPTION

### 3.3.1 DATA REGISTER 1F0 (170)

This register contains the data in 16 bit mode for all data transferred from the controller to the host.

#### 3.3.2 ERROR REGISTER 1F1 (171)

This register contains the ERROR STATUS of the last command executed by the controller. It can only be accessed while the controller is in the NOT BUSY state. This register is not affected by RESET. The bit definitions are:

BIT 7 - BAD BLOCK FOUND.

This indicates that the specified track has previously been formatted with the BAD TRACK flag set in the ID field. It is not possible to access data on this track and the command will be terminated.

BIT 6 - ECC ERROR.

This indicates that a NON-ZERO syndrome was detected in a specified data field. If the data error was corrected by ECC, BIT 2 of the STATUS REGISTER will also be SET and the command will continue if more sectors are specified. If the data error was NOT corrected by ECC, BIT 0 of the STATUS REGISTER will be SET and the command terminated.

BIT 5 - NOT USED.

Set to zero.

BIT 4 - ID NOT FOUND.

This indicates that the controller was able to locate the correct cylinder and head numbers but was unable to locate the correct sector number. An ID CRC error can also generate this error condition.

BIT 3 - NOT USED.

Set to zero.

BIT 2 - ABORTED COMMAND.

The current command issued by the HOST has been aborted due to an undefined COMMAND OPCODE, or a WRITE FAULT/NOT READY condition exist on the selected drive.

BIT 1 - NO CYLINDER ZERO.

This indicates that during a RECALIBRATION command or if retries are enabled no CYLINDER 000 was detected. This error occurs after the controller issues 2048 step pulses towards cylinder 000 and the selected drive does not respond with the TRACK 000 signal.

BIT 0 - NO DATA MARK FOUND.

This indicates that the controller was able to locate the sector but was unable to locate the data mark associated with it.

# 3.3.3 SECTOR COUNT REGISTER 1F2 (172)

This register contains the number of sectors to be processed and is decremented as each sector is processed. It can only be accessed while the controller is in the NOT BUSY state. This register is set to 1 after a RESET.

## 3.3.4 SECTOR NUMBER REGISTER 1F3 (173)

This register contains the current sector number being processed by the controller. It can only be accessed while the controller is in the NOT BUSY state. If an error condition exist, this register contains the sector number in error. It is set to 1 after a RESET.

## 3.3.5 CYLINDER (LSB) REGISTER 1F4 (174)

This register contains the least significant byte of the current cylinder number. It can only be accessed while the controller is in the NOT BUSY state. If an error condition exist, this register contains the least significant byte of the cylinder number in error. This register is set to 0 after a RESET.

## 3.3.6 CYLINDER (MSB) REGISTER 1F5 (175)

This register contains the most significant byte of the current cylinder number. It can only be accessed while the controller is in the NOT BUSY state. If an error condition exist, this register contains the most significant byte of the cylinder number in error. This register is set to 0 after a RESET.

# 3.3.7 SIZE/DRIVE/HEAD REGISTER 1F6 (176)

This register contains the controller ERROR CODE/SECTOR SIZE parameters along with the current DRIVE/HEAD select. It can only be accessed while the controller is in the NOT BUSY state. register is set to 0 after a RESET. The bit definitions are:

BIT 7 - ERROR CODE.

This bit indicates the error code selected. If this bit is set to ONE, the data field will be appended with an ECC field. If set to ZERO, the data field will be appended with a CRC field.

## 3.3.3 SECTOR COUNT REGISTER 1F2 (172)

This register contains the number of sectors to be processed and is decremented as each sector is processed. It can only be accessed while the controller is in the NOT BUSY state. This register is set to 1 after a RESET.

## 3.3.4 SECTOR NUMBER REGISTER 1F3 (173)

This register contains the current sector number being processed by the controller. It can only be accessed while the controller is in the NOT BUSY state. If an error condition exist, this register contains the sector number in error. It is set to 1 after a RESET.

## 3.3.5 CYLINDER (LSB) REGISTER 1F4 (174)

This register contains the least significant byte of the current cylinder number. It can only be accessed while the controller is in the NOT BUSY state. If an error condition exist, this register contains the least significant byte of the cylinder number in error. This register is set to 0 after a RESET.

# 3.3.6 CYLINDER (MSB) REGISTER 1F5 (175)

This register contains the most significant byte of the current cylinder number. It can only be accessed while the controller is in the NOT BUSY state. If an error condition exist, this register contains the most significant byte of the cylinder number in error. This register is set to 0 after a RESET.

# 3.3.7 SIZE/DRIVE/HEAD REGISTER 1F6 (176)

This register contains the controller ERROR CODE/SECTOR SIZE parameters along with the current DRIVE/HEAD select. It can only be accessed while the controller is in the NOT BUSY state. This register is set to 0 after a RESET. The bit definitions are:

BIT 7 - ERROR CODE.

This bit indicates the error code selected. If this bit is set to ONE, the data field will be appended with an ECC field. If set to ZERO, the data field will be appended with a CRC field.

BITS 6, 5 - SECTOR SIZE.

These bits indicate the sector size selected. The sector size definitions are:

BIT 6 5

0 0 - 256 BYTE SECTOR

0 1 - 512 BYTE SECTOR

1 0 - 1024 BYTE SECTOR

1 1 - 128 BYTE SECTOR

BIT 4 - DRIVE SELECT.

This bit reflects the selected drive. If this bit is set to ZERO, drive 0 is selected. If set to ONE, drive 1 is selected.

BITS 3-0 - HEAD SELECT.

These bits indicate the selected head.

# 3.3.8 STATUS REGISTER 1F7 (177)

This register contains the CONTROLLER/DRIVE STATUS. Reading this register de-asserts the INTRQ signal. The bit definitions are:

BIT 7 - BUSY.

This bit indicates the state of the controller. If SET, the controller is busy executing the specified command and is NOT in a DATA TRANSFER state. While set, the STATUS REGISTER is gated on the BUS during any READ to the HOST READ/WRITE REGISTERS. Any WRITE to the HOST READ/WRITE REGISTERS while this bit is set will be ignored. If CLEARED, the controller is either in a NOT BUSY or a DATA TRANSFER state. The DRQ bit will be SET if the controller is in the DATA TRANSFER state.

BIT 6 - READY.

This bit is an inverted copy of the -READY signal of the selected drive.

BIT 5 - WRITE FAULT.

This bit is an inverted copy of the -WRITE FAULT signal of the selected drive.

BIT 4 - SEEK COMPLETE.

This bit is an inverted copy of the -SEEK COMPLETE signal of the selected drive.

BIT 3 - DATA REQUEST.

This bit indicates that controller is in a DATA TRANSFER mode. While this bit is SET, the BUSY bit will be CLEARED and the controller will wait for data to be transferred to or from the HOST.

BIT 2 - CORRECTED.

This bit indicates if a DATA ERROR was corrected. If SET, an ECC error occurred but was corrected. A corrected ECC error will NOT terminate a multiple sector transfer. If CRC is selected, this bit has no meaning and is set to ZERO.

BIT 1 - INDEX.

This bit is an inverted copy of the -INDEX signal of the selected drive.

BIT 0 - ERROR.

This bit indicates if an UNRECOVERABLE ERROR has occurred. If SET, an error condition exist and the STATUS REGISTER must be read to determine the error type.

### 3.3.9 FDC 765 MAIN STATUS REGISTER (OPTIONAL)

Reading this register selects the FDC 765 MAIN STATUS register (if available). For more information, consult the FDC 765 data sheet.

### 3.3.10 FDC 765 DATA REGISTER (OPTIONAL)

Reading this register selects the FDC 765 DATA register (if available). For more information, consult the FDC 765 data ٠. sheet.

### 3.3.11 SECONDARY STATUS REGISTER 3F6 (376)

This register contains the CONTROLLER/DRIVE STATUS. It is identical to the STATUS REGISTER at address 1F7(177). See section 4.0.2.7 for bit definitions.

## 3.3.12 HEAD/SELECT STATUS REGISTER 3F7 (377)

This register contains the HEAD/DRIVE SELECT STATUS. The bit definitions are:

| BIT 7 - DISKETTE CHANGE. | This bit indicates the state of the floppy -DCHG signal. If SET, no |

|--------------------------|---------------------------------------------------------------------|

|                          | diskette, door open or drive NOT READY condition exist.             |

BIT 6 - WRITE GATE. This bit indicates the state of the winchester -WRITE GATE signal.

BIT 5 - HEAD SELECT 3/RWC. This bit indicates the state of HEAD SELECT 3/RWC.

BIT 4 - HEAD SELECT 2. This bit indicates the state of HEAD SELECT 2.

BIT 3 - HEAD SELECT 1. This bit indicates the state of HEAD SELECT 1.

BIT 2 - HEAD SELECT 0. This bit indicates the state of HEAD SELECT 0.

BIT 1 - DRIVE SELECT 1. This bit indicates the state of DRIVE SELECT 1. If set to ZERO, DRIVE 1 is selected. If set to ONE, DRIVE 1 is de-selected.

BIT 0 - DRIVE SELECT 0. This bit indicates the state of DRIVE SELECT 0. If set to ZERO, DRIVE 0 is selected. If set to ONE, DRIVE 0 is de-selected.

## 3.4 HOST WRITE REGISTER DESCRIPTION

# 3.4.1 WRITE PRECOMP/RWC REGISTER 1F1 (171)

This register determines the cylinder at which WRITE PRECOMPENSATION will be applied. The value written is 1/4 the actual precompensation cylinder. A value of 255 will result in no write precompensation/reduce write current. This register should be written prior to the COMMAND REGISTER being written with a WRITE/FORMAT command. It is set to 32 (128) after a RESET.

## 3.4.2 SECTOR COUNT REGISTER 1F2 (172)

This register specifies the number of sectors to be processed. A value of 0 indicates 256 sectors. It should be written prior to the COMMAND REGISTER being written. This register is set to 1 after a RESET.

#### 3.4.3 SECTOR NUMBER REGISTER 1F3 (173)

This register specifies the starting sector number. It should be written prior to the COMMAND REGISTER being written. This register is set to 1 after a RESET.

### 3.4.4 CYLINDER (LSB) REGISTER 1F4 (174)

This register specifies the least significant byte of the starting cylinder number. It should be written prior to the COMMAND REGISTER being written. This register is set to 0 after a RESET.

### 3.4.5 CYLINDER (MSB) REGISTER 1F5 (175)

This register specifies the most significant byte of the starting cylinder number. It should be written prior to the COMMAND REGISTER being written. This register is set to 0 after a RESET.

### 3.4.6 SDH REGISTER 1F6 (176)

This register specifies the controller ERROR CODE/SECTOR SIZE parameters along with the DRIVE/HEAD select. This register should be written prior to the COMMAND REGISTER being written. This register is set to 0 after a RESET. The bit definitions are:

BIT 7 - ERROR CODE.

This bit specifies the error code to be selected. If this bit is SET the data field will be appended with an ECC field. If CLEARED, the data field will be appended with a CRC field.

BITS 6, 5 - SECTOR SIZE. These bits specify the sector size to be selected. The sector size definitions are:

BIT 6 5

0 0 - 256 BYTE SECTOR

0 1 - 512 BYTE SECTOR

1 0 - 1024 BYTE SECTOR

1 1 - 128 BYTE SECTOR

BIT 4 - DRIVE SELECT.

This bit selects the drive. this bit is set to ZERO, drive 0 is selected. If set to ONE, drive 1 is selected.

BITS 3-0 - HEAD SELECT. These bits select the head.

٠.

# 3.4.7 COMMAND REGISTER 1F7 (177)

This register specifies the command to be executed by the controller. It is set to 0 after a RESET. Writing to this register asserts the -COMMAND signal.

# 3.4.8 FLOPPY SELECT/CONTROL REGISTER (OPTIONAL)

Writing this register selects the floppy select/control register (if available). This register is external to the OMTI 5098 and is selected by the -FDD\_REG signal.

# 3.4.9 FDC 765 DATA REGISTER (OPTIONAL)

Writing this register selects the FDC 765 DATA register (if available). For more information, consult the FDC 765 data sheet.

# 3.5 CONTROLLER READ/WRITE REGISTERS

The OMTI 5098 contains 8 registers by which the microcomputer can communicate with the host.

# 3.6 MICROCOMPUTER REGISTER ASSIGNMENT

The following is a list of address along with there read or write function.

| ADDRESS                                                                      | READ                                                                                           | WRITE                                                                                                                            |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 20F0<br>20F1<br>20F2<br>20F3<br>20F4<br>20F5<br>20F6<br>20F7<br>20F8<br>20F9 | WRITE PRECOMP SECTOR COUNT SECTOR NUMBER CYLINDER (LSB) CYLINDER (MSB) SIZE/DRIVE/HEAD COMMAND | HEAD SELECT ERROR SECTOR COUNT SECTOR NUMBER CYLINDER (LSB) CYLINDER (MSB) SIZE/DRIVE/HEAD STATUS EXTERNAL CONTROL DRIVE CONTROL |

TABLE 2 MICROCOMPUTER REGISTER ASSIGNMENT

# 3.7 MICROCOMPUTER READ REGISTER DESCRIPTION

# 3.7.1 WRITE PRECOMP REGISTER 20F1

This register contains the cylinder at which WRITE PRECOMPENSATION will be applied. The value read must be multiplied by 4. A value of 255 will result in no write precompensation/reduce write current. It is read by the controller processor only after a command has been written into the COMMAND REGISTER (HOST).

### 3.7.2 SECTOR COUNT REGISTER 20F2

This register contains the number of sectors to be processed. It is read by the controller processor only after a command has been written into the COMMAND REGISTER (HOST).

### 3.7.3 SECTOR NUMBER REGISTER 2073

This register contains the starting sector number to be processed. It is read by the controller processor only after a command has been written into the COMMAND REGISTER (HOST).

### 3.7.4 CYLINDER (LSB) REGISTER 20F4

This register contains the starting (least significant byte) cylinder number to be processed. It is read by the controller processor only after a command has been written into the COMMAND REGISTER (HOST).

## 3.7.5 CYLINDER (MSB) REGISTER 20F5

This register contains the starting (most significant byte) cylinder number to be processed. It is read by the controller processor only after a command has been written into the COMMAND REGISTER (HOST).

### 3.7.6 SIZE/DRIVE/HEAD REGISTER 20F6

This register contains the controller ERROR CODE/SECTOR SIZE parameters along with the current DRIVE/HEAD select. It is read by the controller processor only after a command has been written into the COMMAND REGISTER (HOST). The bit definitions are:

BIT 7 - ERROR CODE.

This bit specifies the error code to be used. If this bit is set to ONE, the data field will be appended with an ECC field If set to ZERO, the data field will be appended with a CRC field.

BITS 6, 5 - SECTOR SIZE.

These bits specify the sector size to be used. The sector size definitions are:

BIT 6 5

0 0 - 256 BYTE SECTOR

0 1 - 512 BYTE SECTOR

1 0 - 1024 BYTE SECTOR

1 1 - 128 BYTE SECTOR

BIT 4 - DRIVE SELECT.

This bit specifies the drive to be selected. If this bit is set to ZERO, drive 0 is selected. If set to ONE, drive 1 is selected.

These bits specify the head to be selected.

# 3.7.7 COMMAND REGISTER 20F7

BITS 3-0 - HEAD SELECT.

This register contains the command to be executed by the controller. It is read only after the -COMMAND signal has been asserted.

## 3.8 MICROCOMPUTER WRITE REGISTER DESCRIPTION

## 3.8.1 HEAD SELECT REGISTER 20F0

## 3.8.3 SECTOR COUNT REGISTER 20F2

This register is written with the number of sectors processed. It is read by the host only after a command has been executed by the controller.

# 3.8.4 SECTOR NUMBER REGISTER 20F3

This register is written with the sector number that has an error by the controller. It is read by the host only after a command has been executed by the controller.

## 3.8.5 CYLINDER (LSB) REGISTER 20F4

This register is written with the cylinder LSB number that has an error by the controller. It is read by the host only after a command has been executed by the controller.

# 3.8.6 CYLINDER (MSB) REGISTER 20F5

This register is written with the cylinder MSB number that has an error by the controller. It is read by the host only after a command has been executed by the controller.

# 3.8.7 SIZE/DRIVE/HEAD REGISTER 20F6

This register is written with the size/drive/head number that has an error by the controller. It is read by the host only after a command has been executed by the controller.

## 3.8.9 STATUS REGISTER 20F7

This register is written with the status by the controller. It is read by the host only after a command has been executed by the controller.

#### 3.8.10 EXTERNAL CONTROL REGISTER 20F8

This register is written by the controller and has bit significants for the control of the internal operations of the 5098. The bit definitions are:

This bit controlls if DMA INTRQ BIT 7 - DMA BUSY. will clear BUSY status. If this bit is set, the DMA INTRO will set the BUSY status.

This bit controlls if the TDS 0 and BIT 6 - SELECT. TDS 1 output will be enable $\overline{d}$ . If this bit is set, the outputs will be disabled.

This bit controlls if the disk BIT 5 - DIS\_LATCH. latches should be disabled. If this bit is set, the clocks will be disabled.

BIT 4 - DIS\_DCHG. This bit controlls if the disk changed status bit should drive the bus. If this bit is set, the 5098 will not drive the high order bit of the status bus.

This bit controlls if the 16 bit BIT 3 - DIS WORD. data transfer is enabled. If this bit is set, all data transfers will be in 8 bit mode.

0 = Not used.BITS 2 - 0

#### 3.8.11 DRIVE CONTROL REGISTER 20F9

This register is written by the controller and has bit significants for the control of the internal operations of the 5098. The bit definitions are:

BIT 7 - POLARITY. This bit specifies the polarity of the DMA\_INTRQ input. If this bit is SET the input is inverted.

This bit controlls the hardware BITS 6 - DIS\_BUSY. enable of the BUSY status. If this bit is set, BUSY status is disabled.

This bit controlls the READY overide for drive color. BIT 5 - NOT\_RDY\_1. bit is set, the TREADY input is ignored.

BIT 4 - "WF\_1.

This bit controlls the WRITE FAULT status for drive select 1. If this bit is set, the WRT\_FALUT status will not be set.

BIT 3 - -SC\_1.

This bit controlls the SEEK\_COMPLETE status for drive select 1. If this bit is set, the SEEK COMPLETE status will not be set.

BIT 2 - NOT\_RDY\_0.

This bit controlls the READY overide for drive select 0. If this bit is set, the TREADY input is ignored.

BIT  $1 - WF_0$ .

This bit controlls the WRITE\_FAULT status for drive select 0. If this bit is set, the WRT\_FALUT status will not be set.

BIT  $0 - SC_0$ .

This bit controlls the SEEK\_COMPLETE status for drive select 0. If this bit is set, the SEEK\_COMPLETE status will not be

#### SECTION 4

#### D. C. CHARACTERISTICS

#### 4.1 Absolute Maximum Ratings:

- \* Voltages on all pins with respect to GND range from -0.3 V to +7.0 V.

- \* Ambient operating temperature is 0 degrees C. to +70 degrees C.

- \* Storage temperature ranges from -65 degrees C. to +150 degrees C.

Note that stresses greater than those indicated may cause permanent damage. Operation of the chip at conditions above those shown is not implied. Exposure to absolute maximum rating conditions for extended periods may affect the chip's reliability.

#### 4.2 Standard Test Conditions:

The characteristics shown below apply for the following test conditions, unless otherwise noted. Voltages are referenced to Positive current flows into the reference pin. Standard conditions are as follows:

- \* +4.75 V < VCC < +5.25 V

- $\star$  GND = 0 V

- \* 0 degrees C. < TA < +70 degrees C.

#### 4.3 D.C. Characteristics:

| Parameter                                                                                                                                                                                        | Min                                                      | Max                      | Unit                                | Condition | Notes                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------|-------------------------------------|-----------|-----------------------------------------------|

| Input High Voltage Input Low Voltage Output High Voltage Output Low Voltage Output Low Current Output High Current Output Low Current Output High Current Output High Current Output Low Current | 2<br>-0.3<br>2.4<br>4.0<br>-4.0<br>12.0<br>-12.0<br>24.0 | VCC<br>0.8<br>VCC<br>0.4 | V<br>V<br>V<br>MA<br>MA<br>MA<br>MA |           | D_(15:0) D_(15:0) -DS_0&1 IO_CH_RDY -IO_CS_16 |

| Input Leakage<br>Output Leakage<br>VCC Supply Current                                                                                                                                            | -30                                                      | 10<br>10<br>50           | uA<br>uA<br>mA                      |           |                                               |

Enqueued: 5/19/1987 7:44 am (pst)

Printed: 5/19/1987 7:45 am (pst)

Magnification: 8.617879 (auto-scaled)

Enqueued: 5/19/1987 7:44 am (pst)

Printed: 5/19/1987 7:47 am (pst)

Magnification: 8.617879 (auto-scaled)

Enqueued: Printed: Magnification 5/19/1987 7:44 am (pst) 5/19/1987 7:49 am (pst)

Jobi

V88.Z8\$8.JEFFC.\$AT\_DRIVE.SHEET5

Enqueued: Printed: Magnification:

5/19/1987 7:44 am (pst) 5/19/1987 7:51 am (pst) 8.617879 (auto-scaled)

Enqueued: 5/19/1987 7:44 am (pst)

Printed: 5/19/1987 7:52 am (pst)

Magnification: 8.617879 (auto-scaled)

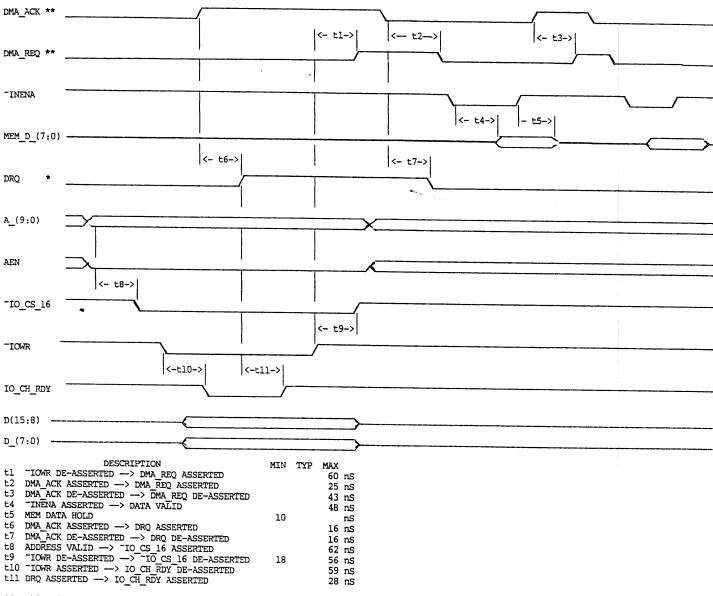

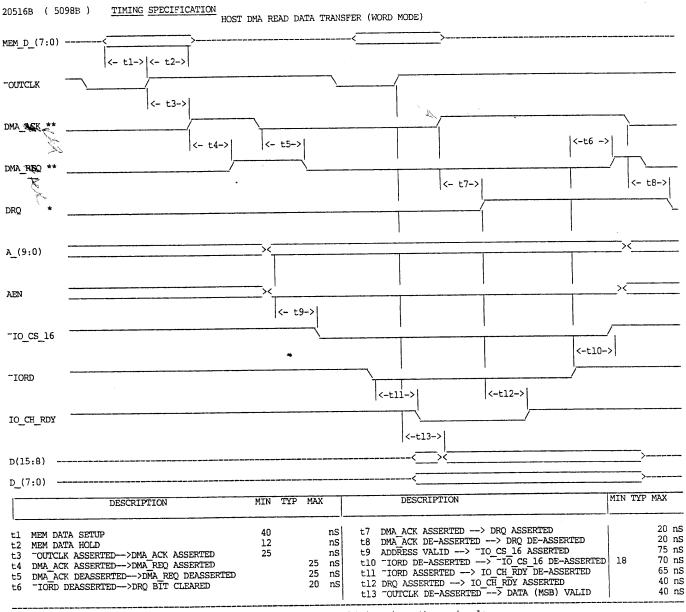

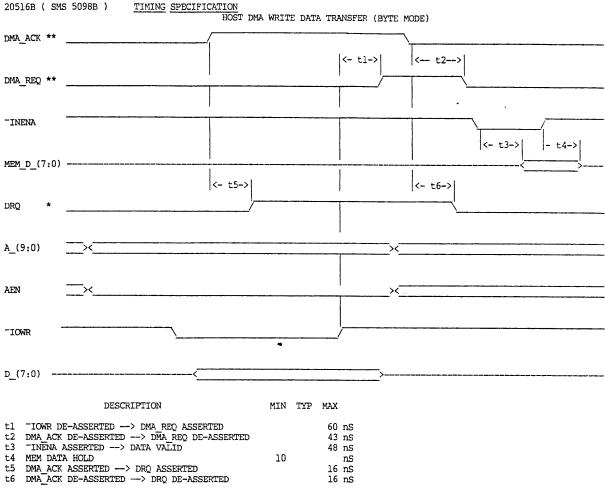

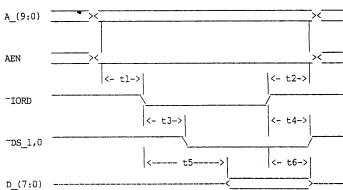

#### HOST DMA WRITE DATA TRANSFER (WORD MODE)

<sup>\*\*</sup> This timing diagram illustrates the SMS SCSI Mode of DMA Handshake, where these signals perform opposite of their nomenclature.[ie: DMA\_ACK signal acts as the HOST REQUEST function,& the DMA\_REQ signal acts as the HOST ACKNOWLEDGE function.]

See the SMS 5055 B ( KOMBO ) Technical Reference Manual for information on SCSI Mode of DMA.

<sup>\*</sup> This signal is the DRQ STATUS BIT = BIT 3 of PROBERT REGISTER 1F7 ( 177 ).

<sup>\*\*</sup> This timing diagram illustrates the SMS SCSI Mode of DMA Handshake, where these signals perform opposite of their nomenclature.[ie: DMA\_ACK signal acts as the HOST REQUEST function,& the DMA\_REQ\_signal acts as the HOST ACKNOWLEDGE function.] See the SMS 5055 B ( KOMBO ) Technical Reference Manual for information on SCSI Mode of DMA.

<sup>\*</sup> This signal is the DRQ STATUS BIT = BIT 3 of READ REGISTER 1F7 ( 177 ).

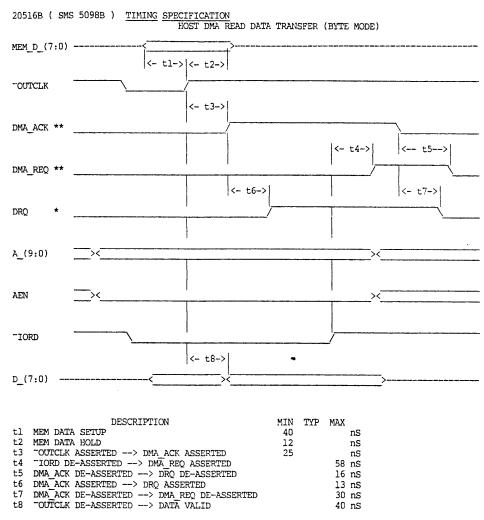

<sup>\*\*</sup> This timing diagram illustrates the SMS SCSI Mode of DMA Handshake, where these signals perform opposite of their nomenclature.[ie: DMA\_ACK signal acts as the HOST REQUEST function, & the DMA\_REQ\_signal acts as the HOST ACKNOWLEDGE function.] See the SMS 5055 B ( KOMBO ) Technical Reference Manual for information on SCSI Mode of DMA.

<sup>\*</sup> This signal is the DRQ STATUS BIT = BIT 3 of READ REGISTER 1F7 ( 177 ).