## 5000 PFM

**Data Controller Chip Set**

5050 PFM

**Data Sequencer**

5060 PFM

Four-Channel Memory

Controller

## **5070 PFM MFM**

VCO/Encode/Decode Chip

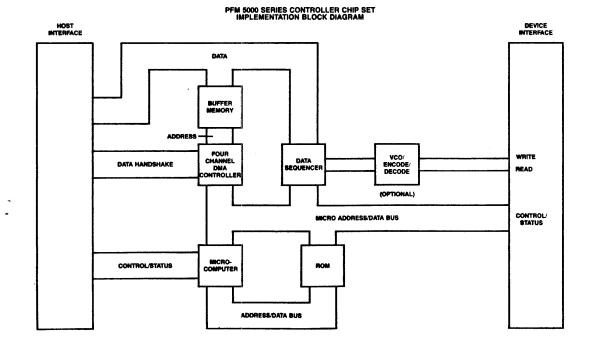

OMTI's advanced VLSI controller chip set is a third generation CMOS design that provides the design engineer with all of the necessary components for a high-performance and cost-effective controller design.

This advanced chip set makes possible such disk controller features as consecutive sector transfers, ECC error detection and correction, 2.0 megabyte host data transfer rates, and intelligent buffer management capable of being implemented in a minimum part count controller design.

The PFM 5050 Data Sequencer is designed to be used with a commercially available, low-cost micro-

processor or microcomputer to manage the flow of block-level information between serial device interfaces and a memory controller.

The OMTI PFM 5060 Four-Channel Memory Controller is intended to be used to manage the flow of block-level information between buffer memory and host and/or byte-oriented peripheral interfaces.

The PFM 5070 VCO/Encode/Decode chip is designed to be used with disk drives requiring MFM encoded data. This device is a fifth generation data separator design that requires only passive components to implement.

#### 5050 PFM Data Sequencer

The OMTI PFM 5050 Data Sequencer chip is a fully programmable 15 megabit CMOS/VLSI device designed to be used with the PFM 5060 Four-Channel Memory Controller, a byte-oriented Microprocessor, RAM buffer and appropriate drivers and receivers in high-performance, low-cost data controller designs.

The PFM 5050 data sequencer is designed to provide the high-speed, bit-serial data management, format control, error detection and serialization/ deserialization functions normally associated with data controllers. The PFM 5050 data sequencer is designed to be used directly with NRZ interfaces such as SMD, LMD, ESDI, etc. or with the PFM 5070 VCO/Encode/Decode chip when used with MFM interfaces such as SA1000, Q2000, ST506, ST412, etc.

Controller design flexibility is provided by making the normally non-programmable format parameters such as gap lengths, gap characters, Header fields, ECC error detection/correction polynomials and data field lengths to be length and value programmable. These parameters may be loaded once, and are used as constants during the execution of the high level command set.

The command set consists of a simple and versatile set of high level commands such as read data, write data, etc. These commands use 32 individually addressable 8-bit registers for storage of the data transfer parameters necessary for command execution. During multiple block operations, registers that control incrementing parameters, such as block number, are automatically incremented.

The microprocessor is relieved of the responsibility of processing real time events such as "timeouts" by providing a register that is decremented from a programmed value by time related events, such as index pulses. This register defaults to the original value upon error-free block processing.

#### Features:

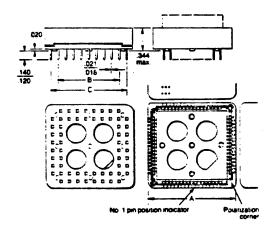

68 PIN LEADLESS PLASTIC PACKAGE 15 MEGAHERTZ BIT RATE NRZ SERIAL DISK INTERFACE EIGHT BIT PARALLEL OUTPUT REAL TIME PROCESSOR INTERVENTION NOT REQUIRED HIGH LEVEL INSTRUCTION SET 64 BIT PROGRAMMABLE (ECC) POLYNOMIAL CRC OR ECC HEADER ERROR DETECTION **POLYNOMIALS** PROGRAMMABLE HEADER SIZES TO 256 BYTES/HEADER USER DEFINABLE HEADER FLAG BYTES PROGRAMMABLE CAP SIZES AND FILL **CHARACTERS** PROGRAMMABLE SECTOR SIZES TO 65536 BYTES/SECTOR PROGRAMMABLE TRACK SIZES TO 256 SECTORS/TRACK MULTIPLE SECTOR READ/WRITE CAPABILITY

**ESDI SECTOR AND ADDRESS MARK OPERATION**

#### Commands:

READ DATA-Read data block(s) to buffer. READ VERIFY-Read data block(s) and compare

READ WITHOUT DATA TRANSFER—Read data block(s) and check for errors.

READ ECC SYNDROME—Read data block plus ECC syndrome to buffer.

READ ID—Read header(s) to buffer.

READ LONG-Read data block plus ECC to buffer. WRITE DATA—Write data block(s) from buffer.

WRITE FORMAT-Write header and data block(s) from buffer.

WRITE LONG—Write data block(s) plus ECC from buffer.

#### **Data Transfer Parameter Register:**

CYLINDER HIGH HEAD ADDRESS NUMBER OF BLOCKS TO TRANSFER **ECC CONTROL**

CYLINDER LOW **BLOCK NUMBER** TIMEOUT COUNT CONFIGURATION CONTROL

Format Parameter Registers:

PRE INDEX GAP HEADER PREAMBLE HEADER ID MARK HEADER ECC/CRC **POLYNOMIAL** DATA PREAMBLE DATA ID MARK DATA ECC POLYNOMIAL

INTERBLOCK GAP

POST INDEX GAP HEADER SYNC FIELD HEADER FIELD LENGTH **HEADER POSTAMBLE**

DATA SYNC FIELD DATA FIELD LENGTH DATA POSTAMBLE DATA POSTAMBLE

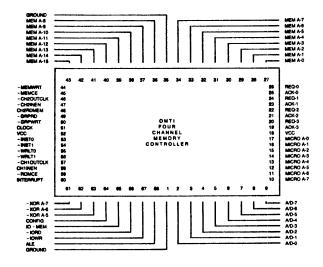

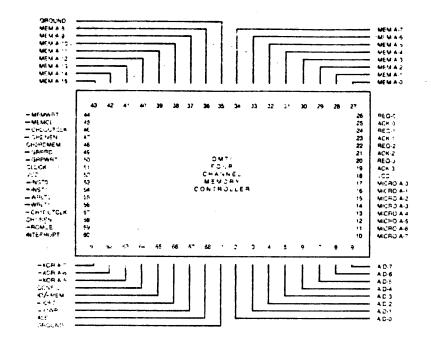

#### **5060 PFM Four-Channel Memory Controller**

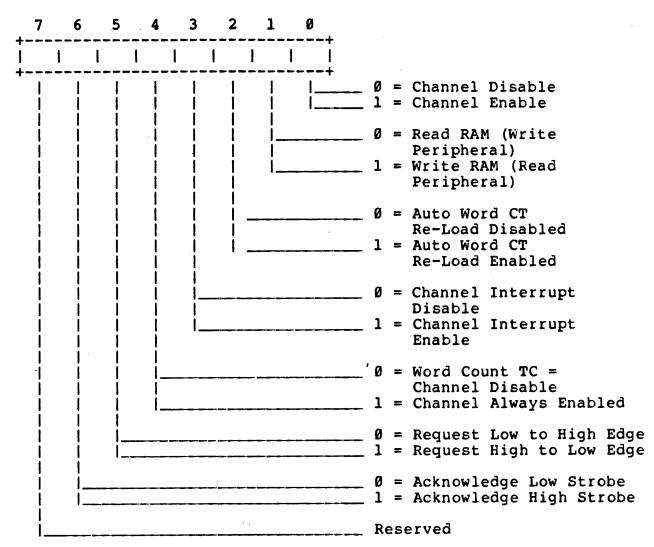

The OMTI PFM 5060 Four-Channel Memory Controller chip is a programmable 5 megabyte CMOS/VLSI device intended for use with the PFM 5050 Data Sequencer in high throughput, multi-function, multi-tasking, block-oriented data controller designs.

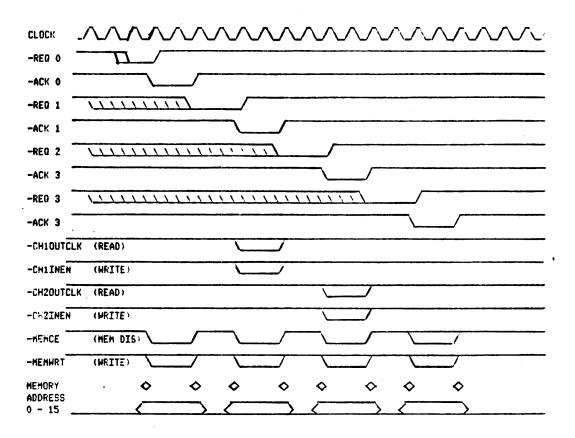

The PFM 5060 memory controller is designed to provide buffer management and data transfer control functions required in high-performance data controllers. The PFM 5060 memory controller contains four independent DMA channels with contention resolution based on preassigned channel priority. Design freedom in the amount and speed of the buffer memory is provided with sixteen bit direct memory addressing (65K) and programmable memory cycle times.

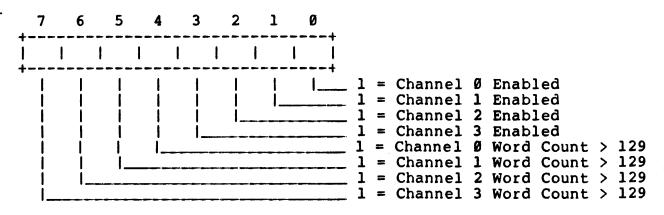

All of the DMA channels are general purpose channels designed for a direct connection to the PFM 5050 data sequencer or the microprocessor bus. All channels can be independently enabled or disabled and memory addresses can be independently set and automatically incremented. 16-bit byte counts can be independently set and are automatically decremented as well as being optionally reinitialized at channel end. Channel end interrupts can be independently enabled or disabled.

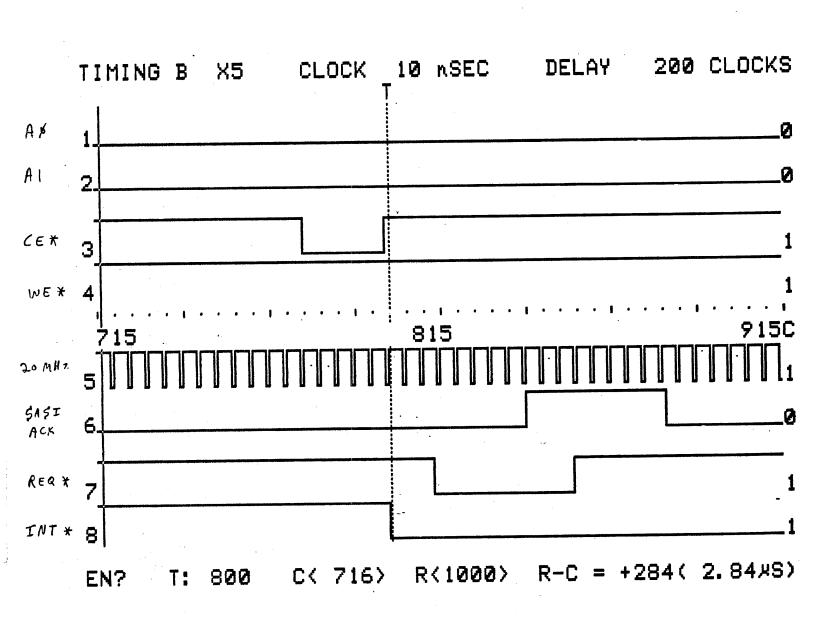

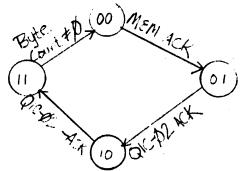

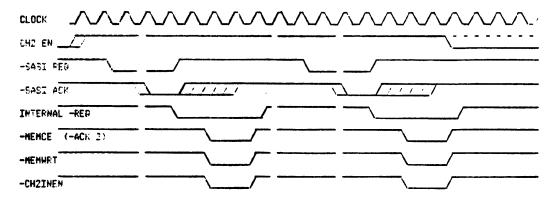

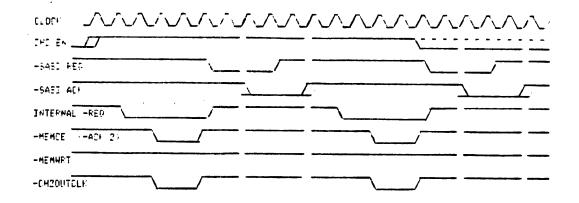

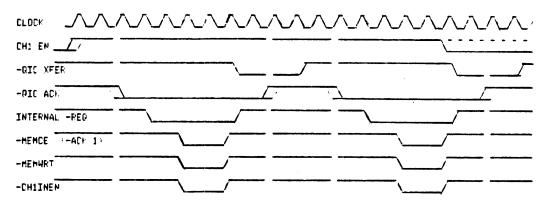

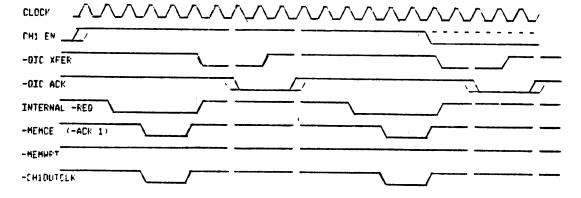

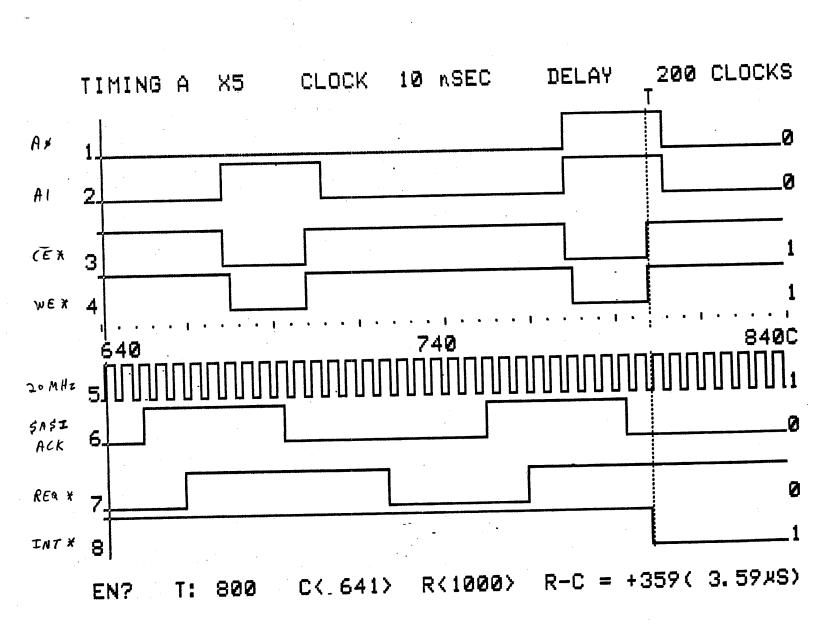

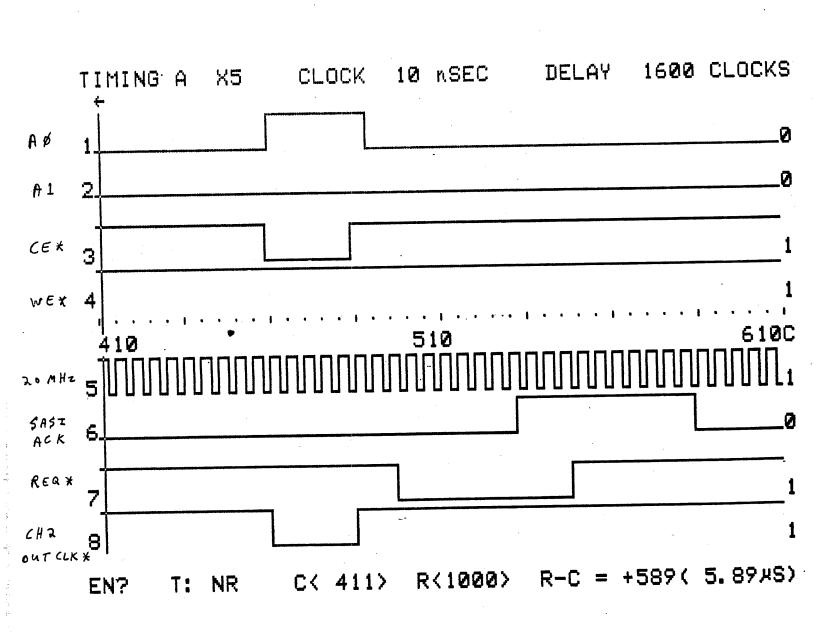

The data transfer protocol used is a standard DMA memory Request/Acknowledge protocol with independent polarity control over the Request/ Acknowledge signals. Two of the DMA channels are, however, programmable as specific purpose channels. One channel can be programmed to use the SCSI Request/Acknowledge data transfer handshake protocol. The second programmable channel can be programmed as a byte oriented peripheral channel using QIC-02 Transfer/Acknowledge data transfer protocol. The ability to program the polarity of the SCSI and QIC 02 handshake signals also allows the ability to adapt these channels to any byte oriented host or peripheral interface.

The PFM 5060 memory controller also provides the ability to address up to eight external registers.

These registers can be used to augment the internal microprocessor registers without increasing valuable real estate or parts cost.

#### Features:

68 PIN LEADLESS PLASTIC PACKAGE FOUR ASYNCHRONOUS DMA CHANNELS INDEPENDENT CONTROL OF EACH CHANNEL 5 MEGABYTE DEVICE BANDWIDTH CONTENTION RESOLUTION ON CHANNEL PRIORITY BASIS

16 BIT MEMORY ADDRESSING AUTOMATIC ADDRESS INCREMENT AUTOMATIC BYTE COUNT DECREMENT AUTOMATIC REINITIALIZATION OF BYTE COUNT REQUEST/ACKNOWLEDGE DMA HANDSHAKE PROTOCOL

INDEPENDENT POLARITY CONTROL OF REQUEST/ACKNOWLEDGE SIGNALS PROGRAMMABLE MEMORY CYCLE TIME INDEPENDENT CONTROL OF CHANNEL END INTERRUPT

CONFIGURABLE 'SASI' REQUEST/ACKNOWLEDGE HANDSHAKE PROTOCOL

CONFIGURABLE 'QIC 02' TRANSFER/ ACKNOWLEDGE HANDSHAKE PROTOCOL CONTROL OF UP TO 8 EXTERNAL REGISTERS

#### **Device Commands:**

| Device Commands:                                                                                                     | DECICTED                                                                  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| COMMAND                                                                                                              | REGISTER<br>SIZE                                                          |

| READ CHANNEL STATUS REGISTER<br>LOAD MEMORY CYCLE TIME/<br>INTERRUPT POLARITY REGISTER                               | 8 bits<br>8 bits                                                          |

| LOAD EXTERNAL REGISTER CONTROL                                                                                       | 8 bits                                                                    |

| CHANNEL 3 BYTE COUNT > 129  CHANNEL 1 BYTE COUNT > 129  CHANNEL 1 BYTE COUNT > 129  CHANNEL 0 BYTE COUNT > 129       | O CHANNEL 0 ENABLED CHANNEL 1 ENABLED CHANNEL 2 ENABLED CHANNEL 3 ENABLED |

| CHANNEL 1 = OIC 02 HANDSHAKE PROTOCOL CHANNEL 2 = SCSI HANDSHAKE PROTOCOL +ACKNOWLEDGE-ACKNOWLEDGE +BEQUEST/-REQUEST | 0 ENABLE:DISABLE CHANNEL READWRITE BUFFER ENABLE:DISABLE BYTE COL         |

| TREGOEST-REGOEST                                                                                                     | REINITIALIZATION                                                          |

ENABLE/DISABLE CHANNEL INTERRUPT

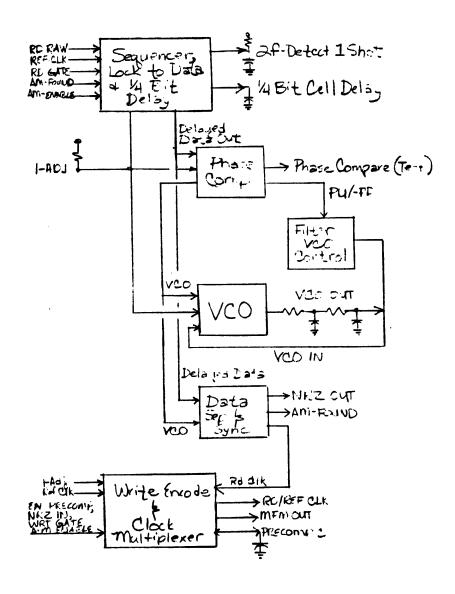

#### 5070 PFM MFM VCO/Encode/Decode Chip

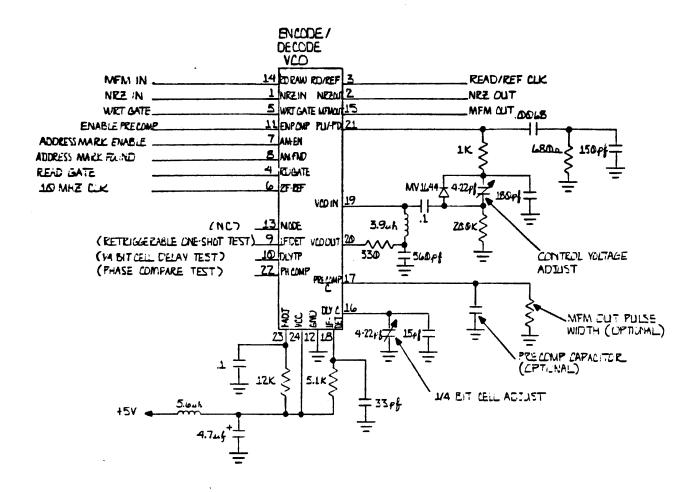

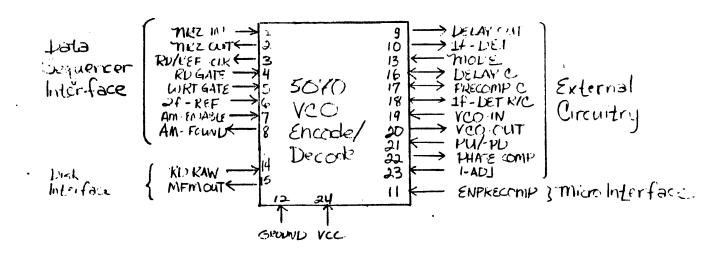

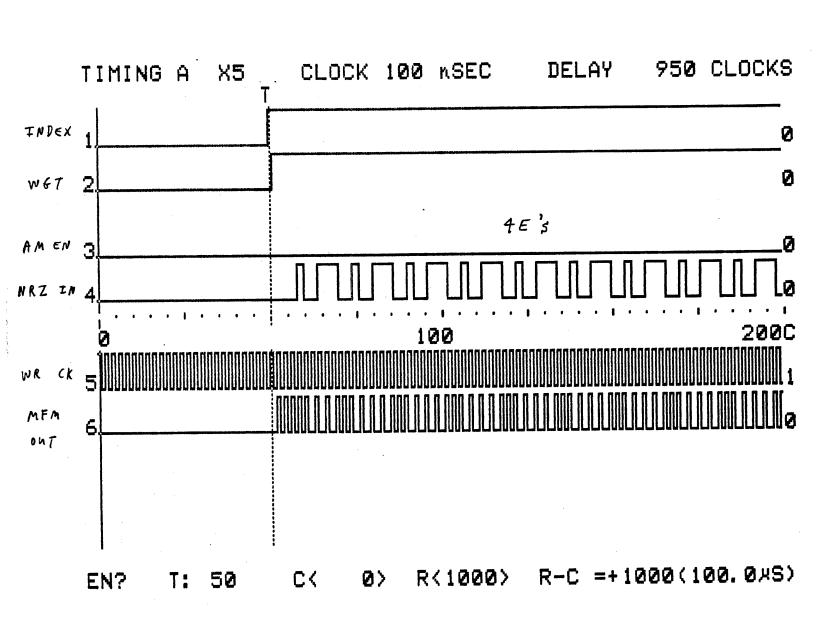

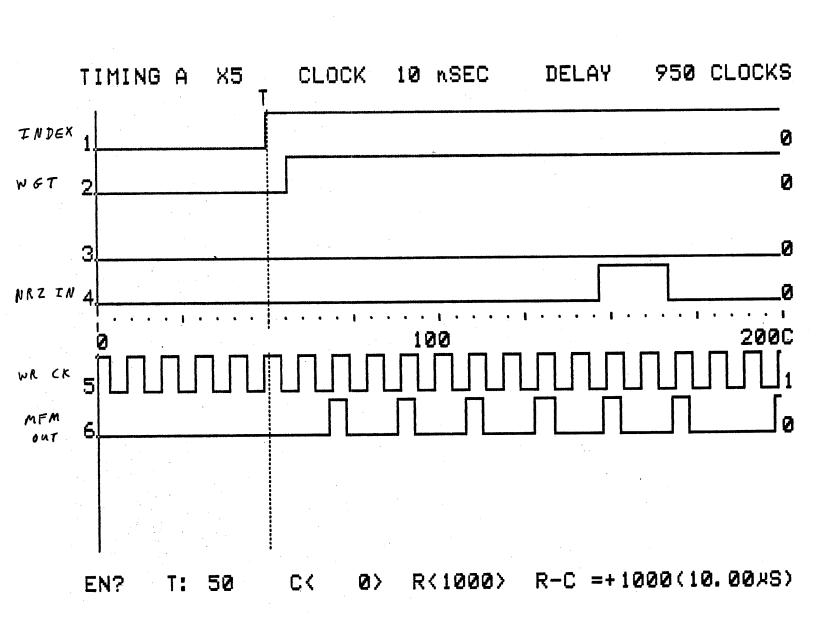

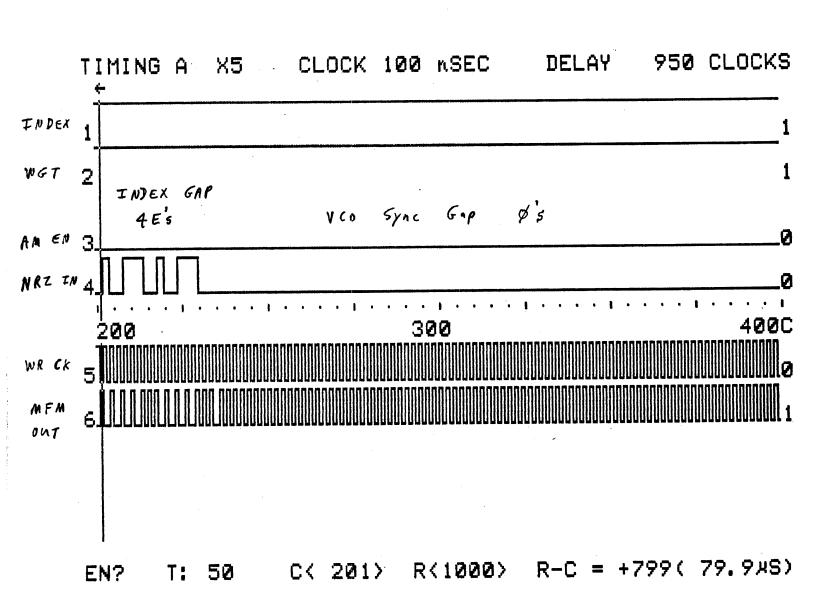

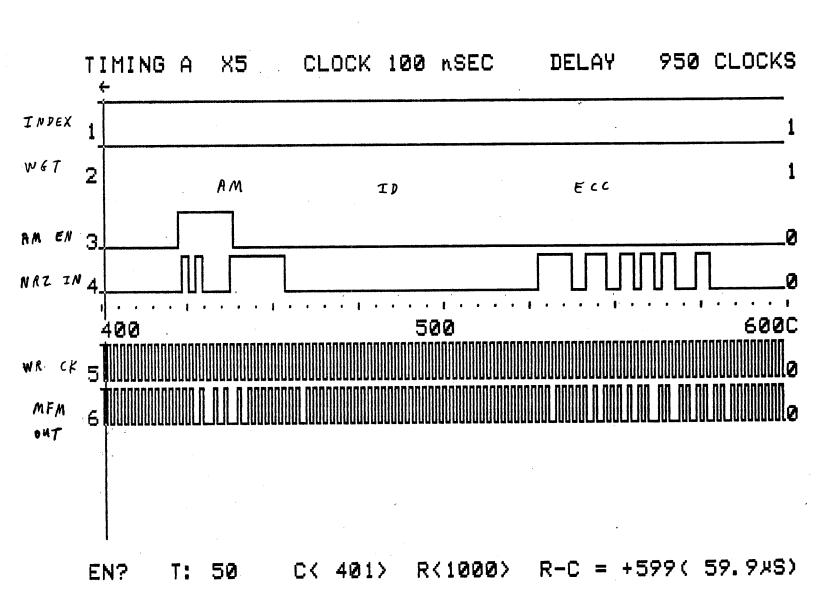

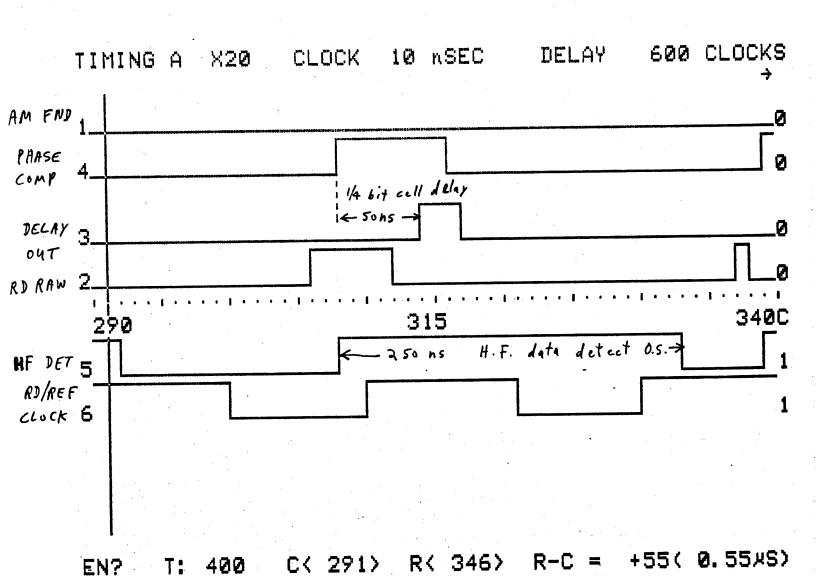

The PFM 5070 VCO/Encode/Decode chip provides all of the necessary functions needed to convert disk drives with MFM serial data interfaces (i.e., ST506/412, SA1000) to NRZ data and clock.

ST506/412, SA1000) to NRZ data and clock.

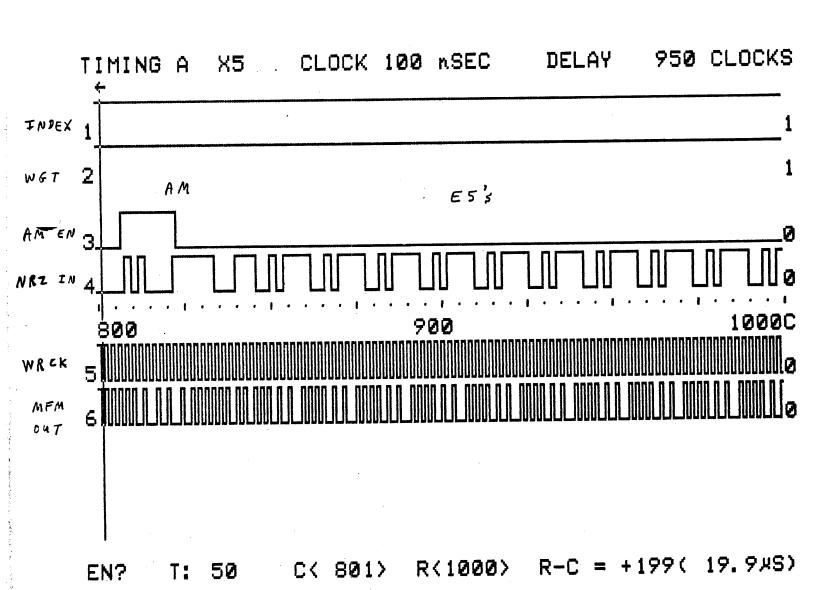

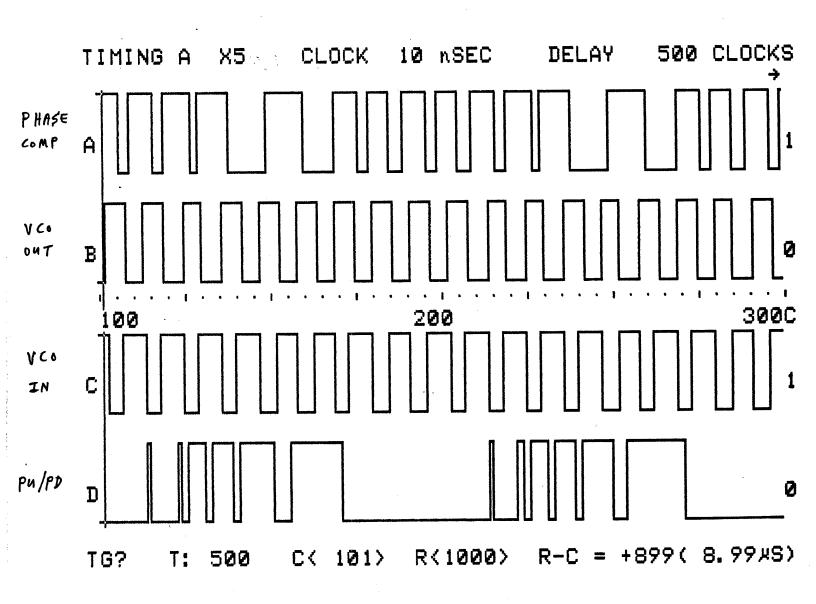

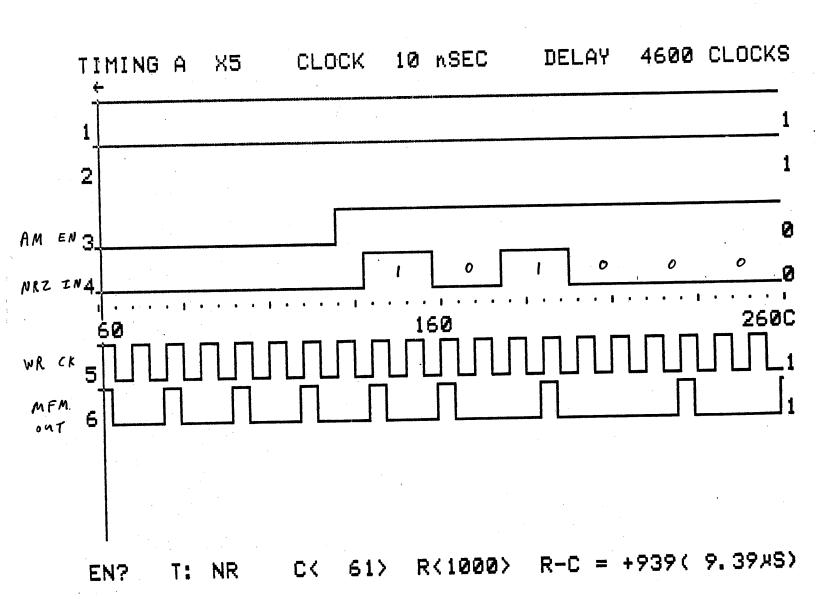

The PFM 5070 VCO/Encode/Decode chip is a completely self contained MFM/NRZ and NRZ/MFM data translator with an internal voltage controlled oscillator, phase locked loop, encode/decode logic, dropped clock address mark generation/detection and write precompensation circuitry.

The PFM 5070 VCO/Encode/Decode chip is capable of operation at data rates to 10 megabits per second by proper selection of the external frequency and loop gain components. Costly delay lines are eliminated by selecting write precompensation values with an internally temperature compensated external RC network.

#### Features:

24 PIN PLASTIC PACKAGE INTERNAL VCO AND PHASE LOCKED LOOP DATA RATE CONTROL TO 10 MEGABITS PER SECOND

NO EXTERNAL LOGIC REQUIRED

MFM TO NRZ AND NRZ TO MFM CONVERSION

ADDRESS MARK DETECTION AND GENERATION

WRITE PRECOMPENSATION

INTERNAL EARLY, ON TIME AND LATE TIMING

| NRZ-IN     |

|------------|

| NRZ-OUT    |

| RD/REF CLK |

| RD GATE    |

| WRT GATE   |

| 2-F REF    |

| A-M ENABLE |

| A-M FOUND  |

| DELAY OUT  |

| 1F-DET     |

| ENPRECOMP  |

| GROUND     |

| 1 2 3 4 5 ENCO 6 DECO 7 VCC 8 9 10 11 12 | DE 19 |

|------------------------------------------|-------|

|------------------------------------------|-------|

VCC

I-ADJ

PHASE COMP

PU/-PD

VCO-OUT

VCO-IN

1-F-DET R/C

PRE-COMP C

DELAY C

MFM OUT

RD RAW

MODE

A Data Controller Company

557 Salmar Avenue Campbell, California 95008 (408) 370-3555

#### NOVEMBER 03, 1983

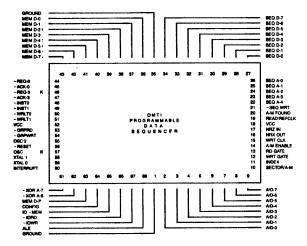

#### HIGH PERFORMANCE PROGRAMABLE DISK SEQUENCER

- \* UP TO 20 MBIT / SEC TRANSFER RATE

- \* MAX 2^8 \* 2^8 BYTES PER SECTOR LENGTHS

- \* HIGH LEVEL COMMANDS ( NO REAL TIME INTERVENTION )

- \* PROGRAMABLE ECC TO 64 BIT POLYNOMIAL & ID CRC OR ECC

- \* TOTAL FIELD COUNT AND VALUE PROGRAMABILITY

- \* NRZ INPUT / OUTPUT

- \* AUTOMATIC SECTOR INCREMENT FOR MULTI-SECTOR OPERATIONS

- \* ESDI SECTOR / ADDRESS MARK MODE

- \* 68 PIN PLASTIC LEADLESS CHIP CARRIER

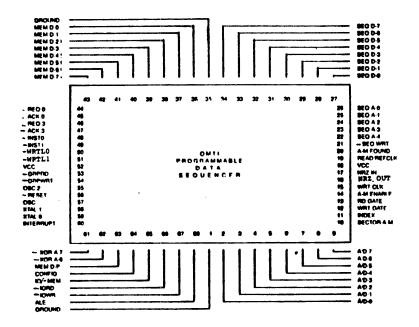

| GROUND MEM D-0 MEM D-1 MEM D-2 MEM D-3 MEM D-4 MEM D-5 MEM D-6 MEM D-6 MEM D-7 |                       | ! ! ! !<br>! ! ! ! | +             |           | SEQ D-7<br>SEQ D-6<br>SEQ D-5<br>SEQ D-4<br>SEQ D-3<br>SEQ D-2<br>SEQ D-1<br>SEQ D-0 |

|--------------------------------------------------------------------------------|-----------------------|--------------------|---------------|-----------|--------------------------------------------------------------------------------------|

|                                                                                | ! 43 42 41 40 39<br>! | 38 37 36 35        | 34 33 32 31 3 | !         |                                                                                      |

| -REQ-0                                                                         | ! 44<br>!             |                    |               | 26 !<br>! | SEQ A-0                                                                              |

| -ACK-0                                                                         | ! 45<br>!             |                    |               | 25 !<br>! | ··· -·· <b>~</b>                                                                     |

| -REQ-3                                                                         | ! 46<br>!             |                    |               | 24 !      | SEQ A-2                                                                              |

| -ACK-3                                                                         | ! 47<br>!             |                    |               | 23 !      | SEQ A-3                                                                              |

| -INSTO                                                                         | ! 48                  |                    |               | 22 !      | SEQ A-4                                                                              |

| -INST1                                                                         | ! 49                  | -                  |               | 21 !      | -SEQ WRT                                                                             |

| -WRLT0                                                                         | 50                    | омті               |               | 20 !      | A-M FOUND                                                                            |

| -WRLT1                                                                         | . 51                  |                    | M             | 19 !      | READ/REFCL                                                                           |

| VCC                                                                            | 1 P                   | ROGRAM             | MABLE         | 18        | VCC                                                                                  |

| -GRPRD                                                                         | !<br>! 53             | DISK               |               | 17 !      | NRZ IN                                                                               |

| -GRPWRT                                                                        | !<br>! 54             | SEQUEN             | CER           | 16!       | NRZ OUT                                                                              |

| osc/2                                                                          | !<br>! 55             |                    |               | 15 !      | WRT CLK                                                                              |

| -RESET                                                                         | !<br>! 56             |                    |               | 14 !      | A-M ENABLE                                                                           |

| osc                                                                            | !<br>! 57             |                    |               | 13 !      | RD GATE                                                                              |

| XTAL 1                                                                         | !<br>! 58             |                    |               | 12 !      | WRT GATE                                                                             |

| XTAL 0                                                                         | !<br>! 59             |                    |               | 11 !      | INDEX                                                                                |

| INTERRUPT                                                                      | !<br>! 60             |                    |               | 10 !      | SECTOR/A-M                                                                           |

|                                                                                | !<br>! 61 62 63 64 65 | 66 67 68 1         | 2 3 4 5 6     | 7 8 9 !   |                                                                                      |

| -XOR A-7 -XOR A-6 MEM D-P CONFIG IO/-MEM -IORD -IOWR ALE GROUND                | +                     | -+ ! ! !<br>+ ! !  | ! ! +         | !         | A/D-2<br>A/D-1                                                                       |

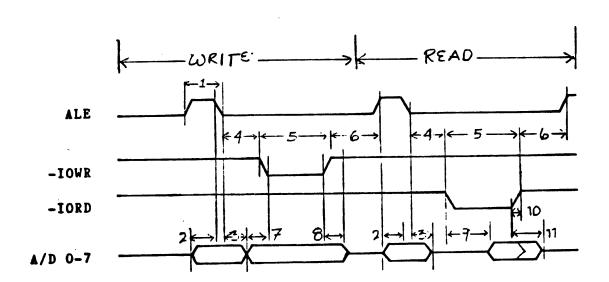

## A/D 0-7 I/O MULTIPLEXED ADDRESS / DATA BUS:

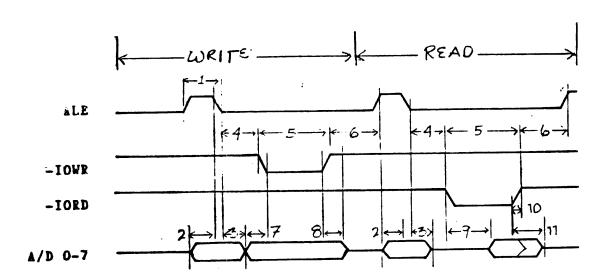

3-STATE ADDRESS / DATA LINES THAT INTERFACE WITH THE CPU LOWER 8 BIT ADDRESS / DATA BUS. THE ADDRESSES ARE LATCHED INTO THE ADDRESS REGISTER ON THE FALLING EDGE OF ALE. THE 8 BIT DATA IS EITHER WRITTEN INTO OR READ FROM THE DISK SEQUENCER REGISTERS DEPENDING ON -IOWR OR -IORD INPUT CONTROL LINES, IF THE ADDRESS IN WITHIN THE RANGE OF THE INTERNAL CHIP SELECT.

#### ALE I ADDRESS LATCH ENABLE:

THIS INPUT STROBE IS FOR STORING ADDRESS 0-7 INTO THE ADDRESS REGISTER ON THE FALLING EDGE OF ALE FOR INTERNAL CHIP AND REGISTER SELECT.

#### -IOWR I I/O WRITE:

THIS ACTIVE LOW INPUT STROBE IS USED BY THE CPU TO LOAD INFORMATION IN THE DISK SEQUENCER WITH THE PROPER ADDRESS FOR CHIP AND REGISTER SELECTION.

#### -IORD I I/O READ:

THIS ACTIVE LOW INPUT STROBE IS USED BY THE CPU TO READ STATUS INFORMATION FROM THE DISK SEQUENCER WITH THE PROPER ADDRESS FOR CHIP AND REGISTER SELECTION.

#### IO/-MEM I IO/-MEMORY:

THIS INTERNALLY PULLED-UP INPUT IS USED FOR AN ACTIVE HIGH CHIP ENABLE. IN AN 8085 SYSTEM THIS LINE IS CONNECTED TO THE SAME MICRO LINE OR IN ANY OTHER MICRO MAY BE LEFT OPEN.

#### XOR 7-6 I EXCLUSIVE OR ADDRESS 7 - 6:

THESE INTERNALLY PULLED-UP INPUTS ARE USED FOR THE INTERNAL CHIP SELECT. THEY CONTROL THE POLARITY OF THE CORROSPONDING ADDRESS LINE. IF ANOTHER GROUP CHIP SELECT IF REQUIRED, GROUND THE APPROPRIATE LINE.

#### CONFIG I CONFIG:

THIS INTERNALY PULLED-UP LINE IS USED TO SEL-ECT THE MICRO STROBE INPUTS. WHEN THIS INPUT IS GROUNDED THE CHIP IS CONFIGURED FOR AN 8085 TYPE MICRO. WHEN LEFT OPEN THE CHIP IS CONFIGURED AS A Z-8 TYPE MICRO.

#### XTAL 0/1 I/O CRYSTAL 0 / 1:

THE XTAL LINES ARE TO BE CONNECTED TO AN EXT-ERNAL CRYSTAL WITH A FREQUENCY OF 4 \* THE DISK 1-F DATA RATE. A CLOCK INPUT MAY BE CONNECTED TO THE XTAL O INPUT WITH THE XTAL 1 LINE LEFT OPEN IF AN EXTERNAL CLOCK SOURCE IS AVAILABLE.

#### OSC O OSCILLATOR:

THIS OUTPUT IS A TTL OUTPUT OF THE XTAL FREQUENCY

#### OSC/2 O OSCILLATOR / 2:

THIS OUTPUT IS A FREE RUNNING CLOCK AT 1/2 THE OSCILLATOR OUTPUT.

#### -RESET I -RESET:

THIS INPUT WHEN ACTIVE RESETS READ GATE OR WRITE GATE AND PUTS THE CHIP IN A NOT BUSY MODE.

#### INTERRUPT O INTERRUPT:

THIS OUTPUT, IF ENABLED IS ACTIVE WHEN THE SEQUENCER IS COMPLETED WITH A COMMAND. THIS OUTPUT IS RESET THEN THE MICRO READS STATUS.

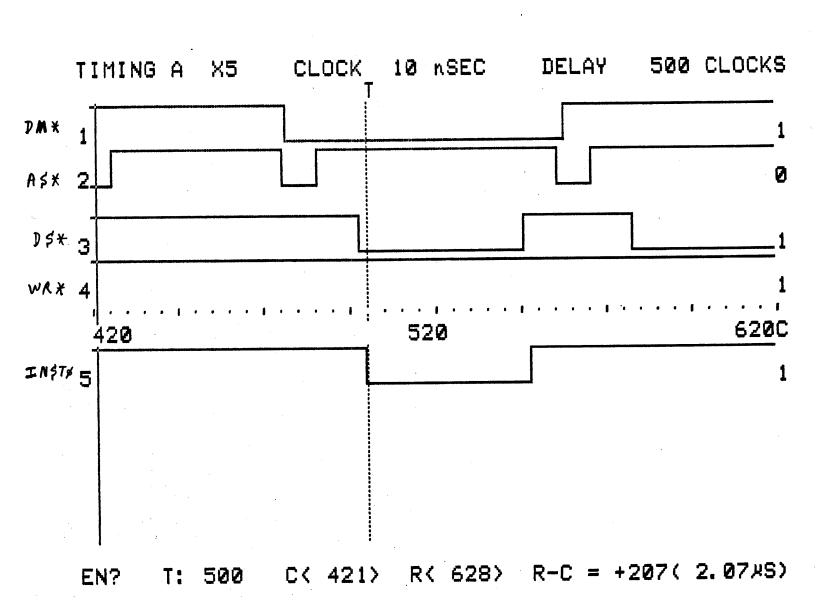

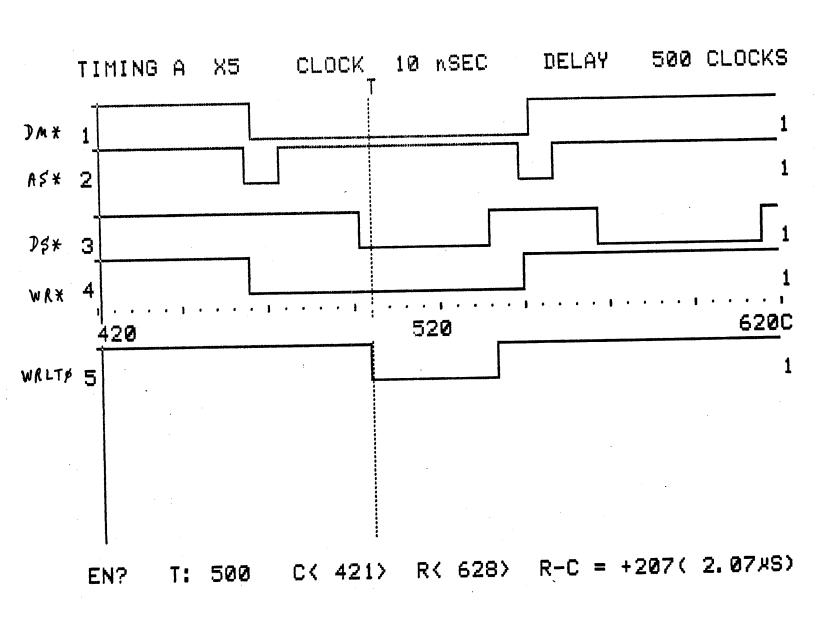

#### -INSTO-1 O IN STATUS 0 / 1:

THESE OUTPUT STROBES ARE INTERALLY DECODE I/O READ STROBES INTENDED TO BE USED BY THE MICRO TO READ DEVICE STATUS THROUGH AN EXTERNAL BUFFER TO THE MICRO DATA BUS.

#### -WRLT0-1 O WRITE LATCH 0 / 1:

THESE OUTPUT STROBES ARE INTERALLY DECODE I/O WRITE STROBES INTENDED TO BE USED BY THE MICRO TO WRITE DEVICE CONTROL THROUGH AN EXTRNAL LATCH FROM THE MICRO DATA BUS.

#### -GRPRD/WR/O GROUP READ / WRITE STROBE:

THESE INTERNALLY DECODED GROUP-SELECT ARE INTENDED TO BE INTERFACED WITH AN EXTERNAL PERIPHERAL CHIP WITH THE REQUIREMENT OF BLOCK MEMORY I/O FROM THE MEMORY CONTROLLER.

#### -REQ 0 O DMA SEQUENCER REQUEST:

THE DMA REQUEST 0 LINE IS ACTIVATED WHEN THE SEQUENCER NEEDS TO TRANSFER DATA TO / FROM THE MEMORY CONTROLLER.

#### -ACK 0 I DMA MEMORY ACKNOWLEDGE 0:

THIS DMA ACKNOWLEDGE LINE IS TO ENABLE DATA FROM THE SEQUENCER IN A WRITE MEMORY FUNCTION OR SAVE DATA IN THE SEQUENCER IN A READ MEMORY FUNCTION.

#### -REQ-3 O REQUEST 3:

THIS OUTPUT IS USED FOR THE MICRO TO REQUEST DATA TO OR FROM THE MEMORY CONTROLLER SYSTEM.

#### -ACK-3 I ACKNOWLEDGE 3:

THIS INPUT IS A RESPONSE FROM REQ-3 FROM THE MEMORY CONTROLLER SYSTEM.

## MEMD 0-7 I/O MEMORY DATA 0-7:

THIS 8 BIT BIDIRECTIONAL DATA BUS IS THE PATH THE DATA GETS TO AND FROM THE MEMORY.

#### MEMD P O MEMORY DATA PARITY:

THIS OUTPUT IS A FALL THROUGH ODD PARITY OF THE MEMORY DATA BUS.

#### NRZ OUT O NRZ DATA OUT:

THIS SERIAL DATA OUTPUT LINE, WHEN WRITE GATE IS TRUE, OUTPUTS ALL SERIAL DATA AND THE ECC FIELD AS PROGRAMED IN THE SEQUENCER.

#### NRZ IN I NRZ DATA IN:

THIS SERIAL DATA INPUT LINE, IS THE OUTPUT FROM THE DATA SEPARATOR OR ESDI TYPE DISK DRIVE.

#### WRT CLK O WRITE CLOCK:

THIS OUTPUT IS THE 1-F NRZ WRITE AT THE RD/REFERANCE CLOCK RATE.

#### RD/REFCLK I READ / REFERENCE CLOCK:

THIS INPUT, THE NRZ WRITE CLOCK OR THE READ NRZ CLOCK IF READ GATE IS TRUE. A CLOCK MUST ALWAYS BE A CLOCK PRESENT AT THIS INPUT.

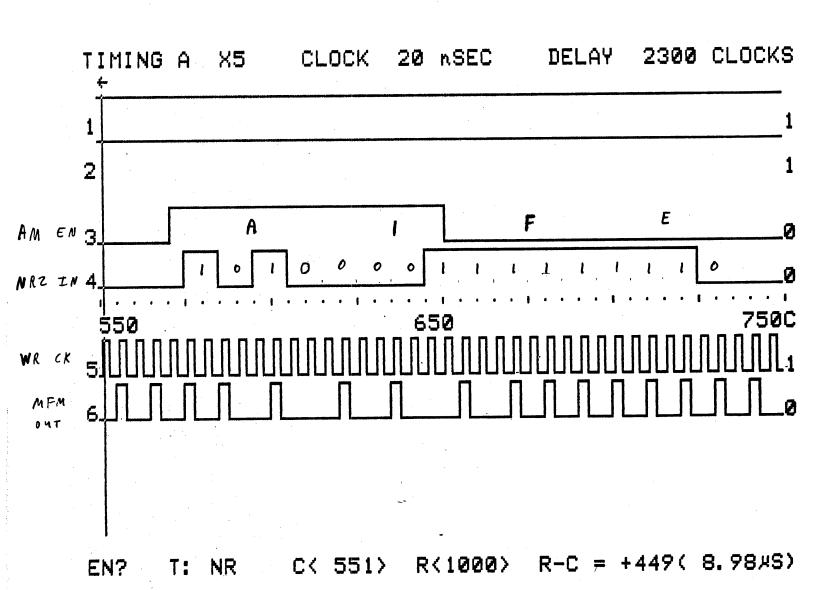

#### A-M EN O ADDRESS MARK ENABLE:

THIS OUTPUT, IF ESDI MODE IS SELECTED IS TRUE AT STATE 1 STROBE TIME. THIS FUNCTION IS FOR WRITING THE ADDRESS MARK TO THE DISK DRIVE. IF ESDI MODE IS NOT SELECTED, THIS OUTPUT IS TRUE FOR STATE STROBE 2 & 8 AND CAN BE USED FOR EXTERNAL ENCODING OF THE DROP CLOCK BYTE.

#### RD GATE O READ GATE:

THIS OUTPUT IS TRUE WHEN THE DISK SEQUENCER IS IN READ MODE. IT IS THE RESPONSIBILITY OF DATA SEPARATOR CHIP TO PROVIDE AM FOUND IF THE SEQUENCER IS IN EXTERNAL SYNC MODE.

#### WRT GATE O WRITE GATE:

THIS OUTPUT IS TRUE WHEN THE DISK SEQUENCER IS WRITE DATA TO THE DISK.

#### INDEX I INDEX:

THIS INPUT IS FROM THE DISK AND IS PULSED EVERY REVOLUTION. THE SEQUENCER USES THE LEADING EDGE OF THIS SIGNAL ONLY FOR A FORMAT COMMAND, AND FOR A PROGRAMABLE "WATCH DOG TIMMER".

#### SEC/A-M I SEC / A-M FOUND / SYNC:

THIS INPUT CAN BE CONFIGURED AS EITHER THE SECTOR LINE IN A HARD-SECTORED DRIVE OR THE ADDRESS-MARK-FOUND INPUT FROM A ESDI TYPE DRIVE.

#### A-M FND I ADDRESS MARK FOUND:

THIS INPUT IS TO BE USED WITH THE ENCODE / DECODE VCO CHIP FOR MFM BYTE SYNC.

## SEQ D0-7 I/O SEQUENCER DATA 0-7:

THIS 8 BIT BI-DIRECTIONAL DATA BUS IS USED BY THE SEQUENCER AS A REGISTER FILE OR RAM FOR STORING THE SEQUENCE FIELD COUNT AND VALUE.

#### SEQ A0-4 O SEQUENCER ADDRESS 0-4:

THESE FIVE ADDRESS LINES ARE USED TO SELECT THE SPECIFIC REGISTER CORRESPONDING TO THE STATE THE SEQUENCER IS IN.

#### -SEQWRT O SEQUENCER WRITE:

THIS OUTPUT IS TRUE WHEN THE MICRO IS DOWN LOADING THE SEQUENCER REGISTER FILE.

## COMMAND / CONTROL REGISTER ASSIGNMENT

## ADDRESS REGISTER AND CONTROL

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | -IOWR | -IORD | REGISTER FUNCTION          |

|---|---|---|---|---|---|---|---|-------|-------|----------------------------|

| S | s | 1 | 0 | 0 | 0 | 0 | 0 | 0     | 1     | COMMAND                    |

| s | s | 1 | 0 | 0 | 0 | 0 | 1 | 0     | 1     | SEQUENCER LOOP COUNT       |

| s | s | 1 | 0 | 0 | 0 | 1 | 0 | 0     | 1     | TIME-OUT                   |

| s | S | 1 | 0 | 0 | 0 | 1 | 1 | 0     | 1     | SECTOR SUB-BLOCK COUNT     |

| S | s | 1 | 0 | 0 | 1 | 0 | 0 | 0     | 1     | CYLINDER HIGH (HDR BYTE 0) |

| s | s | 1 | 0 | 0 | 1 | 0 | 1 | 0     | 1     | CYLINDER LOW (HDR BYTE 1)  |

| s | S | 1 | 0 | 0 | 1 | 1 | 0 | 0     | 1     | HEAD / FLAG (HDR BYTE 2)   |

| S | s | 1 | 0 | 0 | 1 | 1 | 1 | 0     | 1     | SECTOR (HDR BYTE 3)        |

| s | S | 1 | 0 | 1 | 0 | 0 | 0 | 0     | 1     | MICRO TO MEMORY            |

| s | s | 1 | 0 | 1 | 0 | 0 | 1 | 0     | 1     | SEQ START / RE-START STATE |

| s | s | 1 | 0 | 1 | 0 | 1 | 0 | 0     | 1     | SEQUENCER LOOP END STATE   |

| S | s | 1 | 0 | 1 | 0 | 1 | 1 | 0     | 1     | BIT RING START             |

| s | s | 1 | 0 | 1 | 1 | 0 | 0 | 0     | 1     | ECC CONTROL                |

| s | s | 1 | 0 | 1 | 1 | 0 | 1 | 0     | 1     | ENCODE / DECODE CONTROL    |

| s | s | 1 | 0 | 1 | 1 | 1 | 0 | 0     | 1     | SEQ COUNT REG @ RESTART    |

| s | s | 1 | 0 | 1 | 1 | 1 | 1 | 0     | 1     | SEQ VALUE REG @ RESTART    |

S S = INTERNAL CHIP SELECT

#### STATUS / HEADER REGISTER ASSIGNMENT

## ADDRESS REGISTER AND CONTROL

| 7 ( | 6 5 | 4 | 3 | 2 | 1 | 0 | -IOWR | -IORD | REGISTER FUNCTION           |

|-----|-----|---|---|---|---|---|-------|-------|-----------------------------|

| S S | s 1 | 0 | 0 | 0 | 0 | 0 | 1     | 0     | STATUS                      |

| s s | s 1 | 0 | 0 | 0 | 0 | 1 | 1     | 0     | EXTENDED STATUS             |

| s s | S 1 | 0 | 0 | 0 | 1 | 0 | 1     | 0     | RETRY COUNT / STATE ADDRESS |

| s s | s 1 | 0 | 0 | 0 | 1 | 1 | 1     | 0     | FLAG BYTE (HDR BYTE 4)      |

| s s | s 1 | 0 | 0 | 1 | 0 | 0 | 1     | 0     | CYLINDER HIGH (HDR BYTE 0)  |

| SS  | s l | 0 | 0 | 1 | 0 | 1 | . 1   | 0     | CYLINDER LOW (HDR BYTE 1)   |

| s s | s l | 0 | 0 | 1 | 1 | 0 | 1     | 0     | HEAD / FLAG (HDR BYTE 2)    |

| s s | s 1 | 0 | 0 | 1 | 1 | 1 | 1     | 0     | SECTOR (HDR BYTE 3)         |

| s s | 5 1 | 0 | 1 | 0 | 0 | 0 | 1     | 0     | MEMORY TO MICRO             |

| s s | S 1 | 0 | 1 | 0 | 0 | 1 | 1     | 0     | SEQUENCER LOOP COUNT        |

| s s | s 1 | 0 | 1 | 0 | 1 | 0 | 1     | 0     | NOT USED                    |

| s s | s 1 | 0 | 1 | 0 | 1 | 1 | 1     | 0     | NOT USED                    |

| s s | 5 1 | 0 | 1 | 1 | 0 | 0 | 1     | 0     | NOT USED                    |

| s s | s 1 | 0 | 1 | 1 | 0 | 1 | 1     | 0     | NOT USED                    |

| s s | 5 1 | 0 | 1 | 1 | 1 | 0 | 1     | 0     | SEQ COUNT REG @ RESTART     |

| s s | s 1 | 0 | 1 | 1 | 1 | 1 | 1     | 0     | SEQ VALUE REG @ RESTART     |

S S = INTERNAL CHIP SELECT

LOAD ECC POLYMONIAL CONFIGURATION REGISTER ASSIGNMENT WRITE EXTERNAL I/O STROBES

ADDRESS REGISTER AND CONTROL

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | -IOWR | -IORD | REGISTER FUNCTION     |

|---|---|---|---|---|---|---|---|-------|-------|-----------------------|

| S | S | 1 | 1 | 0 | 0 | 0 | 0 | 0     | 1     | POLYNOMIAL 0 - 7      |

| S | S | 1 | 1 | 0 | 0 | 0 | 1 | 0     | 1     | POLYNOMIAL 8 - 15     |

| S | S | 1 | 1 | 0 | 0 | 1 | 0 | 0     | 1     | POLYNOMIAL 16 - 23    |

| S | S | 1 | 1 | 0 | 0 | 1 | 1 | 0     | 1     | POLYNOMIAL 24 - 31    |

| S | S | 1 | 1 | 0 | 1 | 0 | 0 | 0     | 1     | POLYNOMIAL 32 - 39    |

| S | S | 1 | 1 | 0 | 1 | 0 | 1 | 0     | 1     | POLYNOMIAL 40 - 47    |

| S | S | 1 | 1 | 0 | 1 | 1 | 0 | 0     | 1     | POLYNOMIAL 48 - 55    |

| s | S | 1 | 1 | 0 | 1 | 1 | 1 | 0     | 1     | POLYNOMIAL 56 - 63    |

| s | s | 1 | 1 | 1 | 0 | 0 | 0 | 0     | 1     | EXTERNAL OUT STROBE 0 |

| S | s | 1 | 1 | 1 | 0 | 0 | 1 | 0     | 1     | EXTERNAL OUT STROBE 1 |

| s | S | 1 | 1 | 1 | 0 | 1 | 0 | 0     | 1     | NOT USED              |

| s | s | 1 | 1 | 1 | 0 | 1 | 1 | 0     | 1     | NOT USED              |

| s | s | 1 | 1 | 1 | 1 | 0 | 0 | 0     | 1     | EXTERNAL GROUP STROBE |

| S | s | 1 | 1 | 1 | 1 | 0 | 1 | 0     | . 1   | EXTERNAL GROUP STROBE |

| s | s | 1 | 1 | 1 | 1 | 1 | 0 | 0     | 1     | EXTERNAL GROUP STROBE |

| s | s | 1 | 1 | 1 | 1 | 1 | 1 | 0     | 1     | EXTERNAL GROUP STROBE |

S S= INTERNAL CHIP SELECT

READ ECC SYNDROME REGISTER ASSIGNMENT

#### READ EXTERNAL I/O STROBES

ADDRESS REGISTER AND CONTROL

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | -IOWR | -IORD | REGISTER FUNCTION      |  |

|---|---|---|---|---|---|---|---|-------|-------|------------------------|--|

| s | S | 1 | 1 | 0 | 0 | 0 | 0 | 1     | 0     | NOT USED               |  |

| S | S | 1 | 1 | 0 | 0 | 0 | 1 | 1     | 0     | NOT USED               |  |

| S | S | 1 | 1 | 0 | 0 | 1 | 0 | 1     | 0     | NOT USED               |  |

| S | S | 1 | 1 | 0 | 0 | 1 | 1 | 1     | 0     | NOT USED               |  |

| S | S | 1 | 1 | 0 | 1 | 0 | 0 | 1     | 0     | NOT USED               |  |

| S | S | 1 | 1 | 0 | 1 | 0 | 1 | 1     | 0     | NOT USED               |  |

| s | S | 1 | 1 | 0 | 1 | 1 | 0 | 1     | 0     | NOT USED               |  |

| S | S | 1 | 1 | 0 | 1 | 1 | 1 | 1     | 0     | NOT USED               |  |

| S | S | 1 | 1 | 1 | 0 | 0 | 0 | 1     | 0     | EXTERNAL IN STROBE 0   |  |

| S | S | 1 | 1 | 1 | 0 | 0 | 1 | 1     | 0     | EXTERNAL IN STROBE 1   |  |

| S | S | 1 | 1 | 1 | 0 | 1 | 0 | 1     | 0     | NOT USED               |  |

| S | S | 1 | 1 | 1 | 0 | 1 | 1 | 1     | 0     | MICRO-DMA MEM TO GROUP |  |

| S | S | 1 | 1 | 1 | 1 | 0 | 0 | 1     | 0     | EXTERNAL GROUP STROBE  |  |

| s | S | 1 | 1 | 1 | 1 | 0 | 1 | 1     | 0     | EXTERNAL GROUP STROBE  |  |

| S | S | 1 | 1 | 1 | 1 | 1 | 0 | 1 .   | 0     | EXTERNAL GROUP STROBE  |  |

| s | s | 1 | 1 | 1 | 1 | 1 | 1 | 1     | 0     | EXTERNAL GROUP STROBE  |  |

S S= INTERNAL CHIP SELECT

## LOAD SEQUENCER FIELD COUNT REGISTER ASSIGNMENT

## RESTART REGISTER AND CONTROL

| 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 | -IOWR | -IORD | REGISTER FUNCTION      |

|---|---|---|---|----|---|---|---|-------|-------|------------------------|

| Х | Х | Х | Х | 0  | 0 | 0 | 0 | 0     | 1     | ESDI SECTOR GAP COUNT  |

| Х | Х | Х | X | 0  | 0 | 0 | 1 | 0     | 1     | POST-INDEX-GAP COUNT   |

| X | X | X | Х | 0  | 0 | 1 | 0 | 0     | 1     | ID PREAMBLE COUNT      |

| Х | Х | X | X | 0  | 0 | 1 | 1 | 0     | 1     | ID SYNC BYTE COUNT     |

| Х | Х | X | X | 0  | 1 | 0 | 0 | 0     | 1     | ID MARKER BYTE COUNT   |

| X | X | Х | Х | 0  | 1 | 0 | 1 | 0     | 1     | ID DATA FIELD COUNT    |

| Х | Х | Х | X | 0  | 1 | 1 | 0 | 0     | 1     | ID ECC BYTE COUNT      |

| X | Х | Х | Х | 0  | 1 | 1 | 1 | 0     | 1     | ID POSTAMBLE COUNT     |

| X | X | Х | Х | 1  | 0 | 0 | 0 | 0     | 1     | DATA PREAMBLE COUNT    |

| X | Х | Х | Х | 1. | 0 | 0 | 1 | 0     | 1     | DATA SYNC BYTE COUNT   |

| X | Х | X | Х | 1  | 0 | 1 | 0 | 0     | 1     | DATA MARKER BYTE COUNT |

| Х | X | X | Х | 1. | 0 | 1 | 1 | 0     | 1     | DATA FIELD COUNT       |

| X | Х | Х | х | 1  | 1 | 0 | 0 | 0     | 1     | DATA ECC BYTE COUNT    |

| Х | Х | Х | Х | 1  | 1 | 0 | 1 | 0     | 1     | DATA POSTAMBLE COUNT   |

| Х | Х | Х | Х | 1  | 1 | 1 | 0 | 0     | 1     | INTER-SECTOR-GAP COUNT |

| X | X | X | X | 1  | 1 | 1 | 1 | 0     | 1     | PRE-INDEX-GAP COUNT    |

## READ SEQUENCER FIELD COUNT REGISTER ASSIGNMENT

## RESTART REGISTER AND CONTROL

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | -IOWR | -IORD | REGISTER FUNCTION      |

|---|---|---|---|---|---|---|---|-------|-------|------------------------|

| Х | Х | Х | Х | 0 | 0 | 0 | 0 | 1     | 0     | ESDI SECTOR GAP COUNT  |

| Х | Х | Х | Х | 0 | 0 | 0 | 1 | 1     | 0     | POST-INDEX-GAP COUNT   |

| Х | Х | Х | Х | 0 | 0 | 1 | 0 | 1     | 0     | ID PREAMBLE COUNT      |

| Х | Х | Х | X | 0 | 0 | 1 | 1 | 1     | 0     | ID SYNC BYTE COUNT     |

| Х | Х | Х | Х | 0 | 1 | 0 | 0 | 1     | 0     | ID MARKER BYTE COUNT   |

| Χ | Х | Х | Х | 0 | 1 | 0 | 1 | 1     | 0     | ID DATA FIELD COUNT    |

| Х | Х | Х | Х | 0 | 1 | 1 | 0 | 1     | 0     | ID ECC BYTE COUNT      |

| Х | Х | Х | Х | 0 | 1 | 1 | 1 | 1     | 0     | ID POSTAMBLE COUNT     |

| Х | Х | Х | Х | 1 | 0 | 0 | 0 | 1     | 0     | DATA PREAMBLE COUNT    |

| Х | Х | Х | Х | 1 | 0 | 0 | 1 | 1     | 0     | DATA SYNC BYTE COUNT   |

| Х | Х | Х | Х | 1 | 0 | 1 | 0 | 1     | 0     | DATA MARKER BYTE COUNT |

| Х | Х | Х | X | 1 | 0 | 1 | 1 | 1     | 0     | DATA FIELD COUNT       |

| Х | X | Х | Х | 1 | 1 | 0 | 0 | 1     | 0     | DATA ECC BYTE COUNT    |

| Х | X | X | Х | 1 | 1 | 0 | 1 | 1     | 0     | DATA POSTAMBLE COUNT   |

| Х | Х | Х | Х | 1 | 1 | 1 | 0 | 1     | 0     | INTER-SECTOR-GAP COUNT |

| Х | Х | Х | X | 1 | 1 | 1 | 1 | 1     | 0     | PRE-INDEX-GAP COUNT    |

## LOAD SEQUENCER FIELD VALUE REGISTER ASSIGNMENT

## RESTART REGISTER AND CONTROL

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | -IOWR | -IORD | REGISTER FUNCTION       |

|---|---|---|---|---|---|---|---|-------|-------|-------------------------|

| Х | Х | Х | Х | 0 | 0 | 0 | 0 | 0     | 1     | ESDI SECTOR GAP VALUE   |

| Х | X | Х | X | 0 | 0 | 0 | 1 | 0     | 1     | POST-INDEX-GAP VALUE    |

| X | X | X | Х | 0 | 0 | 1 | 0 | 0     | 1     | ID PREAMBLE VALUE       |

| Х | Х | X | Х | 0 | 0 | 1 | 1 | 0     | 1     | ID SYNC BYTE VALUE      |

| Х | X | Х | Х | 0 | 1 | 0 | 0 | 0     | 1     | ID MARKER BYTE VALUE    |

| Х | Х | Х | X | 0 | 1 | 0 | 1 | 0     | 1     | NOT USED                |

| Х | Х | Х | Х | 0 | 1 | 1 | 0 | 0     | 1     | NOT USED                |

| Х | Х | Х | X | 0 | 1 | 1 | 1 | 0     | 1     | ID POSTAMBLE VALUE      |

| Х | Х | Х | Х | 1 | 0 | 0 | 0 | 0     | 1     | DATA PREAMBLE VALUE     |

| X | Х | Х | Х | 1 | 0 | 0 | 1 | 0     | 1     | DATA SYNC BYTE VALUE    |

| X | Х | Х | Х | 1 | 0 | 1 | 0 | 0     | 1     | DATA MARKER BYTE VALUE  |

| Х | Х | Х | Х | 1 | 0 | 1 | 1 | 0     | 1     | FORMAT DATA FIELD VALUE |

| Х | Х | Х | Х | 1 | 1 | 0 | 0 | 0     | 1     | NOT USED                |

| X | Х | Х | Х | 1 | 1 | 0 | 1 | 0     | 1     | DATA POSTAMBLE VALUE    |

| Х | Х | х | Х | 1 | 1 | 1 | 0 | 0     | 1     | INTER-SECTOR-GAP VALUE  |

| X | Х | Х | Х | 1 | 1 | 1 | 1 | 0     | 1     | PRE-INDEX-GAP VALUE     |

## READ SEQUENCER FIELD VALUE REGISTER ASSIGNMENT

| RESTART | REGISTER | AND CONTROL |                         |

|---------|----------|-------------|-------------------------|

| 7 6 5 4 | 3 2 1 0  | -IOWR -IORD | REGISTER FUNCTION       |

| x x x x | 0 0 0 0  | 1 0         | ESDI SECTOR GAP VALUE   |

| x x x x | 0 0 0 1  | 1 0         | POST-INDEX-GAP VALUE    |

| x x x x | 0 0 1 0  | 1 0         | ID PREAMBLE VALUE       |

| x x x x | 0 0 1 1  | 1 0         | ID SYNC BYTE VALUE      |

| x x x x | 0 1 0 0  | 1 0         | ID MARKER BYTE VALUE    |

| x x x x | 0 1 0 1  | 1 0         | NOT USED                |

| x x x x | 0 1 1 0  | 1 0         | NOT USED                |

| x x x x | 0 1 1 1  | 1 0         | ID POSTAMBLE VALUE      |

| x x x x | 1 0 0 0  | 1 0         | DATA PREAMBLE VALUE     |

| x x x x | 1 0 0 1  | 1 0         | DATA SYNC BYTE VALUE    |

| x x x x | 1 0 1 0  | 1 0         | DATA MARKER BYTE VALUE  |

| x x x x | 1 0 1 1  | 1 0         | FORMAT DATA FIELD VALUE |

| x x x x | 1 1 0 0  | 1 0         | NOT USED                |

| x x x x | 1 1 0 1  | 1 0         | DATA POSTAMBLE VALUE    |

| x x x x | 1 1 1 0  | 1 0         | INTER-SECTOR-GAP VALUE  |

| x x x x | 1 1 1 1  | 1 0         | PRE-INDEX-GAP VALUE     |

#### COMMAND REGISTER

```

WRITE DATA BUS

7 6 5 4 3 2 1 0

1 1 1 1 1 1 1 1

! ! ! ! ! ! ! +---- 1 = READ

!!!!!+----

1 = WRITE

1 1 1 1 1

!!!!+-----

0 = NORMAL

1 = FORMAT / ID DATA

1 1 1 1 1

!!!!+----

0 = NORMAL

1 = LONG ( ECC TO / FROM BUFFER )

1 1 1 1

! ! ! +----- 1 = SYNDROME TO BUFFER

0 = ABORT ON FLAG NON-ZERO

1 = IGNORE FLAG CONDITION

! + ---  1 = VERIFY ( BUFFER TO DISK DATA )

+----- 1 = NO DATA TRANSFER

SEQUENCER COUNT

WRITE DATA BUS

7 6 5 4 3 2 1 0

1 1 1 1 1 1 1 1

+-+-+-+-+-+----- NUMBER OF SECTORS ( N = N )

INDEX TIME-OUT

WRITE DATA BUS

7 6 5 4 3 2 1 0

1 1 1 1 1 1 1 1

!!!!+-+-+----

# OF REVS BEFORE TIMEOUT ( 2 - F )

SUB-BLOCK COUNT

WRITE DATA BUS

TOTAL BYTES PER SECTOR =

7 6 5 4 3 2 1 0

DATA FIELD COUNT * SUB-BLOCK COUNT

1 1 1 1 1 1 1 1

+-+-+-+-+-+-+----- # OF SUB-BLOCKES PER SECTOR

```

#### CYLINDER HIGH

WRITE DATA BUS

CYLINDER LOW

WRITE DATA BUS

HEAD

WRITE DATA BUS

SECTOR

WRITE DATA BUS

MICRO TO MEMORY

WRITE DATA BUS

#### SEQUENCER START / RE-START

WRITE DATA BUS

## 7 6 5 4 3 2 1 0 1 1 1 1 1 1 1 1 ! ! ! +-+-+---- START STATE X0 - XF 1 1 1 1 +-+-+- RE-START STATE 0X - FX SEQUENCER LOOP STATE WRITE DATA BUS 7 6 5 4 3 2 1 0 X X X X ! ! ! ! . X X X X +-+-+---- LOOP STATE X0 - XF BIT RING START COUNT WRITE DATA BUS 7 6 5 4 3 2 1 0 X X X X ! ! ! ! X X X X +-+-+---- START BIT 0 - F ECC CONTROL WRITE DATA BUS 7 6 5 4 3 2 1 0 1 1 1 1 1 1 1 1 ! ! ! ! ! ! +----- 0 = ECC CLEAR ON INIT ! ! ! ! ! +----- 1 = ECC PRESET ON INIT! ! ! ! ! +----- 0 = DATA TO ECC ! ! ! ! ! ! +----- 1 = -DATA TO ECC 1 = -DATA TO ECC ! ! ! ! +---- 0 = ECC FEEDBACK!!!!+-----1 = -ECC FEEDBACK1 1 1 1 1 !!!!+----0 = ECC DATA OUT1 = -ECC DATA OUT !!!!+----!!!! 0 = ECC CHECK1 = -ECC CHECK 0 = XFER DISABLE 1 = XFER ENABLE 0 = I - D = CRC1 = ENABLE DATA FIELD SYNC TIMEOUT

## CONFIG CONTROL

## WRITE DATA BUS

| 7 6 5 4 3 2 1 0 |                                                     |

|-----------------|-----------------------------------------------------|

|                 |                                                     |

| 1 1 1 1 1 1 1   |                                                     |

| ! ! ! ! ! ! +   | 0 = SOFT SECTORED                                   |

| 1 1 1 1 1 1 +   | 1 = HARD SECTORED                                   |

| 1 1 1 1 1 1     |                                                     |

| 1 1 1 1 1 +     | 0 = 1 FIELD SYNC                                    |

| !!!!!+          | 1 = 2 FIELD SYNC                                    |

| 1 1 1 1 1 1     |                                                     |

| !!!!+           | O = HEAD / FLAG BYTE                                |

| 1 1 1 1 +       | 1 = FLAG BYTE                                       |

|                 |                                                     |

| 1 1 1 +         | 0 = NOT .ESDI CONFIG                                |

| +               | 1 = ESDI CONFIG                                     |

|                 |                                                     |

| +               | 0 = INTERNAL SYNC DETECT                            |

| +               | 1 = EXTERNAL SYNC DETECT                            |

|                 | _                                                   |

| +               | 0 = DISABLE WRITE GATE EDGE                         |

| 1 1 +           | 1 = ENABLE WRITE GATE EDGE                          |

| 1 1             | -                                                   |

| 1 +             | 0 = INTERRUPT ACTIVE LOW                            |

| 1 +             | 1 = INTERRUPT ACTIVE HIGH                           |

| 1               | T T11 T T11 ( ) T T T T T T T T T T T T T T T T T T |

| <u> </u>        | 0 = INTERRUPT DISABLED                              |

|                 | 1 = INTERRUPT ENABLED                               |

| +               | T - INTERKOLI EMUDDED                               |

| MICRO TO MEMORY                                                                    |                |

|------------------------------------------------------------------------------------|----------------|

| WRITE DATA BUS                                                                     |                |

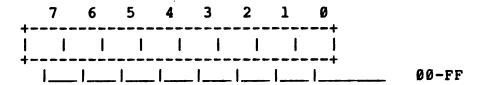

| 7 6 5 4 3 2 1 0<br>! ! ! ! ! ! ! !<br>+-+-+                                        | - FF           |

| EXTERNAL REGISTER 0 STROBE                                                         |                |

| WRITE DATA BUS                                                                     |                |

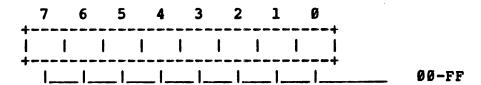

| 7 6 5 4 3 2 1 0<br>! ! ! ! ! ! ! !<br>+-+-+-+-+                                    | - FF           |

| EXTERNAL REGISTER 1 STROBE                                                         |                |

| WRITE DATA BUS                                                                     |                |

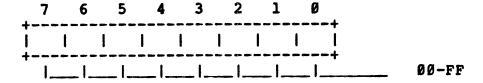

| 7 6 5 4 3 2 1 0<br>! ! ! ! ! ! ! !<br>+-+-+-+-+-+ 00 -                             | - FF           |

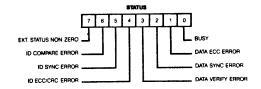

| STATUS                                                                             |                |

| READ DATA BUS                                                                      |                |

| 7 6 5 4 3 2 1 0<br>! ! ! ! ! ! ! ! !<br>! ! ! ! ! ! ! + 1 =<br>! ! ! ! ! ! ! + 1 = | BUSY           |

| !!!!!!+ 1 =                                                                        | DATA ECC ERROR |

| 7       | 6  | 5      | 4              | 3  | 2  | 1 0    |       |   |                              |

|---------|----|--------|----------------|----|----|--------|-------|---|------------------------------|

| Ī       | !  | !      | į              | į  | i  | ! +    | <br>1 | = | BUSY                         |

| !!      | !  | !<br>! | !              | !  | !! | !<br>+ | <br>1 | = | DATA ECC ERROR               |

| !       | 1  | 1      | 1              | !  | !  | •      | -     |   | Billi 100 Billon             |

| !       | !  | !      | !              | !  | +- |        | <br>1 | = | DATA SYNC + MARKER NOT FOUND |

| !       | !  | !      | !              | !  |    |        | ,     |   | D1///1 ///D7// DD0-          |

| :       | 1  |        | :              | +- |    |        | <br>T | = | DATA VERIFY ERROR            |

| !       | !  | !      | <u>.</u><br>+- |    |    |        | <br>1 | = | ID ECC ERROR                 |

| !       | !  | +-     |                |    |    |        | <br>1 | = | ID SYNC + MARKER NOT FOUND   |

| !       | +- |        |                |    |    |        | <br>1 | = | ID DATA NO COMPARE           |

| :<br>+- |    |        |                |    |    |        | <br>1 | = | EXTENDED STATUS NON ZERO     |

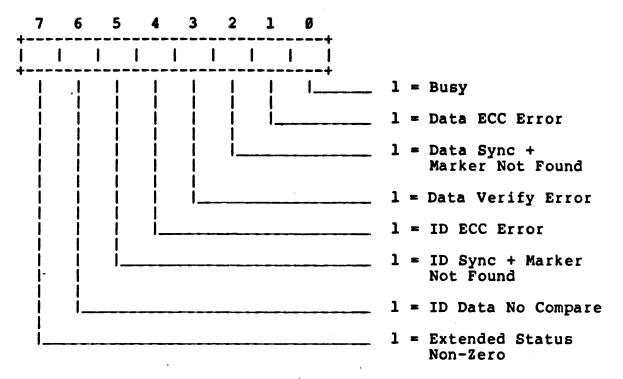

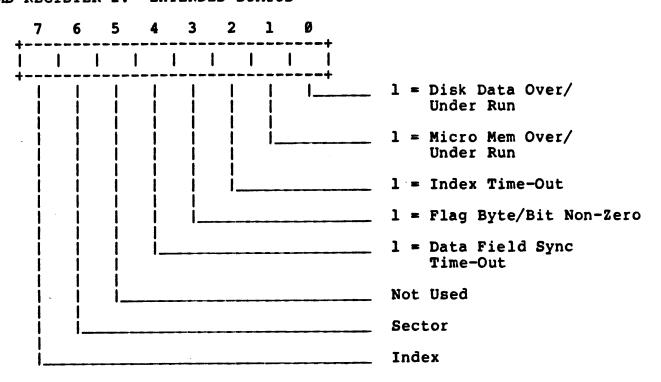

#### EXTENDED STATUS

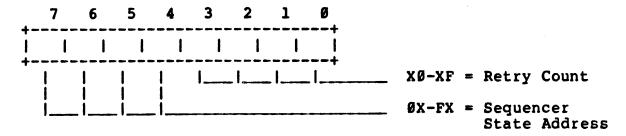

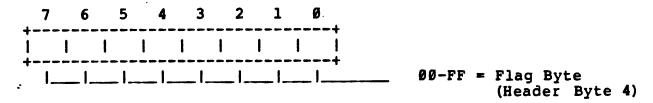

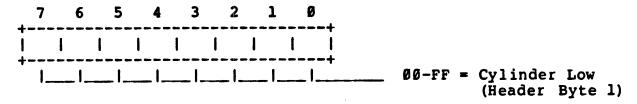

## READ DATA BUS 7 6 5 4 3 2 1 0 1 1 1 1 1 1 1 1 ! ! ! ! ! ! +----- 1 = DISK DATA OVER / UNDER RUN 1 1 1 1 1 1 1 ! ! ! ! ! +----- 1 = MICRO MEM OVER / UNDER RUN 1 1 1 1 1 1 ! ! ! ! ! +----- 1 = INDEX TIMEOUT ! ! ! ! +----- 1 = FLAG BYTE / BIT NON-ZERO 1 1 1 1 1 = DATA FIELD SYNC TIMEOUT NOT USED SECTOR +---- INDEX RETRY COUNT READ DATA BUS 7 6 5 4 3 2 1 0 1 1 1 1 1 1 1 1 ! ! ! +-+-+----- X0 - XF = RETRY COUNT1 1 1 1 +-+-+ OX - FX = SEQUENCER STATE ADDRESS FLAG BYTE READ DATA BUS 7 6 5 4 3 2 1 0 1 1 1 1 1 1 1 1 CYLINDER HIGH READ DATA BUS 7 6 5 4 3 2 1 0 1 1 1 1 1 1 1 1

#### CYLINDER LOW

## FORMAT COMMAND -- STATE SEQUENCE

| MODE    | STATE | FUNCTION         | COUNT   | VALUE         |

|---------|-------|------------------|---------|---------------|

|         | 0     | NOT USED         |         |               |

| START   | 1     | POST-INDEX-GAP   | SEQ-CNT | SEQ-VAL       |

| RESTART | 2     | ID PREAMBLE      | SEQ-CNT | SEQ-VAL       |

|         | 3     | ID SYNC          | SEQ-CNT | SEQ-VAL       |

|         | 4     | ID MARK          | SEQ-CNT | SEQ-VAL       |

|         | 5     | ID DATA FIELD    | SEQ-CNT | MEMORY        |

|         | 6     | ID ECC           | SEQ-CNT | ECC GENERATER |

|         | 7     | ID POSTAMBLE     | SEQ-CNT | SEQ-VAL       |

|         | 8     | DATA PREAMBLE    | SEQ-CNT | SEQ-VAL       |

|         | 9     | DATA SYNC        | SEQ-CNT | SEQ-VAL       |

|         | A     | DATA MARK        | SEQ-CNT | SEQ-VAL       |

|         | В     | DATA FIELD       | CNT*BLK | SEQ-VAL       |

|         | C     | DATA ECC         | SEQ-CNT | ECC GENERATER |

|         | D     | DATA POSTAMBLE   | SEQ-CNT | SEQ-VAL       |

| LOOP    | E     | INTER-SECTOR-GAP | SEQ-CNT | SEQ-VAL       |

| HOLD    | F     | PRE-INDEX-GAP    | INDEX   | SEQ-VAL       |

|         | 10    | DONE             |         |               |

## READ COMMAND -- STATE SEQUENCE

| MODE    | STATE | FUNCTION      | COUNT   | VALUE           |

|---------|-------|---------------|---------|-----------------|

|         | 0     | NOT USED      |         |                 |

|         | 1     | NOT USED      |         |                 |

|         | 2     | NOT USED      |         |                 |

| SRT/RES | SRT 3 | ID SYNC       | SEQ-CNT | SEQ-VAL         |

|         | 4     | ID MARK       | SEQ-CNT | SEQ-VAL         |

|         | 5     | ID DATA FIELD | SEQ-CNT | HEADER REGISTER |

|         | 6     | ID ECC        | SEQ-CNT | ECC CHECK       |

|         | · 7   | SKIP STATE    | 1       |                 |

|         | 8     | SKIP STATE    | 1       |                 |

|         | 9     | DATA SYNC     | SEQ-CNT | SEQ-VAL         |

|         | Α     | DATA MARK     | SEQ-CNT | SEQ-VAL         |

|         | В     | DATA FIELD    | CNT*BLK | DATA TO MEMORY  |

|         | С     | DATA ECC      | SEQ-CNT | ECC CHECK       |

|         | D     | SKIP STATE    | 1       |                 |

| LOOP    | E     | SKIP STATE    | 1       |                 |

|         | F     | NOT USED      |         |                 |

## READ LONG COMMAND -- STATE SEQUENCE

| MODE    | STATE | FUNCTION      | COUNT   | VALUE           |

|---------|-------|---------------|---------|-----------------|

|         | 0     | NOT USED      |         |                 |

|         | 1     | NOT USED      |         |                 |

|         | 2     | NOT USED      |         |                 |

| SRT/RES | SRT 3 | ID SYNC       | SEQ-CNT | SEQ-VAL         |

|         | 4     | ID MARK       | SEQ-CNT | SEQ-VAL         |

|         | 5     | ID DATA FIELD | SEQ-CNT | HEADER REGISTER |

|         | 6     | ID ECC        | SEQ-CNT | ECC CHECK       |

|         | 7     | SKIP STATE    | 1       |                 |

|         | 8     | SKIP STATE    | 1       |                 |

|         | 9     | DATA SYNC     | SEQ-CNT | SEQ-VAL         |

|         | ` A   | DATA MARK     | SEQ-CNT | SEQ-VAL         |

|         | В     | DATA FIELD    | CNT*BLK | DATA TO MEMORY  |

|         | С     | DATA ECC      | SEQ-CNT | ECC TO MEMORY   |

|         | D     | SKIP STATE    | 1       |                 |

| LOOP    | E     | SKIP STATE    | 1       |                 |

|         | F     | NOT USED      |         |                 |

## READ SYNDROME COMMAND -- STATE SEQUENCE

| MODE    | STATE | FUNCTION      | COUNT   | VALUE           |

|---------|-------|---------------|---------|-----------------|

|         | 0     | NOT USED      |         |                 |

|         | 1     | NOT USED      |         |                 |

|         | 2     | NOT USED      |         |                 |

| SRT/RES | RT 3  | ID SYNC       | SEQ-CNT | SEQ-VAL         |

|         | 4     | ID MARK       | SEQ-CNT | SEQ-VAL         |

|         | 5     | ID DATA FIELD | SEQ-CNT | HEADER REGISTER |

|         | 6     | ID ECC        | SEQ-CNT | ECC CHECK       |

| •       | 7     | SKIP STATE    | 1       |                 |

|         | 8     | SKIP STATE    | 1       |                 |

|         | 9     | DATA SYNC     | SEQ-CNT | SEQ-VAL         |

|         | Α     | DATA MARK     | SEQ-CNT | SEQ-VAL         |

|         | В     | DATA FIELD    | CNT*BLK | DATA TO MEMORY  |

|         | C     | DATA ECC      | SEQ-CNT | SYND TO MEMORY  |

|         | D     | SKIP STATE    | 1       |                 |

| LOOP    | E     | SKIP STATE    | 1       |                 |

|         | F     | NOT USED      |         |                 |

## WRITE COMMAND -- STATE SEQUENCE

| MODE    | STATE | FUNCTION       | COUNT   | VALUE           |

|---------|-------|----------------|---------|-----------------|

|         | 0     | NOT USED       |         |                 |

|         | 1     | NOT USED       |         |                 |

|         | 2     | NOT USED       |         |                 |

| SRT/RES | RT 3  | ID SYNC        | SEQ-CNT | SEQ-VAL         |

|         | 4     | ID MARK        | SEQ-CNT | SEQ-VAL         |

|         | 5     | ID DATA FIELD  | SEQ-CNT | HEADER REGISTER |

|         | 6     | ID ECC         | SEQ-CNT | ECC CHECK       |

|         | 7     | ID POSTAMBLE   | SEQ-CNT |                 |

|         | 8     | DATA PREAMBLE  | SEQ-CNT | SEQ-VAL         |

|         | 9     | DATA SYNC      | SEQ-CNT | SEQ-VAL         |

|         | A     | DATA MARK      | SEQ-CNT | SEQ-VAL         |

|         | В     | DATA FIELD     | CNT*BLK | DATA FROM MEM   |

|         | C ·   | DATA ECC       | SEQ-CNT | ECC CHECK       |

|         | D     | DATA POSTAMBLE | SEQ-CNT | SEQ-VAL         |

| LOOP    | E     | SKIP STATE     | 1       |                 |

|         | F     | NOT USED       |         |                 |

## WRITE LONG COMMAND -- STATE SEQUENCE

| MODE    | STATE | FUNCTION       | COUNT   | VALUE           |

|---------|-------|----------------|---------|-----------------|

|         | 0     | NOT USED       |         |                 |

|         | 1     | NOT USED       |         |                 |

|         | 2     | NOT USED       |         |                 |

| SRT/RES | SRT 3 | ID SYNC        | SEQ-CNT | SEQ-VAL         |

|         | 4     | ID MARK        | SEQ-CNT | SEQ-VAL         |

|         | 5     | ID DATA FIELD  | SEQ-CNT | HEADER REGISTER |

|         | 6     | ID ECC         | SEQ-CNT | ECC CHECK       |

|         | 7     | ID POSTAMBLE   | SEQ-CNT |                 |

|         | 8     | DATA PREAMBLE  | SEQ-CNT | SEQ-VAL         |

|         | 9     | DATA SYNC      | SEQ-CNT | SEQ-VAL         |

|         | Α     | DATA MARK      | SEQ-CNT | SEQ-VAL         |

|         | В     | DATA FIELD     | CNT*BLK | DATA FORM MEM   |

|         | С     | DATA ECC       | SEQ-CNT | DATA FROM MEM   |

|         | D     | DATA POSTAMBLE | SEQ-CNT | SEQ-VAL         |

| LOOP    | Е     | SKIP STATE     | 1       |                 |

|         | F     | NOT USED       |         |                 |

## READ VERIFY COMMAND -- STATE SEQUENCE

| MODE    | STATE | FUNCTION      | COUNT   | VALUE           |

|---------|-------|---------------|---------|-----------------|

|         | 0     | NOT USED      |         |                 |

|         | 1     | NOT USED      |         |                 |

|         | 2     | NOT USED      |         |                 |

| SRT/RES | SRT 3 | ID SYNC       | SEQ-CNT | SEQ-VAL         |

|         | 4     | ID MARK       | SEQ-CNT | SEQ-VAL         |

|         | 5     | ID DATA FIELD | SEQ-CNT | HEADER REGISTER |

|         | 6     | ID ECC        | SEQ-CNT | ECC CHECK       |

|         | 7     | SKIP STATE    | 1       |                 |

|         | 8     | SKIP STATE    | 1       |                 |

|         | 9     | DATA SYNC     | SEQ-CNT | SEQ-VAL         |

|         | A     | DATA MARK     | SEQ-CNT | SEQ-VAL         |

|         | В     | DATA FIELD    | CNT*BLK | DATA FROM MEM   |

|         | .C    | DATA ECC      | SEQ-CNT | ECC CHECK       |

|         | D     | SKIP STATE    | 1       |                 |

| LOOP    | E     | SKIP STATE    | 1       |                 |

|         | F     | NOT USED      |         |                 |

## READ VERIFY LONG COMMAND -- STATE SEQUENCE

| MODE    | STATE | FUNCTION      | COUNT   | VALUE           |

|---------|-------|---------------|---------|-----------------|

|         | 0     | NOT USED      |         |                 |

|         | 1     | NOT USED      |         |                 |

|         | 2     | NOT USED      |         |                 |

| SRT/RES | RT 3  | ID SYNC       | SEQ-CNT | SEQ-VAL         |

|         | 4     | ID MARK       | SEQ-CNT | SEQ-VAL         |

|         | 5     | ID DATA FIELD | SEQ-CNT | HEADER REGISTER |

|         | 6     | ID ECC        | SEQ-CNT | ECC CHECK       |

|         | 7     | SKIP STATE    | 1       |                 |

|         | 8     | SKIP STATE    | 1       |                 |

|         | 9     | DATA SYNC     | SEQ-CNT | SEQ-VAL         |

|         | Α     | DATA MARK     | SEQ-CNT | SEQ-VAL         |

|         | В     | DATA FIELD    | CNT*BLK | DATA FORM MEM   |

|         | C     | DATA ECC      | SEQ-CNT | DATA FROM MEM   |

|         | D     | SKIP STATE    | 1       |                 |

| LOOP    | E     | SKIP STATE    | 1       |                 |

|         | F     | NOT USED      |         |                 |

# OMTI 557 SALMAR AVE. CAMPBELL, CALIFORNIA 95008 (408) 370-3555

#### PRODUCT SPECIFICATION

for

OMTI PFM 5050 PROGRAMMABLE DATA SEQUENCER

MAY 1984

# OMTI PFM 5050 PROGRAMMABLE DATA SEQUENCER PRODUCT SPECIFICATION (PART #20505)

| REV. | REVISION HISTORY | PRINT DATE   |

|------|------------------|--------------|

|      | Original Issue   | May 18, 1984 |

|      |                  |              |

Copyright 1984 by OMT Incorporated.

The information in this publication is subject to change without notice. OMTI assumes no responsibility for the use of any circuitry other than circuitry embodied in an OMTI product. No other circuit patent licenses are implied.

# TABLE OF CONTENTS

|                                                                                         | Page    | Numbe                                                       |

|-----------------------------------------------------------------------------------------|---------|-------------------------------------------------------------|

| CHAPTER 1. GENERAL DESCRIPTION                                                          |         |                                                             |

| 1.1 Introduction                                                                        |         | 1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-4<br>1-4<br>1-5<br>1-5 |

| CHAPTER 2. FUNCTIONAL DESCRIPTION                                                       |         |                                                             |

| 2.1 Introduction                                                                        | • • • • | 2-1<br>2-1<br>2-1<br>2-19                                   |

| 2.3 Commands                                                                            | • • • • | 2-20<br>2-22                                                |

| CHAPTER 3. INTERFACING                                                                  |         |                                                             |

| 3.1 Signal Descriptions                                                                 | • • • • | 3-1<br>3-6<br>3-7<br>3-8                                    |

| 3.3 DC Information                                                                      | • • • • | 3-9<br>3-9<br>3-9                                           |

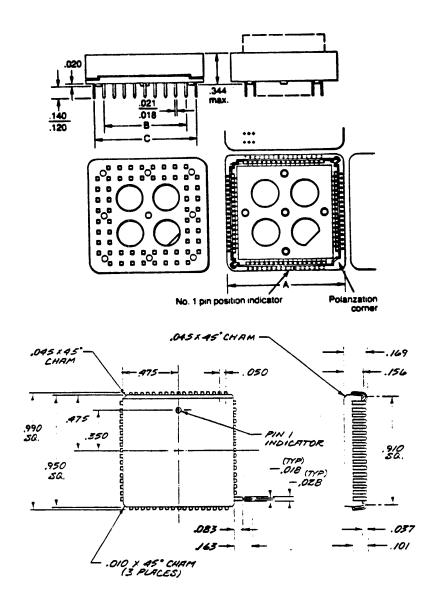

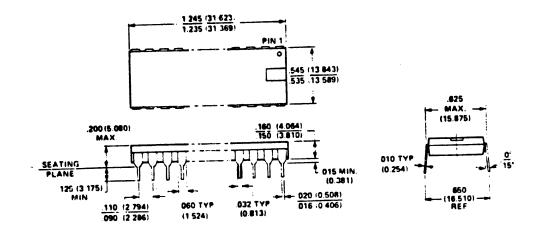

| 3.4 Package Dimensions                                                                  | • • • • | 3-10                                                        |

| APPENDIX A: INITIALIZATION OF THE REGISTER FILE                                         |         |                                                             |

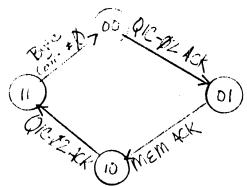

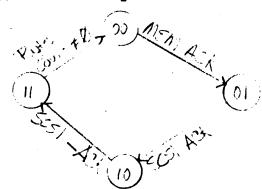

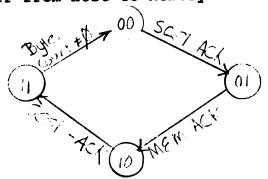

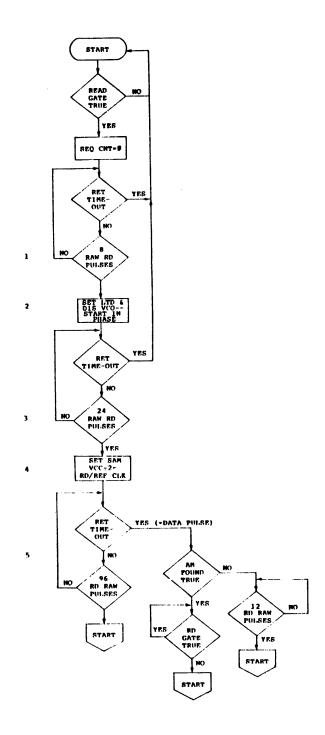

| APPENDIX B: SEQUENCER STATE FLOW CHART (SOFT-SECTORED)                                  | )       |                                                             |

| APPENDIX C: SEQUENCER STATE FLOW CHART (HARD-SECTORED ESDI-SECTORED, ESDI ADDRESS MARK) | •       |                                                             |

| APPENDIX D: DATA TRANSFER PARAMETER REGISTER SUMMARY                                    |         |                                                             |

# LIST OF ILLUSTRATIONS

|                                                                                                    | 1                                                                                                                                                                                                                                                    | Page  | Number                                                        |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------|

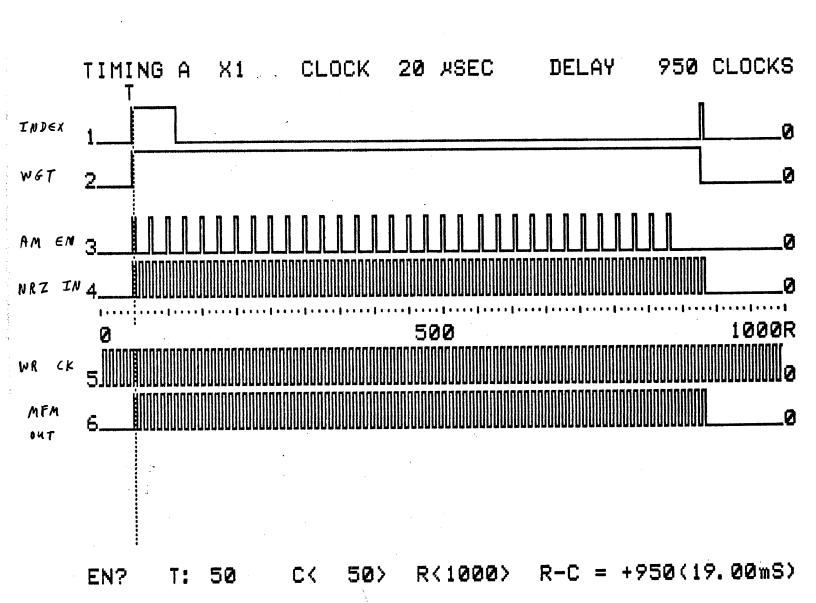

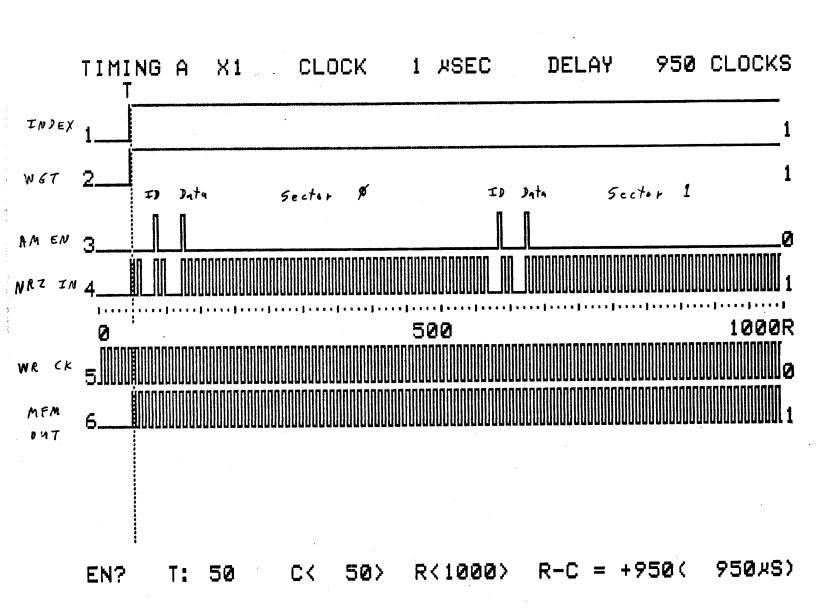

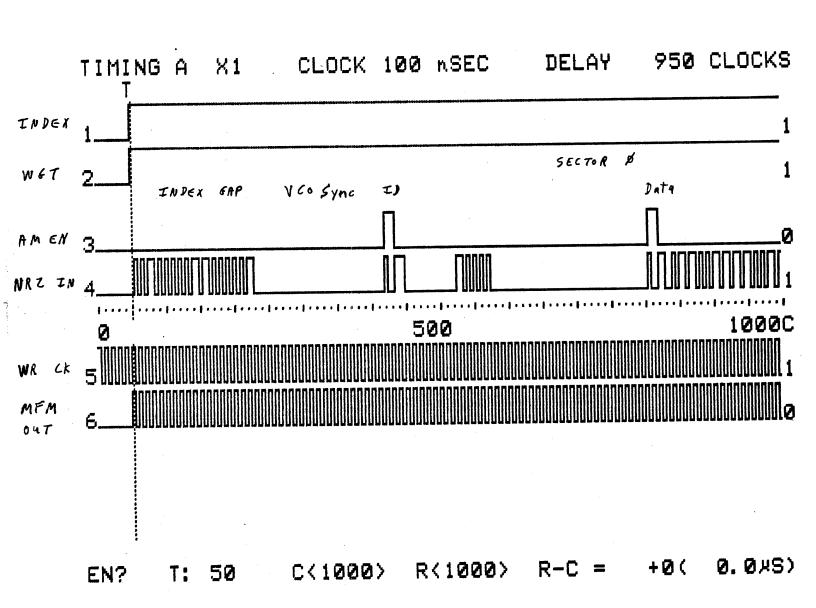

| Figure 1 Figure 2 Figure 3 Figure 4 Figure 5 Figure 6 Figure 7 Figure 8 Figure 9 Figure 1 Figure 1 | Functional Block Diagram  System Configuration  Sync Detect and Byte Clock Timing  XOR Gate Circuit Diagram  State Sequence for Format Command  Pin Assignments  Pin Functions  Z8 Mode Timing  8085/8051 Mode Timing  Socket and Package Dimensions |       | 1-3<br>1-4<br>2-8<br>2-9<br>2-21<br>3-1<br>3-7<br>3-8<br>3-10 |

|                                                                                                    | LIST OF TABLES                                                                                                                                                                                                                                       |       |                                                               |

| Table 1. Table 2. Table 3. Table 4.                                                                | Data Transfer Parameter Registers  Data Transfer Parameter Register Map  Format Parameter Register File  Pin Descriptions                                                                                                                            | • • • | 2-2<br>2-3<br>2-20<br>3-2                                     |

#### CHAPTER 1

#### GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

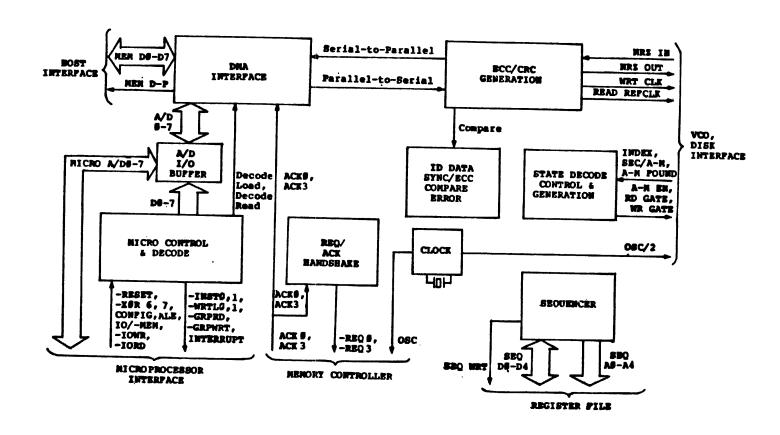

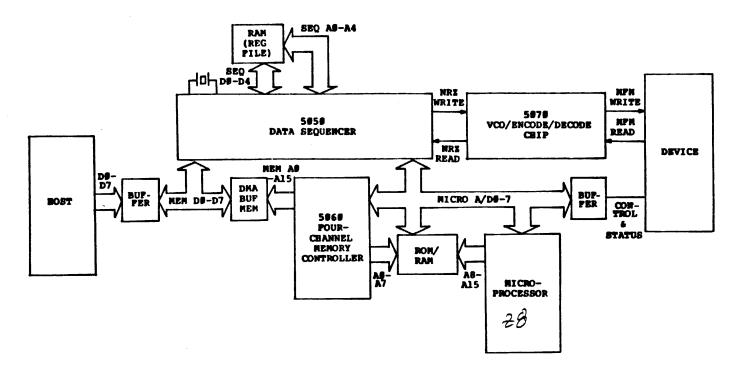

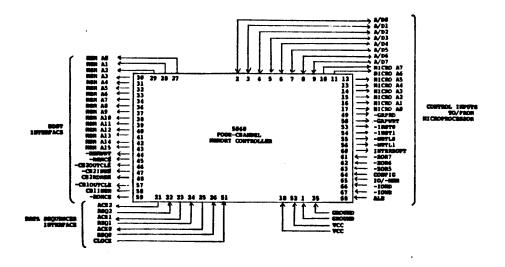

The OMTI PFM 5050 Data Sequencer is a special-purpose CMOS/VLSI component that manages the flow of block-level information between serial disk device interfaces and a DMA memory controller in advanced Winchester disk controller designs.

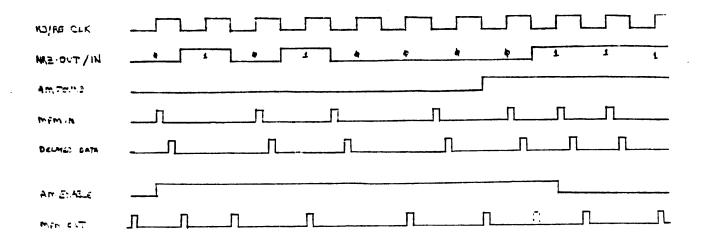

The 5050 is designed to be used with the PFM 5060 Four-Channel Memory Controller, a RAM buffer, a byte-oriented microprocessor, and appropriate drivers and receivers. The Data Sequencer can also be used with the PFM 5070 VCO/Encode/Decode chip to provide all the functions needed to interface to disk drives using MFM-encoded data.

The Data Sequencer provides the bit-serial data management, format control, error detection, and serialization/de-serialization functions normally associated with data controllers. The chip is designed to be used directly with NRZ interfaces such as SMD, LMD, ESDI; when used with the PFM 5070 chip, it provides all the control lines required for MFM interfaces such as Shugart Associates 1000, the Quantum Q2000, and the Seagate Technology ST506 and ST412 drives.

### 1.2 5050 DATA SEQUENCER CAPABILITIES

- \* High level instruction set

- \* Total field count and value programmability:

Programmable sector sizes to 65536 bytes/sector

Programmable header sizes to 256-bytes/header

Programmable gap sizes and fill characters

User-definable header flag bytes

64-bit programmable (ECC) polynomial and ID CRC or ECC

- \* ESDI sector/address mark mode

- \* 15 MHz bit rate--up to 15M bit/sec transfer rate

- \* NRZ serial disk interface

- \* Multiple sector transfers capability with automatic sector increment for multi-sector operations

- \* Programmable number of automatic ID field retries

- \* 68-pin leadless plastic package

## 1.3 ARCHITECTURAL OVERVIEW

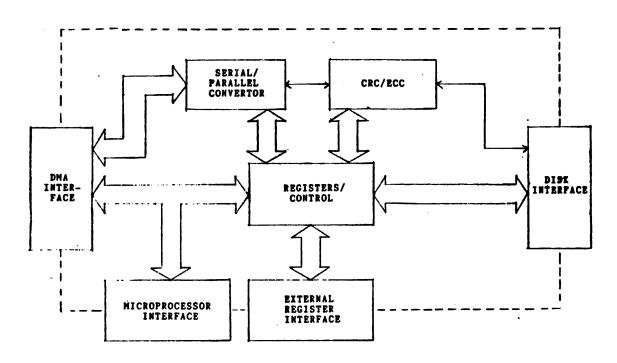

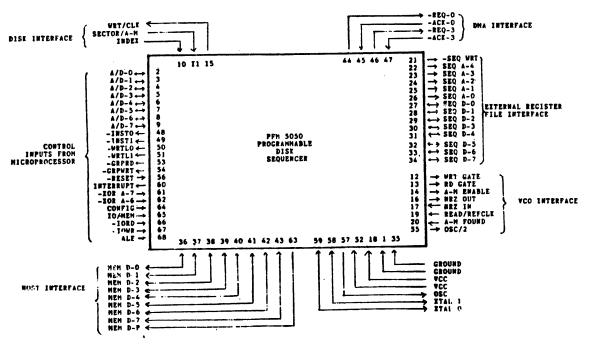

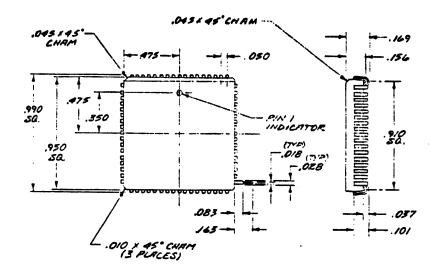

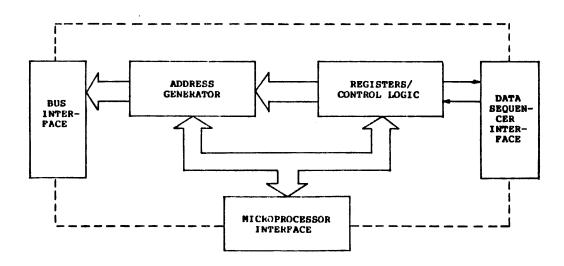

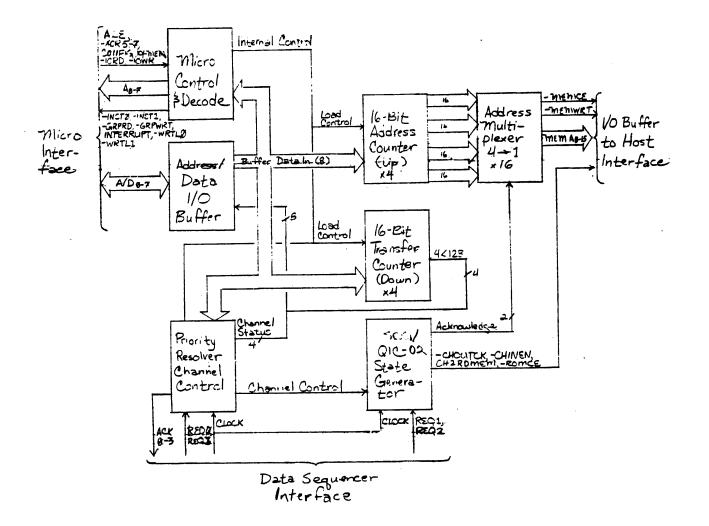

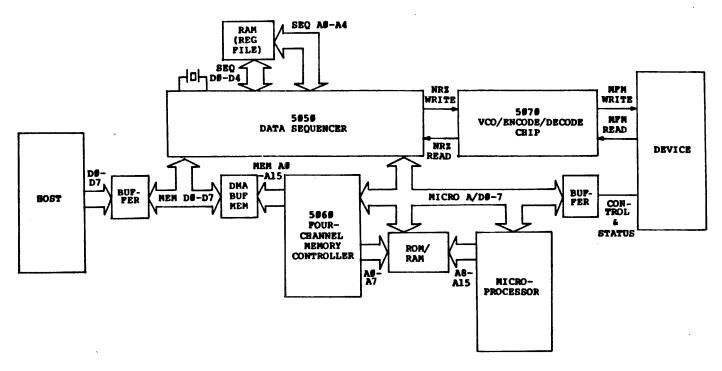

Figure 1 illustrates a conceptual block diagram of the PFM 5050 Data Sequencer, including the major logic blocks. There are three logic blocks entirely within the 5050; four additional blocks define the four external interfaces. The internal blocks are discussed below; the interfaces are discussed in Section 1.4. (For more information concerning details of the implementation, Figure 2 is provided, which includes pin inputs and outputs as well as logic blocks and internal data flow.)

Pigure 1. Conceptual Block Diagram

# 1.3.1 Registers/Control Logic

The Registers/Control block contains 32 8-bit internal control registers and associated control logic. The registers may be individually written to initialize the parameters that control data transfer, and individually read to obtain status information about command execution. Commands are issued to the 5050 by writing to these registers.

## 1.3.2 ECC/CRC Logic

The ECC/CRC logic generates and checks the ECC or CRC bytes appended to the ID and data fields. Bit 6 of WR12 governs whether the fixed CCITT standard CRC-16 polynomial  $(x^{16} + x^{12} + x^5 + 1)$  or the programmable ECC polynomial is appended to the ID field. The ECC polynomial is up to 64 bits in length (modulo 8 bits) and is determined at initialization time by values written into WR16-23.

Figure 2. Functional Block Diagram

# 1.3.3 Serial/Parallel Conversion Logic

Data to and from the disk device must be serial in form, while the host memory bus transfers data in byte-parallel form. The serial/parallel conversion logic is composed of high-speed shift registers which effect the necessary translation between serial and parallel data formats.

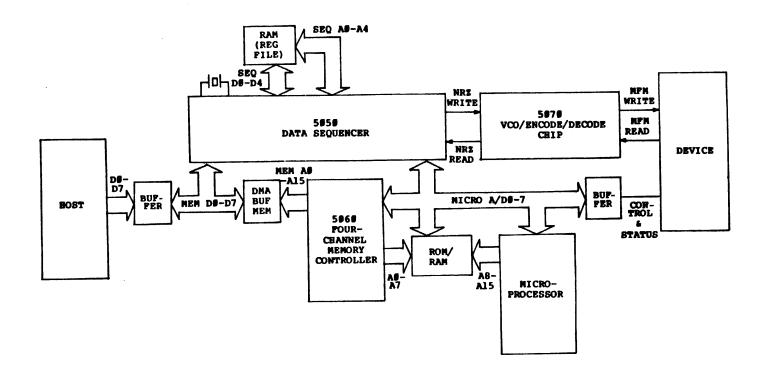

#### 1.4 SYSTEM CONFIGURATION

Illustrated below is a typical system configuration, incorporating the Data Sequencer, the 5060 Memory Controller, and the 5070 VCO/Encode/Decode chip.

Figure 3. Typical System Configuration

#### 1.4.1 Host Interface

Communication with the host is via an 8-bit bidirectional bus. The host interface block contains the logic to transfer data between the 5050 and the DMA buffer memory over this bus. The 5060 DMA Memory Controller provides the addresses in the buffer to which this data is to be transferred.

#### 1.4.2 Disk Interface

The disk interface block contains the logic necessary to drive the control and status lines of the disk itself. In addition, the serial data stream to and from the disk runs through this block.

## 1.4.3 Local Microprocessor Interface

This block contains the logic necessary to allow the local microprocessor to read or write the internal registers. An 8-bit bus connects this block to the register file.

## 1.4.4 External Register Interface

To provide greater flexibility in disk drive selection, 32 of the 64 read/write registers are not on the 5050 chip itself. These registers are located in an external RAM register file accessed via the external register interface block. (Drive select is thus simply a matter of indexing into the Register file containing the format parameters for the particular disk.)

## CHAPTER 2

#### FUNCTIONAL DESCRIPTION

#### 2.1 INTRODUCTION

The 5050's basic function is to translate serial data from a high-speed Winchester disk storage device into parallel bytes of data that are in turn sent to the 5060 Memory Controller for DMA to host memory. The 5050 can be initialized in many different ways to customize it to the unique hardware requirements of different disk drives. This initialization is performed by a program in the local microprocessor (as described in Appendix A) using the programmable Data Transfer Parameter registers of the 5050.

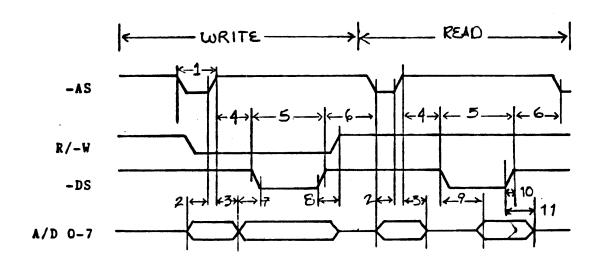

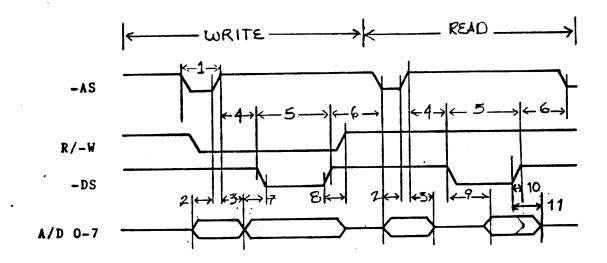

The 5050 is designed to be initialized by a microprocessor having the proper control lines (for example, a 28- or 8085/8051-type microprocessor). Depending on the microprocessor used, the timing and pin functions of the 5050 vary slightly. (See Chapter 3, Interfacing, for specific details.)

#### 2.2 REGISTERS

Registers on the PFM 5050 Data Sequencer are of two types: Data Transfer Parameter Registers, which are used to issue commands and return status information, and Format Parameter Registers, which are used to hold parameter-type information necessary for command execution. Both types of registers are individually addressable.

# 2.2.1 Data Transfer Parameter Registers

The Data Transfer Parameter registers are summarized in Table 1. Their addresses are contained in Table 2. Following the tables is a description of the individual bits in each of the registers.

Table 1. Data Transfer Parameter Registers

| Read | Register Functions        | Write | Register Functions                                            |

|------|---------------------------|-------|---------------------------------------------------------------|

| RRØ  | Status                    | WRØ   | Command Register                                              |

| RR1  | Extended Status           | WRl   | Sequencer Loop Count                                          |

| RR2  | Retry Count/State Address | WR2   | Index Time-Out                                                |

| RR3  | Flag Byte                 | WR3   | Sub-Block Count                                               |

| RR4  | Cylinder High             | WR4   | Cylinder High                                                 |

| RR5  | Cylinder Low              | WR5   | Cylinder Low                                                  |

| RR6  | Head/Flag                 | WR6   | Head Address                                                  |

| RR7  | Sector                    | WR7   | Sector                                                        |

| RR8  | Memory to Micro           | WR8   | Micro to Memory                                               |

| RR9  | Sequencer Loop Count      | WR9   | Sequencer Start/Re-Start                                      |

| RR10 | Not Used                  | WRlØ  | Sequencer Loop State                                          |

| RR11 | Not Used                  | WRll  | Bit Ring Start Count                                          |

| RR12 | Not Used                  | WR12  | ECC Control                                                   |

| RR13 | Not Used                  | WR13  | Configuration Control                                         |

| RR14 | Seq Count Reg @ Seq Start | WR14  | Seq Count Reg @ Seq Start                                     |

| RR15 | Seg Value Reg @ Seg Start | WR15  | Seq Value Reg @ Seq Start                                     |

| RR16 | Not Used                  | WR16  | Polynomial 0-7                                                |

| RR17 | Not Used                  | WR17  | Polynomial 8-15                                               |

|      | Not Used                  | WR18  | Polynomial 16-23                                              |

|      | Not Used                  | WR19  | Polynomial 24-31                                              |

| RR20 |                           | WR2Ø  | Polynomial 32-39                                              |

| RR21 | Not Used                  | WR21  | Polynomial 40-47                                              |

| RR22 | Not Used                  | WR22  | Polynomial 48-55                                              |

| RR23 | Not Used                  | WR23  | Polynomial 56-63                                              |

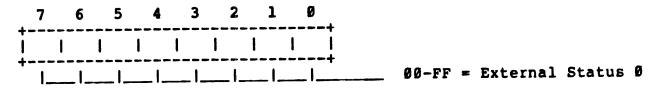

| RR24 | External Status Ø         | WR24  |                                                               |

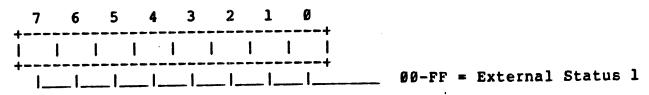

| RR25 | External Status 1         | WR25  |                                                               |

| RR26 | Not Used                  | WR26  | Not Used                                                      |

| RR27 | Micro-DMA Memory to Group | WR27  | Not Used                                                      |

| RR28 | External Group Strobe     | WR28  | Not Used Not Used External Group Strobe External Group Strobe |

| RR29 | External Group Strobe     | WR29  | External Group Strobe                                         |

| RR30 |                           | MKSB  | Exceller group arrone                                         |

| RR31 | External Group Strobe     | WR31  | External Group Strobe                                         |

Table 2. Data Transfer Parameter Register Map

| AD5 | AD4 | AD3 | AD2 | ADl | ADØ | Write    | Read     |

|-----|-----|-----|-----|-----|-----|----------|----------|

| 1   | Ø   | 0   | 0   | 0   | Ø   | WRØ      | RRØ      |

| ī   | Ø   | Ø   | Ø   | Ø   | 1   | WRl      | RRl      |

| ī   | Ø   | Ø   | Ø   | ì   | Ø   | WR2      | RR2      |

| ī   | Ø   | Ø   | Ø   | ī   | ī   | WR3      | RR3      |

| ī   | Ø   | Ø   | ī   | Ø   | Ø   | WR4      | RR4      |

| ī   | Ø   | Ø   | ī   | Ø   | ī   | WR5      | RR5      |

| ī   | Ø   | Ø   | ū   | ī   | Ø   | WR6      | RR6      |

| ī   | ø   | Ø   | ī   | ī   | ī   | WR7      | RR7      |

| ī   | ø   | 1   | Ø   | Ø   | Ø   | WR8      | RR8      |

| ī   | Ø   | ī   | Ø   | Ø   | ī   | WR9      | RR9      |

| ī   | Ø   | ī   | Ø   | ī   | Ø   | WR10     | NOT USED |

| ī   | Ø   | ī   | Ø   | ī   | 1   | WR11     | NOT USED |

| ī   | Ø   | 1   | 1   | Ø   | Ø   | WR12     | NOT USED |

| ī   | Ø   | ī   | 1   | Ø   | 1   | WR13     | NOT USED |

| ī   | 0   | ī   | ī   | 1   | Ø   | WR14     | RR14     |

| ī   | 0   | ī   | ī   | ī   | 1   | WR15     | RR15     |

| ī   | ī   | Ø   | Ø   | 0   | Ø   | WR16     | NOT USED |

| ī   | ī   | ø   | Ø   | Ø   | 1   | WR17     | NOT USED |

| ī   | ī   | ø   | Ø   | ī   | Ø   | WR18     | NOT USED |

| ī   | ī   | ø   | Ø   | ī   | 1   | WR19     | NOT USED |

| ī   | ī   | Ø   | 1   | Ø   | Ø   | WR20     | NOT USED |

| ī   | ī   | Ø   | ī   | 0   | 1   | WR21     | NOT USED |

| ī   | ī   | Ø   | ī   | ī   | Ø   | WR22     | NOT USED |

| ī   | ī   | Ø   | ī   | ī   | ì   | WR23     | NOT USED |

| ī   | ī   | ī   | Ø   | Ø   | 0   | WR24     | RR24     |

| ī   | ī   | ī   | Ø   | Ø   | 1   | WR25     | RR25     |

| ī   | ī   | ī   | Ø   | 1   | 0   | NOT USED | NOT USED |

| ī   | ī   | ī   | Ø   | ī   | 1   | NOT USED | RR27     |

| ī   | ī   | ī   | ĭ   | X   | X   | WR28     | RR28     |

| ī   | ī   | ī   | ī   | X   | X   | WR29     | RR29     |

| ī   | ī   | ī   | ī   | X   | X   | WR30     | RR30     |

| ī   | ī   | ī   | ī   | X   | X   | WR31     | RR31     |

|     |     |     |     |     |     |          |          |

X = don't care

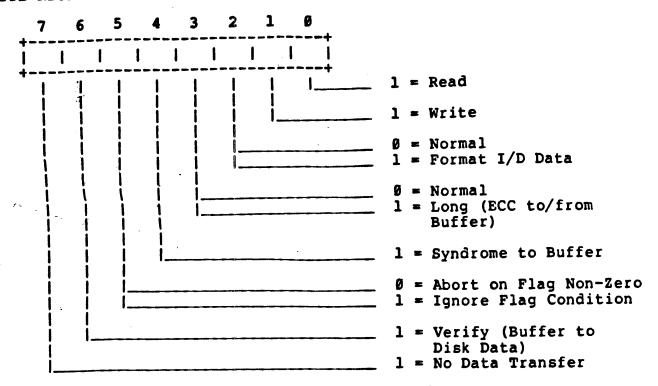

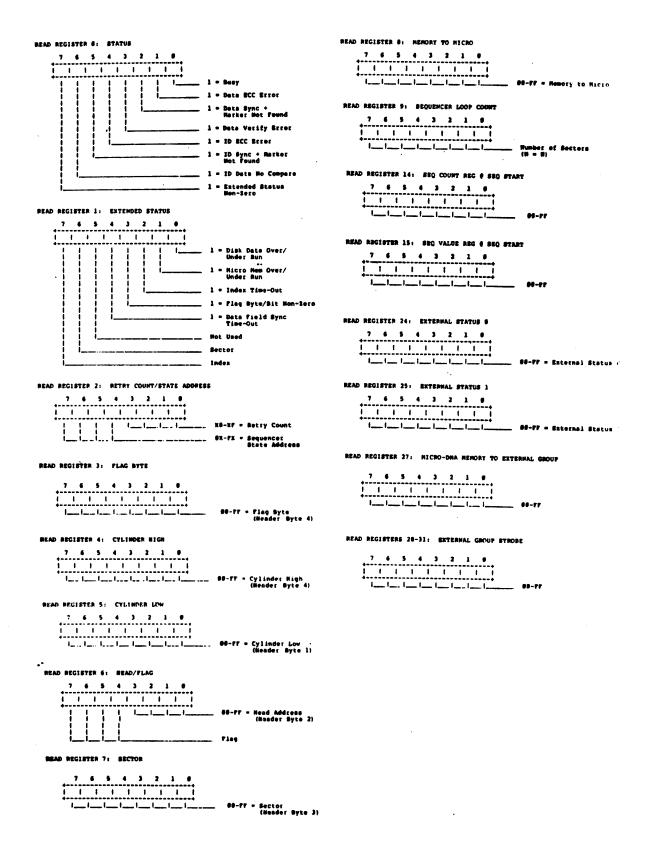

## WRITE REGISTER Ø: COMMAND

The Command register contains 5050 commands and command options.

Bits 0 and 1 determine whether the operation is a read or a write. When bit 0 is set, data is read from the disk to the buffer; when bit 1 is set, data is written from the buffer to the disk.

When bit 2 is set, and the operation is a read, only ID fields will be read to the buffer. In the case of write operations, the entire track will be formatted, i.e., both the ID and data fields will be written to the disk. In this case, the ID information is read from the buffer, and data information is read from the sequencer's Register File at State 11, with the number of requests for each ID determined by the Count register.

When bit 3 is set, both the data and the ECC check bits will be written to or read from the buffer.

When bit 4 is set, the syndrome (the result of the ECC check) will be written to the buffer.

Bit 5 allows processor intervention on all flag conditions. Normally, this bit is clear, i.e., reads and writes to sectors with a flag condition will cause the command to be aborted and the FLAG BYTE/BIT NON-ZERO bit of the Extended Status register to be set. However, having determined the cause of the error, the microprocessor may decide to read or write the sector anyway, in which case it sets this bit.

When bit 6 is set, data is read from the buffer, and the sequencer performs a byte-by-byte comparison with data on the disk.

Bit 7 permits data fields to be read and checked for errors without transfer of the data to the buffer.

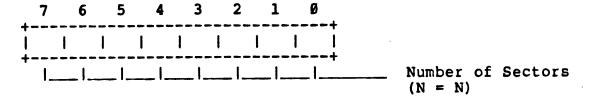

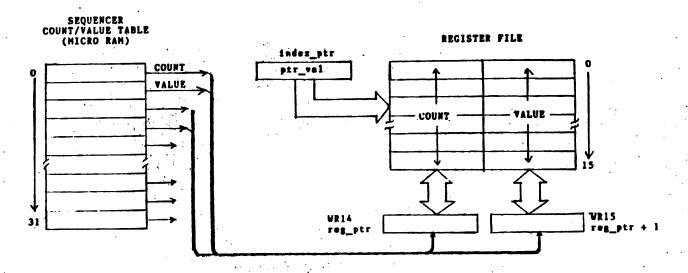

WRITE REGISTER 1: SEQUENCER LOOP COUNT

This register specifies the number of sectors to be read or written, or in the case of a format command, the number of sectors on the disk. (Actually, the value in this register specifies the number of times the loop in the predefined state sequence for the particular command is executed, as explained in Section 3.2.) This value is decremented for each sector handled by the command. An internal count register contains the initial value of this register, so that for repeated commands involving the same number of sectors, the register will be automatically reloaded with the proper value.

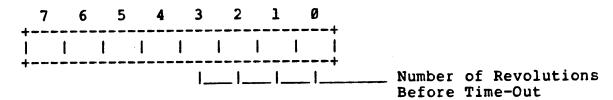

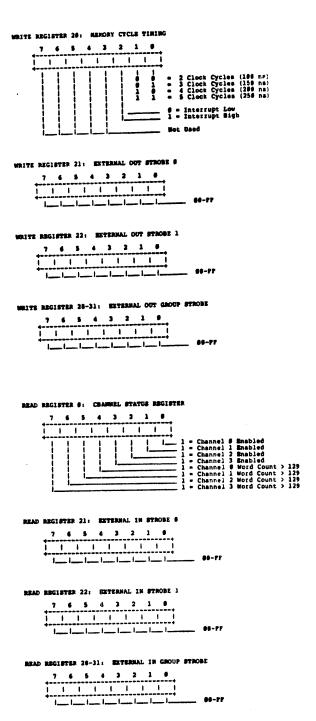

WRITE REGISTER 2: INDEX TIME-OUT

This register specifies the number of disk revolutions (as measured by the number of index pulses) before time-out. Thus, the number of automatic retries per command attempted by the sequencer may be from 2 to 15.

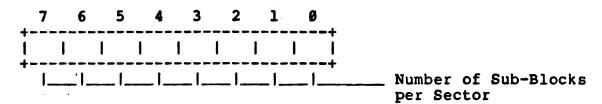

WRITE REGISTER 3: SUB-BLOCK COUNT

This register specifies the number of sub-blocks per sector. The total bytes per sector is equal to this value times the data field count; thus, the sector size may be as large as 65K bytes.

WRITE REGISTER 4: CYLINDER HIGH

This register contains the most significant eight bits of the desired cylinder number. This value is used in conjunction with the Cylinder Low register, specifying a range of 0 to 65535.

WRITE REGISTER 5: CYLINDER LOW

This register contains the least significant eight bits of the desired cylinder number.

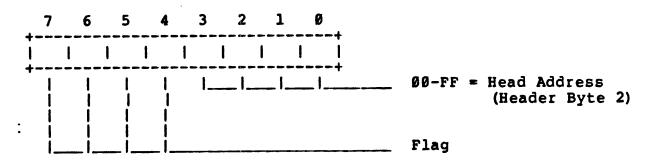

WRITE REGISTER 6: HEAD ADDRESS

This register contains the address of the read/write head accessed by the command.

WRITE REGISTER 7: SECTOR NUMBER

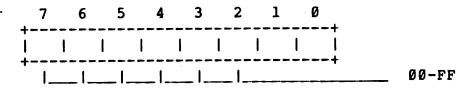

|   | •     | • | _ | _ | 3 |   |   | ا ــــــــــــــــــــــــــــــــــــ | 9<br> |       |

|---|-------|---|---|---|---|---|---|----------------------------------------|-------|-------|

| • | 1     | 1 |   | ı | 1 | 1 | 1 | ı                                      | i     |       |

| • | :<br> |   |   |   |   |   |   |                                        |       | 00-FF |

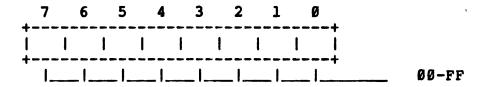

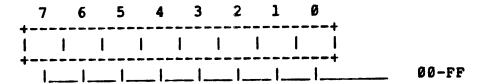

This register specifies the sector number to be read or written. It is a counter register that is auto-incremented at the end of a data field operation.

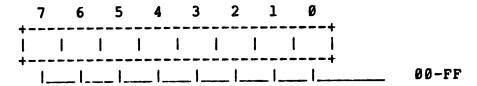

WRITE REGISTER 8: MICRO TO MEMORY

This register contains data to be transferred from the microprocessor to DMA buffer memory.

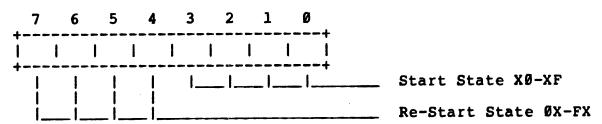

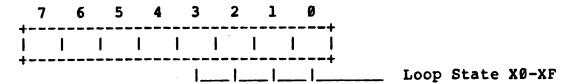

WRITE REGISTER 9: SEQUENCER START/RE-START

During the execution of a command, bits 0-3 specify the state number at which the sequencer will begin execution; bits 4-7 specify the state number from which the sequence will be re-started after the state number specified in WR10 has been reached (and RR1 does not equal 0).

For purposes of initializing the Register File, bits 0-3 are used as an index into the Register File; data contained in WR14 or WR15 will be written to a Count or Value register, respectively.

WRITE REGISTER 10: SEQUENCER LOOP STATE

This register determines the state number of the LOOP mode, at which a jump to the RE-START mode is performed. This value will, of course, depend on the command and the particular disk configuration.

WRITE REGISTER 11: BIT RING START COUNT

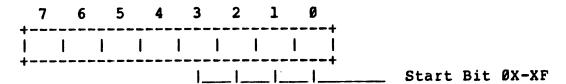

This register allows the user to specify the bit-level timing relationship between sync detect and byte clock (see Figure 4). The value in this register is the ring counter start state for a four-bit ring counter.

Figure 4. Sync Detect and Byte Clock Timing

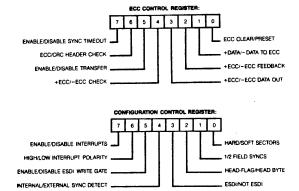

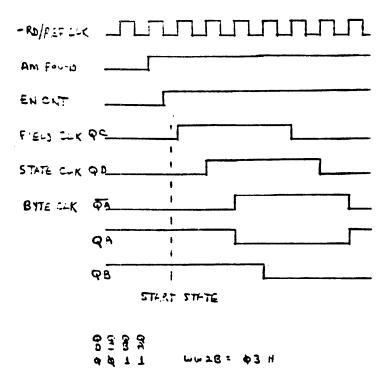

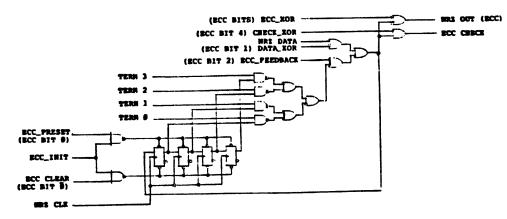

# WRITE REGISTER 12: ECC CONTROL

This register allows format and media compatability with a variety of peripheral chips and various error correction formats.

Bit Ø determines whether or not initialization of the shift register string is cleared (to all zeros) or preset (to all ones).

Bits 1-4 control XOR gates, which determine the polarity of the data at various stages in the ECC check logic. Figure 5 illustrates these gates in relation to the relevant ECC circuits.

Figure 5. XOR Gate Circuit Diagram

Bit 5, when set, enables the auto-read DMA write function, in which data is transferred from an external peripheral chip to DMA buffer memory via RR31.

When bit 6 is cleared, ID information is the fixed CCITT CRC-16 polynomial, rather than the preprogrammed data field polynomial (as specified in WR16-27).

When bit 7 is set, and an ID field has been properly read, failure to find the data field sync after 512 bit times will result in a data field sync time-out.

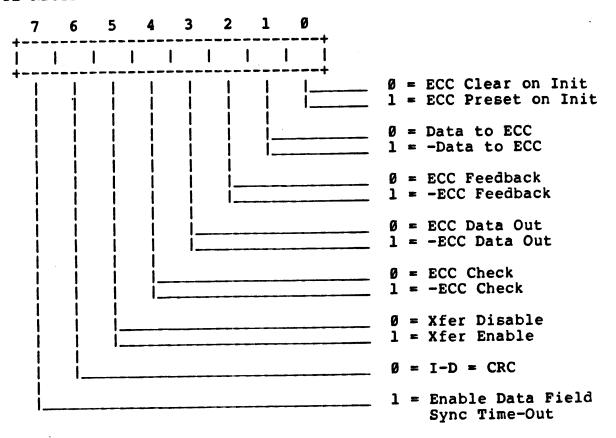

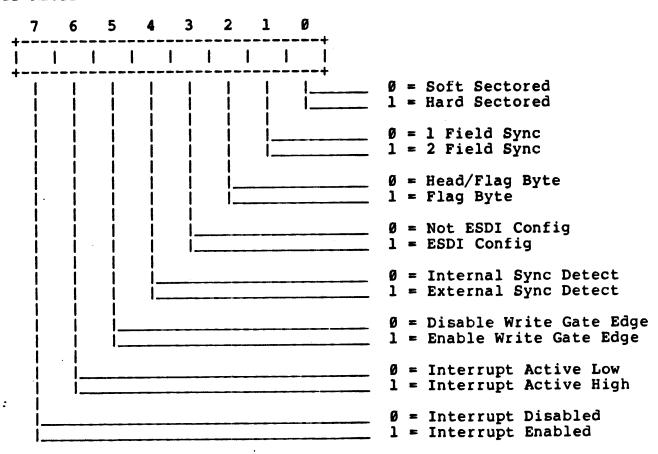

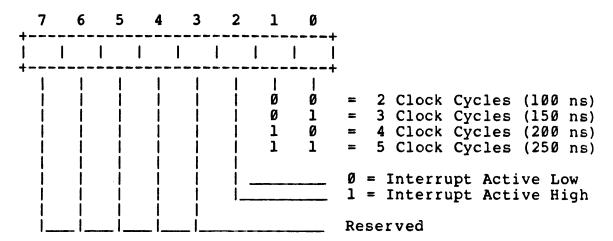

#### WRITE REGISTER 13: CONFIGURATION CONTROL

Bit 0 selects between the hard sector and soft sector disk drive environments.

Bit 1 selects between the 1 field sync (hard sector) and 2 field sync (soft sector) formats.

Bit 2 selects between the Head/Flag Byte (RR6) and the Flag Byte (RR3).

Bit 3 selects between an ESDI and a non-ESDI interface.

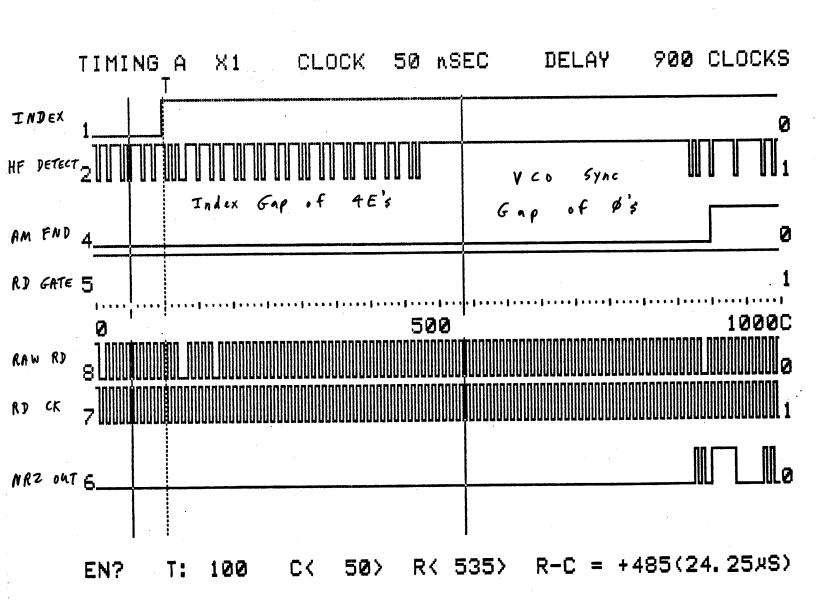

Bit 4 selects between internal sync detect (used for hard sector and ESDI-type interfaces) and external sync detect (used when the sequencer is configured with the VCO/Encode/Decode chip).

Setting bit 5 disables the write gate for two bit times preceding each data field preamble, thereby providing an edge of write gate for every PLO sync field as required by ESDI-type drives.

Bit 6 selects between interrupt active Low or High.

Bit 7 enables or disables interrupts.

WRITE REGISTER 14: SEQ COUNT REG @ SEQ START

This register is used, in conjunction with WR9, to select a Count register in the Register File.