#### 1. INTRODUCTION

The LC8950 and LC8951 Real-Time Error Correction and Host Interface Processors (RCHIP) are dedicated single-chip LSIs for use in CD-ROM (Mode 1) and CD-I (Mode 2, Forms I and 2) disc formats. The LC8951 is hardware and software compatible with the LC8950. The differences in functionality between the two chips is described in appendix E.

The LC8950 RCHIP performs real-time data decoding (error detection and correction) and implements the host interface, which incorporates a first-in first-out (FIFO) command buffer suitable for Small Computer System Interface (SCSI) applications.

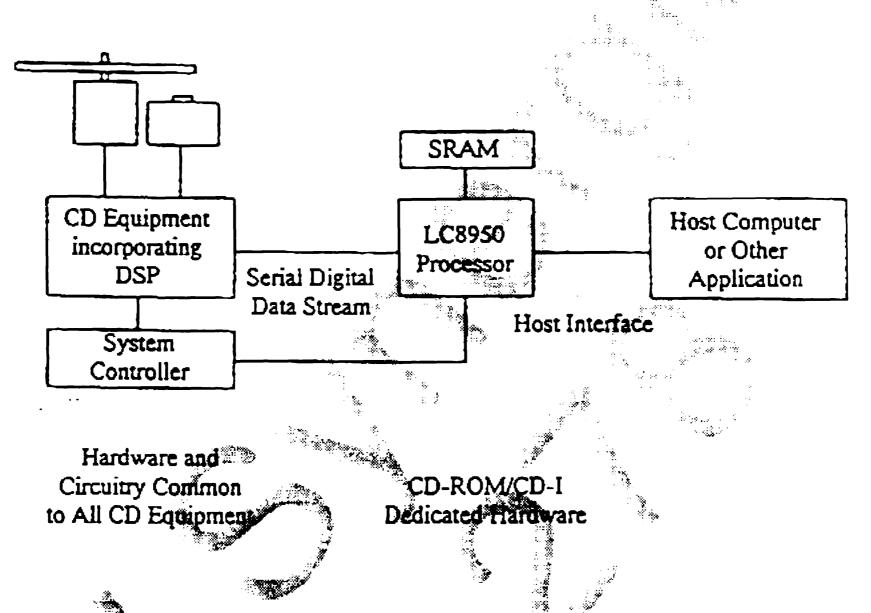

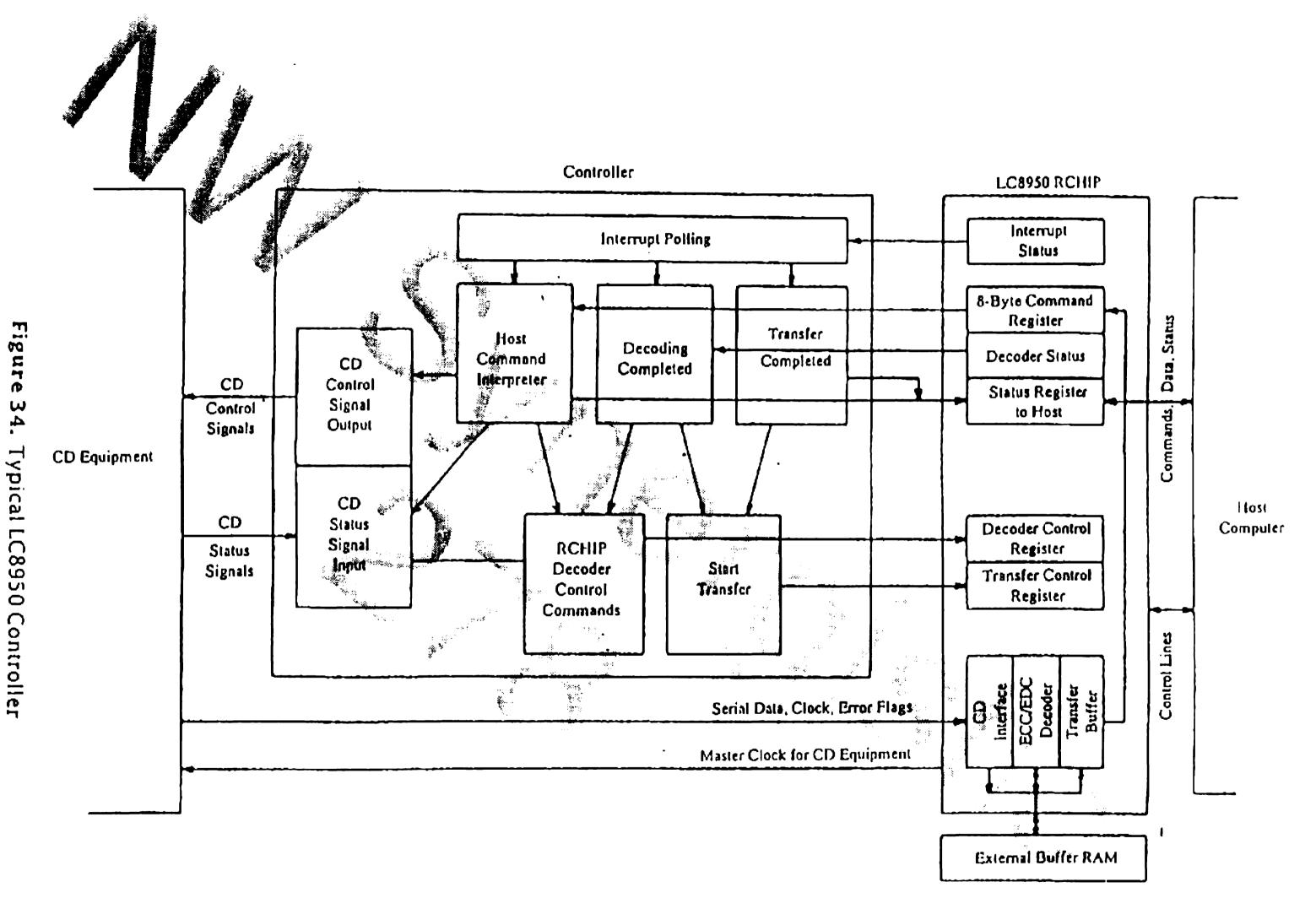

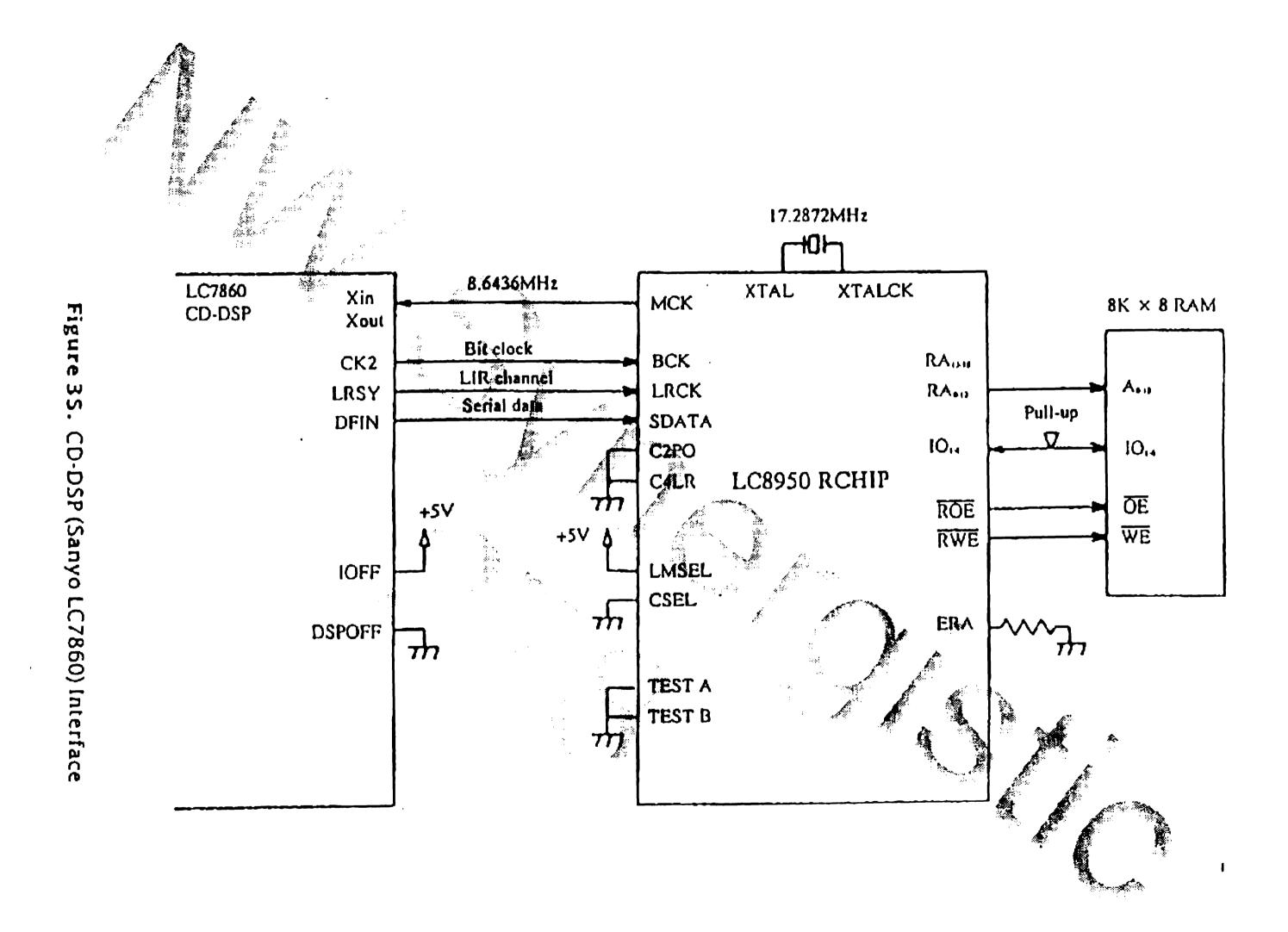

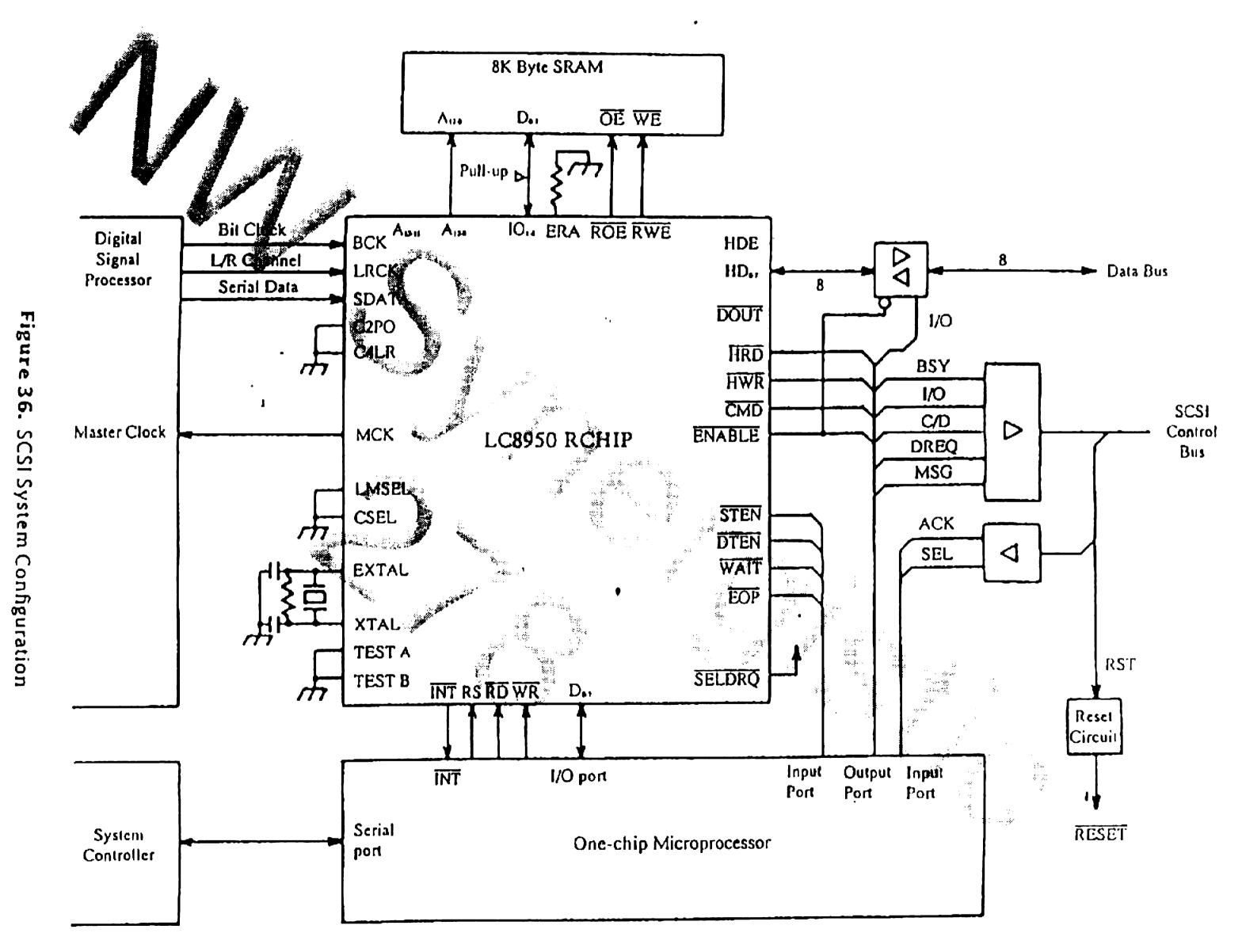

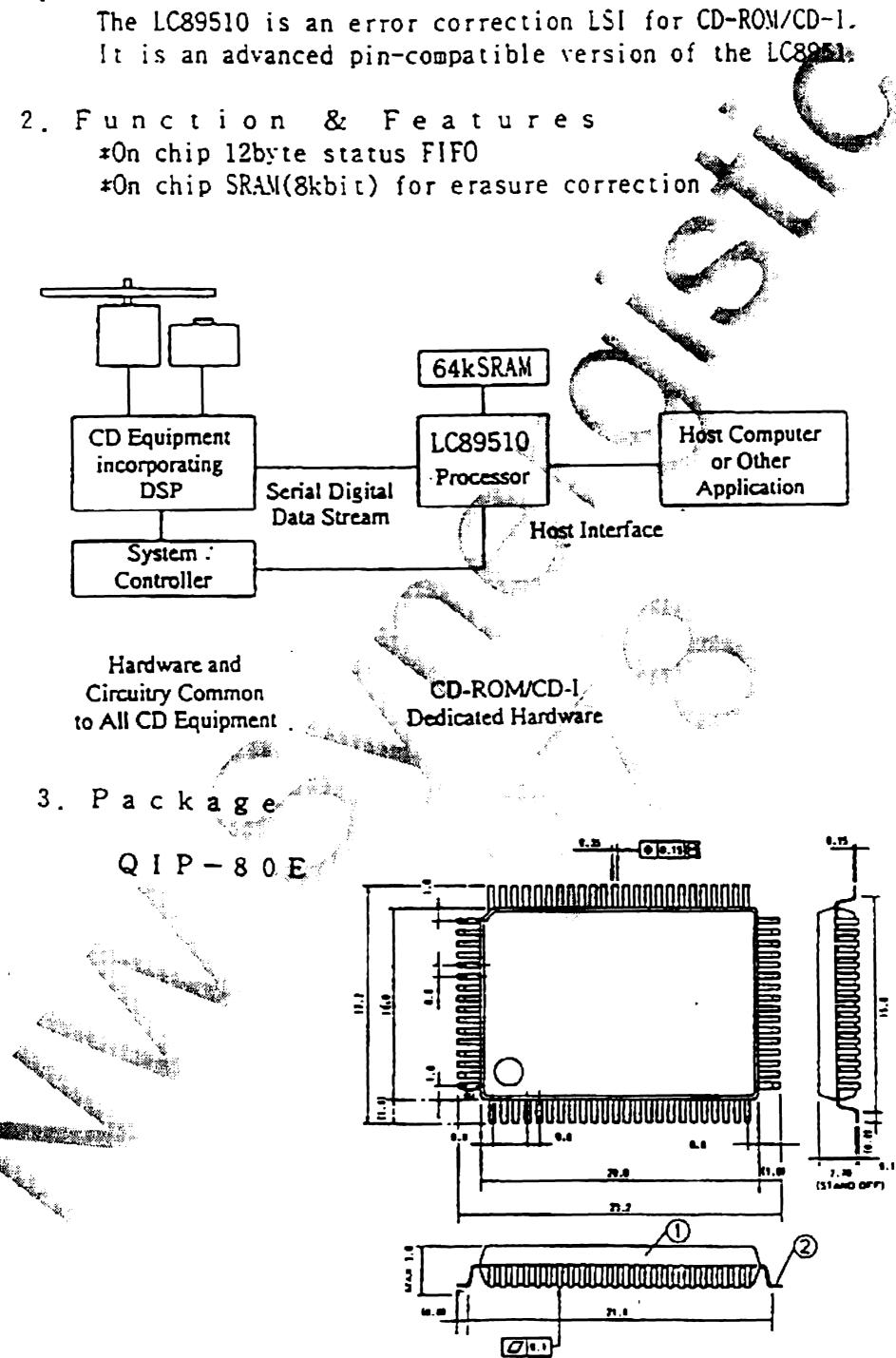

The following figure shows a typical system implementation for a CD-ROM disc drive using the LC8950.

Figure 1. Typical System Implementation

As the LC8950 RCHIP eliminates many of the discrete ICs or gate arrays and additional software control provisions previously required by implementing their in hardware. The net result is faster product design and development cycles, better cost-efficiency and smaller equipment size, as well as improved functionality and reliability.

The LE8950 RCHIP processor is designed to be used with an external controller and external data buffer. This distributed architecture allows both controller and control parameters to be defined during product development, ensuring that the device can be easily incorporated into existing and future applications.

The LC8950 RCHIP is fabricated using a low-power CMOS process, operates on a standard single +5 V power supply, and is available from stock in 80-pin plastic flatpacks.

#### 1.1 Features

- Suitable for both CD-ROM (Mode 1) and CD-I (Mode 2, Forms 1 and 2) disc formats

- All dedicated CD-ROM/CD-I functions provided on-chip

- Real-time error detection and correction in hardware without controller intervention using pipeline processing architecture

- Transparent design separates command functions from hardware control

- · Host system sees decoded data only in final error-free form

- Burst data transfers of up to 2.3 MB/s to host computer

- Multi-block catching (transfer data buffering) accommodates low readspeed hosts.

- Support for real-time erasure correction, detect-and correct algorithms and CRC error detection, without interruption of host data transfers.

- Host interface incorporates FIFO command buffer sultable for SCSI applications.

- Single-chip LSI

- Low-power CMOS process

- Single +5 V power supply

- Available in 80-pin plastic flatpacks

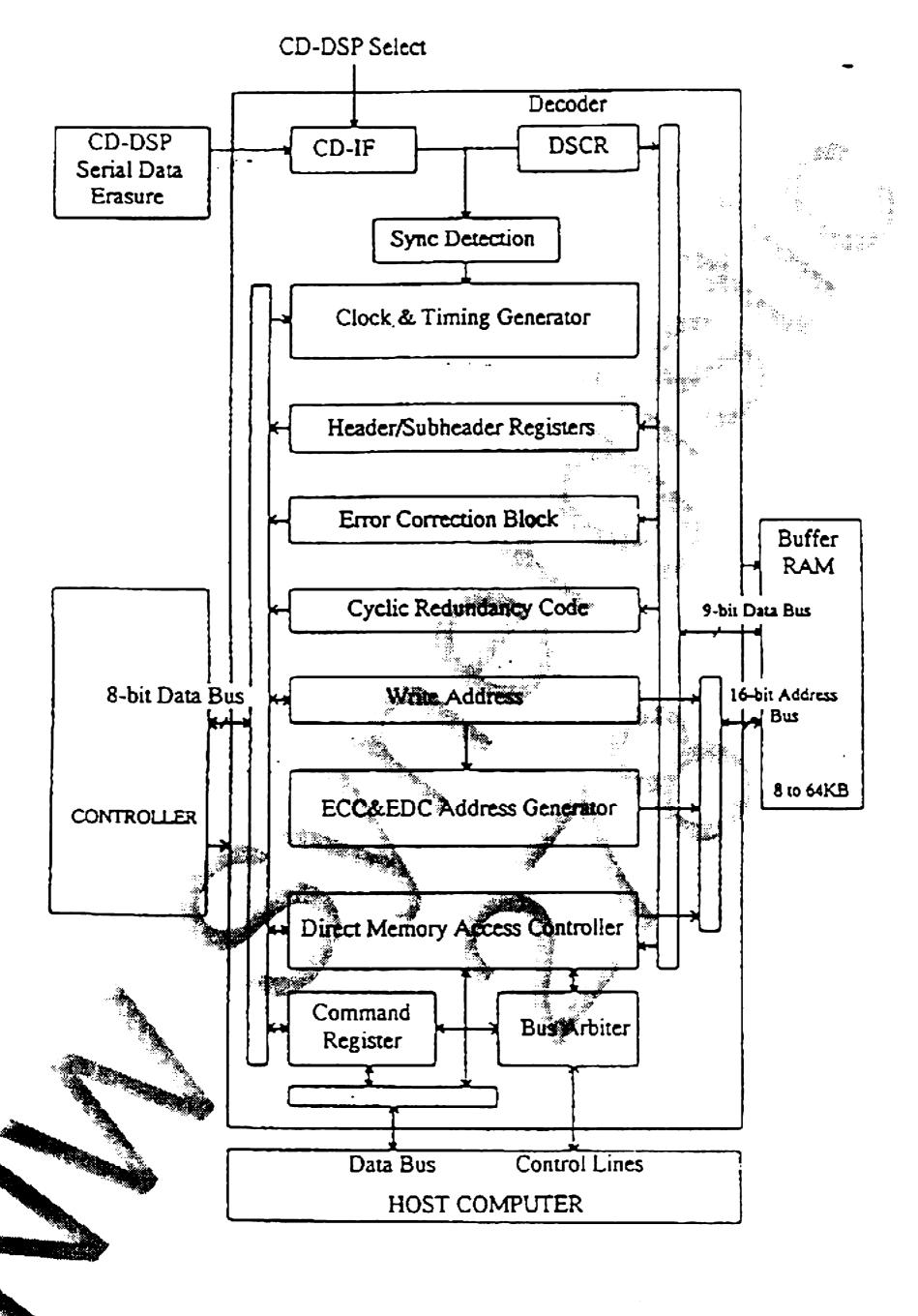

## 2. BLOCK DIAGRAM

igure 2. LC8950 Real-Time Error Correction and Host Interface Processor

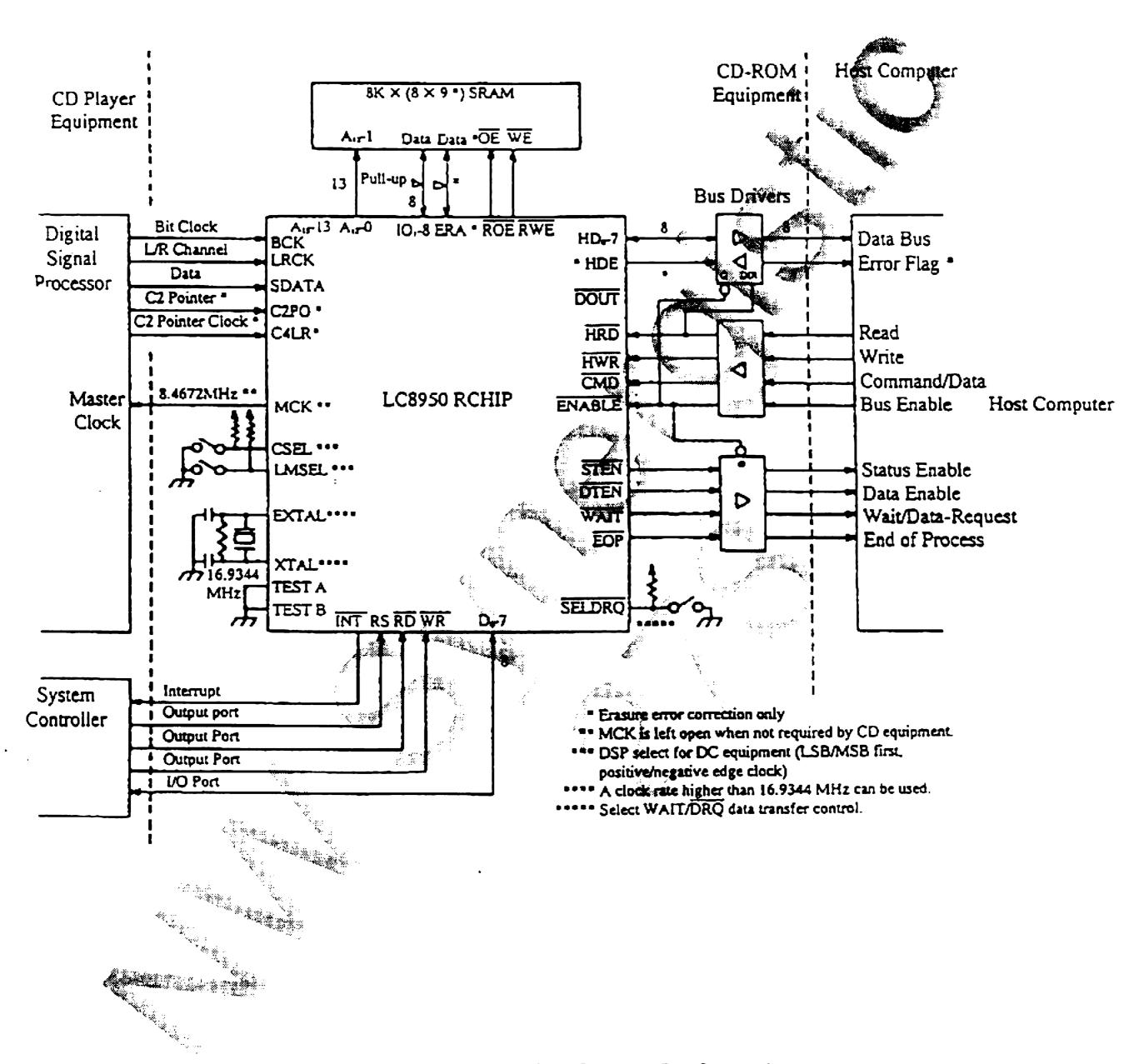

### 3. SYSTEM CONFIGURATION

Figure 3. LC8950 System Configuration

## 4. FUNCTIONAL OVERVIEW

Data input, decoding and data transfer in the LC8950 RCHIP take place simultaneously and in parallel using a pipeline architecture. These operations proceed in real time under synchronous clocking, without the intervention of the external controller.

The LC8950 is divided into three functional blocks.

- Data-input block

- Error-correction block, and

- Host-interface block

The operation of each of these blocks is described in detail below

#### 4.1 Data-Input Block

This section of the LC8950 interfaces with the serial data of the digital signal processing (DSP) unit in the CD equipment.

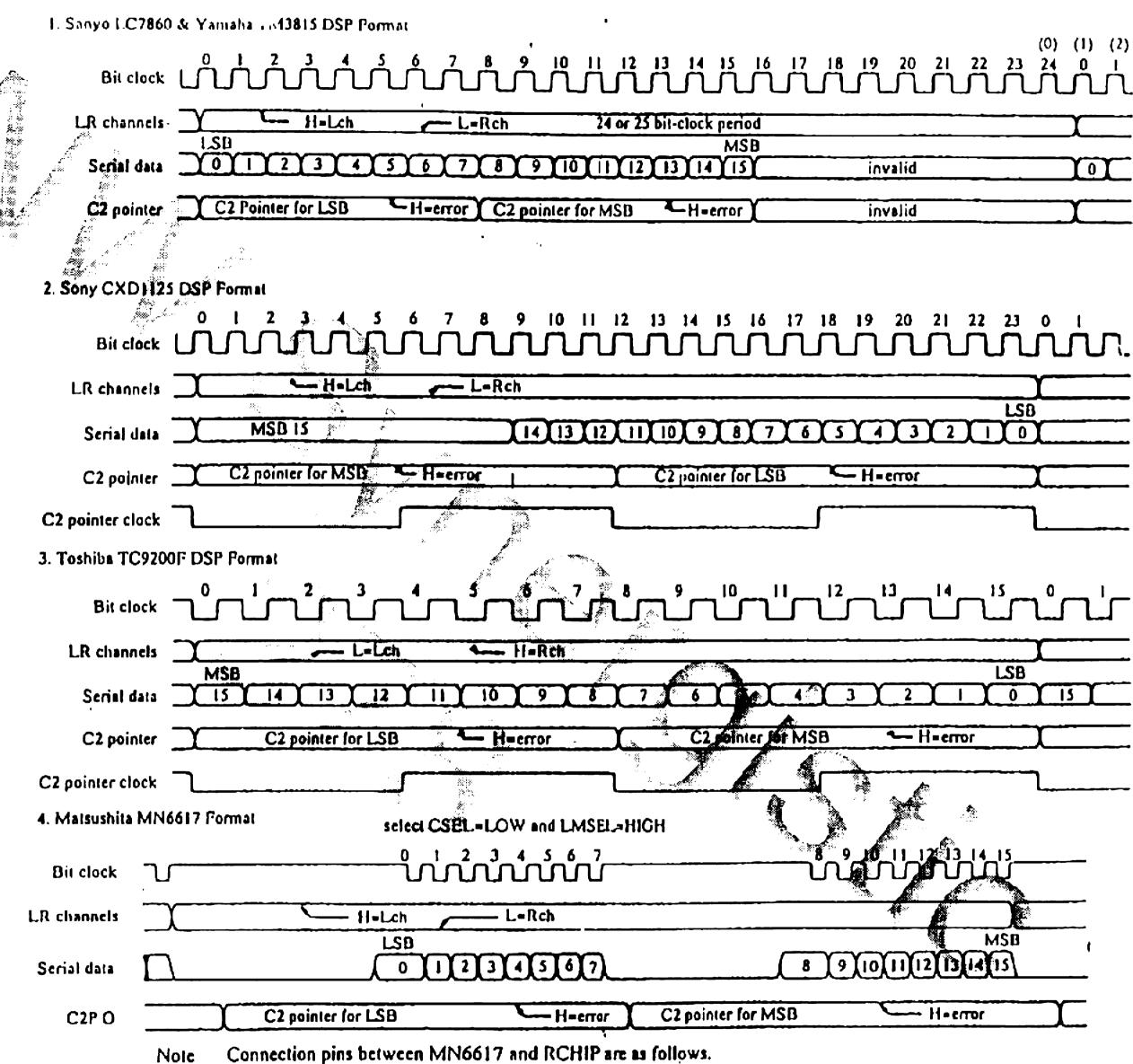

The LC8950 data input interface can be easily adapted to a variety of CD equipment. Simply by setting the CSEL and LMSEL pins, the equipment developer can select one of three serial data input formats.

The LC8950 synchronizes on-chip operations with the incoming data stream by detecting the sync patterns at the head of every data block. Programmable functions for pattern recognition and sync protection can be turned on and off as required.

Once detected, input data pass through a decoder and are written to a 64 Kbytes (max.) data buffer, together with the C2 pointer (error flag) received from the CD equipment. The entire 2352 bytes of data in each block, including the sync pattern, header, subheader and parity data, are written continuously into the data buffer, 🕬 🛣

When the C2 pointer is enabled, the RAM data buffer can be configured for 9-bit words; when disabled, an 8-bit RAM architecture can be selected. However, inhibiting the C2 pointer disables the player's double error-correction function.

The LC8950 also has a master clock output (MCK) which can be connected to the clock input of the digital signal processor on the CD equipment. As the clock signal to MCK passes through a binary prescaler, the clock frequency for the LC8950 should normally be set at twice that required for the CD-DSP clock signal.

#### 4.2 Error-Correction Block

The LC8950 carries out error detection and correction in real time, immediately after a 2352-byte block has been written to the data buffer. Incoming data is corrected and sent to the host computer with no drop in data transfer rate. A simple detect-and-correct algorithm, which does not use error flags, can correct one symbol error per codeword.

The LC8950 error-correction block can also examine the C2 pointer and erase error bytes flagged by the CD equipment. When erasure correction is

enabled, two symbol errors per codeword can be corrected. Erasure error correction is also performed in real time without degrading data throughput.

This correction algorithm is programmable, and can be instructed to perform repeated or QP/PQ correction strategies to achieve higher data reliability.

The LC8950 decodes the error-correcting code. Error-detection code is used with a 32-bit cyclic redundancy code (CRC) to check errors still remaining in the current block. During these operations, the header and subheader data are stored in separate registers for use by the controller.

A decoding-complete interrupt is sent to the controller when the CRC check is completed and the current data block is ready for transfer to the host. The remaining in the current block, controller can then read out the header and subheader data, the address of the block head in the data buffer, and the status information about the decoded data.

#### 4.3 Host-Interface Block

The host interface allows data transfers in bursts at up to 2.3 MB/s. In addition, a data buffer of up to 64 Kbytes can be allocated, allowing the LC8950 to cache up to 27 decoded data blocks. This buffer can also be implemented as a disc cache memory for CD-ROM drive applications.

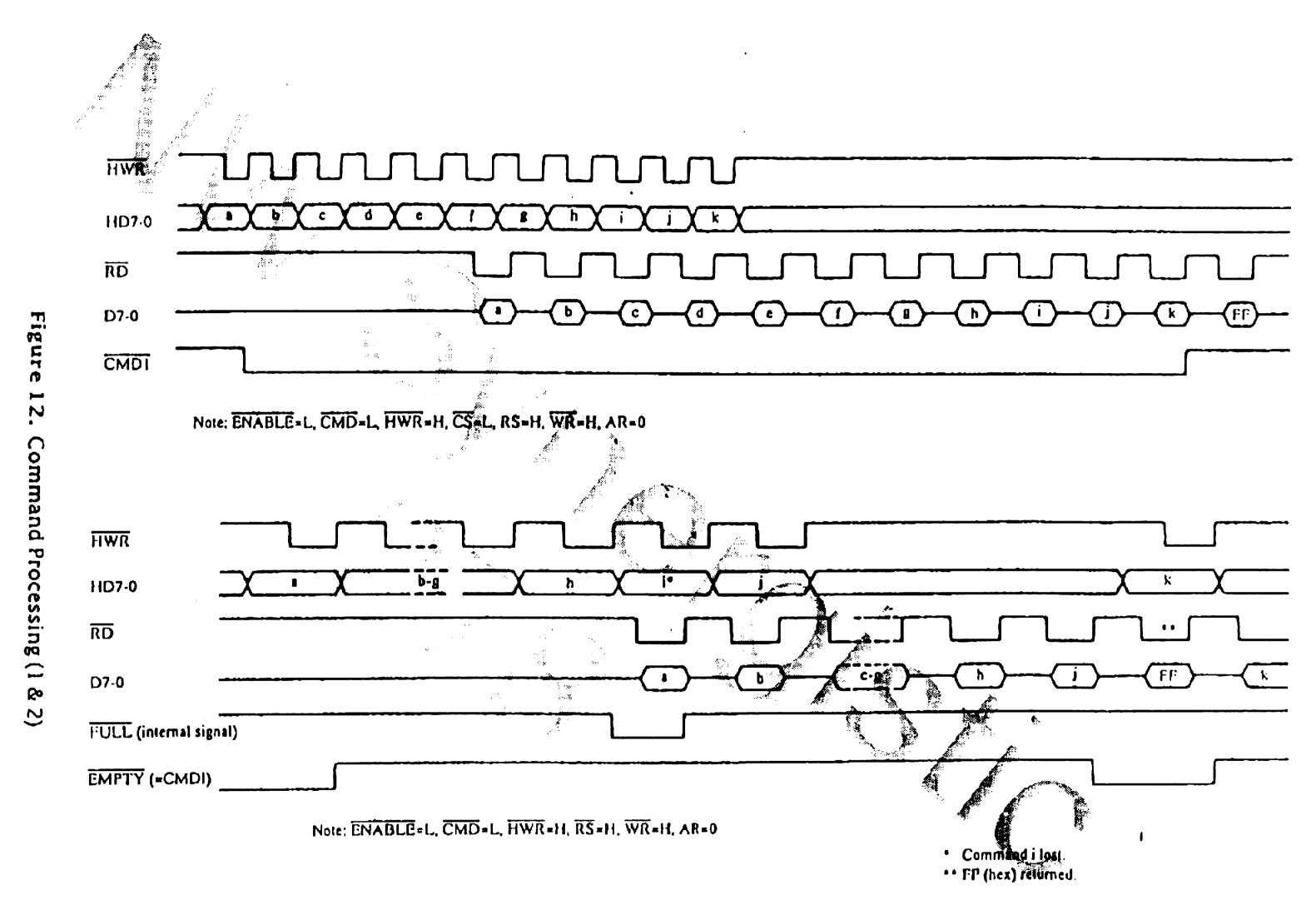

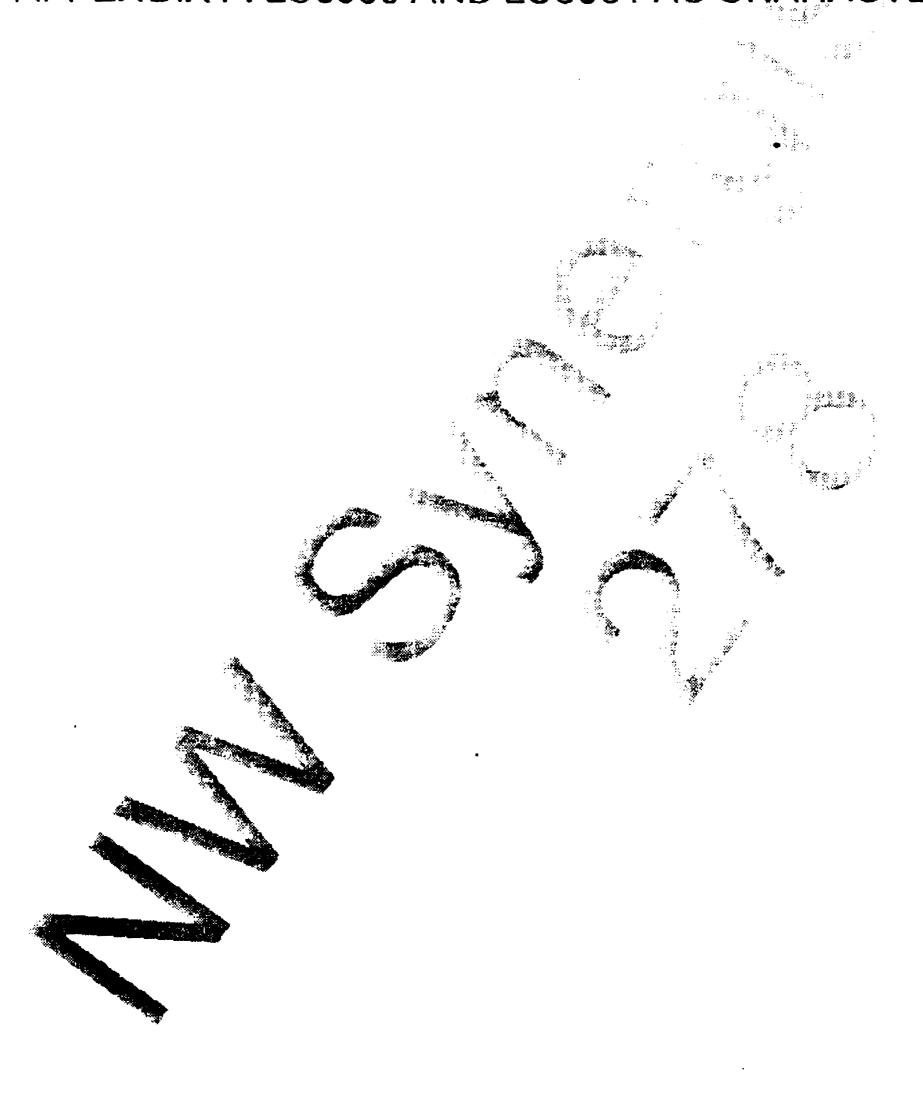

The host interface also has a built-in 8-byte FIFO command buffer to receive instructions from the host computer. When the host signals the LC8950 using the HWR pin, command bursts of up to eight bytes in length can be written to the buffer. When the host writes to the command buffer, the LC8950 sends a command interrupt to the controller. Note, however, that the LC8950 itself does not interpret commands written to the command buffer.

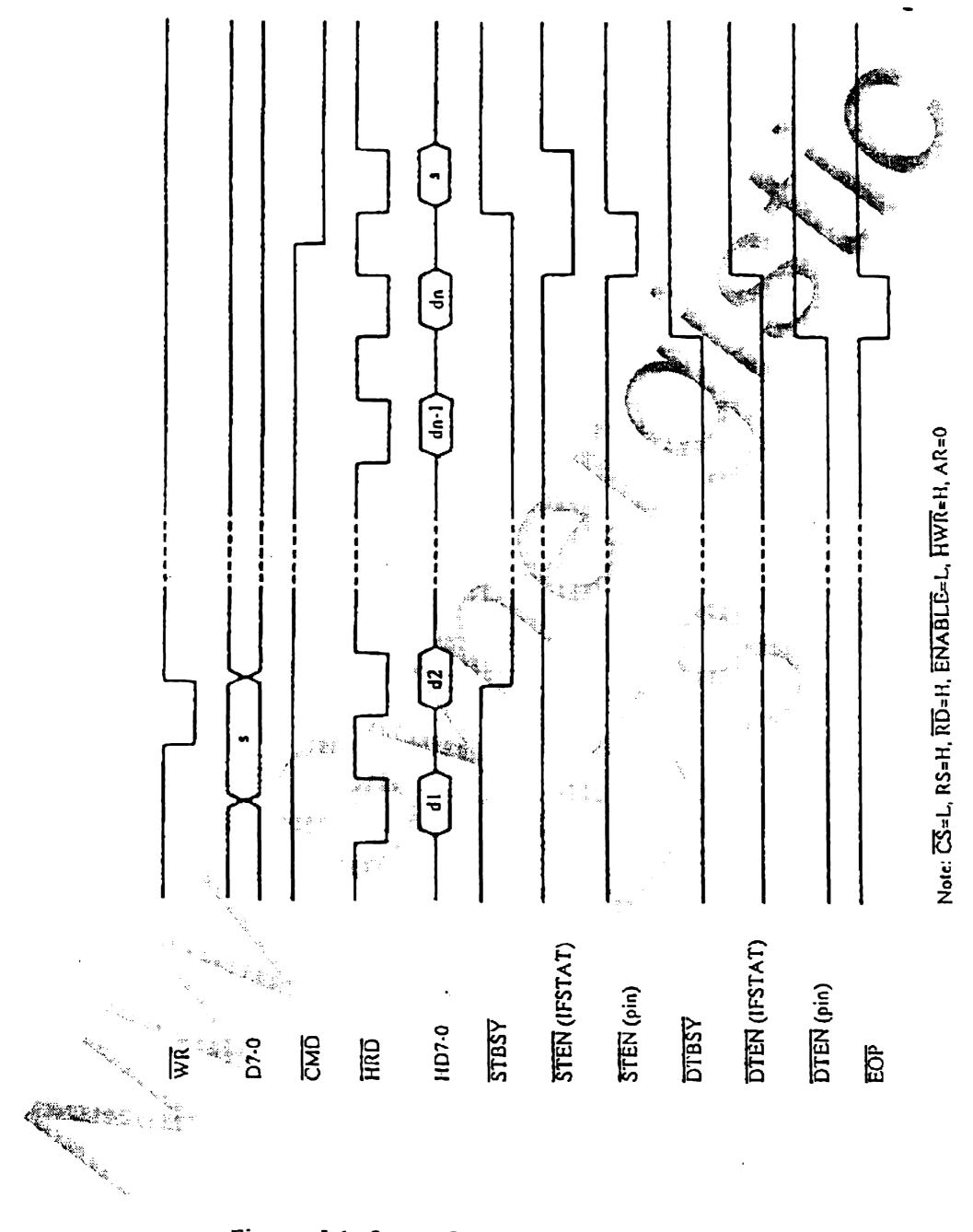

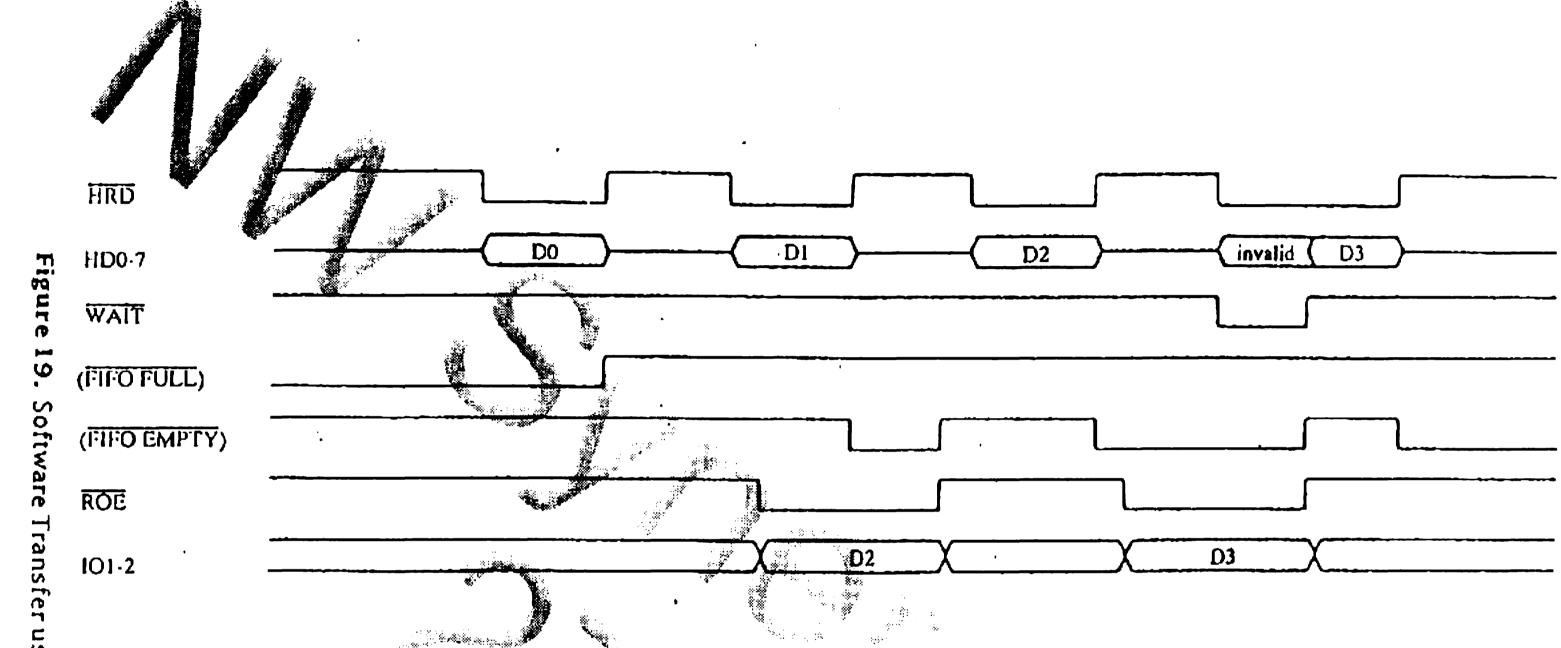

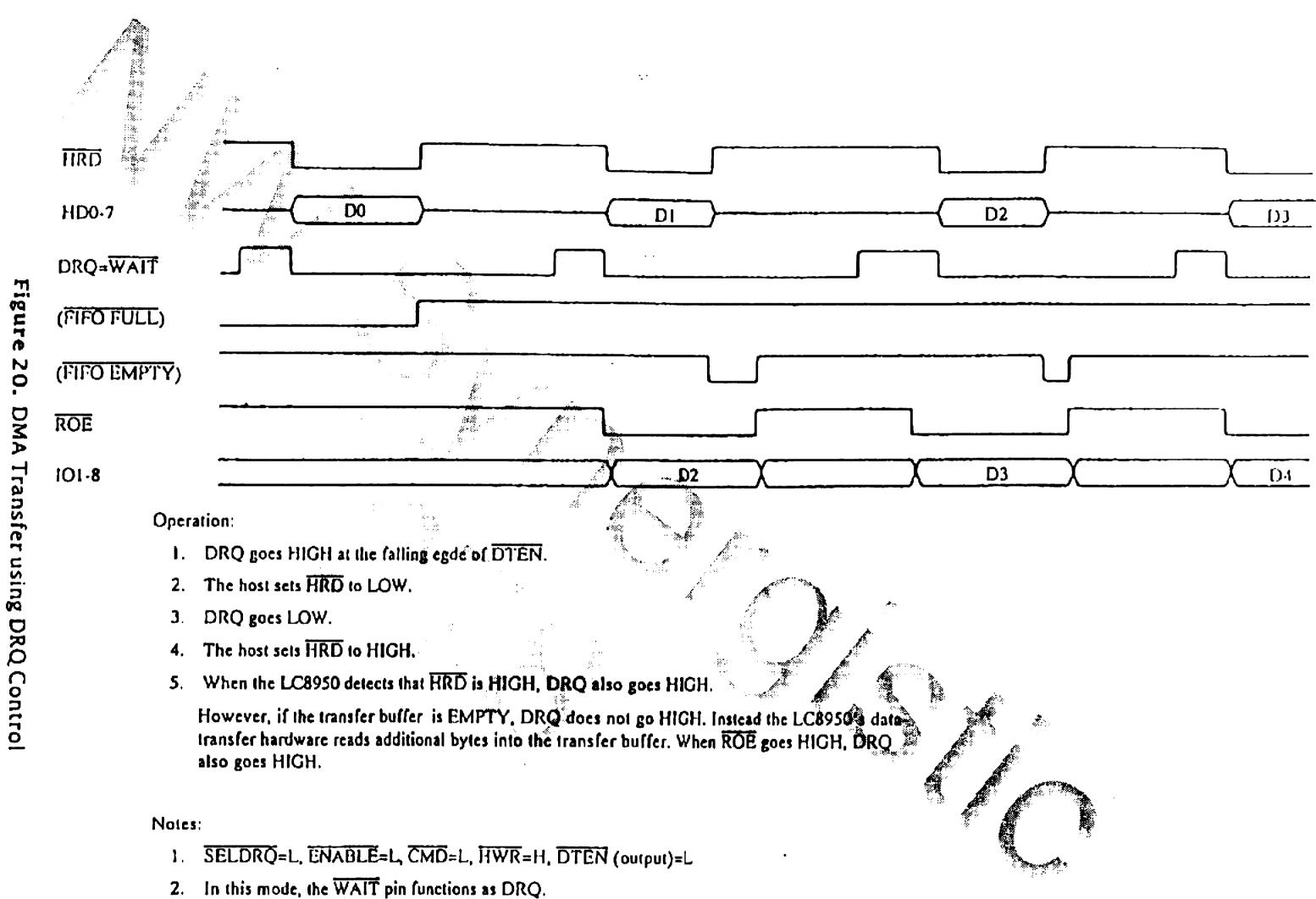

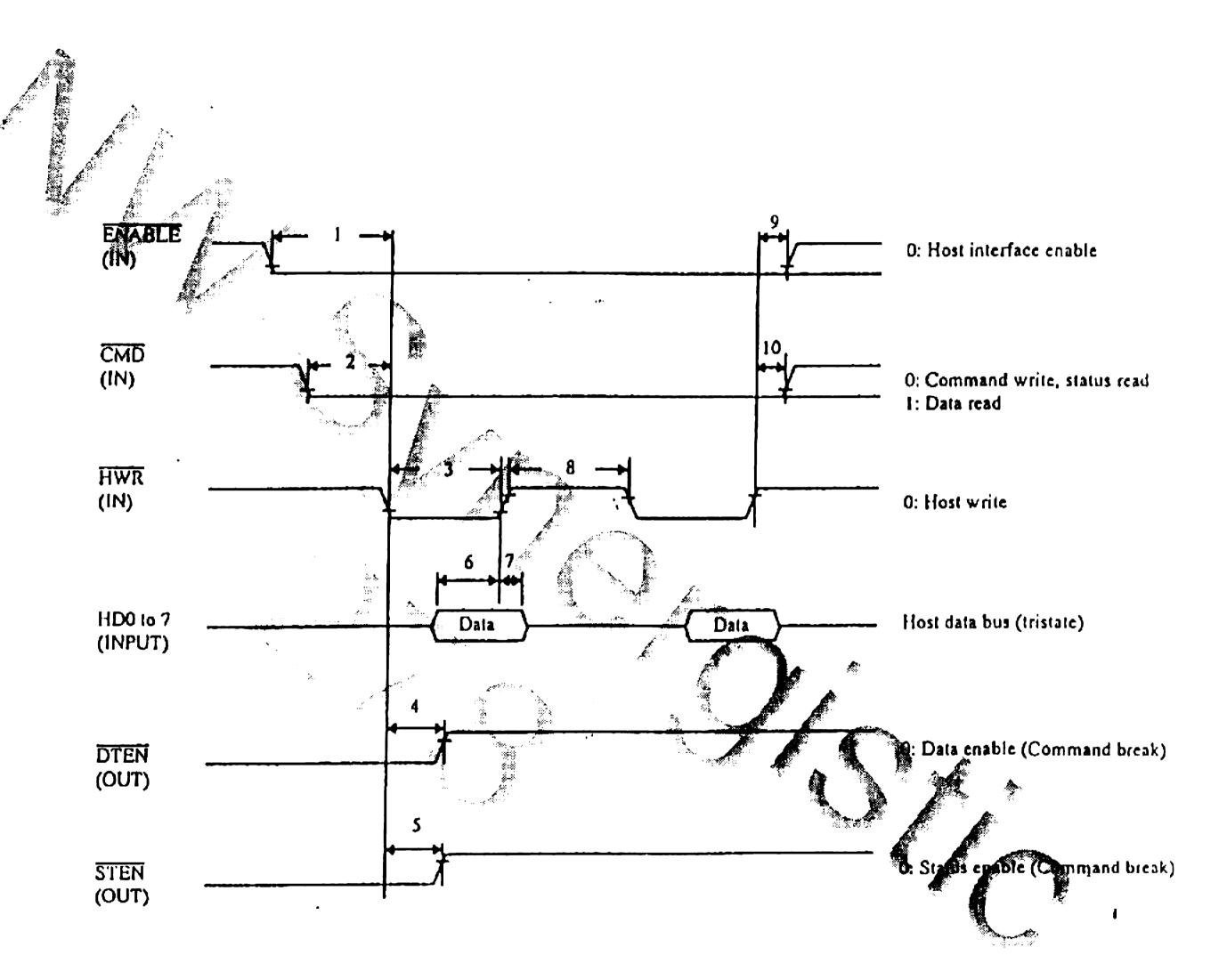

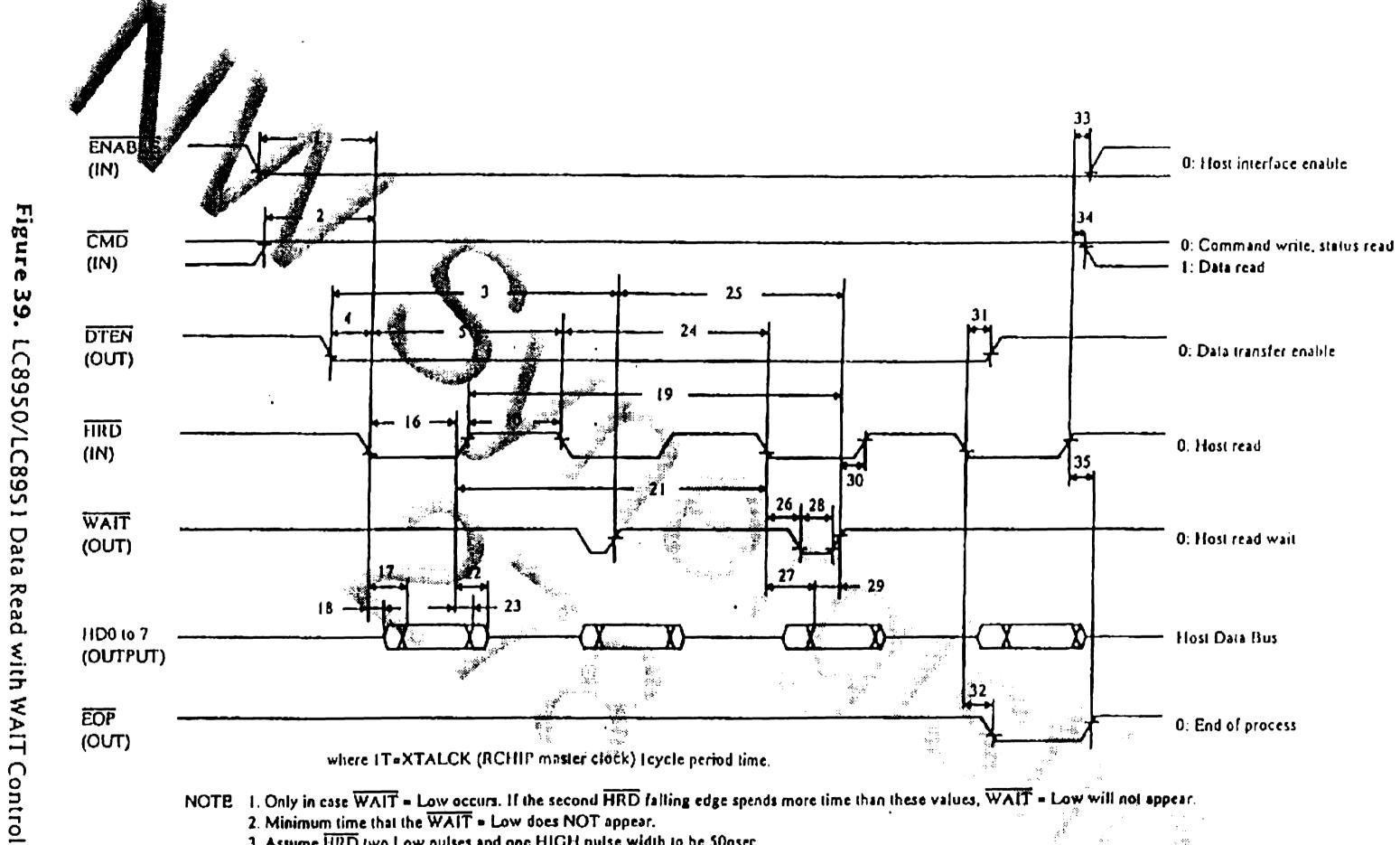

The LC8950 can send data to the host either under software with WAIT control, or with DMA transfers using data request controls. The SELDRQ pin is used to control the type of data transfer.

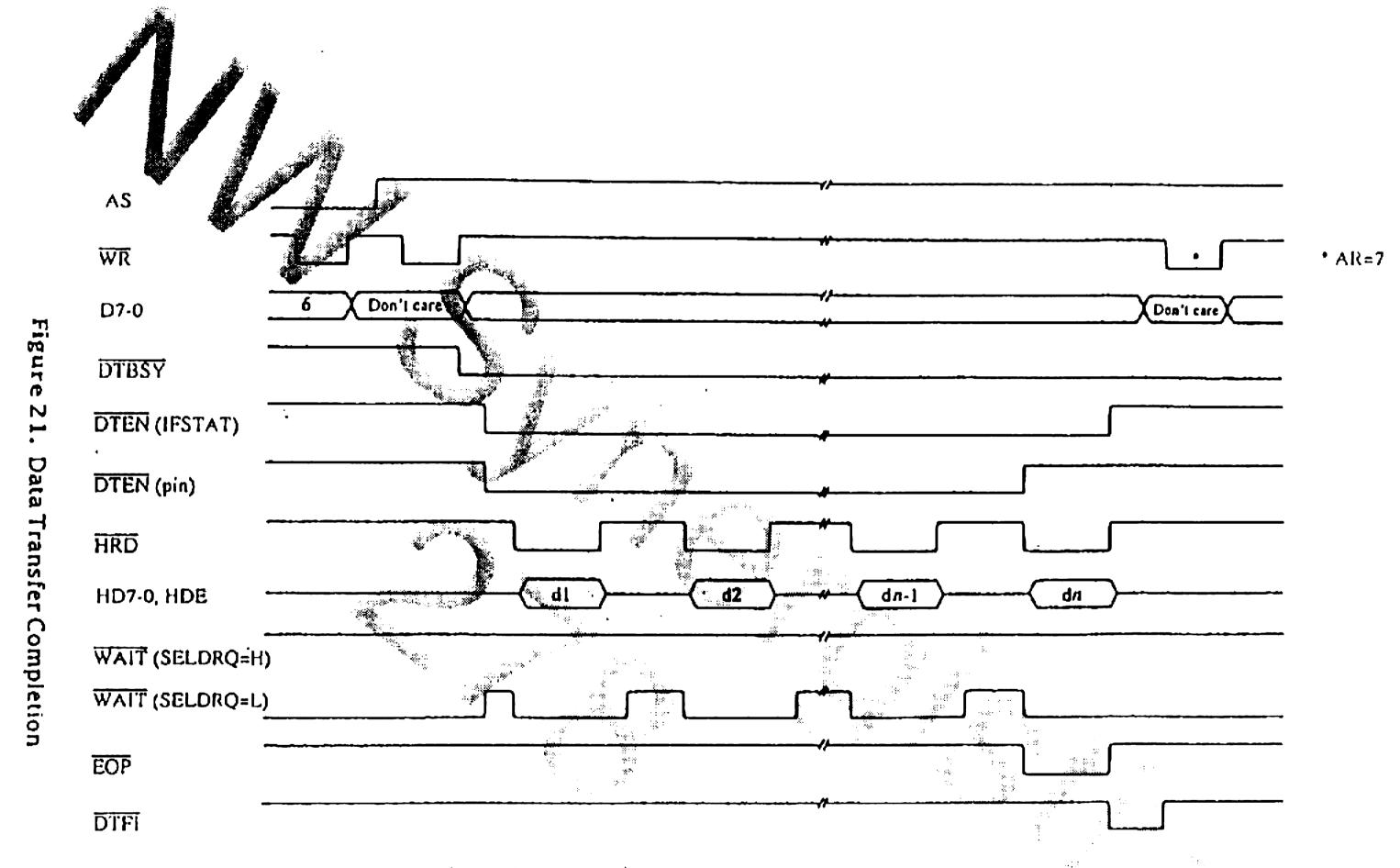

When SELDRQ is HICH, the LC8950 uses software transfer mode. In this mode, the controller places the number of bytes to be transferred and the data buffer address of the block head into the appropriate control registers, and then writes to the transfer-start register. This action sets the pin DTEN to LOW, informing the host that data transfer will start. When the host sees that DTEN is LOW, it sets CMD to HiGH, instructing the LC8950 to transfer successive bytes.

If the read signals from the host exceed the LC8950's maximum data rate (about 2.3 MB/s), the LC8950 sets the WAIT pin to LOW. The host must then hold HRD LOW to delay the read until the WAIT pin goes HIGH. Note that the controller is not directly involved in transfer operations and simply waits to receive the transfer-complete interrupt.

When the SELDRO pin is LOW, the LC8950 performs DMA transfers using the second and operates in a manner similar to a DMA controller.

When the LC8950 sends a data request signal, the host applies signals at HRD p control the data transfer. When the last byte is transferred, the number in the byte counter reaches the number specified by the controller. This condition sets the EOP pin to LOW during the request signal output. At the same time, DTEN goes HIGH and a transfer-complete interrupt is sent to the controller.

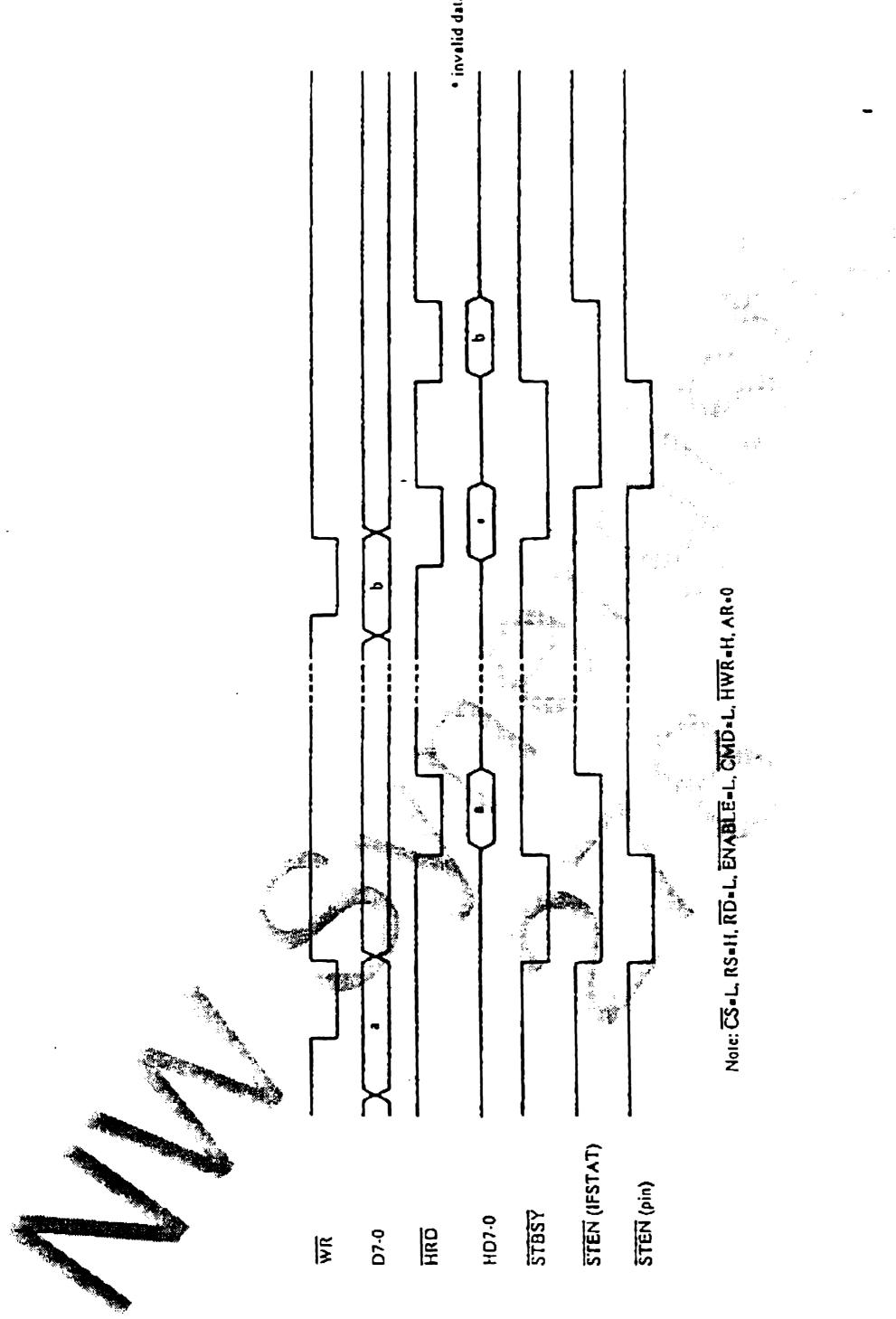

The controller can also use the LC8950 as an intermediary for communicating the CD-ROM drive status or the results of a block decoding operation to the host. The controller writes data to a one-byte status register, and the LC8950 then transmits these data to the host, without modifying their content. The controller and host perform handshaking using signals at the STEN pin.

Since the LC8950 neither interprets nor acts on the command or status registers, equipment developers can freely define their own conventions. This facilitates both the development of new CD-ROM applications and the incorporation of the LC8950 into existing designs.

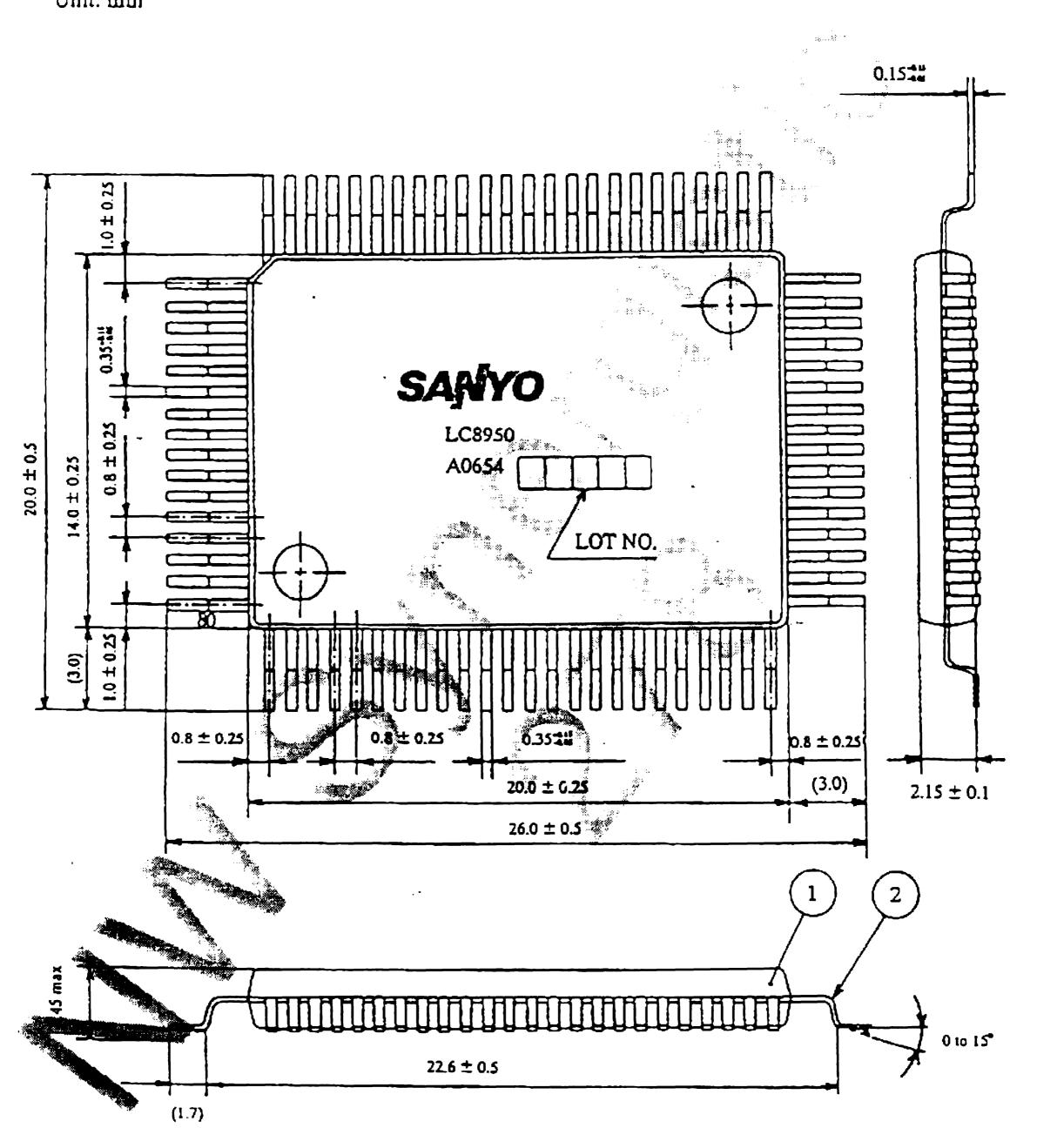

## 5. PACKAGE DIMENSIONS

Scale: 5:1

Unit: mm

Figure 5. 80-Pin Plastic Flatpack Dimensions

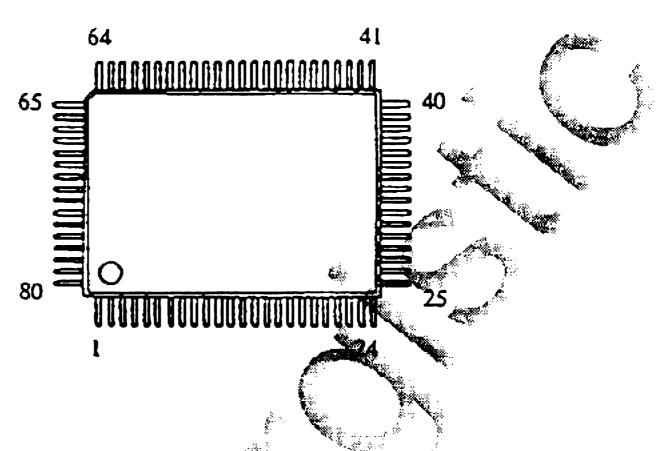

## 6. PIN CONFIGURATION

Figure 6. LC8950 Pin Configuration

The following designations are used for the pin types shown in table 2 over-leaf.

TABLE 1. Pin Designators

| Designator | Pin Type      |

|------------|---------------|

| 1          | Input         |

| O          | Output        |

| 8          | Bidirectional |

| P          | Power supply* |

\*V<sub>SS</sub> should normally be tied to GND.

TABLE 2. Pin Numbers, Names and Designations

| Pin# | Name   | Designator | Pin#            | Name      | Designator           |

|------|--------|------------|-----------------|-----------|----------------------|

| 1    | GND    | P          | 80              | RA5       | 0                    |

| 2    | RA6    | 0          | 79              | RA4       | 0                    |

| 3    | RA7    | 0          | 78              | RA3       | 0                    |

| 4    | RA8    | 0          | 77              | RA2       | 0                    |

| 5    | RA9    | 0          | 76              | RA1       | 0                    |

| 6    | RA10   | 0          | 75              | RA0       | O                    |

| 7    | RA11   | 0          | 74              | SELDRO    | 18 2.<br>18 2. 19 18 |

| 8    | RA12   | 0          | 73              | QQV       | P                    |

| 9    | RA13   | 0          | 72              | HD0       | В                    |

| 10   | RA14   | 0          | 71              | HD1       | В                    |

| 11   | RA15   | 0          | 70              | HD2       | 8                    |

| 12   | RWE    | 0          | 69              | HD3       | 8                    |

| 13   | GND    | Р          | 68              | HD4       | 8                    |

| 14   | ROE    | 0          | 67              | HD5       | * , 8                |

| 15   | ERA    | В          | 66              | HD6       | , В                  |

| 16   | 108    | В          | 65              | * HD7     | 8                    |

| 17   | 107    | В          | 64              | GND       | Ρ                    |

| 18   | 106    | В          | 63              | HDE       | g* O                 |

| 19   | 105    | В          | <sub>3</sub> 62 | DOUT      | 0                    |

| 20   | 104    | 8          | 61              | EOP       | 0                    |

| 21   | 103    | В          | 60              | STEN      | 0                    |

| 22   | 102    | 8          | ***\$9          | DTEN      | 0                    |

| 23   | 101    | 8          | 58              | WAIT      | 0-                   |

| 24   | GND    | <b>%</b> P | * 57            | CMD       |                      |

| 25   | XTALCK | 1          | 56              | , HAD     | 1                    |

| 26   | XTAL   | <b>10</b>  | 55              | HWR       | Parent !             |

| 27   | JEST1  | No.        | 54              | ENABLE    | 1                    |

| 28   | TEST2  | 14         | 53              | RESET     | ı                    |

| 28   | CSEL   | L.F        | 724             | GND       | . Р                  |

| 30   | MSEL   | 1          | 51              | INT       | 0                    |

| 31   | VOD    | Р          | > 50 €          | <b>CS</b> | ı                    |

| 32   | LRCK   | 1          | 49              | ู่⊪พิฅ    | I                    |

| 33   | SDATA  | 1          | 48              | RD        | I                    |

| 84   | BCK    |            | 47              | RS        | 1                    |

| 15   | C4LR   |            | 46              | 07        | В                    |

| 36   | C2PO   | 1          | 45              | D6        | В                    |

| 37   | MCK    | 0          | 44              | D5        | В                    |

| 38   | D0     | 8          | 43              | D4        | В                    |

| 39   | 01     | 8          | 42              | 03        | В                    |

| 40   | D2     | В          | 41              | GND       | Р                    |

|      |        |            | •               |           |                      |

11

## 7. PINOUTS

TABLE 3. Pin Numbers, Names and Functions

| Pin# | Pin Name          | 1/0   | Function                                       |

|------|-------------------|-------|------------------------------------------------|

| 1    | GND               | _     | Ground                                         |

| 2    | RA6               | 0     |                                                |

| 3    | RA7               | 0     |                                                |

| 4    | RA8               | 0     |                                                |

| 5    | RA9               | 0     |                                                |

| 6    | RA10              | 0     | Data buffer RAM and erasure flag BAM           |

| 7    | RA11              | 0     | address outputs                                |

| 8    | RA12              | 0     |                                                |

| 9    | RA13              | 0     |                                                |

| 10   | RA14              | 0     |                                                |

| 11   | RA15              | 0     |                                                |

| 12   | RWE               | ٥     | RAM write enable                               |

| 13   | GND               | ٠     | Ground                                         |

| 14   | ROE               | . 0   | RAM outout enable                              |

| 15   | ERA               | 1/0   | Erasure flag RAM data input/output             |

| 16   | 108               | 1/0   |                                                |

| 17   | 107               | 1/0   |                                                |

| 18   | 106               | 1/0   |                                                |

| 19   | 105               | 41/0- | Data buffer RAM input/output.                  |

| 20   | 104               | 1/0   | (LC8951 has 20 kΩ pull-up resistors on-chip.)  |

| 21   | 103               | 1/0   |                                                |

| 22   | 102               | 1/0   |                                                |

| .23  | <sup>*</sup> ,101 | 1/0   |                                                |

| 24   | GNO               | _     | Ground                                         |

| 25   | XTALCK            | ı     | Clock input                                    |

| 26   | XTAL              | 0     | Clock output                                   |

| 27   | TEST1             | 1     | Test inputs.                                   |

| 28   | TEST2             | 1     | Normally held LOW.                             |

| 29   | CSEL              | I     | Serial data clock phase select                 |

| 30   | LMSEL             | 1     | Serial data byte order control (LSB/MSB first) |

| Pin#       | Pin Name      | 1/0 | Function                                                                    |

|------------|---------------|-----|-----------------------------------------------------------------------------|

| 31         | DOV           |     | Positive power supply connection                                            |

| 32         | LRCK          | 1   | 44.1 KHz left & right channel separator strobe                              |

| 33         | SDATA         | 1   | Serial data input                                                           |

| 34         | ВСК           | 1   | Buffer input clock                                                          |

| 35         | C4LR          | ı   | C2 error flag pointer strobe                                                |

| 36         | C2PO          | 1   | C2 flag pointer                                                             |

| 37         | мск           | 0   | Master clock output                                                         |

| 38         | DO            | 1/0 |                                                                             |

| 39         | D1            | 1/0 | Controller data input/output. (LC8951 has 20 kΩ pull-up resistors on-chip.) |

| 40         | D2            | 1/0 |                                                                             |

| 41         | GND           | _   | Ground                                                                      |

| 42         | D3            | 1/0 |                                                                             |

| 43         | D4            | 1/0 |                                                                             |

| 44         | D5            | 1/0 | Controller data input/output. (LC8951 has 20 kΩ pull-up resistors on-chip.) |

| 45         | D6            | 1/0 | (LOOSSI Has Louis to the Company                                            |

| 46         | D7            | 1/0 |                                                                             |

| 47         | RS            | 1   | Register <b>select</b>                                                      |

| 48         | RD            | - l | Controller data read                                                        |

| 49         | WR            | I   | Controller data write                                                       |

| 50         | <del>CS</del> | 1   | Controller chip select                                                      |

| 51         | INT           | O   | Controller interrupt                                                        |

| 52         | GND           |     | Ground                                                                      |

| 53         | RESE          | l 🦸 | LC8950 chip reset                                                           |

| 54         | ENABLE        |     | Host interface enable                                                       |

| 55         | HWR           | 1   | Host data write input                                                       |

| <b>B6.</b> | HRD           | 1   | Host data read input                                                        |

| 37         | CMD           | 1   | Host command/data select                                                    |

| 188        | WAIT          | 0   | Data transfer WAIT signal/DRO signal                                        |

| 59         | DTEN          | 0   | Data enable output                                                          |

|            | STEN          | 0   | Status enable output                                                        |

| Pin# | Pin Name      | 1/0      | Function                                                            |

|------|---------------|----------|---------------------------------------------------------------------|

| 61   | EOP           | 0        | End-of-process flag output                                          |

| 62   | DOUT<br>(RCS) | 0        | Host computer data buffer control output – (LC8951 RAM chip select) |

| 63   | HOE           | 0        | Host data erasure flag tristate output                              |

| 64   | GND           | _        | Ground                                                              |

| 65   | HD7           | 1/0      |                                                                     |

| 66   | HD6           | 1/0      |                                                                     |

| 67   | HD5           | 1/0      |                                                                     |

| 68   | HD4           | 1/0      | Uses data issue/outsut                                              |

| 69   | ноз           | 1/0      | Host data input/output                                              |

| 70   | HD2           | 1/0      |                                                                     |

| 71   | HD1           | 1/0      |                                                                     |

| 72   | HDO           | 1/0      |                                                                     |

| 73   | VOD           | _        | Positive power supply connection                                    |

| 74   | SELDRO        | l        | Data transfer mode select (WAIT control/DRQ control)                |

| 75   | RA0           | 0.       |                                                                     |

| 76   | RA1           | 0        |                                                                     |

| 77   | RA2           | 0        | Data buffer RAM and erasure flag RAM                                |

| 78   | RA3           | 0        | address outputs                                                     |

| 79   | RA4           | <b>3</b> |                                                                     |

| 80   | RAS           | O.       |                                                                     |

#### 8. PIN DESCRIPTIONS

GND — Ground pins

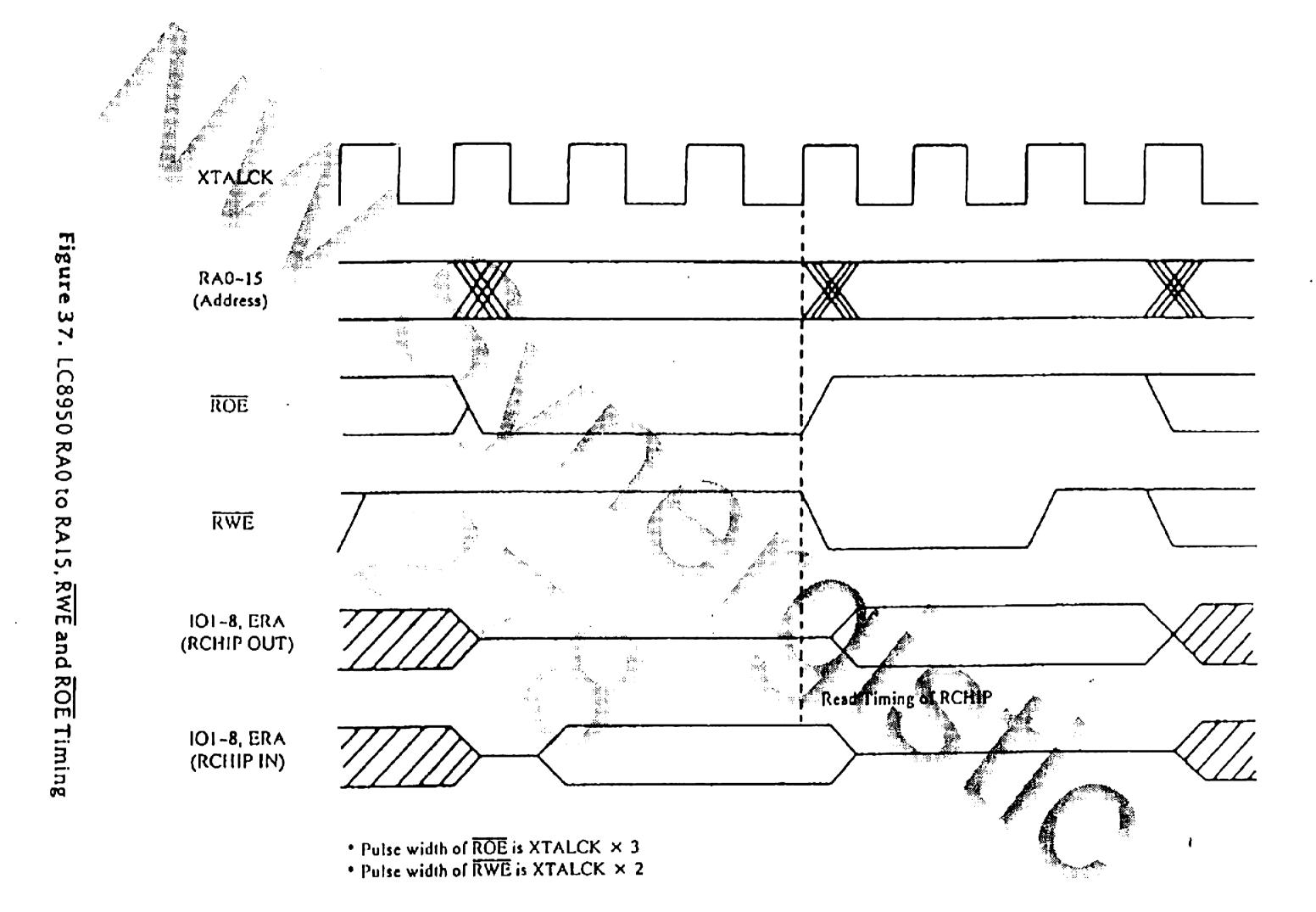

RAO to RA15 - Data buffer RAM and erasure flag RAM address outputs

The LC8950 uses these 16 outputs to specify addresses in the data buffer or erasure data memory, allowing the use of an 8 Kbyte to 64 Kbyte external buffer.

RWE - RAM write enable output

The LC8950 sets this output to LOW when writing data to the external data buffer or erasure flag RAM.

ROE — RAM output enable output

The LC8950 sets this output to LOW when reading data from the external data buffer or erasure flag RAM.

ERA — Erasure flag RAM data I/O pin

This pin is the data bus for the erasure flag RAM. As this pin is a tristate type, a pull-up resistor should be used.

IO1 to IO8 - Data buffer RAM I/O pins

These pins are the data bus to the external data buffer. As these pins are tristate types, pull-up resistors should be used.

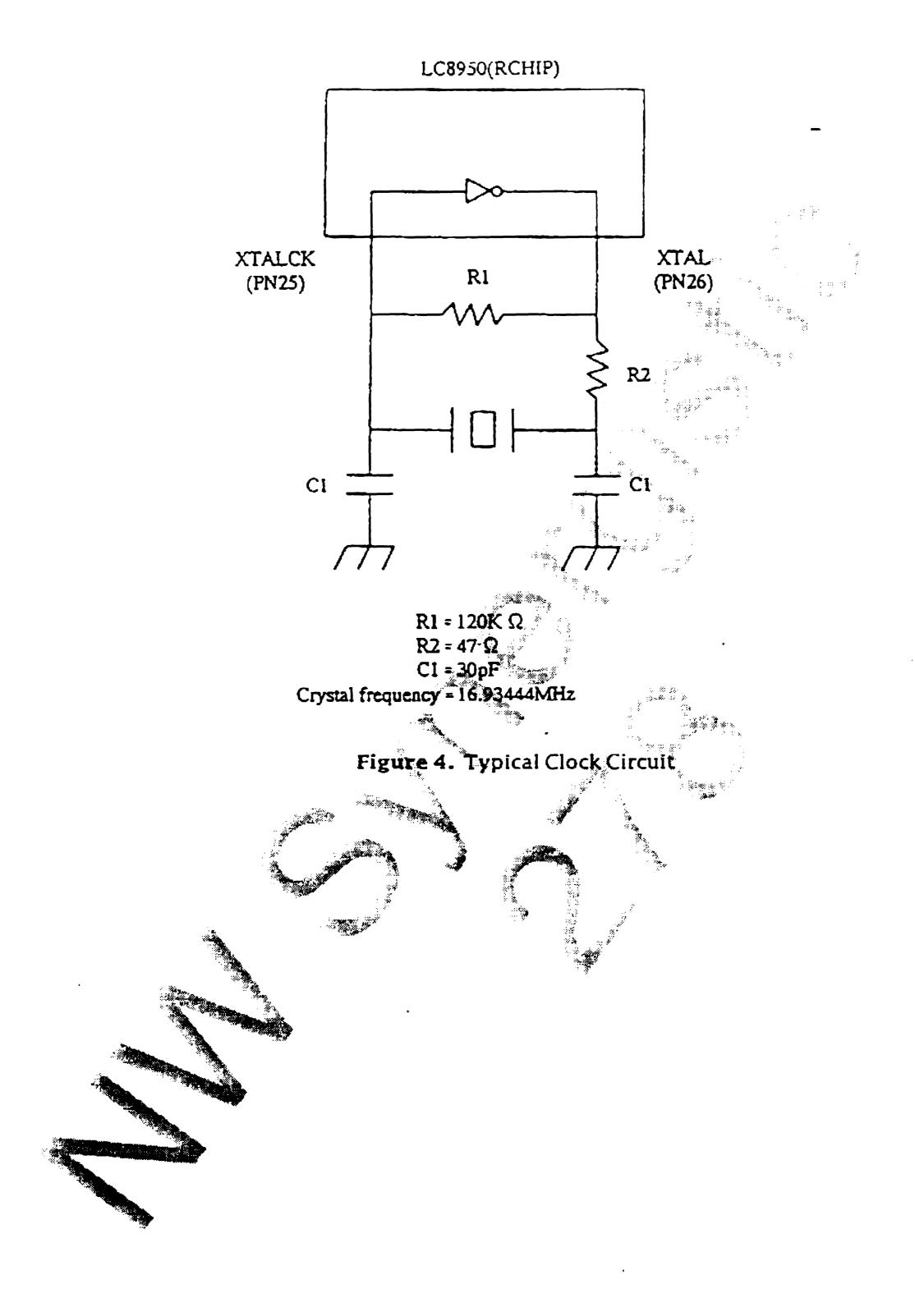

XTALCK, XTAL — External clock signals

As the LC8950's clock circuit includes an on-chip binary prescaler, a 16.9344 MHz crystal should be used to generate the required 8.4672 MHz master clock (MCK) signal.

XTALCK can be driven by a 50±10 % duty external signal. This generates a master clock signal one half the frequency of the external signal. In this case, the XTAL pin should be left floating.

The clock frequency needs to be exactly 16.9344 MHz only when the master clock output is used. Otherwise, select a frequency that results in both the LOW- and HIGH-level signals at LRCK having widths longer than 192 clock pulses.

TEST1. TEST2 — est inputs

Test pins. Usually tied to GND

CSE LMSEL — Clock phase select and serial data byte order inputs

nais select the read timing at the SDATA and C2PO inputs as follows:

- A. When both CSEL and LMSEL are LOW:

- SDATA is read at the falling edge of BCK.

- ii. The data at SDATA are processed beginning from the most-significant bit.

- iii. The edge of LRCK ends the reading of 2-byte words at SDATA, and starts the reading of the next word.

- iv. When more than 16 clock pulses are detected at BCK within one-half cycle of LRCK, only the data read in during the 16 clock pulses immediately before the LRCK edge are significant.

- v. A HIGH-level signal at LRCK identifies the data at SDATA as belonging to the left audio channel.

- vi. Data at C2PO is read in at the rising edge of C4LR.

- vii. Signals applied to C2PO flag the most-significant byte the least-significant byte of the 2-byte words at SDATA.

- viii. In this mode, the LC8950 can be interfaced directly with the Sony CXD1125 digital signal processor.

- B. When CSEL is LOW and LMSEL is HIGH:

- I. SDATA is read at the falling edge of BCK.

- ii. The data at SDATA are processed beginning from the least-significant bit.

- iii. The edge of LRCK marks the start of reading one 2-byte word at SDATA. When reading is completed, the read operation is terminated.

- Iv. When more than 16 clock pulses are detected at BCK within one-half cycle of LRCK, only the data read in during the 16 clock pulses immediately after the LRCK edge are significant.

- v. A HIGH-level signal at LRCK identifies the data at SDATA as belonging to the left audio channel.

- vi. Data at C2PO is read in at the fifth and thirteenth BCK pulses after the LRCK edge. C4LR is not used to supply the timing.

- vii. Signals applied to C2PO flag the least-significant byte then the most-significant byte of the 2-byte words at SDATA.

- viii. In this mode, the LC8950 can be interfaced directly with the Sanyo LC7860, Matsushita MN6617 or Yamaha TM3815 digital signal processors.

- C. When CSEL is HIGH and LMSEL is LOW:

- i. SDATA is read at the rising edge of BCK.

- ii. The data at SDATA are processed beginning from the mostsignificant bit.

- iii. The edge of LRCK marks the end of reading one 2-byte word at SDATA, and starts the reading of the next word.

- Iv. When more than 16 clock pulses appear at BCK within one-half cycle of LRCK, only the data read in during the 16 clock pulses immediately before the LRCK edge are significant.

- v. A HIGH-level signal at LRCK identifies the data at SDATA as belonging to the left audio channel.

- vi. Data at C2PO is read in at the rising edge of C4LR.

- vii. Signals applied to C2PO flag the least-significant byte then the most-significant byte of the 2-byte words at SDATA.

- viil. In this mode, the LC8950 can be interfaced directly with the Toshiba TC9200F digital signal processor.

- D. No operational mode is defined when CSEL and LMSEL are both HIGH. As this mode is reserved for future use, it should not be used.

VDD — Positive power supply connections

VDD should be in the range of  $5.0\pm10$  % V

LRCK — Left and right channel separator clock input

Supplies the signal which separates CD audio data into those for the left and right channels.

In a half cycle of LRCK, 16 bits of data are read in at SDATA. The rising and falling edges of LRCK are used to distinguish between the first and last bits.

SDATA — Serial data input

This serial input receives the data after CIRC (Cross Interleaved Reed-Solomon Code) decoding. The BCK pin controls the flow of data to the LC8950. The received data are stored in the external data buffer.

BCK — Buffer input clock

The clock signal for reading in serial data at SDATA is applied to this input. At least 16 BCK clock pulses should be generated within one-half cycle of LRCK.

C4LR — C2 error flag pointer strobe input

Used to supply the strobe signal for reading in the C2 error flag. When unused, It should be tied to either VCC or GND.

C2PO — C2 error flag pointer input

This input is used for the C2 error flag input during CIRC decoding. The flag is non-inverting; a HiGH level input indicates an error condition. The data at C2PO are read in at the rising edge of the signal at C4LR, if present, or on an internal timing signal generated at BCK and LRCK, and are stored temporarily in a one-bit buffer.

MCK — Master clock output

This output supplies a master clock signal of exactly one-half the frequency of the crystal connected at XTALCK. This output is used to provide a common clocking signal for the clock input of digital signal processor in the CD equipment.

DO to D7 Controller data pins

these pins are the data bus to the external controller. As these pins are high-impledance types, pull-up resistors should be used.

RS, RD and WR - Controller interface control inputs

These are the register select, read and write inputs used to control the operation of the controller interface. They are active only when CS is LOW.

RS selects either the address register (AR) or one of the LC8950's 32 registers. AR is a special register used to select one of the 32 read or write registers on-chlp.

RS - LOW selects direct addressing (AR), whereas RS - HIGH selects indirect addressing (the register pointed to by AR).

CS — Controller chip select input

The controller sets this input to LOW to enable the LC8950's controller interface.

INT - Interrupt output

This output transfers interrupt requests from the LC8950 to the controller when LOW.

RESET — Reset input

Forcing this input LOW resets the LC8950.

ENABLE — Host Interface enable input

This input selects the LC8950. The host computer sets this input to LOW to enable the host interface.

HWR, HRD and CMD - Host interface control inputs

These inputs control the operation of the host interface. HWR is the host data write input, HRD, the host data read input, and CMD, the host command/data select input. They are active only when ENABLE is LOW.

- i. Setting HWR LOW, HRD HIGH and CMD LOW instructs the LC8950 to enter command write mode. The data at HD1 to HD7 are written into the LC8950's command register.

- ii. Setting HWR HIGH, and HRD and CMD LOW instructs the LC8950 to enter status read mode. The data previously written by the controller to the LC8950's status register are output at HD0 to HD7.

- ili. Setting HRW HIGH, HRD LOW and CMD HIGH Instructs the LC8950 to enter data transfer mode. Data in the buffer are read by the LC8950 and output to the host at HDO to HD7. The erasure flag status is output at HDE.

All other combinations of HWR LOW and CMD HIGH, and both HWR and HRD LOW are undefined and should not be set, as the result of their use cannot be guaranteed.

WAIT — Wait output

The function of this output depends on the state of the SELDRQ input.

I. When SELDRO is HIGH (that is, during software transfer mode), the LC8950 sets the WAIT output to LOW to signal the host to suspend the data transfer.

WAIT Is held HIGH while DTEN is HIGH, and while the LC8950 is not transferring data to the host.

li. When SELDRQ is LOW (that is, during DMA transfer mode), WAIT functions as a DRQ (data request) output to the host computer.

WAIT remains LOW while DTEN is HIGH, and while the LC8950 is not transferring data to the host.

DIEN — Data enable output

This output is set to LOW to signal the host computer that data is ready to be transferred.

STEN — Status enable output

This output is set to LOW to signal the host computer that the status byte is ready to be read out.

EOP - End-of-process flag output

The LC8950 sets this flag to LOW on sending the last byte to the host computer using either software or DMA data transfers.

DOUT - Host computer data buffer control output\*

This output is set to LOW to request data from the host computer data buffer when ENABLE and FIRD are both LOW.

HDE — Host data error flag output

This output is used to output error flag signals to the host computer. The error flag is output during data transfers when the corresponding data bytes are being output at HD0 to HD7. When the LC8950 is in status-read mode, HDE is LOW.

HD0 to HD7 — Host data I/O pins

These pins are the data bus to the host computer. As these pins are tristate types, pull-up resistors should be used.

SELDRQ — Data transfer mode select input

When HIGH, this input elects software transfer mode for data transfers to the host (WAIT control); when LOW, DMA transfer mode (DRQ control) is selected.

## 9. ELECTRICAL SPECIFICATIONS

TABLE 4. Absolute Maximum Ratings

| Parameter                                                                                                              | Symbol                                                                                                               | Rating                                                                            | Unit *        | Test<br>Conditions                              |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------|-------------------------------------------------|

| Supply voltage Input/output voltages Power dissipation Operating temperature Storage temperature Soldering temperature | V <sub>DD</sub> max<br>V <sub>1</sub> , V <sub>0</sub><br>P <sub>d</sub> max<br>T <sub>opg</sub><br>T <sub>stg</sub> | -0.3 to 7.0<br>-0.3 to V <sub>DD</sub> +0.3<br>350<br>-30 to 70 -55 to 125<br>260 | www.mww.deg.C | Ta=25 deg. C Ta=25 deg. C Ta<70 deg. C For 10 s |

TABLE 5. Recommended Operating Conditions

(Over operating free-air temperature range)

| Parameter        | Symbol                             | Min | Тур         | Max                     | Unit   |

|------------------|------------------------------------|-----|-------------|-------------------------|--------|

| Supply voltage ( | V <sub>DD</sub><br>V <sub>IN</sub> | 4.5 | 5. <b>0</b> | √5.5<br>V <sub>op</sub> | V<br>V |

TABLE 6. Electrical Characteristics

(i) LC8950 (Input/output level V<sub>DD</sub>=4.5 to 5.5V, over operating free-air temperature range)

| Parameter                              | Symbol          | Min         | Тур    | Max       | Unit     | Test<br>Conditions                                                     | Pins                           |

|----------------------------------------|-----------------|-------------|--------|-----------|----------|------------------------------------------------------------------------|--------------------------------|

| HIGH-level input voltage HIGH          | V <sub>1H</sub> | 2.2         | _      | _         | ٧        |                                                                        | All Input and bus pins,        |

| LOW-level input voltage                | VIL             | _           | _      | 8.0       | ٧        |                                                                        | except XTALCK                  |

| HIGH-level output volt-<br>age         | V <sub>OH</sub> | 2.4         | _      | _         | V        | I <sub>OH</sub> = -0.4 mA                                              | All output and bus             |

| LOW-level output voltage               | VOL             | _           | _      | 0.4       | ٧        | I <sub>OL</sub> -2.0 mA                                                | pins, except XTAL              |

| Input leak current Output leak current | ار<br>اoz       | ~25<br>-100 | <br> - | 25<br>100 | μA<br>μA | V <sub>IN</sub> -V <sub>SS</sub> ,V <sub>DD</sub><br>At high impedance | All inputs<br>HDE and bus pins |

(ii) LC8951

(Input/output level V<sub>00</sub>=4.5 to 5.5V, over operating free-air temperature range)

| Parameter                                                                 | Symbol                               | Min         | Тур    | Max       | Unit       | Test<br>Conditions                                                     | Pins                                             |

|---------------------------------------------------------------------------|--------------------------------------|-------------|--------|-----------|------------|------------------------------------------------------------------------|--------------------------------------------------|

| HIGH-level input voltage LOW-level input voltage HIGH-level input voltage | V <sub>IH1</sub><br>V <sub>IL1</sub> | 2.2         |        | 0.8       | < < <      | ·                                                                      | All input pins except XTALCK, BUS pins and RESET |

| LOW-level input voltage HIGH-level output voltage age                     | VILE<br>Vohu                         | 2.4         |        | 0.6<br>—  | > > /      | I <sub>OH</sub> 20.4 mA                                                | All output and bus<br>pins, except XTAL          |

| LOW-level output voltage  LOW-level output voltage                        | VOL1                                 | _           | _      | 0.4       | V.         | l <sub>OL</sub> =2.0 mA                                                | INT (Open drain out-<br>put)                     |

| Input leak current                                                        | ار<br>اoz                            | -25<br>-100 | <br> - | 25<br>100 | JIA<br>JIA | V <sub>IN</sub> =V <sub>SS</sub> ,V <sub>DD</sub><br>At high impedance | All inputs<br>HDE and bus pins                   |

# 10. REGISTERS

TABLE 7. LC8950 Registers During Reads

| RS | AR   | Number | Name   | Bit7            | Bit6              | Bit5       | Bit4             | Bit3                | Bit2                | Bit1           | Bito           |

|----|------|--------|--------|-----------------|-------------------|------------|------------------|---------------------|---------------------|----------------|----------------|

|    |      | _      | AR     | 0               | 0                 | 0          | 0                | A <sub>3</sub>      | A <sub>Z</sub>      | ^i             | A <sub>0</sub> |

|    | 0000 | Я0     | COMIN  | msb             | -                 | -          | -                | - 🔻                 | <b>/</b> - <b>/</b> | _              | Isb            |

|    | 0001 | R1     | IFSTAT | CMOI            | DTEI              | DECI       | 1                | DTBSY               | STESY               | DTEN           | STEN           |

| 1  | 0010 | R2     | DBCL   | B <sub>7</sub>  | 86                | 85         | 84               | 83                  | A 2                 | 8,             | B <sub>0</sub> |

|    | 0011 | R3     | овсн   | DTEI            | DTEI              | DTEI       | DTEI             | В                   | B,10                | Bg             | B <sub>8</sub> |

|    | 0100 | R4     | HEAD0  | msb             | . –               | _          | -                |                     | _                   | -              | Isb            |

|    | 0101 | R5     | HEAD1  | msb             | -                 | _          | -                | <b>V</b> - <b>V</b> | -                   | -              | isb            |

|    | 0110 | R6     | HEAD2  | msb             | _                 | _          | , -              | 1                   | -                   | _              | Isb            |

| 0  | 0111 | R7     | HEAD3  | msb             | -                 | <b>-</b> 2 |                  | <b>.</b>            | _                   | -              | Isb            |

|    | 1000 | R8     | PTL    | A <sub>7</sub>  | A <sub>6</sub>    | A          | A                | A <sub>3</sub>      | A <sub>2</sub>      | A              | Ao             |

|    | 1001 | R9     | PTH    | A <sub>15</sub> | A <sub>14</sub>   | A13 /      | ⟨A <sub>12</sub> | A <sub>11</sub>     | A <sub>10</sub>     | Ag             | A <sub>8</sub> |

|    | 1010 | R10    | WAL    | A <sub>7</sub>  | A <sub>6</sub>    |            | A4               | A <sub>3</sub>      | A <sub>2</sub>      | A <sub>1</sub> | A <sub>0</sub> |

|    | 1011 | R11    | WAH    | A <sub>15</sub> | . A <sub>14</sub> | 13         | A <sub>12</sub>  | An                  | A <sub>10</sub>     | Ag             | A <sub>8</sub> |

|    | 1100 | R12    | STATO  | CRCOK           |                   | NOSYNC     |                  | WSHORT              | SBLK                | ERABLK         | UCEBLK         |

|    | 1101 | R13    | STAT1  | MINERA          | SECERA            | BLKERA     | MODERA           | SHOERA              | SH1ERA              | SH2ERA         | SH3ERA         |

|    | 1110 | R14"   | STAT2  |                 |                   |            | 7                | MODE                | FORM                |                |                |

|    | 1111 | R15*   | STAT3  | VALST           | MLONG             | .45        |                  |                     |                     |                |                |

Key

| 1     | Always read as one   |

|-------|----------------------|

| 0     | Always read as zero  |

|       | Used                 |

| BLANK | Not used, don't care |

See appendix E for the LC8951.

TABLE 8. LC8950 Registers During Writes

| RS     | AR    | Number | Name   | Bit7            | Bit6            | Bit5            | Bit4            | Bit3             | Bit2            | Bit1           | Bit0           |

|--------|-------|--------|--------|-----------------|-----------------|-----------------|-----------------|------------------|-----------------|----------------|----------------|

|        | _     | -      | AR     |                 |                 |                 |                 | A <sub>3</sub>   | A <sub>2</sub>  | A <sub>1</sub> | A <sub>o</sub> |

|        | 0000  | RO     | SBOUT  | msb             |                 | -               | -               | -                |                 | _              | isb            |

|        | 0001  | R1     | IFÇTRL | CMDIEN          | DTEIEN          | DECIEN          | CMOBK           | DTWAI            | STWAI           | DOUTEN         | SOUTEN         |

|        | 0010  | R2     | DBCL   | 8,              | B <sub>6</sub>  | B <sub>5</sub>  | 84              | 83               | B <sub>2</sub>  | *              | B <sub>0</sub> |

|        | 0011  | R3     | DBCH   |                 |                 |                 |                 | В,,              | B <sub>10</sub> | Bg             | 8,             |

|        | 0100  | R4     | DACL   | A <sub>7</sub>  | A <sub>6</sub>  | A <sub>5</sub>  | A               | A <sub>3</sub>   | A 2             | A <sub>1</sub> | A <sub>D</sub> |

| ,<br>İ | 0101  | A5     | DACH   | A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | <b>^</b> 11      | A <sub>10</sub> | A <sub>9</sub> | A <sub>8</sub> |

|        | 0110  | R6     | DTTRG  |                 | _               | -               | -               | 200 <b>-</b><br> | -               | _              |                |

| 0      | 0111  | R7     | DTACK  | _               | _               | -               | _               |                  |                 | _              | _              |

|        | 1000  | R8     | WAL    | A <sub>7</sub>  | A <sub>6</sub>  | A <sub>5</sub>  | A4 1            | A <sub>3</sub>   | A <sub>2</sub>  | A <sub>1</sub> | A <sub>0</sub> |

|        | 1001  | R9     | WAH    | A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | <sup>2</sup>    | A <sub>11</sub>  | A <sub>10</sub> | Ag             | A <sub>B</sub> |

|        | 1010  | R10*   | CTRLO  | DECEN           | EDCRO           | E01RQ           | AUTORQ          | ERAMRQ           | WRRQ            | QRQ            | PRQ            |

|        | 1011  | R11"   | CTRL1  | SYIEN           | SYDEN           | DSCREN          | COWREN          | MODRQ            | FORMRO          |                | SHOREN         |

|        | 1100  | R12    | PTL    | A <sub>7</sub>  | A <sub>6</sub>  | A <sub>S</sub>  | 3 A4            | Аз.              | A <sub>2</sub>  | A <sub>1</sub> | A <sub>o</sub> |

|        | 1101  | R13    | РТН    | A <sub>15</sub> | A <sub>14</sub> | A 13            | <del></del>     | A11              | A <sub>10</sub> | Ag             | A <sub>8</sub> |

|        | 1110  | R14    |        |                 | ***             |                 |                 |                  |                 |                |                |

|        | 1,111 | R15    | RESET  | _               | -               | · -             | - 88            | - y              | _               | -              | _              |

Key

| - Used          |                          | : :<br>: : :<br>: : : |

|-----------------|--------------------------|-----------------------|

|                 | ed, don't care.          | :                     |

| 30.5 1 5 W 36 M | er, writing 0 is recomme | ended to              |

<sup>\*</sup> See appendix E for the LC8951.

## 11. REGISTER DESCRIPTION

This section describes each of the registers on the LC8950 RCHIP. A range of register options including levels of error correction, can be selected. These allow fully customized interfaces for both the CD equipment and the host computer.

Note that several registers operate differently depending on whether a read or write operation is taking place. See the read and write register tables in the previous section for details.

#### 11.1 AR — Address Register

| BIT7 | BIT6 | BITS | BIT4 | ВІТЗ | BIT2     | BIT1    | ВІТО | R/W |

|------|------|------|------|------|----------|---------|------|-----|

|      |      |      |      |      | Register | Address |      | R/W |

This 4-bit register holds the addresses used to specify the LC8950's 16 internal data registers (R0 to R15).

A register address must be loaded into AR before reading from or writing to that register.

AR increments each time a read or write operation is performed at registers R1 to R15. When the register address reaches R15, the next I/O resets it to 0. Register I/O does not increment AR when the register address is R0.

# 11.2 COMIN/SBOUT — Command Input Register/Status-Byte Output Register (Register R0)

During reads, this register is COMIN, the command input register; during writes it is SBOUT, the status-byte output register. A read/write operation to this register does not increment AR.

#### 11.2.1 COMIN — Command Input Register

| BIT7 | 8176 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 BIT0 | E-R/W |

|------|------|------|------|------|------|-----------|-------|

| msb  |      |      |      |      |      |           | sb R  |

This register is a 8-byte circular buffer between the host computer and the controller. It is configured as a FIFO memory.

When commands from the host computer fill one or more bytes of the FIFO buffer, the CMDI bit in the IFSTAT register is set to 0, forcing the INT pin LOW.

When the command buffer is emptied, CMDI is set to 1, and reading the COMIN register in this state returns a value of FFH.

### 11.2.2 SBOUT — Status-Byte Output Register

| BIT7 | BIT6 | BIT5 | BIT4             | BĬT3     | BIT2 | BIT1 | BITO  | R/W |

|------|------|------|------------------|----------|------|------|-------|-----|

| msb  |      | vi   | ) - 1<br>\hall ( | Yang San | :    |      | - Isb | W   |

This one-byte register buffers status bytes to the host computer. Multiple status bytes are passed to the host byte-by-byte.

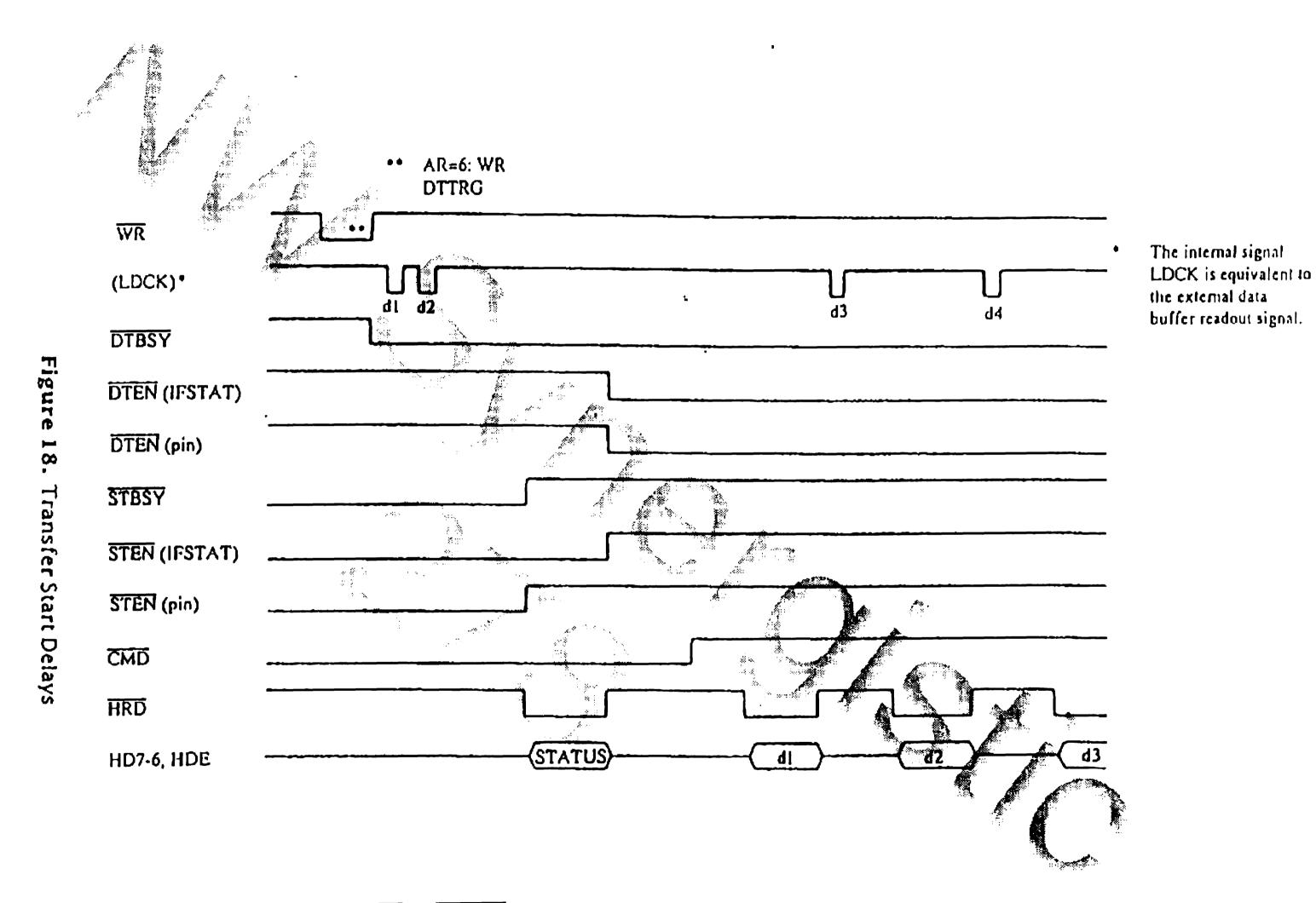

When the SOUTEN bit in the IFCTRL register has been set to 1, writing to the SBOUT register sets the STBSY bit to 0. If the STWAI bit is 0, the STEN pin is immediately set to LOW to inform the host computer that the status byte is ready to be read out.

If the STWAI bit is set to 1 and the DTEN bit in the IFSTAT register is also 1, both the STEN pin and the STBSY go LOW when writing to SBOUT is completed. However, if the STWAI bit is set to 0 and the DTEN bit is 0, the STEN pin is held HIGH until the DTEN bit goes HIGH; thereafter it goes LOW. See figure 13 Status-Byte Processing during Normal Operation and figure 14 Status-Byte Processing when WAIT is Enabled.

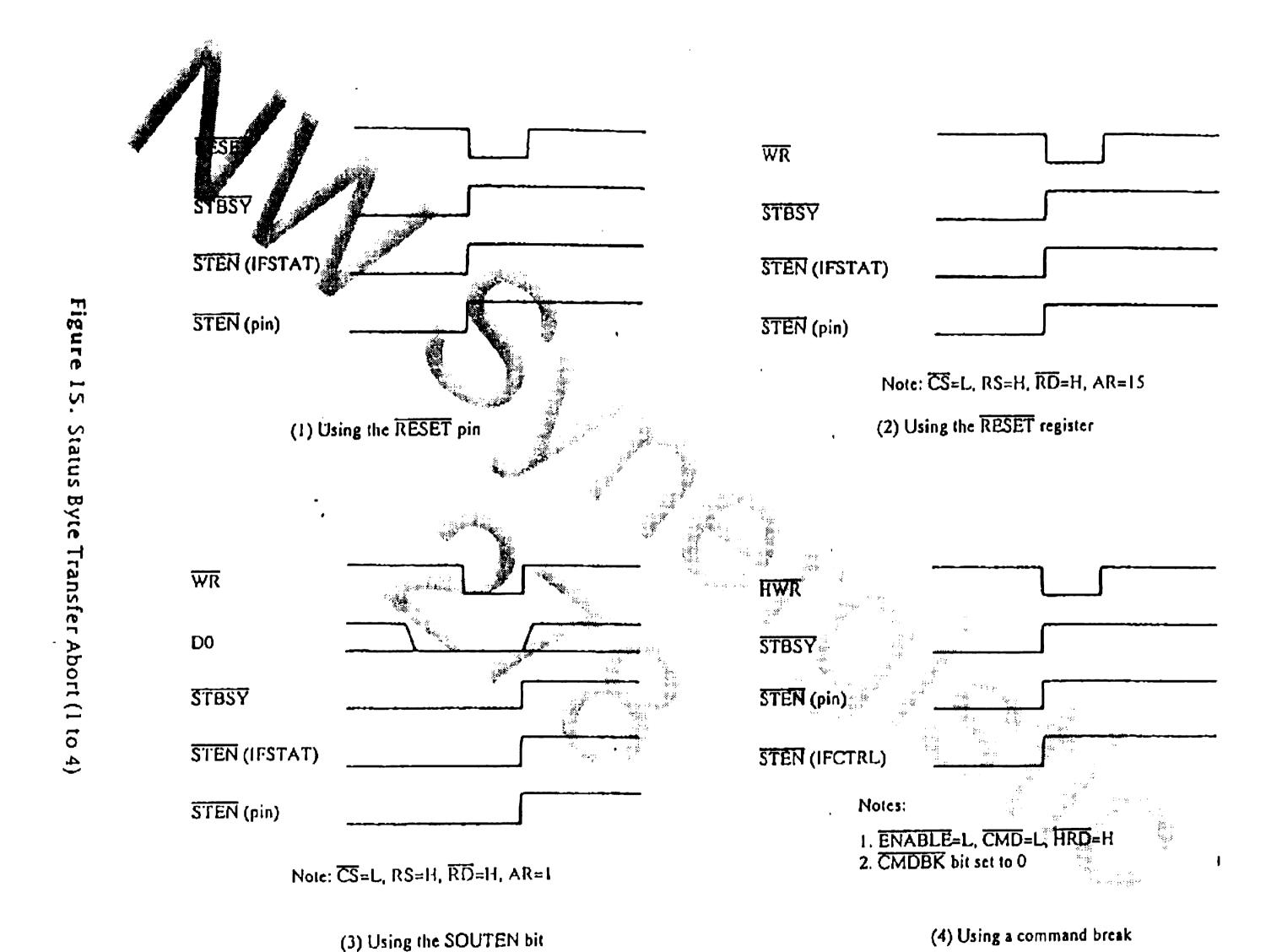

The STEN pin (and the STEN bit in the IFSTAT register) goes HIGH under the following conditions.

- The host computer reads the status byte while the STEN pin is LOW.

- The SOUTEN bit in the IFCTRL register is 0.

- The host writes a command while the CMDBK bit in the IFCTRL register is 0.

- The chip is reset.

# 11.3 IFSTAT/IFCTRL — Interface Status Register/Interface Control Register (Register R1)

During reads this register is IFSTAT, the interface status register; during writes it is IFCTRL, the interface control register. A read/write operation to this register automatically increments AR.

#### 11.3.1 IFSTAT — Interface Status Register

| BIT7 | BIT6 | BIT5 | BIT4 | BIT3  | BIT2  | BIT1 | BITO | 。R/W |

|------|------|------|------|-------|-------|------|------|------|

| CMDI | DTEI | DECI | 1    | DTBSY | STBSY | DTEN | STEN | R    |

This register indicates the status of the controller and host interfaces.

The operation of the DTEN and STEN bits resembles that of the DTEN and STEN pins. They differ in that the rising edges of signals at the DTEN and STEN pins are generated at the falling edge of the signal at pin HRD, while the states of the DTEN and STEN bits change at rising edge of HRD. See figure 18 Transfer Start Delays and figure 21 Data-Transfer Completion.

Bit 4 is unused and always returns a value of 1.

## 1. CMDI — Command Interrupt

| Status         | Oper                   | ation ation         |

|----------------|------------------------|---------------------|

| 0              | Interrupt set          |                     |

|                | Indicates that there a | re command bytes    |

|                | present in the COMIN   | register.           |

| 1.20           | Interrupt cleared      |                     |

| J. J. Carlotte | Indicates that there a | re no command bytes |

|                | in the COMIN register  |                     |

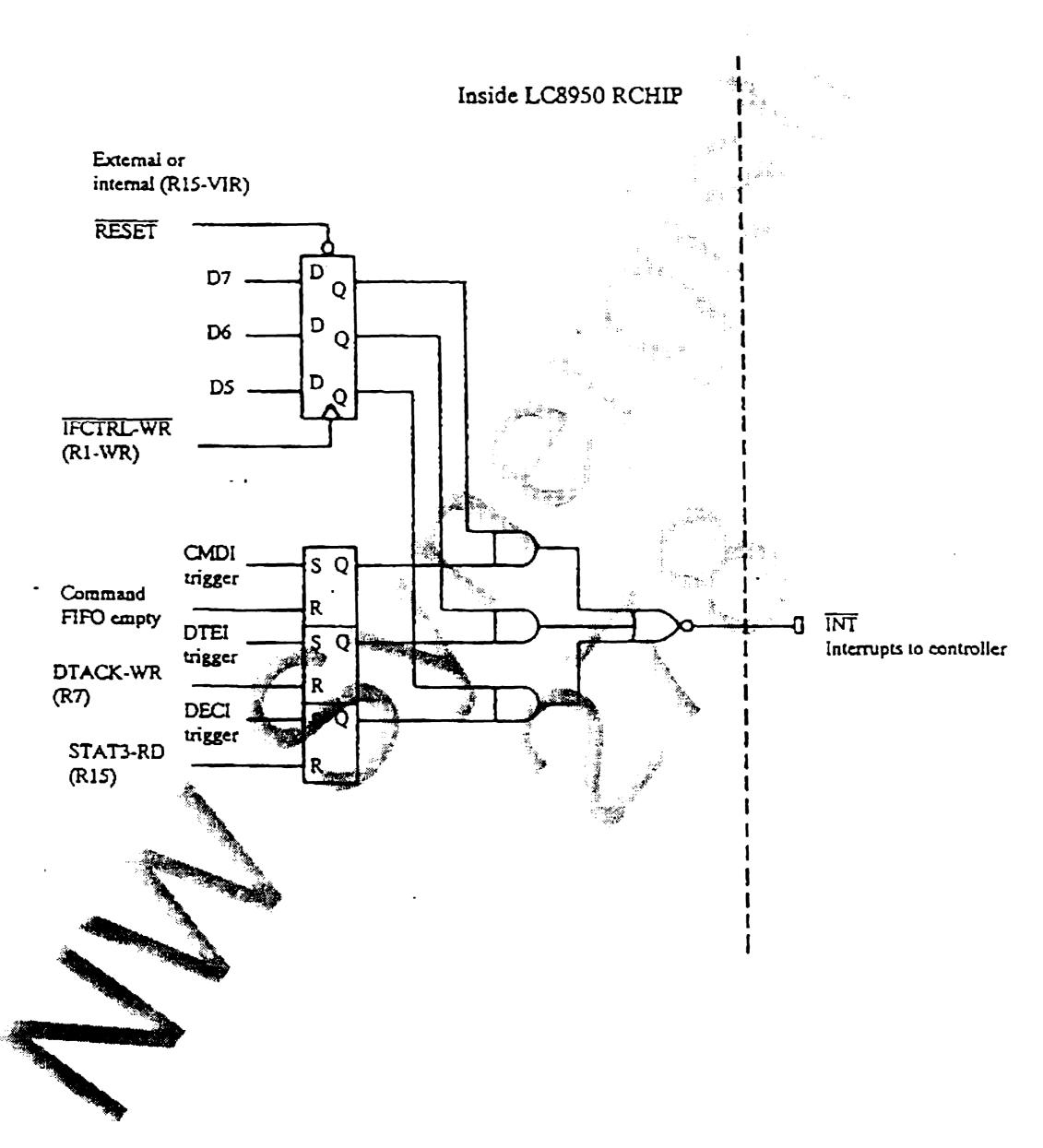

The interrupt clears when the controller empties the FIFO command buffer by reading successive command bytes. See figure 11 Interrupt Control Flags.

# 2. Dit Data-Transfer End Interrupt

| Status | Operation             |

|--------|-----------------------|

| 0      | Set interrupt set     |

| 1      | Set interrupt cleared |

Writing to the DTACK register clears the interrupt. See figure 11 Interrupt Control Flags.

3.  $\overline{DECI}$  — Decoder Interrupt

| Status | Operation         |

|--------|-------------------|

| 0      | Interrupt set     |

| 1      | Interrupt cleared |

Reading the STAT3 register clears the interrupt. See figure 11 Interrupt Control Flags.

4. DTBSY — Data Busy

| Status | Operation                   | <b>\$</b> * |

|--------|-----------------------------|-------------|

| 0      | Data-transfer hardware busy | ,           |

| 1      | Data-transfer hardware idle |             |

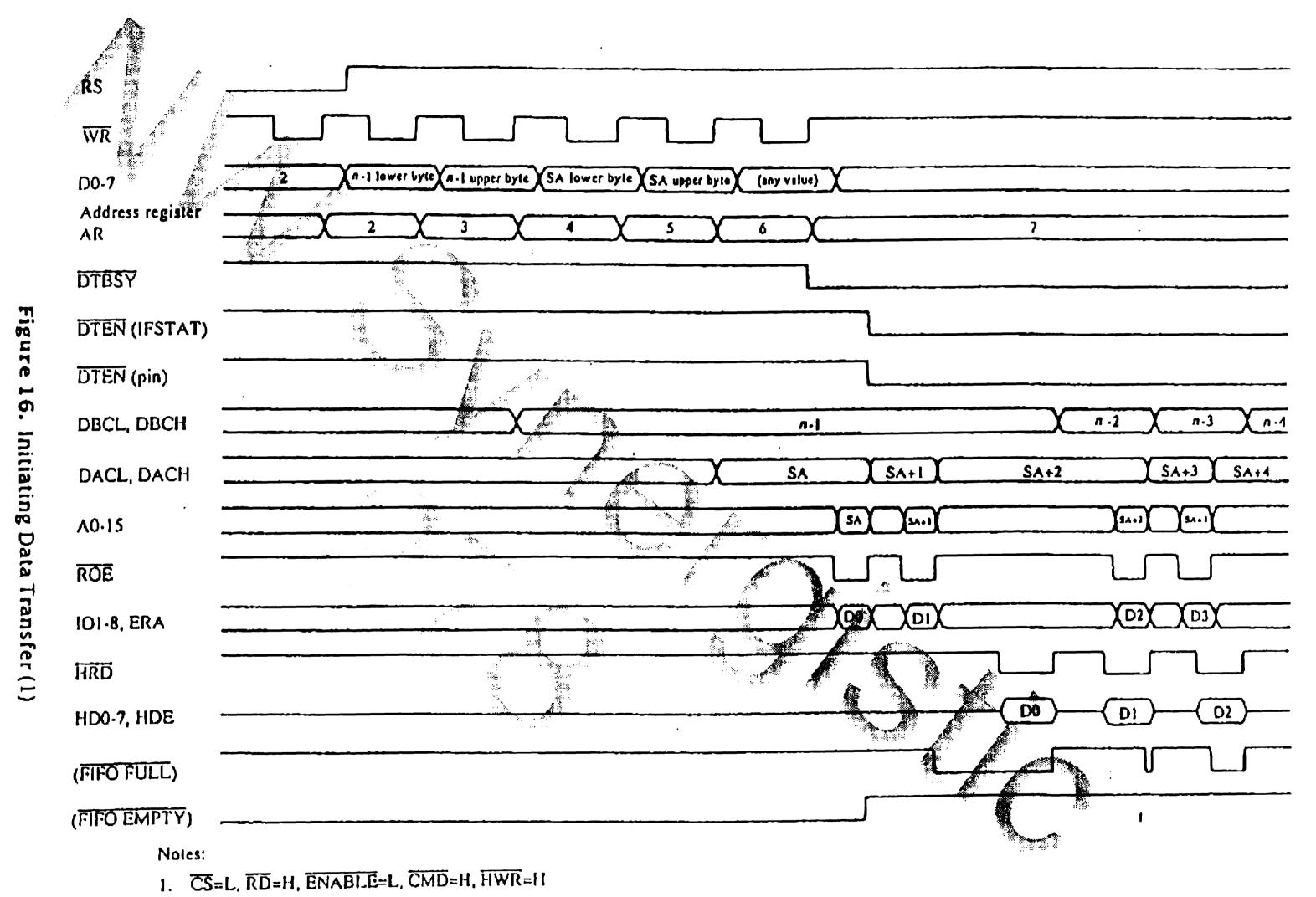

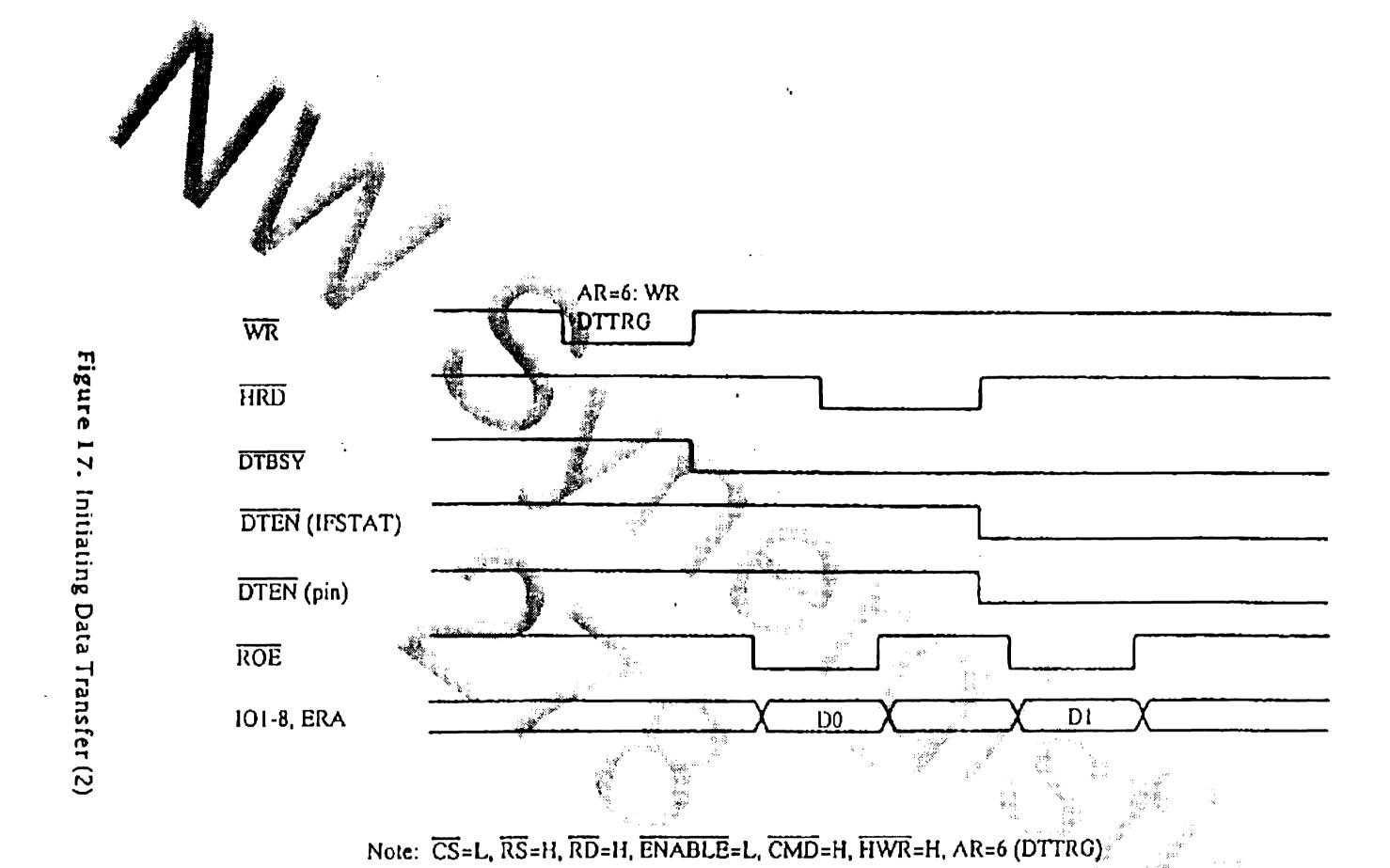

Sets DTBSY to 0. See figures 16 and 17 Initiative Data Transfer (1) and (2).

5. STBSY — Status Busy

|   |        | NAME OF THE PROPERTY OF THE PR |

|---|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Status | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 0      | Status-byte readout hardware busy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| , | 1      | Status-byte readout hardware idle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

6. DTEN — Data Enable

|    |        |                                         |                 |         | <u> </u> |

|----|--------|-----------------------------------------|-----------------|---------|----------|

|    | Status | *************************************** | Operation       |         |          |

|    | 0      | Data tr                                 | ansfer in prog  | ress    | *-       |

| ź. | 14.00  | No dat                                  | a transjer in p | rogress |          |

7. STEN — Status Enable

| Status | Operation /                         |

|--------|-------------------------------------|

| 0      | Status-byte transfer in progress    |

| 1      | No status-byte transfer in progress |

#### 11.3.2 IFCTRL — Interface Control Register

| 9177   | BIT6   | BIT5   | BIT4  | ВІТЗ  | BIT2  | BIT1   | BITO   | R/W |

|--------|--------|--------|-------|-------|-------|--------|--------|-----|

| CMDIEN | DTEIEN | DECIEN | CMOBK | DTWAI | STWAI | DOUTEN | SOUTEN | w   |

This register provides control functions for the host interface.

Resetting the chip clears all bits in this register.

1. CMDIEN, DTEIEN, DECIEN — Enable bits for CMDI, DTEI and DECI

These are all interrupt mask bits. Note that even when a mask bit is set to 1, the corresponding interrupt bit in the IFSTAT register is unmasked. Setting an interrupt forces the INT pin to LOW. See figure 11 Interrupt Control Flags.

CMDIEN, DTIEN and DECIEN do not clear interrupt requests. The INT pin will immediately go LOW if an interrupt is ended (by setting a bit to 1) during an interrupt request.

2. CMDBK — Command Break

This bit enables/disables the command break function.

| Status | Operation              |

|--------|------------------------|

| 0      | Command break enabled  |

| 1      | Command break disabled |

A command break is the suspension of data or status-byte transfer to the host computer caused when the host computer writes a command byte to the command buffer. The data-transfer end interrupt, DTEI is not generated by a command break.

3. DTWAI - Data Transfer Wait

This bit enables disables the data-transfer wait function.

| Status | Operation •                 |

|--------|-----------------------------|

| 0      | Data-wait function enabled  |

| 1      | Data-wait function disabled |

The data wait function allows the LC8950 to delay the hardware execution data transfer until a status-byte transfer (a STEN pin LOW condition) is clearly. In other words, if the DTTRG register is written to while the TEN bit in the IFSTAT register is 0, the DTEN bit is not cleared until the STEN bit is set to 1.

Disabling the data-transfer wait function allows data transfers to take place independently of status-byte transfers. Also note that these enable its do not clear interrupt requests.

The INT pin will immediately go LOW if an interrupt is enabled (by setting a bit to 1) during an interrupt request.

4. STWAI - Status-Transfer Wait

This bit enables/disables the status-transfer wait function.

| Status | Operation                     |  |  |  |  |  |

|--------|-------------------------------|--|--|--|--|--|

| 0      | Status-wait function enabled  |  |  |  |  |  |

| 1      | Status-wait function disabled |  |  |  |  |  |

The status-transfer wait function allows the LC8950 to delay the hardware execution of a status transfer until a data transfer (a DTEN pin LOW condition) is cleared. In other words, if the SBOUT register is written to while DTEN bit in the IFSTAT register is 0, the STEN bit is not cleared until the DTEN bit is set to 1.

Disabling the data wait function allows status-byte transfers to take place independently of data transfers.

5. DOUTEN, SOUTEN — Data Output Enable and Status Output Enable

DOUTEN enables/disables data transfers; SOUTEN enables/disables

status-byte transfers.

| Status | Operation @                    |

|--------|--------------------------------|

| 0      | Output disabled Output enabled |

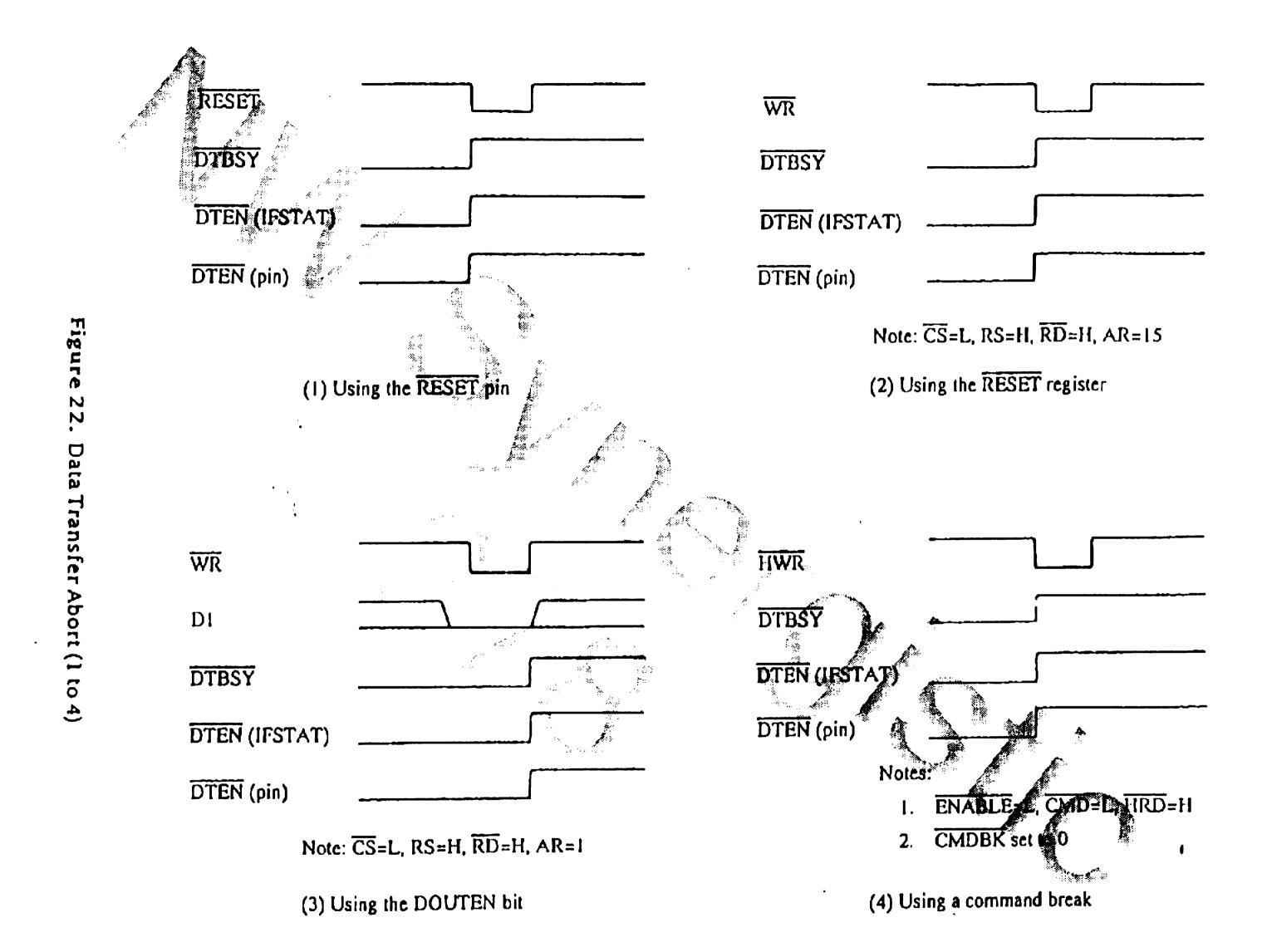

When DOUTEN is set to 0, any data transfers in progress are aborted. Similarly, when SOUTEN is set to 0, any status-byte transfers in progress are aborted.

#### 11.4 DBCL, DBCH — Data Byte Counters (Registers R2 & R3)

| OFFC: | BIT7 | BIT6     | BIT5      | BIT4 | ВІТЗ | BIT2 | BIT1 | BITO | R/W  |

|-------|------|----------|-----------|------|------|------|------|------|------|

| DBCL  |      |          |           |      |      |      |      | Isb  | TR/W |

|       |      | <b>Y</b> |           |      |      |      |      |      |      |

| 22211 | BIT7 | ВІТ6     | 8175      | 8174 | BIT3 | BIT2 | BIT1 | BITO | R/W  |

| DBCH  |      | DTEI dur | ing reads |      | msb  | R/W  |      |      |      |

DBCL and DBCH constitute a 12-bit counter used to set or monitor the number of bytes sent to the host computer during data transfers. DBCL (R2) and DBCH (R3) are the lower- and upper-byte counters, respectively.

To initiate a data transfer to the host computer, the controller writes the number of bytes to be transferred minus one to this counter. Then, while the DTEN pin remains LOW, the counter transfers bytes to the host, decrementing the counter by one each time a byte is passed. When the count reaches -1, that is, when a borrow occurs, the transfer halts and a data-transfer end interrupt is generated.

During a read, Bits 4 to 7 of the DBCH register have the same value as the four bits in DTEI (Bit 6 in IFSTAT) and indicate the end of a transfer when all are set to 1.

During a write, these bits are not significant.

#### 11.5 DACL, DACH — Data Address Counter (Registers R4 & R5 during writes)

| DAG  | BIT7 | BIT6 | BIT5 | BIT4 | 8173 | BIT2 | BIT1 | BITO  | R/W   |

|------|------|------|------|------|------|------|------|-------|-------|

| DACL |      |      |      |      |      |      |      | lsb   | _W    |

|      | BIT7 | BIT6 | BITS | BIT4 | ВІТЗ | BIT2 | BIT1 | BITO. | » R/W |

| DACH | 1    | 1    | i    | 1    |      | L    | I    | W.572 |       |

This 16-bit write-only register is used to specily the RAM bulker additions of the head byte of the data blocks to be transferred to the host.

Once the address has been set, it is incremented automatically as successive bytes are transferred into the 2-byte FIFO transfer buffer. Note, however, that the number of times the counter is incremented may not match, the number of read operations performed by the host. As loading and transfer are performed asynchronously, byte counts may not match.

#### 11.6 DTTRG — Data Transfer Trigger (Register R6 during writes)

| BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 1 BIT1 | BITO | R/W |

|------|------|------|------|------|-------------|------|-----|

|      |      |      |      |      |             |      | w   |

The controller writes to this register to activate the hardware for data transfer to the host. The content of the data written is not significant.

For the write to take place, the DOUTEN bit in the IFCTRL (R1-WR) register must be set to 1. When the data transfer hardware is operating, the DTBSY bit of the IFSTAT (R1-RD) register is set to 0, and the DTTRG register must not be written to.

## 11.7 DTACK — Data Transfer End Acknowledge (Register R7 during writes)

| BIT7 | BIT6 | BIT5 | BIT4 | 9173 | 8172 | BIT1 | BITO | R/W |

|------|------|------|------|------|------|------|------|-----|

|      |      |      |      |      |      |      |      | w - |

The controller writes to this register to clear the data-transfer end interrupt condition at the DTEI bit in the IFSTAT register and at the INT pin.

# 11.8 HEAD0 to HEAD4 — Header/Subheader Data (Registers R4 to R7 during reads)

| NEV DO | BIT7                           | BIT6 | BIT5 | BIT4    | <b>BIT3</b> | BIT2  | BIT1 | ВІТО                                  | <del>R</del> /W                       |  |

|--------|--------------------------------|------|------|---------|-------------|-------|------|---------------------------------------|---------------------------------------|--|

| HEAD0  | msb MINUTES/FILE NUMBER Isb    |      |      |         |             |       |      |                                       |                                       |  |

|        |                                |      |      |         |             |       |      |                                       |                                       |  |

| HEAD1  | BIT7                           | BIT6 | BIT5 | BIT4    | BIT3        | BIT2  | BIT1 | BITO 3                                | R/W                                   |  |

| 1 - 1  | msb SECONDS/CHANNEL NUMBER Isb |      |      |         |             |       |      |                                       |                                       |  |

|        |                                |      |      |         |             |       |      | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |  |

| HEAD2  | BIT7                           | BIT6 | BIT5 | BIT4    | BIT3        | BIT2  | BIT1 | 4 1                                   | R/W                                   |  |

|        | msb BLOCKS/SUBMODE             |      |      |         |             |       |      |                                       | R                                     |  |

|        |                                |      |      |         |             |       |      |                                       |                                       |  |

| HEAD3  | 8177                           | 81T6 | BIT5 | BIT4    | ВІТЗ        | BIT2  | BIT1 | BITO                                  | R/W                                   |  |

| HEAD3  | msb                            |      | MODE | /CODING | INFORM      | ATION |      | lsb                                   | R                                     |  |

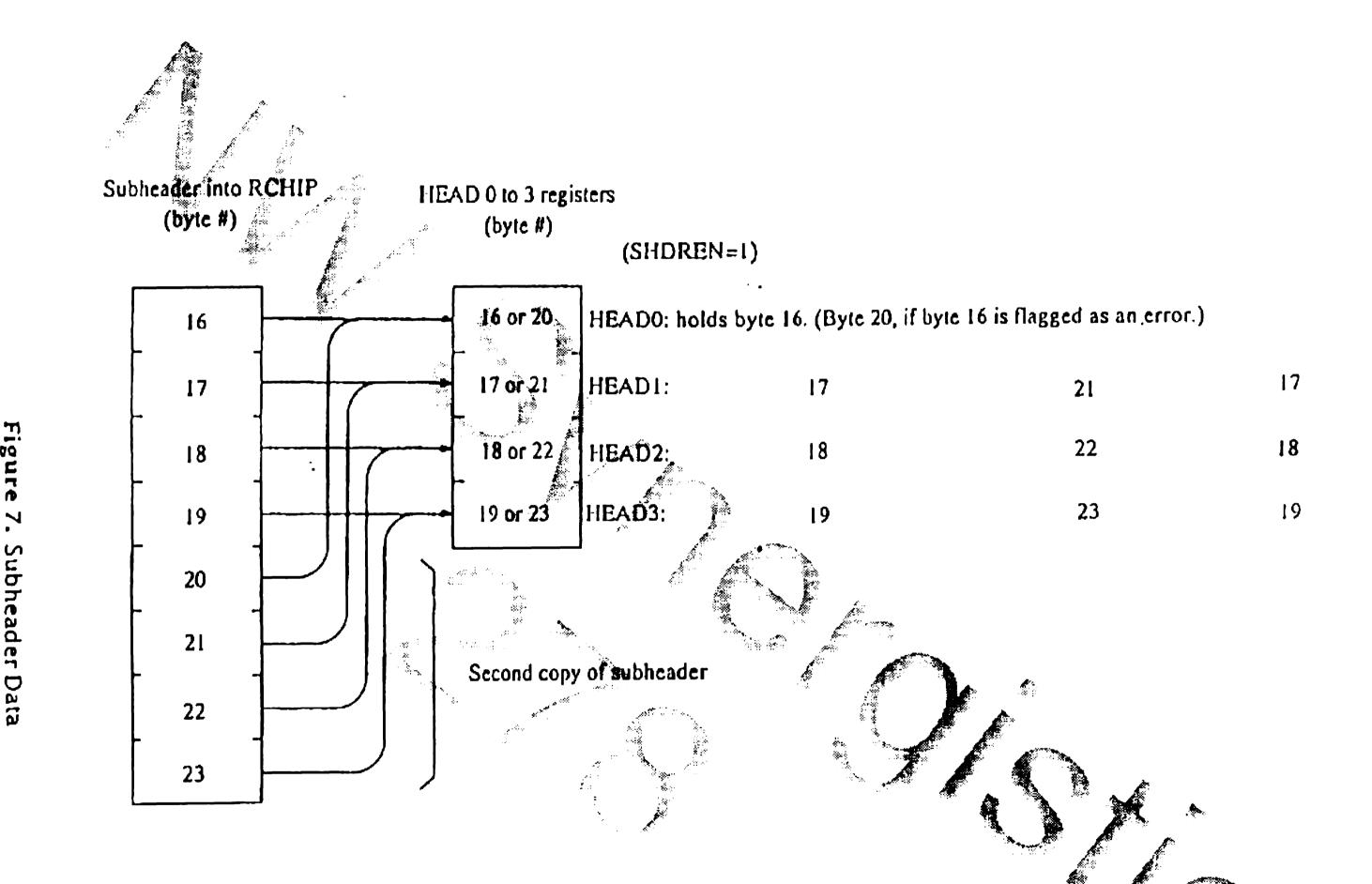

These registers are used to hold the header and subheader data of the current block.

To read the header data set, the SHDREN bit in the CTRL1 register is set to 0; to read the subheader data, set SHDREN to 1. The following byte numbers correspond to the block (sector) byte numbers in Modes 1 and 2 in which the head of sync block is Byte 0.

#### When SHDREN is 0:

HEADO: Header MINUTES (byte 12)

HEAD1: Header SECONDS (byte 13)

HEAD2: Header BLOCKS (byte 14)

HEAD3: Header MODE (byte 15)

#### When SHDREN is 1:

HEADO: Subheader FILE NUMBER (byte 16 0000)

HEAD1: Subheader CHANNEL NUMBER (byte 17 or 21)

HEAD2: Subheader SUBMODE NUMBER (byte 18 or 22)

HEAD3: Subheader CODING INFORMATION (byte 19 or 23)

These registers normally hold subheader data from Bytes 16 to 19. If the error flags for any of these bytes are set, the data for that byte are read from the corresponding location in Bytes 20 to 23.

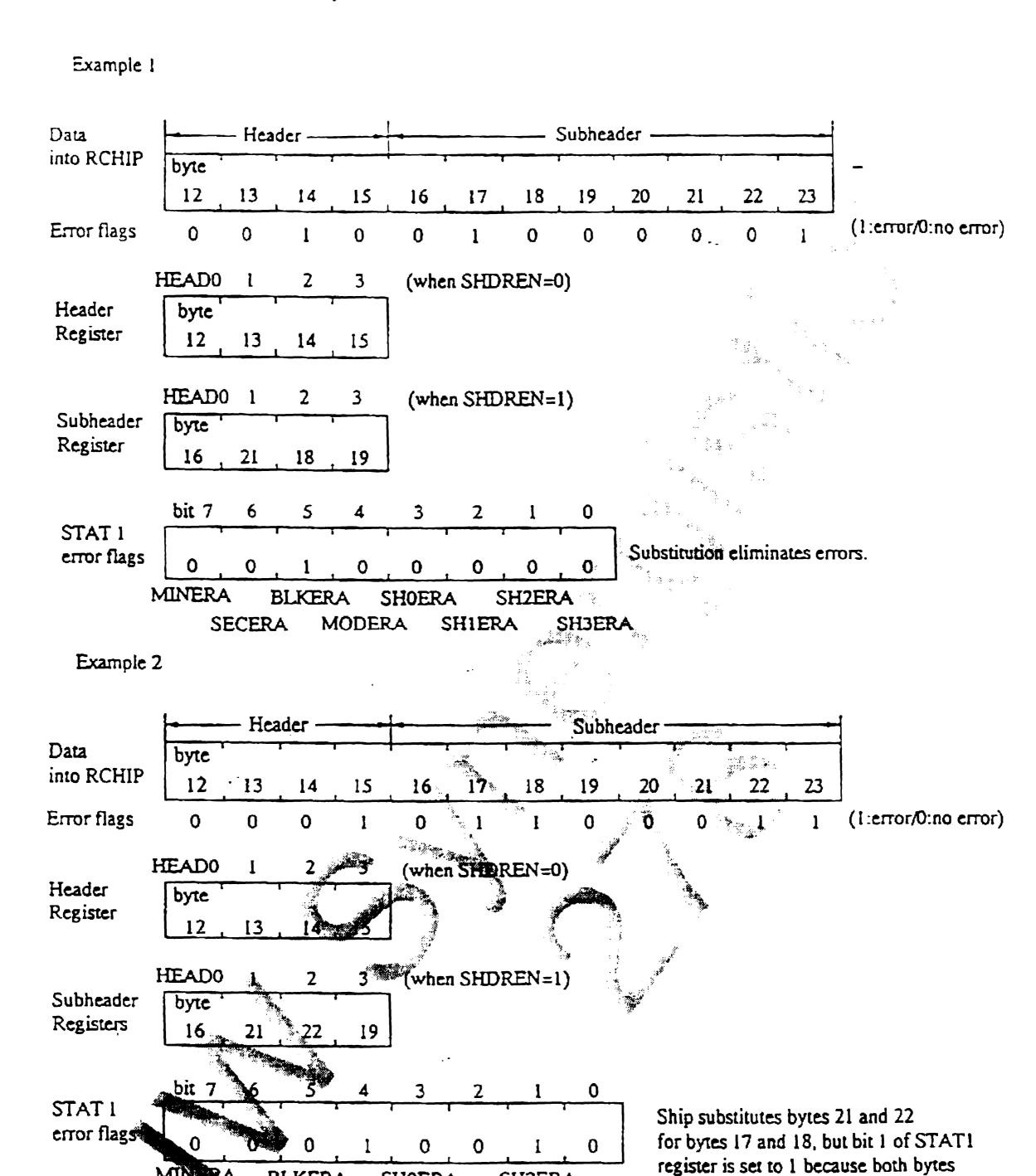

in prors occur both in the original data and in the designated corresponding bytes. Let's 20 to 23 are read for the subheader data. See figure 7 Subheader Pata. The error flags for the header and subheader bytes can be read from the STAT1 register. After error correction, these registers display the eader and subheader data of the current block.

Note:

The CD-I disc specification provides

duplicate copies of the subheader on disc.

Figure 8. Header, Subheader and Error Flags for HEADO to 3 and STAT1 Resisters

**SH3ERA**

18 and 22 contain errors.

SH2ERA

**BLKERA**

**SHOERA**

SHIERA

MODERA

When the LC8950 is set to monitor-only mode, these registers display the header and subheader of the block currently being written to the buffer RAM. In other modes, these registers display the block currently being decoded.

After a reset, the register state is undefined.

# 11.9 PTL, PTH — Block Pointers (Register R8 & R9 during reads; Registers R12 & R13 during writes)

| GTI | BIT7 | BIT6 | BIT5 | BIT4 | ВІТЗ | BIT2 | BIT1 | BITO | R/W   |

|-----|------|------|------|------|------|------|------|------|-------|

| PTL |      |      |      |      |      |      |      | lsb  | · R/W |

|     | ВІТ7 | BIT6 | вітѕ | BIT4 | ВІТЗ | BIT2 | BIT1 | BITO | R/W   |

| PTH | msb  |      |      |      |      |      |      |      | R/W   |

PTL and PTH are the lower and upper bytes, respectively, of this pair of registers. They hold a 16-bit pointer to the RAM address of the head of the current data block after correction. Writing to this register directs the LC8950 to perform error correction on any block in the buffer RAM.

The LC8950 defines the MINUTES byte in the header (Byte 12) at the head of the block and the 12 sync bytes (Bytes 0 to 11) are at the tail of the block. Each block contained in the buffer is taken to be the 2352 bytes from the MINUTES byte of the header through the 12 sync bytes of the next block.

The controller can transfer the decoding block back to the host by copying the address in this register and writing it to the DACL/DACH register immediately after decoder interrupts.

When the WRRQ bit in the CTRLO register is set to 1, this pointer is updated at the sync signal of every 2352-byte block.

# 11.10 WAL, WAH — Write Address Register (Registers R10 & R11 during reads; Registers R8 & R9 during writes)

| WAL | 81T7 | BIT6 | BIT5 | BIT4          | 8IT3         | BIT2 | BIT1     | BITO | B/W |

|-----|------|------|------|---------------|--------------|------|----------|------|-----|

|     |      |      |      |               |              |      |          | lsb  | R/W |

|     |      |      |      | , <del></del> | <del>,</del> |      |          |      |     |

| WAH | BIT7 | BIT6 | BIT5 | BIT4          | BIT3         | BIT2 | BIT1     | BITO | R/W |

| WAA | msb  |      |      |               |              |      | <b>é</b> |      | R/W |

|     |      |      |      |               |              |      |          |      |     |

These registers contain a pointer into write the address to the RAM buffer for the raw data input from the CD device. WAL and WAH are the lower and upper bytes, respectively.

This pointer is automatically incremented during data transfer—that is, while the DECEN and WRRQ bits in the CTRLO register are set to 1, a read operation on the write address register will not return a manningful value. To ensure that the returned value is accurate, the register contents should be read only after DECEN or WRRQ has been set to 0. For the same reason, either DECEN or WRRQ should be set to 0 before writing an address to this register.

After a reset, the register contents are undefined.

#### 11.11 CTRL0 — Control 0 (Register R10 during writes)

| BIT7  | BIT6  | BIT5  | BIT4   | ВІТЗ   | BIT2 | BIT1 | BITO | R/W |

|-------|-------|-------|--------|--------|------|------|------|-----|

| DECEN | EDCRQ | E01RQ | AUTORO | ERAMRO | WRAQ | QRQ  | PRQ  | w   |

Resetting the chip sets all the bits in this register to 0.

#### 1. DECEN — Decoder Enable

This bit enables/disables decoding functions.

| Status | Operation       |

|--------|-----------------|

| 0      | Disable decode. |

| 1      | Enable decode.  |

Setting this bit to 1 enables the decoding functions, including write to buffer, decoding EDC (error detection code), and decoding ECC (error correction codes such P-codes and Q-codes). This also enables the WRRQ EDCRQ QRQ and PRQ bits in the CTRLO register.

## 2. EDCRQ — EDC Decoding Request

This bit is set to 1 while DECEN is 1 to enable the error detection (decoding EDC) after and decoding ECC.

The EDC decoding, which is timed using the LC8950's internal blocksync signal, is performed after all other error correction processes have been completed.

The completion of the EDC decoding generates a decoder interrupt.

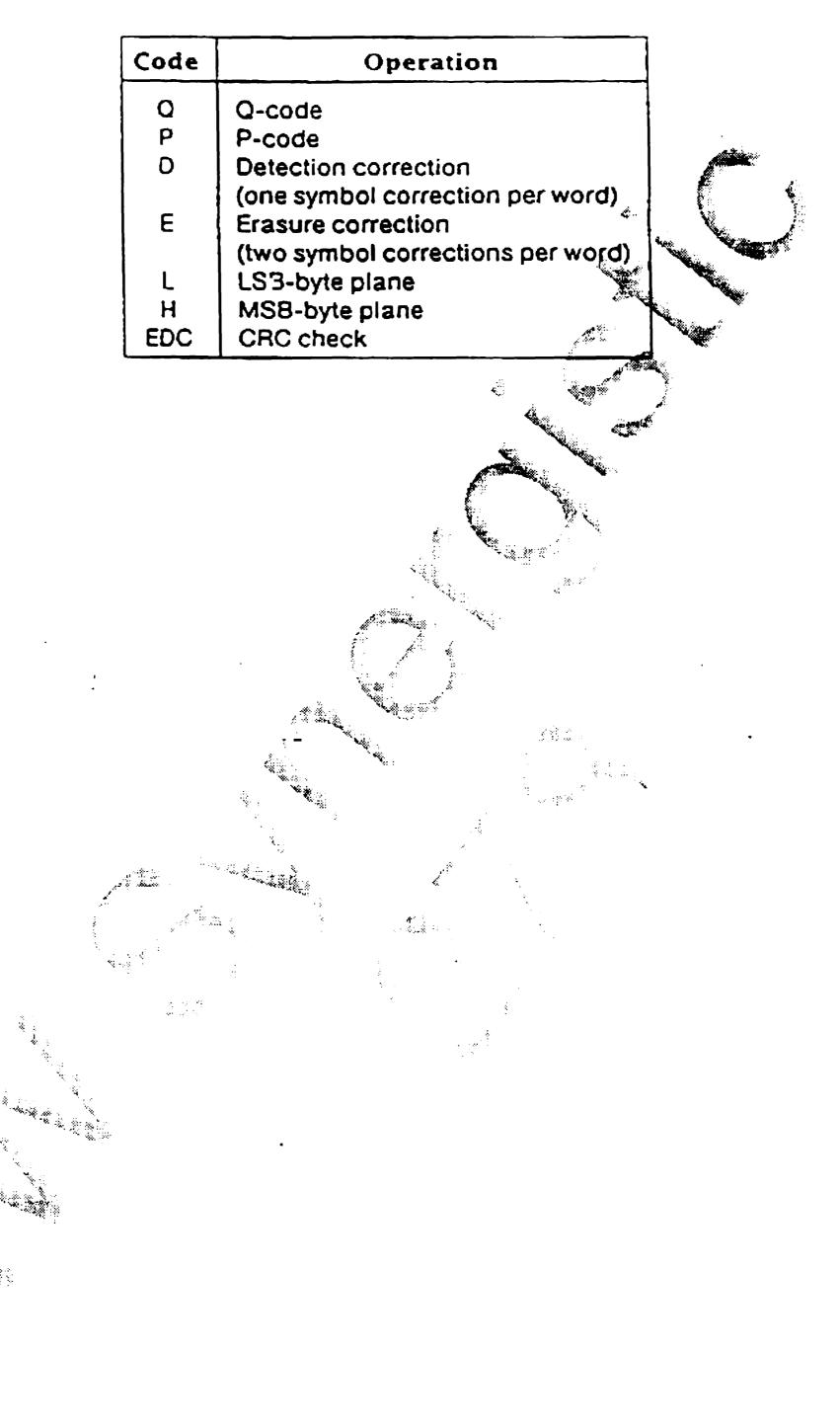

## 3. E01RQ — Error Detect-and-Correct Request

This bit allows system designers to select the most appropriate error handling.

| <u> </u>       |                                                                                                |

|----------------|------------------------------------------------------------------------------------------------|

| Statu <b>s</b> | Operation                                                                                      |

| Ö              | Disable error correction of bytes for which an error has been detected, but not yet corrected. |

| 1              | Enable error correction of bytes for which an error has been detected, but not yet corrected.  |

Setting bit to 0 can suppress miscorrections resulting from too many errors when an efficient error detection algorithm is implemented in the RC (Cross-Interleaved Reed-Solomon Code) decoder, and when errors are localized. Error correction improves significantly at higher error rates when an efficient CIRC decoding scheme is implemented.

Erasure is disabled when the ERAMRQ bit in the CTRLO register is 0. Setting E01RQ to 0 suppresses error correction.

## 4. AUTORQ — Automatic Correction Mode Selection Request

Setting this bit to 1/0 during MODE 2 enables/disables automatic error correction mode when the FORM bit in the subheader is read.

This bit is significant only during MODE 2 error correction—that is, when the MODRQ bit in the CTRL1 register is set to 1.

| Statu | s Operation                         |

|-------|-------------------------------------|

| 0     | Disable automatic error correction. |

| 1     | Enable automatic error correction.  |

The CRC check performed by the EDC also differs in accordance with the FORM flag setting.

## 5. ERAMRQ — Erasure RAM Request

This bit enables/disables reading of the error flag data in the erasure RAM, that is the one-bit buffer RAM for C2PO.

| Status | Operation                 |

|--------|---------------------------|

| . 0    | Disable error flag reads. |