SPECTRA LOGIC CORPORATION 1227 INNSBRUCK DRIVE SUNNYVALE, CALIFORNIA 94086 408 744-0930 TWX 910 339-9566 TELEX 172524 SPL SUVL

# SPECTRA 10 PRODUCT REFERENCE MANUAL

## TABLE OF CONTENTS

| SECTION                         | TITLE                                                                                         |

|---------------------------------|-----------------------------------------------------------------------------------------------|

| 1.0<br>1.1<br>1.2<br>1.3<br>1.4 | GENERAL INFORMATION Introduction Features Functional Characteristics Specifications Versions  |

| 2.0<br>2.1<br>2.2               | INSTALLATION Installation Procedures Option Switches                                          |

| 3.0<br>3.1<br>3.2<br>3.3        | THEORY OF OPERATION<br>Instruction Formats<br>Register Definitions<br>Hardware Operation      |

| 4.0<br>4.1<br>4.2<br>4.3        | DIAGNOSTICS<br>Microdiagnostics and LED's<br>Diagnostic Software<br>Drive Configuration Table |

| 5.0                             | SYSTEM SOFTWARE                                                                               |

| APPENDIX A                      | SMD Cable Connections                                                                         |

| APPENDIX B                      | Troubleshooting Checklist                                                                     |

CONFIDENTIAL - SPECTRA LOGIC CORPORATION This document contains confidential information of Spectra Logic Corporation and may not be used or copied without the prior written consent of Spectra Logic Corporation.

SERTAL NO. 443

Document P/N: 8500001

Revision:

$\mathbf{E}$

Date:

Jan 13, 1982

#### 1.0 GENERAL INFORMATION

#### 1.1 INTRODUCTION

The SPECTRA 10 is an emulating disk controller for Data General Nova/Eclipse compatible computers. The controller is contained on a single DG compatible PCB and attaches up to four (4) Storage Module (SMD) compatible disk drives.

The SPECTRA 10 emulates the DG 6067 disk subsystem and can accommodate a wide range of SMD compatible disk drives. The SPECTRA 10/A provides operating system and diagnostic software transparency when using 80MB SMD compatible disk drives. The SPECTRA 10/A also provides increased storage capacity on the 80MB SMD through a software parameter change (expanded emulation). Similarly, the SPECTRA 10/A version utilizes expanded emulation to attach 300MB SMD compatible disk drives. Up to two of the popular fixed/removable media CMD compatible disk drives can be attached using the SPECTRA 10/D version. The Spectra 10/B provides for attachment of Priam 3450 or BASF Drives with 13,440 bytes per track and limited to 24 sectors per track. The 10/B retains the capability to handle the same drives as the 10/A; at 24 or 32 sectors per track.

#### 1.2 FEATURES

#### 1.2.1 Performance

The SPECTRA 10 provides many important performance features such as:

A. 11 bit burst Error Correction Code (ECC), with local buffer correction of data transparent to system software.

- B. Overlapped Seek on up to four (4) drives to improve access time.

- C. Three (3) sector data buffer of 1536 bytes to eliminate "data lates".

- D. A data channel throttle control to provide a switch selectable burst of 1 to 256 words, with the host microprocessor fixing the "Off Channel" time in firmware. Up to 256 words are transferred consecutively, then a fixed period of time observed before generating additional data requests to allow data channel access by other devices.

- E. Multiple sector transfers up to 8K words per read or write command to avoid lost disk rotations. Optionally, sector interleaving can be provided to balance performance in single sector RDOS applications.

- 1.2.2. Single Printed Circuit Board The SPECTRA 10 occupies only one slot in the DG Nova/Eclipse. The single board design provides cost savings in chassis, power, ease of maintenance, spares, and enhanced reliability.

- 1.2.3. Full Emulation The SPECTRA 10/A is transparent to standard DG RDOS/AOS operating systems and diagnostic software. Emulation of the DG 6067 subsystem is provided by the SPECTRA 10/A when used with 80MB SMD compatible disk drives.

- 1.2.4. System Compatibility The SPECTRA 10 is compatible with all models of DG Nova and Eclipse systems or equivalents.

- 1.2.5. Disk Drive Attachment Up to four (4) 80MB SMD compatible drives may be attached to the SPECTRA 10 without any modification to the operating system. SMD drives of any capacity may be attached through the expanded emulation mode. Either removable media, fixed Winchester, or combination fixed/removable drives may be attached.

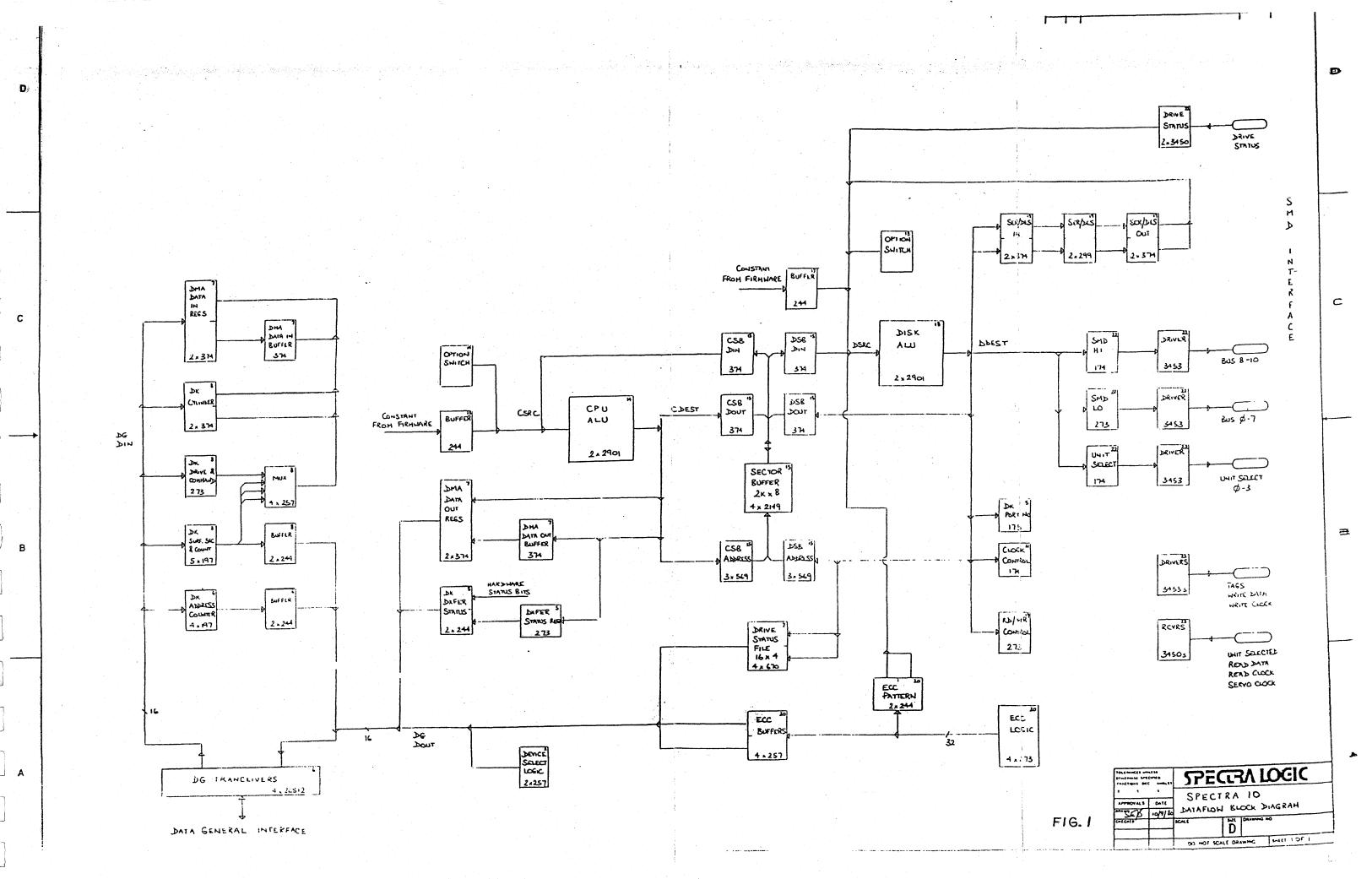

- 1.2.6. Advanced Architecture A dual bipolar bit slice microprocessor architecture for simultaneous control of the disk interface and host interface provides performance improvements in data transfers and simplifies firmware configuration changes.

- 1.2.7. Reliability and Maintainability The SPECTRA 10 provides high reliability through a single PCB, use of pretested IC's and elimination of multi-PCB interconnections and power supplies. On board self-test microdiagnostics provide simple diagnosis, and LEDs aid in fault isolation. In addition, system level diagnostics may be used to verify controller operations.

#### 1.3.0. FUNCTIONAL CHARACTERISTICS

- 1.3.1. Computer Interface The controller is compatible with any model DG Nova or Eclipse computer interface. Data transfer occurs over the standard or high-speed data channel.

- 1.3.2. Disk Interface The disk interface is compatible with the industry standard Storage Module Drive flat cable interface. Up to four (4) drives utilizing either removable or fixed media may be attached. The control cable is daisy chained to the four (4) drives and the data cables are attached radially to each drive.

- 1.3.3. Software Transparency The SPECTRA 10/A emulates the DG 6067 disk subsystem when using 80MB SMD drives and runs under RDOS, AOS, IRIS, and BLIS/COBOL without software modification.

- 1.3.4. Design Architecture The SPECTRA 10 uses a high performance dual bipolar bit slice microprocessor architecture to provide separate dedicated control of the host CPU and disk interfaces. This approach permits high speed operation through concurrent control and allows flexibility in future disk attachments.

- 1.3.5. <u>Data Buffering</u> A 1536 byte (three sector) high speed RAM buffer is provided for buffering data between the disk and DG Nova/Eclipse. The buffer eliminates "data late" conditions and permits optimum speeds to be achieved by smoothing the differences in transfer rates between the disk and data channel.

- 1.3.6. Configurations In addition to the standard DG 6067 emulation, the expanded emulation mode permits attachment of other SMD type drives, including the CMD 9448. The 6060 series command set is used for both modes, with parameter extensions in the expanded emulation mode. Removable pack SMD disk drives may be mixed with fixed Winchester type SMD compatible drives.

- 1.3.7. Error Detection and Correction A 32 bit ECC polynomial is used to detect and correct data errors up to 11 consecutive bits in length. Error correction may optionally be performed within the controller's data buffer.

- 1.3.8. <u>Bad Blocks</u> Bad block or defective sector flagging is provided under standard DG software control.

- 1.3.9. Position Verification The controller automatically verifies position by reading and comparing the cylinder, head, and sector numbers contained in the header prior to any non-format read or write operation. An automatic 16 bit CRC check is also performed on the header information to ensure its validity. These two checks eliminate addressing errors.

- 1.3.10. <u>Self-Test</u> An automatic microdiagnostic self-test is performed upon each power up. In the event an error is detected, an LED is lit.

- 1.3.11. Memory Address Range The controller's memory addressing range for data transfers is 0 to 64K words. Memory mapping is handled by the Nova/Eclipse.

- 1.3.12. <u>Device Codes</u> The standard device code is 27g with 67g as an option. The device code is established in the controller by setting a DIP switch to the desired address.

- 1.3.13. Interrupt Priority The interrupt priority is set to 7 as standard.

- 1.3.14. <u>Dual Port</u> As a standard feature, the SPECTRA 10 supports suitably equipped dual ported disk drives.

#### 1.4.0. SPECIFICATIONS

- 1.4.1. Single P.C. Board The controller is contained on one DG equivalent PCB, 15" x 15", multilayer. The controller mounts in one slot of the CPU or expansion chassis. The embedded single board design saves space, provides high reliability, and ease of maintenance.

- 1.4.2. Error Display Two sets of LEDs, one for each microprocessor, display error status for convenient user diagnosis.

- 1.4.3. <u>Drivers and Receivers SMD compatible balanced line drivers and receivers assure reliable operation of the disk drives up to 50 feet from the Nova/Eclipse computer.</u>

- 1.4.4. Cable Connectors A 60 pin control cable ('A' cable) connector is provided at the side edge of the PCB; mates to 30 TWP flat cable.

Four 26 pin data cable ('B' cable) connectors are provided at the side edge of the PCB, allowing attachment of up to 4 SMD disk drives; mate to 26 conductor flat shielded ribbon cables.

- 1.4.5. Power Uses internal +5V at 7 amps, and -5V at .7 amps maximum.

- 1.4.6. Environmental Exceeds all Nova/Eclipse temperature and humidity specifications.

## 1.5 SPECTRA 10 VERSIONS

The table below lists the curently available and planned versions of the SPECTRA 10.

| Characteristics                                                                       | 10/A or B*                                                    |                                       | 10/D                                    |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------|-----------------------------------------|

| DG Emulation 6067(50 MB)                                                              | 6067(50MB)                                                    | 6067(50MB)                            | 6067(50MB)                              |

| SMD Compa- CDC 9762 SMD<br>tible Drives CDC 9730 MMD<br>Ampex 980<br>Century Data T82 | CDC 9762 SMD<br>CDC 9730 MMD<br>Ampex 980<br>Century Data T82 | CDC 9766 Ampex 9300 Century Data T302 | CDC CMD 9448<br>Ampex DFR 900<br>drives |

| Drive Capacity 80 (MB)                                                                | 80                                                            | 300                                   | 32/64/96                                |

| Media Type Removable;<br>Fixed<br>Winchester                                          | Removable;<br>Fixed<br>Winchester                             | Removable                             | Fixed-<br>Removable                     |

| Emulation Mode Standard                                                               | Expanded                                                      | Expanded                              | Expanded                                |

| Sectors/Track 24                                                                      | 32                                                            | 32                                    | 32                                      |

| Track/Cylinder 5                                                                      | 5                                                             | 19                                    | 2/4/6                                   |

| Cylinder/Drive 815                                                                    | 823                                                           | 823                                   | 823                                     |

| Sector Size(bytes) 512                                                                | 512                                                           | 512                                   | 512                                     |

| Formatted 50.1<br>Capacity(MB)                                                        | 67.4                                                          | 256.4                                 | 27.0/53.9/80.9                          |

<sup>\*10/</sup>B Provides for attachment of Priam 3450 or BASF Drives with 13,440 Bytes per track; 24 sectors only.

#### 2.0 INSTALLATION

#### 2.1.0. INSTALLATION PROCEDURES

This section contains the information needed to install a SPECTRA 10 disk controller. The SPECTRA 10 can be installed in any Data General Nova/Eclipse or equivalent. Maintenance personnel should be familiar with both DG hardware and the specific SMD type drive being installed.

#### 2.1.0.1. Inspection

Perform a thorough visual inspection of the SPECTRA 10 P.C.B. and SMD interface cables after removal from their shipping container. Note any damage and notify the freight carrier immediately as Spectra Logic's warranty does not cover shipping damage. The damage claim is to be filed through the carrier with its insurance company.

Check for any broken components or bent pins, and ensure that all IC's in sockets are securely in place. DO NOT remove IC's from sockets unless absolutely necessary to re-seat properly. If any are re-inserted, observe correct seating with respect to pin 1 of the socket.

## 2.1.0.2. Configuration Verification

Ensure the device select code is set for 27g or 67g in the switch at location 10J. Set the switches in location 9J for the operation desired as described in paragraph 2.2.2. Set the switches in location 3H for the configuration of the drive attached; refer to paragraph 2.2.3.

#### 2.1.0.3. P.C.B. Installation

The SPECTRA 10 P.C.B. is to be installed only after inspection and switch settings are verified. Check the back panel sockets in the slot intended for use to ensure keys will align properly with the slots in the P.C.B.

Prior to insertion, ensure the interrupt priority chain (INTP IN, INTP OUT) on backpanel pins A96 and A95 are connected but not shorted or bypassed on the slot intended for the SPECTRA 10. In addition, check the data channel priority chain (DCHP IN, DCHP OUT) on backpanel pins A94 and A93 to ensure they are also connected but not shorted or bypassed.

After completing the visual inspection, configuration switch check, backpanel preparation, and ensuring that <u>POWER IS OFF</u>, insert the SPECTRA 10 P.C.B. Insertion should be accomplished without forcing it into the backpanel. Once it makes contact with the backpanel connectors, use the P.C.B. extractor levers to "pull" the P.C.B. into a final seating position. If any warpage exists, exert slight pressure above or below the P.C.B. while determining visually if the card edge connectors are aligning properly with the backpanel while pushing into the initial seating position. Ensure the P.C.B. seats fully and components face the same direction as on other boards.

## 2.1.0. INSTALLATION PROCEDURES (cont.)

#### 2.1.0.4. SMD Cable Installation

The SMD cables are to be connected after installing the SPECTRA 10 in the chassis. Ensure that pin 1 of the cables mates with pin 1 of the P.C.B. Both the 60 pin and the 26 pin cable connectors and the P.C.B. headers have a small arrowhead designating pin 1.

Attach the 60 conductor "A" cable and 26 conductor "B" cable to the headers on the back end of the P.C.B. If less than four drives are to be attached, any of the four headers provided may be used. Route the cables out of the chassis neatly, using folds as required. If the chassis is rack mounted, ensure the cables will permit extension of the rack. If multiple drives are installed, ensure a "daisy chain" cable is connected between drives and a terminator is installed on the last drive.

## 2.1.0.5. Power On

Upon completion of the above, power up the system. Ensure no LED's are lit on the SPECTRA 10. You may now proceed to initialize the disk and run diagnostics to verify correct operations.

#### 2.2.0. SPECTRA 10 SWITCHES

| 2.2.1. | Switch A | Location 10J                                                                                                                                                                                                                                             |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OFF    | SW1      | Switch Clock This switch is used in fault diagnosis during manufacturing. It is used to switch the phase of the clock in which the clock is stopped when used with the STEP diagnostic unit or the Spectra Logic test panel.                             |

| OFF    | SW2      | Not used.                                                                                                                                                                                                                                                |

| 27     | SW3-8    | Device Select 0-5 These switches are used to select the DG device code of the controller. The standard device code is 27 — switches 3, 5 are on; switches 4,6,7,8 are off. The alternate device code is 67 — switch 5 is on; switches 3,4,6,7,8 are off. |

ON 1369798

## 2.2.2. Switch B

Location 9J

SW1

ECC Buffer Correct

If this switch is off, the DG software will correct any ECC errors. If this switch is on, the controller will correct any ECC error transparently to the DG software.

SW2-4

Command Decode Options

The DG commands STOP DRIVE and WRITE DISABLE may be interpreted by the SPECTRA 10 controller to do other functions for diagnostic aid. The way these commands are interpreted is decided by these 3 switches as shown in the table below:

|                       |                           | •   | Stop Drive | Write Disable |

|-----------------------|---------------------------|-----|------------|---------------|

| SW4                   | SW3                       | SW2 | Command    | Command       |

| $\geq \overline{Off}$ | $\overline{\mathrm{Off}}$ | Off | Stop Drive | Write Disable |

| Off                   | Off                       | On  | Stop Drive | No-Op         |

| Off                   | On                        | Off | No-Op      | Write Disable |

| Off                   | On                        | On  | No-Op      | No-Op         |

| On                    | _                         |     | Read w/ECC | Write w/ECC   |

SW<sub>5</sub>

Dual Ported Drives

This switch is normally set to OFF. It should be set to ON if any other controllers are attached to dual ported drive(s) cabled to the SPECTRA 10.

SW6-8

**Burst Rate**

These switches are used to vary the number of words the controller will transfer at its maximum rate before pausing to give lower priority devices a chance to gain access to the Data Channel. The number of words transferred in one burst is as shown below:

|                                         | SW6                       | SW7                       | SW8 |           |

|-----------------------------------------|---------------------------|---------------------------|-----|-----------|

|                                         | $\overline{\mathrm{Off}}$ | $\overline{\mathrm{Off}}$ | Off | 2 words   |

|                                         | Off                       | Off                       | On  | 4 words   |

|                                         | Off                       | On                        | Off | 8 words   |

|                                         | Off                       | On                        | On  | 16 words  |

| *************************************** | On                        | Off                       | Off | 32 words  |

|                                         | On                        | Off                       | On  | 64 words  |

|                                         | On                        | On                        | Off | 128 words |

| *                                       | > On                      | On                        | On  | 256 words |

| 1 5                                     |                           |                           |     |           |

ON 3,4,7,8

## 2.2.3. Switch C Location 3H

2.2.3.1. For version A or B of the Firmware

Version A is identified by having PROM number 3A10Axx in location 3A, Version B by having Prom number 4B10BXX in location 4B.

SW1-2 Maximum Cylinder Number

The switches should be set according to the maximum cylinder number of the drive attached to the controller as given in the table below:

FOR 6067 EMULATIONS

| SW1                       | SW2 |                            |

|---------------------------|-----|----------------------------|

| $\overline{\mathrm{Off}}$ | Off | 815 cylinders or less 7308 |

| Off                       | On  | 823 cylinders              |

| On                        | Off | 1645 cylinders             |

| On                        | On  | More than 1645 cylinders   |

For mixed drive configurations, the switches should be set according to the highest cylinder number of any of the drives.

SW3

Maximum Sector Number

If this switch is OFF, the controller assumes there are 24 sectors per track. If this switch is ON, the controller assumes there are 32 sectors per track. NOTE: The disk drive sector count must also be set within the drive. Consult the disk drive user manual. This MUST BE OFF FOR PRIAM OR BASF Drives with 13,440 bytes per track.

SW4-8

e.g.:

Maximum Head Number

These switches should be set to the maximum head number of the drive attached to the controller.

|                  | SW4 | SW5                       | SW6 | SW7          | SW8  |

|------------------|-----|---------------------------|-----|--------------|------|

| CDC9766=19 heads | On  | $\overline{\mathrm{Off}}$ | Off | On           | On ← |

| CDC9762=5 heads  | Off | Off                       | On  | $\bigcap ff$ | On   |

For mixed drive configurations, these switches should be set according to the highest head number of any of the drives.

#### 2.2.3.2 For version D of the Firmware

This version is identified by having PROM number 3A10Dxx in location 3A. It will support up to two physical CMD or lark type disk drives. Each physical drive is divided into two logical drives, one being the fixed part of the media and the other being the removable part.

SW1 Logical to Physical Mapping Option

If SW1 is Off

Logical drive 0 = Physical drive 0, Removable part Logical drive 1 = Physical drive 0, Fixed part Logical drive 2 = Physical drive 2, Removable part

Logical drive 3 = Physical drive 2, Fixed part

If SW1 is On

Logical drive 0 = Physical drive 0, Fixed part

Logical drive 1 = Physical drive 0, Removable part

Logical drive 2 = Physical drive 2, Fixed part

Logical drive 3 = Physical drive 2, Removable part

Please note that the physical drives should only have either a 0 or a 2 plug.

SW2 Maximum Cylinder

SW2

Off Maximum cylinder number is 815 or less

On Maximum cylinder number is 823

SW3

Off

Maximum Sector number is 24

On

Maximum Sector number is 32

SW4 CDC Lark Drive (Firmware Rev A6 or above in location 3A)

SW5-8 Maximum Head (Fixed Part)

These Switches should be set to the number of fixed heads in drive attached to the controller.

e.g.: SW5 SW6 SW7 SW8 96MB CMD= Off 5 fixed heads Off On On CDC Lark OFF ON OFF ON

The logical drive number of the removable part has only one addressable head, head 0.

#### 3.0 THEORY OF OPERATION

The SPECTRA 10 controller is based on a dual microprocessor design. The CPU processor controls all the software visible registers except for Drive Status, First ECC Word, and Second ECC Word. It is responsible for decoding all commands, initiating commands, Data Channel transfers, and final termination of the commands. The software visible registers themselves are implemented in hardware, and they are read or written by the DG buss directly by hardware. The hardware ensures that the controller meets the timing limitations imposed by the DG buss. The DISK processor controls the disk interface and the Drive Status, First ECC Word, and Second ECC Word registers.

The two processors communicate with each other via the first 512 bytes of a The rest of this buffer is used to buffer 3 sectors of 2K byte RAM buffer. data between the two processors. This buffer is therefore called the Sector In addition, there are two flip-flops used for communication between the two processors. The first one is called GO. This is set by the CPU processor to inform the DISK processor that there is a command to perform. All information pertaining to this command will be available in the Communications Area of the Sector Buffer. When the DISK processor accepts this command, it will reset the GO flip-flop. The second flip-flop is called ATTENTION. This is set by the DISK processor to inform the CPU processor that it has finished a data transfer command and has updated all relevant status conditions. processor will wait for ATTENTION before completing the termination and setting DONE. It will also reset the ATTENTION flip-flop at this time in preparation for the next command.

A common oscillator running at 22 MHZ is shared by the two microprocessors. Each microprocessor operates on a clock phase opposite the other. This permits the RAM buffer to be accessed by both microprocessors without contention.

Whenever the SPECTRA 10 does not have a command active, both microprocessors go into idle loops. The CPU microprocessor essentially waits for a new command while the DISK microprocessor polls the four disk drive ports to update and maintain drive status. Any drive switching from a NOT READY to a READY state will cause an appropriate attention flag to set.

## 3.1.0. Instruction Formats

| SPEC      | CIFY C | OMMA           | ND AN   | ID DRI | VE     |         |        |        |                  | (DOA) |     |         |       |               |     |  |

|-----------|--------|----------------|---------|--------|--------|---------|--------|--------|------------------|-------|-----|---------|-------|---------------|-----|--|

| R/W<br>DN |        |                |         |        |        |         |        |        | E                |       | NOT | OT USED |       |               |     |  |

| 0         | 1      | 2              | 3       | 4      | 5      | 6       | 7      | 8      | 9                | 10    | 11  | 12      | 13    | 14            | 15  |  |

| SPEC      | CIFY C | YLIND          | ER      |        |        |         |        |        |                  |       |     |         |       |               |     |  |

| Cont      | ext: 1 | he pre<br>USED | vious 1 | DOA sp | ecifie | d a see | k oper |        | NDER             |       |     |         |       | (DOC)         | ) . |  |

| 0         | 1      | 2              | 3       | 4      | 5      | 6       | 7      | 8      | 9                | 10    | 11  | 12      | 13    | 14            | 15  |  |

| SPEC      | CIFY S | URFAC          | E, SEC  | CTOR A | AND C  | COUNT   |        |        |                  |       |     |         |       |               |     |  |

| Cont      | ext: 7 | he pre         |         |        | d not  | specify |        |        | ation.<br>DDRESS | S     |     | SECTO   | OR CO | (DOC)<br>DUNT |     |  |

| 0         | 1      | 2              | 3       | 4      | 5      | 6       | 7      | 8      | 9                | 10    | 11  | 12      | 13    | 14            | 15  |  |

| REA       | D SUR  | FACE,          | SECTO   | OR AN  | D COU  | JNT     |        |        | •                |       |     |         |       | (DIC)         |     |  |

|           | SURI   | FACE A         | ADDRE   | ESS    |        |         | SECT   | ror Al | DDRESS           | 3     |     | SECTO   | OR CO |               |     |  |

| 0         | 1      | 2              | 3       | 4      | 5      | 6       | 7      | 8      | 9                | 10    | 11  | 12      | 13    | 14            | 15  |  |

| SPE       | CIFY M | EMOR           | Y ADE   | RESS   |        | •       |        |        |                  |       | ,   |         |       | (5.05)        |     |  |

| EMA       |        |                |         |        |        | MEM     | ORY    | ADDRE  | SS               |       |     |         |       | (DOB)         |     |  |

| LSB<br>0  | 1      | 2              | - 3     | 4      | 5      | 6       | 7      | 8      | 9                | 10    | 11  | 12      | 13    | 14.           | 15  |  |

READ MEMORY ADDRESS

| Conte<br>EMA   | ext: A    | lterna  | te instr | ruction  | mode     |                | ORY A      | DDRES           | SS              |                 |            |                  |                  | (DIA)           |                  |

|----------------|-----------|---------|----------|----------|----------|----------------|------------|-----------------|-----------------|-----------------|------------|------------------|------------------|-----------------|------------------|

| LSB<br>0       | 1         | 2       | 3        | 4        | 5        | 6              | 7          | 8               | 9               | 10              | 11         | 12               | 13               | 14              | 15               |

| REAL           | DRIV      | E STA   | TUS      |          |          |                |            |                 |                 |                 |            |                  |                  | (DIB)           |                  |

| INV<br>ST<br>0 | RES<br>1  | TSP     | RDY<br>3 | BSY<br>4 | OFF<br>5 | WR<br>DIS<br>6 | 7          | ILL<br>ADR<br>8 | ILL<br>CMD<br>9 | DC<br>FLT<br>10 | UNS        | POS<br>FLT<br>12 | CLK<br>FLT<br>13 | WR<br>FLT<br>14 | DRV<br>FLT<br>15 |

| REAL           | DAT       | A TRA   | NSFER    | STAT     | rus      |                |            |                 |                 |                 |            |                  |                  | (DIA)           |                  |

| CNT<br>FUL     | R/W<br>DN | SEE     | K DON    | IE       |          | PAR            | SEC<br>ADD | ECC             | BAD<br>SEC      | CYL<br>ADD      | SEC<br>SRF | VFY              | R/W<br>TIM       | DAT<br>LAT      | R/W<br>FLT       |

| REAL           | FIRS      | T ECC   | WOR      | D s      |          |                |            |                 |                 |                 |            |                  |                  |                 |                  |

| Conte          | ext: Al   | ternate | e instru | etion    | mode 2   |                | WODD       |                 |                 |                 |            |                  |                  | (DIA)           |                  |

| 0              | 1         | 2       | 3        | 4        | 5        | 6              | WORD<br>7  | 8               | 9               | 10              | 11         | 12               | 13               | 14              | 15               |

| REAL           | SECO      | OND E   | CC WC    | ORD      |          |                |            |                 |                 |                 |            |                  |                  |                 |                  |

| Conte          | ext: A    | Alterna | te instr | ruction  | mode     |                | 70 MO      | D D             | •               |                 |            |                  |                  | (DIB)           |                  |

| 0              | 1         | 2       | 3        | 4        | 5<br>5   | 6<br>6         | CC WO:     | кD<br>8         | 9               | 10              | 11         | 12               | 13               | 14              | 15               |

S,C, and P Functions

f = S Sets the Busy flag to 1; sets the Done flag to 0. Starts the following operation: READ, WRITE, FORMAT, READ BUFFERS and VERIFY.

- f = C Sets the Busy flag and Done flag to 0 and stops all data transfer operations.

- f = P Starts the following operation: SEEK, RECALIBRATE, OFFSET, STOP, WRITE, DISABLE, RELEASE, and TRESPASS. (Does not affect the Busy flag or Done flag)

Performs all operations listed under f = C and initiates a recalibrate operation on the lowest numbered ready drive if it is not reserved by the other processor. Clears the sector, sector count, and surface addresss. Resets the command register to 0000 (read).

## 3.2. Register Definitions

#### SPECIFY COMMAND AND DRIVE

| DOA | (f) | ac, DSKP |               |   |   |   |   |   |    |    |    |    |    |    |

|-----|-----|----------|---------------|---|---|---|---|---|----|----|----|----|----|----|

| 0   | 1   | 1        | $\mathbf{AC}$ | 0 | 1 | 0 |   | F | 0  | 1  | 0  | 1  | 1  | 1  |

| 0   | 1   | 2 3      | 4             | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Loads bits 5-8 of the specified accumulator into the controller's command register, loads bits 9-10 of the specified accumulator into the controller's drive select register. Clears the done/attention flags selected by its 0-4 of the specified accumulator. After the data transfer, sets the controller's Busy and Done flags and initiates operations according to the function specified by F. The contents of the specified accumulator remain unchanged; its format is as follows:

DDIVE

MOD TIOND

| R/W  | CLR | SEEK DONE   |        | COM     | MAND    |          | DRIV   | /E       |         | NOT    | USED     |           |            |

|------|-----|-------------|--------|---------|---------|----------|--------|----------|---------|--------|----------|-----------|------------|

| 0    | 1   | 2 3 4       | 5      | 6       | 7       | 8        | 9      | 10       | 11      | 12     | 13       | 14        | 15         |

| BITS |     | NAME        | FUNC   | TION    |         |          | *.     |          |         |        |          |           |            |

| 0    |     | Clear       | Clears | the s   | status  | register | 's rea | ad/write | Done    | flag.  |          |           |            |

|      |     | R/W Done    | Clears | all tl  | ne read | d/write  | error  | flags of | except  | read/  | write ti | meout.    |            |

| 1-4  |     | Clear       | Clears | the c   | drive a | ttentio  | n flag | s for d  | rive 0- | 3 resp | ectively | <b>'.</b> |            |

|      |     | Atten (0-3) |        |         |         |          |        |          |         |        |          |           |            |

| 5-8  |     | Command     | Specif | ies the | e comi  | mand to  | be 1   | transmit | ted to  | the s  | selected | drive a   | s follows: |

|      |     | •           | 0000   | Read    |         |          |        |          |         |        |          |           |            |

|      |     |             | 0001   | Recal   | ibrate  |          |        |          |         |        |          |           |            |

|      |     |             | 0010   | Seek    |         |          |        |          |         |        |          |           |            |

|      |     |             | 0011   | Stop    | Drive   |          |        |          |         |        |          |           |            |

|      |     |             | 0100   | Offse   | t forw  | ard      |        |          |         |        |          |           |            |

|      |     |             | 0101   | Offse   | t revei | rse      |        |          |         |        |          |           |            |

|      |     |             | 0110   | Write   | disabl  | e e      |        |          |         |        |          |           |            |

|      |     |             | 0111   | Relea   | se      |          |        |          |         |        |          |           |            |

|      |     |             | 1000   | Trepa   | .SS     |          |        |          |         |        |          |           |            |

|      |     |             | 1001   | Set A   | lterna  | te mod   | e 1    |          |         |        |          |           |            |

|      |     |             | 1010   | Set A   | lterna  | te mod   | e 2    |          |         |        |          |           |            |

1011 No operation 1100 Verify 1101 Read Buffer 1110 Write 1111 Format Specifies drive 0-3 to be selected. 9 - 10Drive 11-15 Reserved Not used SPECIFY CYLINDER DOC (f) ac, DSKP Context: The previous DOA specified a seek operation. AC1 1 F 1 1 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

Loads bits 6-15 of the specified accumulator into the controller's cylinder address register. After the data transfer, sets the controller's Busy and Done flags and initiates operations according to the function specified by F. The contents of the specified accumulator remain unchanged; its format is as follows:

|       |      |          |        |               |        |          |       |         | CYL     | INDER    |        |          |          |      |      |

|-------|------|----------|--------|---------------|--------|----------|-------|---------|---------|----------|--------|----------|----------|------|------|

| 0     | 1    | 2        | 3      | 4             | 5      | 6        | 7     | 8       | 9       | 10       | 11     | 12       | 13       | 14   | 15   |

| BITS  |      | NAME     |        |               | FUNC   | CTION    |       |         |         |          |        |          |          |      |      |

| 0-5   |      |          |        |               | Reser  | ved for  | futu  | re use. | Bit     | 5 is im  | plemen | ted as   | cylinder | 1024 | bit. |

| 6-15  |      | Cylind   | er     |               | Speci  | fies the | desir | ed cyl  | inder   | for a se | ek ope | eration. | •        |      |      |

| SPEC  | IFY  | SURFACE  | E, SEC | CTOR          | AND C  | OUNT     |       |         |         |          |        |          |          |      |      |

| DOC   |      | ac, DSKP |        |               |        |          |       |         |         |          |        |          |          |      |      |

| Conte | ext: | The prev | ious I | DOA d         | id not | specify  | a see | k opera | ation.  |          |        |          |          |      |      |

| 0     | 1    | 1        |        | $\mathbf{AC}$ | 1      | 1        | 0     | -       | ${f F}$ | 0        | 1      | 0        | 1        | 1    | 1    |

| 0     | . 1  | <b>2</b> | 3 4    | 5             | 6      | 7        | - 8   | 9       | 10      | 11       | 12     | 13       | 14       | 15   |      |

Loads bits 1-5 of the specified accumulator into the controller's surface address register, loads bits 6-10 of the specified accumulator into the controller's sector address register, and loads bits 11-15 of the specified accumulator into the controller's

sector count register. After the data transfer, sets the controller's Busy and Done flags and initiates operations according to the function specified by F. The contents of the specified accumulator remain unchanged; its format is as follows:

|   |   | SURI | FACE | ADDRI | ESS | SECT | OR A | DDRES | S |    |    |    |    |    |    |

|---|---|------|------|-------|-----|------|------|-------|---|----|----|----|----|----|----|

| 0 | 1 | 2    | 3    | 4     | 5   | 6    | 7    | 8     | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| BITS  | NAME         | FUNCTION                                                                                                                  |

|-------|--------------|---------------------------------------------------------------------------------------------------------------------------|

| 0     |              | Not Used                                                                                                                  |

| 1-5   | Surface      | Selects the starting surface (head) for a read, write, format or verify operation.                                        |

| 6-10  | Sector       | Selects the starting sector for a read, write, format or verify operation.                                                |

| 11-15 | Sector Count | Specifies the two's complement of the number of sectors to be transferred in one operation (maximum of 40 <sub>8</sub> ). |

## READ SURFACE, SECTOR AND COUNT

| DIC ( | (f) ac, | , DSKI | • |               |   |   |   |   |   |    |    |    |    |    |    |

|-------|---------|--------|---|---------------|---|---|---|---|---|----|----|----|----|----|----|

| 0     | 1       | . 1    |   | $\mathbf{AC}$ | 1 | 0 | 1 |   | F | 0  | 1  | 0  | 1  | 1  | 1  |

| 0     | 1       | 2      | 3 | 4             | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Places the controller's surface address register in bits 1-5 of the specified accumulator, places the controller's sector address register in bits 6-10 of the specified accumulator, and places the contents of the controller's sector count regster in bits 11-15 of the specified accumulator. After the data transfer, sets the controller's Busy and Done flags and initiates operations according to the function specified by F. The format of the accumulator is as follows:

| NOT<br>USED | SURFACE ADDRE | SS SECTOR ADDRESS SECTOR COUNT                                                      |     |

|-------------|---------------|-------------------------------------------------------------------------------------|-----|

| 0 1         | 2 3 4         | 5  6  7  8  9  10  11  12  13  14  15                                               |     |

| BITS        | NAME          | FUNCTION                                                                            |     |

| 0           |               | Not used.                                                                           |     |

| 1-5         | Surface       | Indicates the current surface for a read, write, format or verify operation.        |     |

| 6-10        | Sector        | Indicates the sector immediately following the last which was transferred.          |     |

| 11-15       | Sector Count  | Indicates the two's complement of the number of sectors remaining to be transferred | ed. |

#### SPECIFY MEMORY ADDRESS

| DOB | (f) ac | e, DSK   | P |    |   |   |   |   |     |    |    |    |    |    |    |

|-----|--------|----------|---|----|---|---|---|---|-----|----|----|----|----|----|----|

| 0   | 1      | 1        |   | AC | 1 | 0 | 0 |   | F   | 0  | 1  | 0  | 1  | 1  | 1  |

| 0   | 1      | <b>2</b> | 3 | 4  | 5 | 6 | 7 | 8 | 9 . | 10 | 11 | 12 | 13 | 14 | 15 |

Loads bit 0 of the specified accumulator into the least signficant bit (lsb) of the controller's extended memory address register, and loads bits 1-15 of the specified accumulator into the controller's memory address register. After the data transfer, sets the controller's Busy and Done flags and initiates operations according to the function specified by F. The contents of the specified accumulator remain unchanged; its format is as follows:

| EMA<br>LSB |                            | MEMORY ADDRESS                                                                      |

|------------|----------------------------|-------------------------------------------------------------------------------------|

| 0 1        | 2 3 4                      | 5 6 7 8 9 10 11 12 13 14 15                                                         |

| BITS       | NAME                       | FUNCTION                                                                            |

| 0          | Extended Memory<br>Address | Specifies the lsb of the extended memory address or the data channel map selection. |

| 1-15       | Memory Address             | Specifies the starting address for data channel transfers.                          |

#### READ MEMORY ADDRESS

| DIA (f) | ) { | ac, DSKP  |               |      |   |   |   |   |    |    |    |    |    |    |

|---------|-----|-----------|---------------|------|---|---|---|---|----|----|----|----|----|----|

| Contex  | t:  | Alternate | instruction   | mode | 1 |   |   |   |    |    |    |    |    |    |

| 0       | 1   | 1         | $\mathbf{AC}$ | 0    | 0 | 1 |   | F | 0  | 1  | 0  | 1  | 1  | 1  |

| 0       | 1   | 2         | 3 4           | 5    | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Places the accumulator, and places the contents of the controller's extended memory address register in bit 0 of the specified accumulator, and places the contents of the controller's memory addresss register in bits 1-15 of the specified accumulator. After the data transfer, sets the controller's Busy and Done flags and initiates operations according to the function specified by F. The format of the accumulator is as follows:

| EMA<br>LSB |          |        |     |        | MEMO    | RY AI  | DDRES | SS    |          |       |         |                                       |        |      |         |            |

|------------|----------|--------|-----|--------|---------|--------|-------|-------|----------|-------|---------|---------------------------------------|--------|------|---------|------------|

| 0          | 1        | 2      | 3   | 4      | 5       | 6      | 7     | 8     | 9        | 10    | 11      | 12                                    | 13     | 14   | 15      |            |

| BITS       |          | NAME   | ]   |        | MEANI   | NG W   | HEN 1 | L     |          |       |         | · · · · · · · · · · · · · · · · · · · |        |      |         |            |

| 0          |          | Extend |     | lemory | Indicat | es the | lsb o | f the | extende  | đ mer | nory a  | ddress o                              | or the | NOV  | A 3 map | selection. |

| 1-15       |          | Memo   |     | dress  | Indicat | es the | locat | ion o | f the ne | kt wo | rd in 1 | memory                                | for a  | data | channel | transfer.  |

| READ       | DRIV     | E STAT | rus |        |         |        |       | •     |          |       |         |                                       |        |      |         |            |

| DIB (f)    | ac,<br>1 | DSKP   |     | AC     | 0       | 1      | 1     |       | F        | 0     | 1       | 0                                     | 1      | 1    | 1       |            |

| 0          | 1        | 2      | 3   | 4      | 5       | 6      | 7     | 8     | 9        | 10    | 11      | 12                                    | 13     | 14   | 15      |            |

Places the drive status flags for the drive selected by the previous DOA in bits 0-6 and 8-15 of the specified accumulator; sets bit 7 to 0. After the data transfer, sets the controller's Busy and Done flags and initiates operations according to the function specified by F. The format of the accumulator is as follows:

| INV | RES | TSP      | RDY | BSY | OFF | WR  |   | ILL | ILL | DC  | UNS | POS | CLK | WR  | DRV |

|-----|-----|----------|-----|-----|-----|-----|---|-----|-----|-----|-----|-----|-----|-----|-----|

| ST  |     |          |     |     |     | DIS |   | ADR | CMD | FLT |     | FLT | FLT | FLT | FLT |

| 0   | 1   | <b>2</b> | 3   | 4   | 5   | 6   | 7 | . 8 | 9   | 10  | 11  | 12  | 13  | 14  | 15  |

| BITS      | NAME             | MEANING WHEN 1                                                                               |

|-----------|------------------|----------------------------------------------------------------------------------------------|

| 0         | Invalid Status   | The disk drive is not selected and bits 5-6 and 8-15 should be ignored.                      |

| 1         | Reserved         | The drive is reserved by the other processor.                                                |

| <b>2</b>  | Trespassed       | One of the drives was trespassed upon by the other processor.                                |

| 3         | Ready            | The drive is ready to accept commands.                                                       |

| 4         | Busy             | The drive is busy executing a position command or reporting an aborted seek or a trespass by |

|           |                  | the other processor.                                                                         |

| 5         | Offset           | The positioner is offset forward or reverse.                                                 |

| 6         | Write Disable    | The write circuits are disabled.                                                             |

| 7         | Principles and   | Reserved for future use.                                                                     |

| 8         | Invalid Address  | The surface or cylinder capacity of the drive was exceeded.                                  |

| 9         | Illegal Command  | The drive received an illegal read/write or position command.                                |

| 10        | DC Fault         | The disk drive power supply has a DC voltage problem.                                        |

| 11        | Disk unsafe      | An unsafe condition exists preventing operation.                                             |

| <b>12</b> | Positioner fault | The head positioner malfunctioned.                                                           |

| 13        | Clock fault      | The servo clock malfunctioned.                                                               |

| 14        | Write fault      | The write or head select circuits malfunctioned.                                             |

| 15        | Drive fault      | Any of the above faults (bits 8-14).                                                         |

|           |                  |                                                                                              |

## READ DATA TRANSFER STATUS

| DIA ( | (f) ac | , DSKI | • |               |   |   |   |   |   |    |    |    |    |    |    |

|-------|--------|--------|---|---------------|---|---|---|---|---|----|----|----|----|----|----|

| 0     | 1      | 1      |   | $\mathbf{AC}$ | 0 | 0 | 1 |   | F | 0  | 1  | 0  | 1  | 1  | 1  |

| 0     | 1      | 2      | 3 | 4             | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Places the contents of the controller's Done flags and read/write status flags in bits 0-15 of the specified accumulator. After the data transfer, sets the controller's Busy and Done flags and initiates operations according to the function specified by F. The format of the accumulator is as follows:

| CNT<br>FUL | R/W<br>DN |        | SEEK    | DONE  |       | PAR      | SEC<br>ADD | ECC      | BAD<br>SEC | CYL<br>ADD | SEC<br>SRF | VFY     | R/W<br>TIM | DAT<br>LAT | R/W<br>FLT |                     |              |

|------------|-----------|--------|---------|-------|-------|----------|------------|----------|------------|------------|------------|---------|------------|------------|------------|---------------------|--------------|

| 0          | 1         | 2      | 3       | 4     | 5     | 6        | 7          | 8        | 9          | 10         | 11         | 12      | 13         | 14         | 15         |                     |              |

|            |           |        |         |       |       |          |            |          |            |            |            |         |            |            |            |                     |              |

| BITS       |           | NAMI   |         |       |       | NING V   |            |          |            |            |            |         |            |            | _          |                     | •            |

| 0          |           | Contr  | ol Full | •     | The o | drive c  | omman      | d initia | ated by    | the p      | revious    | OPU     | LSE or     | IORS       | r has no   | ot yet bee          | n issued to  |

|            |           |        |         |       | the s | elected  | drive.     |          |            |            |            |         |            |            |            |                     |              |

| 1          |           | R/W    | Done    |       | The r | read/wr  | ite ope    | ration   | initiat    | ed by 1    | the pre    | vious S | START      | has te     | rminate    | d <b>. (</b> This i | s the same   |

|            |           |        |         |       | as th | e devid  | e Don      | e flag.  | )          |            |            |         |            |            |            |                     |              |

| 2-5        |           | Drive  | 0-3 D   | one   | The r | respecti | ve driv    | es hav   | e exec     | uted a     | positio    | oner co | mmand      | l, have    | rejected   | d an illega         | 1 positioner |

|            |           |        |         |       | comm  | nand, h  | ave be     | en tres  | spassed    | upon,      | or hav     | e char  | iged th    | eir rea    | ıdy statı  | us.                 |              |

| 6          |           | Parity | J ·     |       | A par | rity err | or occu    | irred o  | n a dat    | a trans    | sfer bet   | tween   | the cor    | ntroller   | and the    | e adapter.          | Not used.    |

| 7          |           | Illega | 1 Secto | or    | The s | sector   | address    | excee    | ded th     | e capa     | city of    | the d   | rive.      |            |            |                     |              |

| . 8        |           | ECC    |         |       | A da  | ta erro  | r was      | detecte  | ed by t    | the EC     | C circu    | uits.   |            |            |            |                     |              |

| 9          |           | Bad S  | Sector  |       | A bac | d secto  | r flag     | was de   | etected    | during     | g a sec    | tor he  | ader cl    | heck.      |            |                     |              |

| 10         |           | Cyline | der err | or    | A cy  | linder a | address    | error    | was de     | etected    | during     | g a sec | tor he     | ader cl    | heck.      |                     |              |

| 11         |           | Surf/s | sect er | ror   | A sur | face o   | r secto    | r addr   | ess err    | or was     | detec      | ted du  | ring a     | sector     | header     | check.              |              |

| 12         |           | Verify | y error |       |       |          |            |          |            |            | erify o    |         |            |            |            |                     |              |

| 13         |           | Read   | Write   |       | The 1 | read/wr  | ite ope    | eration  | initiat    | ed by      | the pre    | evious  | START      | ` was r    | not com    | pleted in           | 1 second.    |

|            |           | timeo  | ut      |       |       |          | -          |          |            |            |            |         |            |            | •          | -                   |              |

| 14         |           | Data   | late    |       | The 1 | FIFO o   | verflow    | ed dur   | ing a      | read or    | under      | flowed  | during     | ; a wri    | te.        |                     |              |

| 15         |           |        | /write  | fault |       | of the   |            |          |            |            |            |         |            |            |            | ed by the           | read/write   |

#### READ FIRST ECC WORD

| DIA ( | f) ac | , DSKP |   |    |   |   |   |   |              |    |    |    |    |    |    |

|-------|-------|--------|---|----|---|---|---|---|--------------|----|----|----|----|----|----|

| 0     | 1     | 1      |   | AC | 0 | 0 | 1 |   | $\mathbf{F}$ | 0  | 1  | 0  | 1  | 1  | 1  |

| 0     | 1     | 2      | 3 | 4  | 5 | 6 | 7 | 8 | 9            | 10 | 11 | 12 | 13 | 14 | 15 |

Places bits 0-15 of the controller's ECC remainder register in bits 0-15 of the specified accumulator. After the data transfer, sets the controller's Busy and Done flags and initiates operations according to the function specified by F. The format of the accumulator is as follows:

| 0 .            | 1      | 2                  | 3    | 4       | 5        | 6      | 7      | WORD<br>8 | 9      | 10      | 11      | 12                                    | 13                                    | 14      | 15        |             |      |

|----------------|--------|--------------------|------|---------|----------|--------|--------|-----------|--------|---------|---------|---------------------------------------|---------------------------------------|---------|-----------|-------------|------|

| BITS           |        | NAMI               | Ξ    |         | MEANI    |        |        |           |        |         |         |                                       |                                       |         |           |             |      |

| 0-15<br>operat | ion.   | a <sub>31</sub> -a | 16   |         | Indicate | es the | e coe  | fficients | of     | the hig | h order | bits                                  | of the                                | ECC     | remainder | following a | read |

| READ           | SEC    | OND E              | CC W | ORD     |          |        | •      |           |        |         |         |                                       |                                       |         |           |             |      |

| DIB (f         |        | , DSKP<br>Alternat |      | ruction | mode 2   |        |        |           |        |         |         |                                       |                                       |         |           |             |      |

| 0              | 1<br>1 | $\frac{1}{2}$      | 3    | AC<br>4 | 0<br>5   | 1<br>6 | 1<br>7 | 8         | F<br>9 | 0<br>10 | 1<br>11 | $\begin{matrix} 0 \\ 12 \end{matrix}$ | $\begin{matrix} 1 \\ 13 \end{matrix}$ | 1<br>14 | 1<br>15   |             |      |

FIDER FOC WODD

Places bits 16-31 of the controller's ECC remainder register in bits 0-15 of the specified accumulator. After the data transfer, sets the controller's Busy and Done flags and initiates operations according to the function specified by F. The format of the accumulator is as follows:

|      |   |                    |     | SECO | ND E  | CC W    | ORD      |        |          |        |          |          |     |             |             |          |            |

|------|---|--------------------|-----|------|-------|---------|----------|--------|----------|--------|----------|----------|-----|-------------|-------------|----------|------------|

| 0    | 1 | 2                  | 3   | 4    | 5     | 6       | 7        | 8      | 9        | 10     | 11       | 12       | 13  | 14          | 15          |          |            |

| BITS |   | NAM                | C . |      | MITA  | NINC    | WHEN     | 1      |          |        |          |          |     |             |             |          |            |

|      |   |                    |     |      |       |         |          |        |          |        |          |          |     | <del></del> |             | _        |            |

| 0-15 |   | a <sub>15</sub> -a | 0   |      | Indic | ates th | ne coeff | icient | s of the | low or | der bits | s of the | ECC | remaind     | er followin | g a read | operation. |

#### 3.3 HARDWARE OPERATION

The following paragraphs provide a brief description of the major logical sections and busses within the SPECTRA 10.

#### 3.3.1. The CPU Processor

The CPU processor is a bit slice design using two 2901's. There are two major busses in this processor, CSRC and CDEST. CSRC is an 8 bit data buss providing the 8 bit input source to the two 2901's on their D inputs. The outputs of the 2901's provide the 8 bit destination buss, CDEST. The firmware may select a variety of sources for the CSRC buss and a variety of destinations for the CDEST buss.

The sequencer for the CPU processor consists of three 2911 IC's. These provide the ability to do jumps, conditional jumps, subroutine jumps, and subroutine returns. Up to four levels of subroutines may be nested. Also included in the hardware of the CPU processor is the logic necessary to perform a multiway (vector) jump. The outputs of the 2901's on the CDEST buss of the previous instruction may be used to provide the 8 least significant bits of the target address for the multiway jump. The most significant bits are held high, enabling the multiway jump instruction to jump to a table at the high end of the firmware. This table is a jump table so that the 2911's may recover the current program counter and continue sequencing as before.

The instruction width of the CPU processor is 36 bits, two of which are spare. Either 512x4 or 1Kx4 PROM's may be used. Changing the size of the PROM used requires changing the link W11. The instruction is defined as follows:

|   |     | 35    | Spare                                                                 |

|---|-----|-------|-----------------------------------------------------------------------|

| Ī | 3it | 34-31 | Instruction type - defines type of jump and whether this instruction  |

|   |     |       | includes a flag field.                                                |

| I | 3it | 30-26 | CSRC address - defines one of up to 32 sources.                       |

| ŀ | 3it | 25    | Spare                                                                 |

| I | 3it | 24-22 | CDEST address - defines one of up to 8 destinations.                  |

| I | 3it | 21-17 | 2901 control bits I6, I5, I4, I2, and I0.                             |

| Ĭ | 3it | 16-12 | For jump instructions other than multiway jumps, these bits address   |

|   |     |       | the condition to be selected. The 2901 control bits I8, I7, I3, and   |

|   |     |       | CN are then held low (0) and I1 is held high (1). This enables        |

|   |     |       | certain ALU instructions to be performed at the same time as a        |

|   |     |       | jump instruction.                                                     |

|   |     |       | For instructions other than jump instructions, these bits provide the |

Bit 11-8 For jump instructions, these bits provide the most significant bits of the target address.

For instructions other than jump instructions, these bits provide both the A and B register addresses of the 2901's. Since the A and B addresses are identical, the dual port capability of the 2901's is not used.

2901 control bits 18, 17, 13, 11, and CN directly.

Bit 7-0 For jump instructions, these bits provide the least significant 8 bits of the target address.

For instructions using the flag field, these bits are used to select the flag.

For instructions using a constant for CSRC, these bits provide that

constant.

#### 3.3.2. The DISK Processor

The DISK processor is a bit slice design using two 2901's and is very similar to the CPU processor. The 8 bit source buss is called DSRC and the 8 bit destination buss is called DDEST. The sequencer for the DISK processor consists of three 2911 IC's and is very similar to the CPU processor's sequencer. The major difference between the two sequencers is that the DISK processor does not have the multiway jump facility.

The instruction width of the DISK processor is 32 bits. Eight 1Kx4 PROM's are used. The instruction is defined as follows:

| Bit 31-29 | Instruction type - defines | type of jump | and whether | this instruction |

|-----------|----------------------------|--------------|-------------|------------------|

|           | includes a flag field.     |              |             |                  |

Bit 28-26 DSRC address - defines one of 8 sources.

Bit 25-22 DDEST address - defines one of 16 destinations.

Bit 21-16 2901 control bits I6, I5, I4, I2, I0, and CN.

Bit 15-12 For jump instructions, these bits address the condition to be selected. The 2901 control bit I8, I7, and I3 are then held low (0) and I1 is held high (1). This enables certain ALU instructions to be performed at the same time as a jump instruction.

For instructions other than jump instructions, these bits provide the 2901 control bits I8, I7, I3, and I1 directly.

Bit 11-8 For jump instructions, these bits provide the most significant bits of the target address.

For instructions other than jump instructions, these bits provide both the A and B register addresses of the 2901. Since the A and B addresses are identical, the dual port capability of the 2901's is not used.

Bit 7-0 For jump instructions, these bits provide the least significant 8 bits of the target address.

For instructions using the flag field, these bits are used to select the flag.

For instructions using a constant for DSRC, these bits provide that constant.

#### 3.3.3. The Disk Interface

The SMD disk interface is controlled by the DISK processor. The firmware may write directly to the SMD buss lines and tag lines. The data is passed through two 74S299 IC's used as a 16 bit serializer/deserializer shift register. Further registers surrounding this shift register give the firmware a 16 bit word time to move the first two bytes to or from the Sector Buffer. The firmware is synchronized to the SMD interface by a bit counter which sets a word available flip-flop, WRDAV, each time the counter overflows. All controls for the CRC and ECC logic may also be switched at this word available time. It is necessary for the firmware to pre-load these controls in the previous word time. The controls will be synchronized and enabled at the next word available time.

The firmware will normally elect to write a CRC field after each header. The hardware used to do this is a 9401 IC wired to generate the polynomial  $X^{16} + X^{15} + X^2 + 1$ . This IC is also used when reading the header to check its validity. At

the end of the data field, however, four bytes of ECC are written. The polynomial used in this case is  $X^{32} + X^{23} + X^{21} + X^{11} + X^2 + 1$ . The hardware used to implement this polynomial are several MSI IC's. When reading data from the disk, the firmware may choose to break this polynomial up into its factors and return an ECC pattern identical to the DG 6060 Series. Optionally, the firmware will not factor the polynomial, and any correctable error encountered will be corrected by the firmware in the Sector Buffer before passing the data to the DG computer.

#### 4.0 DIAGNOSTICS

#### 4.1. MICRODIAGNOSTICS AND LEDS

Microdiagnostics are run every time the controller powers up. The CPU processor and the DISK processor each have their own diagnostics. Any failure will cause the LEDs to be lit. The LEDs have the following meaning:

| Off<br>Off<br>Off<br>Off<br>Off                      | Off<br>Off<br>Off<br>Off             | DS2<br>Off<br>Off<br>On<br>On<br>Off                          | Off<br>On<br>Off<br>On<br>On                      | No Fault CPU processor failed basic 2901 test. CPU processor failed ALU function test. CPU processor failed register address test. CPU processor failed RAM buffer test.                                                                                                                            |

|------------------------------------------------------|--------------------------------------|---------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                      |                                      | settings                                                      |                                                   | CPU processor's sequencer failed.                                                                                                                                                                                                                                                                   |

| DS8<br>Off<br>Off<br>Off<br>Off<br>Off<br>Off<br>Off | Off<br>Off<br>Off<br>Off<br>On<br>On | DS6<br>Off<br>Off<br>On<br>On<br>Off<br>Off<br>On<br>settings | DS5<br>Off<br>On<br>Off<br>On<br>Off<br>On<br>Off | No Fault Disk processor failed basic 2901 test. Disk processor failed ALU function test. Disk processor failed register address test. Disk processor failed serializer/deserializer test. Disk processor failed ECC test. Disk processor failed RAM buffer test. Disk processor's sequencer failed. |

N.B.: Since both processors test the RAM buffer, there is some communication between the two processors during diagnostics. For this reason, both processors may be indicating a fault when in fact only one has failed.

## 4.2. DIAGNOSTIC SOFTWARE

The SPECTRA 10 disk controller is designed to emulate the Data General 6067 Disk Subsystem and to run with the standard Data General diagnostics:

| ZDKP | FMTR | (095-000471) | 6067 | Formatter   |         |

|------|------|--------------|------|-------------|---------|

| ZDKP | DIAG | (095-000470) | 6067 | Diagnostic  |         |

| ZDKP | RELI | (095-000469) | 6067 | Reliability | Program |

In standard emulation mode (815 cylinders, 5 heads, and 24 sectors per track), the Formatter and Reliability programs run without modification. The Diagnostic requires a few patches to ignore those features which the SPECTRA 10 does not emulate, none of which affect operational system software. In expanded emulation mode with different numbers of cylinders, heads, and/or sectors per track, additional changes have to be made in order to take advantage of these different capacities.

## 4.2.1. DTOS REV. 7

## ZDKP FMTR (095-000471-03)

## 4.2.1.1. To change sectors per track from 24 to 32:

| Address | Is     | Change to | Comments             |

|---------|--------|-----------|----------------------|

| 113     | 30     | 40        | ;sectors/track       |

| 171     | 30     | 40        | ;sectors/track       |

| 2525    | 176400 | 176000    | ;-(sectors/track*40) |

| 2536    | 1400   | 2000      | sectors/track*40     |

| 2537    | 27     | 37        | ;sectors/track-1     |

|         |        |           |                      |

80MB disk (815 cylinders, 5 heads) is referred to as 50MB 6067. 300MB disk (815 cylinders, 19 heads) is referred to as 190MB 6061.

## 4.2.1.2. To change cylinders from 815 to 823:

| Address | Is   | Change to | Comments  |

|---------|------|-----------|-----------|

| 202     | 1457 | 1467      | cylinders |

80MB disk (823 cylinders, 5 heads) is referred to as 50MB 6067. 300MB disk (823 cylinders, 19 heads) is referred to as 190MB 6061.

## 4.2.1.3. For 160MB disk with 1645 cylinders:

| $\frac{\text{Address}}{202}$                  | <u>Is</u><br>1457          | Change to 3155                                                | Comments ; cylinders                                              |

|-----------------------------------------------|----------------------------|---------------------------------------------------------------|-------------------------------------------------------------------|

| 1167                                          | 34170                      | 34172                                                         | ;load cylinder mask                                               |

| 2606<br>2607                                  | $167400 \\ 123000$         | 2401<br>370                                                   | ;JMP @ .+1                                                        |

| 370<br>371<br>372<br>373<br>374<br>375<br>376 | -<br>-<br>-<br>-<br>-<br>- | 167400<br>123000<br>34404<br>163400<br>2401<br>2610<br>160377 | ;AND 3,1<br>;ADD 1,0<br>;LDA 3,.+4<br>;AND 3,0<br>;JMP @ .+1<br>; |

160MB disk (1645 cylinders, 5 heads) is referred to as 50MB 6067.

## ZDKP FMTR (095-0000471-03) (cont.)

## 4.2.1.4. To change number of heads or cylinders for other drives:

| $\frac{\text{Address}}{202}$ | $\frac{\text{Is}}{1457}$ | Change to CCCC             | Comments<br>;cylinders                                                                |

|------------------------------|--------------------------|----------------------------|---------------------------------------------------------------------------------------|

| 1200                         | 22                       | HH-1                       | ;heads-1                                                                              |

| 1167                         | 34170                    | 34167<br>34170 ——<br>34172 | ;if CCCC less than 1000<br>;if CCCC between 1000 & 2000<br>;if CCCC greater than 2000 |

Disk is referred to as 190MB 6061. CCCC and HH are values taken from the Drive Configuration Table (4.2.3.).

## ZDKP DIAG (095-000470-03)

## 4.2.1.5. Required Changes:

| Address | Is                | Change to |

|---------|-------------------|-----------|

| 1511    | $\overline{6246}$ | 403       |

| 1600    | 6252              | 474       |

| 1723    | 6251              | 6263      |

| 1724    | 60227             | 6274      |

| 3272    | 16000             | 12000     |

| 3322    | 16000             | 12000     |

| 3423    | 6252              | 516       |

| 4113    | 20216             | 557       |

| 6476    | 451               | 401       |

|         |                   |           |

## 4.2.1.6. To change sectors per track from 24 to 32:

| $\frac{\text{Address}}{142}$ | $\frac{\text{Is}}{177750}$ | Change to 177740 | Comments<br>;-sectors/track |

|------------------------------|----------------------------|------------------|-----------------------------|

| 2367                         | 0                          | 400              | ;32 sector write            |

| 2474                         | 102400                     | 20102            | ;check head increment       |

| 2554                         | 40401                      | 40000            | force illegal sector        |

| 2637<br>2640                 | 10006<br>44006             | 10406<br>44406   | ;force illegal surface      |

| 5621                         | 21400                      | 20212            | <b>;</b>                    |

80MB disk (815 cylinders, 5 heads) is referred to as 50MB 6067. 300MB disk (815 cylinders, 19 heads) is referred to as 190MB 6061.

## ZDKP DIAG (095-000470-03) (cont.)

4.2.1.7. To change cylinders from 815 to 823:

| Address | Is                | Change to | Comments  |

|---------|-------------------|-----------|-----------|

| 214     | $\overline{1457}$ | 1467      | cylinders |

80MB disk (823 cylinders, 5 heads) is referred to as 50MB 6067. 300MB disk (823 cylinders, 19 heads) is referred to as 190MB 6061.

4.2.1.8. For 160MB disk with 1645 cylinders:

| $\frac{\text{Address}}{214}$ | $\frac{\mathrm{Is}}{1457}$ | Change to 3155                      | Comments<br>;cylinders                           |

|------------------------------|----------------------------|-------------------------------------|--------------------------------------------------|

| 6655                         | 34211                      | 34212                               | ;load cylinder mask                              |

| 6023<br>6024                 | $\frac{176400}{151220}$    | 2401<br>332                         | ;JMP @ .+1                                       |

| 332<br>333<br>334<br>335     | -<br>-<br>-                | 34212<br>173400<br>176400<br>151220 | ;LDA 3,212<br>;AND 3,2<br>;SUB 3,3<br>;MOVZR 2,2 |

| 336<br>337                   | -                          | 2401<br>6025                        | ;JMP @ .+1                                       |

160MB disk (1645 cylinders, 5 heads) is referred to as 50MB 6067.

4.2.1.9. To change number of heads or cylinders for other drives:

| $\frac{\text{Address}}{214}$ | <u>Is</u><br>1457 | Change to CCCC                                      | Comments<br>;cylinders                                                                |

|------------------------------|-------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------|

| 6707                         | 22                | HH-1                                                | ;heads-1                                                                              |

| 6655                         | 34211             | $\begin{cases} 34212 \\ 34211 \\ 34212 \end{cases}$ | ;if CCCC less than 1000<br>;if CCCC between 1000 & 2000<br>;if CCCC greater than 2000 |