# Standard

MLP-900 MULTI-LINGUAL PROCESSOR

PRINCIPLES OF OPERATION

Standard Computer Corporation

# MLP-900 MULTI-LINGUAL PROCESSOR

PRINCIPLES OF OPERATION

#### RESTRICTED DISTRIBUTION

This document contains preliminary information on an unreleased product. Specifications are subject to change without notice. STANDARD Computer Corporation therefore assumes no liability.

RESTRICTED DISTRIBUTION

Revised, May 1970

Copies of inis und other STANDARD Computer Corporation publications can be obtained through the nearest STANDARD sales office (see back cover). Comments concerning the contents of this publication should be addressed to STANDARD Computer Corporation, Technical Publications, 633 East Young St., Santa Ana, California 92705.

#### PREFACE

This document is an introduction to the functional design of the MLP-900 Multi-Lingual Processor. It includes a description of system architecture, processing facilities and MLP-900 order codes.

The MLP-900 is a microprogrammed processor with an on-line alterable control memory. It possesses a designed-in capability for efficient interpretive execution of instructions in formats and languages other than its own internal order code set. On-line alterable microprogramming is not the only capability needed to make a processor efficient in multi-lingual interpretive applications. Three design principles were followed to develop a processor capable of handling a broad spectrum of target languages:

- The system architecture is generalized and provides direct control of logic functions and access to all storage elements.

- Order codes are well-structured and are similar in function to typical machine language instruction sets.

- The processor uses language-dependent hardware with complementary microprograms to efficiently adapt to widely varying target instruction and operand formats, I/O structures and memory addressing modes.

The language-dependent, plug-in hardware is used to perform a variety of translation and formatting functions more efficiently than unassisted software. Hardware aids can provide:

- High speed in executing repetitive functions; such as target instruction decomposition, order code translation and microprogram execution routine entry.

- Formatting of memory addresses and translation functions, such as page or byte addressing, memory protection, relocation, etc.

- Reduction in Control Memory storage requirements.

STANDARD Computer Corporation representatives are available to aid you in establishing requirements, specifications and performance goals for complementary firmware and hardware application packages for the MLP-900.

# TABLE OF CONTENTS

| Section |                                                                               |                                                                                                                                                                                                                                                                                 | Page                                                                         |

|---------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

|         | List of Ill                                                                   | ustrations                                                                                                                                                                                                                                                                      | iii<br>vii<br>ix                                                             |

| 1       | MLP-900                                                                       | PROCESSOR DESIGN                                                                                                                                                                                                                                                                |                                                                              |

|         | 1.1                                                                           | GENERAL                                                                                                                                                                                                                                                                         | 1-1                                                                          |

|         | 1.2                                                                           | MLP-900 SUMMARY SPECIFICATIONS                                                                                                                                                                                                                                                  | 1-3                                                                          |

|         | 1.3                                                                           | OPERATING ENGINE DESIGN                                                                                                                                                                                                                                                         | 1-4                                                                          |

|         | 1.3.1<br>1.3.2<br>1.3.3<br>1.3.4                                              | General Registers                                                                                                                                                                                                                                                               | 1-6<br>1-7<br>1-8<br>1-9                                                     |

|         | 1.3.4<br>1.3.5<br>1.3.6<br>1.3.7<br>1.3.8                                     | Shift Operations                                                                                                                                                                                                                                                                | 1-10<br>1-11<br>1-11<br>1-12                                                 |

|         | 1.4                                                                           | CONTROL ENGINE DESIGN                                                                                                                                                                                                                                                           | 1-12                                                                         |

|         | 1.4.1<br>1.4.2<br>1.4.3<br>1.4.4<br>1.4.5<br>1.4.6<br>1.4.7<br>1.4.8<br>1.4.9 | Control Memory Addressing Control Memory Design Ministep Registers and Gating Functions Subroutine Return Stack and Stack Control Pointer Registers MINIFLOW Status Word Control Engine Language Boards State Flip-Flops Action Request Servicing Control Engine Data Transfers | 1-15<br>1-17<br>1-17<br>1-18<br>1-18<br>1-20<br>1-21<br>1-22<br>1-25<br>1-27 |

| 2       | MINISTEI                                                                      | P FORMATS AND CONVENTIONS                                                                                                                                                                                                                                                       |                                                                              |

|         | 2.1                                                                           | GENERAL                                                                                                                                                                                                                                                                         | 2-1                                                                          |

|         | 2.2.2                                                                         | OPERATING INSTRUCTIONS                                                                                                                                                                                                                                                          | 2-1                                                                          |

|         | 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4                                              | GEAR - General Arithmetic                                                                                                                                                                                                                                                       | 2-3<br>2-6<br>2-9<br>2-13                                                    |

# TABLE OF CONTENTS (continued)

| Section      |                                              |                                | Page |  |  |  |  |  |

|--------------|----------------------------------------------|--------------------------------|------|--|--|--|--|--|

| 2            | MINISTEP FORMATS AND CONVENTIONS (continued) |                                |      |  |  |  |  |  |

|              | 2.2.5                                        | GENT - General Data Transfer   | 2-16 |  |  |  |  |  |

|              | 2.2.6                                        | TEXT - Transfer External       | 2-17 |  |  |  |  |  |

|              | 2.3                                          | CONTROL MINISTEPS              | 2-20 |  |  |  |  |  |

|              | 2.3.1                                        | BRAT - Branch Test             | 2-20 |  |  |  |  |  |

|              | 2.3.2                                        | BENT - Branch and Enter        | 2-21 |  |  |  |  |  |

|              | 2.3.3                                        | BORE - Branch or Return        | 2-22 |  |  |  |  |  |

|              | 2.3.4                                        | BRAD - Branch and Modify       | 2-22 |  |  |  |  |  |

|              | 2.3.5                                        | BEAD - Branch-Extended Address | 2-23 |  |  |  |  |  |

|              | 2.3.5.1                                      | Conditional Absolute Branch    | 2-23 |  |  |  |  |  |

|              | 2.3.5.2                                      | Absolute Branch Plus Pointer   | 2-24 |  |  |  |  |  |

|              | 2.3.5.3                                      | Continuation Plus Pointer      | 2-24 |  |  |  |  |  |

|              | 2.3.5.4                                      | Conditional Relative Branch    | 2-24 |  |  |  |  |  |

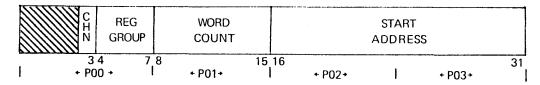

|              | 2.3.6                                        | BLOT - Block Transfer          | 2-24 |  |  |  |  |  |

|              | 2.3.6.1                                      | Pointer Operation              | 2-25 |  |  |  |  |  |

|              | 2.3.6.2                                      | Single Block Load Operations   | 2-25 |  |  |  |  |  |

|              | 2.3.6.3                                      | Multiple Block Load Operations | 2-23 |  |  |  |  |  |

|              | 2.3.7                                        | MAST - Manipulate Status       | 2-28 |  |  |  |  |  |

|              | 2.3.8                                        | MOVE - Control Engine MOVE     | 2-29 |  |  |  |  |  |

| Appendix     |                                              |                                | Page |  |  |  |  |  |

|              |                                              |                                | rage |  |  |  |  |  |

| Α            | SC-700 N                                     | Magnetic Core Memory           | A-1  |  |  |  |  |  |

| В            | Language                                     | e Boards                       | B-1  |  |  |  |  |  |

| C            |                                              | p-Flops                        | C-1  |  |  |  |  |  |

| D            |                                              | nce Panel                      | D-1  |  |  |  |  |  |

| $\mathbf{E}$ | Ministep                                     | Field Decodes                  | E-1  |  |  |  |  |  |

|              | Glossary                                     | of Commonly Used Terms         | G-1  |  |  |  |  |  |

# LIST OF ILLUSTRATIONS

| Figure |                                                  | Page |

|--------|--------------------------------------------------|------|

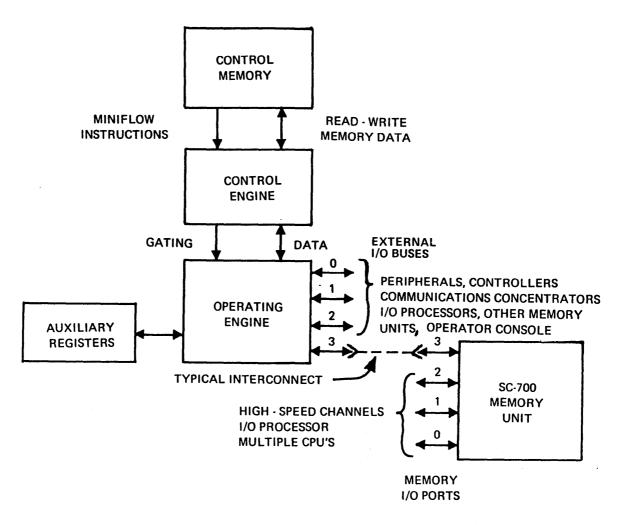

| 1-1    | MLP-900 Overall Block Diagram                    | 1-3  |

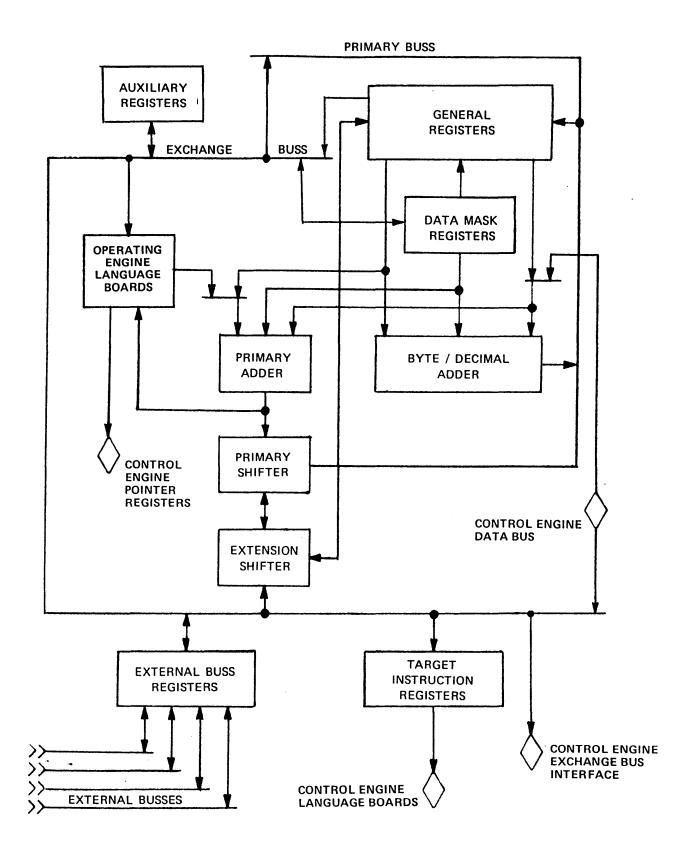

| 1-2    | Operating Engine Block Diagram                   | 1-5  |

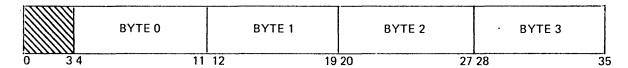

| 1-3    | Byte Data Word Format                            | 1-8  |

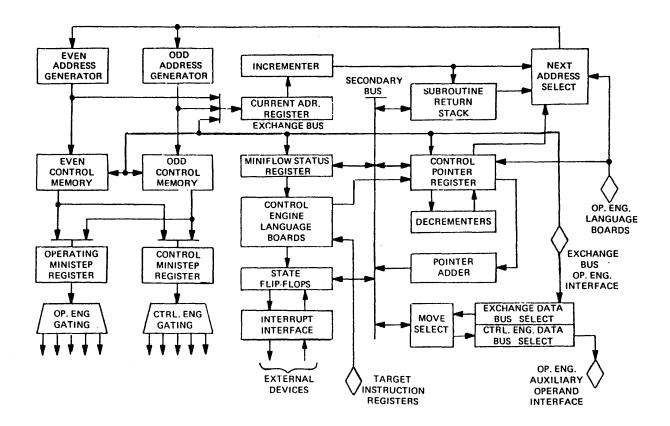

| 1-4    | Control Engine Block Diagram                     | 1-13 |

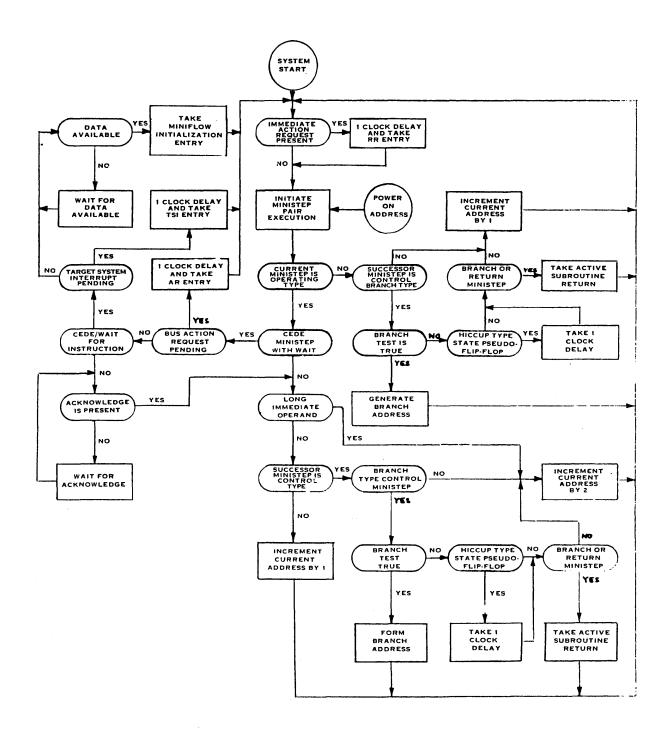

| 1-5    | Control Memory Address Selection, Flow Diagram   | 1-16 |

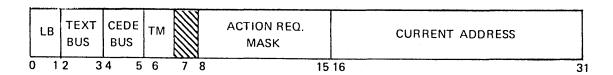

| 1-6    | MINIFLOW Status Word Format                      | 1-20 |

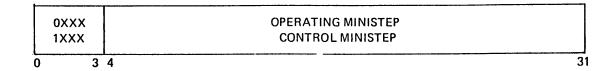

| 2-1    | Basic Ministep Formats                           | 2-1  |

| 2-2    | Operating Ministeps                              | 2-2  |

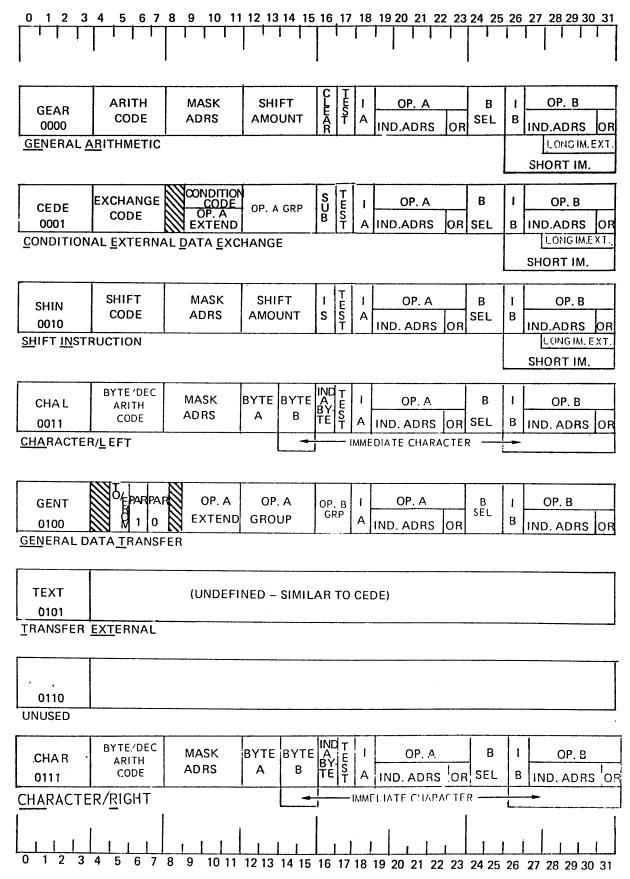

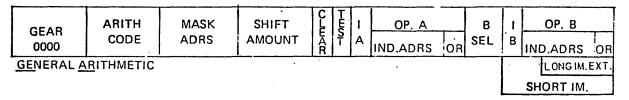

| 2-3    | GEAR Format                                      | 2-3  |

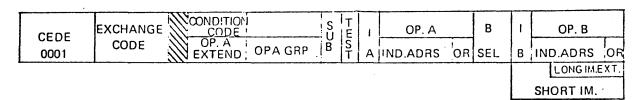

| 2-4    | CEDE Format                                      | 2-6  |

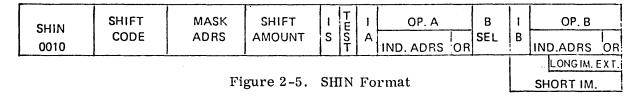

| 2-5    | SHIN Format                                      | 2-9  |

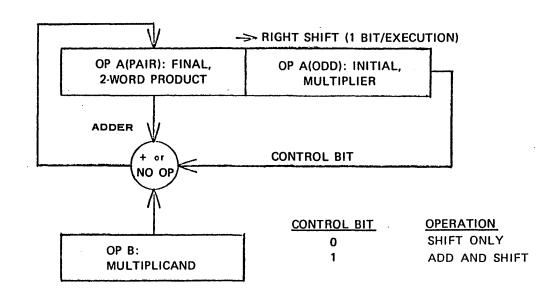

| 2-6    | SHIN/MULTIPLY Flow Diagram                       | 2-12 |

| 2-7    | SHIN/DIVIDE Flow Diagram                         | 2-12 |

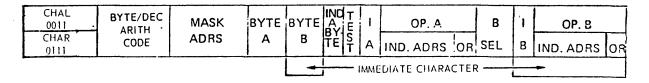

| 2-8    | CHAL/CHAR Format                                 | 2-13 |

| 2-9    | GENT Format                                      | 2-16 |

| 2-10   | Control Ministeps                                | 2-19 |

| 2-11   | Control Ministeps State Flip-Flop Address Format | 2-20 |

| 2-12   | BRAT Format                                      | 2-20 |

| 2-13   | BENT Format                                      | 2-21 |

| 2-14   | BORE Format                                      | 2-22 |

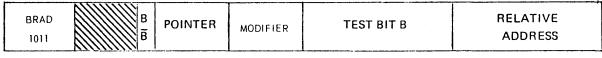

| 2-15   | BRAD Format                                      | 2-22 |

| 2-16   | BEAD Format                                      | 2-23 |

| 2-17   | BEAD Format, Conditional Absolute Branch         | 2-23 |

| 2-18   | BEAD Format, Absolute Branch Plus Pointer        | 2-24 |

| 2-19   | BEAD Format, Continuation Plus Pointer           | 2-24 |

| 2-20   | BEAD Format, Conditional Relative Branch         | 2-24 |

| 2-21   | BLOT Format                                      | 2-24 |

| 2-22   | Load Control Word (LCW) Format (LMB Operations)  | 2-26 |

| 2-23   | MAST Format                                      | 2-28 |

| 2-24   | MOVE Format                                      | 2-29 |

| 2-25   | Register Addressing Format                       | 2-30 |

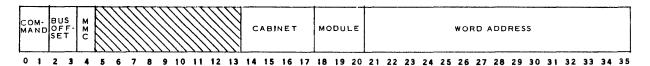

| A-1    | External Command Word                            | A-1  |

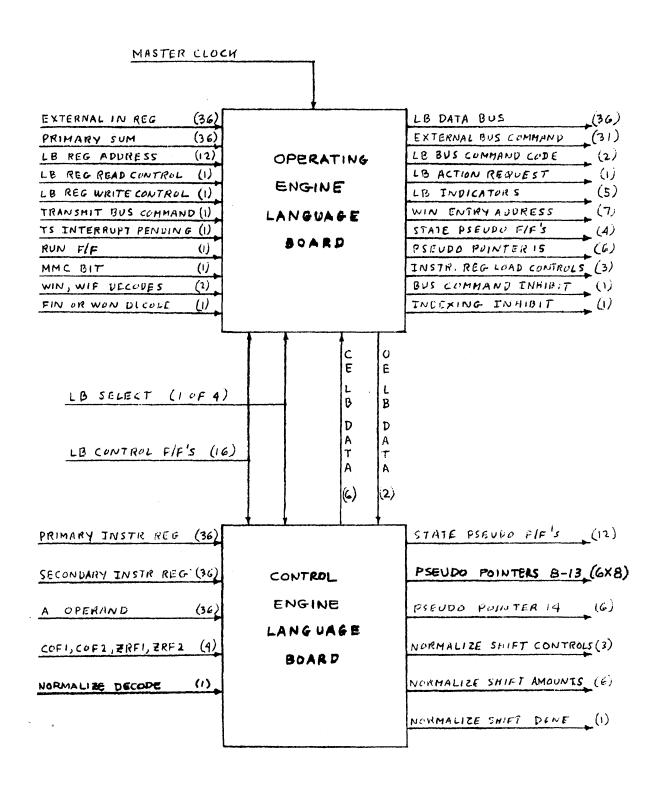

| B-1    | Language Board Input/Output Signals              | B-2  |

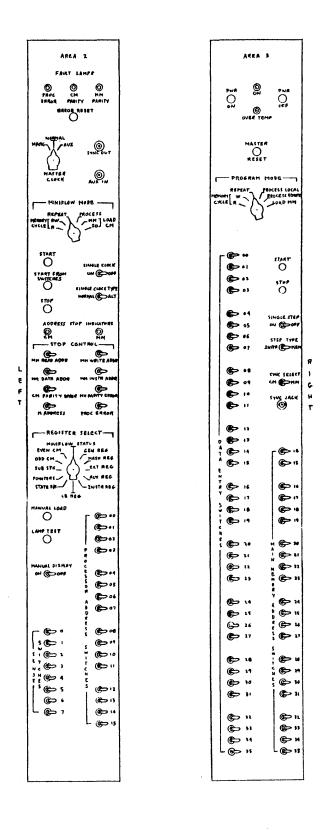

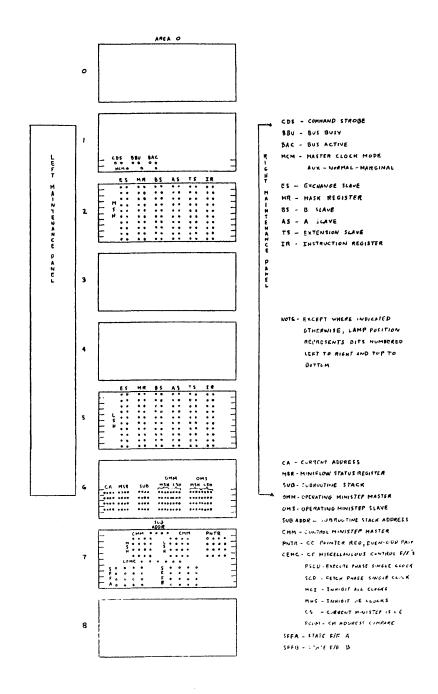

| D-1    | MLP-900 Maintenance Panels                       | C-2  |

| D-2    | MLP-900 Indicator Lamp Layout (Front View)       | D-3  |

# LIST OF TABLES

| Table |                                             | Page |

|-------|---------------------------------------------|------|

| 1-1   | Primary Adder Operations                    | 1-8  |

| 1-2   | Byte/Decimal Adder Operations               | 1-9  |

| 1-3   | Pointer Register Functions                  | 1-19 |

| 1-4   | State Flip-Flop Listing                     | 1-23 |

| 1-5   | MLP-900 Action Request Characteristics      | 1-26 |

| 2-1   | Arithmetic Codes and Functions              | 2-3  |

| 2-2   | State Flip-Flop Functions (GEAR)            | 2-6  |

| 2-3   | CEDE Exchange Codes                         | 2-7  |

| 2-4   | SHIN Ministep Shift Codes and Functions     | 2-11 |

| 2-5   | Byte/Decimal Arithmetic Codes               | 2-15 |

| 2-6   | State Flip-Flop Functions (CHAL and CHAR)   | 2-16 |

| 2-7   | Miscellaneous Group Registers               | 2-18 |

| 2-8   | Control Engine Register Address Assignments | 2-31 |

#### SECTION 1 MLP-900 PROCESSOR DESIGN

#### 1.1 GENERAL

The STANDARD MLP-900 Multi-Lingual Processor is a microprogrammed data processor designed to provide a high degree of versatility and computing power. One of the most important features is the high-speed, on-line alterable microprogram memory. The order code is designed for ease of use. The processor language is called MINIFLOW\*; individual instructions are "ministeps". MINIFLOW programming resembles certain aspects of machine language programming on earlier processors. The MLP-900 is designed for direct access at the microprogram level. The MINI-FLOW programmer can "get to" all mode control flip-flops and machine registers. MINIFLOW routines and complementary hardware tailor the MLP-900 for efficient execution of a broad spectrum of target languages and systems. High level procedures in existing languages can be executed in MINIFLOW directly. Complex macros and subroutines can be synthesized in MINIFLOW and execution can be initiated by the fetch of a single, problem-oriented, target language instruction.

In a typical processor, the instruction set generally can be separated by function into three categories:

- a. Manipulation of arithmetic and logical operands.

- b. Control and sequencing of instruction execution.

- c. Input/output operations (which often combine both arithmetic and control functions).

In the STANDARD MLP-900, the facilities for performing arithmetic and logical transformations on data have been separated from the control and sequencing functions to a large degree. Control signal and data transfer interfaces provide communication between the data handling section, or Operating Engine, and the sequencer, or Control Engine. The Control Engine contains the microprogram (control) memory. Input/output operations, as in other processors, require considerable interaction between the sequencing and the data handling elements of the MLP-900. See Figure 1-1.

MINIFLOW instruction words are similarly divided into two types, called Operating and Control ministeps, which sequence the elements of the Operating and Control Engines, respectively. If an Operating ministep is followed in sequence by a Control ministep, the two will be executed simultaneously. Otherwise, a single Control ministep or one Operating ministep is executed.

Some processor tasks, which are highly repetitive in nature, are relatively inefficient when executed by an unassisted firmware routine. The MLP-900 has provision for up to four sets of Language Boards. The principal functions of Language Boards are to generate addresses and sequence accesses to Main Memory, extract data from target language instructions, and generate MINIFLOW entry addresses (branch vectors).

<sup>\*</sup>MINIFLOW is a trademark of STANDARD Computer Corporation.

NOTE: THE SC-700 MEMORY UNIT IS EXTERNAL TO THE MLP-900 PROCESSOR. ANY MLP-900 BUS CAN BE CONNECTED TO ANY SC-700 PORT. UP TO EIGHT 32K-WORD SC-700 MEMORY MODULES FIT INTO A SINGLE SC-700 CABINET. UP TO SIXTEEN CABINETS CAN BE ACCOMMODATED ON ONE BUS.

Figure 1-1. MLP-900 General Block Diagram

MINIFLOW language design and the MLP-900 hardware provide the following capabilities:

- On-line alterable microprogram (Read/Write Control Memory).

- Expandable Control Memory

- Interpretive execution of a wide range of target languages

- Multiple general-purpose registers

- Up to 1024 high-speed data registers (optional)

- BCD and byte arithmetic

- Multiple, independent, asynchronous, Input/Output buses

- Variable data field manipulation

- Direct access to all registers and control flip-flops

- Indirect register addressing at the microprogram level

- Flexible microprogram branching and transfer of control

- Microprogram subroutine entry and return

- Order code organized for efficient use of Control Memory

# 1.2 MLP-900 SUMMARY SPECIFICATIONS

- 128 nanosecond clock cycle

- 32 General Registers; 36 bits plus 4 parity

- Up to 1024 Auxiliary Registers\*; 36 bits plus 4 parity

- Expandable Control Memory up to 64K (K = 1024) locations; 32 bits plus 1 parity

- Both Read-Write and Read-Only Control Memory available in 512-word modular increments

- 32 Data Mask Registers; 36 bits plus 4 parity

- Four independent, asynchronous, half-duplex, External (Input/Output) Buses; 36 bits plus 4 parity

- Automatic microprogram subroutine stacking to 15 levels

- Up to 4 target languages (independent order code sets) per processor

<sup>\*</sup>Optional in increments of 256 words.

#### 1.3 OPERATING ENGINE DESIGN

Figure 1-2 is the functional block diagram of the Operating Engine. This portion of the MLP-900 contains registers, shifters and arithmetic and logical elements used to manipulate operands. The Operating Engine External Buses interface with Main Memory, peripherals, and other external devices. Several interfaces provide communication with the Control Engine. The Operating Engine can execute seven Operating ministep types:

- a. General Arithmetic (GEAR)--Performs binary arithmetic, logical operations, and single register shifts

- b. Character/Left (CHAL) -- Byte and BCD operations from right to left

- c. Character/Right (CHAR) -- Byte and BCD operations from left to right

- d. Conditional External Data Exchange (CEDE) -- Transfers addresses, target instructions and data between the MLP-900 and Main Memory

- e. Transfer External (TEXT) -- Transfers addresses and data between the MLP-900 and devices on the External Buses

- f. Shift Instruction (SHIN) -- Executes complex shift operations

- g. General Data Transfer (GENT) -- Transfers data between Operating Engine Registers and to and from the Control Engine interface

The nominal Operating Engine register length is 36 bits. The Primary Adder operates on two 36-bit inputs and the Byte/Decimal Adder manipulates two 8-bit bytes. Parity is maintained on 9-bit bytes during data transfers in the Operating Engine. Logical transformations which do not maintain parity, such as arithmetic and shifting operations, are performed by two identical, independent, logical structures. The outputs of the two elements are compared at clock time for identity. If they are identical, parity is regenerated; otherwise, an Action Request (microprogram interrupt) is forced. Byte parity (9-bit) is sent out over the External Buses and incoming parity is checked when data is moved from the External Bus Registers.

The Operating Engine accommodates up to four Language Boards. These provide a hardware assist to data exchange operations (CEDE ministeps) which process target language instructions and format Main Memory addresses. Each Language Board in the Operating Engine is matched with a corresponding Control Engine (CE) Language Board. Operating Engine (OE) Language Boards format addresses and commands to Main Memory. They also gate indirect addresses to General Registers, control the Primary Adder and transfer data to External Bus Registers. These functions allow

Figure 1-2. Operating Engine Block Diagram

certain types of fetches from memory to be addressed by data in an incoming word. The third major function of the OE Language Boards is to translate target language order codes into initial MINIFLOW entry addresses. Memory protection, certain types of indexing, page searching and other special-purpose address modification functions can be performed by OE Language Boards. Language Boards translate order codes and extract data and address fields faster than unaided MINIFLOW. Any function provided by either the OE or CE Language Boards can be accomplished by a MINIFLOW routine at the cost of processing speed and increased Control Memory space.

The MLP-900 accommodates up to 1024 full-word Auxiliary Registers. These registers may be used as high-speed (one-clock-time access) buffers, temporary data storage, etc. Auxiliary Registers are optionally available in increments of 256 words.

A data masking capability allows manipulation of fields shorter than the full Operating Engine register length. Thirty-two Data Mask Registers, 36 bits wide, are preloaded with mask words via MINIFLOW initialization routines. Mask words, or Masks, modify the operation of both the Primary and Byte/Decimal Adders and data transfers into the result register from the Primary Bus. One data masking mode allows loading a field into a register without changing masked-out bits. In the General Arithmetic (GEAR) ministep Clear mode, masked-out bits are zero-set in the result register. Only masked-in data is transferred in either mode. Arithmetic and logical operations apply to masked-in fields and ignore masked-out bits.

A number of register addresses other than General Registers are addressable during CEDE, TEXT and GENT execution. 1024 addresses are reserved for communicating with the OE Language Board Registers. Other addresses are reserved for the Target Instruction Registers (Primary and Secondary), the CE Data Buss, Data Mask Registers, Auxiliary Registers and External Registers.

Ministeps are obtained two at a time from Control Memory each clock cycle. Operating Ministeps are executed out of the OE Ministep Register (refer to Figure 1-4) in the Control Engine. Decoded control signals, from the OE Ministep Register, sequence the logical elements of the Operating Engine.

#### 1.3.1 General Registers

The MLP-900 has 32 General Registers, each 36 data bits wide. Four parity bits, one for each 9-bit byte, are maintained with each register. All 32 registers are addressable as inputs to the Primary and Byte/Decimal Adders. Except for General Register 31, the Shift Extension Register, none of the General Registers has a dedicated function. General Registers have two independent address structures. The Operand A register specified by an Operating ministep is gated to one input of the Adders and the Operand B input goes to the other, depending on the addressing options of the ministep. Any of the General Registers may be specified as either, or both, Operand A or B inputs to the Adders by most Operating ministeps. Both Operand A and B registers can also be addressed indirectly. The indirect address mode of an Operating ministep uses the

five low-order bits in one of the 16 CE Pointer Registers (refer to paragraph 1.4.5) to specify the address of the corresponding operand in the General Registers.

Transfers of data to the General Registers from the Primary Bus (GEAR, CHAL, CHAR, and SHIN ministeps) are modified by the contents of one of 32 Data Mask Registers. In the Non-clear or replacement mode of data masking operations, logic prevents masked-out bits (corresponding to zeros in the mask word) from being changed in the General Registers. In the Clear mode of the GEAR ministep, masked-out bits are replaced with zeros. When the Test function of the GEAR, CHAL, CHAR, SHIN, and CEDE ministeps is enabled, the Operand A General Register is not loaded with the result of the operation, regardless of masking functions.

Odd-numbered General Registers are also bused to the Extension Shifter. During double-register-length shift operations (SHIN ministep), the Extension Shifter is paired with the Primary Shifter. Even-odd pairs of General Registers can be specified. General Register 31, the Shift Extension Register, can be paired with any General Register as an operand for double-length shifts. Refer to paragraph 2.2.3 for a description of the Shift Instruction, shift paths and functions.

# 1.3.2 Primary Adder

The Primary Adder is a 36-bit, parallel binary, arithmetic and logical processor. GEAR ministeps execute the 16 operations listed in Table 1-1. The result of operating on the Operand A and B inputs is placed in the Operand A register, except when the TEST bit is true. The Primary Adder is also used with several CEDE, TEXT, and SHIN ministep types, but operations are limited to binary addition and subtraction.

Operand B inputs to the Primary Adder include General Registers, Long and Short Immediate (literal) operands and the contents of any one of 16 Control Engine Pointer Registers. Operand A inputs are the General Registers or External Bus Input Registers. Inputs from the External Bus Registers are gated to the Primary Adder by Operating Engine Language Boards to speed up memory fetches during some types of CEDE ministeps. The result of this operation goes to the associated External Bus Output Register as an External Command Word.

Data Mask words affect the Primary Adder operation. Masking allows the MINI-FLOW programmer to perform arithmetic, logical manipulation and testing on variable fields. Masking functions are:

- Adder outputs are forced to zero in masked-out bit positions.

- Arithmetic carries are not generated in masked-out bits.

- · Arithmetic carries are propagated over masked-out bits.

Table 1-1. Primary Adder Operations

|                                                                                    | Arithmetic                                  |                                                                                                  | Logical                     |

|------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------|

| $A \leftarrow A+B$ $A \leftarrow A+\overline{B}+1$ $A \leftarrow \overline{A}+B+1$ | (A-B, 2's complement) (B-A, 2's complement) | $A \leftarrow A \cdot B$ $A \leftarrow A \cdot \overline{B}$ $A \leftarrow \overline{A} \cdot B$ | (Logical AND)               |

| A ← A+B+COF1<br>A ← A+B+COF1<br>A ← Ā+B+COF1                                       | (Conditional carry-in)                      | A ← AUB<br>A ← AUB<br>A ← ĀUB                                                                    | (Logical OR)                |

| $ \begin{array}{l} A \leftarrow B \\ A \leftarrow \overline{B} \end{array} $       | (Clear and add) (1's complement)            | $A \leftarrow AEB$ $A \leftarrow AE\overline{B}$                                                 | (Exclusive OR)<br>(Compare) |

"A" is Operand A. "B" is Operand B. "A" is the 1's complement of A. "COF1" is the Carry-out State flip-flop used as initial carry-in. "•" represents the logical product (AND) operation. "U" represents the logical union (OR) operation. "E" represents the Exclusive OR function. "

— " (left arrow) denotes that the result of the operation on the right is transferred to the location specified on the left.

# 1.3.3 Byte/Decimal Adder

The MLP-900 Byte/Decimal Adder operates on 8-bit bytes. During the Character/Left (CHAL) and Character/Right (CHAR) ministeps, the Byte/Decimal Adder combines an 8-bit Operand A with an 8-bit Operand B input. The result goes to the Operand A location unless the TEST bit is on. Operand A inputs are General Registers. Operand B inputs are General Registers and auxiliary Operand B inputs (refer to paragraph 1.3.2). The byte location within a word is also specified. Figure 1-3 shows byte boundaries within a 36-bit register word.

Figure 1-3. Byte Data Word Format

Four CE Pointer Registers (refer to paragraph 1.4.5) are available to tally byte and word locations in two operand character strings. Two of these four Pointers (P00 and P01) are used to indirectly address the A and B byte locations. The other two (P02 and P03) are used to hold character counters. For the CHAL ministeps, Pointers 00 and 02 are decremented if the A byte address is obtained indirectly. Pointers 01 and 03 are decremented if the B byte is indirectly addressed. Zero Sense and All Ones Sense State pseudo-flip-flop outputs, generated by the contents of the four Pointer Registers, are sampled to control sequencing. The CHAR ministep is similar. However, Pointers 00 and 01 are incremented instead of decremented when the associated byte address is indirect, and the pseudo flip-flops sampled for these two pointers would be "Three Sense" and "Four Sense". In both CHAL and CHAR if the TEST bit is true no incrementing or decrementing takes place even though byte address is specified indirect.

The Byte/Decimal Adder executes decimal operations on binary-coded-decimal (BCD) characters (two per byte) and binary operations on 8-bit bytes, as shown in Table 1-2. Decimal arithmetic combines the two-BCD-digit A and B bytes and generates a decimal sum or difference. Both inputs are checked for validity and the result is corrected for carries. Except when masked, binary operations affect the entire 8-bit operand field. CHAL and CHAR Masks are the eight least significant bits of the addressed Data Mask word.

Table 1-2. Byte/Decimal Adder Operations

|   | Decimal |          |   | Binary   |                        |   |         |                        | Logical |       |  |

|---|---------|----------|---|----------|------------------------|---|---------|------------------------|---------|-------|--|

| Α | +       | A+B      | Α | <b>-</b> | A+B                    | Α | <b></b> | A+B+COF1               | Α       | ← B   |  |

| Α | 4       | A+B      | Α | •        | $A + \overline{B} + 1$ | Α | -       | $A+\overline{B}+COF1$  | Α       | ← A·B |  |

| Α | 4       | A+B+COF1 | Α | +        | Ā+B+1                  | Α |         | $\overline{A}$ +B+COF1 | Α       | ← AUB |  |

| Α | 4       | A+B+COF1 |   |          |                        |   |         |                        | Α       | ← AEB |  |

<sup>&</sup>quot;B" represents the 9's complement of two BCD characters in the B byte.

#### 1.3.4 Data Mask Registers and Functions

The MLP-900 Processor has 32 Data Mask Registers, each 36 bits wide. Mask Registers are divided into two banks of 16 registers. Bank selection is controlled by the Bank Select State flip-flop (refer to paragraph 1.4.8). Data masking allows selective operation on bits and fields within a word. Masking is effective during GEAR, CHAD and SHIN ministeps. A Mask Register is addressed each execution of these ministeps. The eight, low-order bits (bits 28-35) in the selected Mask Register are active for CHAD. During SHIN, masking is effective on data in the Primary Shifter. Bit positions in the selected Mask Register which contain a one (1) are defined as masked-in bits. Bits containing a zero (0) are masked-out bits.

During GEAR, Masking can operate in one of two modes. In the Clear mode, all masked-out bits of the result word transferred into the Operand A register are replaced by zeros; masked-in bits are read into the register. If the CLEAR bit is off, masked-out bits inhibit alteration of the contents of corresponding bits of the receiving register. Masked-in bits will be loaded normally. The Clear mode is equivalent to the generation of the logical product of the Mask word and the result word. When the CLEAR bit is false (zero), masked-on bits are loaded into the result register without disturbing data in masked-off bit positions, which is equivalent to field replacement.

Data Masks also modify the operating modes of the Primary and Byte/Decimal Adders, as described in paragraphs 1.3.2 and 1.3.3, respectively. In all masked-out bit positions, the Adder output is forced to zero. This makes it possible to test the result of the operation on masked-in fields. In the Adders, mask logic enables the propagation of carries through masked-out bits and suppresses carry generation. Arithmetic operations are executed correctly on fields shorter than the full register

word (or full byte width during the CHAL and CHAR ministeps). If a carry-out signal is generated in a masked-in field, it will propagate through masked-out bits. If it encounters no masked-in bits, it will be sensed as a Carry-Out signal (COP), and will be loaded into the Carry-Out flip-flop (COF1) at clock time.

Zeros (0) are shifted into vacated masked-in bit positions of the result word when a shift is executed. In the Clear mode of the GEAR ministep, data is shifted into masked-out bit positions without being lost.

#### 1.3.5 Shift Operations

The Operating Engine has two functionally identical Shifters. Both are 36-bits wide and have some shift paths in common. The Primary Shifter operates on the output of the Primary Adder. The Extension Shifter operates on data in odd-numbered General Registers and External Bus Registers. Up to 16 bits of cross-over data is passed when a connected shift is executed. GEAR ministeps control only single-register shifts by the Primary Shifter. Shift Instruction (SHIN) ministeps can execute both single- or double-register shifts. SHIN codes can command connected or independent double-length shifts, single-length shifts, circular shifts (double-or single-length), primitives for iterated divide and multiply algorithms, normalize shifts and indirect shifts. The SIIIFT AMOUNT field of the GEAR, and SHIN ministeps can specify one-clock-cycle shifts of left or right 0, 1, 2, 4, 6, 8, 12, and 16 bits.

SHIN indirect shifts use the Shift Control Pointer Register (P07) in the Control Engine. The 6- and 12-bit shifts cannot be executed by indirection. When an indirect shift is executed, the four least significant bits and the Logical OR of the four most significant bits in 8-bit-wide Shift Control Pointer Register are sampled. Since the maximum single shift is 16 bits, a 16-bit shift is taken each time logic detects a count greater than 16; i.e., a one (1) somewhere in bits 0-3 of the Shift Control Pointer. On execution, the Shift Amount count is reduced by 16. If the four most significant bits are zero, the next lower bit which contains a one (1) controls the shift. If the Shift Control Pointer has a count of 11 (binary 1011), for example, and the indirect shift is repeated, shifts of 8, 2, and 1 bit would be executed consecutively. The count in the Pointer is reduced by the amount of the shift each time. By pairing a "branch" type Control ministep to test the SHD (Shift Done) State pseudo-flip-flop, with a SHIN ministep, a 1-clock-time repetitive loop can be formed to execute indirect shifts until the Pointer count goes to zero.

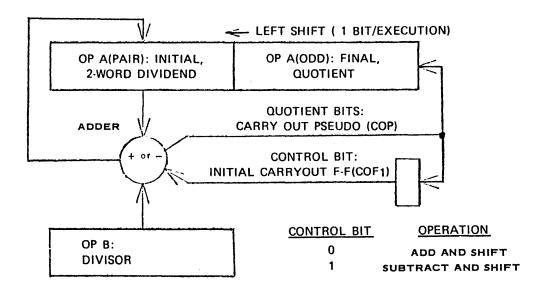

Multiply and Divide capability are provided by repeated execution of corresponding SHIN ministeps. The number of iterations is initially placed in the Shift Control Pointer Register. The count in the Shift Control Pointer is reduced by one each iteration and the loop is normally terminated as the count goes to zero. Normalize shifts are controlled by outputs from the CE Language Board. A tally is kept in the Shift Control Pointer during Normalize. An output of the Language Boards, the Normalize Done State pseudo-flip-flop, is available for testing to control the process. Specifications for SHIN ministep functions are located in paragraph 2.2.3.

#### 1.3.6 External Buses and Registers

Except for some miscellaneous control outputs and interrupt inputs, the MLP-900 Processor I/O interface consists of up to four External Buses. Each is 36 data bits and 4 parity bits wide. Each Bus uses an associated group of control, signalling and timing lines to sequence data transfers in both directions. Buses are bidirectional, time shared (half-duplex) communications ports, designed to send addresses and data out and receive data back with equal facility. The MLP-900 communicates with devices on the bus by way of up to 8 External Bus Registers. Each Bus has a register for incoming data and a register for outgoing addresses and data. Transfers to and from the External Bus Registers are sequenced by Conditional External Data Exchange (CEDE) and Transfer External (TEXT) ministeps. CEDE ministeps are designed for fetching target instructions and operands from Main Memory. TEXT is used to communicate with peripherals. Various fields of incoming target language instructions are processed by the MLP-900 Language Boards under the control of the CEDE ministep. Some of the CEDE ministeps provide semi-automatic sequencing of instruction and operand fetches. A number of CEDE and TEXT varieties place the processor into the Wait mode if an external device has not responded to a request when execution begins. During waits, ministep execution is inhibited until the desired operation occurs, or an Action Request forces a transfer of control.

The MLP-900 Processor samples four parity bits on each input transfer. If bad parity is detected during a fetch sequence, the previously transmitted external address word in the Output Register allows a retry of the fetch. This greatly improves the possibility of recovering from a transient error on the input.

The MLP-900 is designed to work with the SC-700 Magnetic Core memory. With proper interfacing, however, the processor can be adapted to communicate with almost any type of self-clocked memory unit, since data transfers inward have few timing constraints. Appendix A of this document is a short description of the SC-700 memory.

#### 1.3.7 Operating Engine Language Boards

Operating Engine (OE) Language Boards perform a wide variety of tasks related to the generation of MINIFLOW entry addresses from target language instructions and formatting address (External Command) words to Main Memory. In conjunction with a corresponding Control Engine (CE) Language Board, an OE Language Board adapts the MLP-900 to a specific target language (instruction set) and target environment (system framework). Up to four pairs of Language Boards can be installed in each MLP-900 Processor. Appendix B contains a more detailed description of the MLP-900 OE and CE Language Board inputs, outputs and typical functions.

OE Language Boards have two primary functions. One is address modification for accesses to Main Memory. Address modification is effective when External Command words, generated by CEDE ministeps, initiate fetches of target language instructions and operands and generate write addresses. Address modification facilities

translate target system addresses into equivalent Main Memory addresses. Typical functions include:

- Insert Memory Protect keys

- · Modify memory addresses using base register inputs

- Perform address limit violation checks

- · Translate relocated page addresses

- Translate character and byte addresses to word addresses

Another major function of the OE Language Boards is to generate hard-wired, initial entry addresses to initialization MINIFLOW during execution of the CEDE/WIN (Wait for Instruction) ministep, based on target instruction type. Initialization MINIFLOW routines include such functions as operand fetching, indexing, indirection, and some complex types of address modification. After the initialization routine is completed, the execution MINIFLOW routine is entered by branching with the assistance of the Control Engine Language Boards.

Several secondary functions can be performed by the OE Language boards, such as generating operand addresses from target instruction data. Similarly, OE Language Boards can execute fetches, using incoming data, during indirect addressing modes. Various CEDE ministep types are implemented to provide semi-automatic addressing sequences.

# 1.3.8 Target Instruction Registers

There are two Instruction Registers, Primary Instruction Register and Secondary Instruction Register, both of which can be loaded from the active External In Register as controlled by Operating Engine Language Boards. The Operating Engine Language Boards can also cause the Primary Instruction Register to be loaded from the Secondary Instruction Register. The setting of these registers would normally be accomplished during a CEDE/WIN. They are Operating Engine registers and may be addressed in the usual fashion by a GENT or CEDE ministep.

The Target Instruction Registers are sensible by the CE Language Boards. This allows target instruction field extraction.

# 1.4 CONTROL ENGINE DESIGN

Figure 1-4 is a functional block diagram of the MLP-900 Control Engine. The Control Engine can be conceptually divided into two smaller functional groups. One is made up of the Control Memory Address Generators, the Control Memory itself, its Output Registers and the Operating and the Control Engine Gating structures. The second group sequences data transfers, stores data, monitors status and controls testing and sequencing. Major operations of this part of the Control Engine include:

- Generate Control Memory address inputs

- Translate target language instructions and extract data fields

- · Provide iteration control and indirect register addressing

- Hold "Status" data and tally external and internal interrupts.

- Interface between the Operating and Control Engine registers.

Figure 1-4. Control Engine Block Diagram

Two sequential ministeps are fetched each clock cycle. The even and odd Control Memory banks are completely independent. Current ministep addresses may be either even or odd without restriction. Two ministeps will be executed simultaneously when an Operating ministep is followed sequentially by a Control ministep (with one exception). Only the current ministep is executed for other sequences. Control Engine ministeps take no additional processing time when paired. It is not necessary to pair ministeps if there are no processing benefits. This may improve efficiency by saving some locations in Control Memory.

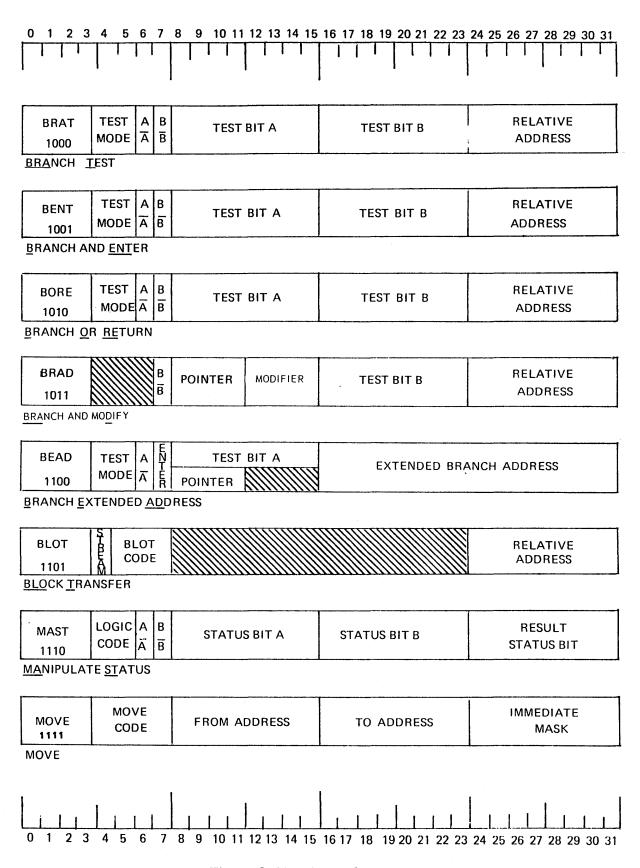

Control ministeps sequence Control Engine logic just as Operating ministeps regulate Operating Engine functions. Eight Control ministep varieties are available. There are five Branch ministeps, a Block Transfer ministep for data transfers between Control Memory or the Subroutine Return Registers and the Operating Engine interface, a ministep for manipulating the State (mode control) flip-flops and a ministep to move data between Control Memory registers.

Branch ministeps test State flip-flops which log the processor current status. Branch ministeps can be used to modify the sequence of Control Memory accesses if the branch test condition is true. Branch ministep execution can alter the sequential execution of the microprogram instruction in several ways. Least complex is the Branch Test (BRAT) ministep, which executes relative branches based on testing one or a combination of two State flip-flops. Branch and Enter (BENT) is similar to BRAT, except taking the branch causes the return address to be loaded into the Subroutine Return Stack. The Branch Or Return (BORE) ministep executes an automatic subroutine return if the branch is not taken. Branch and Modify (BRAD) modifies the amount contained in one of eight Control Engine Pointer Registers by the count specified in the ministep. One of 256 State flip-flops is tested by BRAD.

The Branch-Extended Address (BEAD) ministep has four modes of execution. Two modes execute absolute branches, indexed and unindexed, to any location in the Control Memory. When the branch is made unindexed in one mode, a State flip-flop is tested. The indexed absolute branch adds the contents of one of the Pointer Registers to the 16-bit Extended Branch Address field in the ministep. The third mode allows conditional branches with relative addressing to the full extent of control memory. The fourth mode adds the contents of a Control Engine Pointer Register to the continuation address and transfers. The BEAD ministep can execute a subroutine entry in all modes.

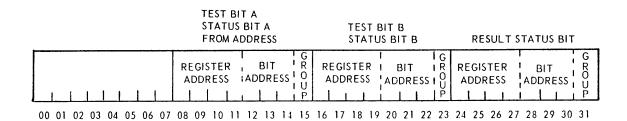

There are three Control ministeps other than Branches. The Manipulate Status (MAST) ministep operates directly on State flip-flops. Any two of the State flip-flops are addressed independently and a combination of their logical states sets or resets the result flip-flop. MAST cannot affect State pseudo-flip-flops (refer to paragraph 1.4.8). Block Transfer (BLOT) loads and reads out the contents of Control Memory and the Control Engine Subroutine Stack (refer to paragraph 1.4.4) and sequences Operating Engine data transfers. BLOT is usually paired with an Operating Engine CEDE, TEXT, or GENT ministep. The BLOT ministep uses "Load Control Words" to execute chained (scatter/load) transfers into the processor. The Control Engine MOVE ministep transfers data between Control Engine Registers and, in conjunction with the GENT, CEDE,

and TEXT ministeps, to and from the Operating Engine. Data is transferred in 8- or 16-bit bytes, depending on the MOVE mode selected. The MOVE ministep also has a mask capability on 8-bit transfers.

# 1.4.1 Control Memory Addressing

Control Memory address inputs are gated from a number of sources to the Control Memory Address Generators by the Next Address Select logic. The major inputs are from the incremented Current Address Register (when no branching or transfer of control takes place), Control Engine Pointer Registers, the Subroutine Return Stack (when a subroutine is EXITED), the Branch Address fields of various Control ministeps, and the OE Language Boards when a CEDE/WIN (Wait for Instruction) Operating ministep is executed. The CEDE/WIN Ministep generates a starting address for MINIFLOW routines to initialize target language instruction processing. Refer to Figure 1-5.

Another input, not shown in Figure 1-2, is a special-purpose Entry Address Generator, which provides hard-wired transfer addresses into error and interrupt MINIFLOW routines. Also not shown are inputs from Maintenance Console switches which are used for trouble-shooting and initialization.

The Even and Odd Address Generators are adders and incrementers which form Control Memory bank addresses from the base address inputs and modifiers gated by the Next Address Select logic. Several modes of addressing are synthesized from these inputs. Departing from the nominally sequential, i.e., current address plus increment (continuation address) and current address plus increment plus one; we have (neglecting the incremented address of the second ministep):

- Branch Relative

- Branch Absolute

- Branch Absolute plus Pointer Count

- Branch and Store Subroutine Return

- Branch and Modify Pointer Count

- Continuation plus Pointer Count

- Subroutine Return

- "Forced" Transfers

High-priority forced transfers occur immediately when internal monitoring logic detects an error Action Request interrupt condition, Lower-priority Action Requests take effect during CEDE Wait modes. Any of a number of lower priority Target System Interrupts can cause a forced transfer if present when a CEDE/WIN ministep execution is attempted.

Figure 1-5. Control Memory Address Selection, Flow Diagram

#### 1.4.2 Control Memory Design

The Control Memory is organized into odd and even banks. Two sequential ministeps are accessed at a time. An important feature of the MLP-900 Control Memory is that it is available in either Read-Write or Read-Only versions. The high-speed, Read-Write Storage (RWS) of the MLP-900 lets the user modify microprograms practically at will. The MLP-900 Processor with a RWS is highly adaptable and can peform processing functions in different languages (order codes) by reading in a new MINIFLOW and enabling the corresponding set of Language Boards.

Read-Write Store modules are composed of 512 32-bit (plus parity), semiconductor registers. To change the microprogram during operation and for initialization when the processor is turned on, the RWS is loaded from an external storage element. The BLOT (Block Transfer) ministep is used for initializing and overwriting the RWS. Due to its flexibility, RWS is highly useful for program check-out, debugging, maintenance and sequential overlay of MINIFLOW routines.

Read-Only Store (ROS) is a high-speed, 32-bit word (plus parity) memory with contents which are permanently fixed when the module is built. Data in the ROS cannot be altered by over-write, power loss or transient conditions. The contents of ROS modules must be completely specified at the time hardware is ordered. ROS modules currently contain 128 words (64 even and 64 odd locations).

#### 1.4.3 Ministep Registers and Gating Functions

Even Control Memory and Odd Control Memory outputs are read into the Operating Ministep Register and Control Ministep Register, depending on sequencing and ministep type. After the Ministep Registers are loaded, their contents are further decoded and passed to gating structures which sequence the Operating and Control Engine elements. After each access of the Control Memory, the Operating and Control Ministep Registers hold the currently addressed MINIFLOW word and its next sequential successor ministep. The current ministep is read from the Control Memory location which has the numerically smaller address of the pair. It may be located at either an odd or an even address. The most significant bit in the OP CODE field (bit zero) determines whether the current ministep is routed to the Operating or Control Engine Gating structure.

If the current ministep is an Operating type and its successor is a Control type, both ministeps will be executed simultaneously with these exceptions:

- If the current ministep is an Operating type and it specifies a Long Immediate Data word (literal operand), the successor word is not an instruction. From the register, it is gated to the Control Engine Data Bus. From there it goes to the Operating Engine as an auxiliary Operand B input of the Primary Adder.

- CEDE/WIN ministeps inhibit execution of any successor ministep, since a forced branch is always taken (to an even Control Memory location).

It is possible to have a Control ministep for the current ministep. When this happens, the current ministep has priority of execution over the successor ministep. The current ministep is routed to the Control Engine Gating when it is a Control ministep and the successor ministep is not executed. Likewise, if the two sequential ministeps are both Operating ministeps, the current ministep has a priority of execution and it is routed to the Operating Engine Gating elements. The successor ministep is not executed at this clock. If no branch is taken, the Current Address Register is augmented by one and the successor ministep and its successor are read from Control Memory the next cycle.

#### 1.4.4 Subroutine Return Stack and Stack Control

The Subroutine Return Stack is a group of 16 storage registers which hold 16-bit return addresses. A subroutine Return Register is loaded each time a subroutine entry is executed. Entries are made when a BEAD (Branch-Extended Address), with the ENTRY bit on, or a BENT (Branch and Enter) ministep executes a branch. Entries are also made when a breakout from the normal MINIFLOW sequence is forced by an Action Request (interrupt). Destacking occurs on a BORE (Branch Or Return) ministep that does not take the branch.

Loading of subroutine return addresses is scheduled by the Stack Pointer Register which addresses the top of the stack (the active return address). Pointer Register 06 is dedicated to this function. When the four least significant bits of the Stack Pointer are zero, the stack is empty. Initial entry into an empty stack is location 01. Subsequent entries go into consecutive ascending locations. A Stack Full Action Request occurs when location 15 is loaded. At the next clock, the now current address is entered in Stack Register 00 and a forced transfer to the Stack Full service routine is executed. A Stack Underflow Action Request occurs when a return is executed and the four least significant bits of the Stack Pointer Register are zero (0), and Action Request Lockout ARL2 is off. The Stack Pointer will decrement, and at the next clock the Action Request breakout will enter the address of the return ministep in Stack Register 00, and control will be transferred to the Stack Underflow service routine.

Although the usable Subroutine Return stack capacity is only 15 words, with an 8-bit Stack Pointer and two MINIFLOW service routines, the stack capacity can be easily extended to 240 levels (15 x 16). More complex service routines can extend the stack depth indefinitely or handle multiple stacks. However, the stack full service routine must detect a real upper-bound stack overflow error, otherwise a programming error can cause subroutine entry to an infinite number of levels. Likewise, the underflow MINIFLOW routine must check for a real lower-bound stack limit for the same reason.

#### 1.4.5 Pointer Registers

A group of 16 Control Engine Pointer Registers are available for counting and indirect addressing functions. Register locations 00-07 are counting Pointers. Locations 08-15 are pseudo-register (non-counting) Pointers, mechanized as sense line outputs, with functions determined by Language Boards. Most of the counting Pointers

perform special services for other Control and Operating Engine logic elements at various times. Otherwise they can be used for general processing functions. Table 1-3 is a list of Pointer assignments.

Table 1-3. Pointer Register Functions

| Pointer Register | <u>Function</u>                      |  |  |  |  |

|------------------|--------------------------------------|--|--|--|--|

| 00 - 03          | CHAL, CHAR, BLOT sequence Counters   |  |  |  |  |

| 04,05            | General Purpose (not dedicated)      |  |  |  |  |

| 06               | Subroutine Stack Pointer             |  |  |  |  |

| 07               | Shift Control Register               |  |  |  |  |

| 08 - 14          | CE Language Boards (Pseudo-register) |  |  |  |  |

| 15               | OE Language Boards (Pseudo-register) |  |  |  |  |

Pointer Register contents indirectly address General Registers for Operating ministeps which allow indirection on Operand A and B selection. In addition, the CHAL (Character/Left) and CHAR (Character/Right) ministeps (paragraph 2.2.4) allow indirect selection of the Byte A and Byte B Operands within the Operand A and B words. However, the CHAL and CHAR Byte A indirect address is specified by Pointer Register 00. The Byte B indirect address is obtained from Pointer 01. Pointers 02 and 03 are normally used as character string length counters for the A and B byte operands respectively when indirect addressing occurs. These four Pointer Registers have individual decrementers. In addition, Pointers 00 and 01 have individual incrementers. The count in the two pairs of Pointers is adjusted by one (1) during the execution of the CHAL and CHAR ministeps when the corresponding indirect byte address mode is specified. In addition to assisting the CHAL and CHAR ministeps, Pointers 00 - 03 are also used to automatically tally locations and word counts during execution of the BLOT (Block Transfer) ministep (refer to paragraph 2.3.6).

Pointer Registers 04 and 05 are undedicated registers and can be used for general-purpose counting or indirect addressing. Pointer 06 is the dedicated Subroutine Stack Pointer (described in paragraph 1.4.4). Pointer 07 holds and tallies indirect shift amounts for several of the Shift Instruction (SHIN) ministep types and maintains a shift count during SHIN Normalize (refer to paragraph 2.2.3). Pointer Pseudo-registers 08-15 represent data translated from target instructions by the Operating and Control Engine Language Boards. Pointers 08-14 are driven by CE Language Boards from the Target Instruction Registers in the Operating Engine. Pointer Pseudo-register 15 is similarly driven by the OE Language Boards. Pointer Pseudo-registers can be used for indirect addressing and auxiliary Operand B inputs, but their contents must be moved to one of the counting Pointer Registers for loop control, shift operations and similar functions.

In addition to the four dedicated single-count decrementers of Pointer Registers 00-03, and incrementers of Pointer Registers 00 and 01, a separate Pointer Adder can be used to alter the contents of the counting Pointer specified in a BRAD (Branch and Modify)

ministep by the amount in the MODIFIER field. The Pointer count can be changed by any amount from plus seven (+7) to minus eight (-8) in one clock cycle.

Most Pointer Registers have a State pseudo-flip-flop (ZSI00-11) which goes to the one (1) logic state when the corresponding Pointer count is zero (refer to paragraph 1.4.8). These Zero Sense State flip-flop indicators can be tested for zero (0) logic conditions during the counting process, to maintain loop control. In addition, Pointer Registers 00-03 are mechanized with All Ones Sense State pseudo-flip-flops (OSI00-03) which are true when the corresponding Pointer contains all ones. In addition, Pointer Registers 00 and 01 have pseudo-flip-flops indicating when they have the value of either three or four (Three Sense TSI00, TSI01 and Four Sense FSI00, FSI01). These outputs are normally used for loop control during CHAL and CHAR ministep execution.

Since the BRAD ministep can increment any counting Pointer (P00-P07) by an amount other than one, it is possible to pass through a zero count from either direction. Consequently, a test of the Pointer Zero Sense pseudo-flip-flop will fail. When the Pointer Register count goes through zero, the overflow (or underflow) output of the Pointer Adder is used to drive the Through Zero State pseudo-flip-flop. This condition is true only during the clock cycle in which the overflow or underflow occurs. Through Zero must be sampled during the execution of BRAD to be valid. Since this output is developed relatively late in the clock cycle, a false branch condition resulting from a test of Through Zero causes a clock inhibit and a "hiccup" or one-clock-cycle delay. When testing a Zero Sense or One Sense pseudo-flip-flop of one of the Pointers, the indication is present at the start of the next clock cycle after the counting operation is complete and testing cannot cause a "hiccup."

Figure 1-6. MINIFLOW Status Word Format

#### 1.4.6 MINIFLOW Status Word

The two elements labeled in Figure 1-4 as "MINIFLOW Status Register" and "Current Address Register" are treated as a single 32-bit register by the BLOT (Block Transfer) ministep. The composite register holds the MINIFLOW Status Word (MSW) in the format shown in Figure 1-6. The MINIFLOW Status Word facilitates initializing the processor from a cold start and when a target language changeover is executed.

The Language Board Select (LB) bits determine which Language Board set is active when executing target instructions. These two bits enable one Control and Operating Engine Language Board pair (out of a possible four pairs). Two groups, of two bits each, separately select the External Bus address for I/O (TEXT BUS) and Memory (CEDE

BUS) communications. When the MSW Test Mode (TM) bit is on, the MLP-900 is in an abnormal state. This mode allows special operations to be performed to exercise and test automatic check and error Action Request logic. The true state (1) of the Test Mode bit enables:

- Writing into Control Memory with bad parity (BLOT/WBP ministep; paragraph 2.3.6).

- Reading Control Memory with bad parity for more than two consecutive clock cycles.

- Loading Operating Engine registers with bad parity (GENT ministep;paragraph 2.2.5).

- Forcing check errors (Check Test State flip-flop;paragraph 1.4.8).

- Setting the State flip-flop Clock Control (CKC) to zero (Machine Halt).

Action Request Mask (ACTION REQ. MASK) bits inhibit some Action Requests (AR's) or groups of AR's so that they cannot force a transfer of control (refer to paragraph 1.4.9).

A convenient way to initialize the MINIFLOW when executing a multiple block transfer (BLOT ministep) from an external source, is to load the MSW as the final step. After loading the MSW, the Current Address Register holds the start-up address for the new MINIFLOW.

# 1.4.7 Control Engine Language Boards

Four Control Engine (CE) Language Boards are paired with corresponding Operating Engine (CE) Language Boards. Language Board sets are selected by two bits in the Miniflow Status Word. The principle function of CE Language Boards to to extract and translate data from fields in target language instruction words. The mechanism for performing this function includes the Operating Engine Primary and Secondary Target Instruction Registers (refer to paragraph 1.3.8) which hold the data in original format; the CE Language Boards, which perform the decomposition and translation operations; and the Control Engine Pointer Pseudo-registers (refer to paragraph 1.4.5) and the CE Language Board State pseudo-flip-flops (refer to paragraph 1.4.8) which make the outputs available to the Control Engine. Appendix B contains a more detailed description of Language Board capabilities and interfaces.

CE Language Boards are passive and contain no internal storage elements. Extracted and translated data is selectively routed to CE Pointers 08-14, which can be tested, transferred or used as addresses or operands. If counting capability is required, the contents of Pointer Pseudo-registers must be moved to one of the countable Pointers. CE Language Boards develop the Group Entry address into the execution MINIFLOW from the target language instruction order code and place it in a Pointer Pseudo-register. The Group Entry address is called the "target entry branch table. Other fields which are normally held in Pointer Pseudo-registers include operand and index register addresses, character and word counts, shift amount data, literal operands (up to 8 bits), etc.

Target language instructions generally contain mode control data needed by the MINIFLOW programmer. To provide access to execution mode data, a group of State

pseudo-flip-flops (CLB00-11) are driven by the CE Language Boards. Control ministeps can sample these outputs to control execution sequencing. The Language Board Control State flip-flops (LBC 00-15) can be sensed by CE and OE Language Boards. They can be used to provide program control inputs to Language Boards as required.

Another function of the CE Language Boards is to examine the mantissa of floating point operands for leading zeros during execution of the SHIN/NORMALIZE Ministep. The output of this sampling process is the Shift Amount control to the Primary and Extension Shifters and a count (modulo the target exponent base) to tally the amount of normalization that takes place. An output is also generated when the process is complete (NMD--Normalize Done pseudo-flip-flop).

# 1.4.8 State Flip-flops

The Control Engine has a group of 256 addressable storage elements, called State flip-flops, which perform mode control functions. In most cases, State flip-flops are actual binary storage elements. Some are general-purpose and are available for scratch-pad use. Others are dedicated and are controlled by internal and external events. The remainder are synthesized from outputs of various logical elements in the processor and are called State pseudo-flip-flops. Table 1-4 is a listing of MLP-900 State flip-flops. They are grouped by characteristics and the addressing structure of the MOVE ministep which can access them. Appendix C describes the individual State flip-flops and their functions. Some general characteristics of the State flip-flops are as follows:

- General Indicator flip-flops are not dedicated and may be used as scratch-pad registers for housekeeping and status data, program monitoring and testing.

- Language Board (LB) Control (LBC00-15) flip-flops are available to use as mode control inputs to the OE and CE Language Boards. When they are not needed for this function, they may be used as general indicators.

- The External Write (EWR0-7) group can be mechanized to provide signals to external devices, separately from the External Buses. When not dedicated, they can be used as general indicators.

- The Action Request (AR) flip-flops respond to conditions which are to the MLP-900 Processor what system interrupts are to a machine language processor. They allow the normal MINIFLOW processing sequence to be modified by various internal conditions and external signals. When the hardware logic and the MINIFLOW simultaneously attempt to set and reset one of these flip-flops, the set input will dominate. The complement of Action Requests and a summary of their characteristics are described in paragraph 1.4.9.

- Control flip-flops are indicators which monitor status and control several important internal processor functions. When the hardware logic and the MINIFLOW simultaneously attempt to set and reset one of these flip-flops, the set input will dominate.

- Target System Interrupt flip-flops comprise four groups of eight bits each. For each Target System Interrupt flip-flop, there is a corresponding Interrupt Mask flip-flop. Each Interrupt Mask inhibits the true state of its corresponding Target System Interrupt flip-flop from causing a forced transfer of control to location 62 immediately prior to an attempt to execute a CEDE/WIN ministep.

Table 1-4. State Flip-Flop Listing (Group 0)

| General<br>Indicator F/F's                                                                                                                                                                                          | General<br>s Indicator F/F's                                                                                                                                                                            | Action<br>Request F/F                                                                                                                                                                                      | r's                                                             | Control<br>F/F's                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gen Ind GI00                                                                                                                                                                                                        | LB Control LBC00                                                                                                                                                                                        | Power On                                                                                                                                                                                                   | PON                                                             | Carry Out 1 COF1                                                                                                                                                                                                                                |

| Gen Ind GI01                                                                                                                                                                                                        | LB Control LBC01                                                                                                                                                                                        | Power Off                                                                                                                                                                                                  | POF                                                             | Carry Out 2 COF2                                                                                                                                                                                                                                |

| Gen Ind GI02                                                                                                                                                                                                        | LB Control LBC02                                                                                                                                                                                        | Odd CM Parity                                                                                                                                                                                              | OPAR                                                            | Zero Flag 1 ZRF1                                                                                                                                                                                                                                |

| Gen Ind GI03                                                                                                                                                                                                        | LB Control LBC03                                                                                                                                                                                        | Even CM Parity                                                                                                                                                                                             | EPAR                                                            | Zero Flag 2 ZRF2                                                                                                                                                                                                                                |

| Gen Ind GI04                                                                                                                                                                                                        | LB Control LBC04                                                                                                                                                                                        | Invalid CM Addr                                                                                                                                                                                            | ICAD                                                            | Invalid Digit IDF                                                                                                                                                                                                                               |

| Gen Ind GI05                                                                                                                                                                                                        | LB Control LBC05                                                                                                                                                                                        | Stack Full                                                                                                                                                                                                 | STAF                                                            | Invalid Sign ISF                                                                                                                                                                                                                                |

| Gen Ind GI06                                                                                                                                                                                                        | LB Control LBC06                                                                                                                                                                                        | Stack Underflow                                                                                                                                                                                            | STUF                                                            | Shift Out Sign SOS                                                                                                                                                                                                                              |