Filed Nov. 27, 1967 30 Sheets-Sheet 1 FIG. 1. 19 MAGNETIC MAIN MEMORY ARITHMETIC 20 AGNET UNIT (MAIN ENGINE, REGISTERS 30 21 31 22 10 32 TAPE 23 I/O CHANNEL INNER 33 CHANNEL COMPUTER 24 34 25 35 OPERATORS CONSOLE AND DISPLAY 26 36 Ť 27 18-TYPE WRITER CARD READER 37 28 38 WESSYC MAIN ENGINE REGISTER BITS AFFECTED 000 00-00 20 20 OWN 00 SO. 20  $\omega \omega \omega$ 3046323104662013253046 00-02 03-05 0608 09-11 115 12-14 15-17 18:20 21-23 24-26 FIG.4 33:35 MAIN ENGINE 00:05 ZONE CONTROL CODES 0308 0611 12-17 18-23 24:29 *3036* 01 3535353537037 09-17 18-26 27:35 116 24-35 13-17 LASZLO L. RAKOCZI DAVID E. KEEFER INVENTORS. GARY J. GOSS ERNEST J. PORCELLI BY 18:35 0935 20 00<del>-35</del> 00 00:3E 33

Filed Nov. 27, 1967

Filed Nov. 27, 1967

Filed Nov. 27, 1967

30 Sheets-Sheet 4

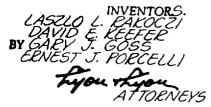

LASŽLO L. RAKOCZ/ DAVID E. KEEFER INVENTORS. GARY J. GOSS ERNEST J. PORCELL/ BY

Lyon Thyon ATTORNEYS

Filed Nov. 27, 1967

30 Sheets-Sheet &

LASZLO L. RAKOCZ/ DAVID E. KEEFER INVENTORS. GARY J. GOSS ERNEST J. PORCELLI BY

Tryon thyon

Filed Nov. 27, 1967

Filed Nov. 27, 1967

30 Sheets-Sheet 7

LASZLO L. RAKOCZI DAVID E. KEEFER INVENTORS. GARY J. GOSS ERNEST J. PORCELLI

> hyon thyon ATTOENEYS

Filed Nov. 27, 1967

30 Sheets-Sheet 8

LASZLO L. RAKOCZI DAVID E: KEEFER 'INVENTORS, GARY J. GOSS ERNEST J. PORCELLI BY

ATTORNEYS

Filed Nov. 27, 1967

Filed Nov. 27, 1967

Filed Nov. 27, 1967

## L. L. RAKOCZI ET AL

## LANGUAGE INDEPENDENT COMPUTER

Filed Nov. 27, 1967

# L. L. RAKOCZI ET AL LANGUAGE INDEPENDENT COMPUTER

Filed Nov. 27, 1967

Filed Nov. 27, 1967

30 Sheets-Sheet 14

F16.16c.

LASZLO L. RAKOCZI DAVID E. KEEFER INVENTORS. GARY J. GOSS ERNEST J. PORCELLI

> Lyon + Lyon ATTOENEYS

Filed Nov. 27, 1967

30 Sheets-Sheet 15

FIG. 14c

INVENTORS.

LASZLO L. RAKOCZI

DAVID E. KEEFER

BY GARY J. GOSS

ERNEST J. PORCELLI

Lyon Lyon

ATTORNEY

Filed Nov. 27, 1967

30 Sheets-Sheet 16

F1G. 14e

Filed Nov. 27, 1967

30 Sheets-Sheet 17

FIG. 15b<sub>1</sub>

INVENTORS.

LASZLO L. RAKOCZI

DAVID E. KEEFER

BYGARY J. GOSS

ERNEST J. PORCELLI

Lyon Thyon AT TORNEYS

Filed Nov. 27, 1967

FIG. 15c

FIG.15d

FIG. 15f

FIG. 15a

Filed Nov. 27, 1967

30 Sheets-Sheet 19

FIG. 15e

LASZLO L RAKOCZ/ DAVID E KEEFER INVENTORS. GARY J. GOSS ERNEST J. PORCELL/ BY

ATTORNEYS

Filed Nov. 27, 1967

30 Sheets-Sheet 20

# YB? (CONTINUED) IF YAUXI OR YAUXZ (TRAP) OR LK7. LK4 (SLOW TRANSFER) PB ICGO TO YB3 IF LK5 60 TO YB4 IF TK5. LKG 60 TO YB5 IF TK5. TKG (C) IF PIG 40 (NOT TRANSFER TRAP MODE) AND LKT. LK4 (FAST TRANSFER) AND LISAT (TEST SATISFIED) OR RITE (TRAP'TRANSFER INSTRUCTION) NEXT INSTRUCTION ADDRESS PD IC EXIT IF LK7 · LK4 (FAST TRANSFER) AND LTSAT (TEST NOT SATISFIED) NEXT NSTRUCTION ADDRESS PB IC 400ER 107 EXIT (E)IF PIG 40 (TRANSFER TRAP MODE) AND RITE (NOT TRAP TRANSFER INSTRUCTION) AND LISAT (TEST SATISFIED) AND LK7. TK4 (FAST TRANSFER) PB ICGO TO YB5

FIG. 15b2

LASZLO L. PAKOCZI

DAVID E. KEEFER

BY GARY J. GOSS

ERNEST J. PORCELLI

ATTORNEYS

Filed Nov. 27, 1967

30 Sheets-Sheet 21

| -    | -     |

|------|-------|

|      | 7 T   |

| FIG. |       |

|      | . , . |

|          |    | _             |

|----------|----|---------------|

| YA-T     | 1  | DTDDDT        |

| 1/7/     | _1 | PTR29-T       |

| Y2-T     | 7  |               |

| 76-7     | J  | PTR31-T       |

| PDOO-T   |    | PTR32-T       |

| 0004 5   | 4  |               |

| PDO1-T   | I  | PTR33-T       |

|          | 4  |               |

| PDO2-T   | i  | PTR34-T       |

| PDO3-T   | 7  |               |

|          | _  | PTR35-T       |

| PD04-T   | 1  | PEVEN-T       |

|          | 4  | PEVELVE       |

| PD05-T   | i  |               |

|          | 1  | 0-0-1         |

| PD06-T   |    | PTROX-T       |

| PD07-T   | 1  |               |

|          | 1  | PTRIX-T       |

| PD08-T   | I  | PTR2X-T       |

|          | 4  |               |

| PD09-T   | 1  | PTR3X-T       |

| PDIO-T   | 1  |               |

| PDIO-T   | 1  | PTR4X-T       |

| PDII-T   | 1  | PTPEY-T       |

| , , , ,  | 4  | PTR5X-T       |

|          | 1  | PTRGX-T       |

|          | 1  | 1,12011       |

|          | 1  | PTE7X-T       |

|          | 1  | PTRYAT        |

|          | 1  | PTRXO-T       |

| •        | 1  | PTRX1-T       |

|          | 1  | 1 /2011       |

|          | 1  | PTRX2-T       |

|          |    | OTOUR T       |

|          |    | PTRX3-T       |

|          |    |               |

|          | l  | PTEX4-T       |

| YTA29-T  | i  | PTRX5-T       |

| 7771207  |    |               |

| YTA31-T  | l  | PTRXG-T       |

|          | ł  |               |

| YTA3C-T  |    | PTRX 7-T      |

|          | 1  |               |

| YTA 33-T |    |               |

| YTA34-T  |    |               |

|          |    |               |

| YTA35-T  |    |               |

|          |    | 0             |

|          |    | RETCK-T       |

| KCDC     |    |               |

| KCP6     |    | RTTRA-T       |

| LJBI-T   |    | RTCKB-T       |

|          |    |               |

| PIGOG-T  |    | REEOF-T       |

|          |    |               |

| PIGI4-T  |    | REOFB-T       |

| PIG22-T  |    |               |

|          | l  | RAPID-T       |

| PIGZ4-T  | 1  | REAOV-T       |

|          |    | ~~~/          |

| PIG32-T  |    | _             |

|          |    |               |

| PIG34-T  | l  |               |

| PIG44-T  | Į  |               |

|          | 1  |               |

| PIG4G-T  |    |               |

|          | ł  |               |

| RINOZ-T  | l  |               |

| RINO3-T  | l  |               |

|          | Į  |               |

| RINIO-F  | j  |               |

|          | J  |               |

| PACOF-T  | I  |               |

|          |    |               |

| PACQZ-T  | ł  |               |

| PACS-T   |    |               |

|          | i  | 1467          |

| PMQS-T   | 1  | LASZ<br>DAVIL |

|          | 1  | DAVIL         |

| 1        | i  |               |

|          |    | GARY          |

TRANSLATOR A

LASZLO L. RAKOCZI DAVID E. KEEFER INVENTORS. GARY J. GOSS ERNEST J. PORCELLI

hyou thyou ATTORNEYS

Filed Nov. 27, 1967

Filed Nov. 27, 1967

30 Sheets-Sheet 23

FIG. 190

| 1851d<br>1890d<br>1890<br>1890<br>1890<br>1890<br>1890<br>1890<br>1890<br>1890    |                |                                                                                                                           |

|-----------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------|

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                             | C DECODE LOGIC | S T LTSAT-T  R F LTSAT-F                                                                                                  |

| 1-200d<br>1-200d<br>1-000d<br>1-0MSS1<br>1-5MSS1<br>1-5MSS1<br>1-8MSS1<br>1-1MSS1 | TRAWSLATOR C   |                                                                                                                           |

| 180M9<br>180M9<br>180M9<br>180M9<br>180M9                                         |                | LASZLO L. RAKOCZI<br>DAVID E. KEEFER<br>INVENTORS.<br>GARY J. GOSS<br>ERNEST J. PORCELLI<br>BY<br>Lyon Thyon<br>ATTORNEYS |

FIG. 19C.

Filed Nov. 27, 1967

30 Sheets-Sheet 24

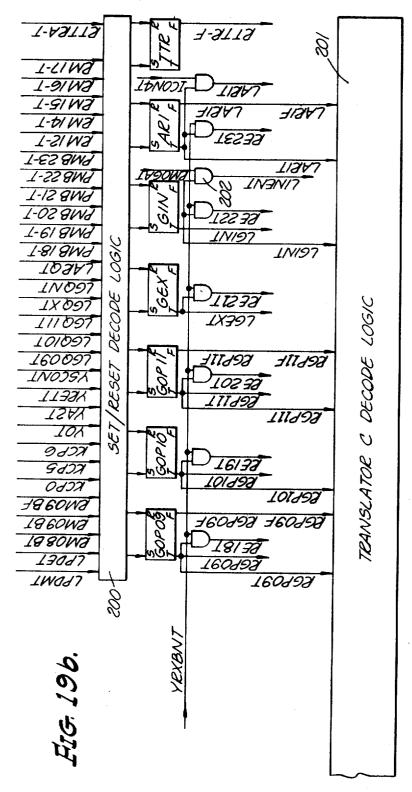

TRANSLATOR C

LASZLO L. LAKOCZI DAVID E. KEEFER INVENTORS. GALY J. GOSS. ELNEST J. PORCELLI

BY

Lyon thyon ATTORNEYS

# L. L. RAKOCZI ET AL LANGUAGE INDEPENDENT COMPUTER

Filed Nov. 27, 1967

Filed Nov. 27, 1967

30 Sheets-Sheet 26

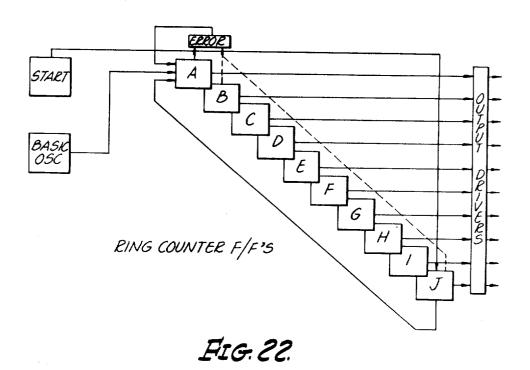

RING COUNTER

F/F'S 50 100 150 200 250 300 350 400 450 500 NANO SECS.

A

B

C

D

E

H

H

I

J

KCP0=J-A

KCP1=A-B

KCP2=C-D

KCP3=D-F

KCP5=G-H

KCP6=H-I

KCP1=I-J

FIG. 23.

LASZLO L. RAKOCZI DAVID E. KEEFER INVENTORS. GARY J. GOSS ERNEST J. PORCELLI Y

> Lyon thyon ATTORNEYS

Filed Nov. 27, 1967

30 Sheets-Sheet 27

FIG. 24

LASZLO L. RAKOCZI DAVID E. KEEFER INVENTORS. GARY J. GOSS ERNEST J. PORCELLI

> Lyon thyon ATTORNEYS

Filed Nov. 27, 1967

Filed Nov. 27, 1967

Filed Nov. 27, 1967

1

3,544,969 LANGUAGE INDEPENDENT COMPUTER Language index end David E. Keefer, Gary J. Goss, and Ernest J. Porcelli, Mission Viejo, Calif., assignors to Standard Computer Corporation, Santa Ana, 5 Calif., a corporation of Arizona

Filed Nov. 27, 1967, Ser. No. 685,857 Int. Cl. G06f 15/16, 9/00 U.S. Cl. 340—172.5

21 Claims

#### ABSTRACT OF THE DISCLOSURE

A digital computer which may be viewed as a computer within a computer and which can interpret a variety of machine languages permitting direct execution 15 of program libraries compiled for other computers without modifications or reprogramming. The inner computer has its own memory and registers and acts as an interpreter. The inner computer is programmed to interpret the language of another computer and to set up 20 the necessary logic for processing data, while the outer computer essentially acts as though it were the computer it is intended to emulate. Generalized console apparatus and circuitry enables duplication of operating conditions.

The present invention relates generally to digital data processors and more particularly to digital data processors that emulate new or prior art computer systems or 30 the like.

As is well-known to those skilled in the art, a program consisting of a series of computational procedures are written in order to permit the computerized solution of a problem. This program is eventually translated (either 35 by a programmer or the computer itself) into a sequence of steps called machine-language instructions before being executed by the computer. The machine language of a particular computer is the collection of all permissible machine instructions it can understand and execute. The  $^{40}$ number, meaning, and format of these machine-language instructions varies greatly from one make or model computer to the next. For example, one computer system may have a machine language expressed in terms of 48 binary digits (bits); whereas another may be expressed as a variable number of 8-bit characters. Furthermore, one computer model may require only one instruction to direct it to take two numbers from memory, add them together, and put the results back into memory. On the other hand, it might require three sequential instructions to perform the same computation on a different computer. It has been estimated that more than a hundred different programming languages are used with the thousands of computers in the United States.

One of the most important qualities of a particular machine language is its ability to control communications between the various functional stations or subsystems (memory, register, arithmetic units, input/output devices, etc.) of the computer system. Generally speaking, in present day computer systems the relationships among the functional stations is frozen completely, or to a large extent, by the design and wiring of the system. Since the machine language format of a particular computer is generally predicated upon the logic and wiring of the system, such fixed relationships mean that a particular computer can execute only one machine language in an economical manner, and thus is unable to utilize the full potential of each functional station.

As new and improved computing hardware is developed, it is almost imperative to use a new and improved format for the machine-language instructions in order

2

to take advantage of the improved features of the new generation equipment. Thus, the newer generation computing equipment will not understand and will not be able to directly execute programs written for the older generation computers. The user of older generation computers often finds it desirable to trade the older equipment for a newer model to benefit from the improved speed and computing techniques built into the newer equipment. In doing so, however, he often finds it costly and time consuming to rewrite his proven and useful programs so that they can be used with the newer generation computer. As related problem is faced by users of large scale computer installations who have a number of computer systems. These computer systems frequently have different machine-language repertoires which are not compatible with each other. That is, a program written for one computer system of the user will not perform on another computer system of the same

Accordingly, it is a principal object of this invention to provide a machine-language independent data processor for emulating other data processors and which can employ the program libraries thereof without modifications or reprogramming.

Another object of the present invention is to provide a data processor having the capability to duplicate the instruction repertoire of other computers.

An additional object of this invention is to provide a data processor capable of assuming the identity of another data processor in a flexible manner but which is lower in cost.

A further object of this invention is to provide a data processor for emulating other data processors and which can run programs directly from the programming media used by the processor it emulates.

Another object of this invention is to provide a data processor having what may be termed an outer computer and an inner computer for emulating a number of different computer systems.

A still further object of this invention is to provide a console system for a data processor which emulates the operational environment of other computers.

Another object of this invention is to provide a programable man-machine interface enabling an improved operating environment and which facilitates relatively simple on-line program debugging, analysis and diagnostics.

An additional object of this invention is to provide a data processor in which the machine-language repertoires of a number of computers may be stored as desired at various times to allow the execution of programs written for several different and incompatible computer systems.

Another object of this invention is to provide a data processor having the capability to include new and improved machine instructions which may be used in addition to, or in place of, regular machine instructions without requiring hardware changes in the data processor.

Another object of this invention is to provide a data processor system having the capability to be optimized for various types of problems.

A further object of this invention is to provide an upward and downward compatible series of data processors capable of variable performance by tailoring system configurations to particular data throughput requirements.

A still further object of this invention is to provide a data processor capable of executing higher level language statements without the same first being translated into a machine language.

An additional object of this invention is to provide a method of emulating computers.

These and other objects and advantages of the present invention will become more apparent upon reference to

10

the following description and the accompanying drawings

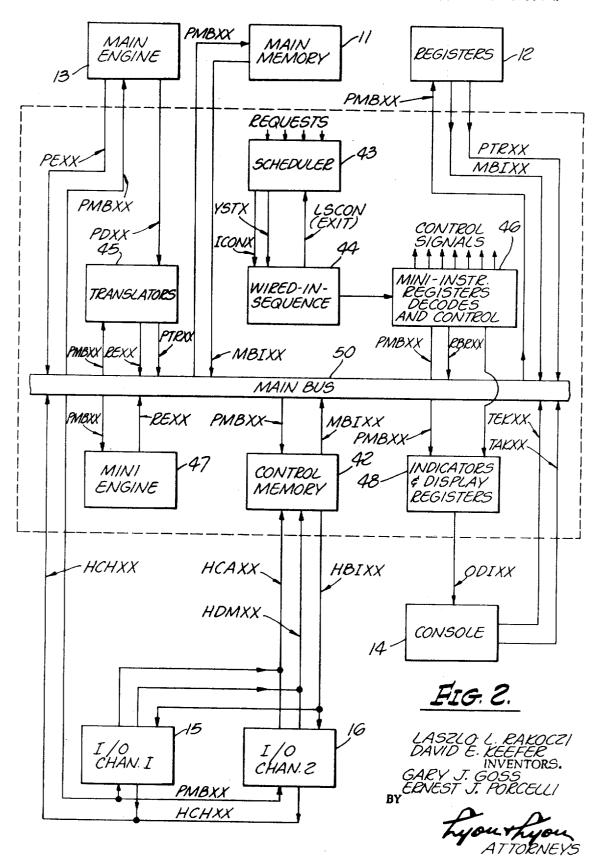

FIG. 1 illustrates in general block diagram form a computing system according to the present invention;

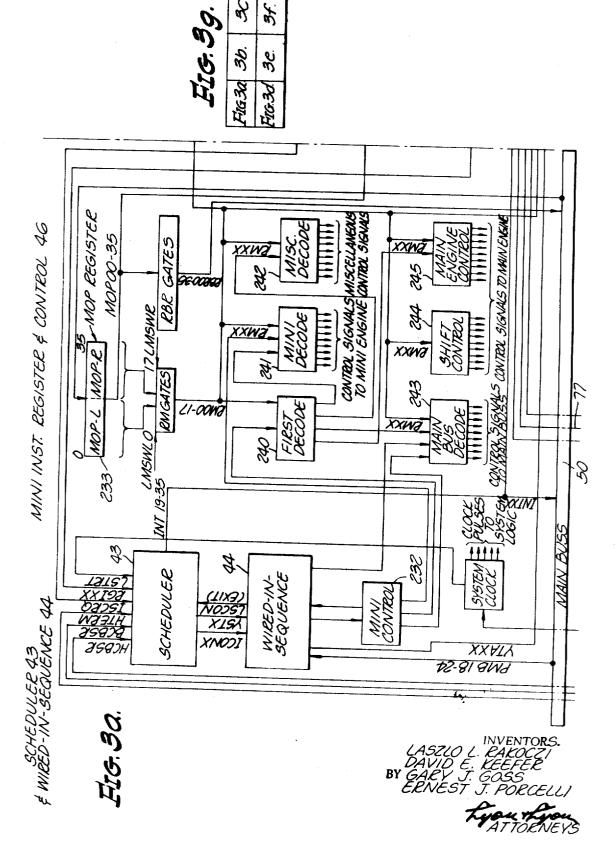

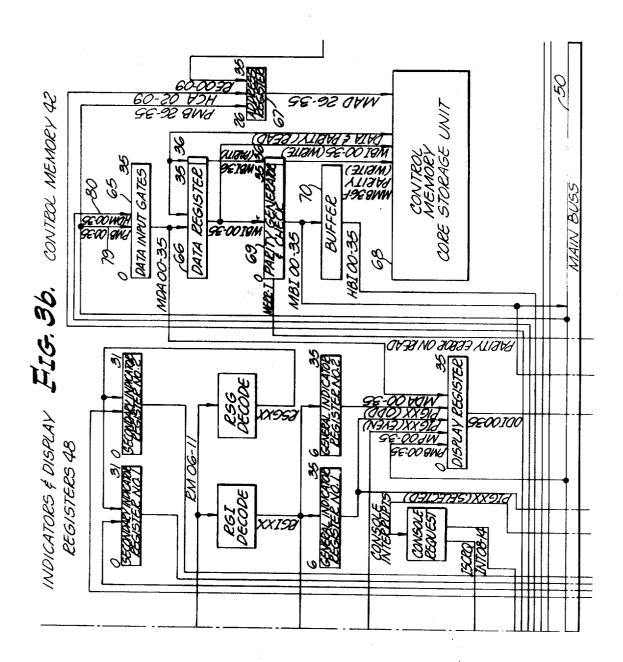

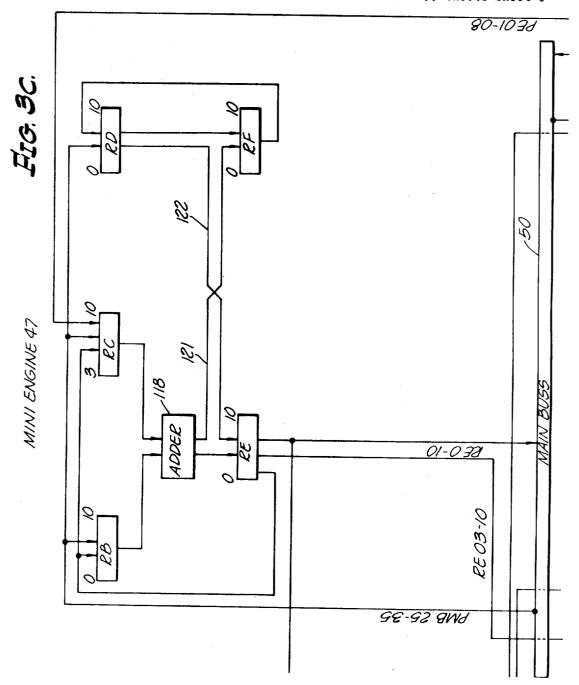

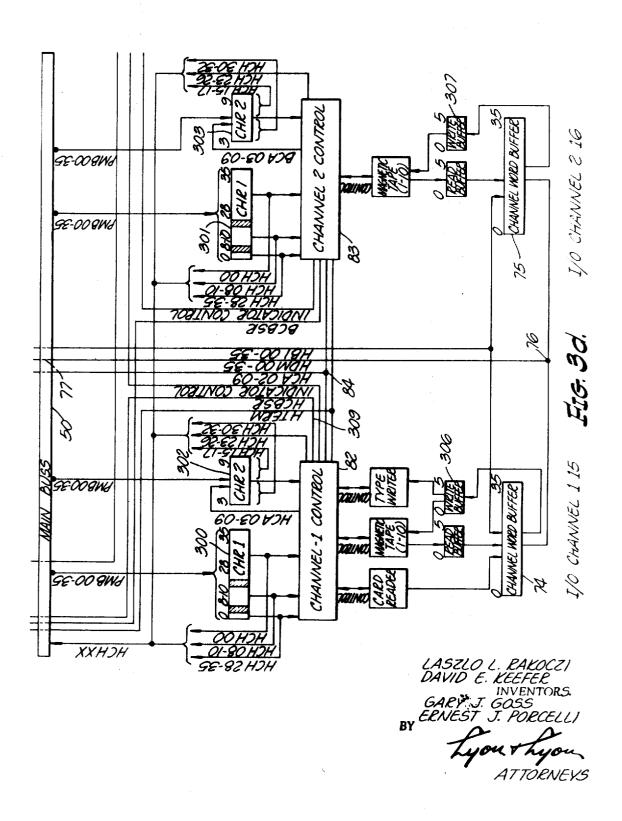

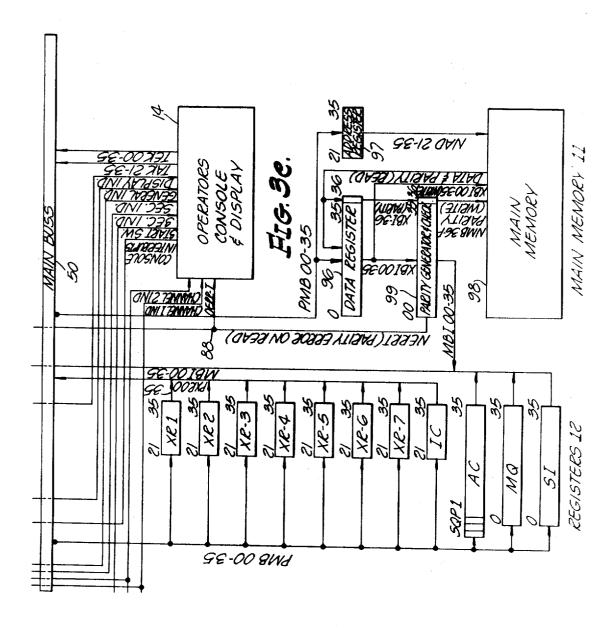

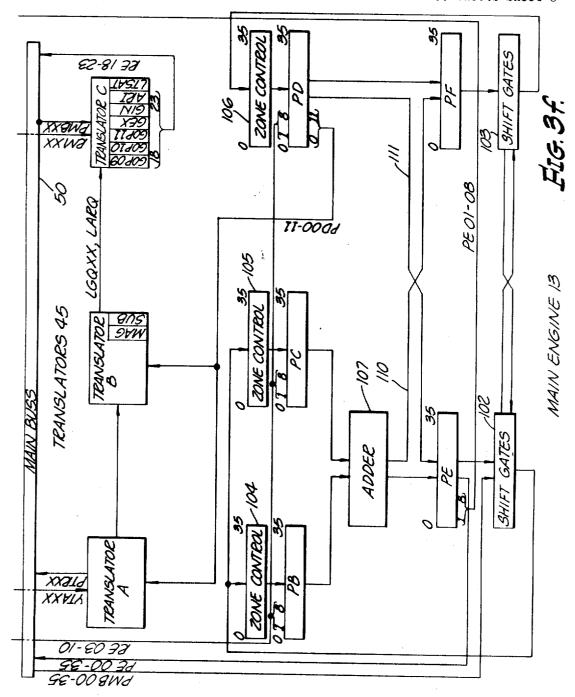

FIG. 2 shows the system of FIG. 1 but illustrates the components of the inner computer in block diagram form; FIGS. 3a-3g are more detailed block diagrams of the

computing system shown in FIGS. 1 and 2;

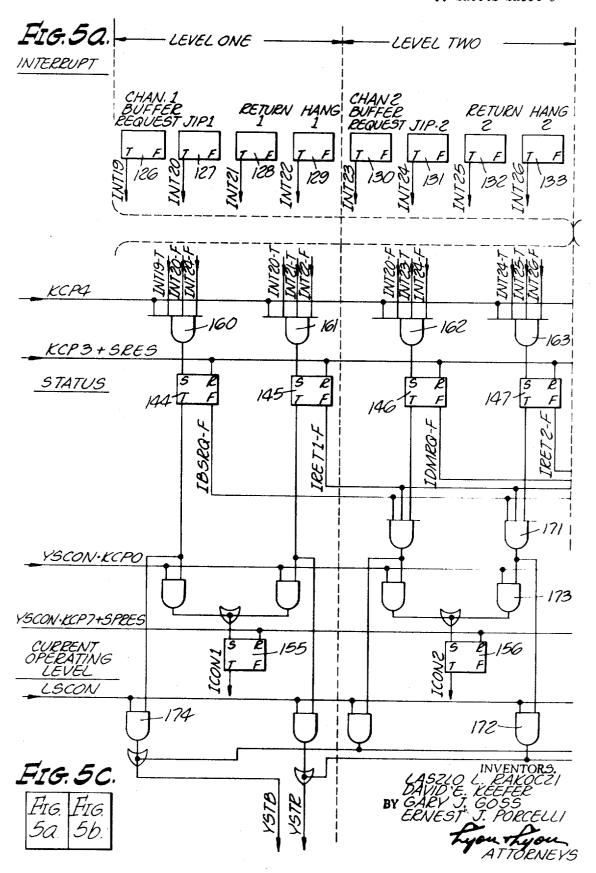

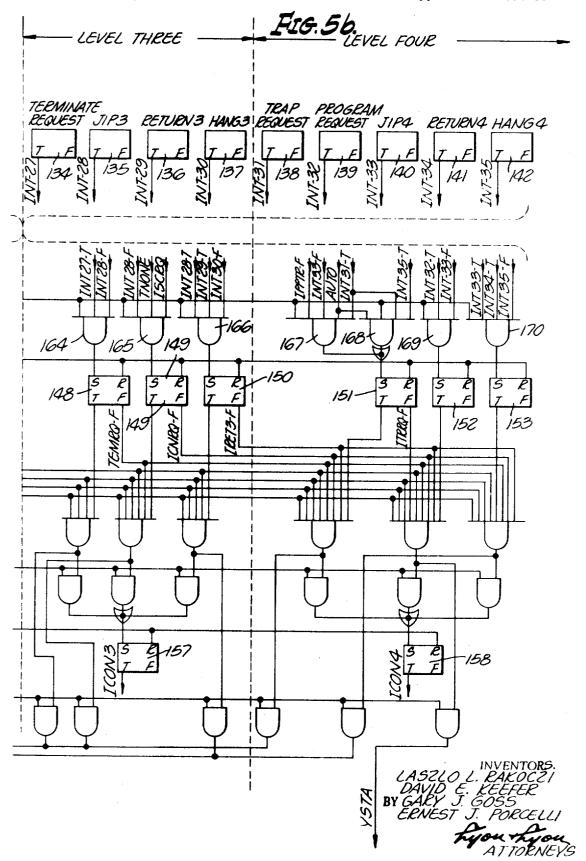

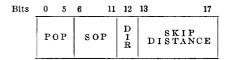

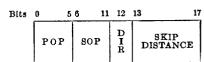

FIG. 4 is a diagram of main engine zone control codes; FIGS. 5a-5c are logic diagrams of a scheduler;

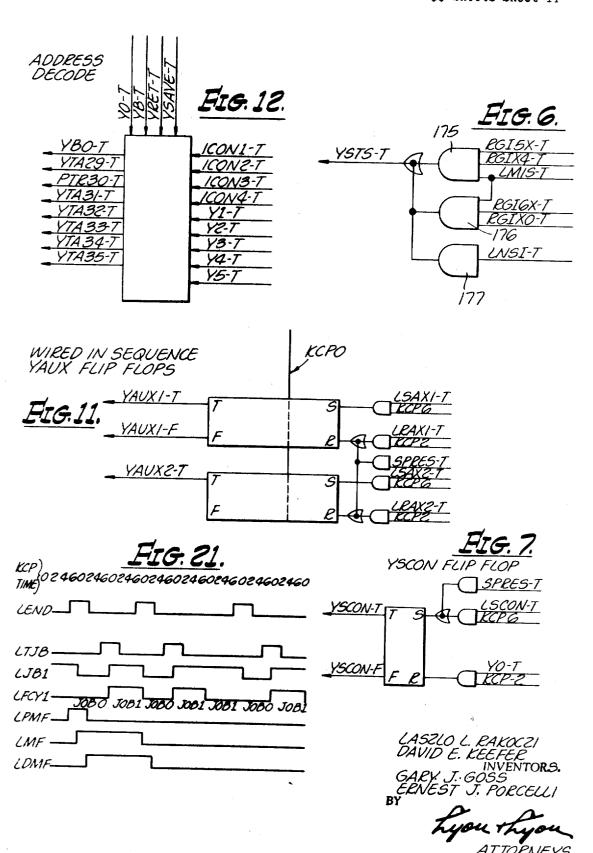

FIGS. 6 and 7 are logic circuits;

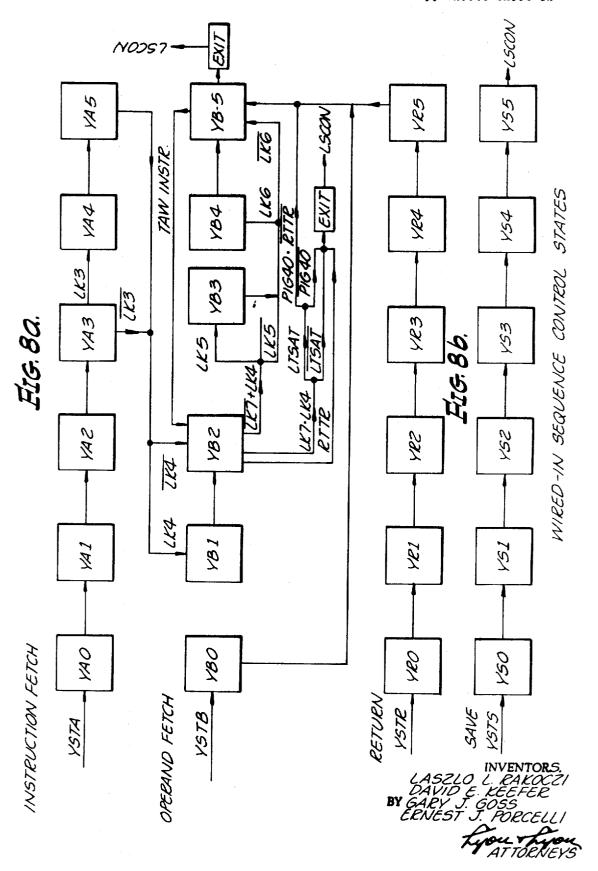

FIGS. 8a and 8b are flow diagrams of wired-in-se-

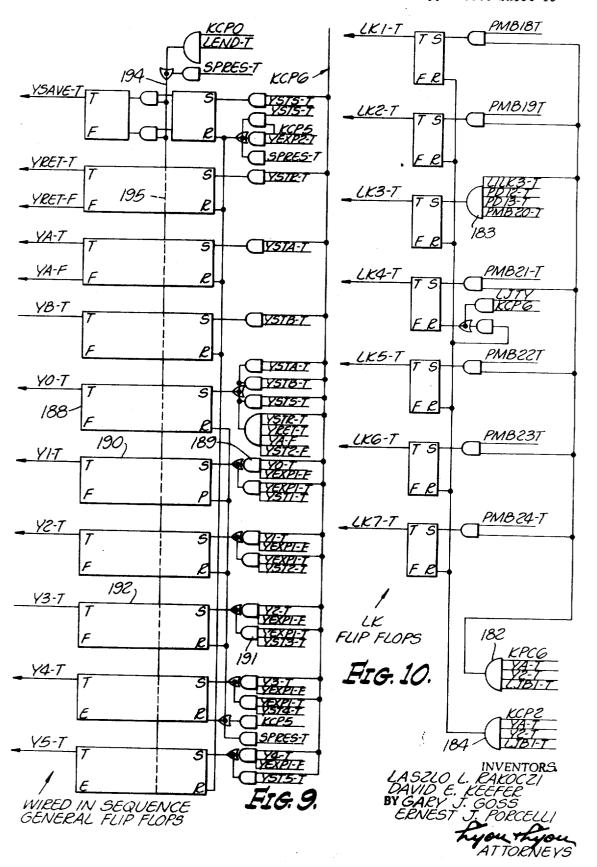

quence control states; FIG. 9 is a logic diagram of flip-flops used in a wiredin-sequence:

FIG. 10 is a logic diagram of LK flip-flops;

FIG. 11 is a logic diagram of wired-in-sequence auxiliary flip-flops:

FIG. 12 is an address decode logic diagram;

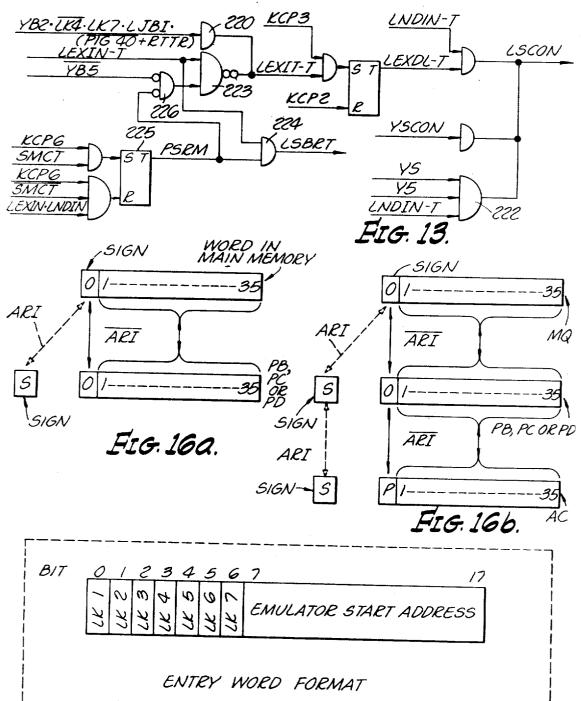

FIG. 13 is an exit conditions logic circuit;

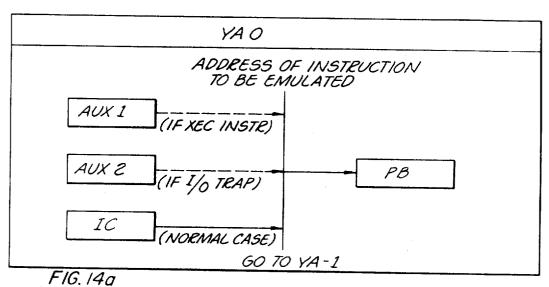

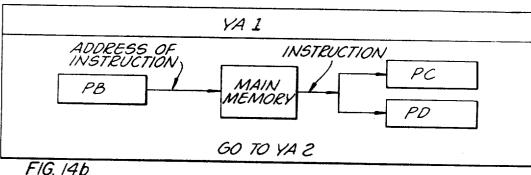

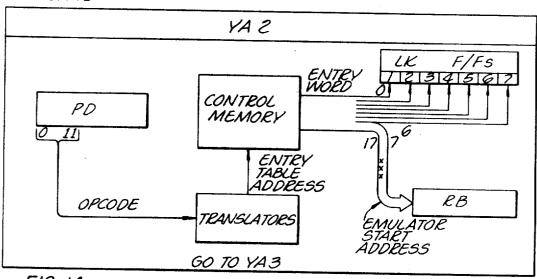

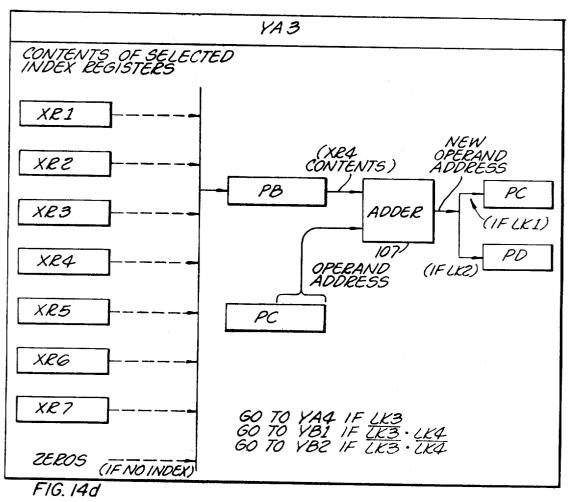

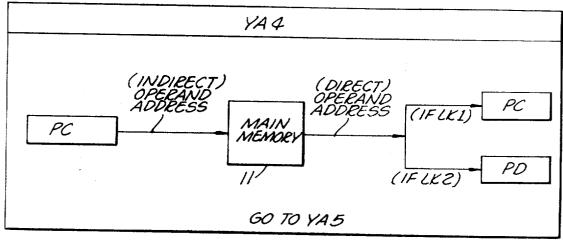

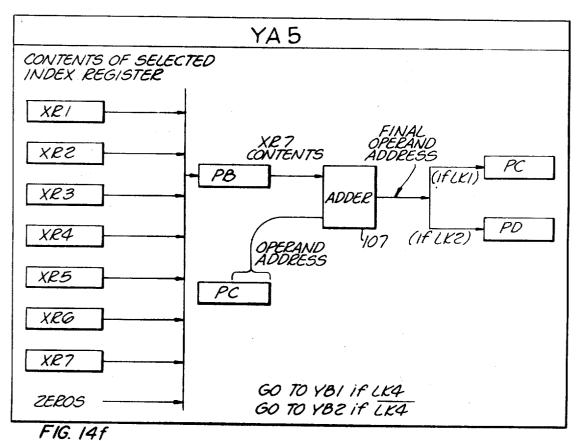

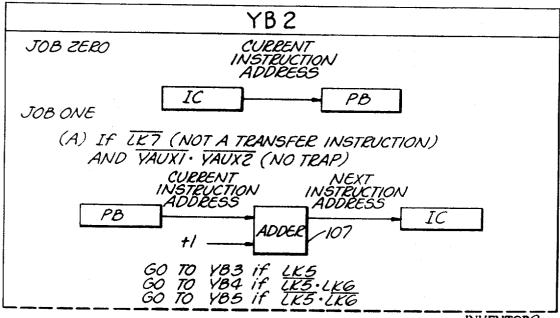

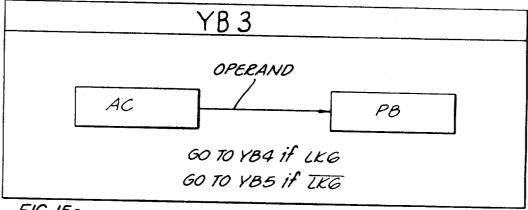

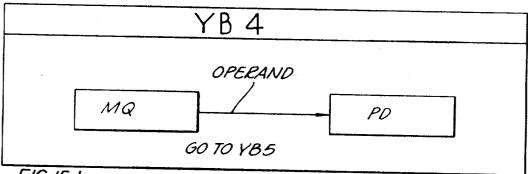

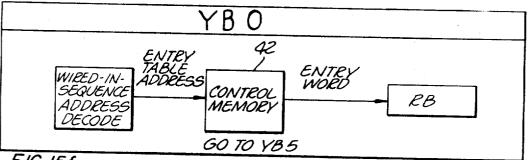

FIGS. 14a through 14f and FIGS. 15a, 15b,  $15b_2$  and 15c through 15f are flow diagrams explaining operations by the wired-in-sequence;

FIGS. 16a through 16b is a sign control flow diagram;

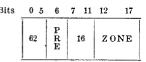

FIG. 16c is a diagram on an entry word format;

FIG. 17 is a logic diagram of a translator A;

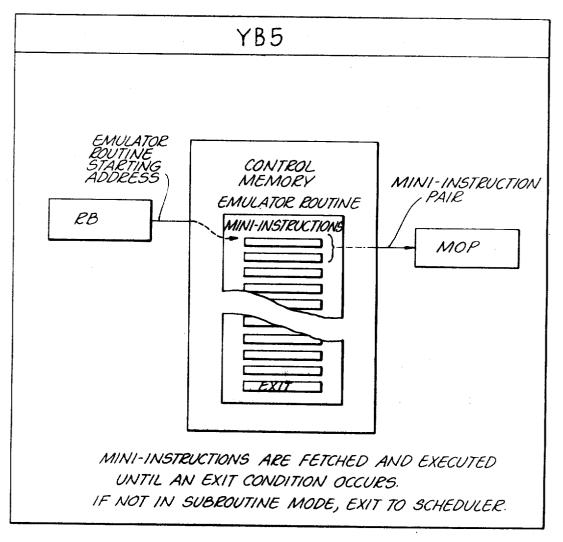

FIG. 18 is a logic diagram of a translator B;

FIGS. 19a-19c are logic diagrams of a translator C;

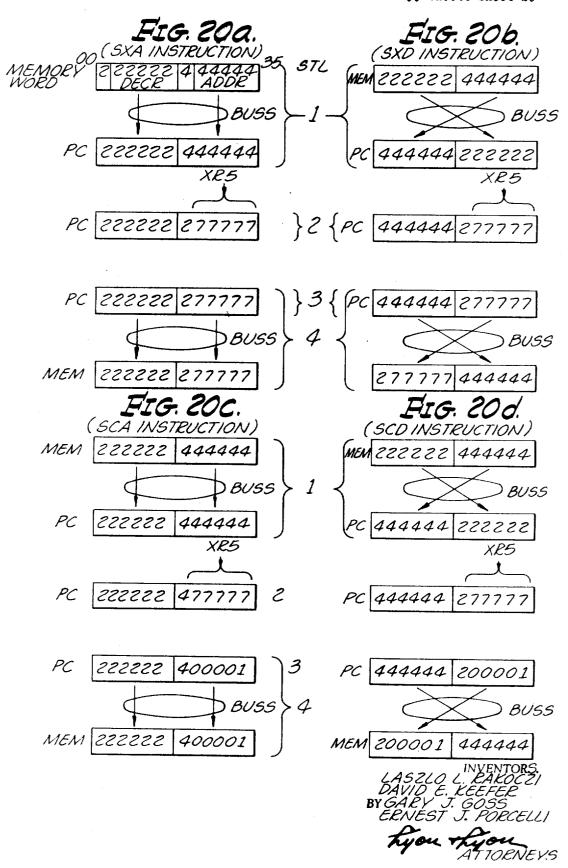

FIGS. 20a through 20d are diagrams illustrating the operations performed in emulating certain instructions; 30

FIG. 21 is a diagram of mini-control timing;

FIG. 22 illustrates the system clock;

FIG. 23 is a clock timing diagram;

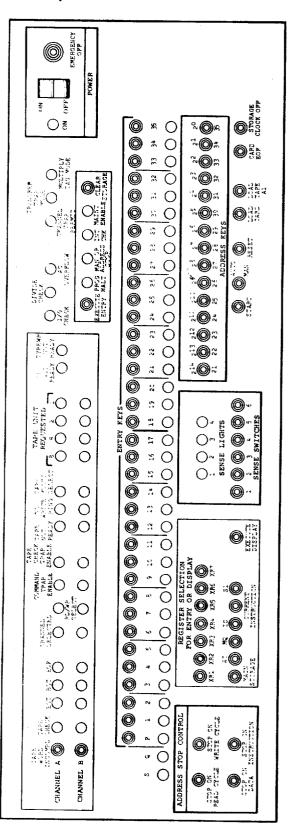

FIG. 24 is a diagram of a console display unit;

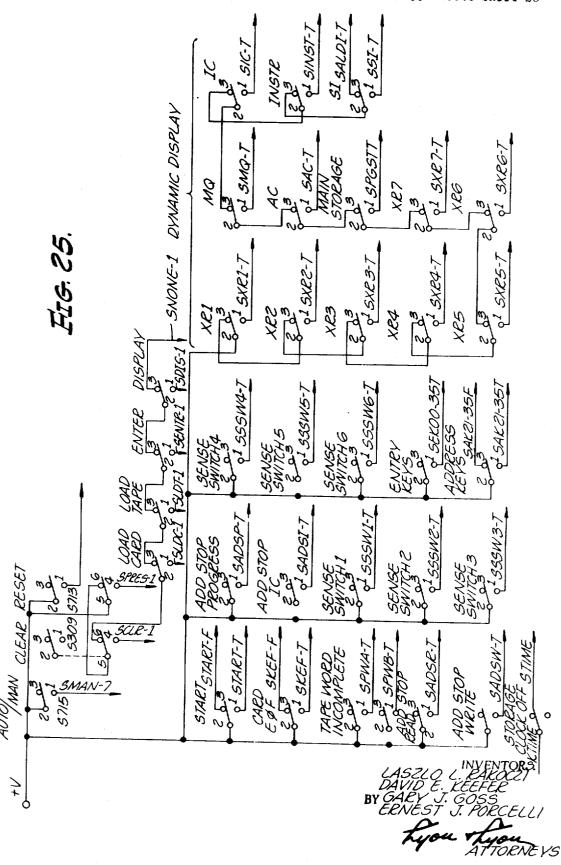

FIG. 25 is a diagram of console switches; and

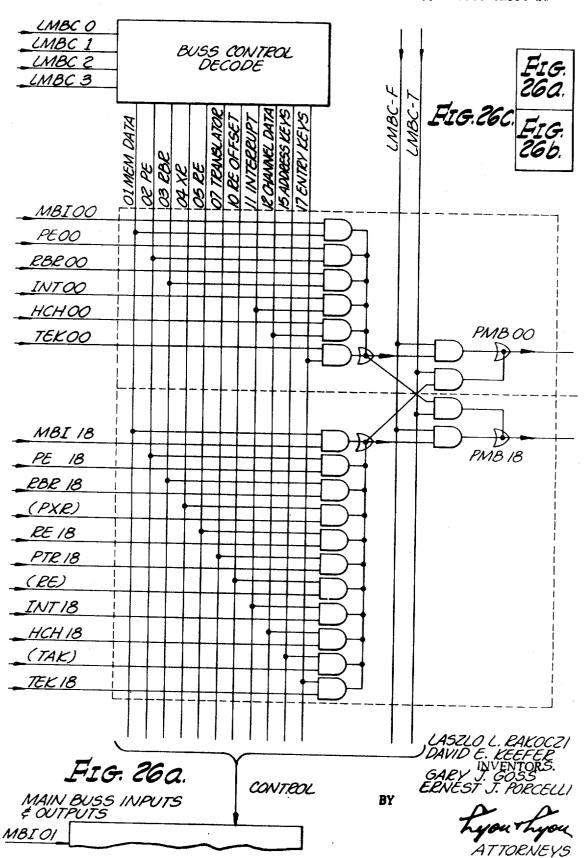

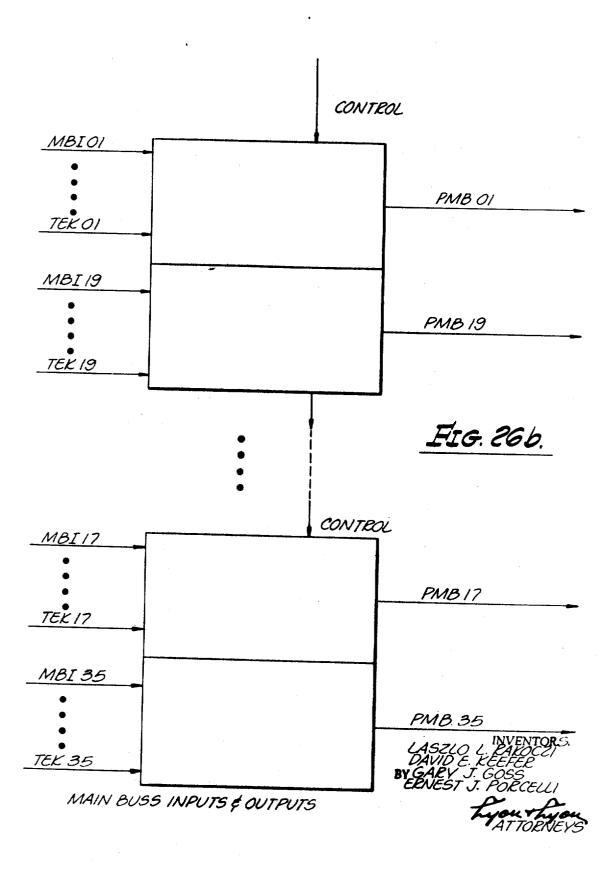

FIGS. 26a, 26b and 26c illustrate the main buss in more

The above and related objectives are achieved in an embodiment of the present invention which is a computing system composed of a number of different and specialized functional stations as well as conventional functional stations which are connected to each other by means of a controlling arrangement such that together they are capable of executing a total computational task. In accordance with one form of the invention some of the functional stations may be considered small specialized computers or data processors.

The broad concept of the present invention may be referred to as a computer-within-a-computer. This concept eliminates the permanent bond between the various functional stations heretofore experienced in conventional computers because of the fixed wiring and logic of the system. With the present invention all functional stations communicate with each other through the inner computer, allowing each functional station to behave in its most natural and economical fashion. The inner computer, having its own control memory, control units, and registers, can be set up to emulate the instruction repertoire and program capacity of new or prior art computers. This multi-lingual capability, implemented by an emulation process allows the use of existing program libraries without reprogramming or hardware modification.

In keeping with the computer-within-a-computer concept, the present invention may be considered to be divided into two parts, namely, the external functional stations, and the inner computer. The external functional stations include a main memory, arithmetic units, and registers, input/output channels, input/output devices, and an operator's console. These stations perform the functions of similar devices on the computers being emulated. The inner computer, including a scheduler, wiredin-sequence, control memory, translators, mini-instruction registers and decoders, indicators and display registers, and mini-engine, takes the place of much of the wiring and control logic in a conventional system. The 75 additional bits for overflow and sign control,

overall computer may be said to contain its own interpreter such that it can process data in the language of other computer systems. The control memory in the inner computer is used to convert the data used by the other computer into terms it can then supply to its own logic. Thus, the inner computer essentially is loaded with a program to interpret the language of the other computer and to set up the logic for processing the data. The computer of the present invention interprets rather than merely translates.

Programs written in the language of the machine being emulated are stored in the main memory. When the program is to be run, the inner computer fetches and instruction from the main memory, and performs the necessary  $_{15}$  indexing and indirect addressing operations by means of an emulator hardware sequence. The instruction is decoded and an emulator routine in the control memory is entered which directs the inner computer through all the steps necessary to execute this particular instruction. The next instruction is then fetched from main memory and the entire process is repeated until the program is completed or terminated. The inner computer thus acts as an interpreter thereby directing the total system to respond as though it were the computer it is intended to model.

#### BRIEF SYSTEMS DESCRIPTION

A brief description of an embodiment of the invention will be given first in order to provide a general understanding of the various functional stations and the manner in which they operate together in executing a program written for another computer. This will be followed by a more detailed description of the system and the emulation process as it is handled by the inner computer, as well as a more detailed description of the functional stations, including various features and unique concepts embodided

A typical configuration of the invention as it is used to emulate a well-known second generation data processing machine is illustrated in FIG. 1 and includes the inner computer 10 with its associated registers and control memory, and external functional stations; namely a main memory 11, high speed registers 12, arithmetic and logical unit 13, operator's console and display unit 14, and two input/output channels 15 and 16 as shown in FIG. 1. One channel 15 typically controls a card reader 17, I/O typewriter 18, and up to ten magnetic tape units 19 through 28, and the other channel 16 typically handles up to ten tape units 29 through 38. A brief description of each of the various units now will be given.

The external functional stations include the main memory 11, registers 12, the arithmetic unit 13, the operator's console and display unit 14, input/output channels 15 and 16, the peripheral units (tape units, card reader and typewriter). The main memory 11 functions as the core storage of the computer being emulated. It is used to store data and instructions which are in the form of a program in the machine language of the computer being emulated. The main memory typically contains 32,768 words consisting of 36 bits plus one parity bit.

The registers 12 are high speed storage elements available to the operator and programmer on the same basis as those in the computer being emulated. The inner computer 10 assigns certain functions to certain of the registers as required to duplicate those available on the computer being emulated. Typical assignments are: Accumulator (AC), 38 bits; Multiplier-Quotient (MQ), 36 bits; Index Registers, (XR1-XR7), 15 bits each; Instruction Counter (IC), 15 bits, and so forth.

The arithmetic and logical functions such as fixed and floating point addition, multiplication, logical AND, OR, 70 and masking operations are performed in the arithmetic unit 13. The unit is called the "main engine," and is also used by the inner computer 10 for internal operations. It contains registers PB, PC, PD, PE, and PF (to be described subsequently) which are 36 bits in length plus

The operator's console 14 is a flexible unit which simulates all the console functions of the computer being emulated. The console contains the keys, switches, and lamps necessary for manual and semiautomatic control and the visual checking of information in the system. Power to the system may be controlled from the console. All memory and register locations can be displayed. An execute entry function permits execution of console-keyed instructions without disturbing main memory. Address stop control provides several optional stop modes.

The input/output channels 15 and 16 control the quantity and destination of all data transmitted between the inner computer 10 and the peripheral units (e.g., input/ output units). The channels may be considered small specialized data processors since they perform their func- 15 tions independently of the inner computer and each other.

The peripheral units on a typical system are magnetic tape units 19 through 28 and 29 through 38, a card reader 17, and an I/O typewriter 18. The tape units are fully compatible with the tape units of the computer being 20 emulated. The card reader and typewriter formats, where they differ from that of the computer being emulated are converted within the inner computer 10 to a compatible format by means of a combination of hardware and software emulation techniques.

The inner computer (see FIG. 2) includes a control memory 42, a scheduler 43, a wired-in-sequence 44, translators 45, mini-instruction register and decoders 46, a miniengine 47, and indicators and display registers 48. The control memory 42 contains, for example, 1,024 words con- 30 sisting of 36 data bits and one parity bit. The control memory is used primarily to store emulator routines, to store data and constants used by the routine and the hardware while executing emulator instructions, and as a transient input/output area for data transmitted between main 35 memory 11 and the input/output channels 15 and 16. The control memory 42 and the main memory 11 are completely independent and fully overlapped, with the control memory 42 functioning significantly faster than the main memory, e.g., the former has a cycle time of two micro- 40 seconds and the latter has a cycle time of four microseconds.

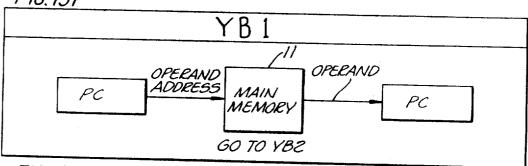

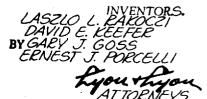

Since certain processes in the external functional stations may be taking place simultaneously, it is necessary for the inner computer 10 to take action promptly when some device needs attention. This function is performed by the scheduler 43, which receives requests for action from the input/output channels 15 and 16, the operator's console 14, and from circuitry which indicates that a program in main memory 11 is in progress. The scheduler 43 passes control to certain entry points in the wiredin-sequence 44 depending on the type of priority of the request honored. The wired-in-sequence 44 contains a number of wired subroutines or sequences, for example four, consisting of six steps each. These sequences, for example, are (see FIG. 8) YA (instruction fetch), YB (operand fetch), YS (save), and YR (restore). The scheduler 43 passes control to state zero of one of these sequences depending upon the type of request which has been honored. From there, the sequence is stepped from one state to another, although not necessatily in a sequential manner. Steps may be skipped within a sequence and control may be passed from one sequence to another. The purpose of the YA sequence is to fetch the instruction to be emulated from main memory 11, decode it, 65 and perform indexing and indirect address operations. The primary purpose of the YB sequence is to update an instruction counter (IC) and to fetch the operand or operands required by the instruction being emulated. The YS sequence is used to save the contents of certain 70 registers by storing them in predetermined locations in the control memory 42 when an emulator interrupt or hang conditions occurs. The function of the YR sequence is to restore the registers which are saved during the save sequence.

The translators 45 include three translators (A, B, and C). The function of the translators is to decode the instruction being emulated and to determine (by means of an entry table in the control memory) the starting address of the emulator routine necessary to complete the emulation and to set certain general control flip-flops (in

translator C) in order to pass on specific information about instruction characteristics to the emulator rou-

The inner computer 10 has stored therein a specialized, hardware-oriented, machine language which is designed for interpretive work. This is the language in which emulator routines are written. An individual instruction in this internal language typically is 18 bits long and is called a mini-instruction. When an emulator routine is being executed, mini-instructions are brought from the control memory 42 to the mini-instruction register 46 from whence the bit configuration is passed to the miniinstruction decoders. The decoders determine the operation or operations to be performed and accordingly send control signals to the various units of the overall system.

The mini-engine 47 is similar in construction to that of the main engine or arithmetic unit 13 except that no shifting operations (and hence multiply, divide, and floating point operations) are performed. The mini-engine 47 controls shifting in the main engine 13, and contains several registers RB (mini-instruction counter), RC (shift counter), RD (save counter for subroutine mode), RE, and RF, all of which typically are eleven bits in length, except RC which is eight bits.

The indicators and display registers 48 are sets of flipflops and high speed storage elements which are used to store hardware and emulator program status, the occurrence of certain events within the system and the like. The registers in this unit are a display register (36 bits), general indicators 1 and 2 (32 bits each) and secondary indicators 1 and 2 (32 bits each). Most of the bits in these registers may be individually set, reset, or both by emulator instructions, and many are connected to lamps on the operator's console 14.

Before turning to a more extensive discussion of an exemplary embodiment of a computer according to the concepts of the present invention, a number of the principal concepts or features thereof will first be outlined. The inner computer is switched to serve the various facilities of the emulated computer, such as, instruction execution, I/O initiate-terminate, real time clock, console functions, and I/O data flow. This switching is accomplished by the scheduler which has been briefly described above. The utilization of a switchable inner computer to serve the various facilities of the system in a flexible manner by means of emulator routines permits a computer according to the present invention to emulate a number of different computer systems. The scheduler serves to schedule each task and to service the various facilities, and this is accomplished through the emulator routines. For example, to perform a particular task the scheduler may transfer control to the wiredin-sequence which controls, for example, translators, control memory and other functional units, and emulations requiring actions by means of an emulator program which interprets the instruction of a computer being emulated. Eventually, control is returned to the sched-

In order to provide an efficient system and enable the control memory of the inner computer to be kept within economical limits, a single emulator routine may be utilized in many different types of emulation procedures by allowing the return at the end of the routine (exit point) either to the scheduler or to another emulator routine. In other words, although control is normally returned to the scheduler after execution of an emulator routine, the control need not be returned to the scheduler, but by means of a subroutine mode another routine may be first 75 executed.

Machine-instruction decoding may be accomplished in a flexible and changeable manner by means of a translator and an entry table in the control memory. Additionally, machine-instruction fetch, indexing and indirect addressing also may be controlled by the wired-in-sequence. These aspects provide flexibility in the emulator program memory allocation and facilitate changing emulator routines. As an example, the translator may point to the control memory where the entry table is stored which in turn points to a routine in the control memory. The 10 entry table includes an address along with modifier bits, which are used to prime an emulator routine contained in the wired-in-sequence to vary the same.

Of particular significance is the emulation of the operating environment of various computers by a single com- 15 puter. In order to accomplish this, the console switches are executed in an interpretive mode. The console switches are connected to the inner computer and their function is controlled through emulator routines. The switches thus are not hard-wired to specific functional units of the sys- 20

tem as with conventional computers.

In order to eliminate the need for many time consuming jump emulator instructions (also referred to as ministeps) and to permit a higher speed straight line coding, as well as to provide an economical system, a single 25 emulator routine may be utilized for emulating multiple machine instructions. This type of operation is accomplished by control flip-flops, which will be discussed in greater detail subsequently, under the control of a translator. As an example, a number of instructions being emu- 30 lated have common and uncommon portions. Flip-flops are used to store the nature of the uncommon portions, and thereby enables either instruction to be executed by sensing the state of these flip-flops.

The emulator programs can be loaded and overlayed 35 in order to permit a computer according to the present invention to emulate multiple machine languages in an economical manner. This is accomplished through utilization of the control memory providing both control read and write capabilities. This memory can be loaded from 40 external devices, such as card reader or magnetic tape units. This approach, for example, enables the present system to be quickly changed (within a few minutes) so that it can emulate different computers. Since this memory has a write capability, storage areas thereof can be used for storing intermediate results generated by emulator routines, and may be used for input/output buffer purposes.

In some applications, it is important to permit the system to work on any subfield or a memory word without 50 disturbing the remaining part of the word. This approach allows machine-language independency to be accomplished through emulation of machines with fixed words as well as machines with variable words. The same is accomplished through "zone" functions of the various arithmetic unit oriented mini-steps. For example, it may be desired to add a one to three bit field of one word with a similar length field of another word to emulate a particular machine.

Execution of the emulation process may be sped up by 60 providing self-repeat capabilities for certain multicycle mini-steps. Control of the repetition is accomplished by the mini-engine. For example, the main engine may operate under control of the mini-engine to perform variable length add-shift and subtract-shift cycles. In this manner operations can be repeated without returning control to the control memory.

The specific manner in which the various principal concepts and features discussed above are made possible in a computer according to the present invention will become 70 more apparent as the detailed discussion of the overall system progresses. The components of the system and their functions now will be considered in more detail with particular reference to FIG. 3 as well as the other more detailed figures of subsystems of the computer.

8 THE INNER COMPUTER

Turning now to the inner computer 10 in more detail, this unit has the general capabilities of typical stored program computers, but has a specialized hardware-oriented machine-language designed for interpretive operations. Basically, this unit schedules and controls the various functional stations of the system according to an emulator program comprising a number of mini-instructions stored in the control memory 42. A routine is made up of emulator, or mini, instructions, and these instructions include one or more emulator, or mini, steps. As discussed before, the main functional components of the inner computer are the scheduler 43, wired-in-sequence 44, control memory 42, translators 45, mini-instruction registers and decoders 46, mini-engine 47, and the indicators and display registers 48. The main engine 47, also referred to as the arithmetic unit, has been shown as a portion of the outer computer, but this engine operates extensively in conjunction with the inner computer and may also be regarded as a part thereof. The components of the inner computer are shown within the dotted line in FIG. 2. The principal communication paths between functional units also are illustrated, and these communicate through a main buss 50 which includes gates for appropriately gating data and signals between units. Such busses are well-known to those skilled in the art, and a buss is used as shown rather than complicating the system and drawings with each connection between the various stations.

Before proceeding with an explanation of the units of the inner computer 10, it may be desirable to discuss further the emulator process. In order to emulate a new or prior art computer, an emulator is first loaded into the inner computer 10. Briefly, this is accomplished by pressing a switch which causes a loader program to be read into the control memory, for example, from a card reader or tape unit, which program in turn causes all the necessary emulator routines and entry tables to be loaded into control memory from said card reader or tape unit. The emulator "system" consists of sets of programs or routines which correspond to families of machine-language instructions of the computer to be emulated. After the emulator system is loaded, control is passed to the scheduler at which time the computer of the present invention for all practical purposes acts just like the computer it is intended to model, i.e., the complete set of machine language instructions, and the input, output, and console

functions thereof are available.

For each instruction in the program (which is loaded in main memory) of the machine being emulated, the inner computer 10 executes a routine or group of routines which are made up of sequences of mini-steps or mini-instructions. Similarly, for each input/output operation and each console function to be performed, the inner computer 10 executes still another set of routines. Most of these routines are stored in the inner computer's control memory 42, but for the sake of speed some of these which are used most frequently are "stored" or implemented into a portion of the logic called the wired-in-sequence 44. The entire collection of routines present in the inner computer 10 at any one time is called an emulator system. It is the emulator system which tells the inner computer how to interpret the machine-language instructions of some new or prior art computer. It follows that in order to emulate a different computer it is only necessary to change the emulator system which, for the most part, consists of a program resident in the control memory 42.

In a typical sequence of operations, the scheduler 43 passes control to the wired-in-sequence 44 which in turn causes execution of one or more mini-instructions which are taken from the control memory 42 and executed from the mini-instruction register 46. When the execution is completed, control is returned to the scheduler 43.

When a program request is honored by the scheduler 43, 75 control is passed to a YA phase (to be discussed subse-

Ç

quently) of the wired-in-sequence 44. At this time, an instruction from the main memory 11 is brought to the main engine 13. The address of the next instruction to be emulated is kept in the instruction counter register. The operation code portion of the instruction is sent to the translators 45 which generate an address pointing to a word in an entry table in the control memory 42. This word, which is the starting address of the emulator routine needed to complete the emulation, is sent from the control memory 42 to the mini-engine 47. The address portion of the 10instruction is then modified if necessary by index registers and indirect addressing. A YB phase of the wired-insequence is then entered where the operands, if any, are brought from main memory 11 or the registers 12 to the main engine 13. An emulator program is then executed 15 starting at the control memory address specified by the word just loaded into the mini-engine 47. When the emulator program is completed, an exit is generated which returns control to the scheduler 43. The process is repeated again when the scheduler 43 honors a program request.

The above explanation is somewhat simplified, but provides a general understanding of the manner in which the inner computer 10 interprets an instruction. It should be noted that not all instructions being emulated require the same wired-in-sequence operations, and a few instructions 25 require no emulator routine for their execution. In addition, operations such as input/output and console functions which are not directly connected with the emulation of a specific instruction use a different portion of the wired-in-sequence and a different set of emulator routines, but 30 the process is similar to that described above.

Turning now to a consideration of the manner in which the inner computer intercommunicates and communicates with the outer computer, the main buss 50 provides a common data path through the machine. The main buss can 35 accept data from a majority (for example eleven) of the inner and outer units, and gate data into the output lines (PMB00 through PMB35). Main buss decode control signals (LMB0 through LMB3) determine which of the eleven inputs are gated onto the output lines. The code for 40 these control signals and a description of each of the inputs will be discussed subsequently. Each device or functional station that is connected to the main buss outputs contain its own gates so that the data from the main buss will enter a particular functional station when an appropriate control signal is enabled.

The main buss also can perform a half-exchange, in which the data on the main buss is divided in half and the halves exchanged, i.e., output bits 00 through 17 are exchanged with output bits 18 through 35. When a control signal LMBC is false, the main buss output is normal and when this control signal is true a half exchange occurs.

The main buss is used in the exemplary embodiment of the invention to simplify the logic, and used in the description and illustration in order to facilitate understanding of the present invention. Improved performance can be realized by making direct connections between the various functional units but this increases the complexity of the control logic. In a version of the invention, for example, greater speed can be realized by making a direct connection between the registers 12 and the main engine 13, rather than using the main buss 50 and its gates to transfer the data between these two functional stations.

The control memory 42 contains, for example, 1024 words consisting of 36 data bits and one parity bit. The control memory is used primarily to store emulator routines, to store data and constants used by the emulator system and the hardware while executing emulator instructions, and as a transient input/output area for data transmitted between the main memory 11 and input/output channels 15 and 16. The control memory 42 and the main memory 11 are independent and fully overlapped, with the control memory functioning significantly faster than the main memory as noted previously. The control memory is protected during system operation, i.e., neither the opera-

10

tor nor the program being emulated can destroy the data in the control memory.

Emulator instructions may be only 18 bits long and stored two per control memory word. As far as the emulator instructors are concerned, the control memory 42 contains 2,048 18-bit mini-locations. These mimi-locations have mini-addresses numbered from 0000 through 3777 in octal notation. Certain portions of the control memory 42 are reserved for specific purposes, as set forth below:

```

Mimi-Address (octal)

0000-0077 ____ Temporary Storage & Soft Registers.

0100-0117 ___ Register Save Area, Level 1.

0120-0137 ___ Register Save Area, Level 2.

0140-0157 ___ Register Save Area, Level 3.

0160-0177 ___ Register Save Area, Level 4.

0200-0277 ___ Entry Table.

0300-0377 ___ Duplicate Entry Table.

0400-0477 ___ I/O Buffer, Channel A.

0500-0577 ___ I/O Buffer, Channel B.

0600-3777 ___ Emulator Routines.

```

The control memory 42 as seen in FIG. 3b includes data input gates 65, data and address registers 66 and 67, a core storage unit 68, a parity generator and check circuit 69 and a buffer 70. The memory 42 receives data from two sources: (1) the main buss 50 (lines PMB00-35); and (2) the I/O channels 15 and 16 (lines HDM00-35). The outputs of the channel word buffers 74 and 75 (FIG. 3d) in I/O channels 1 and 2 are ORed together as indicated at 76 before they appear at control memory data input gates 65. The dashed line 77 in line HDM00-35 from the buffers 74 and 75 extending across the main buss 50 indicates that the line bypasses the buss. In reference to the nomenclature used in FIG. 3, which illustrates an exemplary embodiment in detail, it should be noted that in order to prevent cluttering up the drawings with a maze of lines which would tend to obscure the system and interconnections thereof, single lines with alphanumeric relations are shown. These notations indicate the data and signal flow. For example, two lines 79 and 80 into the control memory 42 in FIG. 3b are shown as inputs to data input gates 65 and are labelled respectively "PMB00-35" and "HDM00-35", and thereby indicate thirty six inputs to the gates 65 respectively from the main buss 50 and from the I/O channels 15 and 16. These types of notations are used throughout the specification and drawings rather than reference numerals alone in order to more clearly designate the interconnections of the various units and the data and signal flow therebetween. Although a single line is used between components of the system, it will be understood that multiple lines are used (e.g., PMB00-35) to transfer multiple bits. The various inputs and outputs of the main buss 50 will be covered in greater detail subsequently along with a more detailed discussion of the main buss.

The address of the memory area in the storage unit 68 to be written into or read from comes to the control memory address register 67 from three sources: (1) the mini-engine 47 (line RE00-09) (FIG. 3c); (2) the main buss 50 (lines PMB26-35); and (3) the I/O channels 15 and 16 (lines HCA02-09). The outputs of the channel controls 82 and 83 of the I/O channels 1 and 2 (FIG. 3d) are ORed together as indicated at 84 before appearing at the input of the control memory address register 67. These channels will be discussed subsequently. Each of the controls 82 and 83 includes an address counter for selecting the desired words.

channels 15 and 16. The control memory 42 and the main memory 11 are independent and fully overlapped, with the control memory functioning significantly faster than the main memory as noted previously. The control memory is protected during system operation, i.e., neither the operation of the above sources is transmitted through the data input gate 65 to the data register 66. The data goes to the parity generator and check circuit 69 and on a line 86 to the core storage unit 68. The circuit 69 generates a parity bit

11

(MMB36-F) and passes this to the unit 68. Odd parity is used.

During a read operation data is passed through the line 86 to the register 66, with the parity bit going to bit position 36. This data is transferred to the parity circuit 69 where parity is checked. The data (without the parity bit) is passed (lines MBI00-35) from the circuit 69 to the main buss 50, and through the buffer 70 (lines HBI00-35) as a separate data path to the channel word buffers 74 and 75 of the respective I/O channels 15 and 16. An error signal (MERR-T) is generated by the parity circuit 69 if an even number of bits are read out. This error signal is ORed at 88 (FIG. 3e) with a similar signal (NERR-T) from the main memory 11 and supplied (OERR-T) to the console 14.

Turning briefly to the main memory 11, it will be seen from FIG. 3e that the data flow to and from the main memory is similar to that of control memory 42. The main memory 11 includes similar data and address registers 96 and 97 respectively, a core storage unit 98 and 20 a parity generator and check circuit 99. No data input gates (like gates 65 in the control memory 42) are used; otherwise, data flow is the same as in the control mem-

ory.

Turning for the moment to the main engine 13 (FIG. 25 3f), although it is shown as part of the outer computer, it also performs functions for the inner computer. The main engine performs all required storage and data manipulations when emulating an instruction taken from the main memory 11. This engine may be controlled in a 30 conventional manner to perform single and multiple precision, fixed and floating point arithmetic, and shift operations. The main engine consists of five registers (PB, PC PD, PE, PF), an adder, zone control circuitry, and shift circuitry as seen in FIG. 3f. The registers are 36 bits 35 long, with additional bits for overflow and sign control. The PE and PF registers are used strictly as data paths or a temporary storage. Data sent from the main engine 11 to other parts of the system passes through the PE register to the main buss 50. The input (lines PMB00-35) to the main engine is through shift gates 102. The shift gates 102 and shift gates 103 are interconnected so that information may be transmitted from the main engine input PE register or PF register to the PB, PC, or PD registers. At any one time, a number may be shifted 1, 2, 3, or 4 positions either right or left or transferred straight through without shifting by the shift gates 88 and 89. Zone controls 104 through 106 perform operations on the data as it is transferred to the PB, PC, or PD registers. There are 32 different zone control codes which 50 will be discussed subsequently. The adder 107 allows a large number of different arithmetic and logical operations to be performed on data residing in the PB and PC registers.

The principal function of the main engine is to store 55 data, but it also contains the adder and shift control circuits, and performs arithmetic and logical manipulations of 36 bit binary words. The main engine registers may be called the working registers of the system. The main engine is used during operation of the wired-in-sequence 44 and during execution of emulator routines to perform all the required storage and data manipulations when emulating another computer's instruction. As noted before, inputs to the main engine are from the main buss 50. Outputs from the main engine go to the main buss 50 and 65 to the translators 45 to begin the emulation.

Data flow during a straight transfer is from the adder 107 to the PE register and from the PD register to the PF register. During a cross transfer, which is provided by lines 110 and 111, the data flow is from the adder 107 70 to the PF register and from the PD register to the PE register. This enables the contents of the PD register to be used as an operand for the adder 107 by first passing through the PE register and then being loaded into

12

the adder 107 to be loaded into the PD register via the PF register.

The adder 107 may do more than just add, it allows all logical combinations of data in the PB or PC registers. For example, control signals may be supplied to the adder to provide data combinations called PXBN, PXBC, PXNC, and PXNN, the meanings of which are set forth helow:

PXBC=exclusive OR, PB and PC; PXBN=exclusive OR, PB and  $\overline{PC}$ ; PXNC=exclusive OR, PC and  $\overline{PB}$ ; PXNN=exclusive OR,  $\overline{PC}$  and  $\overline{PB}$ .

Thus, for any data bit combinations, the adder outputs are as shown below:

| INPUT     |           | OUTPUT |      |      |      |

|-----------|-----------|--------|------|------|------|

| PB<br>BIT | PC<br>BIT | PXBC   | PXBN | PXNC | PXNN |

| 0         | 0         | 0      | 0    | 0    | 1    |

| 0         | 1         | 0      | 0    | 1    | 0    |

| 1         | 1         | 1      | Ô    | ŏ    | 0    |

The shift gates 102 and 103 are coupled with the outputs of the PE and PF registers, and each is in two stages, shift three bits and shift one bit. At each state, control signals are used to specify shift left, shift right or no shift. Control comes from the mini-instruction registers and control 46 which will be described subsequently. The RC register on the mini-engine 47 (FIG. 3c) holds the shift count which is monitored during shift operations. On any one data pass through the shift gates, nine combinations are possible in one clock cycle as follows: left four, left three, left two, left one, none, right one, right two, right three, or right four. More shifts can be provided over a number of clock cycles. Note that the shift gates are the entry point for data from the main buss entering the main engine. In entry, no shift occurs as data is gated from main buss 50 to the PB, PC or PD registers.

The zone controls 104 through 106 allow the thirty six bit PB, PC and PD registers to perform arithmetic, logical and masking operations. For example, a six bit add operation may be performed by zoning off unnecessary or unwanted bits; e.g., the desired six bits of words stored in the PB or PC registers may be added together in the adder 107 while ignoring the remaining bits of these words. A carry flip-flop (not shown) preferably is provided to receive any carry or overflow from the most significant bit of the specified zone in a conventional manner for use as desired (e.g., to enable the system to test for overflow). The blocked in portions of FIG. 4 show the allowable zones (of several bits) for main engine operations. The octal code given in the left hand column is incorporated as a part of certain mini-instructions to specify which zone is to be used. In loading the registers PB, PC and PD, zone control can be used to load only desired bits of a thirty six bit word. For example, the instruction "502030" means to take the contents of the PD register and load them into the PB register, but load only bits 0, 1 and 2 (discarding bits 3-35). The "50" in the instruction means the PB register is the destination of the data, the "20" means the PD register is the source. and the "30" means to load only the first three bits of the word in the PB register (as indicated in FIG. 4 at 115). Another instruction, for example, "533627" means to add bits 3-17 of the PB register to bits 3-17 of the PC register and store the results in the PD register. The "53" in the intsruction means to store the result in the PD register, the "36" means to add PB to PC, and the "27" means to operate on only bits 3-17 of the affected registers (as seen in FIG. 4 at 116). The entire contents of the PB either the PB or PC registers. It also allows results from 75 and PC registers are brought into the adder in this case,

but the zone control 106 only allows bits 3-17 of the result to be stored in the PD register. By substituting other digits (i.e., 24) for the middle two digits of the above instruction, the logical AND of the PB and PC registers can be performed on the specified zone. More examples will be apparent later when specific "primary operation codes" (POP) and "secondary operation codes" (SOP) are discussed.

The mini-engine 47 (FIG. 3c) is similar to the main engine 13 except that no shifting or zoning operations are performed. The registers employed are RB, RC, RD, RE, and RF as seen in FIG. 3c. These registers are, for example, eleven bits in length, except the RC register which is eight bits in length. The output (lines RE00-10) of the mini-engine 47 is through the RE register. Inputs (lines PMB25-35) from the inner computer go directly to the RB, RC or RD registers from the main buss without going through shift circuits as is the case with the main engine 13. The adder 118 functions in a manner similar to the adder in the main engine 13.

The functions of the various mini-engine registers will be explained in more detail in conjunction with other sections of the system. The RB register functions as the mini-instruction counter, and may be loaded from the buss or from the RE register. The contents of the RB register 25 specify the mini-address of a mini-instruction located in the control memory 42. The most significant ten bits (bits 0-9) indicate the address of a pair of mini-instructions residing in the control memory, and the least significant bit (bit 10) specifies which instruction of the pair is to 30 be executed.

The register RC is used as a shift counter to control shifting in the main engine 13, i.e., it counts the number of bits data is to be shifted in the main engine. The RC register also serves to hold a skip distance when a skip 35 instruction is executed. The RC register is decremented during shifting operations which are discussed below. No shifting of data takes place within the mini-engine. A shifting operation (including multiply and divide operations) may be performed on the data contained in one 40 or more of the main engine PB, PC or PD registers, i.e., the contents of PB, PC, or PD may be shifted individually, or PB with PD, or PC with PD. Shifting takes place through the shift gates 102 and 103 of the main engine. During a shift, a shift count from bits 12-17 of a shift 45 mini-instruction is loaded into the mini-engine RC register. The remaining bits of the mini-instruction specify which main engine register or registers is to be shifted and whether to shift left or right. This shift count stored in the mini-engine RC register controls the number of places 50 the data is to be shifted. For example, if the RC register contains a count of 4 or greater, the data is shifted 4 places by the shift gates, and the register is decremented by 4. This process is repeated during subsequent clock cycles until the RC register contains a count less than 4. 55 If the contents of the RC register is zero, the shifting operation is complete. If it is a 1, 2, or 3, the data is then shifted 1, 2, or 3 places, respectively, and the RC register is cleared to zero. Consider a mini-instruction "662605." The "66" specifies a shift operation, the "26" specifies that the PC and PD registers are to be shifted together and the entire contents of both shifted left as one data group, and the "05" specifies that the registers are to be shifted five bits. When this instruction is executed, the 05 is loaded into the RC register. Since it 65 is greater than 4, the PC and PD registers are shifted 4 places left during the first clock cycle, and RC is decremented by 4, becoming a 1. Then the contents of PC and PD are shifted 1 place left during the next clock cycle, and RC is cleared to zero, completing the operation. In 70 the shifting operation, the data from the PC and PD registers are transferred through the PE and PF register to the shift gates 102 and 103. The first shift of 4 occurs and the shifted results are returned to the PC

nificant bits of PC are lost and the most significant bits of PD become the least significant bits of PC. A similar operation occurs for the remaining one bit shift.

During a floating point normalize operation, the number of places to be shifted is determined by the data itself, i.e., the data is to be shifted left an undetermined number of times until a "one" appears in the most significant bit position. For this type operation, bits 9-35 of the PB register are shifted along with bits 9-35 of the PD register, and shifted left until a one appears in the bit 9 position of the PB register. Bits 0-8 in each register are not involved in a normalize operation and are not disturbed. Bits shifted out of the most significant bit positions of the PD register are shifted into the least significant bit positions of the PB register. The normalize operation is started as a result of executing the normalize mini-instruction "6614xx", where the "66" specifies shift, the "14" specifies a floating normalize operation using the PB and PD registers in the manner described above, and the "xx" may be any octal number ranging from 00 through 77. If the latter is any number from 00-76, it will be loaded into the RC register as described previously for a shift count. If it is 77, the contents of the RC register will not be altered. The normalize operation is performed as follows. If the PB register bits 9-12 do not contain a "one," the contents of PB and PD as described above are shifted 4 places left and a 4 is added to the contents of the RC register. This process takes one clock cycle, and is repeated until a "one" appears in bits 9-12 of PB. If the one is in bit position 9, the normalize operation has been accomplished; otherwise, bits 9-12 are decoded to cause a shift 1, 2, or 3 places left and a 1, 2, or 3, respectively, is added to the contents of the register. This completes the operation. During each clock cycle the data from the PB and PD registers passes through the PE and PF registers and is shifted by the shift gates 102 and 103, with the results being returned to the PB and PD registers. This is repeated for as many clock cycles as necessary to complete the required operation.

A masking operation is performed on the mini-engine RC register under the following conditions. Whenever any test mini-instruction is decoded, the skip distance portion of the instruction is loaded into the RC register. The purpose of a skip instruction is to jump up or down an instruction list, or emulator routine, to fetch another instruction. Inasmuch as the skip distance is five bits long, and the RC register is eight bits long, the three most signicant bits of the RC register are cleared to zero during this particular loading operation to ensure that the register does not contain any bits not involved in the skip operation. Under test conditions which will cause a skip, the contents of the RC register are added to the contents of the RB register and the result is stored in the RB register thereby giving the location of the next instruction. A simple example of the use of a skip operation may occur where the sign of a number is tested to determine if it is plus or minus. If the sign is minus, it may be desired to skip a part of a routine dealing with positive numbers and thus use only the steps of the routine dealing with negative numbers.

The register RD is used to save the contents of the minimulator contents of both shifted left as one data group, and the "05" specifies that the registers are to be shifted five bits. When this instruction is executed, the 05 is loaded into the RC register. Since it is greater than 4, the PC and PD registers are shifted 4 place left during the first clock cycle, and RC is decremented by 4, becoming a 1. Then the contents of PC and PD are shifted 1 place left during the next clock cycle, and RC is cleared to zero, completing the operation. In the shifting operation, the data from the PC and PD registers are transferred through the PE and PF registers. It will be apparent that the most sig-

14

in the adder 118, and transferring the result to the RD register. The start address of the subroutine as specified by the SMCT instruction is loaded into the RB register, and the subroutine is executed under control of the RB register until completion of the subroutine. When the subroutine is completed, the contents of the RD register are then loaded back into the RB register in order to continue execution of the emulator routine commencing with the next instruction following the SMCT instruction.

The registers RE and RF are used when a transfer within the mini-engine occurs, and thus are used for temporary storage and data paths within the mini-engine. Data flow during a straight transfer is from the adder 118 to the RE register and from the RD register to the RF register. During a cross transfer provided by lines 121 and 122, the data flow is from the adder to the RF register and from the RD register to the RE register.

The scheduler 43 (FIG. 3a) is the basic controller of the inner computer. The scheduler receives requests from the various functional stations and determines the appropriate action to be taken based upon a system of priorities. By this means, the facilities of the system are switched and controlled in a flexible manner to perform the operations corresponding to those of the computer being emulated, such as, instruction execution, 25 input/output initiation and termination, input/output data flow, console functions, and real time clock. In general, the scheduler 43 determines the request which is to be serviced, and passes control to the wired-in-sequence 44 which in turn causes execution of the appro- 30 priate emulator routine. The utilization of a switchable inner computer to serve the various systems facilities in a flexible manner by means of emulator routines permits a computer embodying the concepts of this invention to emulate a number of different computer systems. The 35 scheduler is of principal importance in accomplishing this objective.

The requests to the scheduler 43 are divided into four levels according to their urgency. When several requests are simultaneously present, the scheduler selects the re- 40quest which has the highest priority. Control is then passed to the appropriate state of the wired-in-sequence 44. The following is a list of the scheduler requests in descending order or priority, and the corresponding wired-in-sequence states to which control is passed.

| Priority<br>level | Flip-flop<br>set | Request or interrupt               | First<br>W-I-S<br>state |

|-------------------|------------------|------------------------------------|-------------------------|

| 1                 | I CON 1          | Return                             | YRO                     |

|                   |                  | Channel 1 buffer service           | YBO                     |

| 2                 | 1 CON 2          | Return<br>Channel 2 buffer service | YBO                     |

| 3                 | I CON 3          | Return                             | YRO                     |

|                   |                  | Terminate                          | YBO                     |

| 4                 | I CON 4          | Return                             | YRO                     |

| 1                 |                  | Trap                               | YBO                     |

|                   |                  | Program                            | YAO                     |

The channel one buffer service request may be indi- 60 cated by an emulator instruction, or as a result of the I/O channel filling one of its buffers. The object of this request is to inform the inner computer to remove the data from the buffer before the channel has a chance to overlay the buffer with new data. When the buffer 65 service request is recognized by the scheduler 43, wiredin-sequence state YBO is enabled. The wired-in-sequence states and the resulting action will be described subsequently.

The channel two buffer service request is similar to 70 the channel one buffer service request except that it is used to service channel two on two channel systems and has a lower priority than the channel one buffer service request. When this request is recognized by the scheduler 43, wire-in-sequence state YBO is enabled.

16 The terminate request may be set by an emulator instruction or by a signal from one of the I/O channels

indicating the end of an input/output operation. When the scheduler 43 recognizes this request, it enables wired-

in-sequence state YBO.

There are six keys on the operator's console 14 which will cause a console request. These are the interval timer, reset, clear, load card, load tape, execute entry, and execute display. If any of these keys are on, a flip-flop in the scheduler 43 will be set. When this request is recognized by the scheduler, control will be passed to state YBO of the wired-in-sequence.

If a condition occurs which would cause a trap on the computer being emulated, the trap request may be set by an emulator instruction. When the trap request is recognized by the scheduler 43, state YBO of the wiredin-sequence is enabled. When emulating a certain present day computer, there are some conditions under which it is desirable to delay the recognition of a trap request. This may be accomplished by providing a postpone trap flip-flop which is set by means of an emulator instruction in addition to setting the trap request. This allows one program request to be recognized before the trap request will be recognized. In effect, this reverses the priority of the program and trap requests for the duration of one instruction in the language of the computer being emulated.

The program request may be set by an emulator instruction or by the operator when he presses the start key of the console. When a program request is recognized by the scheduler 43, sequence state YAO of the wired-in-sequence 44 is enabled.

It is sometimes necessary to temporarily interrupt the operation of one level until some later event takes place. To control this activity, each level has what is called a "hang" and a "return request." A hang condition may be set for any scheduler level by an emulator instruction. This also sets a return request, but causes all requests occurring at that level to be temporarily ignored. When the hang is cleared, the return request will be honored according to its level's priority. If in any one level there exists both an "original" request and a return request, the return request will be honored first. When the scheduler 43 recognizes any return request, step YR0 of the wired-in-sequence is entered.

Within each scheduler priority level there are three groups of flip-flops as seen in FIGS. 5a and 5b. These flip-flops are the interrupt (INTxx) flip-flops 126 through 142, and status flip-flops 144 through 153, and the current operating level flip-flops (ICONx) 155 through 158. Briefly, the interrupt flip-flops are used to store any one or more conditions or requests (such as a program request) which requires servicing by the scheduler 43. One or more interrupt flip-flops are set whenever such conditions occur. The outputs of these flip-flops are coupled as inputs to the following AND gates 160 through 170 as indicated by the designations on outputs of these gates in FIGS. 5a-5b. As will be described later, each cycle of the system clock includes pulses KCP0 through KCP7, the "KCP" indicating a clock pulse and the numeral (e.g., 7) indicating the clock time. At KCP4 time of each clock cycle, as indicated by line 172, all of the interrupts present at each level are gated into the status flip-flops 144 through 153 by the gates 160 through 170 which are coupled to the set inputs of these flip-flops. At this time, all the requests present are "frozen," so to speak, in the status flip-flops 144 through 153 so that there will be no further changes in the states of these flip-flops until KCP3 time of the next clock cycle when these flip-flops are reset. After KCP4 time noted above, if the scheduler gains control it will use the outputs of the status flip-flops at KCP0 time to set the proper current operating level flip-flop (ICONx) 155 through 158 according to the logic shown in FIGS. 5a 75 and 5b.

More specifically, there are four basic interrupt flipflops (level four contains five) for each level as shown below:

utilized to service other requests. The hang flip-flop for any level can be set by the mini-instruction "0654xx" where the "06" specifies a miscellaneous mini-instruc-

| Flip/Flop       | Level 1    | Level 2    | Level 3    | Level 4                  |

|-----------------|------------|------------|------------|--------------------------|

| Request         | 126(INT19) | 130(INT23) | 134(INT27) | 138([NT31)<br>139([NT32) |

| Job-in-progress |            | 131(INT24) | 135(INT28) | 140(LNT33)               |

| Return          |            | 132(INT25) | 136(INT29) | 141(INT34)               |

| Hang            | 129(INT22) | 133(INT26) | 137(INT30) | 142(TNT35)               |

The "request" flip-flops 126, 130, 134, 138 and 139 10 tion, and the "54" specifies hang present level. The xx (INT19, INT23, INT27, INT31 and INT32) are set and reset in the following manner:

INT19 (SET)=Channel 1 Buffer Service Request (HCBSR), OR "Set Level 1 Buffer Service Request" mini-instruction:

INT19 (RESET)="Reset all Hangs and Requests" miniinstruction, OR Machine Reset (SRES);

INT23 (SET)=Channel 2 Buffer Service Request (BCBSR), OR "Set Level 2 Buffer Service Request" mini-instruction:

INT23 (RESET) = same as INT 19 Reset;

INT27 (SET)=Terminate Request (HTERM-T) AND Level 3 not in operation (ICON3-F), OR "Set Terminate Request" mini-instruction;

INT27 (RESET) = same as INT19 Reset;

INT31 (SET)="Set Channel Trap Request" mini-instruction:

INT31 (RESET)="Reset Level 4" mini-instruction, OR Machine Rest, OR Console Reset (SPRES):

INT32 (SET)=Trap Request Status F/F (ITRRQ), set AND no higher level status flip-flops set, AND YSCON, OR "Set Program Reset" mini-instruction;

INT32 (RESET)=Reset Program request signal, OR Program Request Status F/F (IPGRQ) set AND no higher level status F/Fs set AND Manual Mode AND YSCON.

The general logical form for setting and resetting the above interrupts may be illustrated by means of the following example. The "Reset and hangs and requests" mini-instruction term for resetting INT19 is: RG17x. RGIx6·LMIS·KCP6. The RGIxx signals originate in a RGI decide circuit which will be discussed later, and in this example mean that a SOP code of 76 has been decoded. The LMIS means that a miscellaneous instruction performs this operation, and the KCP6 means the INT19 flip-flop 126 is reset at clock time six.

The Job In Progress (JIPx) flip-flops 127, 131, 135 and 140 (INT20, INT24, INT28, INT33) for any level are used to store the fact that the last request recognized 50 by the scheduler at this level is still being serviced even though the servicing of such a request may have been temporarily interrupted by a hang condition. The JIPx flip-flops are set at KCP0 time by the same conditions that set the current operating level (ICONx) flip-flops 155 through 158 as will be discussed. The JIP flip-flops are reset as follows:

INT20 (RESET) = same as INT19 reset, OR Exit from Level 1:

INT24 (RESET)=same as INT19 reset, OR Exit from Level 2;

1NT28 (RESET)=same as INT19 reset, OR Exit from Level 3;

INT33 (RESET)=same as INT19 reset, OR Exit from Level 4.

A hang is a condition initiated by a "miscellaneous" mini-instruction which indicates that the scheduler level currently in operation must be temporarily interrupted. The hang condition is useful, for example, in the emulation of certain input/output functions where an input/ output operation cannot be initiated because some other input/output operation is already in progress. Due to the hang feature of the scheduler, the time which might be wasted in waiting for the first operation to finish can be 75 will not be loaded at KCP4, and therefore none of the

portion of the instruction is not used. Logically, this may

HANGn (SET)=ICON $n \cdot RGI5X \cdot RGIX4 \cdot LMIS \cdot KCP6$

be expressed as for any level "n" as

In addition to the above logic, the level 4 hang flip-flop 142 may be set by the mini-instruction "0660xx" which means "set program halt and hang level 4." This miniinstruction is used to emulate halt instructions of other computers.

The same logic which sets the hang flip-flop for any level also sets the return flip-flop for that level, that is, RETURN, (SET)=HANGn (SET). Also, the decoding of the "hang current level" mini-instruction generates the signal YSTS by means of gate 175 (FIG. 6). The decoding of the "set program halt and hang level 4" also generates YSTS by means of gate 176. The YSTS signal starts the wired-in-sequence at state YSO.

The wired-in-sequence proceeds from states YS0 through YS5, storing the contents of certain registers in control memory, as will be explained in the discussion of the wired-in-sequence 44. When the operation is complete, the signal LSCON is generated which sets the YSCON flip-flop (FIG. 7) which returns control to the scheduler, but does not reset the job-in-progress (JIP) flip-flop for the level currently in operation. The job-inprogress flip-flop is usually reset by the signal LEXIT which means exit from current level. Observe on FIGS. 5a and 5b that if for any level the hang flip-flop is set and the job-in-progress flip-flop is also set, no status flipflop for that level can be set at KCP4 time. Thus, any request for a level which has been "hung" is "locked out" temporarily. The signal YSCON will reset the current operating level flip-flop ICONx at KCP7 time, and if a request for some other level or levels is stored in the status flip-flops, the appropriate ICONx flip-flop will be set at KCP0 time. The level which was "hung" will be ignored by the scheduler until the hang flip-flop for that level is reset. The hang flip-flop for any level is usually reset at some point in time when an emulator routine detects conditions which make it appropriate to continue the emulator program which caused the hang condition. For example, assume that an I/O emulation program at level 2 cannot be continued because of an I/O operation already in progress, so that hang 2 flip-flop 133 is set which also sets the return 2 flip-flop 132 and control passes to the scheduler as previously described. Later, an emulator routine may be entered, for example as the result of a terminate request, which detects that the I/O operation which was in progress has been completed. This routine may then issue a mini-instruction to reset the hang 2 flip-flop 133. When this is done, the level 2 return status flip-flop 147 will be set at KCP4 time by means of gate 163 (FIG. 5a) since the JIP2 flip-flop 131 and return 2 flip-flop 132 are both set and the hang flip-flop 133 65 is now reset.