Field Service Manual for the Sun-3/160 Workstation

Part Number 800-1258-05 Revision: 50 of 15 January 1986 Class 2

### Credits and Trademarks

Sun Microsystems and Sun Workstation are registered trademarks of Sun Microsystems, Incorporated. Sun-2, Sun-2/xxx, Sun-3, Sun-3/xxx, Deskside, SunStation, SunCore, SunWindows, and DVMA are trademarks of Sun Microsystems, Incorporated.

UNIX is a trademark of Bell Laboratories.

#### **CAUTION**

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are design to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

Copyright © 1986 by Sun Microsystems, Inc.

This publication is protected by Federal Copyright Law, with all rights reserved. No part of this publication may be reproduced, stored in a retrieval system, translated, transcribed, or transmitted, in any form, or by any means manual, electric, electronic, electro-magnetic, mechanical, chemical, optical, or otherwise, without prior explicit written permission from Sun Microsystems.

## Contents

| Chapter 1 Sun-3/160 Functional Overview                   | 3   |

|-----------------------------------------------------------|-----|

| Chapter 2 Diagnostics and Troubleshooting                 | 45  |

| Chapter 3 Component Removal and Replacement               | 89  |

| Appendix A Cardcage Configuration                         | 133 |

| Appendix B CPU Board and VME-SCSI Board Connector Pinouts | 139 |

| Appendix C Degaussing the Monitor                         | 145 |

| Appendix D Power Supply Voltage Adjustment                | 149 |

| Appendix E ASCII/Hex Conversion Chart                     | 153 |

## Contents

| Preface                                 | xvii |

|-----------------------------------------|------|

| Chapter 1 Sun-3/160 Functional Overview | 3    |

| 1.1. The 2060 CPU Board                 | 4    |

| 2060 Bus Architecture                   |      |

| Data Buses                              | 6    |

| Address Buses                           | 8    |

| CPU Logic and DVMA Devices              | 9    |

| The MC68020 CPU                         | 9    |

| On-Chip Cache Memory                    | 9    |

| Floating Point Processor                | 10   |

| Optional Data Ciphering Processor       | 10   |

| Processor Supporting Logic              | 11   |

| System Reset                            | 11   |

| Interrupt Logic                         | 11   |

| System Clocks                           | 12   |

| The Real Time Clock                     | 12   |

| The Boot PROM                           | 12   |

| The EEPROM                              | 12   |

| Direct Virtual Memory Áccess            | 13   |

| User DVMA                               | 13   |

| Memory Management                       | 14   |

| On-Board Main Memory Logic              | 15   |

| Memory Refresh Logic                    | 15   |

| Main Memory                             | 15   |

| Video Interface Logic.      |                |

|-----------------------------|----------------|

| Video Memory                |                |

| Video Sync Control          | Logic          |

| Video Shift Logic           |                |

| Serial Communications       | s Interface    |

| Ethernet Interface          |                |

| VMEbus Interface            |                |

| VMEbus Arbitration          |                |

| VME Master Read/W           | rite Cycles    |

| VME Interrupt Acknowledge   | owledge        |

| VME Slave Mode              |                |

| VME Implementation          |                |

| 1.2. Memory Expansion Box   | ard            |

| 1.3. The 160C/160G Color I  | Board          |

| Color Board VMEbu           | s Interface    |

| Frame Buffer Logic          |                |

| Frame Buffer Memo           | ory            |

| Frame Buffer Addre          | essing         |

| Address Modes               |                |

| Raster Op Modes             |                |

| Memory Timing an            | d Sync Logic   |

| Color Maps and DA           | Cs             |

| 1.4. VME SCSI Board         |                |

| SCSI Bus Interface Log      | gic            |

| DMA Controller              |                |

| 1.5. Optional Printed Circu | it Boards      |

| VME-Multibus Adapt          | ter Board      |

| VME-VME Adapter Bo          | ard            |

| The 160C Graphics P         | rocessor Board |

| Viewing Processor           |                |

| Painting Processor          |                |

| Processor Associat          | ed Logic       |

| The 160C Graphics B         | Buffer Board   |

| 1.6. | Memory Subsystem                      | 36         |

|------|---------------------------------------|------------|

| 1.7. | The Power Supply                      | 37         |

|      | Sun-3/160 Power Consumption           | 39         |

| 1.8. | Monitors                              | 40         |

|      | Sun-3/160C Color Monitor              | 40         |

|      | Sun-3/160M Black and White Monitor    | 40         |

|      | Gray Scale Monitor                    | 40         |

| Chap | ter 2 Diagnostics and Troubleshooting | 45         |

| 2.1. | Scope of This Chapter                 | 45         |

| 2.2. | Related Documents                     | 45         |

| 2.3. | Conventions Used in This Chapter      | 45         |

| 2.4. | Graceful Power-Down                   | 46         |

|      | The Reset Button                      | 46         |

|      | Normal Start-up                       | 47         |

|      | Normal LED Patterns                   | 47         |

|      | Automatic Boot-up                     | 47         |

|      | To Abort the Auto-Boot                | 48         |

|      | Redirecting Console I/O               | 48         |

|      | No Console Display?                   | 49         |

|      | Failure to Boot                       | 49         |

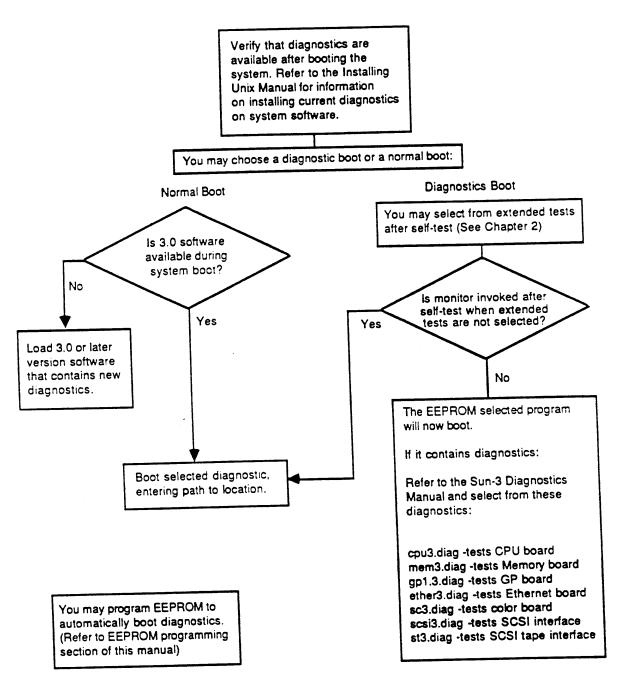

| 2.7. | Diagnostic Boot-Up                    | <b>4</b> 9 |

|      | Prerequisites                         | 50         |

|      | Null Modem Cable Wiring               | 51         |

|      | Self-Test Interaction                 | 52         |

|      | Successful Self-Test Display          | 53         |

|      | When the CPU Fails a Test             | 55         |

|      | To Go On Testing                      | 55         |

|      | To Read the LED Table                 | 56         |

| 2.8. | The PROM Monitor                      | 57         |

|      | Monitor Command Syntax                | 57         |

|      | Monitor Command b                     | 58         |

|      | Manitor Command k                     | <b>c</b> : |

|        | Monitor Command q                           | 59 |

|--------|---------------------------------------------|----|

|        | Monitor Command s                           | 59 |

|        | Monitor Command t                           | 60 |

|        | Monitor Command u                           | 60 |

|        | Monitor command v                           | 61 |

|        | Monitor Command w                           | 61 |

|        | Monitor Command x                           | 61 |

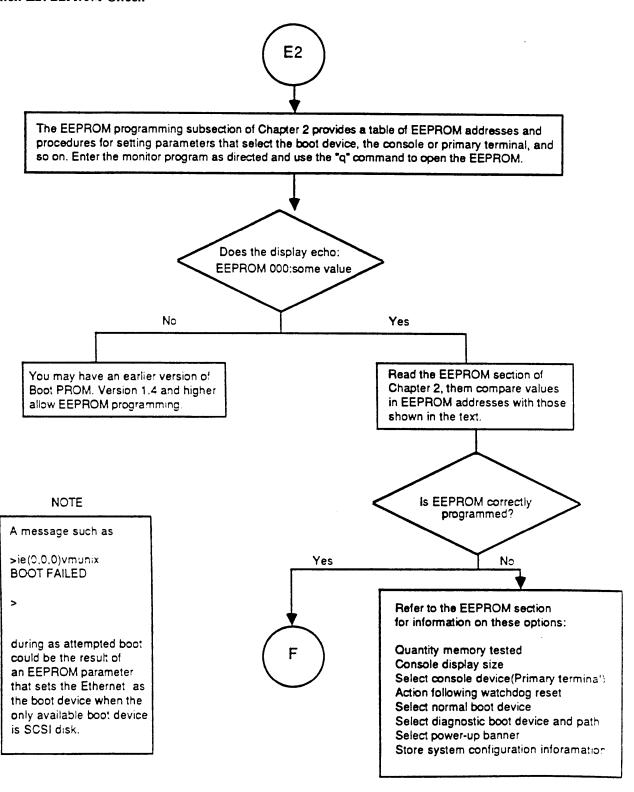

| 2.9. E | EEPROM Programming                          | 61 |

|        | Setting Quantity of Memory Tested           | 63 |

|        | Changing Monitor Display Size               | 63 |

|        | Changing Action that Follows Watchdog Reset | 63 |

|        | Selecting the Boot Device                   | 64 |

|        | Setting Up Console I/O                      | 64 |

|        | Changing the Banner                         | 65 |

|        | Turning Keyboard Click On or Off            | 66 |

|        | Selecting the Diagnostic Boot Device        | 66 |

|        | Setting the Diagnostic Boot Path            | 67 |

|        | Recording System Configuration              | 68 |

|        | CPU Board Block                             | 69 |

|        | Memory Expansion Board                      | 70 |

|        | Color Board                                 | 70 |

|        | SMD Disk Controller Board                   | 70 |

|        | Tape Controller Board                       | 70 |

|        | Asynchronous Line Multiplexer               | 71 |

|        | SCSI Board                                  | 71 |

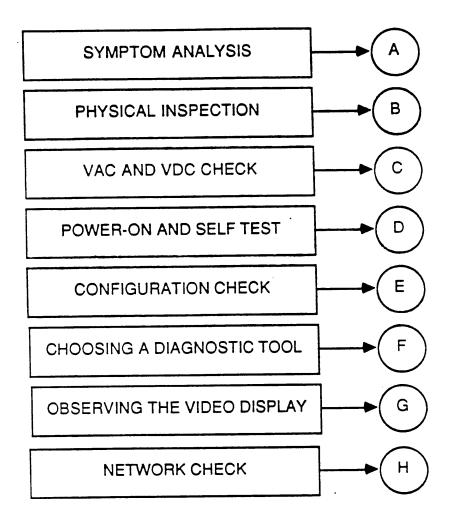

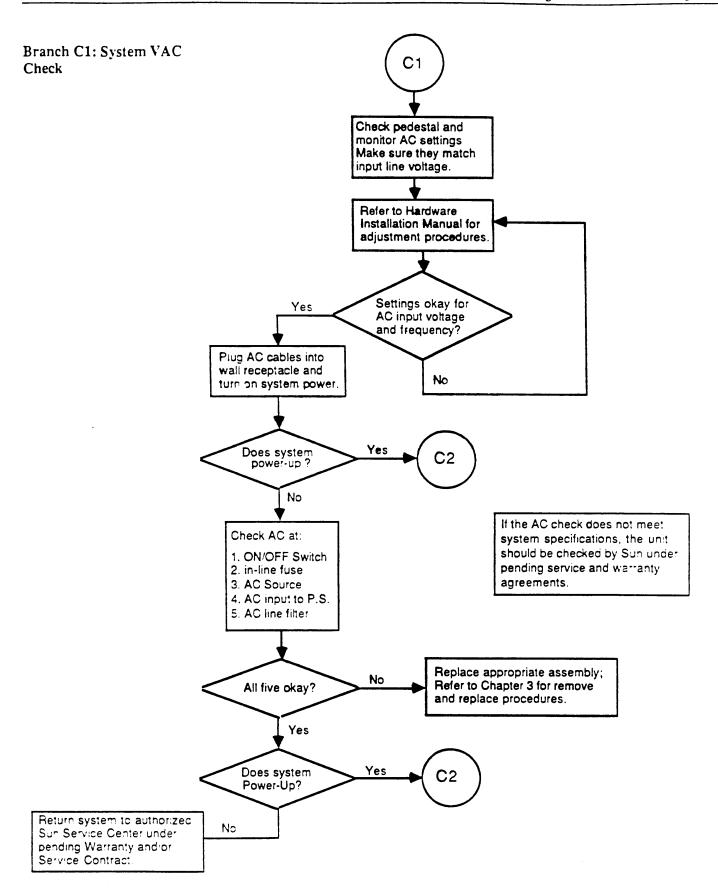

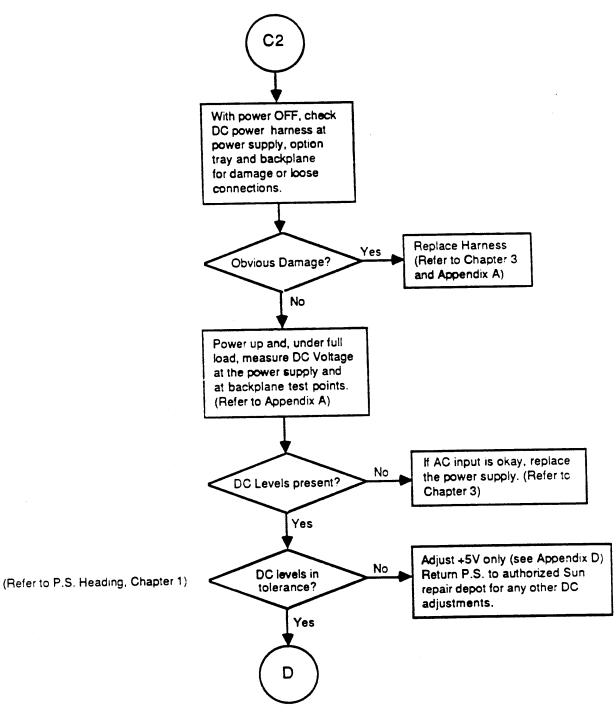

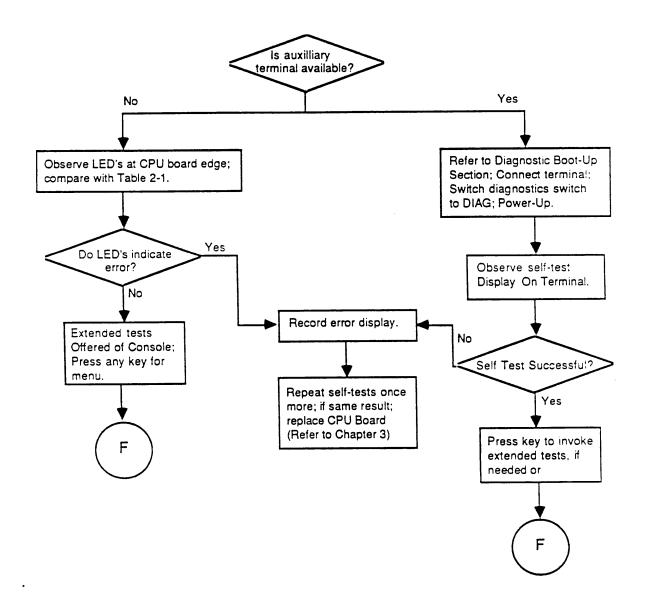

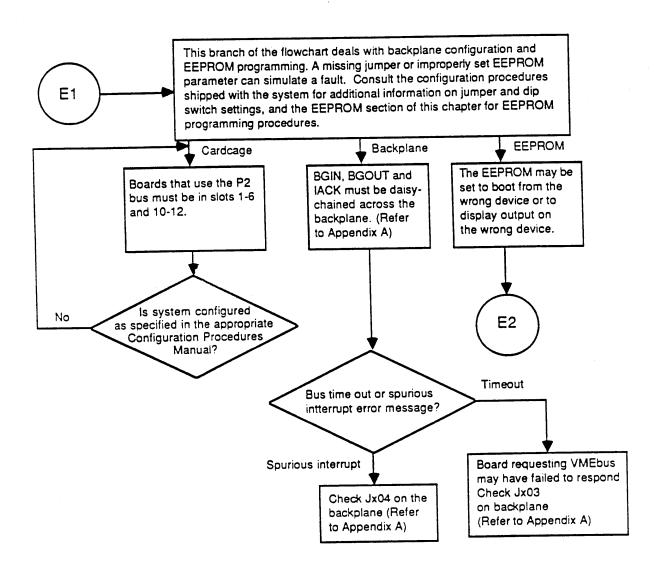

| 2.10.  | Troubleshooting Flow Chart                  | 72 |

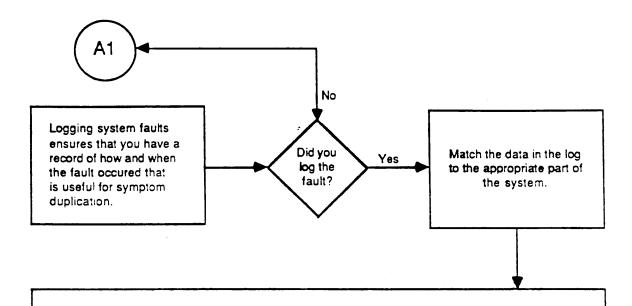

|        | Branch A: Symptom Analysis Log              | 73 |

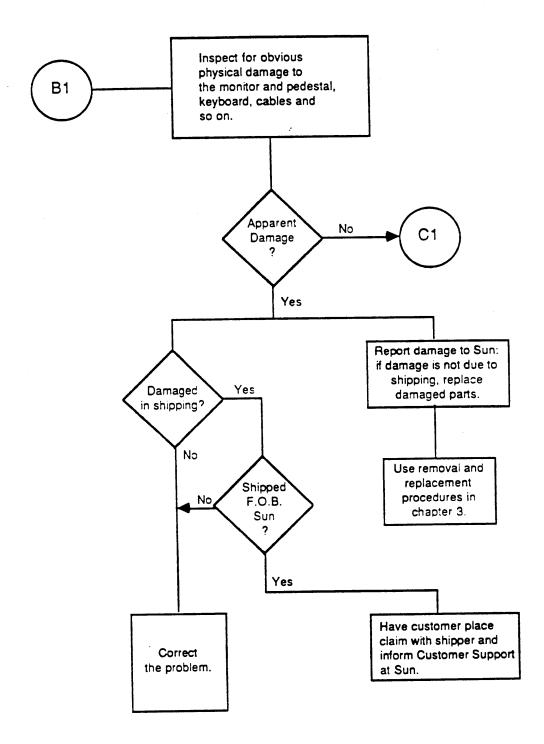

|        | Branch B: Physical Inspection               | 74 |

|        | Branch C1: System VAC Check                 | 75 |

|        | Branch C2: System VDC Check                 | 76 |

|        | Branch D: Power-On and Self-Test            | 77 |

|        | Branch E1: System Configuration Check       | 78 |

|        | Reach F2: FFPROM Check                      | 79 |

| Branch F: Choosing the Applicable Diagnostic Tool | 80  |

|---------------------------------------------------|-----|

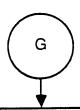

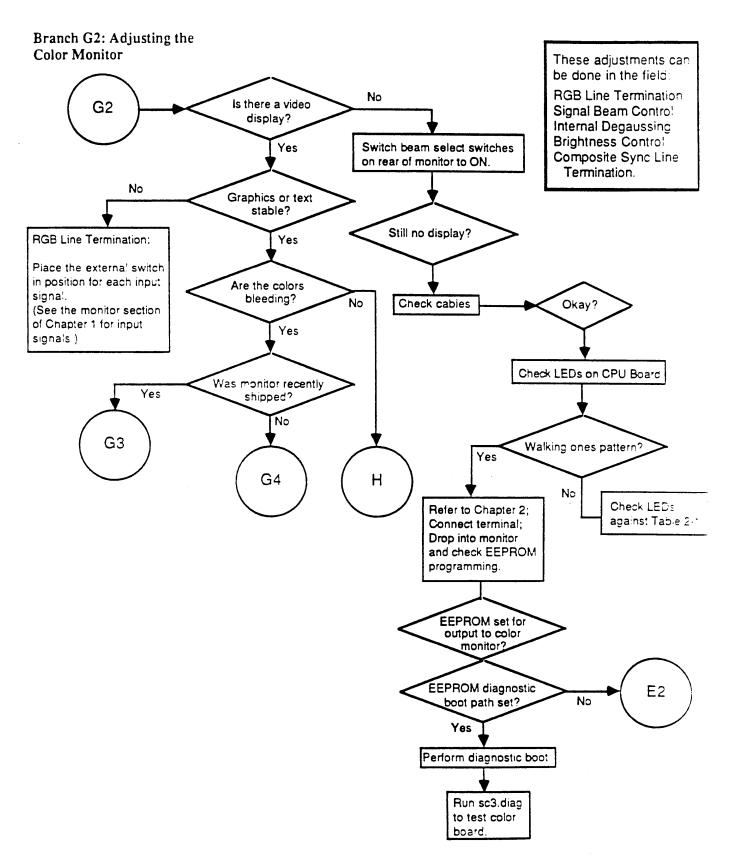

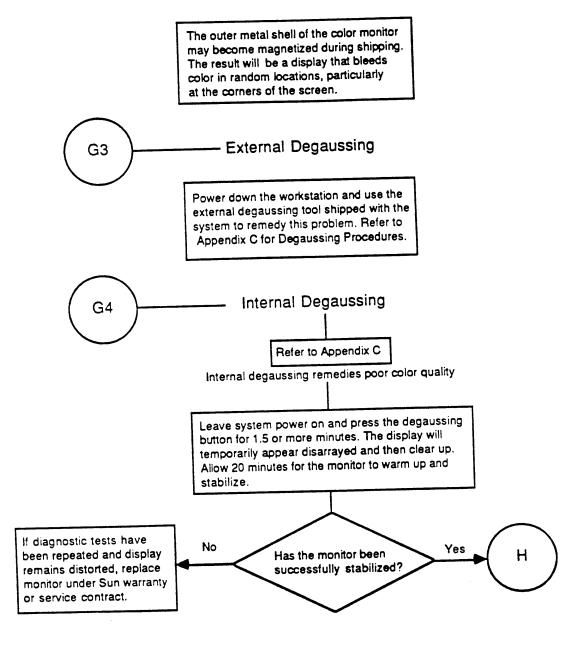

| Branch G: Observing the Video Display             | 81  |

| Branch G1: Adjusting the Monochrome Monitor       | 82  |

| Branch G2: Adjusting the Color Monitor            | 83  |

| Branch G3 and G4: Degaussing the Color Monitor    | 84  |

| Branch H: Network Check                           | 85  |

| Chapter 3 Component Removal and Replacement       | 89  |

| 3.1. Graceful Power-Down                          | 89  |

| 3.2. Monitor Removal                              | 90  |

| 3.3. Printed Circuit Board (PCB) Removal          | 90  |

| ID PROM Replacement                               | 91  |

| Socketed IC Removal and Insertion                 | 93  |

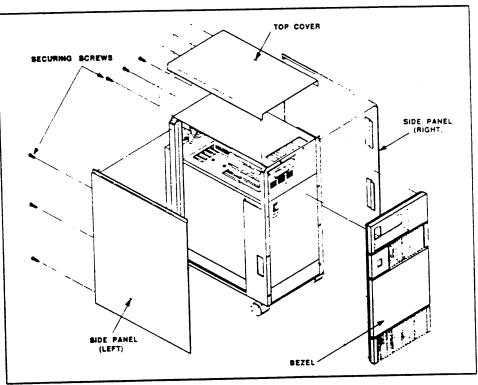

| 3.4. Trim Removal                                 | 9-1 |

| Top Cover Removal                                 | 94  |

| Side Panel Removal                                | 94  |

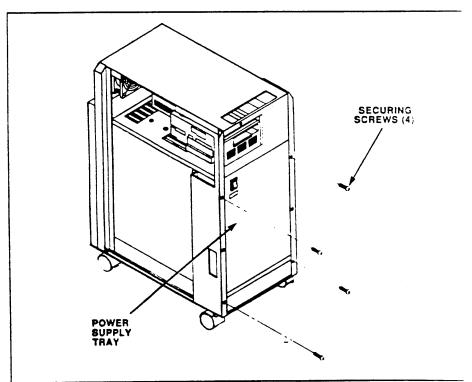

| 3.5. Power Supply Removal                         | 95  |

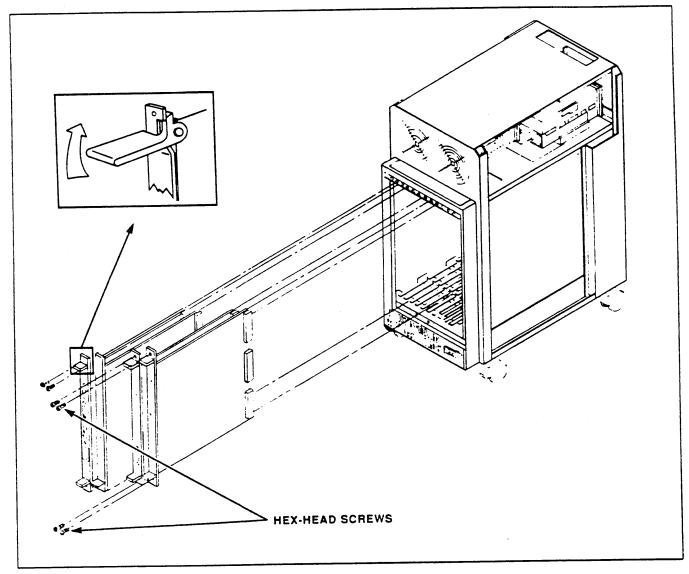

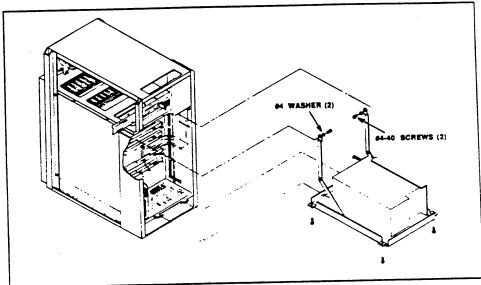

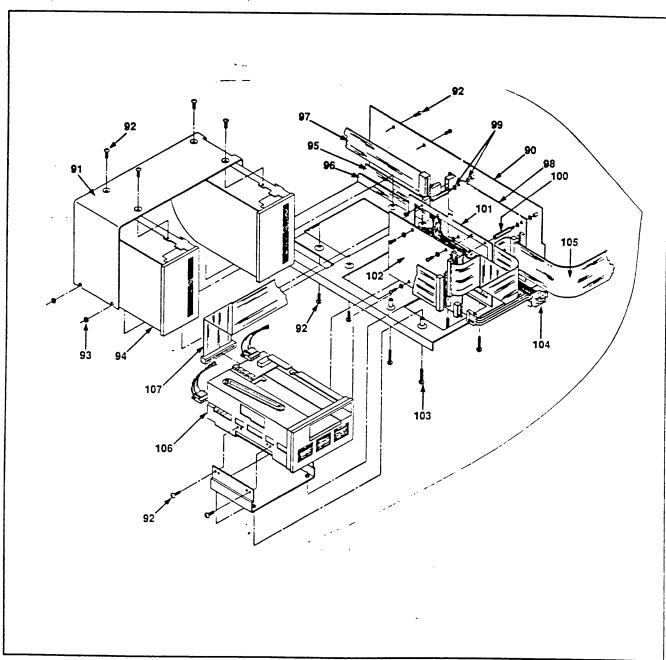

| 3.6. Option Tray Removal                          | 101 |

| 3.7. Removing Drives From the Option Tray         | 102 |

| Tape Drive Removal                                | 102 |

| Disk Drive Mounting                               | 104 |

| Single Disk Drive Removal (Version A)             | 104 |

| Single Disk Drive Removal (Version B)             | 105 |

| Dual Disk Drive Removal                           | 106 |

| For Option Tray A                                 | 106 |

| For Option Tray B                                 | 107 |

| For Either Option Tray                            | 107 |

| 3.8. Drive Controller Board Removal               | 108 |

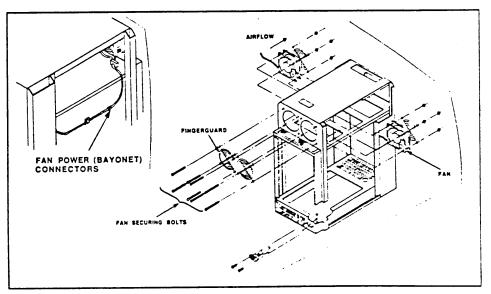

| 3.9. Upper Fan Assembly Removal                   | 112 |

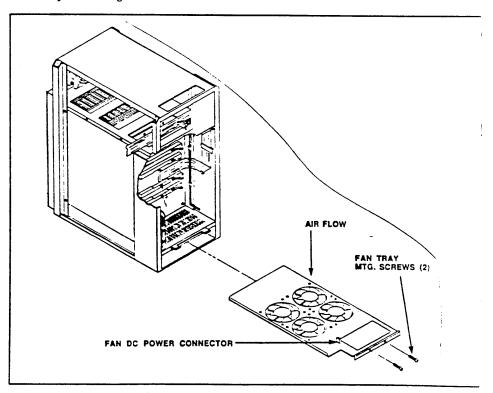

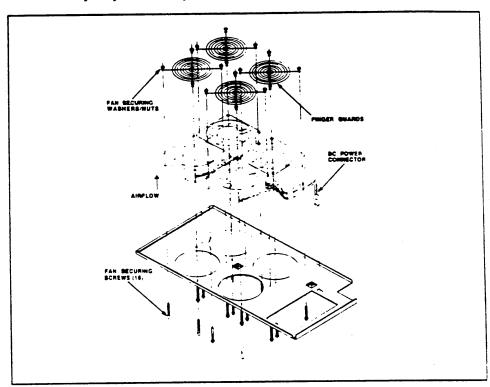

| 3.10. Lower Fan Assembly Removal                  | 112 |

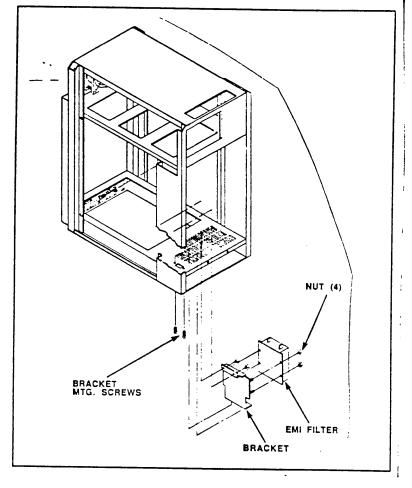

| 3.11. Cardcage/Backplane Removal                  | 114 |

| 3.12 Illustrated Parts Breakdown                  | 116 |

| Appendix A Cardcage Configuration                         | 133 |

|-----------------------------------------------------------|-----|

| A.1. Cardcage Slot Numbering and Board Locations          |     |

| A.2. Backplane Connectors/Jumpering                       | 134 |

| Backplane Connector Function                              | 135 |

| Appendix B CPU Board and VME-SCSI Board Connector Pinouts | 139 |

| B.1. CPU Board Connector Pinouts                          | 139 |

| B.2. VME-SCSI Board Cable Pinout                          | 141 |

| Appendix C Degaussing the Monitor                         | 145 |

| C.1. Internal Degaussing                                  | 146 |

| Appendix D Power Supply Voltage Adjustment                | 149 |

| Appendix E ASCII/Hex Conversion Chart                     | 153 |

| E. 1. Use of the ASCII/Hex Conversion Chart               | 153 |

## Tables

| Table 1 D | Occumentation                                 | <b>xv</b> iii |

|-----------|-----------------------------------------------|---------------|

| Table 1-1 | CPU Board 8-Bit Data Buses                    | 6             |

| Table 1-2 | Master Capabilities                           | 20            |

| Table 1-3 | Slave Capabilities                            | 21            |

| Table 1-4 | System Controller Capabilities                | 21            |

| Table 1-5 | Backplane Connector Function                  | 21            |

| Table 1-6 | 850 Watt Power Supply Input Specs             | 38            |

| Table 1-7 | 850 Watt Power Supply Output Specs            | 38            |

| Table 1-8 | DC Overvoltage Limits                         | 38            |

| Table 1-9 | Typical Sun-3/160 Component Power Consumption | 39            |

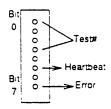

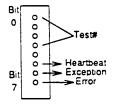

| Table 2-1 | LED Interpretation                            | 56            |

|           | Monitor Help Menu                             |               |

|           | EEPROM Address Space Allocation               | 62            |

| Table B-1 | Pinout of Keyboard/Mouse DB-15 Connector      | 140           |

|           | Pinout of Serial Ports A and B                | 140           |

|           | Pinout of Ethernet Connector                  |               |

| Table B-4 | Pinout of Video Connector                     | 141           |

| Table B-5 | VME-SCSI Board Cable Pinout                   | 141           |

| Table E-1 | ASCII/Hex Conversion                          | 153           |

# Figures

| Figure 1-1  | System Level Block Diagram              |     |

|-------------|-----------------------------------------|-----|

| Figure 1-2  | CPU Board Overview                      |     |

| Figure 1-3  | Data Bus Block Diagram                  |     |

| Figure 1-4  | 2060 Board Address Bus                  | :   |

| Figure 1-5  | Processor Logic Diagram                 | (   |

| Figure 1-6  | MMU Block Diagram                       | 1.  |

| Figure 1-7  | Video Logic Block Diagram               | 10  |

| Figure 1-8  | Ethernet Interface                      | 1   |

| Figure 1-9  | VMEbus Interface                        | 19  |

| Figure 1-10 | Sun-3/160C/160G Color Video Board Logic | 2:  |

| Figure 1-11 | VMEbus Interface Logic                  | 2   |

| Figure 1-12 | Color Board Frame Buffer Logic          | 2:  |

| Figure 1-13 | Memory Timing and Synchronization Logic | 26  |

| Figure 1-14 | Color Map and DAC Logic                 | 21  |

| Figure 1-15 | VME SCSI Board Logic                    | 28  |

| Figure 1-16 | SCSI Bus Interface Logic                | 29  |

| Figure 1-17 | DMA Controller Logic                    | 30  |

| Figure 1-18 | VME-Multibus Adapter Board Logic        | 3:  |

| Figure 1-19 | Graphics Processor Board Logic          | 33  |

| Figure 1-20 | Viewing Processor Logic                 | 3-  |

| Figure 1-21 | Painting Processor Logic                | 35  |

| Figure 1-22 | Memory Subsystem                        | 37  |

|             |                                         |     |

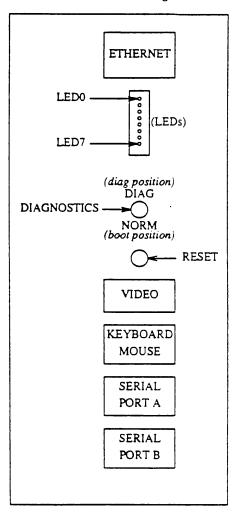

| Figure 2-1  | CPU Board Connector Edge                | 5 1 |

|             | Null Modem Cable Pin Arrangement                                  | 52  |

|-------------|-------------------------------------------------------------------|-----|

| _           |                                                                   | 53  |

| Figure 2-3  | Diagnostic Boot-Up Display                                        |     |

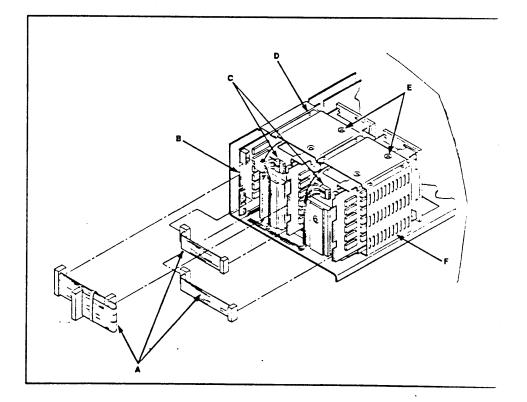

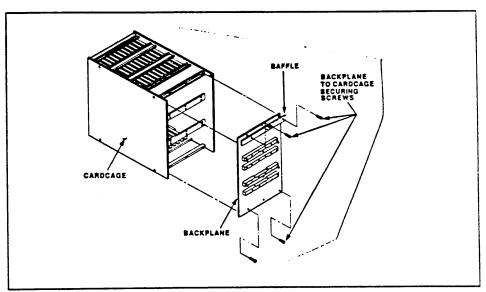

| Figure 3-1  | Sun-3/160 Cardcage                                                | 92  |

| •           | Trim Removal                                                      | 94  |

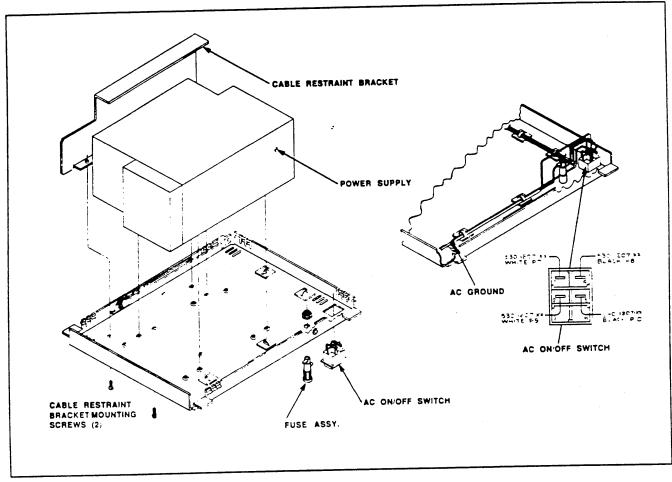

| •           | Power Supply Panel Securing Screws                                | 95  |

| •           | Power Supply Panel Retainers                                      | 96  |

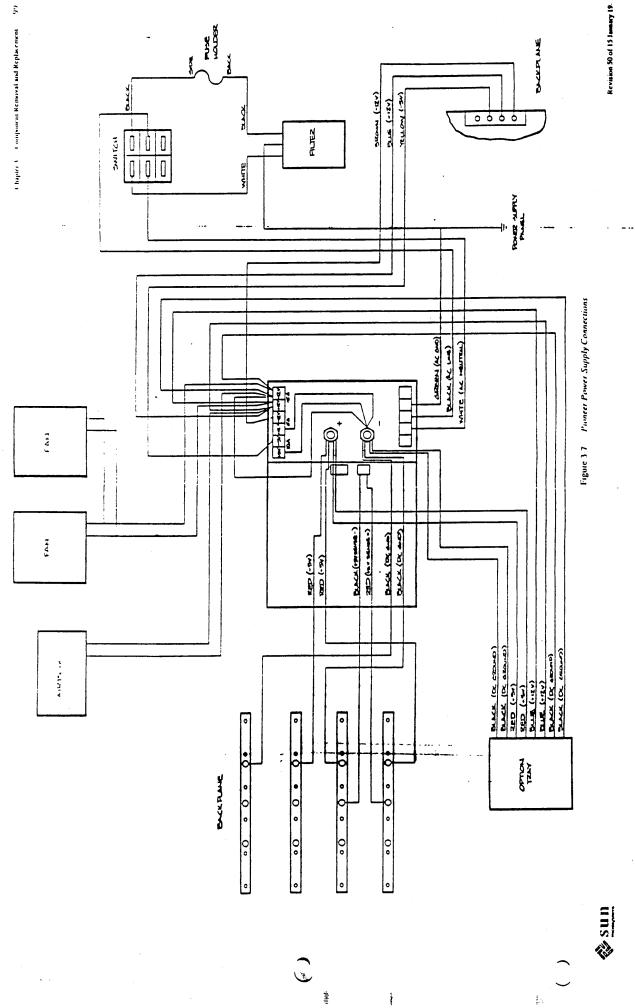

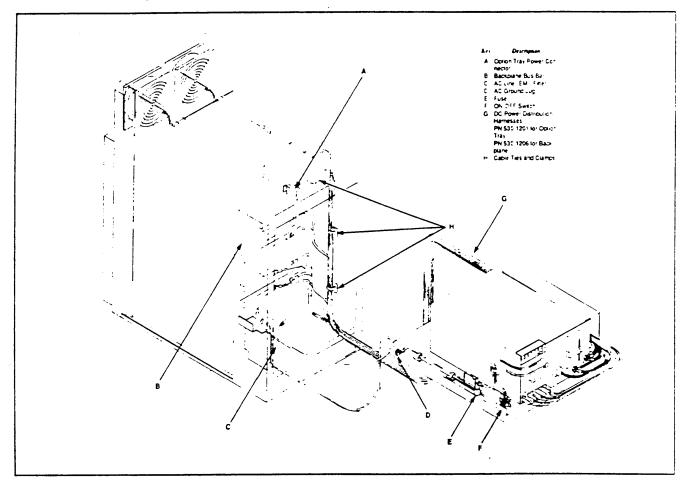

| •           | DC Distribution Harnesses                                         | 97  |

| •           | Power Supply-to-Panel Mounting                                    | 98  |

| •           | Pioneer Power Supply Connections                                  | 99  |

| •           | ETA Power Supply Connections                                      | 100 |

| _           | DC Power to the Option Tray                                       | 101 |

| _           | Option Tray Mounting                                              | 102 |

| ~           | Tape Drive to Option Tray Mounting                                | 103 |

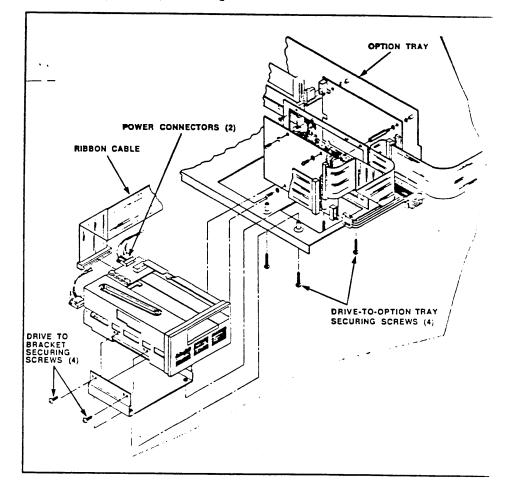

| •           | Single Disk Drive Removal (Version A)                             | 104 |

| Figure 3-13 | Single Drive Removal (Version B)                                  | 105 |

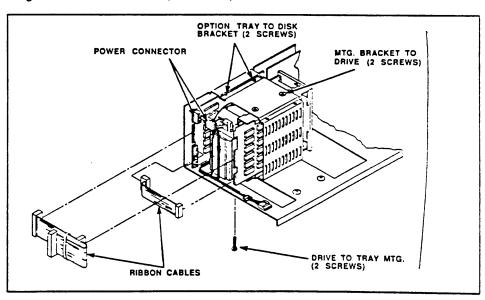

| Figure 3-14 | Dual Disk Drive Mounting (Version B)                              | 106 |

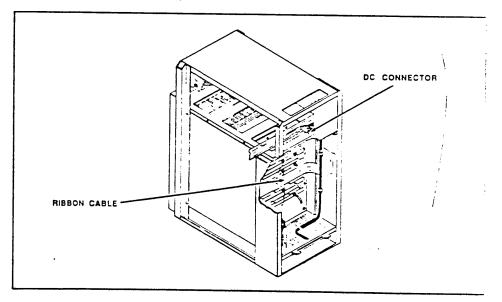

| Figure 3-15 | Dual Disk Drive Cabling (Option Tray A)                           | 107 |

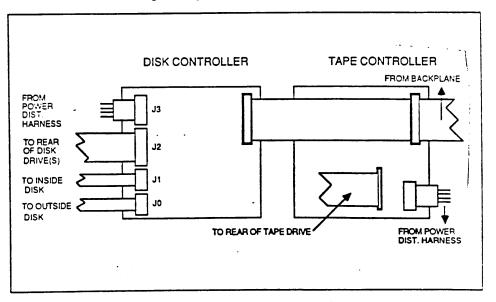

| Figure 3-16 | Dual Disk Drive Cabling (Option Tray B)                           | 108 |

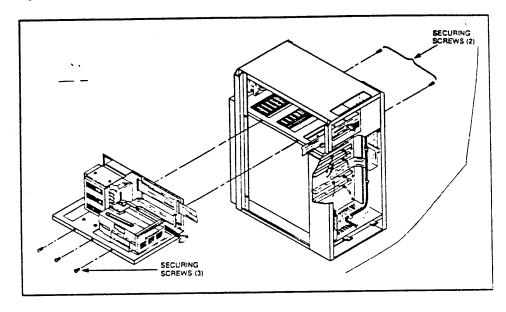

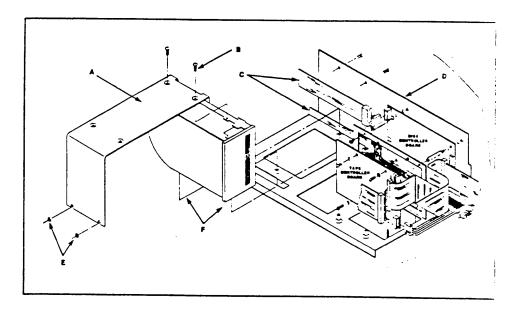

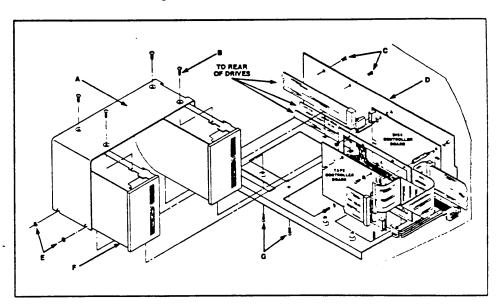

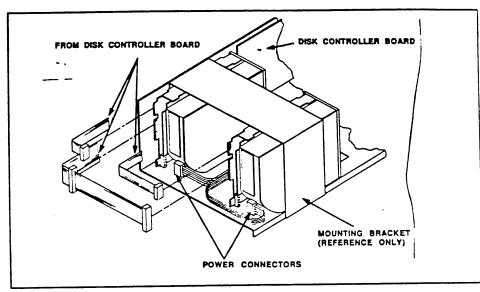

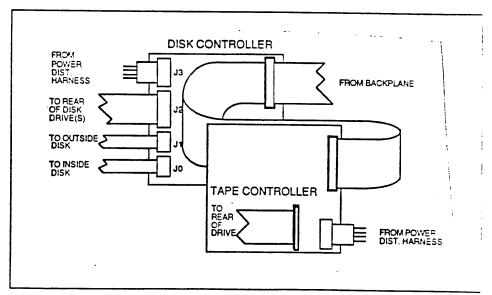

| Figure 3-17 | Controller Board Mounting For Option Tray Version A               | 110 |

| Figure 3-18 | Controller Board Cabling For Option Tray A                        | 110 |

| Figure 3-19 | Controller Board Mounting For Option Tray B                       | 111 |

| Figure 3-20 | Controller Board Cabling For Option Tray B                        | 111 |

| Figure 3-21 | Upper Fan Assembly Mounting                                       | 112 |

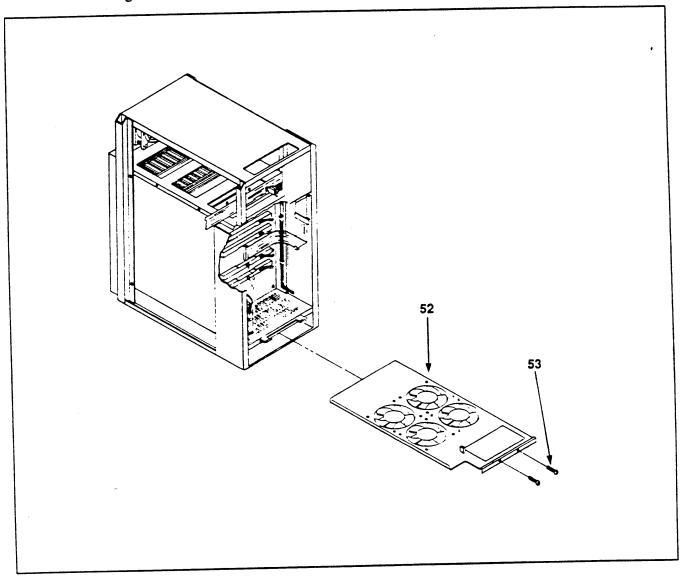

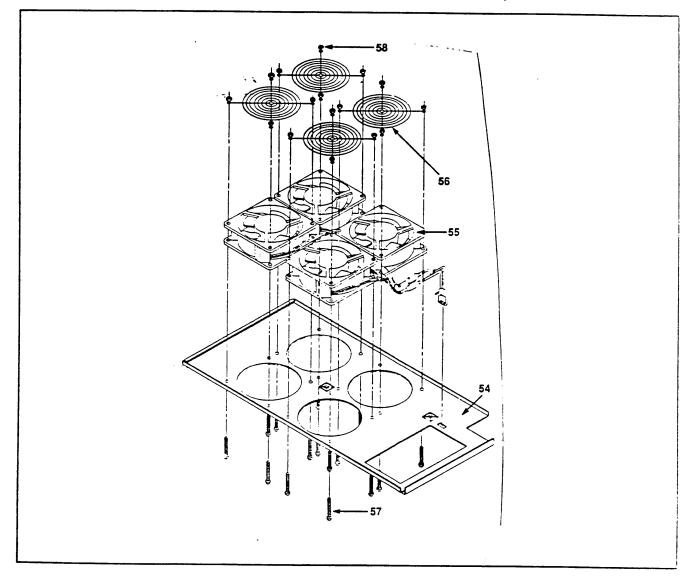

| Figure 3-22 | Fan Tray Mounting                                                 | 113 |

| Figure 3-23 | Fan Removal                                                       | 114 |

| Figure 3-24 | Cardcage and EMI Filter Mounting                                  | 115 |

| Figure 3-25 | Backplane-to-Cardcage Mounting                                    | 116 |

| Figure 3-26 | Sun-3/160 Illustrated Parts Breakdown #1: Monitor, Keyboard/Mouse | 117 |

| Figure 3-27 | Illustrated Parts Breakdown #2: Cover and Panels                  | 118 |

| _           | Illustrated Parts Breakdown #3: PC Boards in Card Cage            | 119 |

| _           | Illustrated Parts Breakdown #4: Front Door and Castors            | 120 |

| Figure 3-30 | Illustrated Parts Breakdown #5: ETA Power Supply  Mounting                      | 121 |

|-------------|---------------------------------------------------------------------------------|-----|

| Figure 3-31 |                                                                                 | 122 |

| Figure 3-32 | Illustrated Parts Breakdown #7: Upper Fan and AC Receptacle                     | 123 |

| Figure 3-33 | Illustrated Parts Breakdown #8: Lower Fan Mounting                              | 124 |

| Figure 3-34 | Illustrated Parts Breakdown #9: Airbox Assembly                                 | 125 |

| Figure 3-35 | Illustrated Parts Breakdown #10: Option Tray With Single Disk (PN 540-1247)     | 126 |

| Figure 3-36 | Illustrated Parts Breakdown #11: Option Tray With Tape Only (PN 540-1117)       | 127 |

| Figure 3-37 | Illustrated Parts Breakdown #12: Option Tray With Dual Disks (PN 540-1246)      | 128 |

| Figure 3-38 | Illustrated Parts Breakdown #13: Option Tray, Dual Disks and Tape (PN 540-1130) | 129 |

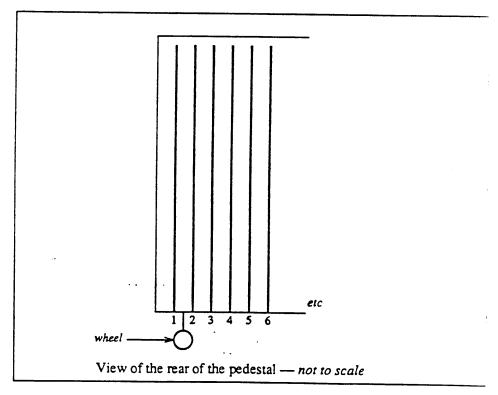

| Figure A-1  | Card Slot Numbering Viewed from Rear of Pedestal                                | 133 |

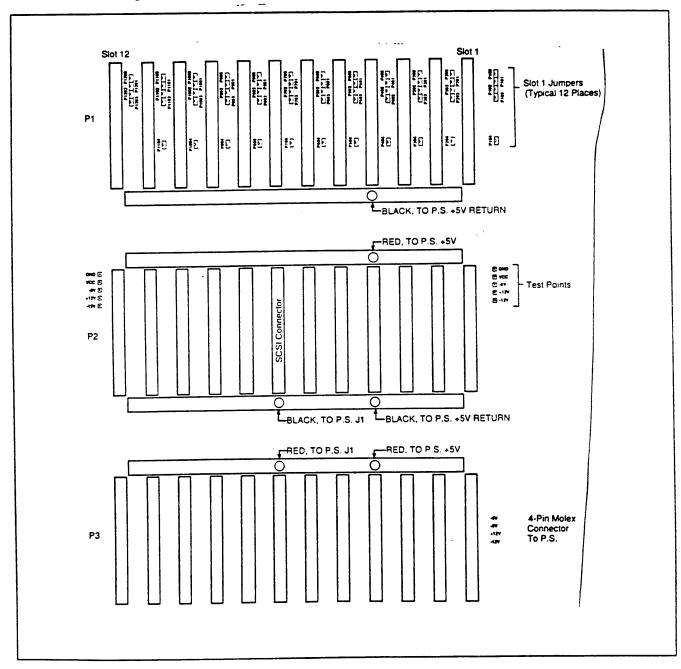

| Figure A-2  | Slot Numbering and P Connectors — As Seen From the Front of Pedestal            | 134 |

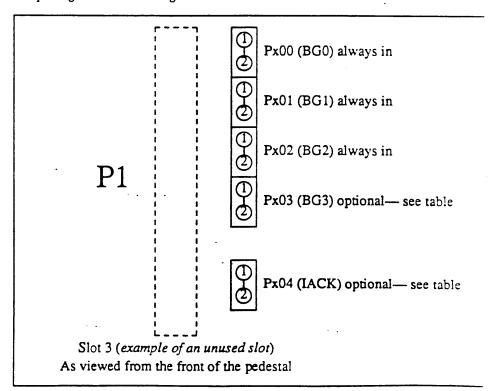

| Figure A-3  | Jumpering Unused Cardcage Slots                                                 | 135 |

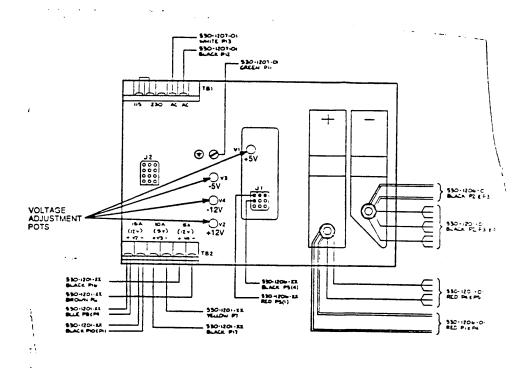

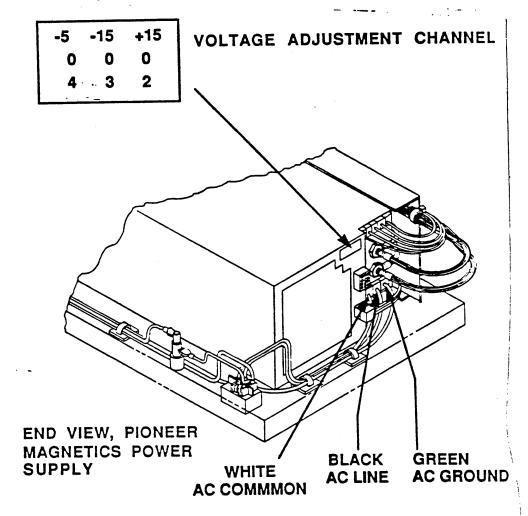

| Figure D-1  | ETA Adjustment Pot Locations                                                    | 149 |

| Figure D-2  | Pioneer Adjustment Pot Locations                                                | 150 |

.

### Preface

This manual is intended to provide information to aid field service engineers in board level troubleshooting and installation of field replaceable units for the Sun-3/160M, Sun-3/160C, and Sun-3/160G Workstation.

It is assumed that the reader is familiar with Transistor to Transistor Logic (TTL) and Emitter Coupled Logic (ECL), and with the Motorola MC68020 Microprocessor. The reader should also understand local area networks, Sun-3 virtual memory management architecture, and the VMEbus specification.

#### Summary of Contents

The contents of this manual are organized in this way:

Chapter 1

Sun-3/160 Functional Overview — Provides a basic understanding of major component function and the interaction between those functional blocks, and defines differences and similarities between the Sun-3 models.

Chapter 2

Diagnostics and Troubleshooting — provides troubleshooting and diagnostic information to aid in board level fault isolation.

Chapter 3

Component Removal and Replacement — describes how to remove and replace printed circuit boards, the power supply, fans, and other subassemblies.

Appendix A

Backplane Configuration — provides backplane jumpering and slot designation information required for installation and configuration of additional printed circuit boards.

Appendix B

PC Board Connector Pinouts — gives pinouts for the CPU and SCSI board connectors.

| Appendix C           | Degaussing the Monitor — provides procedures for degaussing the monitor to remedy color distortion.                                                                                                                                         |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Appendix D           | Power Supply Voltage Adjustment — shows location of DC output voltage adjustment potentiometers and terminal designations.                                                                                                                  |

| Appendix E           | ASCII/Hex Conversion Chart — provides the hexadecimal equivalent of basic ASCII characters for use in EEPROM programming.                                                                                                                   |

| Applicable Documents | We emphasize that this manual outlines rather than exhausts many of the topics contained within. References to applicable documents are listed below, however, and we urge you to read these documents should you need further information. |

Table 1 Documentation

| Part Number    | Description                                                                                                            |

|----------------|------------------------------------------------------------------------------------------------------------------------|

| 800-1150       | System Administration for the Sun Workstation                                                                          |

| 800-1314       | Hardware Installation Manual for the Sun-3/160                                                                         |

| 800-1317       | Installing UNIX on the Sun Workstation                                                                                 |

| 800-1361       | Sun Diagnostics Manual                                                                                                 |

| 813-1000       | Sun Hardware Options Guide                                                                                             |

| 813-2000       | Sun Configuration Procedures                                                                                           |

| MC68020UM(ADI) | Motorola 68020 CPU Manual                                                                                              |

| MVMEB.7/D2     | VMEbus Specification Manual, Rev. C, Feb. 1985                                                                         |

|                | SCSI Bus Specification                                                                                                 |

|                | Intel 82586 Ethernet Data Link Controller Technical Manual                                                             |

|                | HM-4619 Color Monitor Installation, Operation and Maintenance Guide                                                    |

|                | 19" Video Display Unit, Model M19P114A/5102 Service/Operator Manual, Phillips Electronics Ltd., Video Display Products |

## Sun-3/160 Functional Overview

| Sun-3/160 Functional Overview        |    |  |

|--------------------------------------|----|--|

| 1.1. The 2060 CPU Board              | 4  |  |

| 1.2. Memory Expansion Board          | 22 |  |

| 1.3. The 160C/160G Color Board       | 22 |  |

| 1.4. VME SCSI Board                  | 28 |  |

| 1.5. Optional Printed Circuit Boards | 31 |  |

| 1.6. Memory Subsystem                | 36 |  |

| 1.7. The Power Supply                | 37 |  |

| 1.8. Monitors                        | 40 |  |

## Sun-3/160 Functional Overview

This chapter describes the function of the basic Sun-3/160M, Sun-3/160C and Sun-3/160G components and their interaction. The physical appearance of models 160M,160C and 160G Workstations are identical, with the exception of hardware present in the Sun-3/160C that relates to the function of the color monitor, and in the Sun-3/160G that relates to the gray scale monitor.

The three models are therefore treated as one in this manual. Subsections that deal with components present only in the Sun-3/160C and 160G, such as the color video board, are included under headings such as *The 160C/160G Color Video Board*.

The Sun-3/160M, Sun-3/160C, and Sun-3/160G are all stand-alone workstations that include a 19-inch monitor, keyboard and mouse, and a deskside pedestal that houses the microcomputer, memory subsystem, power supply, and associated circuitry. Each model can function as a node in a local area network.

The list of applicable documents at the front of this manual refers to other sources of theory on components that are briefly described in this chapter.

This overview begins with the microcomputer boards that are housed in the 12-slot VME card cage inside the desk-side pedestal. The CPU and memory expansion boards are the heart of Sun-3 architecture, and are discussed first. Optional boards and the remaining major workstation subassemblies are described next.

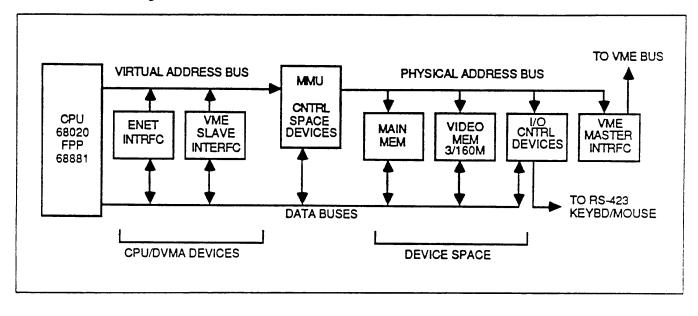

Figure 1-1 illustrates the relationship of the components discussed in this chapter, which are presented in this order.

- CPU board

- VME Implementation

- Memory Expansion Board

- Color Video Board

- □ VME SCSI Board

- VME/Multibus Adapter Board

- VME/VME Adapter Board

- Optional Graphics Processor Board

- Optional Graphics Buffer Board

- Memory Subsystem (Mass Storage and Interfaces)

- Power supply and Monitors

OPTIONAL GRAPHICS BUFFER .O MONITOR (160C) OPTIONAL GRAPHICS PROCESSOR OPTIONAL OTHER OPTIONAL BOARDS FPA BOARD BOARD (160 ONLY) TO MONITOR (160M) (150 ONLY) VMEBUS P1.P2 CPU BOARD VME-SCSI SCSI BUS MEMORY SUBSYSTEM TO/FROM ETHERNET

Figure 1-1 System Level Block Diagram

### 1.1. The 2060 CPU Board

The 2060 board is a single board computer that is housed in a 12-slot card cage inside the pedestal. Appendices A and B provide information on physical characteristics of the and backplane CPU board connectors.

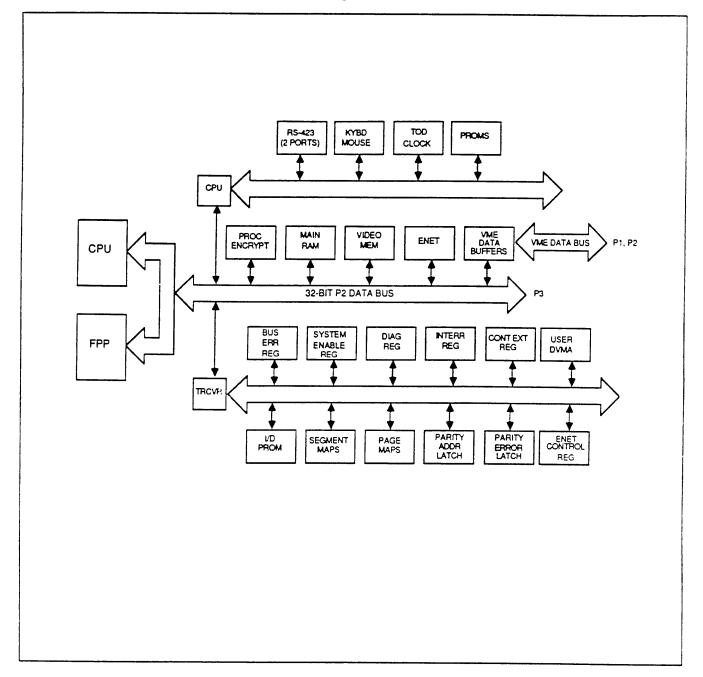

The board can be divided into functional blocks that are interconnected by the bus structure, as illustrated in Figure 1-2. Main 2060 board components are the MC68020 CPU, four Megabtyes of RAM, and interface circuitry that supports the VMEbus, Ethernet and serial ports.

This text provides a functional overview of these blocks in this order:

- D CPU Board Overview

- Bus Architecture

- CPU/DVMA Devices

- □ Memory Management Unit (MMU)

- Main Memory

- Video Control Circuitry

- Serial Interface logic

- Ethernet Interface logic

- VME Interface logic

Figure 1-2 CPU Board Overview

Figure 1-2 is a simplified block diagram of the 2060 CPU board. The CPU and DVMA devices depicted on the left side of the diagram supply virtual addresses to the MMU and arbitrate for control through the DVMA controller.

The MMU and control space devices (in the center of the diagram) are accessed in Function Code 3 space. Processor function codes further define virtual addresses and provide additional available address space.

The control space devices include processor extensions such as the bus error register, the system enable register, the diagnostic register, and the ID PROM.

The ID PROM stores basic information on the machine type; the node's unique 48-bit Ethernet address; a unique serial number for software licensing and distribution, the date the PROM was generated; and a checksum.

The MMU translates the virtual addresses into physical addresses to provide access to devices such as main and video memory, the VMEbus master interface, and I/O. It protects and manages these devices, and allows them to be shared.

The device space is divided into four types:

Type 0 — for main and video memory

Type 1 — for I/O and control devices (listed in MMU section)

Type 2 and 3 — for the VME master interface

2060 Bus Architecture

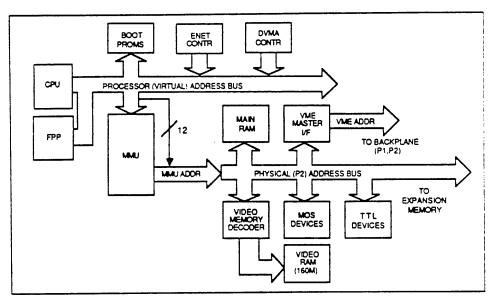

Figures 1-3 and 1-4 provide detailed diagrams of CPU board buses. The VMEbus interface is described in paragraphs following the Ethernet Interface subsection.

Data Buses

The 2060 board uses a 32-bit bus and two 8-bit buses for on-board data transfer. The 32-bit (P2) data bus provides a high-bandwidth path between both the CPU and DVMA devices and main memory. Two separate 8-bit buses segregate MOS and TTL devices.

MC68020 dynamic bus sizing capability facilitates longword moves along the 8-bit bus to the parity address latch and page map interfaces. The dynamic bus sizing mechanism allows the processor to transfer operands to or from external devices while automatically determining device port size on a cycle by cycle basis.

The 8-bit buses service these components:

Table 1-1 CPU Board 8-Bit Data Buses

|                                                          | MOS BUS                                                               | TTL BUS                                                                                                                       |

|----------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Device Space<br>Components                               | Keyboard/Mouse<br>RS423 Ports<br>Time of Day Clock<br>EEPROM<br>EPROM | Parity Error Register Parity Address Latch Ethernet Control Register Interrupt Register                                       |

| Control Space<br>Components<br>(Processor<br>Extensions) |                                                                       | I.D. PROM Segment/Page Maps Diagnostic Register User DVMA Register System Enable Register Bus Error Register Context Register |

Figure 1-3 Data Bus Block Diagram

Address Buses

The CPU directly addresses the FPP, MMU, and boot PROMs by way of the 32-bit processor address bus.

Buffered address lines from the processor and MMU buses become the P2 address bus. The P2 address bus services the VME Master Interface, the Data Cyphering Processor, TTL devices, MOS devices, as well as main, video, and expansion memory. Figure 1-4 depicts the address bus structure of the 2060 board.

Figure 1-4 2060 Board Address Bus

### CPU Logic and DVMA Devices

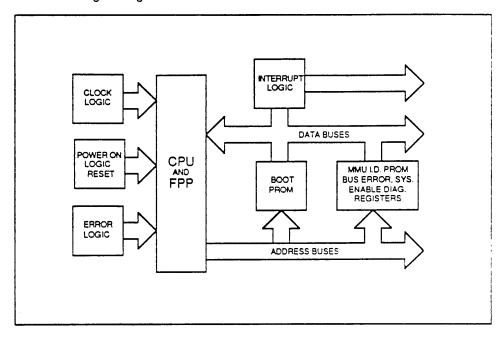

The functional blocks that comprise processor logic are shown in Figure 1-5, and discussed in the text that follows.

Figure 1-5 Processor Logic Diagram

The MC68020 CPU

The CPU board is based on the Motorola MC68020 virtual memory microprocessor, which runs at 16.67 Mhz and uses 32-bit addresses, as well as 32-bit registers and data paths. The CPU also features on-chip instruction cache and full IEEE floating point support (implemented with the 68881 FPP).

The MC68020 CPU uses sixteen 32-bit general-purpose data and address registers; a 32-bit program counter, a 16-bit status register, a 32-bit vector base register, two 3-bit alternate function code registers and two 32-bit cache handling registers.

On-Chip Cache Memory

The 256 byte direct mapped instruction cache is organized as 64 long-word entries. Each cache entry consists of a tag field made up of the upper 24 address bits, the Function Code 2 (user/supervisor) value, one valid bit, and 32 bits of instruction data.

The instruction cache stores a copy of previously executed instructions that are stored in main memory which effectively decreases main memory access time. The CPU first checks the cache for the next instruction; if the required instruction is found there, no instruction fetch is needed, thus increasing system performance.

### Floating Point Processor

The MC68881 Floating Point Processor chip is a customer option and is software enabled. The MC68881 can also optionally run on an independent clock.

The 32-bit floating-point co-processor is designed for operation closely coupled with the MC68020 CPU. It performs mathematical calculations in strict accordance with the proposed IEEE specification *P754*, *Revision 10*, which guarantees support for all required operations, data types, rounding modes and rounding precision.

The chip also provides root value, trigonometric, exponential, and logarithmic functions, to name a few. It calculates all operations to 80-bit precision and eliminates inefficiencies associated with executing software envelopes through hardware implementation.

## Optional Data Ciphering Processor

The Data Ciphering (Encryption) Processor (DCP) provides enhanced encryption capabilities that enable certification with governmental agencies. When used with the UNIX crypt utility, the encryption process is expedited.

To comply with U.S. Customs law, the DCP and its support PAL are socketed, and offered as a domestic option.

The algorithm processing unit of the DCP uses the National Bureau of Standards Data Encryption Standard (DES) to encrypt and decrypt data.

The chip supports three ciphering options:

- Electronic Code Book for disk applications

- Chain Block Cipher for high-speed telecommunications

- Cipher Feedback for low to medium speed, byte oriented communications.

Data bytes can be transferred through both Master and Slave ports on the chip, and key bytes can be written through Auxiliary and Master ports.

The Master Key, Encryption Key and Decryption Key each use a separate 56-bit, write-only key register. Eight-bit Mode, Command and Status registers provide MC68020 access through the Master Port.

**Processor Supporting Logic**

Logic supporting the MC68020 includes programmed array logic (PAL) chips that perform CPU space decoding, reset, bus error detection, data transfer acknowledge, and interrupt priority encoding/acknowledgment. Boot-up and diagnostic code is stored in 64Kbytes of erasable, programmable read-only memory (EPROM).

System Reset

The power-on/reset logic provides a means of starting a processor and/or system initialization sequence in response to fluctuations in supply voltage; a reset signal from an external bus or the watchdog reset switch; or a halt in the CPU processing cycle.

Power-on reset is active for a minimum 100 msec after the power supply voltage reaches 4.5V. Power-on reset results in the following:

- CPU Reset

- System Enable Register Clear

- Forced Boot State

- Diagnostic Register Reset (lights LEDs)

- FPP Reset

- □ Memory Error/Interrupt Register Reset

- □ Keyboard/Mouse; RS423 Port Reset

- VMEbus Reset

- Ethernet Interface Reset

- All State Machine PALs Reset

If the CPU board is jumpered to enable a VME bus arbiter other than the CPU board, the VME bus SYSRESET signal, initiated off-board, can cause a power-on reset.

A double bus fault that causes a CPU halt results in a watchdog reset, which results in execution of the PROM monitor program, or restart of system self-tests, depending on EEPROM programming. (Heading 2.9 in *Chapter 2* describes EEPROM programming.)

The User Reset Switch, located on the rear edge of the CPU board, provides a manual watchdog reset.

The 2060 board interrupt logic determines the priority of interrupt requests that are directed to the CPU from internal and external logic groups.

The various levels of VME interrupts are mapped to the corresponding on-board levels.

On-board interrupts receive higher priority than off-board VME interrupts at the same level. On-board interrupts are autovectored on all levels, with the exception of level 6, which represents the serial communications controllers (SCC)s. SCCs provide their own vector for functions such as transmit and receive, which eliminates time that interrupt software would take to determine which part of the SCC originated the interrupt.

Interrupt Logic

Priorities for on-board device interrupts are determined in this way:

| Level | Device                                 |

|-------|----------------------------------------|

| 7     | NMI - Real time clock and parity error |

| 6     | Serial controllers (8530A chips)       |

| 5     | Real Time Clock                        |

| 4     | Video vertical interrupt               |

| 3     | Ethernet - System enable register 3    |

| 2     | System enable register 2               |

| 1     | System enable register 1               |

The order in which boards are placed in the card cage determines off-board interrupt priority.

System Clocks

Two crystal oscillators provide a main system clock and an optional FPP clock.

The clock generator logic takes the main clock 33.33Mhz frequency and divides it by two, to provide timing for internal data processing. The PALs stretch the high part of processor cycle state 4 for an extra 30 nanoseconds, which allows more time for data to be returned to the processor and for data acknowledge turnaround. The resultant 16.67Mhz clock may also be jumpered to provide FPP timing.

A second, 25Mhz crystal provides, through a flip-flop, a 12.5Mhz clock which can be jumpered to the FPP clock or used for 12.5MHz system clock timing. The Configuration Procedures manual, Sun PN 813-2000 describes CPU board jumper settings.

The Real Time Clock

The Real Time Clock is an Intersil 7170 time-of day clock with battery backup. The clock interrupt signal causes an interrupt request on Level 5 or 7 through the interrupt register.

The Boot PROM

Boot-up and diagnostic code is stored in 64Kbytes of eraseable, programmable read-only memory (EPROM). The CPU uses the boot code during reset and "boot state". Boot code execution bypasses the MMU and determines that the CPU board is ready for initialization of the operating system or for execution of diagnostic code. Chapter 2, Diagnostics and Troubleshooting, describes the boot-up and self-test sequence.

The EEPROM

An electrically eraseable PROM stores parameters that determine the following:

- Which device is the system console or primary terminal during a non-diagnostic boot-up.

- From which device UNIX will be booted during a boot with the diagnostics switch set on NORM.

- The quantity of memory to be tested by boot PROM diagnostics during a non-diagnostic boot.

- □ Whether the console display size will be 900x1152.

- What will happen following a Watchdog Reset: a self-test restart or display of the PROM monitor prompt.

- The boot device used for a diagnostic boot, and the location of a selected diagnostics program.

- □ Whether the Sun logo or a custom banner is displayed during boot-up.

- □ Whether or not the keyboard "click" is enabled.

A record of the board and storage device types present in the system is also stored on the EEPROM.

The Diagnostics and Troubleshooting section of this manual provides instructions on EEPROM programming, which is done through the PROM monitor at this time.

Direct Virtual Memory Access

Direct virtual memory access (DVMA) allows devices to use the MMU to read from and write to memory. DVMA devices include the Ethernet interface, the VMEbus slave interface, and refresh circuitry.

A DVMA cycle is initiated when inputs from either the memory refresh logic, the Ethernet control or the VMEbus slave interface are synchronized and presented to the DVMA controller. The controller then generates a processor bus request and waits for a bus grant signal. The CPU issues the bus grant, which the DVMA controller acknowledges by asserting a bus grant acknowledge and removing the bus request.

The DVMA controller then determines the priority level of the request; sends a DMA enable signal to the requester, and, for VME slave or Ethernet requests, asserts the P2 DVMA address strobe. Following an acknowledge from memory or video circuitry, the transaction is ended with removal of the address strobe and bus grant acknowledge, and then the DMA enable signal.

DVMA handling for refresh circuitry differs slightly from that for other DVMA devices, in that the controller does not issue a P2 address strobe and waits for a special R.SSAS refresh signal rather than an acknowledge signal.

The refresh circuitry receives highest priority, followed by the Ethernet and VMEbus slave interfaces. The Ethernet interface can issue a HOLD signal along with the bus request to retain bus mastership for the 82586 FIFO circuitry.

A User DVMA Enable Register provides an external VME device with 256 MBytes of accessible memory for each of eight contexts.

User DVMA occurs with user function codes when a VME device accesses the top two gigabytes of 32-bit address space on the VMEbus, provided that the corresponding context is enabled in the User DVMA Enable Register.

User DVMA

### Memory Management

The memory management unit translates virtual memory addresses into physical ones. The MMU is composed of a user/supervisor context register, segment map RAMs, page map RAMs and associated logic, and allows devices to work in a shared and protected environment.

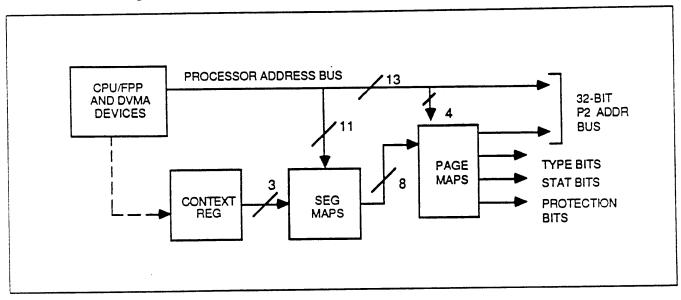

Figure 1-6 MMU Block Diagram

A context register appends three bits to the virtual address through the segment and page map RAMs to produce physical addresses.

The segment map RAMs use the context value, combined with a processor address, to produce a page map entry group (pmeg). The pmeg is, in turn, input to the page map RAMs, which generate an output composed of mapped address lines and a number of status and control bits. This output provides addresses to memory by way of the P2 address bus.

When an "s" protection bit is set for a page of memory, only supervisor accesses (for program or data fetches) are allowed. Otherwise, the memory address is accessible for user (application) as well as supervisor fetches.

Status and type bits further define and extend physical addressing capabilities. Status bits determine whether or not a page of memory has been accessed or modified in order to assist the swapping software.

Type bits divide memory addressing in this way:

Type 0: Main and Video Memory

Type 1: I/O and Control Devices

Keyboard/Mouse Interface

Serial I/O Ports

EEPROM

EPROM

Time of Day Clock

Parity Error Registers

Interrupt Register

Ethernet Control Register

Data Cyphering Processor

Type 2: 16-Bit Data VME Master Interface

Type 3: 32-bit Data VME Master Interface

## On-Board Main Memory Logic

Sun-3 memory architecture is based on the concept of virtual memory, in which only a small portion of the total logical address space is mapped onto the physical memory resident on the boards. The balance of the maximum available memory space is located either on a secondary storage device (e.g. a large capacity disk drive) or on the network, and accessed through the DVMA scheme.

When the CPU attempts to access a virtual memory address location that is not currently residing in physical memory, a page fault occurs, and the data is fetched from the secondary storage device.

Memory Refresh Logic

The refresh logic provides a refresh cycle for memory every 15.7 usec. This logic is composed of a PAL and a pair of counters. The first (8-bit) counter generates a clock pulse, which is used by the DVMA control logic to produce an enable signal for the second (refresh) counter. The refresh counter then sends a refresh address to memory.

Main Memory

Main memory consists of 144 256Kx1, 120 nsec DRAMs, divided into four 1Mbyte banks. (Additional memory resides on up to three memory expansion boards.) Sun Configuration Procedures manual) enables four megabytes of additional memory.

The main memory address decode logic, which includes RAS and CAS PALs, and a row/column multiplexer, determines which bank of memory is being addressed. Memory access occurs when the write data and the read/write control signals are valid at the same time that CAS is valid.

### Video Interface Logic

This discussion of 2060 board video logic applies only to the Sun-3/160M Workstation.

The Sun-3/160C and 160G use the color board (described in Subsection 1.3) to control the function of its color monitor.

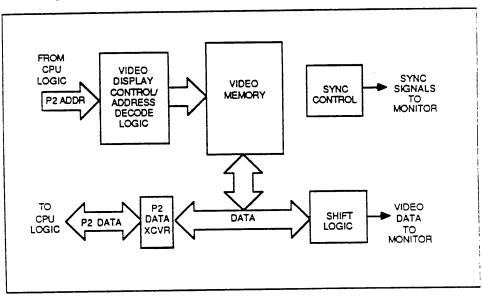

CPU board video logic generates and transmits differential ECL video signals, as well as TTL horizontal and vertical sync pulses, to the Sun-3/160M monochrome monitor. Video logic consists of video memory, with its associated control and address decoding circuitry, sync control logic and shift circuitry. Figure 1-7 provides a functional block diagram illustrating this logic.

Figure 1-7 Video Logic Block Diagram

Video Memory

Video memory is a 128K byte block configured as 16K, 64-bit words. The memory is dual ported to allow access by both the CPU and the video refresh logic.

The video memory bus provides a path for row and column address transmission from the CPU. Two address registers latch the addresses for input to video memory. A pair of address counters generate row and column addresses, which are latched and routed to memory for the video refresh cycle.

The video memory controller is a state machine that manages video memory operation. Memory controller outputs are used to select either the processor address or the video refresh address, allowing the controller to initiate any of three memory cycles: idle, processor update and video refresh.

A sequence of 16 states, continuously executed by the state machine, determines when the cycles are performed. Idle and processor update cycles are executed during the first eight states; the video refresh cycle is executed during the last eight.

Video Sync Control Logic

Video sync control logic is composed of horizontal and vertical state machines that generate horizontal and vertical sync signals, respectively. The video controller register latches state machine outputs, which are then transmitted to the video monitor.

Video Shift Logic

Video shift logic consists of a TTL-to-ECL converter and a 100MHz shift register. Video data is loaded from video memory into the TTL to ECL converter and clocked through the 100 Mhz shift register. The converter supplies differential ECL video to the monitor.

Serial Communications Interface

Two 8530 Serial Communication Controllers (SCCs) implement communication between the CPU board and the keyboard, mouse and the RS-423 interface.

One SCC is dedicated to the keyboard and mouse; the other to RS-423 communication. The SCCs function as Universal Synchronous/Asynchronous Receiver/Transmitters (USARTs) to serialize parallel data that is transmitted from the CPU board, and route it to the respective interfaces. The inverse is true for incoming serialized data.

Each SCC provides two high-speed, fully symmetrical, programmable serial channels with built-in baud rate generators.

The SCC that supports the Sun-3/160 RS423 interface supplies serial I/O from Channel A to the rear panel serial port A, and serial I/O from Channel B to to the serial port B. Channels A and B can also be shared for synchronous transfers.

The SCC that services the keyboard and mouse functions as an asynchronous receiver/transmitter, using Channel A for the keyboard, and Channel B for the mouse.

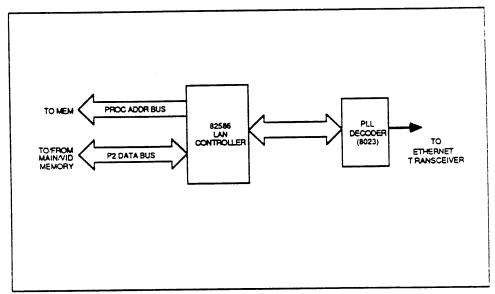

**Ethernet Interface**

The primary components of the Ethernet interface are an Ethernet controller PAL, an Intel 82586 Ethernet Data Link Controller (EDLC), phase locked loop encoding/decoding circuitry, and address and data buffers, which interact to provide the hardware necessary for communication between the Sun-3/160 and other nodes connected to the Ethernet. Figure 1-8 illustrates Ethernet interface logic.

Figure 1-8 Ethernet Interface

The Ethernet Controller PAL holds random Ethernet logic, handling functions such as transmission of P2 bus mastership requests to the DVMA controller.

The 82586 (EDLC)handles most of the functions associated with the data link and physical link layers of local area network (LAN) architecture. It performs frame boundary delineation, addressing, bit error detection, and link management functions.

The EDLC controller shares Sun-3/160 memory space and can issue a HOLD signal in order to retain bus mastership when necessary for its FIFO operation

The 82586 receives serial data and handles address recognition and CRC checking in its receive unit. Its command unit executes instructions that come from the MC68020 CPU through a reserved portion of memory.

The 8023 encoder, or front end chip, translates clock and data from the Sun-3/160 into a single, self-clocking serial data stream. The encoder drives the transmit pair of transceiver cables, using Manchester encoding, and places a preamble on the frame to allow channel circuitry throughout the network to become stable before receiving valid input. The decoder removes the preamble from incoming frames and translates the incoming serial data stream into clock and data for the EDLC to process.

The VMEbus interface provides bidirectional data access between the CPU board and any device connected to the VMEbus. The interface logic consists of bus arbitration and request circuitry, as well as logic that allows the CPU board to act as the bus master or as a bus slave. Figure 1-9 is a block diagram of VMEbus interface logic.

VMEbus Interface

P2 ADDRESS

VMEBUS

MASTER

INTERFACE

VME DATA

VMEBUS

SLAVE

INTERFACE

INTERFACE

Figure 1-9 VMEbus Interface

VMEbus Arbitration

Two PALs and a pair of registers monitor bus request levels and arbitrate requests, using a level daisy chain. When the CPU requests the bus (in order to perform a read/write cycle, or to acknowledge an interrupt), it sends a bus select signal to one of the PALs.

If the arbitration logic does not control the bus, it will assert a VME bus request signal to request bus mastership. If the arbiter currently controls the bus, it will retain control until another bus master requests it.

When the arbitration logic has attained VME bus mastership, the CPU may access any slaves on the bus through the VMEbus master interface. When the CPU relinquishes bus mastership, it becomes a bus slave, and may be accessed by other VMEbus masters, through the VMEbus slave interface.

VME Master Read/Write Cycles

During a VME Master read or write cycle, the type bits coming out of the MMU indicate either an access to Type 2 or Type 3 space (refer to the MMU subsection). VME address and data strobes are then generated, and the CPU board waits for a DTACK signal from the VME device being addressed. Upon receipt of data transfer acknowledge, the VME bus master will negate the address and data strobes, ending the transfer.

If the VMEbus does not return a data transfer acknowledge signal within 3.3usec, a short time-out occurs, during which the CPU rearbitrates for the P2 bus, allowing refresh or Ethernet devices to use the bus. The VME Interface is frozen until the suspended cycle can be rerun. If a P2 data transfer acknowledge does not occur within 256 tries, the CPU receives a bus error and the VME master controller enters idle mode, retaining bus mastership, and waiting for another VME select signal to come in.

VME Interrupt Acknowledge

During a VME interrupt acknowledge cycle, the VME bus master will acknowledge the interrupt and negate the address and data strobes. The interrupt acknowledge signal is transmitted to the cardcage, where it is daisy-chained to each of the boards resident there. Each board is polled, in turn, to determine which one is the source of the interrupt. When the board generating the interrupt is located, it drives a vector address onto the VME bus, along with the data transfer acknowledge signal.

VME Slave Mode

A VME slave mode cycle begins when an external device asserts a bus request. The arbiter eventually grants the VMEbus to the requesting device, at which point the device enables its addresses and data onto the VMEbus and asserts address and data strobes. The addresses are then latched on the CPU board.

The slave space decoders then look at the latched address. If the address refers to the CPU board, the decoders generate either a supervisor or user DMA signal that indicates that a valid access request has come from a VME slave.

A transfer request now tells the DVMA controller that the slave interface wants to use the P2 bus, and the controller in turn asserts a processor bus request. The transfer is enabled onto the P2 bus, and a memory read or write cycle occurs. after which the address strobe and DMA enable signals are removed, and a data transfer acknowledge is asserted.

VME Implementation

The tables that follow show how Sun-3/160 backplane circuitry and CPU board VME interface circuitry comply with the VMEbus Specification, and which options are implemented.

Table 1-2 Master Capabilities

| D32 MASTER 32/16/8 bit data   |

|-------------------------------|

| A32 MASTER (DYN)              |

| 32/24/16 bit addresses        |

| TOUT(737) 737 microsecond     |

| timeout period                |

| None                          |

| IH(1-7)(STAT) Levels 1-7,     |

| independently jumperable      |

| ROR R(3) Release on request,  |

| level 3                       |

| Releases BBSY after AS asser- |

| tion when releasing bus       |

| Will not release VMEbus dur-  |

| ing Read/Modify/Write         |

| Cycles                        |

|                               |

Table 1-3 Slave Capabilities

| Data bus Size       | D32 SLAVE (DYN)             |

|---------------------|-----------------------------|

|                     | 32/16/8 bit data            |

| Address Bus Size    | A32 SLAVE (DYN) 32/24       |

|                     | bit addresses (no 16-bit    |

|                     | addresses)                  |

| Sequential Access   | None                        |

| Special Access Mode | A high-speed access mode    |

|                     | is engaged if the time from |

|                     | DTACK assertion to the      |

|                     | next AS and DS assertion is |

|                     | less than 200ns.            |

| Interrupter Options | None                        |

Table 1-4 System Controller Capabilities

| Clock Option        | SYSCLK 16 Mhz, jumper-    |

|---------------------|---------------------------|

|                     | able (not used on board)  |

| Arbiter Option      | ONE Bus Request/Grant,    |

|                     | Level 3 only, or External |

|                     | Arbiter                   |

| Bus Time Out Module | None                      |

| Sysreset Option     | SYSRESET MASTER or SYS-   |

|                     | RESET SLAVE, including    |

|                     | manual button             |

| Sysfail Option      | Not monitored             |

| ACfail Option       | Not implemented (ACFAIL   |

|                     | is connected to SYSRESET) |

The table below shows which 96-pin connectors and rows of pins on the backplane service the VMEbus, and which serve the "P2" Physical Address Bus:

Table 1-5 Backplane Connector Function

| Connector | Row | Function |

|-----------|-----|----------|

| P1        | Α   | VME      |

|           | В   | VME      |

|           | С   | VME      |

| P2        | Α   | "P2"     |

|           | В   | VME      |

|           | С   | "P2"     |

| P3        | Α   | Power    |

|           | В   | "P2"     |

|           | С   | Power    |

# 1.2. Memory Expansion Board

The 2061 memory expansion board is available in two configurations, which provide either 2 or 4 MBytes of additional memory to the Sun-3/160 workstation.

Expansion memory is organized identically to the memory section of the 2060 CPU board. Memory address decoding is also virtually identical. Refer to the Sun Configuration Procedures, Sun PN 813-2000, for expansion board component layout and jumper select options and dip switch settings.

# 1.3. The 160C/160G Color Board

Both the Sun-2 and Sun-3 color board provide high resolution color graphics for the Sun-3/160C workstation. This board replaces the monochrome video logic resident on the CPU board, which is enabled only when a monochrome monitor is part of the workstation. The color board provides the Sun-3/160G monitor with 256 levels of white through the green and sync cables. Because color board function is basically the same for the Sun-2 and Sun-3 boards, the majority of this text applies to both versions, with references to minor variations when necessary.

The board is a bit-mapped graphics subsystem that features a 1152x900x8, 66Hz non-interlaced display; a frame buffer that appears as a million 8-bit-deep pixels that each define one-out-of-256 shades of red, blue or green; and 8-plane "RasterOp" support.

Color board logic is separated into the following functional blocks:

- VMEbus interface

- frame buffer logic

- memory timing and synchronization circuitry

- color maps

- digital-to-analog converters (DACs).

Figure 1-10 presents a functional block diagram of color video board logic.

ADDR ADDR REC VME ADD= VMEBUS INTERFACE LOGIC FRAME BUFFER LOGIC DATA GREE! VME DATA COLOR MAP AND DAC LOGIC BLUE 8 PLANE ROP MEM TIMING AND SYNC HORIZIVERT SYNC LOG:C

Figure 1-10 Sun-3/160C/160G Color Video Board Logic

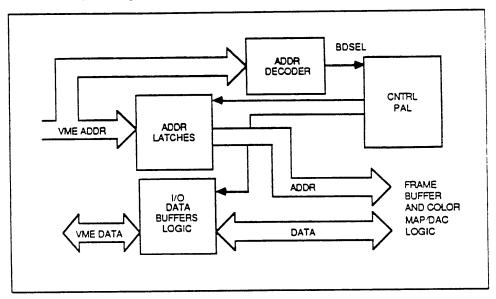

Color Board VMEbus Interface

The color board VME bus interface manages the transfer of VME bus addresses and data, and provides control signals to the frame buffer address decode circuitry. This logic operates asynchronously with the state machines and responds to VME bus read, write and interrupt acknowledge cycles.

The VME bus interface consists of address latches, data input and output buffers, an address decoder and a control PAL. Figure 1-11 provides a block diagram supporting the VME bus interface logic.

Figure 1-11 VMEbus Interface Logic

Frame Buffer Logic

Frame buffer logic consists of frame buffer memory, the address decode and generation circuitry, the video refresh logic and the RasterOp chips (ROPCs).

The Sun Configuration Procedures manual, Sun PN 813-2000, contains jumper setting information. Refer to Figure 1-12 for a block diagram of frame buffer logic.

FROM VMEBUS INTERFACE LOGIC ROPCS (FOR PLANES A-H)

ADDR ADDR LOGIC MEM ADDR

DATA

FRAME

BUFFER TO VIDEO

PIPELINE

A-H)

ADDR LOGIC MEM ADDR

Figure 1-12 Color Board Frame Buffer Logic

Frame Buffer Memory

The frame buffer is separated into eight planes, labeled A through H. The Sun-2 frame buffer consists of 128 64K nibble-mode RAM chips, while 32 64Kx4 Video DRAMs make up the Sun-3 frame buffer.

Frame Buffer Addressing

The frame buffer receives addresses from either of two sources: the VME address bus or the video refresh logic. During updates to the frame buffer memory, the VME address lines are multiplexed to form the CAS and RAS addresses.

Specific bits in the VME address are also used to select the possible addressing modes: word mode, pixel mode, or ROP mode. The word mode and pixel mode counters each generate an address, which, when selected, is driven to the frame buffer inputs. Video refresh memory cycles and inactive read/write cycles take their addresses from a pair of 16-bit counters and the Word-Pan Base Address register.

Address Modes

The data input to the frame buffer is dependent upon the frame buffer addressing mode. Ten addressing modes are available: word-mode memory, pixel-mode memory and four word and four pixel modes controlled by the RasterOp chips (ROPCs).

Raster and other operations that use less than eight bits per pixel use word mode accesses, while drawing, shading algorithms and other imaging related applications use pixel mode accesses.

Raster Op Modes

RasterOp means that rectangular areas of display data (Raster) are modified or combined according to a preselected operation (OP). ROP chips are used to speed the combination of text with graphics and the ROP modes provide the ability to access a variable number of planes or pixels within the frame buffer memory.

Either frame buffer memory or the VME data bus loads ROPC source registers, sometimes on a read and sometimes on a write.

Each memory plane in the frame buffer has a separate RasterOp unit. These units can function individually or in parallel to update as many as 128 frame buffer bits simultaneously. Data from the frame buffer is converted from TTL to ECL.

The DAC address inputs are connected to an internal color map, which translates the address to a 24-bit data value. The translated value drives three video DACs, whose outputs are routed to the red, green and blue BNC connectors.

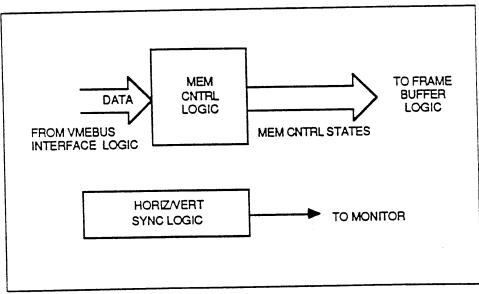

Memory Timing and Sync Logic

This logic group consists of the memory control logic (which controls the timing for the frame buffer memory) and the horizontal and vertical sync circuitry (which transmits horizontal and vertical sync pulses to the monitor). Figure 1-13 is a functional block diagram that illustrates this logic.

Figure 1-13 Memory Timing and Synchronization Logic

The horizontal and vertical sync circuitry is composed of a pair of state machines, which generate horizontal and vertical sync pulses for use by the monitor.

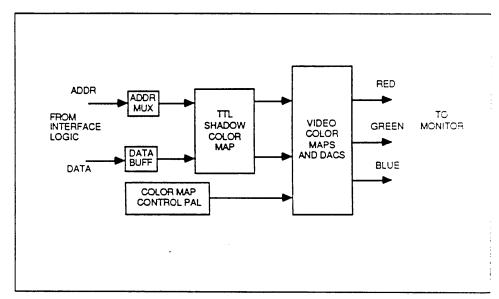

Color Maps and DACs

Color map and DAC logic consists of the color map video translation tables, the video digital-to-analog converters (DACs), the TTL shadow color map, the color map control PAL and associated circuitry. Figure 1-14 illustrates this logic.

Figure 1-14 Color Map and DAC Logic

The color map video translation tables and the video digital-to-analog converters are housed in a single hybrid ECL device. The DACs send red, green and blue color signals to the monitor.

The TTL color map consists of a pair of 1K x 4-bit static RAMs. Because of the real-time constraints involved in updating the internal ECL color maps, the TTL color map is used to provide read/write access. Transmission of TTL color mapped data and addresses to the ECL color map occurs during vertical retrace.

The VME address bus routes color mapped addresses to the TTL shadow color map. The shadow color map also receives 8 bits from the VME data bus. During the vertical blanking interval, data stored in the shadow color map is routed to the DAC color maps. The color map control PAL selects from the red, green or blue color maps.

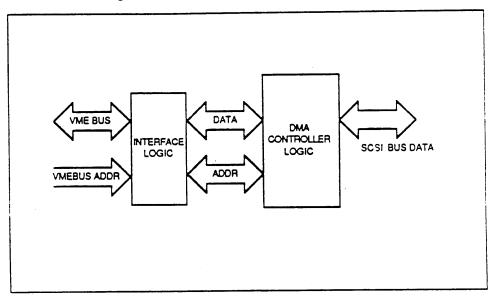

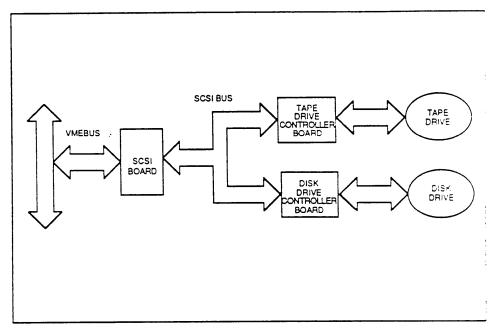

### 1.4. VME SCSI Board

The VME Small Computer System Interface (SCSI) board allows the Sun-3/160 to access the tape and/or disk drives that make up its internal memory subsystem. VME SCSI board logic is separated into two principle groups: the SCSI bus interface and the DMA controller. Figure 1-15 provides an overview of the VME SCSI board logic.

Figure 1-15 VME SCSI Board Logic

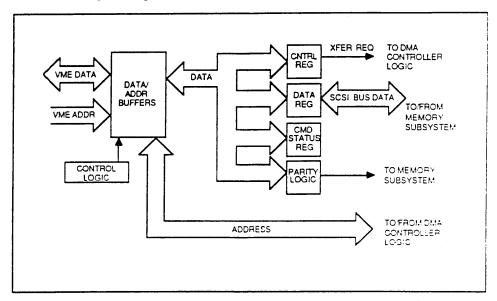

**SCSI Bus Interface Logic**

The SCSI bus interface logic consists of the interface control, data and command/status registers, as well as the parity logic and control circuitry. The SCSI bus interface logic is illustrated in the block diagram in Figure 1-16.

Figure 1-16 SCSI Bus Interface Logic

The interface control register manages the interface between the VME bus and the SCSI bus by means of 8 bits from the VME data bus and 8 control lines from the SCSI bus. The control lines and data bits are input to the control PAL, which generates control signals for use by the SCSI board. The original control and data bits are then buffered back onto the VME data bus.

The data register is used to transfer data between the VME and SCSI buses. The mechanics of data transfers between the VME bus and the 8-bit SCSI bus are described in the paragraph that discusses byte sequencing.

The command/status register transfers commands and status between the two buses. The command/status register is 8 bits wide on both the VME and SCSI bus sides.

The parity logic generates odd parity for data being output onto the SCSI bus and verifies the odd parity of incoming SCSI bus data. The control PAL latches parity errors and the control interface register buffers them back to the VME data bus.

The SCSI bus interface circuitry is responsible for byte sequencing, the SCSI bus request/acknowledge handshake and interrupt generation. This circuitry operates under the influence of two modes: DMA enable or word mode.

DMA enable mode determines whether or not data transfers use DMA. Word mode, when enabled, allows two SCSI data bytes to be transferred over the VMEbus at once. With word mode disabled, each byte of data requires its own separate transfer operation. During normal operation, both DMA and word mode are enabled.

Byte sequencing is used when word mode is enabled. It manages the transfer of data between the 8-bit SCSI bus and the VMEbus. SCSI data, to be output onto the VME bus, is "packed" into the data register two bytes at a time, allowing both bytes to be transferred over the VMEbus in a single operation. Incoming VMEbus data is "unpacked" in the correct order for transmission over the SCSI bus.

Each byte of data transferred over the SCSI bus requires a bus request/acknowledge handshake. The drive controller asserts a request signal and the SCSI interface logic responds with an acknowledge signal. An acknowledge is also asserted whenever the VMEbus accesses the data or command/status register.

Note that in word mode, half the data bytes are transferred over the VME bus without any register access and thus do not meet the criteria for the handshake. In this mode, the interface control logic generates an automatic acknowledge in response to the request.

The SCSI board will generate an interrupt during requests for status, messages or data with DMA enable mode off. The SCSI interrupt is driven onto the VME bus, which then responds with an acknowledge signal. The level of the acknowledge signal is compared to the SCSI board's interrupt level, with a successful match resulting in an interrupt acknowledge out signal being sent to the CPU board.

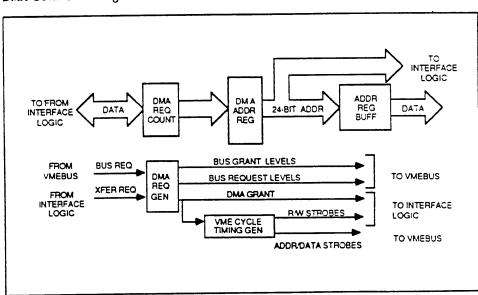

The DMA controller logic generates DMA addresses and timing signals for the SCSI board. This logic consists of the DMA address and count registers, the DMA cycle timing generator and the DMA request generation logic. Figure 1-17 is a functional block diagram that illustrates this logic.

Figure 1-17 DMA Controller Logic

The DMA count register is a 16-bit counter which may be written to or read from the VME bus. Its function is to determine how many bytes of data have been transferred utilizing DMA, and to enforce a maximum count. Sixteen bits of data

DMA Controller

are passed through the counter to provide inputs for the DMA address register. Because of the counter's tracking function, it increments in unison with the address register.

The DMA address register is 24 bits wide. It produces a 24-bit address from the 16-bit data bus by utilizing the lower 8 bits twice. The register output is placed on an internal address bus, where it is routed to both the VME address bus and the SCSI board's internal data bus.

The DMA cycle timing generator runs the DMA cycle. The generator is primarily composed of two PALs, which supply read/write strobes for the data register as well as data and address strobes for the CPU board.

The control register sends a transfer request signal to initiate a DMA request. This signal is input to the bus requester PAL, which then transmits the appropriate bus request level to the VME bus.

All bus arbitration capability for the SCSI board resides in the CPU board arbiter logic (refer to the CPU board functional overview). The CPU arbiter logic asserts a bus-grant-in signal at the appropriate level, which is presented to the bus requester PAL. The PAL then grants control of the bus to the SCSI board.

Refer to the Sun Configuration Procedures manual for select jumper options.

1.5. Optional Printed Circuit Boards

The VME/Multibus Adapter, Graphics Processor and Buffer Boards, and VME VME Adapter are among the optional boards that are offered as Sun-3 workstation enhancements. This subsection contains an overview of each of these boards.

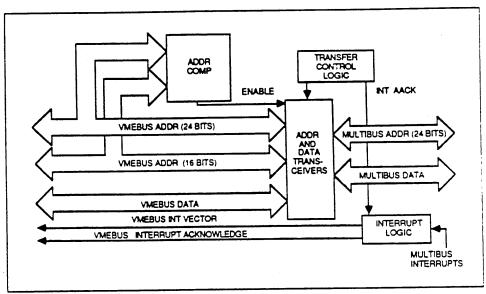

VME-Multibus Adapter Board The VME-Multibus adapter board allows Multibus boards to interface with the Sun-3/160 VMEbus. VME signals are routed through the adapter board logic, enabling Multibus boards to be written to, read from and interrupted. Refer to Figure 1-18 for a functional block diagram depicting this logic.

Figure 1-18 VME-Multibus Adapter Board Logic

The adapter board may be configured to respond to blocks of addresses in both the 24- and 16-bit VME address spaces. Dip switches on the adapter board set base addresses for these address blocks. Refer to the Sun Configuration Procedures Manual, Sun PN 813-2000, for information on dip switch settings.

Incoming VME bus addresses are checked to determine if they are within the dip switch selected block of addresses. A valid address initiates a data transfer sequence.

Data is transferred between the VMEbus and Multibus through a bank of bidirectional data transceivers. The data may be transferred either as a 16-bit word or as an 8-bit byte.

All adapter board data transfers, as well as the bus request/bus grant handshake, are controlled by a group of PALs. These PALs receive bus control signals from both the VMEbus and Multibus.

The adapter board must translate VMEbus vectored interrupts, even though Multibus does not support them. The adapter board generates a vectored interrupt by means of DIP switch settings. The interrupt occurs when the Multibus board interrupts on only one level or if a multi-level interrupt vectors to the same place. If the Multibus board interrupts on more than one level and a separate vector is required for each level, a PROM generates the vector.

Adapter board jumpers enable bus and constant clock signals for Multibus boards that require them. Refer to the Sun Configuration Procedures Manual, Sun PN 813-2000, for jumper options.

VME-VME Adapter Board

The VME-VME adapter board functions as an interface between triple-height and double-height board configurations. There are no components on the board.

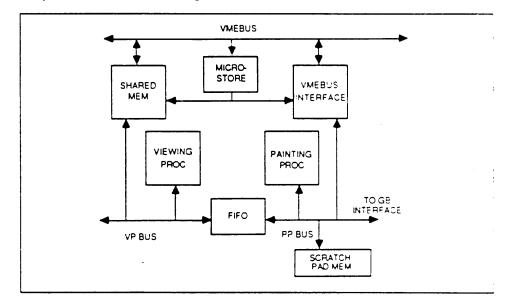

The 160C Graphics Processor Board

The optional Graphics Processor (GP) board is designed to enhance the graphics performance of the Sun-3/160C. The GP runs in parallel with the host processor (located on the CPU board) and performs many of the image display tasks currently done by the host, while remaining under host processor control.

Graphics Processor board logic is designed as two pipelined processors: the viewing processor and the painting processor. These processors, along with their associated logic, are illustrated in Figure 1-19.

Figure 1-19 Graphics Processor Board Logic

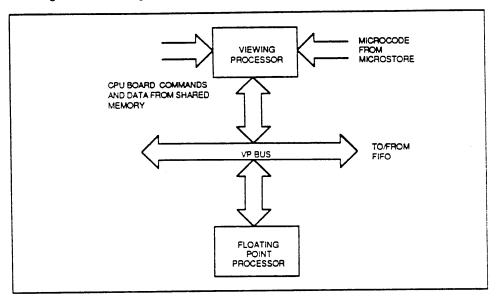

Viewing Processor

The viewing processor is made up of two devices: one that interprets commands from the host processor, and one that performs the floating point operations required to translate the image from real world coordinates to screen coordinates. Refer to Figure 1-20 for a block diagram illustrating viewing processor logic.

Figure 1-20 Viewing Processor Logic

The CPU board and viewing processor use GP board shared memory to exchange commands and data. This memory is made up of 16K x 16 dual-ported static RAM. Information and instructions are passed between the various logic components of the viewing processor by way of the 16-bit VPBUS.

Painting Processor

The painting processor is used to transfer the graphic data, in pixels, into the frame buffer on the color video board. Painting processor logic includes the processor itself, the VME bus interface logic, the scratchpad memory and the optional Graphics Buffer board. Refer to Figure 1-21 for a block diagram of painting processor logic.

**VMEBUS INTERFACE MICROCODE** FROM MICROSTORE SCRATCH-PAD MEM **PAINTING PROC OPTIONAL GRAPHICS** BUFFER BOARD TO/FROM PP BUS **FIFO**

Figure 1-21 Painting Processor Logic

The painting processor uses the board's VMEbus interface logic to access the color board's frame buffer. While the VME interface is primarily used as a link between the GP and the color board, it may be used to access any other device on the VMEbus, including the host memory and the viewing processor's shared memory. The VMEbus interface also allows the GP board to generate and transmit an interrupt to the host processor.

Static RAM scratchpad memory is provided by 4Kx16 bit static RAM chips, and used to perform various algorithms necessary to painting processor function.

The 16-bit PPBUS transfers commands and data between the various painting processor components.

Processor Associated Logic

Viewing processor and painting processor logic share microstore logic and the FIFO buffer. Refer to the overview of the GP board logic in Figure 1-19 for an illustration of the relationship of this logic to the processors.

Microstore logic holds microcode for both the viewing and the painting processors. The two processors run 180 degrees out of phase, and therefore may share the microstore. A third port is available to allow access through the VME bus, but is active only when both the viewing and painting processors are halted.

The FIFO buffer is the pipeline mechanism between the viewing and painting processors. It provides 512 x 16 bits of transfer storage and is "reversible", allowing data to be transmitted back and forth between the VPBUS and the PPBUS.

The Sun Configuration Procedures manual contains jumper and switch settings for various GP and GB configurations.

# The 160C Graphics Buffer Board

The graphics buffer (GB) board facilitates graphic applications that require the generation and display of solid images. This board consists of 2Mbytes of dynamic RAM, a 16-bit integer multiplier and a PROM for the storage of numerical constants.

The dynamic RAM is used in graphic operations such as the hidden surface elimination algorithm, which require large amounts of storage. The integer multiplier and its associated PROM increase the performance of advanced shading operations.

The graphics processor board and graphics buffer board communicate over the PPBUS. This bus is extended to the buffer board, which allows the painting processor to access GB board logic.

The Sun Configuration Procedures manual contains jumper and dip switch settings for various GP and GB configurations.

# 1.6. Memory Subsystem

The Sun-3/160 internal memory subsystem provides mass storage in these configurations:

- One Disk Drive and One 1/4-inch Tape Drive

- □ Two Disk Drives and One Tape Drive

- One or Two Disk Drives with no Tape Drive

- □ Tape Drive only

The disk drive is a 5 1/4" winchester with an 85 MByte unformatted storage capacity. The tape drive type is a 9-track, streaming tape, with 45 MBytes of storage capacity.

Separate drive controller boards in the option tray allow communication between the drives and the VME SCSI board that resides in the system cardcage. Figure 1-22 illustrates the memory subsystem and its relationship to the Sun-3/160.

Addition of large capacity disk drives requires external integration and an SMD controller board. Information on these other mass storage options may be found in the Sun Hardware Options Guide, Sun PN 813-1000.

Figure 1-22 Memory Subsystem