# USER'S GUIDE TO THE GENERIC BUS INTERFACE

June 1986

# USER'S GUIDE TO THE GENERIC BUS INTERFACE

June 1986

This document was prepared by the Graphics Division of Symbolics, Inc.

The software, data, and information contained herein are proprietary to, and comprise valuable trade secrets of, Symbolics, Inc. They are given in confidence by Symbolics pursuant to a written license agreement, and may be used, copied, transmitted, and stored only in accordance with the terms of such license.

This document may not be reproduced in whole or in part without the prior written consent of Symbolics, Inc.

Copyright (c) 1986 Symbolics, Inc. All rights reserved.

Symbolics, Symbolics 3600, Symbolics 3670, Symbolics 3640, SYMBOLICS-LISP, ZETALISP, MACSYMA, Document Examiner, S-DYNAMICS, S-GEOMETRY, S-PAINT, and S-RENDER are trademarks of Symbolics, Inc. PDP-11, UNIBUS, and VAX are trademarks of Digital Equipment Corporation. MULTIBUS is a trademark of Intel Corporation.

Restricted rights legend.

Use, duplication, or disclosure by the government is subject to restrictions as set forth in subdivision (b)(3)(ii) of the Rights in Technical Data and Computer Software Clause at FAR 52.227-7013.

Printed in the USA.

# TABLE OF CONTENTS

| INTRODUCTION              | i          |

|---------------------------|------------|

|                           |            |

| GBI ARCHITECTURE          | , <b>1</b> |

| Interface                 | 1          |

| How the 3600 Sees It      | 3          |

| Interrupts                | 4          |

| MULTIBUS Option           | 4          |

| UNIBUS Option             | 5          |

| Address Map               | 5          |

| 68000 Processor           | 6          |

| Devices and Addresses     | 7          |

| Gbus Memory Space         | 7          |

| Gbus I/O Space            | 8          |

|                           |            |

| INSTALLATION              | 13         |

|                           | 10         |

| MULTIBUS                  | 13         |

| UNIBUS                    | 22         |

| Software                  | 27         |

|                           | _,         |

|                           |            |

| PROGRAMMING THE GBUS      | 29         |

|                           |            |

| GBI Software              | 29         |

| Flavor gbus-interface     | 29         |

| Bus Cycle Error Flavors   | 32         |

| Control Word Messages     | 33         |

| Use of Buffer Memory      | 37         |

| Buffer Memory Messages    | 37         |

| Flavor unibus-interface   | 39         |

| Serial Ports              | 43         |

| Parallel Port             | 44         |

| Defining Peripherals      | 45         |

| Other Kinds of Interfered | 47         |

# **APPENDIXES**

|      |            | UNIBUS Registers, Interrupts, and Priorities<br>Parallel and Serial Port Connectors | 51<br>59 |

|------|------------|-------------------------------------------------------------------------------------|----------|

|      |            | -Assembler for the Gbus MC68000 Processor                                           | 67       |

|      |            | Symbolics 4-Slot MULTIBUS Card Cage and Backplane                                   | 75       |

|      | INDEX      |                                                                                     | 79       |

|      |            |                                                                                     |          |

|      |            |                                                                                     |          |

| LIST | OF ILLUS   | TRATIONS                                                                            |          |

|      |            |                                                                                     |          |

|      | Figures    |                                                                                     |          |

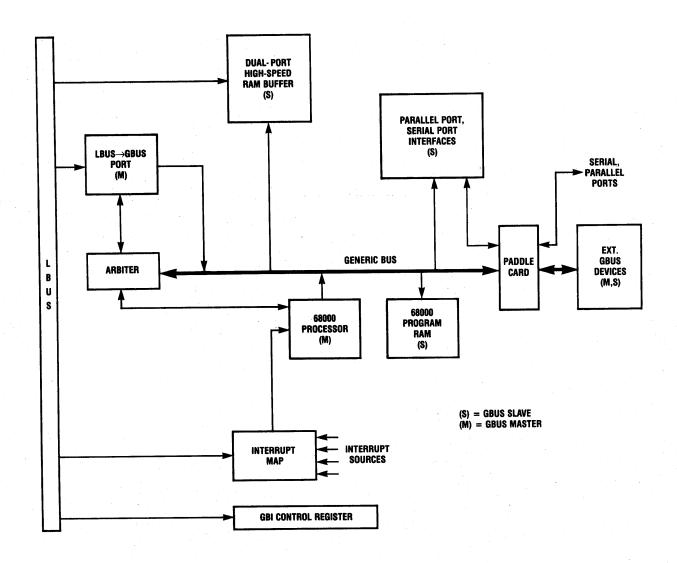

|      | Figure 1.1 | Logical relationship of devices on the Gbus                                         | 2        |

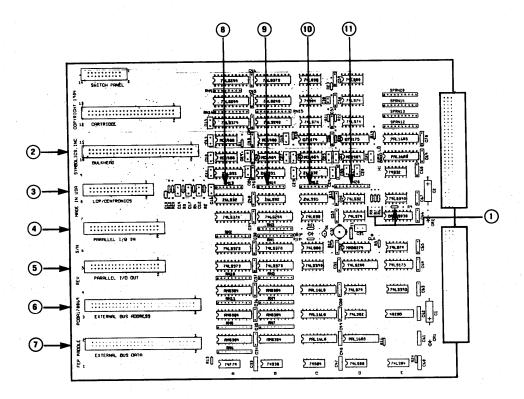

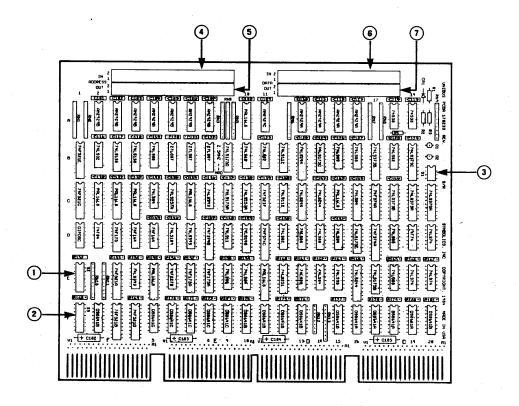

|      | Figure 2.1 | Gbus paddle board                                                                   | 14       |

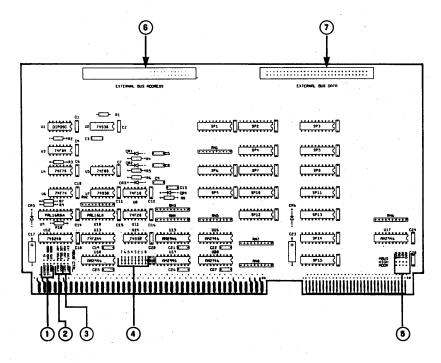

|      | Figure 2.2 | MULTIBUS interface board                                                            | 16       |

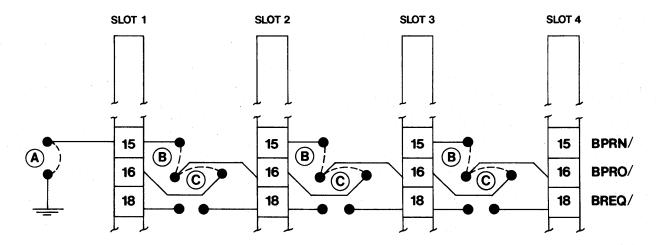

|      | Figure 2.3 | Symbolics 4-slot MULTIBUS backplane, front view                                     | 19       |

|      | Figure 2.4 | UNIBUS interface board                                                              | 23       |

|      | Figure A.1 | UNIBUS address map register                                                         | 57       |

|      |            |                                                                                     |          |

|      | Tables     |                                                                                     |          |

|      |            |                                                                                     |          |

|      | Table B.1  | Gbus-to-Centronics device pin connections                                           | 60       |

|      | Table B.2  | 16-bit parallel-in cable pins                                                       | 62       |

|      | Table B.3  | 16-bit parallel-out cable pins                                                      | 63       |

|      | Table D.1  | Pin assignments on MULTIBUS backplane P1 connectors                                 | 75       |

### INTRODUCTION

This document describes the *Generic Bus Interface* (GBI). Both hardware and software are covered as well as specific examples and suggestions covering several kinds of applications. This document also includes installation instructions for both hardware and software.

This document is divided into the following chapters:

- 1. "GBI Architecture" provides a physical description of the GBI and includes a block diagram to show the logical location of devices on the *Generic Bus* (Gbus).

- 2. "Installation" is divided into hardware and software installation; hardware installation includes jumper connections and DIP switch settings. Diagrams of the interface boards are included.

- 3. "Programming the Gbus" describes the Lisp messages and flavors used to control devices on the Gbus.

- 4. Several appendixes are included. Appendix A describes the available hardware registers and the values to which they can be programmed. Appendix B lists the pinouts used for connecting the GBI to serial or parallel devices other than UNIBUS or MULTIBUS. Appendix C describes how to use the 68000 assembler provided on the Gbus system tape. Appendix D gives specific information about pin assignments on the Symbolics-manufactured MULTIBUS backplane.

In this document, the term 3600 refers to any member of that family of computers unless specifically contrasted or compared with other specific model numbers (such as 3670).

Although the term Gbus refers specifically to the external Gbus (the 60-conductor ribbon cable that connects to the UNIBUS or MULTIBUS interface board), it is also used to refer to the entire package of GBI boards and cables.

### GBI ARCHITECTURE

#### Interface

The architecture of the Generic Bus Interface package can be more easily understood by making a logical separation at the rear bulkhead of the 3600. Installed within the 3600 backplane is the *Generic Bus Interface* (GBI), consisting of an Lbus board and a paddle board. Extending from the bulkhead is the *Generic Bus* (Gbus, or sometimes *external Gbus*), a pair of 60-conductor ribbon cables that connects the GBI to a UNIBUS or MULTIBUS interface board installed in the backplane of an external system.

The GBI forms the interface between the high-speed Lisp Machine world and the slower, asynchronous world supported by devices with UNIBUS or MULTIBUS backplanes. Through this interface, which supports UNIBUS and MULTIBUS backplane interface boards, the Symbolics 3600 can originate cycles on the Gbus, and both the 3600 and bus masters on the external bus have read-write access to a dual-ported memory buffer on the GBI.

The GBI consists of two boards that are installed in the Lisp Machine: a 16" x 18" Lbus board and a paddle board. Software is included for the GBI. An optional 68000 microprocessor is available for the GBI and can be used to manage Gbus devices when fast response to external events is required. An assembler is provided with the Gbus software for use in programming this optional 68000.

The external Gbus consists of a pair of 60-conductor ribbon cables that connects the GBI to the external device. It is an asynchronous bus functionally similar to that specified by the MULTIBUS standard. (For background on the MULTIBUS, refer to Intel MULTIBUS specification, Intel part no. 9800683-4.) Although the internal circuits of the GBI are buffered electrically from the external Gbus by the paddle board, the external Gbus is logically the same as the bus internal to the GBI.

The data path is 16 bits wide; the Gbus can handle either 8- or 16-bit transfers (the number of bits is specified by the bus master when the cycle is initiated). Like the MULTIBUS, Gbus address space is divided into memory and I/O: memory address space is 1 Mbyte (optionally 16 Mbytes) and I/O address space is 64 Kbytes.

The block diagram on the next page shows the major functional components of the Gbus. As shown in this diagram, the Gbus has master and slave devices. A master device can request and gain control of the bus; a slave is accessible for read or write operations by a bus master.

Figure 1.1 Logical relationship of devices on the Gbus

A master can initiate either a read or a write cycle in memory space or I/O space, using the messages :memory-read, :memory-write, :io-read, and :io-write. The master devices on the Gbus are the Lbus—Gbus port and the optional 68000 processor. The other devices, including the 68000 program RAM as well as parallel- and serial-type interface devices, are slaves. The UNIBUS interface board has slave devices on it. Each slave is assigned a specific address on the bus. A slave can be either some sort of memory or an I/O device such as a UART.

Both slave and master devices can exist within the external UNIBUS or MULTIBUS backplane. However, master devices on the external backplane must observe the following two restrictions:

- 1. The 3600 does not permit external processors to have direct memory access (DMA) to 3600 memory. Communication between the 3600 and the external device must take place in one of two ways: by either the Gbus or the external device using the dual-ported memory on the Gbus interface board; or by the 3600 doing bus cycles.

- 2. The Gbus cannot interrupt the 3600. Neither 3600 hardware nor software supports interrupts. The 3600 must poll the state of the Gbus and/or external devices to determine interrupt status. The 68000, however, does field interrupts and is recommended for real-time response to external stimuli.

### How the 3600 Sees It

The 3600 can use the Lbus→Gbus port to initiate cycles on the Gbus by executing functions provided in the support software. In this way, the 3600 can read from or write to any slave device on the Gbus and any attached external bus. The 68000's program memory is accessed in this manner.

The 3600 can also directly read from and write to the dual-port high-speed RAM buffer as its own memory. A displaced array can be made to point to the buffer. This array can be used as any normal array would be. High-speed data transfers between external bus masters and the 3600 are made using the buffer. In the example of a UNIBUS option and a DR11-W DMA controller, the 3600 sets the device's registers using the Lbus—Gbus port, causing it to transfer data to or from the buffer.

# Interrupts

Although it is not possible to interrupt the 3600 or to access 3600 memory directly from the Gbus, interrupts can be handled by interrupting the 68000 processor. Interrupting the 68000 processor is the preferred method for dealing with devices or problems that require very fast response. The 68000 can respond to an interrupt request in approximately 6 microseconds, from assertion to executing the first instruction of the service routine.

Fifteen interrupt sources are on the Gbus: seven "external bus" interrupts, plus eight from devices on the board. Interrupt requests from external devices can be stored in a 2K x 8-bit RAM called the *interrupt map*, where the 3600 can then read and determine the type and priority of the incoming interrupt request. A macro for defining this interrupt map is provided in the Gbus software and is described on pages 35 and 36.

# **MULTIBUS Option**

With the MULTIBUS interface board, the Gbus can be connected to a MULTIBUS backplane, which can be either in an existing computer system or in a card cage with various MULTIBUS devices.

Since Gbus address space is logically the same as MULTIBUS address space, the MULTIBUS interface board performs only electrical buffering. With a MULTIBUS interface board, it is as if the Gbus is directly connected to the backplane, with no address mapping or restriction. Bus masters in the MULTIBUS backplane can access any slave on the Gbus board, including the buffer and 68000 program memory. Both the 3600 (through the Lbus—Gbus port) and the 68000 can access any slave on the MULTIBUS backplane. The MULTIBUS interface board can be jumpered to supply the bus-clock signals if necessary (see step 4 of MULTIBUS installation on page 15).

When designing or installing a Gbus/MULTIBUS system, be especially careful of address assignment conflicts between slave devices on both sides of the bus. Do not assign MULTIBUS devices to any of the addresses assigned to Gbus devices or designated "reserved" in the section "Devices and Addresses" (see page 7). In addition, caution must be exercised when interfacing MULTIBUS devices that use only 8 bits of I/O addressing. The MULTIBUS interface board does not decode any of the I/O address bits, so MULTIBUS devices that use only 8 I/O address bits should be assigned only addresses 0 through 177 (octal).

# **UNIBUS Option**

The UNIBUS interface board interfaces the Gbus with a UNIBUS backplane in either an existing computer system or a card cage containing only I/O devices.

An 18-bit range of Gbus addresses is mapped directly into UNIBUS, and access of an address in that range initiates a UNIBUS cycle. A 15-bit (16-Kword) range of UNIBUS addresses can be mapped via a set of software-settable mapping registers to either Gbus memory or I/O space. The mapping registers can be set from either side. The actual UNIBUS address of the mapped area is set by switches on the interface board, and the size of the mapped area is likewise selected.

You can configure the UNIBUS interface board to be the *primary CPU* in the backplane. The primary CPU fields interrupts and arbitrates bus mastership. The UNIBUS cannot interrupt the 3600, but it can interrupt the 68000 processor. When the UNIBUS interface board is not the primary CPU, it can, under the control of a Gbus master, generate interrupts of specified vectors and priorities.

The registers, interrupts, and priorities of the UNIBUS interface board are described in Appendix A--"UNIBUS Registers, Interrupts, and Priorities."

### Address Map

The address map is accessible in UNIBUS address space at a location that can be switch-programmed anywhere above 760,000(8). The Map Register Address DIP switch on the interface board is provided to select the address offset. (See page 24 for the settings.)

The map must be accessed in word mode.

Switches 7 and 8 (size 1 and size 0, respectively) select the size of the mapped area. The choices are 4, 8, 16, and 32 Kbytes. Each 2-Kbyte segment has a map register. When less than the full mapped area is selected, only the first map registers are used, for example, when 4 Kbytes are mapped, the first two map registers are used. See page 25 for instructions on setting these switches.

The UNIBUS Select DIP switch locates the mapped portion of UNIBUS address space. Six switches select the high 6 bits of the address of the mapped area (see page 25). The mapped area can be placed anywhere in UNIBUS address space.

### 68000 Processor

The 68000 processor on the Gbus works like any other 68000 processor, with the following peculiarities:

- The very top 64 Kbytes of the 68000's 24-bit address space map into Gbus I/O space. The base address of 68000 I/O space is 77,600,000(8), or FF0,000(16).

- Byte addressing is reversed from standard 68000 practice. That is, when doing a byte transfer when address bit <A0> is cleared, data bits <0-7> are selected; when <A0> is set, data bits <8-15> are selected. This byte-addressing scheme is compatible with DEC processor practice, as opposed to Motorola (and IBM-360) practice and should be noted when trying to port programs from other 68000 processors.

- All interrupts are auto-vectored. The three interrupt lines to the 68000 come from the three high-order outputs of the interrupt map.

- The 68000 processor uses an 8-MHz clock. Reads of the 68000 program memory occur with no wait states; writes cause one wait state. Reads and writes of all other Gbus devices cause at least one wait state; the exact number varies from device to device.

A watchdog timer is included on the GBI; the timer can be enabled and disabled under control of the 3600. When enabled, the 68000 processor must perform a write to a certain I/O space address at least once every 8 seconds, or the timer asserts 68000 Reset.

### **Devices and Addresses**

The Gbus address space, for historical reasons, supports a 20-bit memory-space addressing mode. In this mode, the high 4 bits of any Gbus memory-space address are ignored. A setting in the control register enables or disables 20-bit mode. If full 24-bit addressing is used, the high-order 4 bits for the address comparison are taken from a field of the control register. If the MULTIBUS option is used with an existing computer system, you almost certainly want to use full 24-bit addressing. Gbus masters always generate 24-bit addresses, so care should be taken in assigning addresses of I/O devices if the MULTIBUS option is used in a standalone backplane. The functions in the supplied software always take high-address bits into account when addressing the on-board slave devices.

# Gbus Memory Space

Note that the following addresses are 20-bit addresses. If 24-bit addressing is enabled, the following are offsets within the 24-bit address space. In that case, the 4 high-order bits are determined by the high-address-bit field in the control register (see :enable-hi-addr message on page 34). Addresses are in octal.

| 0 - 377,777           | 128 Kbytes reserved for 68000 program RAM.                                                            |

|-----------------------|-------------------------------------------------------------------------------------------------------|

| 400,000 - 1,377,777   | Reserved.                                                                                             |

| 1,400,000 - 1,777,777 | Dual-port high-speed buffer.                                                                          |

| 2,000,000 - 2,777,777 | UNIBUS option, if present. Memory cycles made to this block of addresses are performed on the UNIBUS. |

Note: The UNIBUS option decodes only the low 20 address bits and so does not function correctly when 24-bit addressing is enabled.

When the MULTIBUS interface board is used, Gbus and MULTIBUS address spaces are the same. When the Gbus is used in a currently operating computer system, it might be wise to set the high-address-bit field of the control register to some nonzero value to avoid collision between the computer's low-address memory and the 68000 program RAM. In such an installation it seems unlikely to be using the on-board 68000, so moving the 68000 program memory should not be a problem.

# Gbus I/O Space

The location of the I/O device registers on the GBI depends on the setting of the high-address-bit field of the control register. The base address for the devices is 140,000(8) plus 1,000(8) times the high-address bits. The following addresses are in octal.

| High-Address Bits <a20-a23></a20-a23> | I/O Base Address |

|---------------------------------------|------------------|

| 0                                     | 140,000          |

| <b>1</b>                              | 141,000          |

| 2                                     | 142,000          |

| :                                     | :                |

| 15                                    | 155,000          |

The offsets given on the next page are added to the base address in order to obtain the device-specific address. Hence, when high-address bits contain 0, the first serial port device register is at 140,200(8).

See Appendix A--"UNIBUS Registers, Interrupts, and Priorities" for addresses and bit assignments of I/O devices on the UNIBUS interface board.

# Serial Ports (Byte mode only)

Refer to Intel 8274 Data Sheet for programming information for the Multi-Protocol Serial Controllers (MPSC).

| Offset(8)                | Register                                                                                                                                                                                                      |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 200<br>201<br>202<br>203 | MPSC A Channel A Data MPSC A Channel B Data MPSC A Channel A Control MPSC A Channel B Control                                                                                                                 |

| 204<br>205<br>206<br>207 | MPSC B Channel A Data MPSC B Channel B Data MPSC B Channel A Control MPSC B Channel B Control                                                                                                                 |

| 342                      | Serial Clock Control  Bit <4> MPSC A Channel A Ext Clock Enable (1 = Enable)  Bit <5> MPSC A Channel B Ext Clock Enable  Bit <6> MPSC B Channel A Ext Clock Enable  Bit <7> MPSC B Channel B Ext Clock Enable |

| 354                      | Serial Baud Rate (word mode only; write only) Bits <0-3> MPSC A Channel A Baud Bits <4-7> MPSC A Channel B Baud Bits <8-11> MPSC B Channel A Baud Bits <12-15> MPSC B Channel B Baud                          |

# Each four-bit field is coded as follows:

| Value(8) | Baud Rate |

|----------|-----------|

| 0        | 50        |

| 1        | 75        |

| 2        | 110       |

| 3        | 134.5     |

| 4        | 150       |

| 5        | 300       |

| 6        | 600       |

| 7        | 1200      |

| 10       | 1800      |

| 11       | 2000      |

| 12       | 2400      |

| 13       | 3600      |

| 14       | 4800      |

| 15       | 7200      |

| 16       | 9600      |

| 17       | 19 200    |

# Parallel Port (Word mode only)

| Offset(8) | Register                      |                                |

|-----------|-------------------------------|--------------------------------|

| 370       | Data bits<br>16-bit interface |                                |

|           | Bits <0-15>                   | Parallel Port Data 0-15 In/Out |

|           | 8-bit interface               |                                |

|           | Bits <0-7>                    | Parallel Port Data 0-7 In/Out  |

|           | Bits <8-13>                   | Not used                       |

|           | Bit <14>                      | Select (read only)             |

|           | Bit <15>                      | Paper Empty (read only)        |

| 372       | Control bits                  |                                |

|           | Bit <0>                       | Data Out Accepted (read only)  |

|           | Bit <1>                       | Data In Ready (read only)      |

|           | Bit <2>                       | Start Write Transfer           |

|           | Bit <3>                       | Not used                       |

| ,         | Bit <4>                       | Data In Ready Interrupt Enable |

|           | Bit <5>                       | Need Data Interrupt Enable     |

|           | Bit <6>                       | Spare Write Signal             |

|           | Bit <7>                       | Spare Read Signal              |

|           |                               |                                |

# Other Registers

| Offset(8) | Register                                            |                                                                                    |

|-----------|-----------------------------------------------------|------------------------------------------------------------------------------------|

| 210-213   | Reserved                                            |                                                                                    |

| 240 - 277 | Paddle Board ID Prom (read only)                    |                                                                                    |

| 340       | 68000 Control Regi<br>Bit <0><br>Bit <1><br>Bit <2> | ster<br>68000 Interrupt Enable<br>Lisp→68000 Doorbell<br>Doorbell Interrupt Enable |

| 600       | Calendar Address F<br>Bits <8-11>                   | Register<br>Address input to the calendar chip                                     |

| 602       | Calendar Data Reg<br>Bits <8-11>                    |                                                                                    |

Offset(8) Register Timer (word mode only; write only) 604 (Timer rate is selected by jumpers on the paddle board.) **Enable Timer Interrupts** Bit <8> Bit <9> Clear Timer Interrupt Reset Timer Bit <10> 612 Keep-Alive Register The 68000 should perform a write to this address at least once every 8 seconds when the watchdog timer is enabled. See the message :enable-timeouts on page 33. 614 Reserved

### INSTALLATION

### **MULTIBUS**

# 1. Set the 68000 interrupt timer.

The Gbus paddle board is wired at the factory to support 31.25 KHz. To select a different rate, cut the wire in R6 and solder a wire into one of four pins on the paddle board. (See page 14 for the location of devices on the Gbus paddle board.)

The following frequencies are available:

| Jumper position | Frequency           | Period                      |

|-----------------|---------------------|-----------------------------|

| R6              | 31.25 KHz           | 32 usec (factory frequency) |

| <b>R7</b>       | 62.5 KHz            | 16 usec                     |

| R8              | 125 KHz             | 8 usec                      |

| R9              | 250 KHz             | 4 usec                      |

| R7<br>R8        | 62.5 KHz<br>125 KHz | 16 usec<br>8 usec           |

### 2. Configure the 8-bit parallel port.

If the 8-bit parallel port option is included and you intend to use it, you must configure the GBI paddle board for the type of electrical interface you want. The four types of interface are Symbolics Enhanced Line Printer (ELP), Centronics, Data Products Long Lines, and Data Products TTL.

• ELP and Data Products Long Lines interfaces:

Load SIP resistor networks RN12, RN13, and RN14, and remove SIP resistor network RN20.

• Centronics and Data Products TTL interfaces:

Remove SIP resistor networks RN12, RN13, and RN14, and load SIP resistor network RN20.

(See Appendix B for more information about parallel port cabling.)

Figure 2.1 Gbus paddle board

| • 1 | Interrupt timer                |

|-----|--------------------------------|

| 2   | Bulkhead connector             |

| 3   | LGP/Centronics connector       |

| 4   | Parallel I/O input connector   |

| 5   | Parallel I/O output connector  |

| 6   | External bus address connector |

| 7   | External bus data connector    |

| 8   | RN13 SIP resistor network      |

| 9   | RN14 SIP resistor network      |

| 10  | RN12 SIP resistor network      |

| 11  | RN20 SIP resistor network      |

### 3. Install the GBI boards.

The GBI Lbus board can be installed in any Lbus backplane slot that is not wired for the color bus. This wiring is accomplished by either backplane hard-wiring or the installation of the baby backplane.

The paddle board installs behind the Lbus board.

# 4. Set the Bus Clock jumpers.

The MULTIBUS interface can be configured to drive the BCLK and CCLK signals if no other device in the MULTIBUS card cage generates these clocks.

To enable driving the clocks, install the jumpers between the following pins in the group marked MBUS CTRL:

LOC BCLK to BCLK LOC CCLK to CCLK

Do not install these jumpers if another device in the MULTIBUS card cage generates these clocks or if the MULTIBUS interface is used in existing computer systems, since microprocessor boards generate these signals.

Note: Certain jumpers in the MBUS CTRL group might not be labeled in early versions of the board. The following diagram shows the correct placement of jumpers:

**EXT INIT** INIT PWR RST INIT 0 0 LOC BCLK BCLK LOC CCLK CCLK 0 0 GND **BPRN** CBRQ OUT CRBQ 0 0 CBRQ OUT CRBQIN HI **CBRQIN** 0

### 5. Set the MULTIBUS INIT configuration.

The MULTIBUS interface can be configured to assert the MULTIBUS INIT signal under one or both of the following conditions:

- When the card cage containing the MULTIBUS is powered up.

- When, under 3600 program control, the MULTIBUS INIT line is asserted by the Gbus.

Figure 2.2 MULTIBUS interface board

| 1 | Bus Arbitration jumpers        |

|---|--------------------------------|

| 2 | Bus Clock jumpers              |

| 3 | INIT configuration jumpers     |

| 4 | Interrupt jumpers              |

| 5 | High-Address-Bit jumpers       |

| 6 | External bus address connector |

| 7 | External bus data connector    |

To enable an INIT signal when the MULTIBUS card cage is powered up, install a jumper between the following pins in the MBUS CTRL group:

### PWR RST to INIT

To enable INIT under the control of the Gbus in the 3600, install a jumper between the following pins:

### EXT INIT to INIT

If you want the MULTIBUS interface to assert the INIT signal when the card cage is powered up and under control of the GBI in the 3600, install both jumpers.

Note: It is essential that a device in the MULTIBUS environment generate INIT at power-up.

# 6. Set the Bus Arbitration jumpers.

The way in which the arbitration jumpers are configured depends on the type of other MULTIBUS devices present.

a. When the MULTIBUS interface board is the only master-type device, install jumpers between the following pins in the MBUS CTRL group:

# HI to CBRQIN GND to BPRN

(These pins might not be marked in early versions of the board. Refer to step 4.)

Make sure jumpers are not installed on the CBRQIN and CBRQ OUT pins.

b. When one or more other master-type devices are in the MULTIBUS card cage and none of them uses the Common Bus Request (CBRQ) signal, install a jumper between the following pins:

### HI to CBRQIN

Make sure jumpers are not installed on the CBRQ, BRPN, GND, and CBRQ OUT pins.

c. When some master-type devices that use Common Bus Request are in the MULTIBUS card cage, install jumpers between the following pins:

CBRQ OUT to CBRQ CBRQ OUT to CBRQIN

Make sure nothing is connected to the HI pin.

d. When the MULTIBUS interface is to be the highest priority device in a serial-priority resolution scheme, add a jumper between the following pins:

### GND to BPRN

(These pins might not be marked in early versions of the board. Refer to step 4.)

# 7. Set the High-Address-Bit jumpers.

The MULTIBUS interface supports MULTIBUS systems using either 20- or 24-address bits. The four jumpers in the MBUS HI ADDR group connect P2 edge connector pins 55, 56, 57, and 58 to the address transceivers on the MULTIBUS interface board.

The High-Address-Bit jumpers should always be installed in 24-address-bit systems. They can also be installed in 20-address-bit systems unless those P2 connector pins are used for some other purpose.

Note: In early versions of the MULTIBUS interface, the silkscreened labels for the pairs of jumper pins might be incorrect. When the board is viewed from the component side with the cable connectors at the top, A20 is the rightmost jumper.

### 8. Set the Interrupt jumpers.

The MULTIBUS interface can be jumpered so that any two of the eight MULTIBUS INT lines generate interrupts to the Gbus. The jumper group labeled INT1 MBUS INT2 determines which MULTIBUS interrupt lines affect the Gbus.

The 8 MULTIBUS INT lines (numbered 0 through 7) terminate in the jumper group labeled INT1 MBUS INT2. Two of these interrupts can be selected by

using a jumper to connect them to any of the pins under the labels INT1 and INT2. All pins under the label INT1 connect to Gbus Interrupt 1; all pins under INT2 connect to Gbus Interrupt 2.

For example, setting the jumpers indicated in the following diagram connects MULTIBUS INTO to Gbus Interrupt 1 and connects MULTIBUS INT5 to Gbus Interrupt 2:

| Interrupt<br>Lines | INT1      | MBUS | INT2 |

|--------------------|-----------|------|------|

| 0                  | 0         | 0    | 0    |

| 1                  | 0         | 0    | 0    |

| 2                  | 0         | 0    | 0    |

| 3                  | O         | 0    | 0    |

| 4                  | · , · · O | 0    | 0    |

| 5                  | O         | 0    | 0    |

| 6                  | 0         | 0    | 0    |

| 7                  | O         | 0    | 0    |

|                    |           |      |      |

# 9. Configure the MULTIBUS backplane jumpers for priority resolution.

The MULTIBUS interface can be used with either serial- or parallel-priority resolution schemes.

• For serial-priority resolution, the Bus Priority In (BPRN) and BPRO signals must be chained correctly between boards in the card cage through use of backplane jumpers and/or ensuring that no empty slots exist between boards. Figure 2.3 shows the location of the jumpers on the Symbolics 4-slot MULTIBUS backplane (as seen from the front):

Figure 2.3 Symbolics 4-slot MULTIBUS backplane, front view

- a. Make sure the jumper labeled A is installed.

- b. Install jumpers labeled B when the slot to the left does not contain a master-type device.

- c. Install jumpers labeled C when the slot to the left contains a master-type device.

- A parallel-priority resolution scheme must be accomplished by a resolution circuit external to the Symbolics MULTIBUS interface. If you are using a parallel-priority scheme, remove serial-priority jumpers from the backplane and all wirewrap connections between BREQ and BPRN (Bus Priority In) pins and the parallel-priority resolver.

# 10. Configure the MULTIBUS backplane for 24-bit addressing, if necessary.

Some backplanes, such as the Symbolics 4-slot backplane, require additional wiring to support 24 bits of memory addressing. For 24-bit addressing, the following four pins in each slot must be bussed across the P2 connectors of the backplane:

Pin 55 (ADR16/) Pin 56 (ADR17/) Pin 57 (ADR14/) Pin 58 (ADR15/)

In the case of other MULTIBUS backplanes, refer to the relevant manufacturer's documentation.

#### 11. Install the MULTIBUS interface board.

Install the MULTIBUS interface board into one slot in a standard MULTIBUS card cage. The slot that the board is plugged into is determined by the number and type of other MULTIBUS devices in the card cage. The MULTIBUS environment can fall into one of the following three categories:

a. The Symbolics MULTIBUS interface is the only master-type device in the MULTIBUS card cage, that is, all other MULTIBUS boards are either memory or non-DMA I/O devices.

In this case, plug the MULTIBUS interface board into any MULTIBUS slot.

b. Other master-type devices are in the MULTIBUS card cage; none of them uses the Common Bus Request (CBRQ) signal.

In this case, plug the MULTIBUS interface board into the slot that has lowest bus priority. If a serial-priority resolution scheme is being used, the MULTIBUS interface must be the master-type board located furthest from the board whose BPRN input is grounded.

c. Other master-type devices are in the MULTIBUS card cage; at least one of them uses Common Bus Request.

In this case, install the MULTIBUS interface board at a priority that is either lower or higher than other boards that use Common Bus Request but lower than all master-type devices that do not use Common Bus Request.

# 12. Connect the MULTIBUS-Gbus external cables.

The interface between the MULTIBUS interface board and the Gbus paddle board uses two 60-conductor cables. One cable is used for address, the other for data.

Plug one end of one cable in the external bus address connector on the paddle board. Plug one end of the other cable in the external bus data connector on the paddle board.

Plug the free end of the cable connected to the external bus address connector into the address connector on the MULTIBUS interface board. Plug the free end of the cable connected to the external bus data connector into the data connector on the MULTIBUS interface board.

### 13. Connect the serial and parallel port cables (if included).

- a. Connect the Gbus serial port cable to the bulkhead connector on the Gbus paddle board.

- b. Connect the 8-bit parallel port cable to the LGP/Centronics connector on the Gbus paddle board.

### 14. Load the software.

See the section "Software" starting on page 27.

### **UNIBUS**

### 1. Set the 68000 interrupt timer.

The Gbus paddle board is wired at the factory to support 31.25 KHz. To select a different rate, cut the wire in R6 and solder a wire into one of four pins on the paddle board. (See page 14 for the location of devices on the Gbus paddle board.)

The following frequencies are available:

| Jumper position | Frequency | Period  |                     |

|-----------------|-----------|---------|---------------------|

| R6              | 31.25 KHz | 32 usec | (factory frequency) |

| <b>R</b> 7      | 62.5 KHz  | 16 usec |                     |

| R8              | 125 KHz   | 8 usec  |                     |

| R9              | 250 KHz   | 4 usec  |                     |

# 2. Configure the 8-bit parallel port.

If the 8-bit parallel port option is included and you intend to use it, you must configure the Gbus paddle board for the type of electrical interface you want. The four types of interface are Symbolics Enhanced Line Printer (ELP), Centronics, Data Products Long Lines, and Data Products TTL.

• ELP and Data Products Long Lines interfaces:

Load SIP resistor networks RN12, RN13, and RN14, and remove SIP resistor network RN20.

• Centronics and Data Products TTL interfaces:

Remove SIP resistor networks RN12, RN13, and RN14, and load SIP resistor network RN20.

(See Appendix B for more information about parallel port cabling.)

### 3. Install the GBI boards.

The GBI Lbus board can be installed in any Lbus backplane slot that is not wired for the color bus. This wiring is accomplished by either backplane hard-wiring or the installation of the baby backplane.

The paddle board installs behind the Lbus board.

Figure 2.4 UNIBUS interface board

| 1 | UNIBUS Select DIP switch        |

|---|---------------------------------|

| 2 | MAP Register Address DIP switch |

| 3 | 4-unit DIP switch               |

| 4 | Address-In connector            |

| 5 | Address-Out connector           |

| 6 | Data-In connector               |

| 7 | Data-Out connector              |

|   |                                 |

### 4. Set the 4-unit DIP switch on the UNIBUS interface board.

The DIP switch in position B20 uses only switches 2, 3, and 4.

Switch 2: Open - Activating the Gbus INIT line automatically

activates the UNIBUS INIT line.

Closed - Activating the Gbus INIT line does not

activate the UNIBUS INIT line.

Switch 3: Must be closed.

Switch 4: Open - The 3600 is the UNIBUS primary CPU.

Closed - The 3600 is not the UNIBUS primary CPU. See the section "Address Map" on page 5.

# 5. Set the Map Register Address DIP switch.

This 8-unit DIP switch, which is in location F1 on the UNIBUS interface board, selects part of the address offset for the UNIBUS map registers in UNIBUS address space.

The address offset must fall between 760,000 and 777,760. Hence bits <A13-A17> of the offset are preset to 1s. The switches select bits <A5-A12> of the offset. Switch 1 selects bit <A12>, switch 2 selects bit <A13>. The other switches follows this pattern until switch 8, which selects bit <A5>. When the switch is open, the corresponding address bit is a 1.

For example, if you wanted to assign the starting location of the map registers to UNIBUS address 770,000 (octal), you would set the Map Register Address switches as follows:

- 1 Open (1)

- 2 Closed (0)

- 3 Closed

- 4 Closed

- 5 Closed

- 6 Closed

- 7 Closed

- 8 Closed

### 6. Set the UNIBUS Select DIP switch.

This 8-unit switch, which is in location E1 on the UNIBUS interface board, selects the size and offset for the FEP in UNIBUS address space. Switches 7 and 8 (size 1 and size 0, respectively) are used to select the size. They map as follows:

|           | Size 1     | Size 0     |  |

|-----------|------------|------------|--|

|           | (Switch 7) | (Switch 8) |  |

| 4 Kbytes  | Closed     | Closed     |  |

| 8 Kbytes  | Closed     | Open       |  |

| 16 Kbytes | Open       | Closed     |  |

| 32 Kbytes | Open       | Open       |  |

The remaining 6 switches select the offset. Switch 1 selects bit <A17>, switch 2 selects bit <A16>; the switches follow this pattern until switch 6, which selects bit <A12>. If the switch is open, the corresponding address bit is a 1.

If the size is 8 Kbytes, only 5 of the switches are needed; if the size is 16 Kbytes, only 4 of the switches are needed, etc. All unused switches must be set closed.

For example, if you wanted to map 8 Kbytes of UNIBUS address space into Gbus space starting at UNIBUS address 100,000 (octal), you would set the UNIBUS Select DIP switch as follows:

| 1 | Closed (0 |

|---|-----------|

| 2 | Closed    |

| 3 | Open (1)  |

| 4 | Closed    |

| 5 | Closed    |

| 6 | Closed    |

| 7 | Closed    |

| 8 | Open      |

|   |           |

#### 7. Install the UNIBUS interface board.

If you are installing the UNIBUS interface board in an existing computer system, install it at a lower priority than the processor or UBA. Otherwise, install it in the highest priority slot of the UNIBUS backplane. This is the top slot in the Symbolics-supplied Wesperline backplane; use connectors C, D, E, and F (the rightmost connectors).

Be sure to refer to the manufacturer's documentation for specific installation instructions when installing the UNIBUS board into an existing computer system.

# 8. Connect the UNIBUS-Gbus external cables.

The interface between the UNIBUS interface board and the Gbus paddle board uses two 60-conductor cables. One cable is used for address, the other for data.

Plug one end of one cable in the external bus address connector on the paddle board. Plug one end of the other cable in the external bus data connector on the paddle board.

Plug the free end of the cable connected to the external bus address connector into the connector labeled "Address-In" on the UNIBUS interface board. Plug the free end of the cable connected to the external bus data connector into the connector labeled "Data-In" on the UNIBUS interface board.

# 9. Connect the serial and parallel port cables (if included).

- a. Connect the Gbus serial port cable to the bulkhead connector on the Gbus paddle board.

- b. Connect the 8-bit parallel port cable to the LGP/Centronics connector on the Gbus paddle board.

### 10. Load the software.

See the section "Software" starting on page 27.

#### Software

# 1. Load the tape.

Software comes on a standard distribution format cart tape. To load it, use the function dis:load-distribution-tape. This creates the directory SYS:Gbus; on the system host, and loads the files for the systems Gbus and Gbus-ASSEMBLER.

# 2. Load the system.

Type the command :Load System Gbus (or :Load System Gbus-ASSEMBLER) to bring the system into memory. When the Gbus system is loaded, the world, which now contains the Gbus system, can be saved to disk for transfer to other Lisp machines. The Gbus system facilitates this transfer by clearing itself of any machine-specific knowledge when the world is saved to disk.

When a cold boot is executed, the Gbus system reconfigures itself to account for the current machine-specific information, ensuring up-to-date values for the variables representing the GBI boards. The world can be saved with the Gbus system and transferred to other machines; when the world is saved, the Gbus system clears all knowledge of the particular machine on which it is running and reconfigures itself upon cold boot.

# 3. Update the namespace entry.

If a UNIBUS interface board is connected to the Gbus board, it must be declared in the namespace entry for the host because there is no way to detect the presence or absence of the UNIBUS option; the program must rely on the peripheral field of the host's namespace entry.

Since the MULTIBUS is electrically identical to the Gbus and since all signals sent to the Gbus are therefore sent through buffers to the MULTIBUS, the MULTIBUS need not be declared as a separate item in the namespace. A MULTIBUS device should be declared using interface type GBUS <n> (for example, GBUS 0). A Gbus that connects to a MULTIBUS need only be declared as Gbus in the peripheral namespace entry.

For the purpose of the namespace entry, multiple Gbus boards are identified by number. Numbering starts at 0 at the leftmost Gbus board and increases by 1 for each Gbus board to the right. A lone Gbus board is always 0. This corresponds to the position of the corresponding instance in the list in the variable \*gbus-interfaces\*, that is, the instance for unit <n> can be located by (nth <n> \*gbus-interfaces\*).

Enter a peripheral entry in the following manner:

Peripheral: Pair: UNIBUS Set: Pair: GBUS 0

Pair: NUMBER 0

Pair: ACCESS-BASE 140000 Pair: ACCESS-SIZE 2048

You assign unit numbers to the UNIBUS board via the Number attribute. When other peripheral entries refer to a UNIBUS number, it is the Number attribute of the namespace entry that refers to the UNIBUS board.

ACCESS-BASE is the octal address of the beginning of the mapped area in the UNIBUS address space, as set in the switches on the UNIBUS board. ACCESS-SIZE is the decimal size of the mapped area in words as set in the switches and must be one of 2048, 4096, 8192, or 16384.

If you want the Gbus software to automatically configure peripheral devices connected to the UNIBUS, you can have entries in the namespace entry for their hosts.

An example entry might be:

Peripheral Pair: PS-300 Set: Pair: UNIBUS 0

More information using the namespace to set up interface software can be found on page 46 in the section "Defining Peripherals."

Variable

### PROGRAMMING THE GBUS

#### **GBI Software**

The file sys:gbus:gbus.lisp provides a software model of the GBI and the UNIBUS interface board to make writing software applications more convenient. You are welcome to use this software and to modify it as you see fit.

All Lisp symbols mentioned in this section are implicit in the package GBUS (which uses GLOBAL) unless qualified with a package name.

# Flavor gbus-interface

An instance of the flavor gbus-interface is the model of a single GBI board. It supports a set of messages relevant to the operation of the GBI. The GBI control word is accessed, in whole or by individual fields, through messages to a gbus-interface instance. Bus cycles are done similarly.

A gbus-interface can have one or more external-interfaces, which are models of the various option boards. The MULTIBUS interface board has no software model; its function is purely electrical.

# \*gbus-interfaces\*

Contains a list of **gbus-interface** instances, one for each board in the machine, sorted by ascending slot number (slot 0 being the slot furthest from the data path and other CPU boards in the backplane). In multiboard systems, the proper way to select the correct instance is to add peripherals entries to the host's namespace entry and use the function **gbus:find-peripheral-model**. The position in this list of each instance corresponds to the *unit number* of the board it represents. See page 27 for information on using the namespace system.

:unit

Message to gbus-interface

Returns a fixnum, the number of the unit in which the corresponding Gbus board resides.

# :external-bus-interfaces

Message to gbus-interface

Returns a list of several elements, either an instance of flavor external-interface, a dependent, or nil.

The software does not automatically notice external interfaces; they must be declared on the local host's Peripheral attribute in its namespace record. This procedure is described on page 45 in the section "Defining Peripherals." Note that a MULTIBUS interface board has no software model; it is only an electrical extension of the Gbus.

# :buffer-memory-size

Message to gbus-interface

Returns a fixnum, the count of 32-bit words in the dual-port high-speed RAM buffer. Double this number for the count of 16-bit words.

#### :buf-base

Message to gbus-interface

Returns a fixnum, the virtual address of the beginning of buffer memory in Lisp Machine address space. This number can be used as the target of a displaced array. An array of type art-16b is recommended since buffer memory is accessed as 16-bit words by the Gbus.

#### :device-io-base

Message to gbus-interface

Returns a fixnum, the base Gbus I/O space address of the GBI on-board I/O devices. This fixnum is dependent on the high-address bits in use on the board; it is therefore a message and not a constant.

:memory-read memory-address & optional byte-mode-p

Message to gbus-interface

Reads from memory location memory-address. A single fixnum is returned.

:memory-write memory-address data &optional byte-mode-p Message to gbus-interface

Writes data to memory location memory-address. nil is returned.

:io-read i/o-address & optional byte-mode-p

Message to gbus-interface

Reads from location i/o-address. A single fixnum is returned.

:io-write i/o-address data &optional byte-mode-p

Message to gbus-interface

Writes data to location i/o-address. nil is returned.

:device-read device-offset & optional byte-mode-p

Message to gbus-interface

Reads from the I/O device located at the address derived from adding the on-board I/O device base address to *device-offset*. This is equivalent to using the message :io-read, adding *device-offset* to the value returned by the message :device-io-base.

:device-write device-offset data & optional byte-mode-p

Message to gbus-interface

Writes to the I/O device located at the address derived from adding the on-board I/O device base address to *device-offset*. This is equivalent to using the message :io-write, adding *device-offset* to the value returned by the message :device-io-base.

## **Bus Cycle Error Flavors**

When a bus error occurs when performing any of the mentioned bus cycles, the condition is signaled by the following flavors:

## gbus-cycle-error

Flavor

Base flavor of the following five flavors, built on the flavor gbus-error, which is built on error.

### no-transfer-acknowledge

Flavor

Signaled when a slave device does not respond to the bus cycle within 2 milliseconds.

#### bus-conflict

Flavor

Signaled when an interface board cannot get access to its external bus (such as when the UNIBUS is continuously busy). The software automatically retries such a transfer five times before signaling this error.

## bus-grant-timeout

Flavor

Signaled when some other bus master had control of the Gbus and the Lbus—Gbus port was not granted the bus within 2 milliseconds of requesting it.

### external-bus-not-present

Flavor

Signaled when a cycle is done on some external interface that is declared in the namespace but not actually attached. Discovery of an unattached external interface is made by detecting recursive bus errors while trying to signal an external bus error.

## external-bus-error

Flavor

Base flavor for errors involving cycles on external bus interfaces. The UNIBUS errors are based on this flavor and are documented in section on the UNIBUS software on page 39.

## **Control Word Messages**

The following messages are supported for manipulating fields of the control word.

:enable-slaves :disable-slaves Message to gbus-interface Message to gbus-interface

Enable/disable the on-board slave devices, including the 68000 program memory, serial I/O, and buffer memory.

enable-timeouts:

Message to gbus-interface Message to gbus-interface

Enable/disable the 68000 watchdog timer. When the watchdog timer is enabled, the 68000 must write to the Keep-Alive Register in I/O device space at least once every 8 seconds, or the watchdog timer resets the 68000. The board is initialized with timeouts disabled.

### :reset-68000

Message to gbus-interface

Halts and resets the 68000. The Reset line is asserted only momentarily, then cleared, as it resets the serial I/O ports also. 68000 program execution, when started, begins by taking the reset vector at address 0.

Note: Be careful using :reset-68000 when high-address bits are nonzero. (See the message :enable-hi-addr (page 34). The high-address bits apply to the 68000 program memory as well, that is, setting that field changes the address of 68000 program memory. The 68000 always takes the reset vector at address 0 no matter the setting of the high-address bits, while the program memory might have been moved. Resetting the 68000 then causes it to halt from bus errors.

:halt-68000 :start-68000

Message to gbus-interface Message to gbus-interface

Halt/start the 68000. 68000 program execution continues where it left off. The board is initialized with the 68000 halted.

#### :reset-and-start-68000

Message to gbus-interface

Halts, resets, and starts the 68000. 68000 program execution, when started, begins by taking the reset vector at address 0.

:gbi-auto-cmd :gbi-manual-cmd Message to gbus-interface Message to gbus-interface

Affect the way the Lbus—Gbus port handles bus cycles for the 3600. You do not need to use these messages unless the timing of bus cycles must be handled manually. The board is initialized to auto-cmd and must be in that state when the bus-cycle messages are used.

# :ring-doorbell

Message to gbus-interface

Asserts the 68000's Lbus interrupt request line. Interrupt requests must be enabled by the 68000 control register to actually interrupt the 68000. This bit is cleared only by the 68000.

:hog-gbus :dont-hog-gbus Message to gbus-interface Message to gbus-interface

Assert/deassert Bus-Request at the Lbus-Gbus port, locking out other bus masters. Useful when doing many bus cycles on a busy bus.

:gbi-init

Message to gbus-interface

Momentarily asserts Bus-INIT. Resets and disables/halts all devices including the 68000.

:enable-hi-addr high-address-bits

Message to gbus-interface

Enables 24-bit addressing mode, setting the high-address bits to the 4-bit fixnum value supplied. 20-bit vs. 24-bit mode applies to on-board slave devices in memory space, although the on-board devices in I/O space are affected by high-address bits as well. See the section "Devices and Addresses" on page 7. Be careful when using the 68000 when the high-address bits are set to other than 0, since the reset vector might not come from the currently assigned 68000 program memory.

## :ignore-hi-addr

# Message to gbus-interface

Changes to 20-bit addressing mode. This message also clears the high-address bits. See the section "Devices and Addresses" on page 7.

:turn-on

Message to gbus-interface

Enables local arbitration, local devices, buffer memory, and halts the 68000.

:wait-for-interrupt

Message to gbus-interface

&optional (bit-mask #o17) timeout

Waits for one of the Gbus—Lisp Machine interrupts to be asserted. Four different signals can be selected from the 15 interrupt signal sources via the Gbus map. The optional argument bit-mask allows testing of a subset of the four. timeout is given multiples of 1/60th of a second and defaults to no timeout. The method for this uses process-wait; therefore, the response time is likely to be longer than 1/60th of a second. The message :wait-for-interrupt-hard can be used when it is necessary to spend time in a tight loop awaiting the assertion of an interrupt line.

### :wait-for-interrupt-hard

Message to gbus-interface

&optional (bit-mask #o17) (timeout-in-msec 1000.)

Waits in a tight loop with scheduling inhibited for one of the four Gbus—Lisp Machine interrupts to be asserted. Note: The timeout argument is now in milliseconds and cannot be nil.

# construct-interrupt-map &rest specs

Macro

Makes an interrupt-map array that can be loaded into the Gbus interrupt map using the :install-interrupt-map message. The arguments should all be lists of the form source-name destination-name. The space of names is as follows:

Sources

Destinations

:external-bus-<1 through 7>

:mpsc-<a or b>

:paddle-timer

:pio

:lisp-flag

:doorbell

:Lbus-<0 through 3> :68000-<1 through 7> Note: The Lbus interrupt requests signified in this mapping scheme consist of four independent integers representing the four possible Lbus interrupt requests. The seven 68000 interrupt request lines, however, are determined by reading the bit-weighted value of three separate interrupt request lines. When no lines are asserted, the value is zero. When one or more lines are asserted, the combination of interrupt requests makes up one of the integers 1 through 7. For more information, see page 51 in Appendix A--"UNIBUS Registers, Interrupts, and Priorities."

Furthermore, external bus interrupts are "priority-coded," as are the 68000 interrupt inputs. This means that asserting one 68000 interrupt might mean that another interrupt is blocked. In the case of simultaneous interrupt requests, the order in which arguments to this macro are specified is significant, and priority proceeds in ascending order. That is, the later specification(s) have priority over the earlier one(s). For example, given the following specifications in the following order:

```

(:pio :68000-7)

(:doorbell :68000-3)

```

the doorbell interrupt preempts the PIO interrupt even though the PIO interrupt has a numerically higher priority. The order in which they are declared is the deciding factor.

construct-interrupt-map is used as the initial value in a defconst or defvar form, as shown:

Use the :install-interrupt-map message to actually load the map into the interface.

:install-interrupt-map interrupt-map-array

Message to gbus-interface

Loads the supplied interrupt-map array into the Gbus interface. The previous contents of the interface's interrupt map are lost.

:set-interrupt-map slot value

Message to gbus-interface

Changes the contents of one slot of the interface's interrupt map. This is a primitive interface and is included for compatibility only. New programs should use the facilities above.

## Use of Buffer Memory

The dual-port high-speed RAM buffer provides fast communication between the two worlds. While not really "dual-ported" in the original sense, access to the memory is arbitrated between the two busses. It is both readable and writable from the Lbus and Gbus, and its cycle time is fast enough that even with both sides doing block transfers, wait states are kept to a minimum. When both sides request access simultaneously, the Gbus side has priority.

Each gbus-interface instance has a displaced array pointing to its buffer memory. This array is available by sending the :buffer-memory-array message. It is an art-fixnum array and is as long as the actual buffer memory in the board. This array can be used by itself, or it can be used as the host for other indirect and index-offset arrays.

In applications in which a DMA peripheral or external processor must communicate blocks of data with the 3600, the buffer memory can be used as the staging area. Blocks of several hundred words or a few Kwords can be set aside for transfers, and blocks of several words can be used as flags and simulated "control registers."

Since the array returned is an art-fixnum-type array, writing IEEE single-precision, floating-point numbers to the buffer memory is not possible using simple aref and aset calls. It is recommended that you either indirect a like-sized art-q-type array to it or use the subprimitive %fixnum to coerce the data type of the flonum to fixnum before using aset. Be careful, however, using an art-q pointing to buffer memory; objects that are neither fixnums nor single-floats will not be stored meaningfully because the buffer memory is only 32 bits and does not record the type field.

All data read from the buffer memory array using aref are fixnums, regardless of the type of array used to read them. The subprimitive %flonum can be used to coerce the data type in the cases where the data in the buffer memory are actually IEEE single-precision, floating-point numbers.

#### **Buffer Memory Messages**

The buffer memory messages are provided for using the buffer memory. They are not required to use the buffer memory, but might be useful when different activities are sharing the Gbus.

### :buffer-memory-array

Message to gbus-interface

Returns an art-fixnum-type array, displaced to the board's buffer memory.

#### :buffer-base-address

Message to gbus-interface

Returns, as a fixnum, the Gbus address of the base of buffer memory. If the high-address bits are in use, they are included in the address returned. This gives the program the address needed by external bus DMA devices or the UNIBUS—Gbus map.

:allocate-buffer-memory elements array-type &key (wait-p t) less-is-ok

Message to gbus-interface

Assigns a portion of the buffer memory for use. This message is to be used when concurrent processes are using the Gbus. *elements* should be the number of array elements to allocate, of the specified array type. *array-type* should be either an array-type symbol (such as **art-8b** or **art-string**) or an array (or string) object. Conversion from array elements to words is done internally. *wait-p* is **t** when the message waits for space to be available, or is nil when the message returns nil immediately if the requested space cannot be given. *less-is-ok* allows the largest available portion to be allocated, even if it is smaller than requested.

The three values returned are buffer-index, gbus-address, and elements-allocated. buffer-index is the index into the buffer memory if it were accessed through an array of type array-type. gbus-address is the Gbus byte address of the first element of the allocated area. elements-allocated is the number of elements allocated, which might not be the number requested if the message was passed with less-is-ok being other than nil.

:deallocate-buffer-memory buffer-index array-type

Message to gbus-interface

Frees the allocated portion of buffer memory. An error is signaled when the specified portion was not allocated.

:copy-array-to-buffer array start-index n-elements buffer-index

Message to gbus-interface

Copies the specified portion of array to the buffer memory, starting at buffer-index. buffer-index should be the first value returned from :allocate-buffer-memory.

:copy-buffer-to-array array start-index n-elements buffer-index Message to gbus-interface

Copies the specified portion of the buffer memory to array, starting at buffer-index. buffer-index should be the first value returned from :allocate-buffer-memory.

## Flavor unibus-interface

The flavor unibus-interface models the UNIBUS interface board. Instances of this flavor can be found using gbus:find-peripheral-model, passing a device type of :unibus and 0 in the keyword argument number.

# :read-register offset

Message to external-interface

Reads the I/O-space register located at the interface's base address plus offset. This message and the following one are useful for manipulating the registers of the UNIBUS interface.

# :write-register offset data

Message to external-interface

Writes data to the I/O-space register located at the interface's base address plus offset.

#### :unibus-read address

Message to unibus-interface

Performs a read cycle to the address specified. The read cycle is done via a :memory-read. :unibus-read is available in word-mode only. The result of the cycle is returned as a fixnum, or an error is signaled.

#### :unibus-write address data

Message to unibus-interface

Performs a write cycle to the address specified. The write cycle is done via a :memory-write. :unibus-write is available in byte-mode only and either returns nil or signals an error.

## :unibus-interrupt vector

Message to unibus-interface

Initiates an interrupt. An interrupt can be done only when the UNIBUS interface board is configured not to be the primary CPU. *vector* should be a fixnum in the range 100(8) to 476(8).

## :interrupting-unibus-p

Message to unibus-interface

Returns t if an interrupt has been initiated with the :unibus-interrupt message and has not yet been handled by the CPU. Returns nil otherwise.

# :set-priority level

Message to unibus-interface

Sets the interrupt and bus mastership priority of the interface board. Priority depends on whether the board is configured as the primary CPU. See page 51 for information about the UNIBUS Priority Register.

# :priority

Message to unibus-interface

Returns the current priority level.

# :interrupt-vector

Message to unibus-interface

Returns the vector for the most recent UNIBUS interrupt. This message is useful only when the UNIBUS interface board is configured as the primary CPU, since it does not field interrupts otherwise.

# :interrupt-request-p

Message to unibus-interface

Tells whether a device is requesting an interrupt. This message is useful only when the UNIBUS interface board is configured as the primary CPU.

# :clear-interrupts &optional (mask #o17)

Message to unibus-interface

Clears any interrupts that are currently being passed into the Gbus. The optional argument mask can be used to selectively clear the interrupts.

## :enable-interrupts & optional (mask 1)

Message to unibus-interface

Allows the specified interrupt signals to be passed into the Gbus. The default mask is 1 since 1 corresponds to UNIBUS Interrupt, which is the interrupt most likely to be in use.

# :disable-interrupts & optional (mask 1)

Message to unibus-interface

Disables the passing of UNIBUS interface board interrupts into the Gbus. The bits specified in *mask* are cleared in the Gbus Interrupt Enable/Disable Register.

The UNIBUS interface board does not have a separate :wait-for-interrupts method. It can generate an external bus priority 7 interrupt, which can be mapped by the

interrupt map into one of the Gbus—Lbus interrupt request lines. This can be tested much more efficiently than repeatedly checking the Gbus Interrupt Read/Clear Register.

:write-map UNIBUS-address Gbus-address Message to unibus-interface &optional io-space-p byte-mode-p (byte-number 0)

Writes the proper slot in the UNIBUS—Gbus access map. The Gbus address can be in memory space or I/O space. Since there is no byte-mode read cycle on the UNIBUS and some Gbus registers require being addressed in byte mode, the map entry can specify byte-mode access and the low bit to be used. The 11 low-order bits of the two addresses must be the same. An error is signaled when the low-order bits are not the same, when the address is outside the mapped area of UNIBUS space, or when the mapped area was not specified in the namespace entry.

The map is composed of 16 registers, each one corresponding to 1 Kword (2 Kbytes). Only one use of this message is needed for each 1-Kword segment.

Note that a CPU on the UNIBUS can set the map itself, because it is mapped into the UNIBUS address space as well.

## :read-map-register register-number

Message to unibus-interface

Returns the 12-bit fixnum stored in the addressed map register. register-number should be a fixnum in the range 0 to 15. The low 9 bits of this fixnum are bits <19:12> of the Gbus address. The other bits are documented on page 56 in Appendix A--"UNIBUS Registers, Interrupts, and Priorities." Three other values are also returned:

- 1. t if the register maps to I/O space or nil if it maps to memory space;

- 2. t if the register specifies byte-mode accesses or nil if it specifies word-mode accesses;

- 3. the low-order bit used for byte-mode accesses.

The following conditions might be signaled while performing :read-map-register:

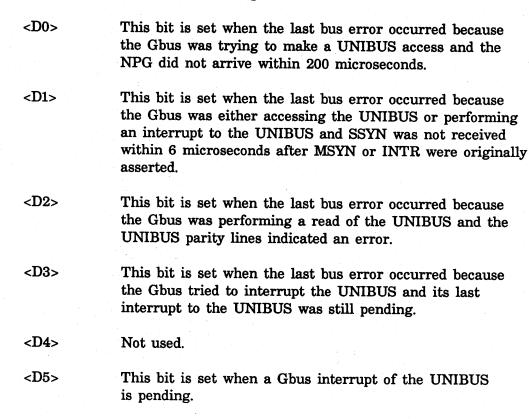

unibus-error Flavor

Base flavor for the following flavors. It is based on external-bus-error, which is based on gbus-cycle-error.

# unibus-grant-timeout

Flavor

The UNIBUS was continuously busy for 200 microseconds.

# unibus-non-existent-memory

Flavor

No slave responded within 6 microseconds.

# unibus-parity-error

Flavor

A parity error occurred reading from UNIBUS memory.

# unibus-interrupt-still-pending

Flavor

The :unibus-interrupt message was sent, but the last interrupt requested was still pending.

#### **Serial Ports**

## :make-serial-stream &rest keyword-args

Message to gbus-interface

Makes a serial stream that connects to the serial hardware in the Gbus board. The same keyword arguments used in si:make-serial-stream apply.

Note: The :unit keyword value should be between 1 and 3, inclusive. Unit 1 corresponds to the EIA 5 serial connector, unit 2 corresponds to EIA 6, and unit 3 corresponds to EIA 7. Likewise, unit 1 corresponds to MPSC A, channel B; unit 2 corresponds to MPSC B, channel A; and unit 3 corresponds to MPSC B, channel B.

# gbus:serial-binary-stream gbus:serial-character-stream

Flavor Flavor

Instances of these flavors control Gbus serial streams. They support the same messages as regular serial streams. They are not, however, handled by an external processor, the way the FEP handles the regular serial ports. Thus input from these streams is not as simple a thing, since characters might be missed. If an application cannot afford to have the 3600 spending much of its time polling the Gbus serial hardware, it is recommended that you use the 68000 processor to handle serial I/O.

### :transmit-buffer-not-full

Message to basic-gbus-serial-stream

Returns t when the hardware for the port is ready to transmit another character or byte, and nil when it is not ready. This can be used in places where letting the :tyo method wait using process-wait takes too much time and the application needs more control of how it waits for the hardware to be ready. This message is supported in addition to the regular protocol for a serial stream.

#### Parallel Port

Since there is only one parallel port on a Gbus board, the gbus-interface instance handles its protocol directly.

:parallel-port-output 8-or-16-bit-value :parallel-port-set 8-or-16-bit-value Message to gbus-interface Message to gbus-interface

Place the given value in the Parallel Port Output Register. The first message waits until any previous cycle has been acknowledged, as when a handshaking, stream-oriented device is connected. The second message just sets the register and returns.

Note: If the Gbus parallel port is configured as an 8-bit interface, only the lower-order 8 bits of the data value are relevant.

:parallel-port-input :parallel-port-read Message to gbus-interface Message to gbus-interface

Read the data on the parallel port inputs. The first message waits until a dataready signal appears, as when a handshaking, stream-oriented device is connected. The second message just reads the register. A 16-bit fixnum is returned.

If the parallel port is configured as an 8-bit interface, bits <0-7> of the value returned contain the data, and bits <14> and <15> contain the value of the Select and Paper Empty Status, respectively.

# :parallel-port-listen

Message to gbus-interface

Returns t if the attached device is asserting data ready, nil if not.

# :parallel-port-ready

Message to gbus-interface

Returns t when the hardware is ready to begin an output cycle, nil when a cycle is in progress.

## :parallel-start-write

Message to gbus-interface

Forces:parallel-port-ready to return t. This message is to be used at the beginning of any handshaking output interaction when the state of the handshaking is unknown.

## **Defining Peripherals**

By using some utilities provided in the namespace system, you can automatically configure device interfaces upon loading the application system and cold booting.

The peripherals field in a host's namespace entry allows you to declare peripheral devices on the host. The UNIBUS is declared in this way, as shown in the chapter "Installation" (page 27). The kind of connection between peripherals and the machine is declared by specifying an *interface type*. The interface type should be the first attribute declared for the peripheral.

The following interface types are significant to the Gbus user:

| Туре         | Significance                                                                                                                                                       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UNIT<br>GBUS | The peripheral uses some type of serial interface.  The peripheral uses a Generic Bus Interface. (Select this interface type if your Gbus connects to a MULTIBUS.) |

| UNIBUS       | The peripheral uses a UNIBUS interface board.                                                                                                                      |

Other external interfaces can define their own interface types.

The kind of peripheral is declared by the device type, which is the first token in the peripheral entry. The following is an example of a peripheral entry in the namespace:

Peripheral: MODEM UNIT 1 MODEL CDS-224 PHONE-NUMBER 2134780681 AUTO-ANSWER Yes

Here, the device type is MODEM and the interface type is UNIT, which implies a serial interface. Other options are present as well.

The namespace system allows you to declare the recognized options to devices and their interface types, so that the system can parse the options (into numbers, for example) for the application. In the above example, the UNIT option is declared an integer by the UNIT interface type, and the AUTO-ANSWER option is declared to be boolean by the MODEM device type.

For more information, see the source code of the Gbus system, in uses of neti:define-peripheral-interface-type and neti:define-peripheral-device-type.

The Gbus system uses these utilities to automatically configure the Gbus system by the information on the local host's namespace entry, both when the Gbus system is loaded, and at cold-boot time if the Gbus system was previously saved in a world.

If you are programming Gbus applications, you can also use the namespace utilities and the Gbus system's hooks to initialize the state of your own software. This way, the Gbus software notes that your peripheral is declared on the local host and either calls a user-defined function or instantiates a user-defined flavor.

If you anticipate having more than one possible interface for a device, you should have setup functions or flavors for each interface type.