# 2SP 2SPB 2SPBT

# Owner's Manual

Two serial line units

8 bit parallel input/output

or line printer port

Multidevice bootstrap

Bus termination

# TABLE OF CONTENTS

| Theory of Operation                                                                                                        | 12             |

|----------------------------------------------------------------------------------------------------------------------------|----------------|

| Four-cycle Mueller Handshake Protocol Specifications                                                                       | 22             |

| Warranty                                                                                                                   | . • 2 <u>:</u> |

|                                                                                                                            | 1              |

| Device Register Format                                                                                                     | 11             |

| Tables                                                                                                                     |                |

| Function Switch  Baud Rate Selection  Serial Communication Protocol  Serial Communication Format  Console Break            | 5              |

| Device Standard Address and Vector Parallel Communication Protocol Memory Diagnostics Error Messages Termination Selection | 7              |

Copyright (c) 1980 by Technical Magic, Irvine, California, U.S.A.

LSI-11, DEC, and Q-Bus are trademarks of Digital Equipment Corporation.

#### FUNCTIONAL DESCRIPTION

The TECHNICAL MAGIC 2SPBT combines one parallel and two serial ports with an intelligent, multi-device bootstrap and Q-bus termination on a single dual-width board. This high density, multifunction board saves backplane space while allowing easy user configuration of its many options and is completely compatible with LSI-11.

The serial ports can be used as general purpose interfaces to serial peripheral devices using Electronic Industry Association (EIA) standard RS-232C, RS-423 or RS-422 communication protocol and are DEC DJV11-J compatible. One of the two serial ports can be configured as the console port to communicate with a local or remote terminal.

The parallel port can be used as a general purpose interface to parallel peripheral device using four-cycle Mueller handshake communication protocol. The parallel ports of two 2SPBTs can be connected directly together using industry standard mass-termination cable and connectors to create a high speed parallel communication link between two LSI-11s by simply inverting the cable at the end. The parallel port can also be configured as a printer port to drive a Centronics or Data Products compatible line printer.

All serial and parallel ports are hardware and software compatible with the LSI-11.

The bootstrap performs memory diagnostics and boots peripheral devices in a priority chain manner. If the first device in the priority chain list does not exist, it then boots the second device. If the device exits, the 2SPBT waits until the device is ready, and boots from it. Typing an escape on the console will proceed directly to the next device. The standard priority chain list is RKO5 followed by RXO1/RXO2. Bootstraps for any standard DEC devices are available. Custom bootstraps can be written for any devices.

The bus terminator can be removed easily if the module is not used as a terminator.

#### THEORY OF OPERATION

#### **GENERAL**

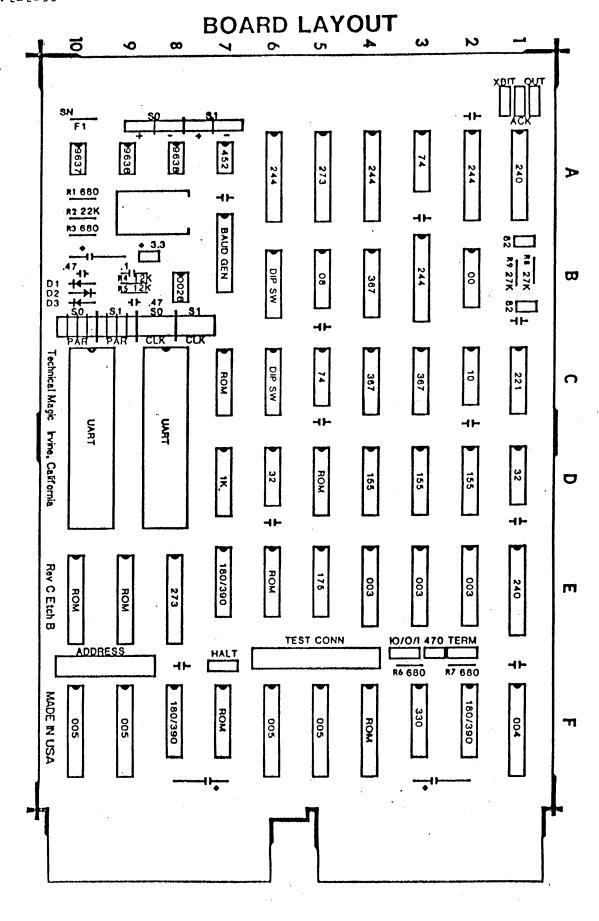

This module has two serial ports which are implemented with two universal asynchronous receivers and transmitters (UART) associated with a baud rate generator and transceivers for EIA interface. The parallel port is implemented with an octal latch and two octal drivers with latches and gates to control handshake with the user device. The bootstrap and memory diagnostic program is stored in two bootstrap PROMs. The bus interface which performs address matching, vector forcing and control signals generating is implemented with a DEC Chipkit, two address PROMs, a vector PROM and three address decoders with some gates.

#### BUS INTERFACE

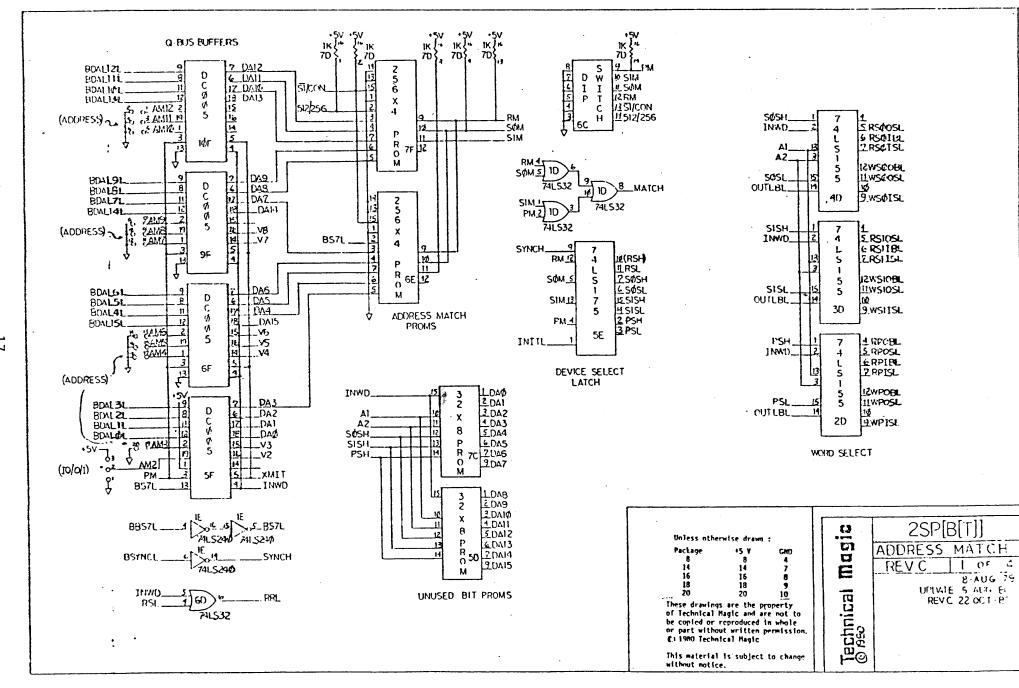

The bus interface is mainly handled by a DEC chipkit which has four transceiver logic chips, three interrupt logic chips and a protocol logic chip. The address matching is performed by the four transceiver logic chips which buffer the address lines into two address PROMs, compare against the user-assigned parallel port address and generate a match signal. The two address PROMs also compare the address lines against the programmed serial port and bootstrap addresses and generate match signals. These match signals are then interpreted by the address decoders which generate control signals that read from or write to the serial ports, the parallel port, or the bootstrap PROMs.

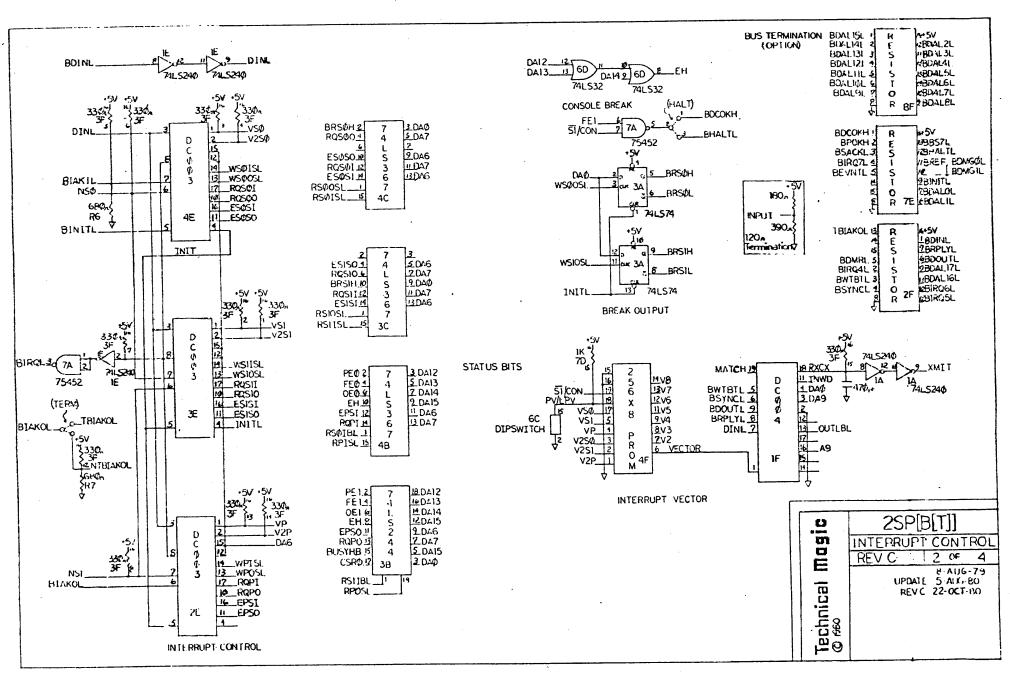

Vector forcing is performed by the three interrupt logic chips which generate vector request signals to a vector PROM when an interrupt request signal is received. The vector PROM sends the programmed interrupt vector to the transceiver chips which force this interrupt vector to the bus.

Bus timing is handled by the protocol logic chip which decides whether the operation is a read or a write.

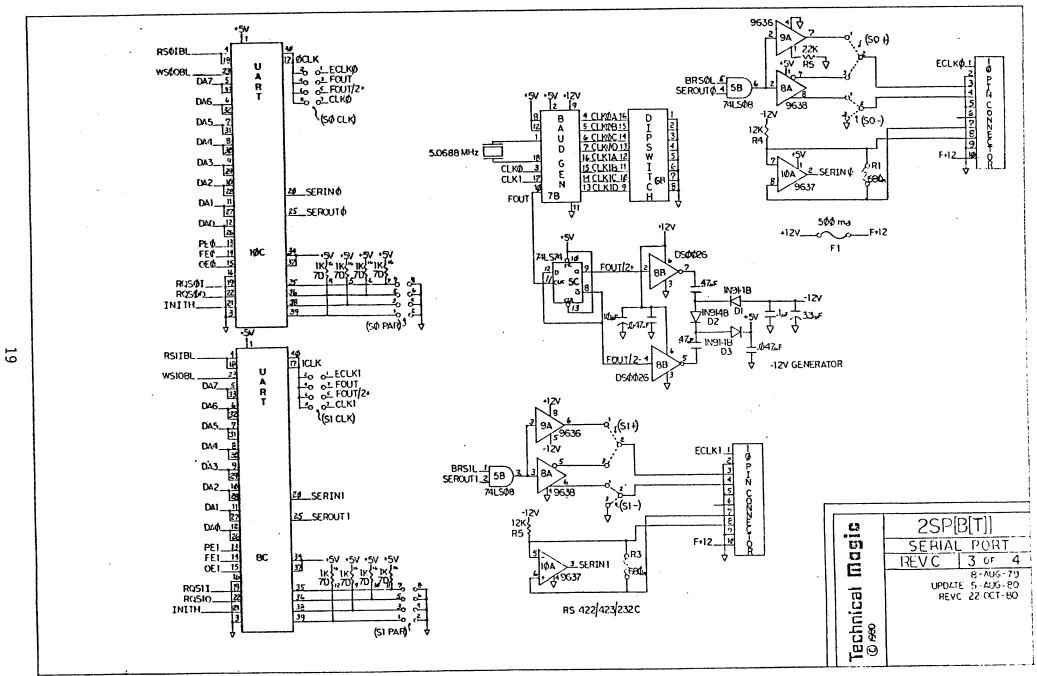

#### SERIAL PORTS

Each serial port is implemented with a universal asynchronous receiver and transmitter (UART) which converts serial data to parallel data, converts parallel data to serial data, generates error signals, and sends interrupt request

signals. Serial data is received or transmitted through an EIA receiver or driver. Error signals are buffered through drivers to the high byte of the input buffer register. Interrupt request signals are sent to the interrupt logic chip to activate interrupts.

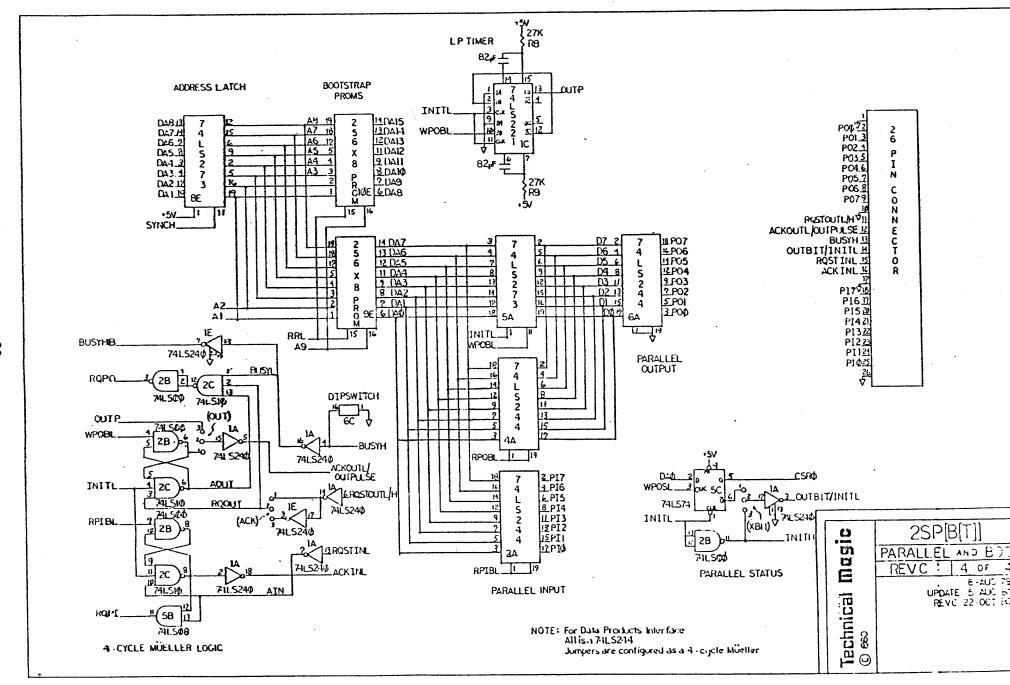

#### PARALLEL PORT

The parallel port is implemented with an octal latch and two octal drivers. The output data is stored in the octal latch by the control signal from the address decoders. Similarly, the output and input data are read through the octal tri-state drivers by the control signal. Handshake with the user device is controlled by latches and gates which interpret the request signal from and generate the acknowledge to the user device and generate interrupt request signals to the interrupt logic chip.

#### BOOTSTRAP

The bootstrap and memory diagnostics are contained in the two bootstrap PROMs.

The size of user random access memory (RAM) is calculated by the bootstrap program and printed on the console. The memory diagnostics are then run and numeric error messages are printed on the console if the memory fails the diagnostics.

After successful completion of the memory diagnostics, the bootstrap tries to boot the first device in the priority chain. If the first device does not exist, it is skipped and the next device in the priority chain is tried. If the first device is busy, it can be skipped by typing an escape on the console and the next device is tried. If the last device in the priority chain is tried and fails, the bootstrap is halted. The devices in the priority chain can be retried by typing a capital P. The standard priority chain list is RKO5, RXO1/RXO2.

#### UNUSED BIT PROMS

Two open-collector PROMs are utilized to force the unused bits of the parallel and two serial ports read as zeros.

#### CONFIGURATION

#### **GENERAL**

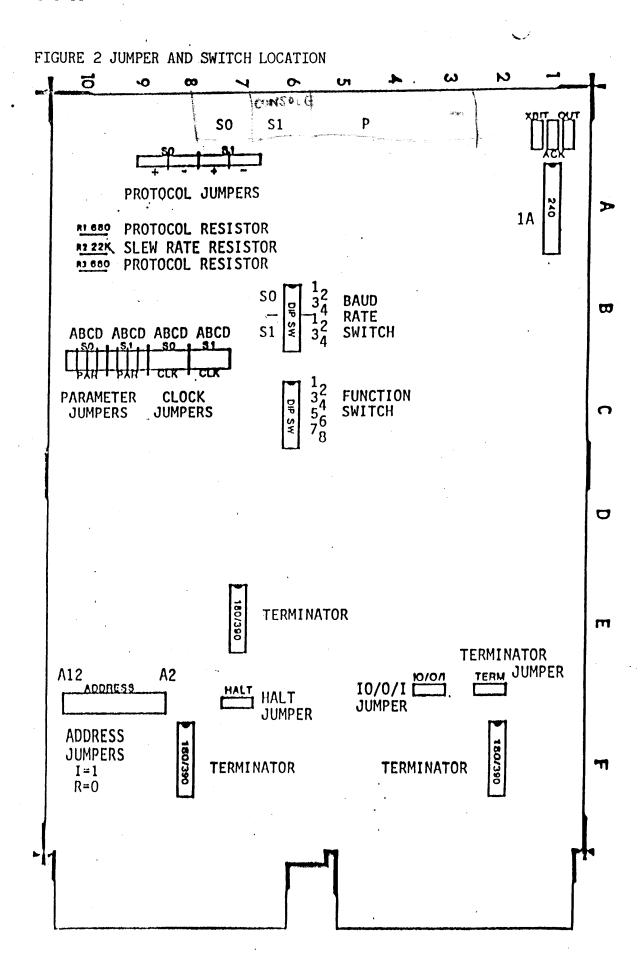

Each function of this module can be disabled or enabled individually as best fits the user system. One of the serial ports (S1) can be configured as the console port and the parallel port can be configured as a printer port by the function switch. The individual function switch assignments are shown in Table 1. The device register bit assignments are shown in Figure 1. The jumper and switch locations are shown in Figure 2. Each function is described in the following paragraphs.

# TABLE 1 FUNCTION SWITCH

| SWITCH<br>1 | FUNCTION<br>BUSY | DESCRIPTION<br>should be closed if there is no connection<br>to Extra Received Bit on the parallel<br>connector and a 74LS240 is at 1A | 0             |

|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 2           | P/LP             | closed to configure as a parallel port opened to configure as a printer port                                                           | $\mathcal{O}$ |

| 3           | 512/256          | closed to choose 512 word bootstrap space opened to choose 256 word bootstrap space                                                    | C             |

| 4           | S1/CON           | closed to configure as a second serial port opened to configure as the console port                                                    | 0             |

| 5           | RM               | closed to disable the bootstrap closed to disable the first serial port                                                                | 6             |

| 6<br>7      | SOM<br>S1M       | closed to disable the second serial port<br>closed to disable the parallel port                                                        | ð             |

| 8           | PM               | GTOSEG to grante one baratter bor a                                                                                                    | $\cup$        |

#### SERIAL PORT

The addresses and vectors of the two serial ports and the console port are fixed and stored in the address and vector PROM respectively. They can be programmed by the user or at the factory. The standard address and vector configuration is shown in Table 6.

The baud rate can be selected by the clock jumpers and baud rate switch as shown in Table 2. The communication interface protocol can be configured as RS-232C, RS-423 or RS-422 by changing the protocol jumpers and resistor as shown in Table 3. The slew rate for RS-232C and RS-423 is specified by the slew rate resistor as shown in Table 2 and the character format is specified by the parameter jumpers as shown in Table 4.

If the second serial port is set for console operation and a break character is received, the system will re-boot, halt or do nothing depending on the halt jumper as shown in Table 5.

| TA     | BLE    | 2  | BAUD           | RATE | SE  | LEC | TION | SLEWITATE | D. MT          |

|--------|--------|----|----------------|------|-----|-----|------|-----------|----------------|

| JUI    | MPE    | RS |                | SW   | IŤC |     |      | RESISTOR  | BAUD RATE      |

| A      | В      | C  | D <sub>.</sub> | 4_   | _2  | 3   | 4,   |           | <b>E</b> 0     |

| I      | R      | R  | R              | C    | C   | C   | C    | 1M OHM    | 50<br>75       |

| I      | R      | R  | R              | C.   | C   | C   | 0    | 1M OHM    | 110            |

| Ι      | R      | R  | R              | С    | C   | 0   | С    | 1M OHM    |                |

| I      | R      | R  | R              | С    | С   | 0   | 0    | 1M OHM    | 134.5          |

| I      | R      | R  | R              | С    | 0   | C   | C    | 1m ohm    | 150            |

| Ī      | R      | R  | R              | С    | 0   | C   | 0    | 1m ohm    | 300            |

| Ī      | R      | R  | R              | C    | 0   | 0   | С    | 1M OHM    | 600            |

| Ī      | R      | R  | R              | Č    | 0   | 0   | 0    | 820K OHM  | 1200           |

| Ī      | R      | R  | R:             | Ŏ.   | Č   | C   | C    | 620K OHM  | 1800           |

| Ī      | R      | R  | R              | 0    | C   | Č   | 0    | 560K OHM  | -2000          |

| Ì      | R      | R  | R              | ŏ    | Č   | Ō   | Č    | 430K OHM  | 2400           |

| Ī      | R      | R  | R              | Ö    | Č   | Ō   | Ö    | 330K OHM  | 3600           |

| Ī      | R      | R  | R              | . 0  | ŏ   | Č   | Č    | 200K OHM  | 4800           |

| Ī      | R      | R  | R              | Ö    | ŏ   | Č   | ŏ    | 160K OHM  | 7200           |

| Ī      | R      | R  | R              | Ö    | ŏ   | ŏ   | Č.   | 120K OHM  | 9600           |

| Ī      | R      | R  | R              | ŏ    | ŏ   | Ŏ   | 0    | 51K OHM   | 19200          |

| R      | n<br>R | I  | R              | X    | X   | X   | X    | 22K OHM   | 38400          |

| R      | I      | R  |                | X    | X   | X   | X    | 10K OHM   | 76800          |

| n<br>R | R      | R  | I              | X    | X   | X   | X    |           | External clock |

I=Inserted R=Removed C=Closed O=Opened X=Don't care

The module outputs the selected internal clock with the jumper D inserted, unless the external clock is being used as input clock.

TABLE 3 SERIAL COMMUNICATION PROTOCOL

| JUMPERS                         |                            | RI R3<br>RESISTOR          | PROTOCOL                    |

|---------------------------------|----------------------------|----------------------------|-----------------------------|

| +<br>L to C<br>L to C<br>C to R | C to R<br>C to R<br>L to C | 680 OHM<br>none<br>100 OHM | RS-232C<br>RS-423<br>RS-422 |

L=Left R=Right C=Center

#### TABLE 4 SERIAL COMMUNICATION FORMAT (PARAMETER)

| JUMPER | DESCRIPTION     |                  |

|--------|-----------------|------------------|

| A      | I=Odd parity    | R=Even parity    |

| В      | I=7 data bits   | R=8 data bits    |

| C      | I=1 stop bit    | R=2 stop bits    |

| D      | I=Enable parity | R=Disable parity |

I=Inserted R=Removed

# TABLE 5 CONSOLE BREAK (HALT)

| JUMPER | DESCRIPTION |

|--------|-------------|

| L to C | Re-boot     |

| R to C | Halt        |

| N      | Do nothing  |

L=Left R=right C=Center N=No Jumper

#### PARALLEL PORT

The addresses of the parallel and printer port can be assigned by inserting or removing the address jumpers. The vectors are fixed and stored in the vector PROM. Non-standard vectors can be specified by the user when ordering. The standard addresses and vectors of the parallel and line printer port are shown in Table 6.

# TABLE 6 DEVICE STANDARD ADDRESS AND VECTOR

| DEVICE         | ADDRESS   | <b>VECTOR</b> |

|----------------|-----------|---------------|

| Serial port SO | 176500    | 300           |

| S1             | 176510    | 310           |

| Console port   | 177560    | 60            |

| Parallel port  | 167770(*) | 320           |

| Printer port   | 177514(*) | 200           |

| Bootstrap      | 173000    |               |

<sup>\*</sup> This address can be specified by the address jumpers. Other addresses and vectors are fixed in the address and vector PROMs.

The parallel port can be configured as a parallel port with four-cycle Mueller handshake protocol, a printer port with Centronics interface or a printer port with Data Products interface by changing jumpers and a chip. This is shown in Table 7.

#### TABLE 7 PARALLEL COMMUNICATION PROTOCOL

| SWITCH | JUMPERS       |        |        | CHIP  | DESCRIPTION |

|--------|---------------|--------|--------|-------|-------------|

| P/LP   | XBIT ACK      | OUT    | IO/0/I | 1A    |             |

| C      | T to C T to C | T to C | N      | LS240 | <b>*</b> 1  |

| C      | T to C T to C | T to C | R to C | LS240 | <b>*</b> 2  |

| C      | T to C T to C |        |        |       | <b>*</b> 3  |

| 0      | T to C T to C |        |        |       | <b>*</b> 4  |

| Ō.     | B to C B to C |        |        |       | <b>*</b> 5  |

C=Closed O=Opened

T=top B=Bottom C=Center

L=Left R=Right C=Center N=No Jumper

#### BOOTSTRAP AND TERMINATOR

The starting address of the bootstrap is fixed and stored in the address PROM. The standard starting address of bootstrap is shown in Table 6. The numeric error messages of the memory diagnostics are listed in Table 8. Memory diagnostics may be continued by typing a capital P. The termination can be disabled by changing the termination jumper and removing the terminators as shown in Table 9.

# TABLE 8 MEMORY DIAGNOSTICS ERROR MESSAGES

173062\* Error in writing the address to the bad location.

RO points to the bad memory location.

173112\* Error in writing 0 or 177777 to memory. RO points to the bad memory location. R1 contains what was being written.

\* These Addresses may differ slightly in custom versions of the bootstrap.

<sup>\*1=</sup>Parallel port with input only

<sup>\*2=</sup>Parallel port with output only

<sup>\*3=</sup>Parallel port with input and output both

<sup>\*4=</sup>Printer port with Data Products interface

<sup>\*5=</sup>Printer port with Centronics interface

# TABLE 9 TERMINATION SELECTION

JUMPER TERMINATOR DESCRIPTION

L to C I Enable termination R to C R Disable termination

I=Inserted R=Removed

L=Left R=Right C=Center

FIGURE 1 DEVICE REGISTER DESCRIPTION SERIAL PORTS

| 0  | 0                                           | 0  | 0                                      | 0 | 0                                                                                                                                                                           | 0                                   | 0                     | RD   | RIE  | 0    | 0     | 0              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                 | 0  |

|----|---------------------------------------------|----|----------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------|------|------|------|-------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----|

| •  | Bits<br>8-15<br>7<br>6<br>0-5               |    | Code<br>O<br>RD<br>RIE<br>O            |   | not<br>Rec<br>Rec                                                                                                                                                           | used<br>eiver                       | i<br>Don<br>Int       | Regi | •    |      | etion | r<br>r<br>r    | ead o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | as ze                             | _  |

| ΙE | OE                                          | FE | PE                                     | 0 | 0                                                                                                                                                                           | 0                                   | 0                     | D7   | D6   | D5   | D4    | D3             | D2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D1                                | DO |

|    | 3its<br>15<br>14<br>13<br>12<br>3-11<br>0-7 |    | Code<br>IE<br>OE<br>FE<br>PE<br>O<br>D | , | Inpu<br>Over<br>Fram<br>Pari                                                                                                                                                | it Er<br>run<br>ing<br>ty E<br>used | ror<br>Erroi<br>Erroi |      | ster | Func | tions | re<br>re<br>re | ecessed of ead o | nly<br>nly<br>nly<br>nly<br>s zer | °0 |

| 0  | 0                                           | 0  | 0                                      | 0 | 0                                                                                                                                                                           | 0                                   | 0                     | TR   | TIE  | 0    | . 0   | 0              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                 | ТВ |

| 1  | its<br>-15<br>7<br>6<br>-5                  | c  | Code<br>O<br>TR<br>TIE<br>O<br>TB      |   | Output Status Register Functions Access not used read as zero Transmit Ready read only Transmit Interrupt Enable read/write not used read as zero Transmit Break read/write |                                     |                       |      |      |      |       |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |    |

| 0  | 0                                           | 0  | 0                                      | 0 | 0                                                                                                                                                                           | 0                                   | 0                     | D7   | D6   | D5   | D4    | D3             | D2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D1                                | DO |

| 8. | lts<br>-15<br>0-7                           | (  | Code<br>0<br>D                         |   | Outpu<br>not u<br>Data                                                                                                                                                      | ut Bu<br>used                       | ffer                  | Regi | ster | Func | tions | re             | cess<br>ad as<br>ite c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | zero                              | )  |

# PARALLEL PORT

| 0  | 0                                   | 0 | 0                                       | 0 | 0                                                                                                                                                                                                               | 0                                       | 0     | RD   | RIE   | 0     | 0     | 0        | 0                                         | 0                    | 0  |

|----|-------------------------------------|---|-----------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------|------|-------|-------|-------|----------|-------------------------------------------|----------------------|----|

| 8  | Bits<br>B-15<br>7<br>6<br>D-5       | • | Code<br>O<br>RD<br>RIE<br>O             |   | not<br>Rece<br>Rece                                                                                                                                                                                             | ut St<br>used<br>eiver<br>eiver<br>used | Done  | •    |       | ÷     | tion  | re<br>re | ccess<br>ead a<br>ead o<br>ead/w<br>ead a | s zer<br>nly<br>rite |    |

| 0  | 0                                   | 0 | 0                                       | 0 | 0                                                                                                                                                                                                               | 0                                       | 0     | D7   | D6    | D5    | D4    | D3       | D2                                        | D1                   | DO |

| 8  | 3its<br>3-15<br>0-7                 |   | Code<br>0<br>D                          |   |                                                                                                                                                                                                                 | ut Bu:<br>used                          | ffer  | Regi | ster  | Funct | tions | re       | ccess<br>ead a<br>ead o                   | s zer                | ro |

| RF | 0                                   | 0 | 0                                       | 0 | 0                                                                                                                                                                                                               | 0                                       | 0     | TR   | TIE   | 0     | 0     | 0        | 0                                         | 0                    | TF |

| 8  | 3its<br>15<br>3-14<br>7<br>6<br>1-5 |   | Code<br>RF<br>O<br>TR<br>TIE<br>O<br>TF |   | Output Status Register Functions Access Extra Received Bit read only not used read as zero Transmit Ready read only Transmit Interrupt Enable read/write not used read as zero Extra Transmitted Bit read/write |                                         |       |      |       |       |       |          |                                           |                      |    |

| 0  | 0                                   | 0 | 0                                       | 0 | 0                                                                                                                                                                                                               | 0                                       | 0     | D7   | D6    | D5    | D4    | D3       | D2                                        | D1                   | DO |

| 8  | Bits<br>8-15<br>0-7                 | ( | Code<br>0<br>D                          |   | -                                                                                                                                                                                                               | ut Bu<br>used                           | uffer | Regi | ister | Func  | tion  | re       | cess<br>ead a                             |                      | 0  |

# PARTS LIST

# WITHOUT BOOTSTRAP AND TERMINATION

| QUANTITY 10 1 3 1 2 1 2 2 1 2 1 3 1                           | PART NUMBER 0.047UF 3.3UF 39UF 0.1UF 82PF 470PF .47UF 680 OHM 12K OHM 22K OHM 27K OHM 100 or 680 OHM 330 OHM x 15 1K OHM x 15 1N914B | resistor network<br>resistor network<br>diode                                                                                                                                                                                                                                    |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>1<br>1<br>1<br>1<br>2<br>2<br>3<br>1<br>1<br>1           | 5.0688MHz 5036 or K1135 0.5A @ 12V 74LS00 74LS08 74LS10 74LS32 74LS74 74LS155 74LS21 74LS240 74LS240 74LS244 74LS244 74LS273 74LS367 | crystal baud generator  Hybrid baud generator fuse quad nand gate quad and gate tri nand gate quad or gate dual flip-flop dual decoder quad flip-flop dual monostable multivibrator octal buffer octal buffer octal latch hex driver                                             |

| 2<br>3<br>2<br>2<br>1<br>1<br>1<br>1<br>1<br>3<br>1<br>4<br>2 | HD6402<br>6331<br>6300<br>6309<br>75452<br>9636<br>9637<br>9638<br>DS0026<br>DC003<br>DC004<br>DC005<br>8-position                   | UART 32x8 open-collector PROM 256x4 open-collector PROM 256x8 tri-state PROM dual nand open-collector buffer RS-422 driver RS-422/423/232C receiver RS-423/232C driver charge pump driver DEC interrupt logic chip DEC protocol logic chip DEC transceiver logic chip DIP-switch |

| 2 | 10316-01-445 | 16-pin socket |

|---|--------------|---------------|

| 2 | 10320-01-445 | 20-pin socket |

| 2 | 87567-1      | 10-pin header |

| 1 | 87567-9      | 26-pin header |

# WITH BOOTSTRAP

# plus

| QUANTITY | PART NUMBER  | DESCRIPTION          |

|----------|--------------|----------------------|

| 2        | 6309         | 256x8 tri-state PROM |

| 2        | 10320-01-445 | 20-pin socket        |

# WITH TERMINATION

# plus

| QUANTITY | PART NUMBER  | DESCRIPTION   |

|----------|--------------|---------------|

| 3        | 180/390      | termination   |

| 3        | 10316-01-445 | 16-pin socket |

# CONNECTOR PIN-OUT

# SERIAL PORT

| 1 | External Clock | 10 | +12V         |

|---|----------------|----|--------------|

| 2 | GND            | 9  | GND          |

| 3 | Transmit+      |    | Receive+     |

| 4 | Transmit-      | 7  | Receive- (*) |

| 5 | GND            | 6  | No Pin -KEY  |

\* Pin 7 should be grounded externally for RS-232C and RS-423

# PARALLEL PORT

| 1 2 | GND<br>Output 0    | 26<br>25 | GND<br>Input 0        |

|-----|--------------------|----------|-----------------------|

| 3   | Output 1 "         | 24       | Input 1               |

| 4   | Output 2           | 23       | Input 2               |

| 5   | Output 3           | 22       | Input 3               |

| 6   | Output 4           | 21       | Input 4               |

| 7   | Output 5           | 20       | Input 5               |

| 8   | Output 6           | 19       | Input 6               |

| 9   | Output 7           | 18       | Input 7               |

| 10  | GND                | 17       | GND                   |

| 11  | Request Output     | 16       | Acknowledge Input     |

| 12  | Acknowledge Output | 15       | Request Input         |

| 13  | Extra Received Bit | 14       | Extra Transmitted Bit |

# DATA PRODUCTS PRINTER PORT

| 1  | GND         | 26 | NC  |

|----|-------------|----|-----|

| 2  | Data 1      | 25 | NC  |

| 3  | Data 2      | 24 | NC  |

| 4  | Data 3      | 23 | NC  |

| 5  | Data 4      | 22 | NC  |

| 6  | Data 5      | 21 | NC  |

| 7  | Data 6      | 20 | NC. |

| 8  | Data 7      | 19 | NC  |

| 9  | Data 8      | 18 | NC  |

| 10 | GND         | 17 | NC  |

| 11 | Demand      | 16 | NC  |

| 12 | Data Strobe | 15 | NC  |

| 13 | Ready       | 14 | NC  |

# CENTRONICS PRINTER PORT

| 1  | GND 16                                      | 26  | NC    |              |

|----|---------------------------------------------|-----|-------|--------------|

| 2  | Data 1 — 2                                  | 25  | NC    |              |

| 2  | Data 2 — 3                                  | 24  | NC    | •            |

| ې  |                                             |     |       |              |

| 4  | Data 3 — 4                                  | 23  | NC    |              |

| 5  | Data 4 ——— 5                                | 22  | NC    |              |

| 6  | Data 5 — 6                                  | 21  | NC    |              |

| -  |                                             | 20  | NC    |              |

| 7  | Data 6 — 7                                  | 20  |       |              |

| 8  | Data 7 —— 8                                 | 19  | NC    |              |

| 9  | Data 8 —— 9                                 | 18  | NC    |              |

|    |                                             | 17  | NC    | ,            |

| 10 | GND17                                       | 1.6 |       |              |

| 11 | Acknlg ———————————————————————————————————— | 16  | NC    |              |

| 12 | Data Strobe — 1                             | 15  | NC    |              |

|    |                                             | 111 |       | Drima 21 ?   |

| 13 | Busy —                                      | 14  | Tubac | Prime — 31 ( |

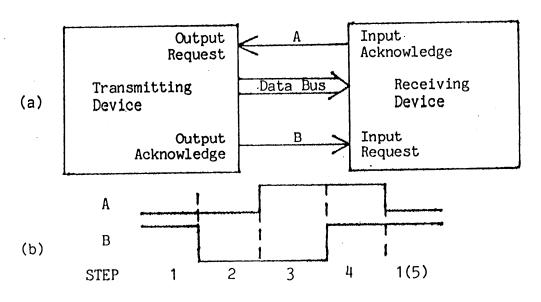

# FOUR-CYCLE MUELLER HANDSHAKE PROTOCOL

asynchronous Four-cycle Mueller handshake is an communication protocol. A data transfer from one device to another requires two control lines and a data path. At each device, one control signal is an input and one control signal is an output. At the device\* receiving data, the output control signal is designated Input Acknowledge and the input control signal is called Input Request. At the device transmitting data, the output control signal is designated Output Request and the input control signal is called Output Acknowledge. To connect the transmitting device to the receiving device Input Acknowledge is tied to Output Request while Output Acknowledge is tied to All of these control signals are active Request. (asserted) at a logic low level except Input Acknowledge, which is active high. This exception makes possible the operation of this communication protocol.

Figure 3a shows a sample of two devices communicating via four-cycle Mueller handshake. The following is a step by step description of a data transfer from the transmitting device on the left to the receiving device on the right. The two controlling signals are labelled A and B and a timing diagram is shown in Figure 3b.

# (1) Request Data Transmission

In the initial state, all outputs are inactive and no data is being passed. Since Input Acknowledge is low in the inactive state and is tied to Output Request, Output Request is asserted and the transmitting device is requested to generate data.

|         | TRANSM | ITTING DEVICE | Ξ        | RECEIV | ING DEVICE  | •        |

|---------|--------|---------------|----------|--------|-------------|----------|

| CONTROL | SIGNAL | NAME          | STATE    | SIGNAL | NAME .      | STATE    |

| A LOW   | Output | Request       | ACTIVE   | Input  | Acknowledge | INACTIVE |

| B HIGH  | Output | Acknowledge   | INACTIVE | Input  | Request     | INACTIVE |

#### (2) Request Data Reception

After the transmitting device places valid data on the data lines, the transmitting device asserts Output Acknowledge and therefore also asserts Input Request at the receiving device.

|         | TRANSM | ITTING DEVICE | Ξ      | RECEIV | ING DEVICE  |          |

|---------|--------|---------------|--------|--------|-------------|----------|

| CONTROL | SIGNAL | NAME          |        |        | 3 11111 113 | STATE    |

| A LOW   | Output | Request       | ACTIVE | Input  | Acknowledge | INACTIVE |

| B LOW   | Output | Acknowledge   | ACTIVE | Input  | Request     | ACTIVE   |

# (3) End Data Reception

After the receiving device accepts data it asserts Input Acknowledge which thereby negates Output Request.

|         | TRANSM | ITTING DEVICE | -      | RECEIVING DEVICE  |        |

|---------|--------|---------------|--------|-------------------|--------|

| CONTROL |        |               | STATE  | DIGHUD HILL       | STATE  |

| A HIGH  | Output | Request       |        | Input Acknowledge |        |

| B LOW   | Output | Acknowledge   | ACTIVE | Input Request     | ACTIVE |

# (4) End Data Transmission

The inactive Output Request then causes the transmitting device to remove data from the data lines and to negate Output Acknowledge which thereby negates Input Request at the receiving device. The data transfer is now complete.

| TRANSMI                      | TTING DEVICE    | 3                 |       | ING DEVICE  |                             |

|------------------------------|-----------------|-------------------|-------|-------------|-----------------------------|

| CONTROL SIGNAL A HIGH Output | NAME<br>Request | STATE<br>INACTIVE | Input | Acknowledge | STATE<br>ACTIVE<br>INACTIVE |

| B HIGH Output                | Acknowledge     | INACTIVE          | Input | Request     | TMACITAE                    |

# (5) Repeat Step (1)

The inactive Input Request at the receiving device then negates Input Acknowledge. Output Request is thereby asserted and another data transmission request cycle is initiated.

| •         | TRANSMI          | TTING DEVICE | -               | RECEIVING DEVICE  |                               |

|-----------|------------------|--------------|-----------------|-------------------|-------------------------------|

| CONTROL S | SIGNAL<br>Output | NAME         | STATE<br>ACTIVE | Input Acknowledge | STATE<br>INACTIVE<br>INACTIVE |

# FIGURE 3 FOUR-CYCLE MUELLER HANDSHAKE

# SPECIFICATIONS

Two Serial and One Parallel Ports Name

with Bootstrap and Terminator

2SP[B[T]]Identification

Dual-width card Dimensions

5.187x8.5" (13.18x21.6cm)

2A @ 5V without termination Power requirements 3A @ 5V with termination

100mA @12V

O to 50 Celsius Operating temperature 32 to 122 Fahrenheit

50, 75, 110,134.5, 150 300, 600, 1200, 1800, 2000 2400, 3600, 4800, 7200, 9600 Serial communication rate

19200, 38400, 76800 baud

with external clock capability

EIA RS-232C, RS-423 or RS422 Serial interface

four-cycle Mueller Parallel interface

Centronics or Data Products Printer interface

1

Parallel output driver

24mA @ 0.5A Sink current -15mA @ 2.4A Source current

Parallel input receiver

-200UA Sink current 20UA Source current 200mV Hysteresis

Bus load

4 layer epoxy glass Construction

#### WARRANTY

Technical Magic warrants to the original purchaser (Customer) of this Product that it is free from defects in materials and workmanship and meets the specifications applicable at time of manufacture. If any failure to meet specifications occurs within one (1) year of original purchase, Customer should contact Technical Magic by mail or telephone to obtain a Repair Number and then return Product, shipping prepaid, to Technical Magic. At its sole expense, Technical Magic will either repair or replace the defective Product and return it, shipping prepaid, to the Customer. Technical Magic's liability, to the extent allowed by law, shall be limited solely to replacement of Product, and this Warranty does not apply to any Product that has been abused, misused, or damaged.

Any Product not covered above may be returned to Technical Magic for prompt repair or refurbishment at our current Service Rate. Contact Technical Magic for further information.