## Model 960B Computer Memory, Memory Controller and Direct Memory Access Channel (DMAC)

Part No. 942773-9702 1 May 1977

# TEXAS INSTRUMENTS

## © Texas Instruments Incorporated 1977 All Rights Reserved

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

No disclosure of the information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments Incorporated.

### LIST OF EFFECTIVE PAGES

INSERT LATEST CHANGED PAGES DESTROY SUPERSEDED PAGES

Note: The portion of the text affected by the changes is indicated by a vertical bar in the outer margins of the page.

Model 960B Computer Maintenance Manual Memory, Memory Controller and Direct Memory Access Channel (DMAC) (942773-9702)

Change 1

...

...

1 September 1975 (ECN 393164)

Revised and Reissued

...

...

1 May 1977 (ECN 419763)

Total number of pages in this publication is 86 consisting of the following:

| PAGE<br>NO.          | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. |

|----------------------|---------------|-------------|---------------|-------------|---------------|

| Cover                | 0             |             |               |             |               |

| Effective Pages      | 0             |             |               |             |               |

| iii-viii             | 0             |             |               |             |               |

| 1-0 - 1-58           | 0             |             |               |             |               |

| 2-1 - 2-6            | 0             |             |               |             |               |

| Alphabetical Index I | Div 0         |             |               |             |               |

| Index-1 - Index-6    | 0             |             |               |             |               |

| User's Response .    | 0             |             |               |             |               |

| Business Reply .     | 0             |             |               |             |               |

| Cover Blank          | 0             |             |               |             |               |

| Cover                | 0             |             |               |             |               |

#### TABLE OF CONTENTS

| Paragraph | Title                                         | Page |

|-----------|-----------------------------------------------|------|

|           | SECTION I. MEMORY SYSTEM                      |      |

| 1.1       | Introduction                                  | 1-1  |

| 1.1.1     | Memory Features                               | 1-1  |

| 1.1.2     | Physical Description                          | 1-1  |

| 1.2       | Memory Controller Circuit Board               | 1-2  |

| 1.2.1     | Memory Controller External Interface          | 1-2  |

| 1.2.2     | Memory Controller to Memory Interface         | 1-10 |

| 1.2.3     | Memory Controller Test Interface              | 1-14 |

| 1.2.4     | Memory Controller Block Diagram               | 1-15 |

| 1.2.5     | Control Circuits                              | 1-19 |

| 1.2.6     | Memory Store                                  | 1-26 |

| 1.2.7     | Memory Fetch                                  | 1-32 |

| 1.2.8     | Error Checking and Correction                 | 1-33 |

| 1.2.9     | Memory Refresh                                | 1-41 |

| 1.2.10    | Reset Control                                 | 1-46 |

| 1.2.11    | Clock Generation                              | 1-47 |

| 1.3       | Memory Circuit Board                          | 1-51 |

| 1.3.1     | Memory Size Jumpers                           | 1-51 |

| 1.3.2     | Power Control and Decoupling                  | 1-53 |

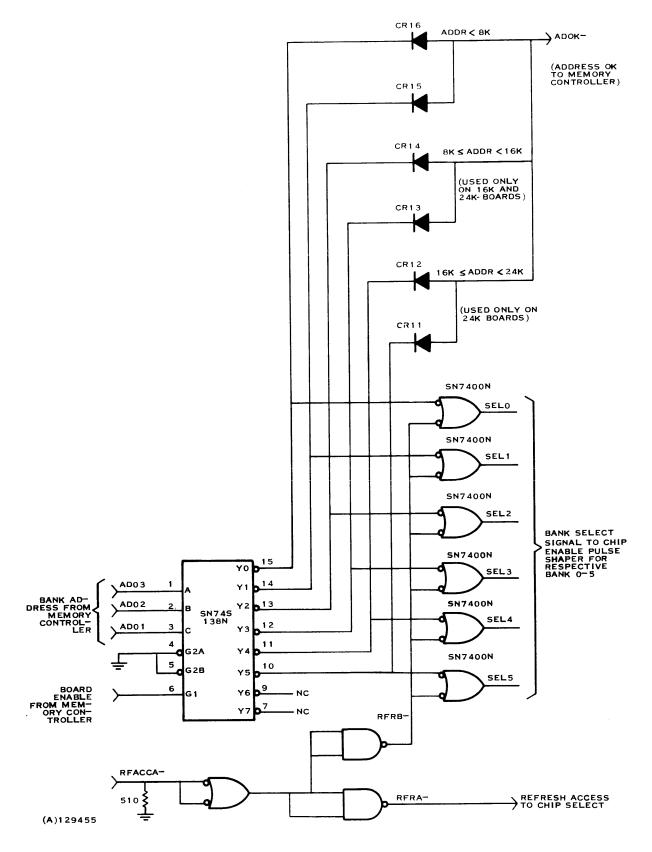

| 1.3.3     | Bank Address Decode                           | 1-53 |

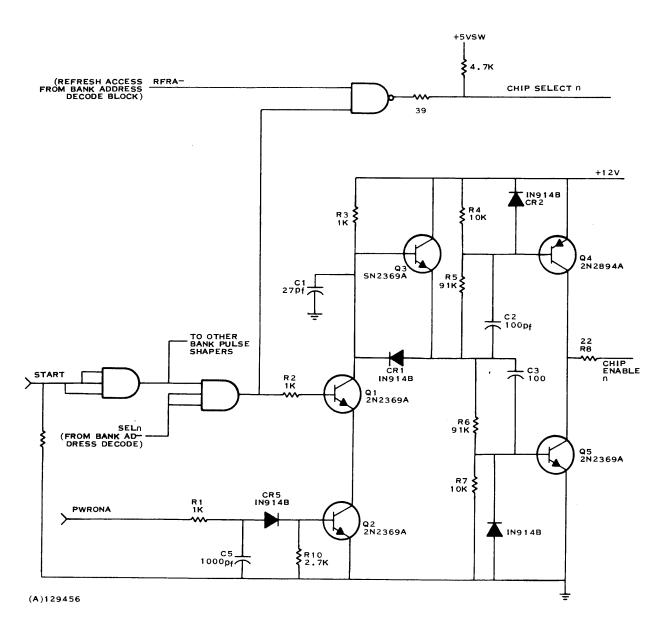

| 1.3.4     | Chip Enable Pulse Shaper                      | 1-55 |

| 1.3.5     | Chip Select                                   | 1-56 |

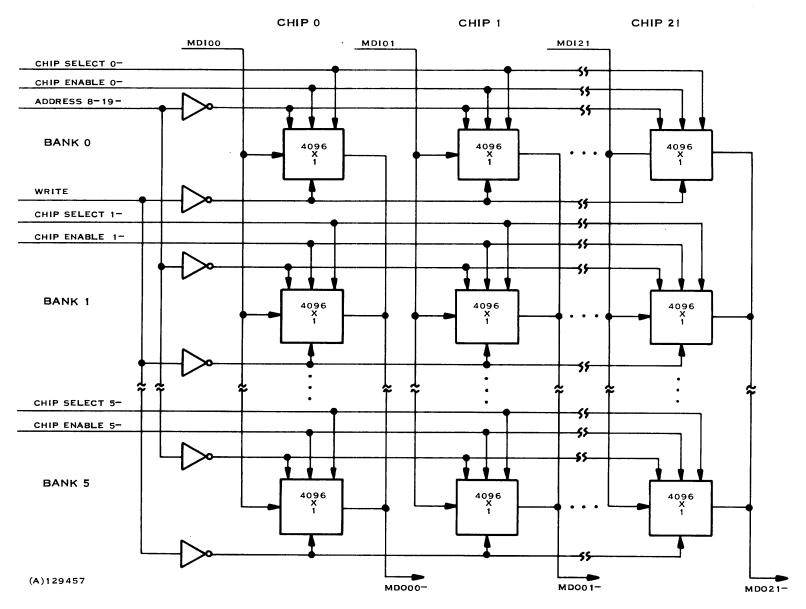

| 1.3.6     | Memory Matrix                                 | 1-56 |

| SECTI     | ON II. DIRECT MEMORY ACCESS CHANNEL INTERFACE |      |

| 2.1       | Introduction                                  | 2-1  |

| 2.2       | Theory of Operation                           | 2-1  |

| 2.2.1     | Memory Address Register                       | 2-1  |

| 2.2.2     | Write Data Register                           | 2-1  |

| 2.2.3     | Read Data Buffers                             | 2-1  |

| 2.2.4     | System Clock                                  | 2-3  |

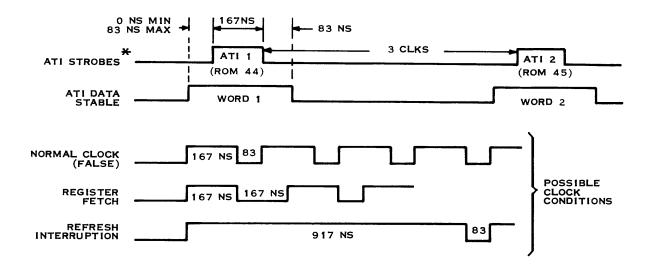

| 2.2.5     | ATI Strobes                                   | 2-3  |

| 2.2.6     | Interrupt Recognized                          | 2-3  |

| 2.2.7     | Access Granted                                | 2-3  |

| 2.2.8     | Parity Error                                  | 2-3  |

| 2.2.9     | Master Reset                                  | 2-3  |

| 2.2.10    | Memory Cycle Complete                         | 2-3  |

| 2.2.11    | Fetch and Store                               | 2-4  |

| 2.2.12    | Access Request                                | 2-4  |

#### LIST OF ILLUSTRATIONS

| Figure | Title                                            | Page  |

|--------|--------------------------------------------------|-------|

| 1-1    | Model 960B Computer Memory System                | 1-0   |

| 1-2    | Memory System Chassis Locations                  | 1 - 3 |

| 1-3    | Memory Controller External Interface and         |       |

|        | Power Connections                                | 1-4   |

| 1-4    | Memory Controller-to-Memory Interface            | 1-10  |

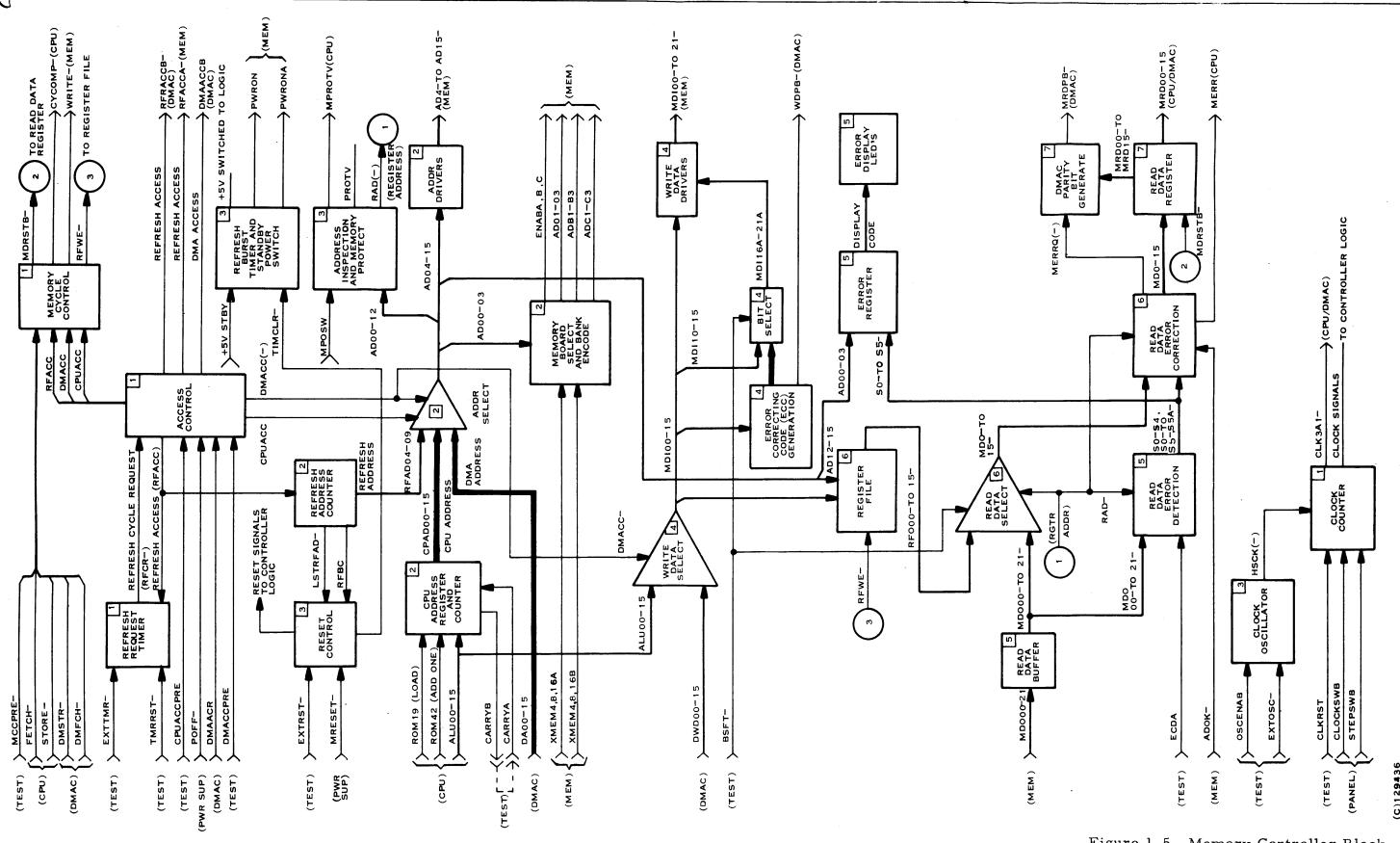

| 1-5    | Memory Controller Block Diagram                  | 1-17  |

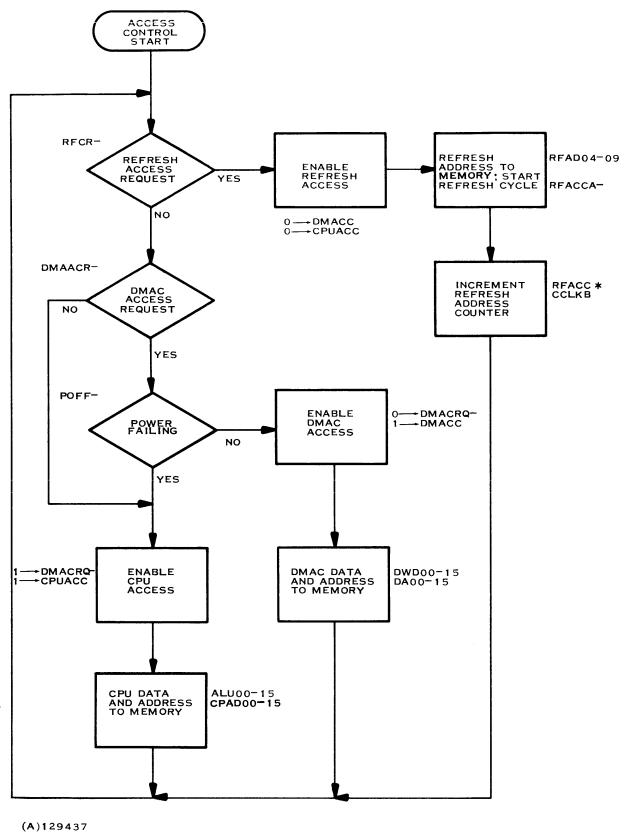

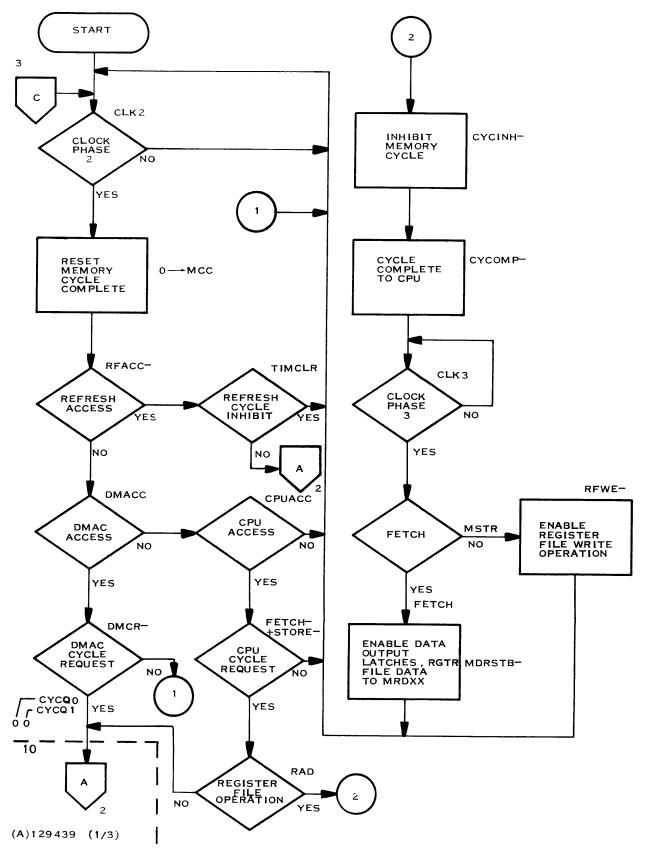

| 1-6    | Access Control Logic Flowchart                   | 1-20  |

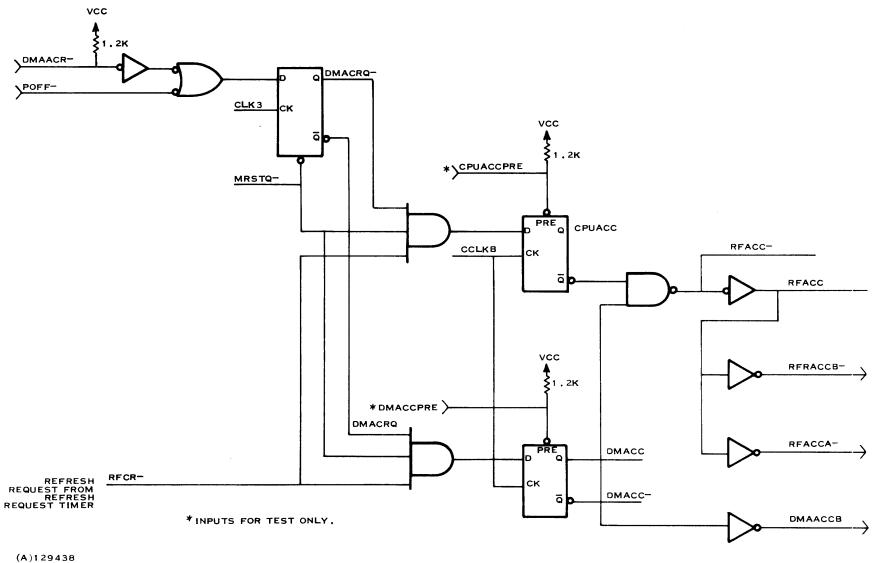

| 1 - 7  | Access Control Simplified Logic Diagram          | 1-22  |

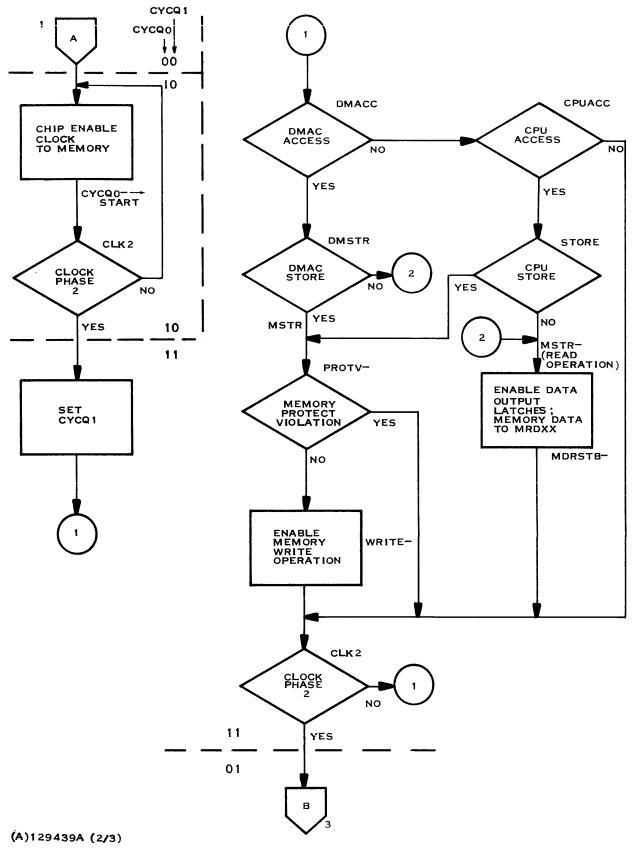

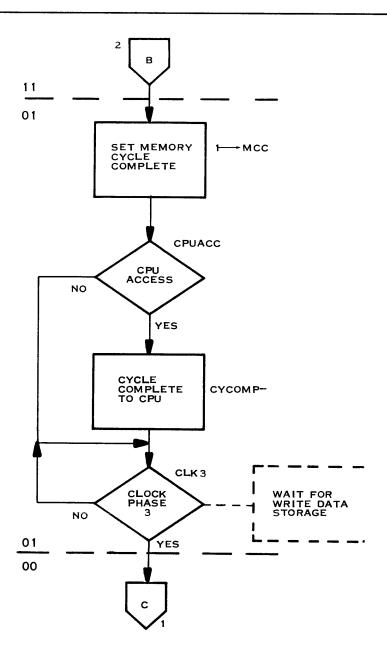

| 1-8    | Memory Cycle Control Logic Flowchart             | 1-23  |

| 1-9    | Memory Board Select and Bank Encode              |       |

|        | Comparison Code                                  | 1-28  |

| 1-10   | Protected Memory Upper Bound Jumper              |       |

|        | Connections                                      | 1-30  |

| 1-11   | Error Correction Check Bit Generation            | 1-34  |

| 1-12   | BSFT - Jumper Connection for Maintenance Use     | 1-35  |

| 1-13   | Error Correcting Gate                            | 1-37  |

| 1-14   | Bank and Bit Error Indicators                    | 1-38  |

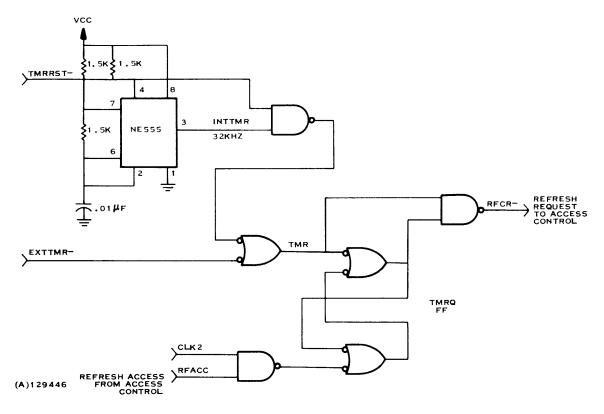

| 1-15   | Refresh Request Timer Simplified Logic Diagram   | 1-42  |

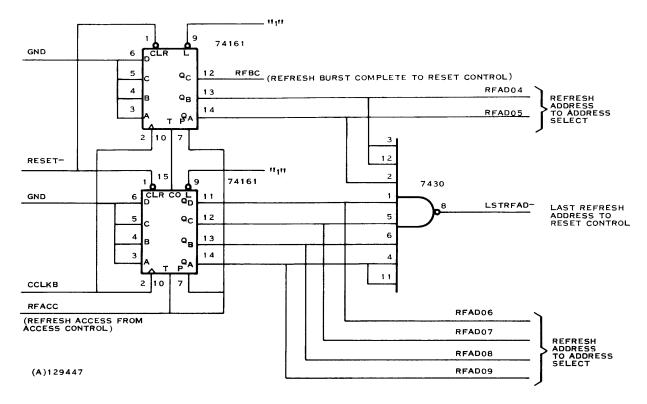

| 1-16   | Refresh Address Counter                          | 1-43  |

| 1-17   | Refresh Burst Timer                              | 1-44  |

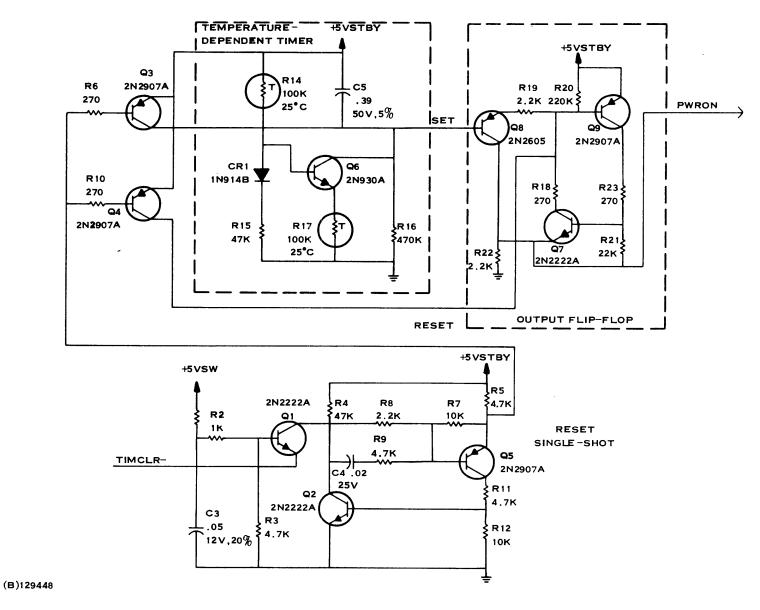

| 1-18   | Standby Power Switch Schematic Diagram           | 1-46  |

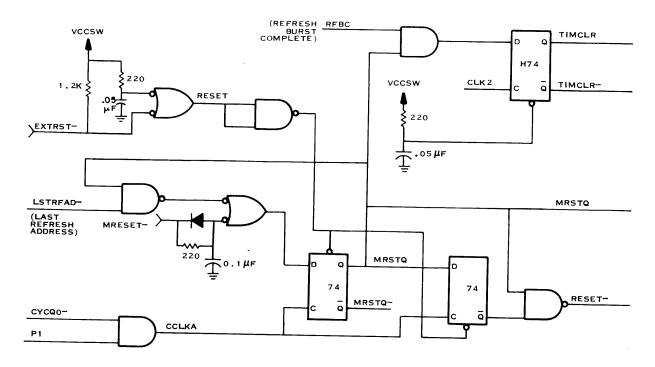

| 1-19   | Reset Control Simplified Logic Diagram           | 1-47  |

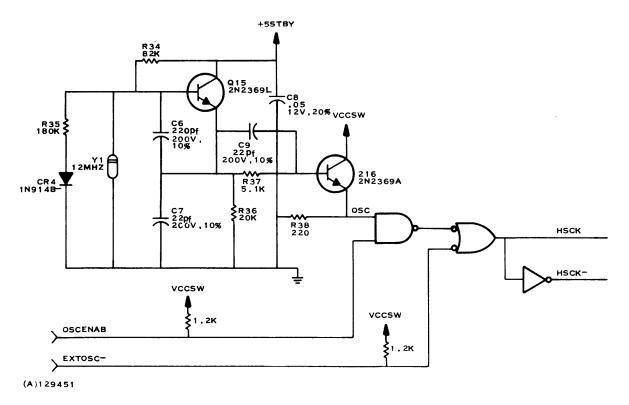

| 1-20   | Clock Oscillator Schematic Diagram               | 1-48  |

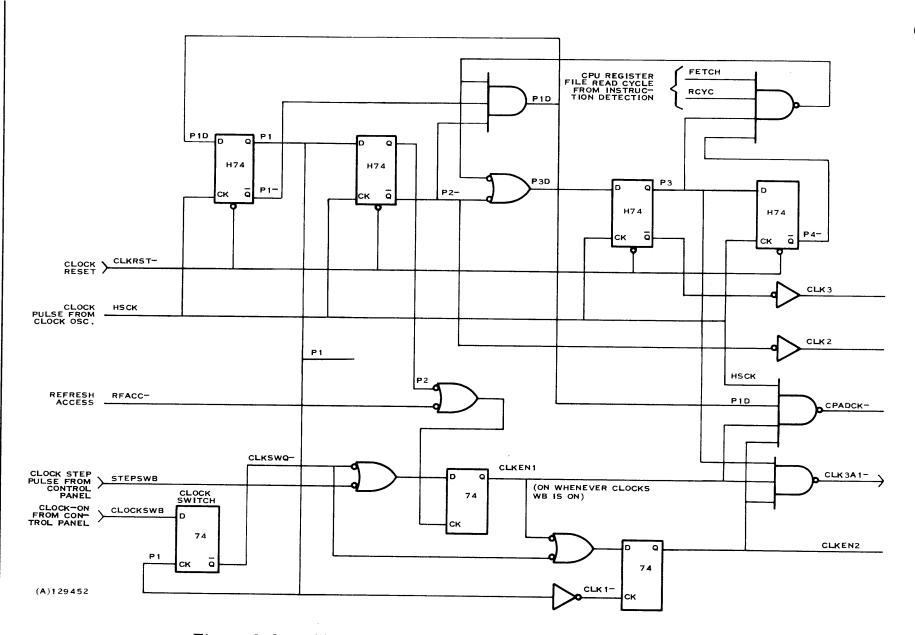

| 1-21   | Clock Counter Circuit (Simplified Logic Diagram) | 1-49  |

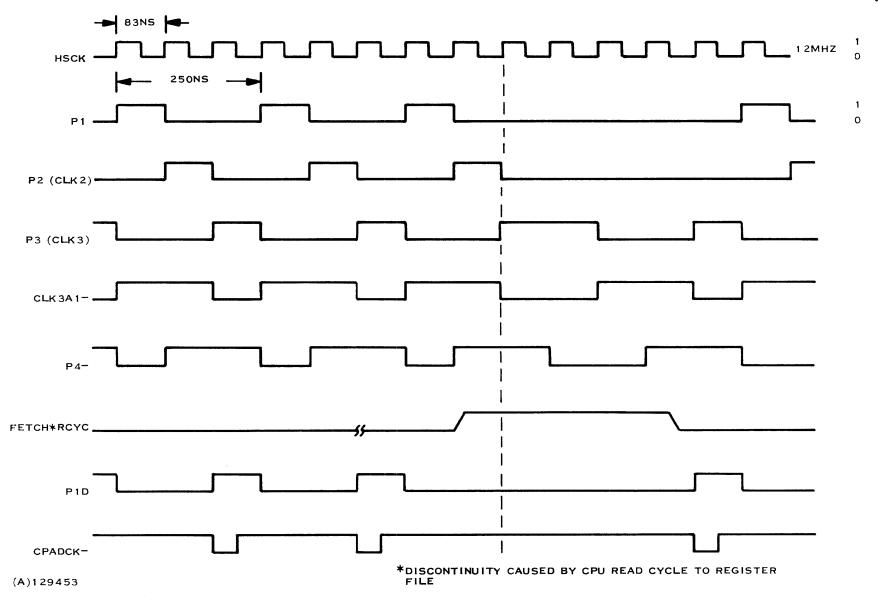

| 1-22   | Clock Counter Circuit Timing Diagram             | 1-50  |

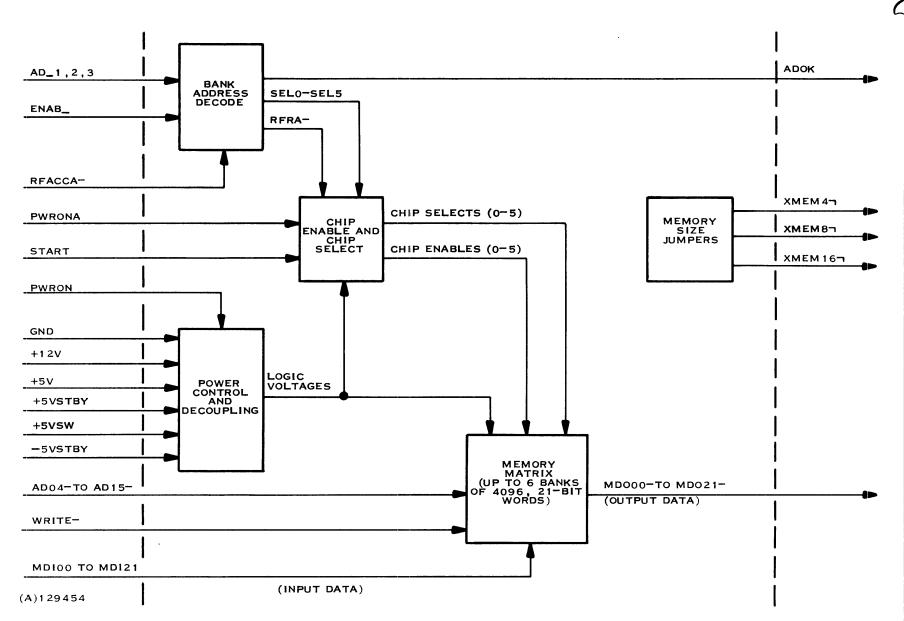

| 1-23   | Memory Board Block Diagram                       | 1-52  |

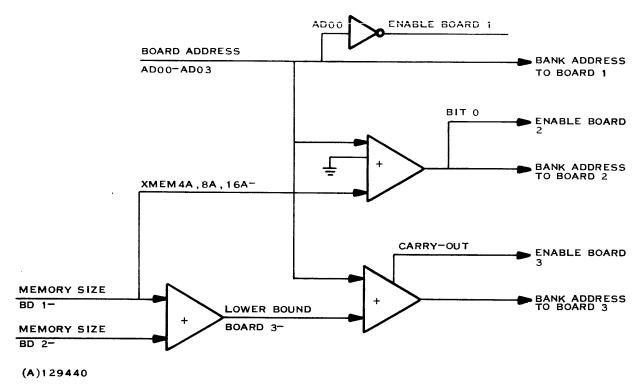

| 1-24   | Bank Address Decode Circuit                      | 1-54  |

| 1-25   | Chip Enable Pulse Shaper-Divider                 | 1-55  |

| 1-26   | Memory Matrix Addressing and Data Paths          | 1-57  |

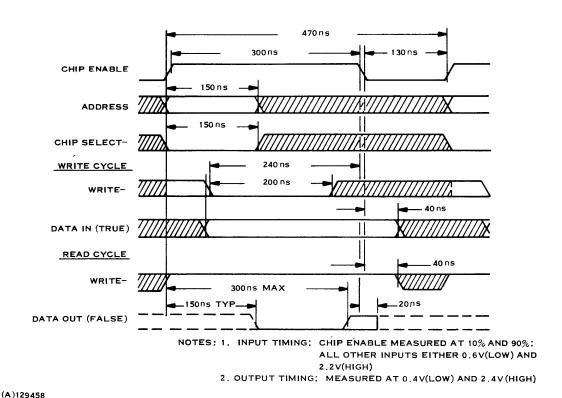

| 1-27   | Memory Chip Optimum Timing Diagram               | 1-58  |

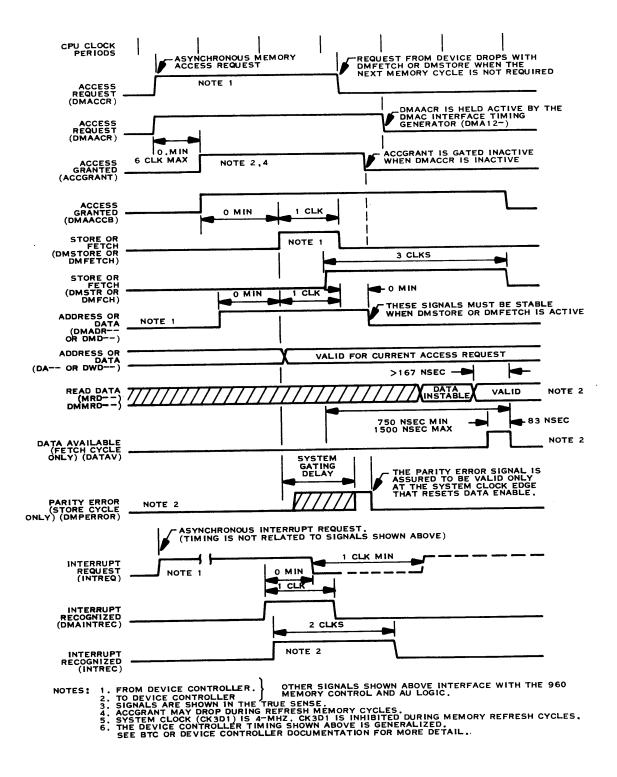

| 2-1    | Controller Interface Signal Relationships        | 2-2   |

#### LIST OF TABLES

| Table        | Title                                         | Page |

|--------------|-----------------------------------------------|------|

| 1-1          | Memory Controller External Interface Signals  | 1-5  |

| 1-2          | Memory Controller to Memory Interface Signals | 1-11 |

| 1-3          | Memory Controller Test Interface Signals      | 1-14 |

| 1-4          | Segmented Areas of Memory                     | 1-29 |

| 1 <b>-</b> 5 | Memory Protect Upper Bound Options            | 1-31 |

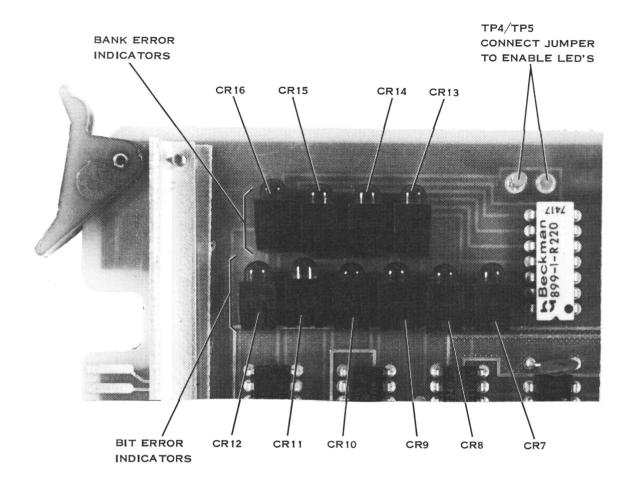

| 1-6          | Bank Error Indicator Decode                   | 1-39 |

| 1-7          | Bit Error Indicator Decode                    | 1-40 |

#### PREFACE

This manual describes the memory system and the Direct Memory Access Channel (DMAC) for the Texas Instruments Model 960B Computer. Section I provides a detailed discussion of the memory controller and memory circuit boards, and includes block diagrams, interface signal definitions, and detailed theory of operation. Section II discusses the DMAC interface. Detailed electrical schematic diagrams for the circuit boards are contained in Model 960B Maintenance Manual Electrical Drawings, TI Part Number 942773-9705. Parts lists for the assemblies are contained in Model 960B Maintenance Manual Parts Lists and Assembly Drawings, TI Part Number 942773-9704. This manual is part of a complete set of manuals that supplies information for maintaining and repairing the computer. The manual set is specifically defined in Model 960B Maintenance Manual System Description, TI Part Number 942773-9701.

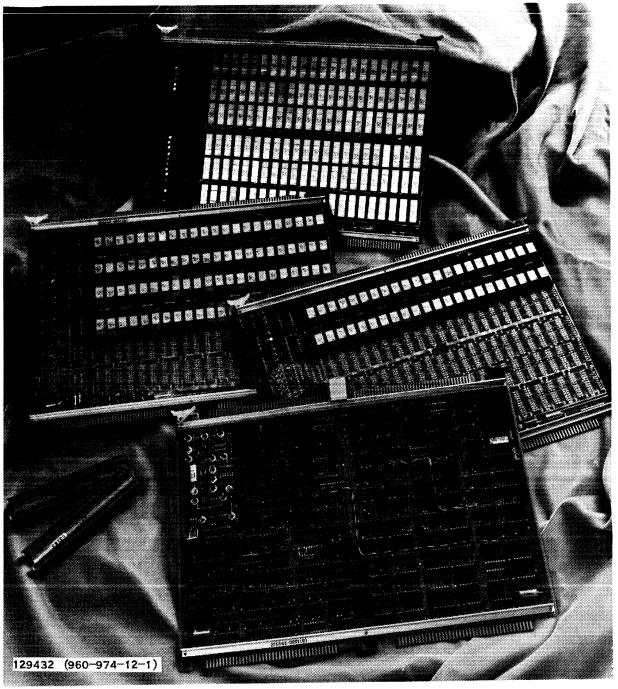

Figure 1-1. Model 960B Computer Memory System

#### SECTION I

#### MEMORY SYSTEM

#### 1.1 INTRODUCTION

The memory system for the Texas Instruments Model 960B Computer consists of a single memory controller circuit board, one, two, or three memory circuit boards, and the interconnecting boards to interface the memory controller to the memory boards as illustrated in figure 1-1. The standard memory configuration offers 8,192 words (8K) of memory and includes one memory circuit board. Optional configurations offer additional memory capacity in increments of 8K words to a maximum capacity of 65,536 words that employs three memory circuit boards. The following paragraphs provide an overview description of the memory system capabilities. The remainder of this section of the manual describes the theory of operation for the memory controller and the memory, and defines the interface between them and the interface between the controller and the requesting interface.

#### 1.1.1 MEMORY FEATURES

The memory system receives data and addresses from either the Central Processing Unit (CPU) or the Direct Memory Access Channel (DMAC) of the computer and performs all data transfer and control operations required to store, retrieve and maintain data within the memory. In addition, the memory system provides the following features:

- A 16-word Register File for high-speed storage and retrieval operations.

- A protected memory area whose size is selectable by jumper wire connections on the memory controller board.

- A temperature-dependent circuit to maintain data in memory when main power is off.

- Error detecting/correcting logic that corrects single-bit errors and detects double-bit errors that occur during a memory read.

- Error indicators that pinpoint the exact memory integrated circuit that caused a correctable memory error.

#### 1.1.2 PHYSICAL DESCRIPTION

Memory control circuitry is TTL family integrated circuit packages and discrete component circuits. Memory storage is performed by a high-density Metal Oxide Semiconductor (MOS) integrated circuit package that provides random access for read or write operations on 4096 individually addressable bits. Each memory package is a 22-pin dual-inline-package (DIP) that is socket-mounted on the memory circuit board for easy replacement in the event of a circuit failure.

- 1.1.2.1 CIRCUIT BOARDS. The printed wiring boards for the memory system are 361.95 mm (14.25 inches) wide and 260.35 mm (10.25 inches) high. Two connectors, Pl and P2, are formed along the bottom edge of the board by printed conductor contacts. The contacts are numbered from 1 through 80 with the even numbered contacts on the component side of the circuit board. An additional tab, slightly offset from center along the bottom edge of the board, prevents the circuit board from being inserted into the chassis connectors when the board is backward. As an additional reminder, one of the ejector tabs on the top of edge of the card is colored and the other tab is white. The colored tab should always be toward the right (as viewed from front of computer) of the chassis. Two additional connectors, P3 and P4, are formed along the top edge of each circuit board. These connectors are identical to P1 and P2 and provide the interface connection between the memory controller and the memory circuit boards.

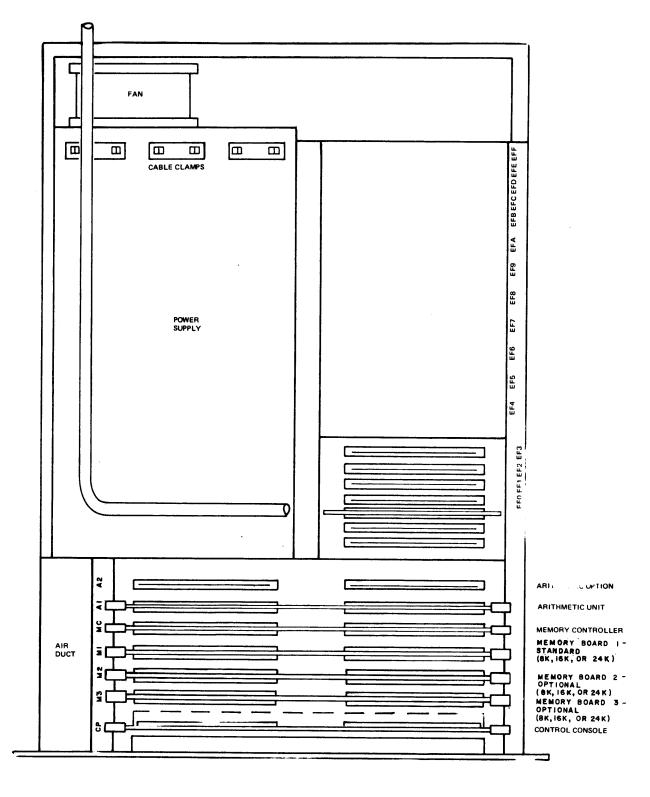

- 1.1.2.2 LOCATION. Figure 1-2 illustrates the placement of the circuit boards within the computer chassis. If only one memory board is used, it must be inserted into the location designated for Memory Board 1 (M1). Similarly, two memory boards must occupy locations designated for Memory Board 1 and Memory Board 2 (M1 and M2). Each memory board may contain either 8K, 16K or 24K words of memory. However, if three memory boards are used and each board contains 24K words, only 65K words of memory will be recognized and usable by the controller.

#### 1.2 MEMORY CONTROLLER CIRCUIT BOARD

The memory controller circuit board selects data and controls data transfer between the computer memory circuit boards and either the Central Processing Unit (CPU) or the Direct Memory Access Channel (DMAC). In addition, the memory controller supplies a rapid-access register file for storage and retrieval of program data, a system clock circuit to coordinate the activities of the controller, memory, and CPU, plus a refresh system to maintain data in the dynamic memory during standby (power loss) operation as well as full power operation. The following paragraphs define the interfaces between the memory controller and the other system components, and describe the operation of the controller circuits for coordination of memory activities.

#### 1.2.1 MEMORY CONTROLLER EXTERNAL INTERFACE

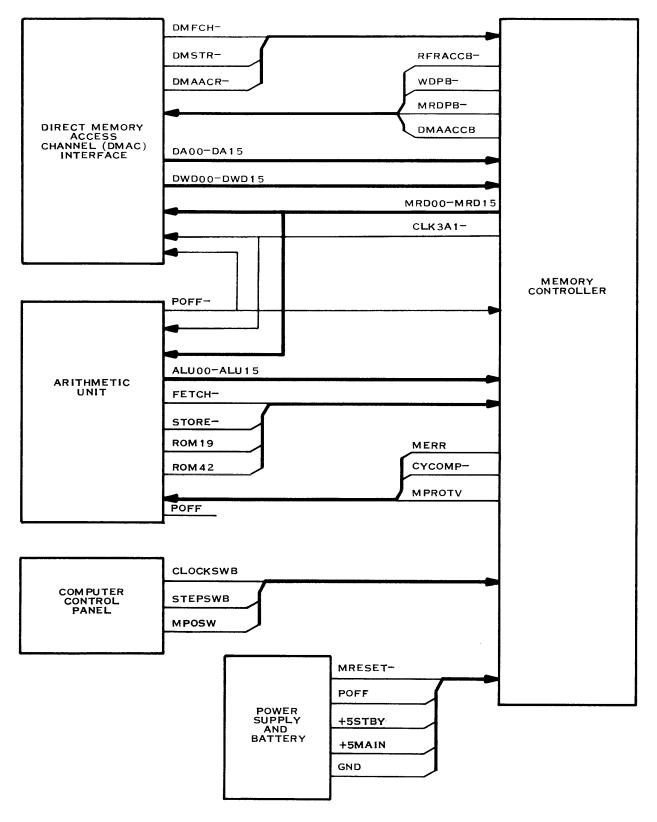

The memory controller provides the interface for the memory system with all computer components external to the memory system. Both the computer arithmetic unit and the Direct Memory Access Channel can request memory operations. In addition, the computer power supply and control panel both supply control signals that modify or regulate the operation of the memory system. Figure 1-3 illustrates these external interface signals. Table 1-1 defines each signal and its function.

(B) 129433

Figure 1-2. Memory System Chassis Locations

(A)129434A

Figure 1-3. Memory Controller External Interface and Power Connections

Table 1-1. Memory Controller External Interface Signals

| Signature                                                                                                                                             | Pin No.                                                                                         | Definition                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK3A1-                                                                                                                                               | P1-16                                                                                           | A system clock signal from the memory controller to the DMAC interface. This signal is also supplied to the AU and CRU interfaces as a system clock. The signal is a 4-MHz, one-third duty cycle clock.                    |

| MRD00<br>MRD01<br>MRD02<br>MRD03<br>MRD04<br>MRD05<br>MRD06<br>MRD07<br>MRD08<br>MRD09<br>MRD10<br>MRD11<br>MRD11<br>MRD12<br>MRD13<br>MRD14<br>MRD15 | P1-71 P1-68 P1-67 P1-72 P1-63 P1-60 P1-12 P1-26 P1-35 P1-11 P1-24 P1-34 P1-56 P1-55 P1-19 P1-18 | Memory Read Data from the memory controller to the DMAC or the AU interface. Read data from either main memory or the register file is held on these lines by buffer latches until the next memory read cycle has started. |

| DMFCH-                                                                                                                                                | P1-45                                                                                           | DMAC Fetch - A single line from the DMAC interface that instructs the memory controller to initiate a memory read cycle.                                                                                                   |

| DMSTR-                                                                                                                                                | P1-43                                                                                           | DMAC Store - This line from the DMAC interface instructs the memory controller to initiate a memory write cycle.                                                                                                           |

| DMAACR-                                                                                                                                               | P1-36                                                                                           | DMAC Access Request - This line from<br>the DMAC interface indicates to the<br>memory controller that the DMAC inter-<br>face requires access to memory.                                                                   |

| DMAACCB                                                                                                                                               | P1-53                                                                                           | DMAC Access Granted - indicates to the DMAC interface that the memory controller has given access to the DMAC in response to a DMAACR- signal.                                                                             |

Table 1-1. Memory Controller External Interface Signals (Continued)

| Signature      | Pin No.        | Definition                                                                                                                                                                                                                                      |

|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFRACCB-       | P1-51          | Refresh Access Granted - indicates to the DMAC interface that a refresh cycle is in progress; DMAC gates off the system clock during refresh cycles in response to this signal.                                                                 |

| WDPB-          | P1-48          | Write Data Parity Bit - a parity bit generated by the memory controller from data being written into memory from the DMAC interface. When low, this line indicates to the DMAC interface that the data contains an odd number of "1" data bits. |

| MRDPB-         | P1-66          | Memory Read Data Parity Bit - a parity bit generated by the memory controller from data being read from memory.  When low, this line indicates to the DMAC interface that the data contains an odd number of "1" data bits.                     |

| DWD00          | P2-22          | DMAC Write Data - 16 input data lines                                                                                                                                                                                                           |

| DWD01          | P2-16          | from the DMAC interface that supply                                                                                                                                                                                                             |

| DWD02          | P2-11          | data to be stored into memory during a                                                                                                                                                                                                          |

| DWD03          | P2-19          | DMAC Store operation.                                                                                                                                                                                                                           |

| DWD04          | P2-10          |                                                                                                                                                                                                                                                 |

| DWD05          | P2-17          |                                                                                                                                                                                                                                                 |

| DWD06          | P2-13          |                                                                                                                                                                                                                                                 |

| DWD07          | P2-09          |                                                                                                                                                                                                                                                 |

| DWD08          | P2-37          |                                                                                                                                                                                                                                                 |

| DWD09          | P2-34<br>P2-30 |                                                                                                                                                                                                                                                 |

| DWD10<br>DWD11 | P2-30<br>P2-28 |                                                                                                                                                                                                                                                 |

| DWD11<br>DWD12 | P2-26<br>P2-29 |                                                                                                                                                                                                                                                 |

| DWD12<br>DWD13 | P2-29<br>P2-42 |                                                                                                                                                                                                                                                 |

| DWD13<br>DWD14 | P2-44          |                                                                                                                                                                                                                                                 |

| DWD14<br>DWD15 | P2-43          |                                                                                                                                                                                                                                                 |

| DA00           | P2-57          | DMAC Memory Address - 16 input lines                                                                                                                                                                                                            |

| DA01           | P2-56          | from the DMAC interface that specify to                                                                                                                                                                                                         |

| DA02           | P2-54          | the memory controller the location in                                                                                                                                                                                                           |

| DA03           | P2-55          | memory that will be accessed during a                                                                                                                                                                                                           |

| DA04           | P2-51          | DMAC memory operation (store or                                                                                                                                                                                                                 |

| DA05           | P2-27          | fetch).                                                                                                                                                                                                                                         |

Table 1-1. Memory Controller External Interface Signals (Continued)

|                                                                              | T                                                           |                                                                                                                                                                                                               |

|------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signature                                                                    | Pin No.                                                     | Definition                                                                                                                                                                                                    |

| DA06<br>DA07<br>DA08<br>DA09<br>DA10<br>DA11<br>DA12<br>DA13<br>DA14<br>DA15 | P2-48 P2-26 P2-25 P2-52 P2-41 P2-45 P2-46 P2-47 P2-50 P2-49 |                                                                                                                                                                                                               |

| MERR                                                                         | P1-49                                                       | Memory Error - This signal from the memory controller indicates to the AU that an uncorrectable error has occurred in data read from memory and that the data on the MRDxx data bus is incorrect.             |

| FETCH-                                                                       | P1-42                                                       | CPU Fetch - This signal from the AU instructs the memory controller to initiate a read cycle from either the register file or main memory.                                                                    |

| STORE-                                                                       | P1-33                                                       | CPU Store - This signal from the AU instructs the memory controller to initiate a write cycle to either the register file or main memory.                                                                     |

| ROM19                                                                        | P1-22                                                       | Address Load Enable - This signal from the AU indicates to the memory controller that the data on the ALUxx bus is an address rather than data. The controller then loads the data into its address register. |

| ROM42                                                                        | P2-64                                                       | Address Increment - This signal from the AU increments the address currently contained in the memory controller address register to allow sequential access to contiguous memory locations.                   |

| ALU00<br>ALU01<br>ALU02                                                      | P2-24<br>P2-18<br>P2-12                                     | Write Data and Address - These 16 lines from the AU supply either data to be written into a specified memory location,                                                                                        |

Table 1-1. Memory Controller External Interface Signals (Continued)

| Signature | Pin No.       | Definition                                                                                                                                                                                                                                                                                     |

|-----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1 111 110.    | Bernitten                                                                                                                                                                                                                                                                                      |

| ALU03     | P2-20         | or an address to specify a memory loca-                                                                                                                                                                                                                                                        |

| ALU04     | P2-14         | tion for either a fetch or store operation.                                                                                                                                                                                                                                                    |

| ALU05     | P2-21         | The use of this bus is defined by the state                                                                                                                                                                                                                                                    |

| ALU06     | P2-15         | of the ROM19 interface signal.                                                                                                                                                                                                                                                                 |

| ALU07     | P2-23         |                                                                                                                                                                                                                                                                                                |

| ALU08     | P2-36         |                                                                                                                                                                                                                                                                                                |

| ALU09     | P2-35         |                                                                                                                                                                                                                                                                                                |

| ALU10     | P2-32         |                                                                                                                                                                                                                                                                                                |

| ALU11     | P2-31         |                                                                                                                                                                                                                                                                                                |

| ALU12     | P2-59         |                                                                                                                                                                                                                                                                                                |

| ALU13     | <b>P2-</b> 58 |                                                                                                                                                                                                                                                                                                |

| ALU14     | P2-38         |                                                                                                                                                                                                                                                                                                |

| ALU15     | P2-33         |                                                                                                                                                                                                                                                                                                |

| CYCOMP-   | P1-20         | Cycle Complete - This signal from the memory controller indicates to the AU that the current memory operation (read or write to memory or register file) is complete.                                                                                                                          |

| MPROTV    | P1-21         | Memory Protect Violate - This signal from the memory controller indicates to the AU that the last store operation attempted to write into an area in protected memory and was, therefore, not honored.                                                                                         |

| CLOCKSWB  | P1-47         | System Clock Enable - When low, this signal from the operator panel CLOCK/STEP switch indicates that the switch is in the OFF (center) position, and disables generation of the system clock in the memory controller.                                                                         |

| STEPSWB-  | P1-58         | System Clock Step - This signal from the operator panel CLOCK/STEP switch indicates that the switch has been moved to the STEP (momentary down) position, and instructs the memory controller to produce a single system clock pulse, when the STEP SWITCH is returned to the center position. |

Table 1-1. Memory Controller External Interface Signals (Continued)

|           | T                                                | <b>\$</b>                                                                                                                                                                                                                                                                    |

|-----------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signature | Pin No.                                          | Definition                                                                                                                                                                                                                                                                   |

| MPOSW     | P1-23                                            | Memory Protect Override Switch - This signal from the operator panel MPO switch indicates that the switch is in the ON (up) position, and enables the memory controller to store data in protected memory.                                                                   |

| MRESET-   | P2-61                                            | Master Reset - This signal from the computer power supply indicates that AC power has been interrupted. The signal initializes the memory controller during power application, and inhibits the start of a new memory cycle if a power failure or power removal is imminent. |

| POFF-     | P1-52                                            | Power Failing - This signal indicates to the memory controller that interruption of power to the computer is imminent. The controller then prevents memory access from the DMAC interface so that the CPU may execute its power down routine before main power is removed.   |

| +5 STBY   | P2-7,8,73,74                                     | Standby Power - +5 Vdc that remains on to power the memory controller circuits during refresh bursts when main power has failed and the memory is being maintained by the battery.                                                                                           |

| +5 MAIN   | P1-3,4,77,78<br>P2-3,4,77,78                     | Main Power - +5 Vdc to power the memory controller circuits during normal operation when ac power is present in the power supply.                                                                                                                                            |

| GND       | P1-1,2,39,40,<br>79,80<br>P2-1,2,39,40,<br>79,80 | Ground                                                                                                                                                                                                                                                                       |

|           |                                                  |                                                                                                                                                                                                                                                                              |

#### 1.2.2 MEMORY CONTROLLER TO MEMORY INTERFACE

The memory controller generates a set of control signals to initiate data transfer between the memory controller and the memory circuit boards. The interface may be implemented with one, two or three memory circuit boards. The interface signals are carried through the top edge connectors of the memory controller and the memory circuit boards. Special interconnect boards complete the connection between the memory controller and one, two or three memory boards. For the three different configurations, the interconnect board part numbers are as follows:

|                             |   | Right (P3) | <u>Left (P4)</u> |

|-----------------------------|---|------------|------------------|

| One Memory Circuit Board    | _ | 943718     | 943718           |

| Two Memory Circuit Boards   | - | 943706     | 943705           |

| Three Memory Circuit Boards | - | 943716     | 943714           |

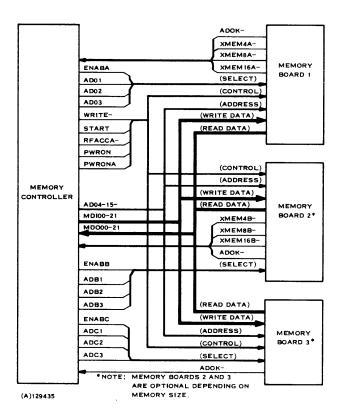

Figure 1-4 illustrates the interface signals between the controller and the memory boards. Table 1-2 lists these signals and defines their function.

Figure 1-4. Memory Controller-to-Memory Interface

Table 1-2. Memory Controller to Memory Interface Signals

| Signature      | Pin No. | Definition                            |

|----------------|---------|---------------------------------------|

| MDO00          | P4-51   | Memory read data output from memory   |

| MDO01          | 43      | to memory controller.                 |

| MDO02          | 35      | de momory controller.                 |

| MDO03          | 27      |                                       |

| MDO04          | 19      |                                       |

| MDO05          | 13      |                                       |

| MDO06          | 09      |                                       |

| MDO07          | 05      |                                       |

| MDO08          | P4-04   |                                       |

| MDO09          | P3-75   |                                       |

| MDO10          | 71      |                                       |

| MDO11          | 63      |                                       |

| MDO12          | 55      |                                       |

| MDO13          | 47      |                                       |

| MDO14          | 39      |                                       |

| MDO15          | P3-31   |                                       |

| MDO16          | -       |                                       |

| MDO16<br>MDO17 | P3-23   | Error check bits from memory during a |

| MDO17<br>MDO18 | 17      | read operation.                       |

| 3              | 13      |                                       |

| MDO19<br>MDO20 | 09      |                                       |

| MDO21          | 05      |                                       |

| MDOZI          | P3-04   |                                       |

| MDI00-         | P4-53   | Memory write data input from memory   |

| MDI01-         | 45      | controller to memory.                 |

| MDI02 -        | 37      | ,                                     |

| MDI03-         | 29      |                                       |

| MDI04-         | 21      |                                       |

| MDI05-         | 15      |                                       |

| MDI06-         | 11      |                                       |

| MDI07-         | 07      |                                       |

| MDI08-         | P4-03   |                                       |

| MDI09-         | P3-77   |                                       |

| MDII0-         | 73      |                                       |

| MDIII-         | 65      |                                       |

| MDI12-         | 57      |                                       |

| MDI13-         | 49      |                                       |

| MDI14-         | 41      |                                       |

| MDI15-         | P3-33   |                                       |

|                |         |                                       |

|                |         |                                       |

Table 1-2. Memory Controller to Memory Interface Signals (Continued)

| Signature                                                                                       | Pin No.                                   | Definition                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDI16-<br>MDI17-<br>MDI18-<br>MDI19-<br>MDI20-<br>MDI21-                                        | P3-25<br>19<br>15<br>11<br>07<br>P3-03    | Error check bits to memory during a write operation.                                                                                                                                                                                          |

| AD04-<br>AD05-<br>AD06-<br>AD07-<br>AD08-<br>AD10-<br>AD11-<br>AD12-<br>AD13-<br>AD14-<br>AD15- | P4-73 69 77 75 67 61 71 63 65 59 55 P4-57 | Least significant 12 bits of address from CPU or DMAC used as a store or fetch address when accessing a memory location. The most significant six bits of this address is generated internal to the controller for use during refresh cycles. |

| ADOK-                                                                                           | P4-39                                     | A low active signal indicating that the memory board has accepted an address as valid.                                                                                                                                                        |

| ENABA                                                                                           | P4-72                                     | Memory Board Select to enable bank de-<br>coder on board 1.                                                                                                                                                                                   |

| ENABB                                                                                           | P4-54                                     | Memory Board Select to enable bank decoder on board 2.                                                                                                                                                                                        |

| ENABC                                                                                           | P4-58                                     | Memory Board Select to enable bank decoder on board 3.                                                                                                                                                                                        |

| AD01<br>AD02<br>AD03                                                                            | P4-74<br>P4-76<br>P4-78                   | A 3-bit code sent to memory board 1 to indicate which bank (0-5) of memory chips is to be cycled. AD03 is the least significant bit of the code.                                                                                              |

| ADB1<br>ADB2<br>ADB3                                                                            | P4-62<br>P4-60<br>P4-52                   | A 3-bit code sent to memory board 2 to indicate which bank (0-5) of memory chips is to be cycled. ADB3 is the least significant bit of the code.                                                                                              |

Table 1-2. Memory Controller to Memory Interface Signals (Continued)

| Signature                      | Pin No.                 | Definition                                                                                                                                                                                                                              |  |  |  |  |  |

|--------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ADC1<br>ADC2<br>ADC3           | P4-48<br>P4-50<br>P4-56 | A 3-bit code sent to memory board 3 to indicate which bank (0-5) of memory chips is to be cycled. ADC3 is the least significant bit of the code.                                                                                        |  |  |  |  |  |

| XMEM4A-<br>XMEM8A-<br>XMEM16A- | P3-27<br>P3-29<br>P3-21 | A 3-bit complement code from memory board 1 that designates to the memory controller the size of the memory contained on the memory board. Valid codes are:                                                                             |  |  |  |  |  |

|                                |                         | 1       8-       4-         1       0       1       8K memory         0       1       16K memory         0       0       1       24K memory                                                                                             |  |  |  |  |  |

| XMEM4B-<br>XMEM8B-<br>XMEM16B- | P3-28<br>P3-30<br>P3-22 | A 3-bit complement code from memory board 2 that designates to the memory controller the size of the memory contained on the memory board. Valid codes are the same as for XMEM_A  No memory size code is required from memory board 3. |  |  |  |  |  |

| WRITE-                         | P4-64                   | When a logic one, this signal indicates that a read cycle is to be performed from the addressed memory location. When this line is a logic zero, the memory performs a write operation.                                                 |  |  |  |  |  |

| START                          | P4-70                   | This signal initiates a memory cycle in the addressed memory board. A discrete clock driver on the memory board changes the signal level to +12 Vdc (active) and 0 Vdc (inactive) to drive the clock input of the MOS memory chips.     |  |  |  |  |  |

| RFACCA-                        | P4-68                   | When coincident with START, this signal initiates a refresh cycle in all of the memory chips. The refresh address is determined by the address lines from the memory controller.                                                        |  |  |  |  |  |

Table 1-2. Memory Controller to Memory Interface Signals (Continued)

| Signature | Pin No.                      | Definition                                                                                                                                                                                                |

|-----------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

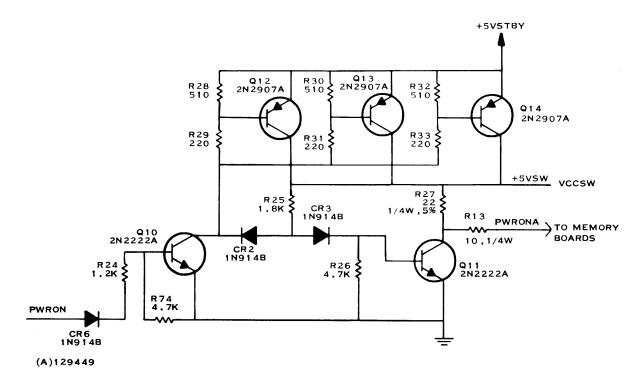

| PWRON     | P3-37                        | This signal to the memory boards turns on +5 Vdc (switched) to the logic elements. When computer main power drops, this signal drops, disabling power to the logic elements except during refresh bursts. |

| PWRONA    | P4-66                        | This signal is a delayed power-on signal that disables memory clock until +5 Vdc (switched) becomes stable after being switched on. During normal power conditions, this signal is a logic one.           |

| GND       | P3-1,2,79,80<br>P4-1,2,79,80 | Signal Ground                                                                                                                                                                                             |

#### 1.2.3 MEMORY CONTROLLER TEST INTERFACE

The memory controller circuit board also provides for test monitoring and control of the circuits for checkout and maintenance purposes. Table 1-3 defines the function of each of these checkout signals.

Table 1-3. Memory Controller Test Interface Signals

| Signature | Pin No. | Definition                                                                                                                                                                                          |  |  |  |  |

|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CARRYB    | P2-53   | Output from the CPU address Register and Counter that indicates a carry-out from the least significant eight bits.                                                                                  |  |  |  |  |

| CARRYA    | P2-69   | Input to the most significant eight bits of the CPU address Register and Counter. Allows the counter to be incremented by 256 word jumps.                                                           |  |  |  |  |

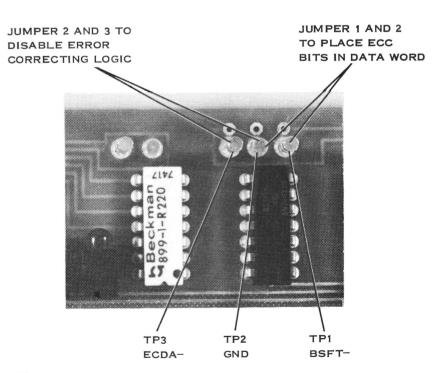

| BSFT-     | P2-66   | Input that, when low, places bits 10-15 of the data word in place of ECC bits 16-21 during a store operation, and places ECC bits 16-21 into bits 10-15 during a read. Replaced bits are discarded. |  |  |  |  |

| CLKRST-   | P1-15   | Input that, when low, clears the clock counter circuit.                                                                                                                                             |  |  |  |  |

Table 1-3. Memory Controller Test Interface Signals (Continued)

| Signature | Pin No. | Definition                                                                                                                                  |  |  |  |  |

|-----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CPUACCPRE | P3-68   | Preset input for the CPUACC FF in the Access Control logic.                                                                                 |  |  |  |  |

| DMACCPRE  | P1-17   | Preset input for the DMACC FF in the Access Control logic.                                                                                  |  |  |  |  |

| ECDA-     | P1-73   | Input that, when low, disables the error correction logic.                                                                                  |  |  |  |  |

| EXTOSC-   | P1-32   | Allows connection of an external oscillator to replace the clock oscillator for the system clock.                                           |  |  |  |  |

| EXTRST-   | P2-67   | Reset signal used for test only.                                                                                                            |  |  |  |  |

| EXTTMR-   | P1-44   | Allows connection of an external timer to generate refresh requests during full power operation.                                            |  |  |  |  |

| MCCPRE-   | P1-50   | Preset input for the Memory Cycle Complete FF (MCC FF)                                                                                      |  |  |  |  |

| OSCENAB   | P1-13   | Input that, when low, disables the internal oscillator in the system clock circuit. This input must be low in order to use the EXTOSCinput. |  |  |  |  |

| TMRRST-   | P1-46   | Input that, when low, resets the Refresh Request Timer.                                                                                     |  |  |  |  |

NOTE: CARRYA and CARRYB are connected on the backplane when the memory controller is plugged into the system.

#### 1.2.4 MEMORY CONTROLLER BLOCK DIAGRAM

To aid in understanding the flow of data and control lines through the memory controller, figure 1-5 illustrates the major functional circuits within the controller and their interrelationship. This diagram is the basis of the detailed theory discussion that appears later in this section. The block diagram is a generalized version of the logic diagrams for the memory controller. The following paragraphs describe the format and special conventions used on the diagram to provide better understanding of information contained on the diagram.

1.2.4.1 LOGIC DIAGRAM PAGE NUMBER. Each functional block on the diagram represents a logic or electrical circuit that is represented in detail in the logic diagram for the memory controller. To facilitate location of the circuit within the logic diagram, the sheet number of the logic diagram that

Figure 1-5. Memory Controller Block Diagram

contains the major portion of the functional circuit appears in the upper right corner of the functional block as illustrated below:

1.2.4.2 EXTERNAL ORIGINS AND DESTINATIONS. Signals that leave or enter the circuit board through connector pins have their origins or destinations indicated in parentheses as follows:

| (CPU)     | Central Processing Unit         |

|-----------|---------------------------------|

| (MEM)     | Memory Circuit Board            |

| (DMAC)    | Direct Memory Access Channel    |

| (TEST)    | Special Test Fixture Connection |

| (PWR SUP) | Power Supply                    |

1.2.4.3 MULTIPLE SIGNAL PATHS. Bold lines represent a large group of signals or a data bus. Lines that carry both the true and false sense signal are labeled with the false sense indicator (a dash) in parentheses following the signature:

SIGNAL(-)

#### 1.2.5 CONTROL CIRCUITS

The memory controller has two major control circuits that coordinate data transfers and refresh cycles throughout the memory system. The Access Control circuit determines the origin of a memory cycle to be either from the CPU or DMAC interfaces or a result of a memory refresh cycle. Concurrently, the Memory Cycle Control circuit determines whether the cycle will be a store or a fetch operation and indicates the end of the memory cycle. The following paragraphs explain the operation of these control circuits.

1.2.5.1 ACCESS CONTROL. Access Control determines the origin of a memory access and generates gating signals that select input data and addresses and that determine the timing of a register file memory cycle. Refresh cycle requests receive highest priority and are always recognized. DMAC requests receive next consideration. In the absence of either of these two memory requests, the circuit enables CPU memory access. Figure 1-6 illustrates the Access Control logical decision paths.

Figure 1-6. Access Control Logic Flowchart

Circuit Description. Access Control consists of three flip-flops and associated gating circuitry as illustrated in figure 1-7. A refresh request from the Refresh Request Timer disables the input gates to the two access control flip-flops (CPUACC and DMACC) clearing both flip-flops with the next clock pulse. With both flip-flops clear, the circuit produces four refresh cycle recognition signals: RFACC-, RFACC, RFRACCB- and RFACCA-. The first two signals are internal gating signals. RFRACCB- returns to the DMA Controller to disable system clock pulses during a refresh cycle so that the DMA Controller is unaware of the refresh cycle. RFACCA- is forwarded to the memory boards to initiate the refresh cycle. During standby operation, refresh access is continually granted during a refresh burst because MRSTQ- is low, disabling the access control flip-flops.

DMACRQ-FF. In the absence of a refresh request, the DMACRQ-FF sets or clears the access control flip-flops. This flip-flop clears when it receives a memory request from the DMAC interface (DMAACR-), and no power failure is about to occur (POFF-). Clearing this flip-flop sets the DMACC FF on the next clock pulse to enable DMAC data and address into memory. In the absence of a DMAC request, or if a power failure is about to occur, the DMACRQ-FF sets. Setting this flip-flop sets the CPUACC FF to gate data and address from the CPU into memory. Enabling CPU data during a power failure allows the CPU to store certain program parameters before power fails.

1.2.5.2 MEMORY CYCLE CONTROL. Memory Cycle Control monitors the store and fetch signals from both the CPU and the DMAC interfaces, receives destination information from the Address Inspection circuit and generates the gating signals required to transfer data through the controller to or from the specified area in memory. This circuit also receives inputs from the Access Control circuit to enable requests from either the DMAC or the CPU interface. The control logic consists of two state-control flip-flops, CYCQ0 and CYCQ1, plus the combinational logic required to define the four possible controller states and generate the gating signals required during each controller state. All memory operations except a register file operation must progress through each of the four controller states, and require three phase 2 clock times to perform the cycle. Register file operations are performed entirely within state 00. Figure 1-8 illustrates the logic flow within the controller that produces the required gating signals. The following paragraphs describe the decisions within each state.

State 0. Controller State 0 (CYCQ0 and CYCQ1 both clear) monitors the inputs to the controller to determine what type of cycle is to be requested. Upon entering the state, the controller clears the Memory Cycle Complete flip-flop (MCC) that was set at the end of the previous memory cycle. Clearing this flip-flop enables a new memory access. The controller then determines which interface has access to memory and whether that interface has requested access to memory. If the DMAC interface has access and has

Figure 1-7. Access Control Simplified Logic Diagram

Figure 1-8. Memory Cycle Control Logic Flowchart (Sheet 1 of 3)

Figure 1-8. Memory Cycle Control Logic Flowchart (Sheet 2 of 3)

(A)129439A (3/3)

Figure 1-8. Memory Cycle Control Logic Flowchart (Sheet 3 of 3)

generated a memory request, the controller enters State 2 (CYCQ0 set; CYCQ1 clear). If the CPU has access and has requested memory, the controller determines if the operation is intended for the register file. If the operation is for main memory, the controller enters State 2. If the operation is a register file operation, the controller prevents the start of a new memory cycle to main memory, issues Cycle Complete to the CPU (without setting MCC), and produces the gating signal required to complete either the store or fetch operation. Register file operations occur within one clock period. However, a register file fetch operation extends the period of the system clock to allow for increased propagation time delays. This modification of the clock signal is performed within the Clock Counter circuit.

State 2. Setting the CYCQ0 flip-flop immediately produces a chip enable signal (START) to the memory boards. This signal remains high as long as CYCQ0 is set. The controller waits for a phase 2 clock pulse before entering State 3.

State 3. In State 3 (CYCQ0 set; CYCQ1 set) the controller determines if the operation is a store or a fetch operation. If the operation is a fetch, the controller generates MDRSTB- to transfer memory data to the output data latches for placement on the memory bus to the requesting interface (DMAC or CPU). If the operation is a store, the controller produces a WRITE- signal to the memory boards if the operation is not intended for a protected area in memory. Store operations to protected memory do not produce a WRITE- signal; the memory boards perform a non-destructive read operation. In all cases the controller enters State 1 with the next phase 2 clock pulse.

<u>State 1</u>. In State 1 (CYCQ0 clear; CYCQ1 set) the controller sets the Memory Cycle Complete flip-flop (MCC). If the cycle is a CPU memory access, the controller also enables the cycle complete indication (CYCOMP-) to the CPU. The controller then waits for the phase 3 clock pulse to return it to the State 0 wait mode.

#### 1.2.6 MEMORY STORE

If Memory Cycle Control determines that the operation is a store, then the controller will receive both data and address from the interface selected by Access Control. The controller then examines the address to determine the destination of the store operation, and generates the addressing signals required to properly route the data to the correct location in memory or in the register file. Concurrently, the controller examines data for memory and generates an Error Checking and Correcting (ECC) code that is stored along with the data in memory. The Error Checking and Correcting circuits are discussed separately, later in this section. The following paragraphs explain the function of each major circuit involved in the memory store operation. Although the addressing circuits are used during both store and fetch operations, they will be described only in reference to store operations. Their function is identical for a fetch operation.

- 1.2.6.1 CPU ADDRESS REGISTER AND COUNTER. The CPU uses the same bus lines to carry both data and addresses to the memory controller. Therefore, the memory controller must retain the address from the CPU while the data is being transferred. The CPU Address Register performs this function, and also allows the CPU to transmit a single increment signal to access consecutive memory locations instead of sending new addresses for each location. If the data on the ALU0-15 bus from the CPU is an address, the CPU activates the ROM19 interface signal. This signal, together with the recognized CPU request, gates the address from the data bus into the address register. This address remains in the register until replaced or modified by another CPU command. The output from the register is then available to the Address Select circuit for transfer to the memory boards, the Address Inspection circuit, and to the register file as required. To access the next consecutive memory location, the CPU activates the ROM42 interface signal. This signal enables the next clock pulse (CPADCK-) to increment the address in the register. For test and checkout purposes, the carry from the least significant byte to the most significant byte (CARRYB/CARRYA) is routed through the main chassis connector. This connection not only allows the carry signal to be monitored, but permits the address in the register to be jumped in 256 address blocks if connected to the proper test fixture. These two signals are normally connected together in the computer backplane.

- 1.2.6.2 ADDRESS SELECT. Address Select uses two access granted signals from Access Control to choose an address for a memory access. If the DMACC signal is active, the circuit enables the 16-bit address from the DMAC interface (DA00 to DA15) for use during the memory cycle. If the CPUACC signal is active, the circuit enables the 16-bit address from the CPU Address Register (CPAD00 to CPAD15). If neither access granted signal is active, the select circuit enables the 6-bit refresh address (RFAD04 to RFAD09) to the memory boards. The upper four bits are not required during a refresh cycle. Both access granted signals cannot be active at the same time.

- 1.2.6.3 ADDRESS DRIVERS. Twelve NAND gates receive the 12 least significant bits of the address from Address Select, invert the logic level of the address, and transmit the address to the memory boards. The selected memory board uses these address bits to select the required memory location.

- 1.2.6.4 MEMORY BOARD SELECT AND BANK ENCODE. This circuit receives the four most significant bits of a memory address (AD00 to AD03), compares that address with the size of the memory available from the first two memory boards, and selects the memory board that contains the address. In addition the circuit creates a 3-bit code that is sent to the selected memory board to designate the memory bank that will receive the 12-bit word address. Figure 1-9 illustrates the comparisons that produce the memory board enables and bank select codes.

Figure 1-9. Memory Board Select and Bank Encode Comparison Code

Board 1. The circuit always transmits a 3-bit bank select code, comprised of address bits 1, 2 and 3, to memory board 1 (the memory board closest to the controller). If address bit 0 is a logic "0", the circuit also produces an enable (ENABA) to memory board 1 so that the memory board will decode the bank select code. However, if the bank select code exceeds the capacity of memory board 1, it will not recognize the address.

Board 2. The circuit also compares the four MSB's of the memory address with the memory size bits from memory board 1 to determine if the address is contained on memory board 2. By adding the memory address bits to the complement memory size code from board 1 with a logic zero in the MSB position, the circuit determines if the address is in excess of the capacity of memory board 1. If this subtraction process produces a result whose MSB is a logic "1", then the address is larger than the capacity of board 1. The MSB of the result becomes the enable signal to board 2 (ENABB), while the other three resultant bits become the bank select code. If the address is sufficiently larger than the capacity of board 1 (approximately 40K), then the address could not be on board 2. The complement addition in that case may produce an overflow that leaves the MSB of the result at a logic "0", disabling the decoding circuits on board 2.

Board 3. To determine if the address is on board 3, the circuit adds the capacity of board 1 to the capacity of board 2. All addresses in excess of

this result are on board 3. If they are not, they will not be recognized by board 3. The circuit performs a complement addition of the address with the lower bound of board 3 (capacity of 1 + 2). If the addition produces a carry-out from the most significant bit, then the address is greater than the lower bound address. The carry-out signal from this addition becomes the decode enable signal for memory board 3 (ENABC). The three LSB's of the addition become the bank select code that is sent to board 3.

1.2.6.5 ADDRESS INSPECTION. Memory addresses are segmented into two protected areas and three unprotected areas as outlined in table 1-4. The Address Inspection circuit examines the most significant 13 bits of the memory address to determine which of these memory areas is being accessed.

Register File Address. If the memory address is of the form  $008X_{16}$  (within the range  $0080_{16}$  to  $008F_{16}$ ), the address specifies a location in the register file on the memory controller board. When such an address is detected, this circuit generates two signals, RAD and RAD-, that enable the register file data output, disable the error correction and detection logic, and spread out the system clock pulse to allow for gating delays during the register file read operation. This signal is also relayed to the Memory Cycle Control logic to generate other control signals.

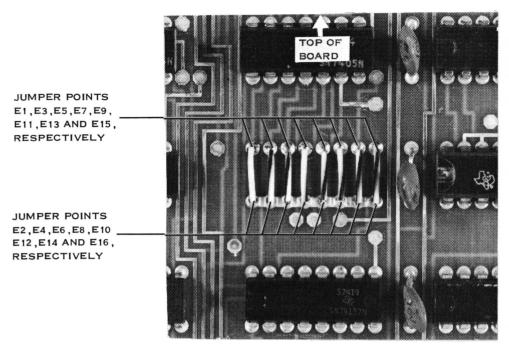

Protected Memory. Protected memory is a range of memory addresses that cannot be written into unless such an operation is specifically enabled by setting the MPO switch on the control panel to the ON position. The lower bound of this area is  $0000_{16}$ . The upper bound of the protected area is determined by a set of jumper wires on the memory controller circuit board as illustrated in figure 1-10. Table 1-5 defines the jumper wire configurations for each of the nine possible upper bound addresses. Other jumper wire configurations are physically possible, but they create non-continuous areas of protected memory and are, therefore, not useful.

are physically possible, but they create non-continuous a nemory and are, therefore, not useful.

Table 1-4. Segmented Areas of Memory

| Address Range | Description                                                            |  |  |

|---------------|------------------------------------------------------------------------|--|--|

| 0000 to 007F  | Protected; usually reserved for bootstrap programs                     |  |  |

| 0080 to 008F  | Unprotected; register file addresses                                   |  |  |

| 0090 to 00A7  | Unprotected; usually reserved for interrupt and I/O status information |  |  |

| 00A8 to 7FFF  | Protected; upper limit changeable by jumper wires                      |  |  |

| 8000 to FFFF  | Unprotected                                                            |  |  |

129441 (960-974-12-3)

Figure 1-10. Protected Memory Upper Bound Jumper Connections

<u>Circuit Operation</u>. If the MPOSW signal from the control panel is high (MPO switch in OFF position), the circuit examines the address to determine if it is within the range of protected memory as defined by the lower bound address and the upper bound address represented by the jumper connections. If the address is protected, the circuit produces an internal signal to Memory Cycle Control to disable any write operation for that address. If the operation is a write, that signal (PROTV-) changes the operation to a nondestructive read operation. When that read operation is complete, this circuit generates a protection violation indication (MPROTV) to the CPU.

1.2.6.6 WRITE DATA SELECT. Write Data Select uses DMAC access granted (DMACC-) to determine which of two 16-bit inputs to transfer to the write drivers for transmission to the memory boards. If DMACC- is low, the circuit selects the data input from the DMAC interface for storage into memory. If DMACC- is high, the circuit selects the input from the CPU interface (ALU00 to ALU15). In addition to being transferred as write data to the memory boards, the selected 16 bits are input to the Register File if it is a register file store operation, or to the ECC Generation circuit if it is a memory store operation.

Table 1-5. Memory Protect Upper Bound Options

| PROTECTED MEMORY<br>UPPER BOUND* | JUMPER CONFIGURATION |               |          |          |            |          |             |          |

|----------------------------------|----------------------|---------------|----------|----------|------------|----------|-------------|----------|

|                                  | E1-E2                | E3-E4         | E5-E6    | E7-E8    | E9-E10     | E11-E12  | E13-E14     | E15-E16  |

| 7 F F F                          | 0 0                  | 0 0           | 0 0      | 0 0      | 0 0        | 0 0      | 0 0         | 0 0      |

| 3 F F F                          | <b>~</b> ~           | 0 0           | 0 0      | 0 0      | 0 0        | 0 0      | 0 0         | 0 0      |

| 1 F F F                          | <del></del>          | <del></del> 0 | 0 0      | 0 0      | 0 0        | 0 0      | 0 0         | 0 0      |

| 0 F F F                          | <b>→</b>             | <b>~</b>      | <b>~</b> | 0 0      | 0 0        | 0 0      | 0 0         | 0 0      |

| 0 7 F F                          | <b>~</b>             | <b>~</b>      | <b>○</b> | <b>~</b> | 0 0        | 0 0      | 0 0         | 0 0      |

| 0 3 F F                          | <b>→</b>             | <b>~</b>      | <b>~</b> | <b>~</b> | <b>⊶</b> ∘ | 0 0      | 0 0         | 0 0      |

| 0 1 F F                          | <b>⊶</b>             | <b>~</b>      | <b>→</b> | <b>→</b> | <b>⊶</b>   | <b>⊶</b> | 0 0         | 0 0      |

| 0 0 F F                          | <b>~</b>             | <b>⊶</b>      | <b>⊶</b> | <b>~</b> | <b>⊶</b>   | <b>⊶</b> | <del></del> | 0 0      |

| 0 0 7 F                          | ⊶                    | <b>~</b>      | <b>⊶</b> | <b>⊶</b> | <b>⊶</b> ∘ | <b>⊶</b> | <b>⊶</b>    | <b>S</b> |

<sup>\*</sup>LOWER BOUND = 0000; ADDRESSES 0080 THROUGH 00A7 ARE NEVER PROTECTED

1.2.6.7 WRITE DATA DRIVERS. Twenty-two inverter-driver circuits receive 16 data bits from the Write Data Select circuit and six more ECC bits from the ECC Generation circuit, invert the logic levels of the bits, and transmit them to the memory boards. The selected memory board then stores the data into the addressed area in memory.

#### 1.2.7 MEMORY FETCH

If Memory Cycle Control determines that the operation is a fetch, then the controller receives address bits from and transmits memory data to the interface selected by Access Control. The controller examines the address to determine the source of the requested data, and generates the addressing signals required to route the data from memory or the register file, through the error correction circuits, and to the requesting interface. The following paragraphs describe the major functional circuits involved in the fetch operation excluding the error correction logic and the addressing circuits. Both of these areas are covered elsewhere in this section.

- 1.2.7.1 READ DATA BUFFERS. Twenty-two inverter-buffer circuits receive data from memory during a memory read cycle (16 data bits and 6 ECC bits), invert the logic levels of the data, and apply the inverted data to the Read Data Select and Read Data Error Detection circuits. The inversion provided by this circuit restores memory data to its proper sense, since the memory chips invert the data when reading from the memory location. Therefore, the output of the data buffers represents the data that was originally stored in memory.

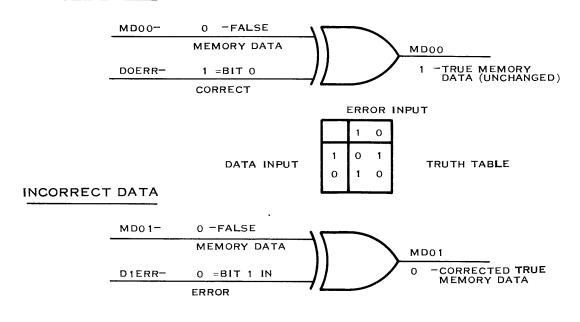

- 1.2.7.2 REGISTER FILE. The memory controller provides the CPU with 16 words of rapid access memory through the Register File. The Register File is a group of four 16 x 4 TTL Read-Write memory chips. Each chip receives four bits of input data during a write operation and supplies four bits of output data during a read operation. The four least significant bits of memory address select the location within the Register File to be accessed. An additional control signal, RFWE- (Register File Write Enable), indicates to the Register File whether the operation is a read or a write. When RFWE- is low, the input data from Write Data Select is stored in the location specified by address bits 12 through 15. At all other times, the Register File uses the four least significant bits of the current address to produce an output to the Read Data Select circuit with each memory cycle. If the operation is a register file read, the data is enabled by the Read Data Select circuit.