# Model 960 Computer Communications Register Unit Manual

Part No. 966313-9701 1 May 1977

# TEXAS INSTRUMENTS

#### © Texas Instruments Incorporated 1977 All Rights Reserved

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

## LIST OF EFFECTIVE PAGES

INSERT LATEST CHANGED PAGES DESTROY SUPERSEDED PAGES

Note: The portion of the text affected by the changes is indicated by a vertical bar in the outer margins of the page.

Model 960 Computer, Communications Register Unit Manual (966313-9701)

1 December 1972 Original Issue..... 1 June 1974 (ECN 393671) Revised and Reissued . . . . . . 1 November 1974 (ECN 393125) Revised and Reissued . . . . . . 1 April 1976 (ECN 408282) Change l ...... 1 May 1977 (ECN 419764)

Total number of pages in this publication is 82 consisting of the following:

| PAGE<br>NO.   | CHANGE<br>NO.                            | PAGE<br>NO. | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. |

|---------------|------------------------------------------|-------------|---------------|-------------|---------------|

|               | NO 2 2 1 0 2 0 2 0 1 0 1 0 1 0 1 0 1 0 2 |             |               | NO.         | NO.           |

| Cover Blank . | 0                                        |             |               |             |               |

#### TABLE OF CONTENTS

| Paragraph | Title                                          | Page    |

|-----------|------------------------------------------------|---------|

|           | SECTION I. INTRODUCTION                        |         |

|           | SECTION II. OPERATION                          |         |

| 2.1       | General                                        | 2-1     |

| 2.1.1     | CRU Instructions                               | 2-1     |

| 2.1.2     | Interrupts                                     | 2-7     |

| 2.1.3     | CRU Signal Distribution                        | 2-8     |

| 2.2       | CRU Modules                                    | 2-8     |

| 2.2.1     | Data Module, 16 Input/16 Output (TI Part       | _ 0     |

| 2 2 2     | Number 214103)                                 | 2-9     |

| 2.2.2     | Data Module, 32 Input (TI Part Number 217382)  | 2-13    |

| 2.2.3     | Data Module, 32 Output (TI Part Number 217380) | 2-14    |

| 2.2.4     | Data Module Contactor (TI Part Number 214111)  | 2-15    |

| 2.2.5     | EIA Data Module (TI Part Number 966630)        | 2-17    |

| 2.2.6     | Interval Time Module (TI Part Number 214114)   | 2-18    |

| 2.2.7     | Interrupt Module (TI Part Number 214087)       | 2-21    |

| 2.2.8     | A/D Converter-Multiplexer (TI Part Number      |         |

| 2.2.9     | 217690)                                        | 2-22    |

| 2.2.7     | D/A Converter with Registers (TI Part          |         |

| 2.2.10    | Number 217686)                                 | 2-25    |

| 2.2.10    | Data Communications Module (TI Part            | * *<br> |

| 2.2.11    | Number 961642)                                 | 2-27    |

| 2.2.11    | Card Reader Column Buffer Module (TI Part      |         |

| 2.2.12    | Number 943795)                                 | 2-30    |

| 2.2.12    | OCI Data Module (TI Part Number 966495)        | 2-32    |

| 2.2.14    | OCI Interrupt Module (TI Part Number 966787)   | 2-34    |

| 2.2.14    | Regulator Module, ±15 Volt (TI Part Number     |         |

| 2.3       | 226855)                                        | 2-36    |

| 2.3.1     | CRU System Configurations                      | 2-38    |

| 2.3.2     | Basic System                                   | 2-38    |

| 2.3.3     | Mainframe CRU Expansion                        | 2-38    |

| 4.5.5     | External CRU Expansion                         | 2-38    |

|           | SECTION III. ADDRESSING                        |         |

| 3.1       | General                                        |         |

| 3.2       | Addressing of 16 Line Medula                   | 3-1     |

| 3.2.1     | Addressing of 16-Line Modules                  | 3 - 1   |

| J. Z. 1   | Mainframe CRU System                           | 3-1     |

#### TABLE OF CONTENTS (Continued)

| Paragraph                                                                                                                     | Title                                                                                                                                                                                                                                                      | Page                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 3.2.2<br>3.2.3<br>3.3<br>3.3.1                                                                                                | Expansion to 1, 2, or 4 CRU Expansion Units Expansion to 5 to 16 CRU Expansion Units Addressing of 32-Line Modules                                                                                                                                         | 3-3<br>3-3<br>3-5<br>3-5                                                         |

| 3.3.2<br>3.3.3                                                                                                                | Expansion to 1 or 2 CRU Expansion Units Expansion to 3 to 8 CRU Expansion Units                                                                                                                                                                            | 3-5<br>3-5                                                                       |

|                                                                                                                               | SECTION IV. THEORY OF OPERATION                                                                                                                                                                                                                            |                                                                                  |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7 | General  Mainframe CRU System  CRU Interface  CRU Modules  Signal Levels  Signal Flow  Signal Timing  Externally Expanded CRU System  CRU Interface  CRU Expander  Buffer  CRU Module  Signal Levels  Signal Flow  Signal Flow  Signal Flow  Signal Timing | 4-1<br>4-1<br>4-2<br>4-2<br>4-2<br>4-3<br>4-3<br>4-5<br>4-6<br>4-7<br>4-7<br>4-7 |

|                                                                                                                               | SECTION V. ELECTRICAL DRAWINGS                                                                                                                                                                                                                             |                                                                                  |

|                                                                                                                               | LIST OF ILLUSTRATIONS                                                                                                                                                                                                                                      |                                                                                  |

| Figure                                                                                                                        | Title                                                                                                                                                                                                                                                      | Page                                                                             |

| 2-1<br>2-2<br>2-3                                                                                                             | CRU Channel System Functional Diagram                                                                                                                                                                                                                      | 2-2<br>2-3<br>2-5                                                                |

| 2-4<br>2-5<br>2-6                                                                                                             | Store CRU Instruction                                                                                                                                                                                                                                      | 2-6<br>2-7                                                                       |

| 2-7<br>2-8<br>2-9                                                                                                             | Assignment                                                                                                                                                                                                                                                 | 2-9<br>2-10<br>2-19<br>2-39                                                      |

### LIST OF ILLUSTRATIONS (Continued)

| Figure     | Title                                                  | Page         |

|------------|--------------------------------------------------------|--------------|

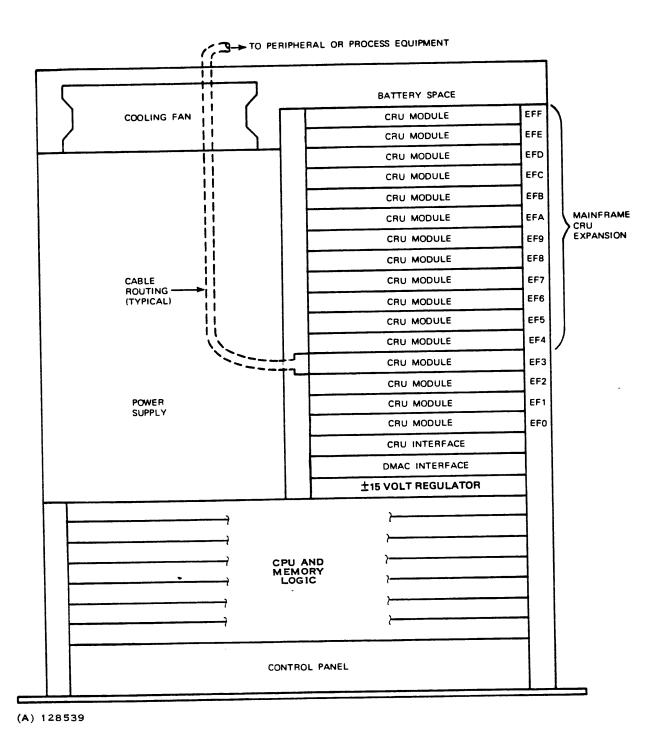

| 2-10       | Mainframe CRU Expansion - Mechanical Configuration     | 2 40         |

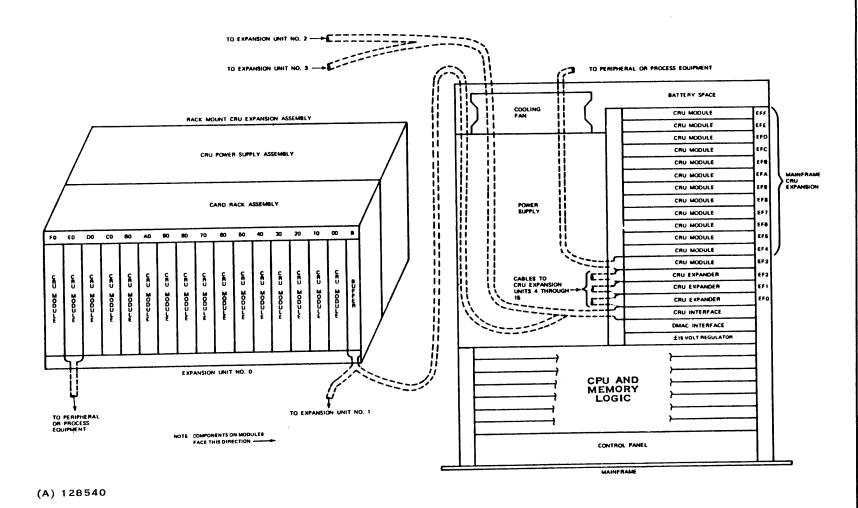

| 2-11       | CRU Expansion Unit - Mechanical Configuration          | 2-40<br>2-42 |

| 3-1        | Address Decoding and Module Selection, 16-Line Modules | 2 2          |

| 3-2        | Address Decoding and Module Selection, 32-Line         | 3-2          |

| 4 1        | Modules                                                | 3-6          |

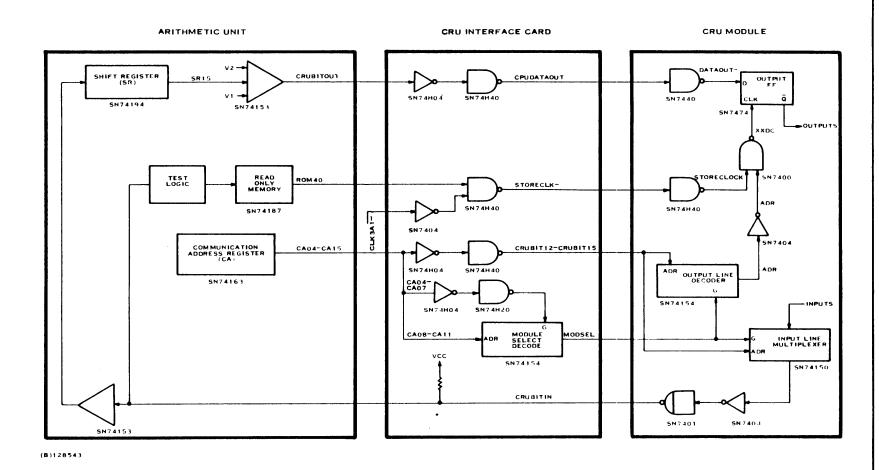

| 4-1<br>4-2 | Mainframe CRU System - Signal Flow Diagram             | 4-4          |

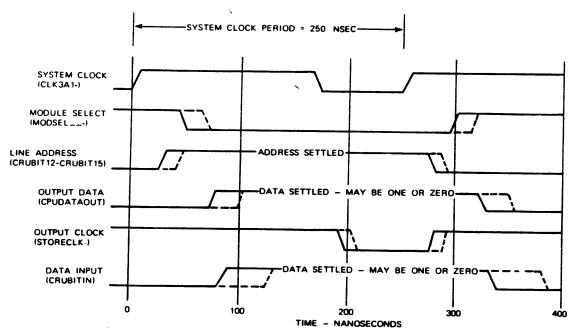

| 4-2        | Mainframe CRU System - Timing Diagram                  | 4-5          |

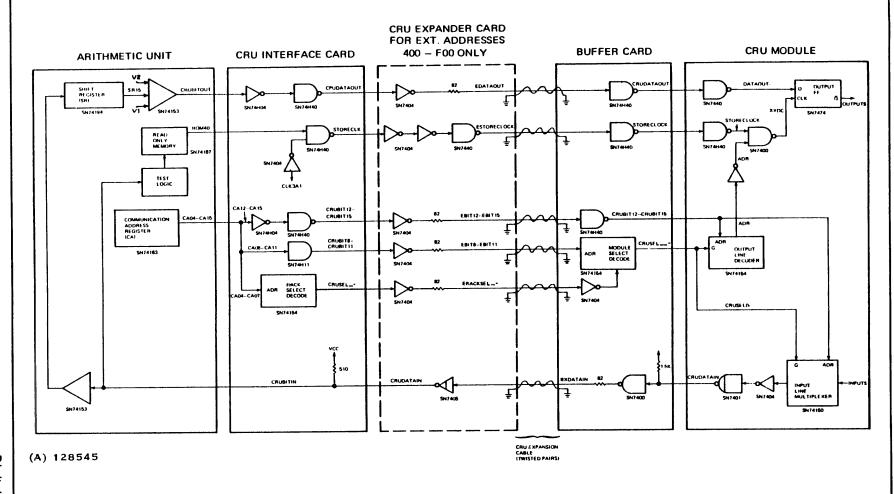

| 4-4        | External CRU Expansion - Signal Flow Diagram           | 4-8          |

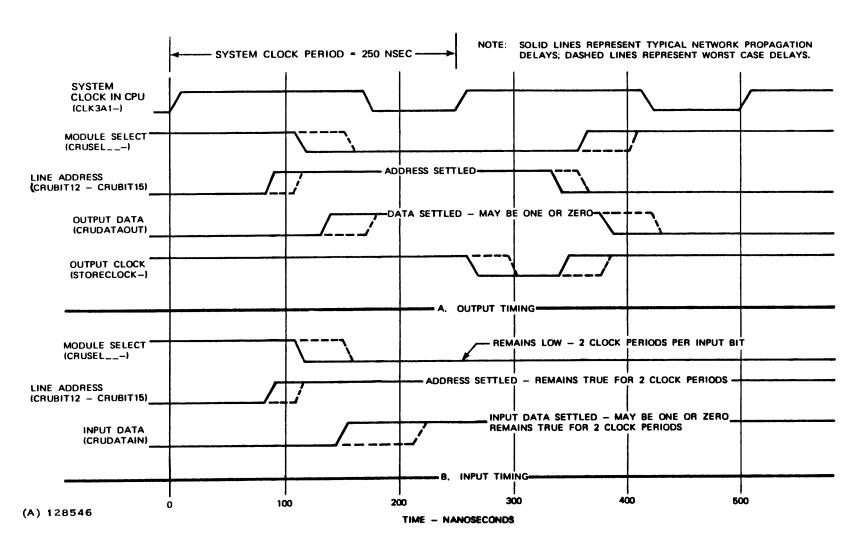

| 1-1        | External CRU Expansion - Signal Timing                 | 4-9          |

|            | LIST OF TABLES                                         |              |

| Table      | Title                                                  | Page         |

| 1-1        | CRU Module and System Peripheral User's  Manual        | 1-1          |

| 2-1        | Data Module (16 Input/16 Output) Specifications        | 2-10         |

| 2-2        | CRU Bit Functions for the Data Module                  | 2-11         |

| 2-3        | Data Module (32 Input) Specifications                  | 2-13         |

| 2-4        | CRU Bit Functions for the 32 Input Module              | 2-14         |

| 2-5        | Data Module (32 Output) Specifications                 | 2-15         |

| 2-6        | CRU Bit Functions for the 32 Output Module             | 2-16         |

| 2-7        | Data Module Contactor Specifications                   | 2-16         |

| 2-8        | CRU Bit Functions for the Contactor Module             | 2-17         |

| 2-9        | EIA Data Module Specifications                         | 2-18         |

| 2-10       | Interval Timer Module Specifications                   | 2-20         |

| 2-11       | CRU Bit Functions for the Interval Timer               | 2-20         |

| 2-12       | Interrupt Module Specifications                        | 2-21         |

| 2-13       | CRU Bit Functions for the Interrupt Module             | 2-22         |

| 2-14       | A/D Converter-Multiplexer Specifications               | 2-23         |

| 2-15       | Pin Assignments for A/D Converter Multiplexer  Module  | 2-24         |

| 2-16       | CRU Bit Functions for the A/D Converter/Multiplex-     |              |

| 2-17       | er Module                                              | 2-24         |

| 2-17       | D/A Converter Specifications                           | 2-25         |

| 2-19       | Pin Assignments for D/A Module Outputs                 | 2-26         |

| 2-19       | CRU Bit Functions for the D/A Module                   | 2-27         |

| 2-20       | Data Communications Module Specifications              | 2-28         |

#### LIST OF TABLES (Continued)

| Table        | Title                                                 | Page  |

|--------------|-------------------------------------------------------|-------|

| 2-21         | Pin Assignments for Data Communications               | 2-29  |

|              | Module Interface Signals                              | 2-29  |

| 2-22         | CRU Bit Functions for the Data Communications  Module | 2-29  |

| 2-23         | Card Reader Column Buffer Module Specifications       | 2-30  |

| 2-24         | CRU Bit Functions for the Card Reader Column          |       |

|              | Buffer Module                                         | 2-31  |

| 2-25         | OCI Data Module Input Specifications                  | 2-33  |

| 2-26         | OCI Data Module Interface Pin Assignments             | 2-34  |

| 2-27         | OCI Interrupt Module Specifications                   | 2-35  |

| 2-28         | Pin Assignments for the OCI Interrupt Module          | 2-36  |

| 2-29         | CRU Bit Functions for the OCI Interrupt Module        | 2-37  |

| 2-30         | Regulator Module Specifications                       | 2-37  |

| 2-31         | ±15V Regulator Pin Assignments                        | 2-37  |

| 2-32         | CRU Expansion Cables                                  | 2-43  |

| 2-33         | CRU Expansion Unit Options                            | 2-43  |

| 3-1          | Address Segment Functions                             | 3 - 1 |

| 3-2          | Expansion Module Address Assignments for              |       |

|              | 16-Line Modules                                       | 3-3   |

| 3-3          | Expansion Unit (0-3) Address Assignments              | 3-4   |

| 3-4          | Expander Card Unit Locations and Address Assign-      |       |

|              | ments for 16-Line Modules                             | 3-4   |

| 3 <b>-</b> 5 | Expansion Module Address Assignments for              | 2 7   |

|              | 32-Line Modules                                       | 3-7   |

| 3-6          | Expansion Unit (0-1) Address Assignments              | 3 - 7 |

| 3-7          | Expansion Card/Unit Address Assignments for           | 3-7   |

|              | 32-Line Modules                                       | 5-1   |

| 4-1          | CRU Module Pin Assignments                            | 4-3   |

| 4-2          | Jumper Schedule for CRU Expansion                     | 4-6   |

#### SECTION I

#### INTRODUCTION

This manual describes the Communication Register Unit (CRU) which is the serial Input/Output (I/O) channel of the Texas Instruments Model 960A and Model 960B Computers. This manual is separated into two parts: the first part describes CRU programming and interface modules; the second part explains CRU hardware implementation.

It is assumed throughout the manual that the reader is familiar with the concepts explained in the Model 960A System Description Manual (TI Part No. 226750-9701) or the Model 960B System Description Manual (TI Part No. 942773-9701), and the Model 960 Basic Programming Guide (TI Part No. 955378-9701).

Detailed maintenance information, including parts lists and assembly drawings for all CRU components, may be obtained by purchasing the Model 960 Maintenance Manual, Volume IV (TI Part No. 226750-9704).

Complete programming and electrical information for each CRU module and system peripheral that is attached to the modules is included in the appropriate User's Manual. Available User's Manuals are identified and listed in table 1-1 with the corresponding TI Part Numbers.

Table 1-1. CRU Module and System Peripheral User's Manuals

| Module or Peripheral Hardware     | TI Manual Number |

|-----------------------------------|------------------|

| 16 In/16 Out Data Module          | 966366-9701      |

| 32 In Data Module                 | 966367-9701      |

| 32 Out Data Module                | 966368-9701      |

| Contactor Data Module             | 966369-9701      |

| Interrupt Module                  | 966373-9701      |

| A/D Converter Module              | 966371-9701      |

| D/A Converter Module              | 966372-9701      |

| Interval Timer Module             | 966374-9701      |

| Full Duplex Communications Module | 966375-9701      |

| Teletypewriter                    | 966314-9701      |

| Card Reader                       | 966316-9701      |

| Video Terminal                    | 966318-9701      |

| Paper Tape Reader                 | 965940-9701      |

| Paper Tape Punch                  | 965934-9701      |

| Analog Systems                    | 964580-9701      |

| Silent 700 Terminals              | 959227-9701      |

## SECTION II OPERATION

#### 2.1 GENERAL

The Communication Register Unit (CRU) is a line-oriented input-output (I/O) channel. The output function of this channel is to set a selected CRU output line to a logic ONE or ZERO, or to output a field of bits from a memory location to a set of consecutive CRU output lines. The CRU input function is to read the logic level on a selected CRU input line into the computer, or to read information on a set of consecutive CRU input lines into a memory location.

In the fully expanded configuration, the CRU channel provides 4,096 output lines and 4,096 input lines. The CRU lines are selected by a 12-bit address that is generated by the computer. Each address selects one input line and one output line. The input or output to a given line address is controlled by the executed instruction.

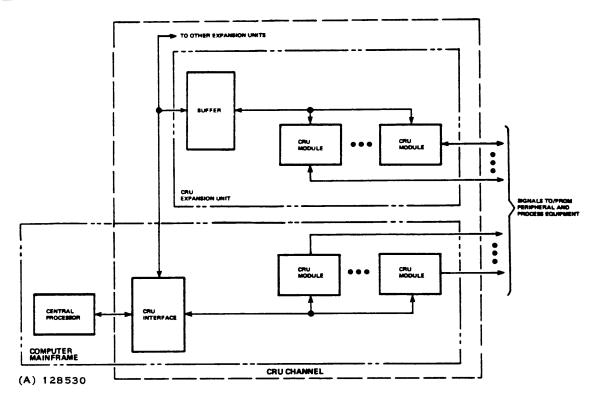

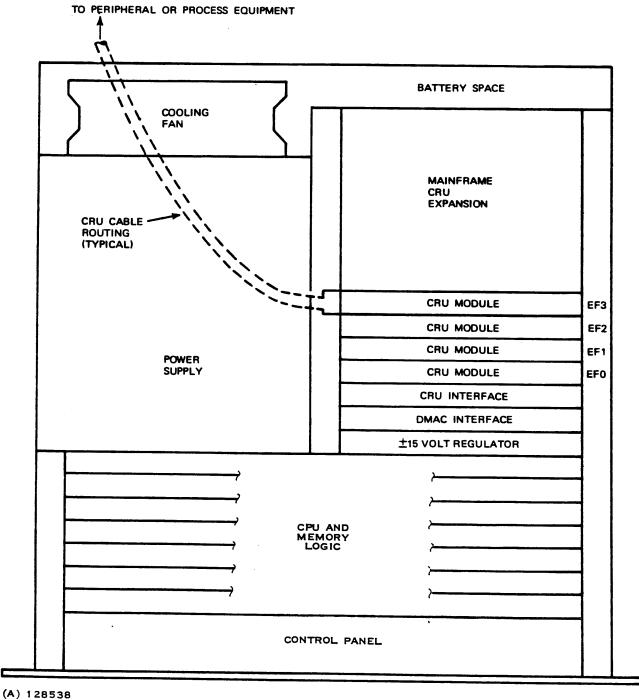

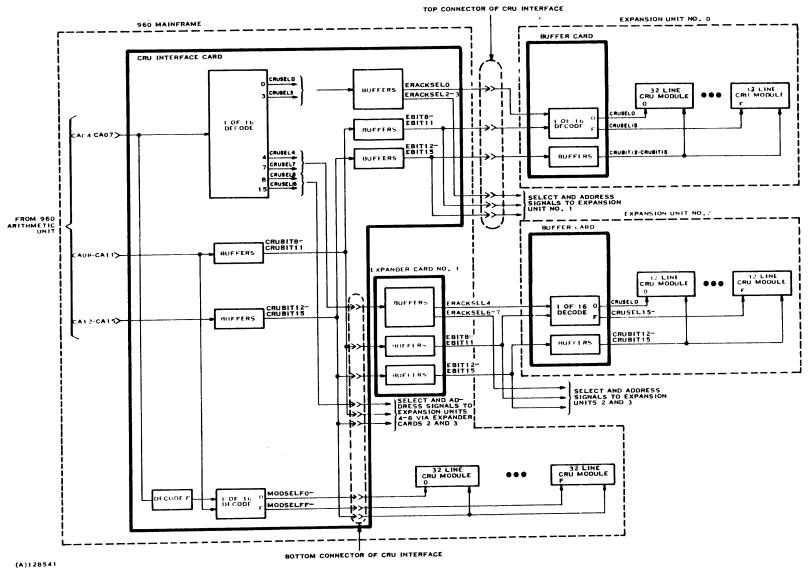

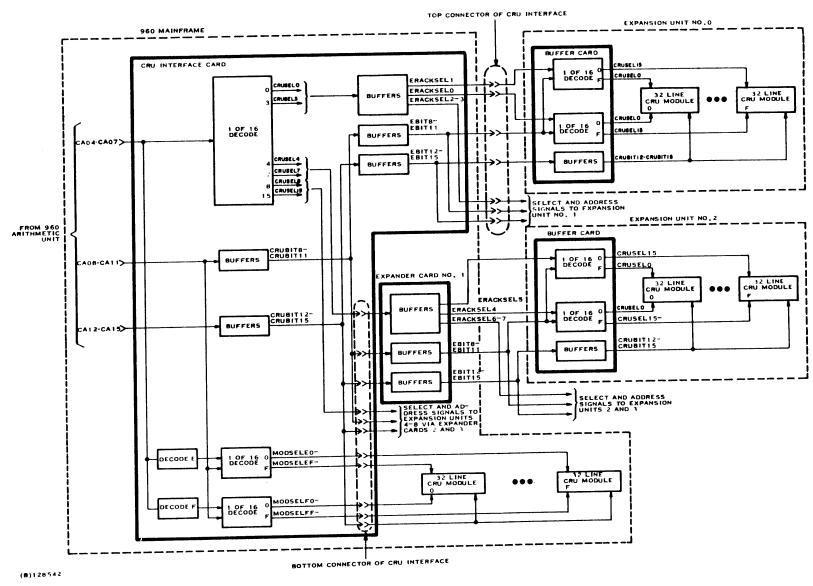

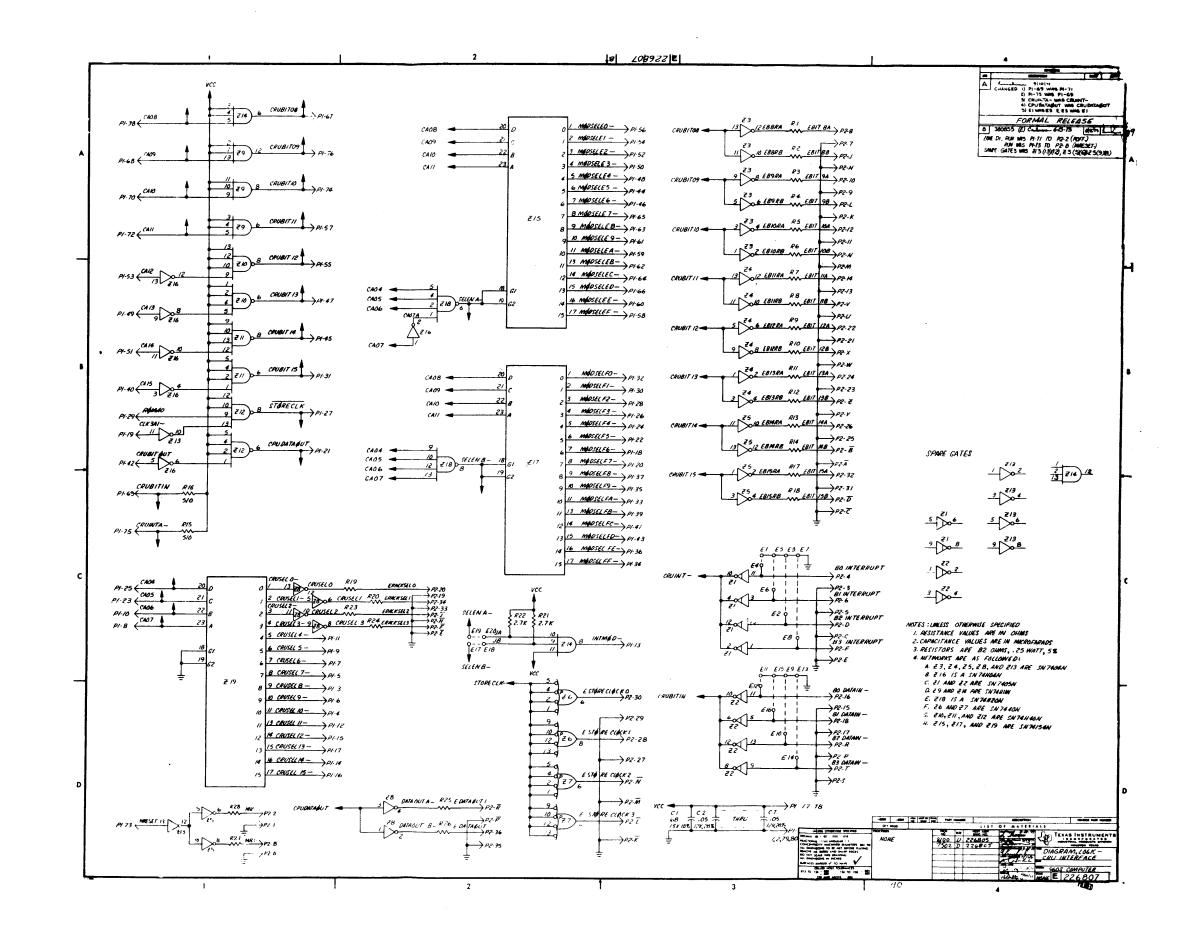

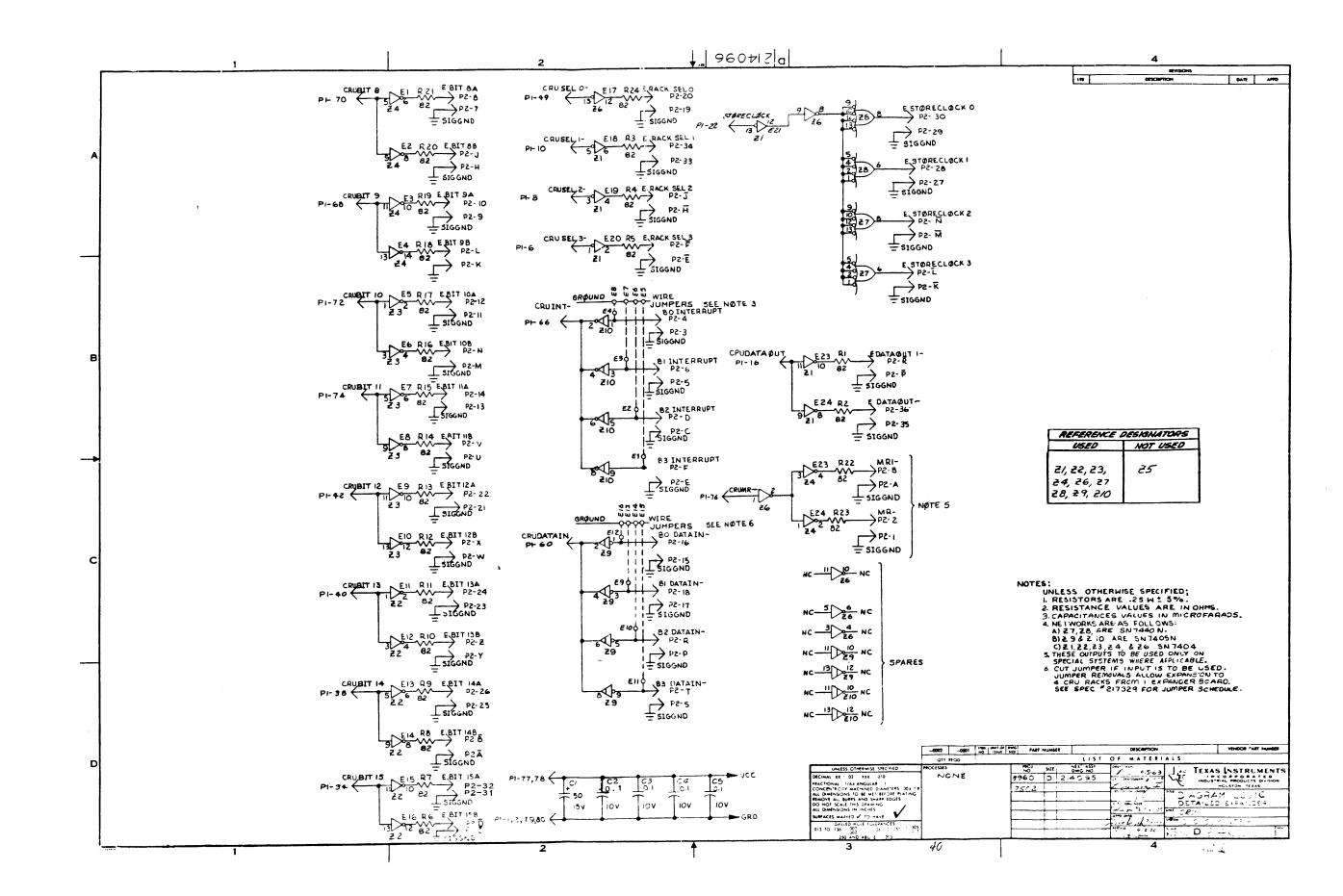

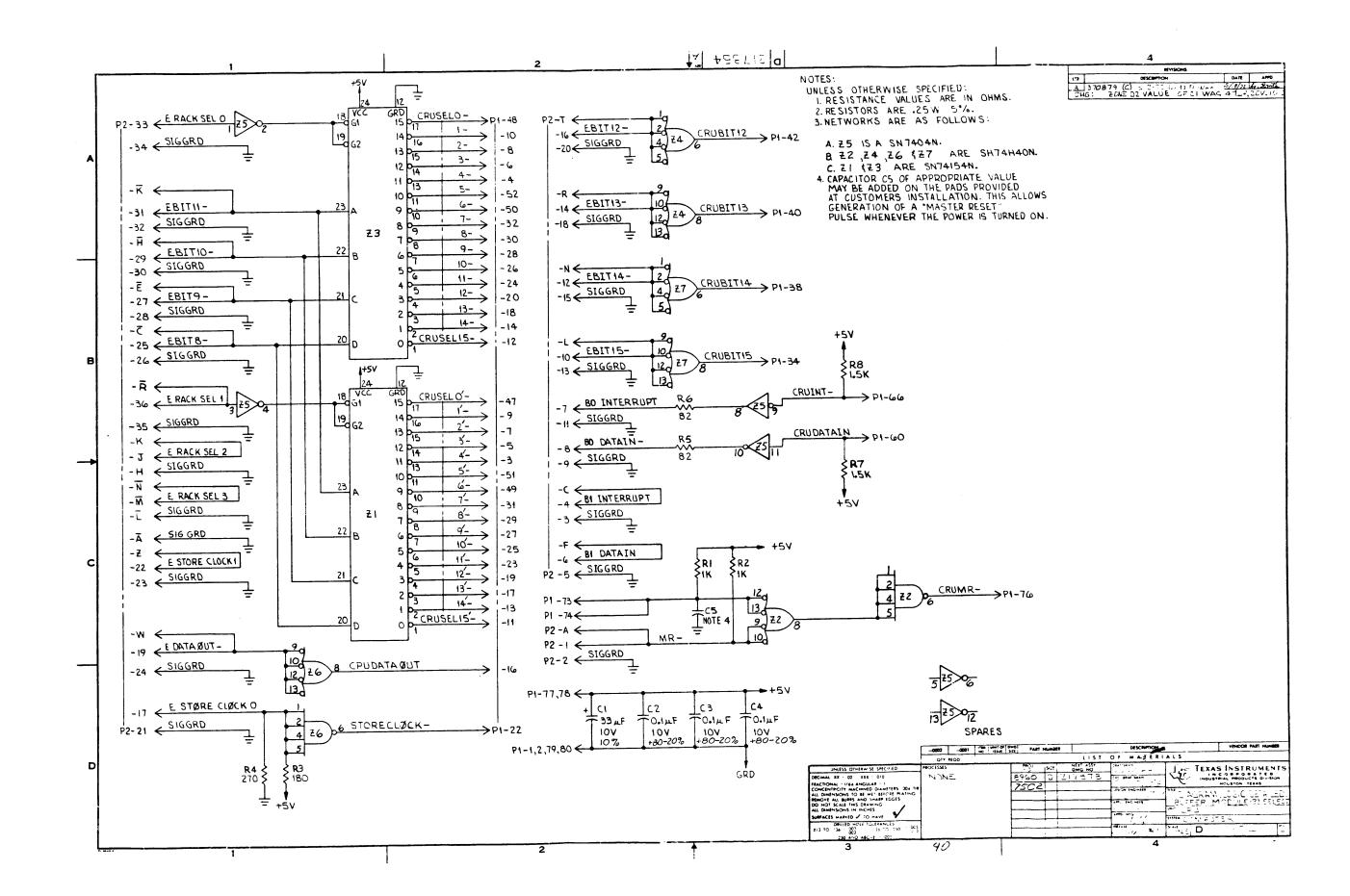

The CRU channel consists of one CRU interface printed circuit (PC) board and from one to sixteen CRU module printed circuit boards that are installed in the computer mainframe as illustrated in figure 2-1. In addition, an expanded CRU system includes one or more CRU expansion units external to the computer mainframe. Up to 16 CRU modules are installed in each expansion unit.

All CRU input and output lines are physically implemented on the CRU modules.

#### 2.1.1 CRU INSTRUCTIONS

The CRU channel is activated by six computer instructions. Each CRU instruction is described below with the aid of a simplified block diagram to illustrate CRU channel operation. Operation of circuits within the CRU channel is described in greater detail in Section III.

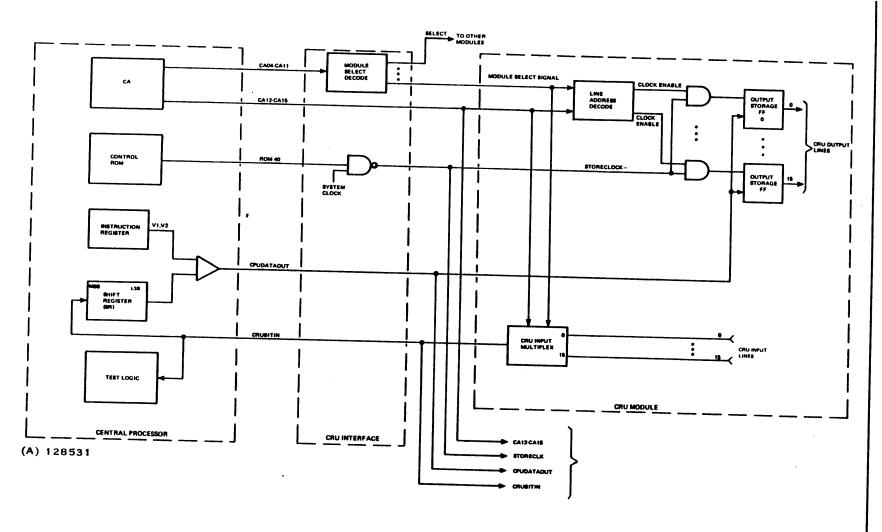

Figure 2-2 shows the major Central Processor Unit and CRU channel hardware items involved in the execution of a CRU instruction.

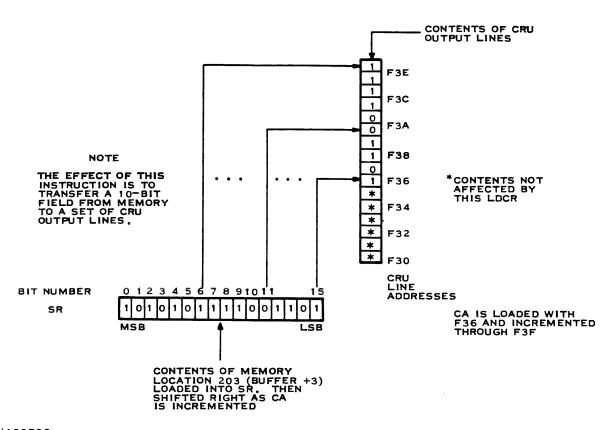

2.1.1.1 LOAD CRU (LDCR). The LDCR instruction causes a field of data, 1 to 16 bits in length, located in a memory location to be output to consecutive CRU lines. The 32-bit instruction word contains fields from which the data source address and the beginning CRU output address are calculated. Another instruction word field specifies the number of bits to be output.

In the LDCR instruction, the output data field is transferred serially to the CRU channel. The Central Processor Unit (CPU) calculates the 12-bit address of the first CRU line using the contents of CPU Register 7 (either mode)

Figure 2-1. CRU Channel System Functional Diagram

and a 10-bit field from the instruction word. This address is stored in the 12 Least Significant Bits (LSB) of the CRU Address Register (CA); i.e., CA bits 4 through 15. The data is fetched from the memory address specified by the contents of CPU Register 4 and another 10-bit field from the instruction. It is stored in the Shift Register (SR). Neither CA nor SR is a program addressable register.

The module select decoder on the CRU interface board is enabled by a code in the most significant four bits (CA04-CA07) of the CRU address. Address bits CA08 through CA11 are decoded to generate one of 16 module select signals. The module select signal enables the line address decoder on the CRU module. The line address decoder generates one of 16 enable signals for the storage flip-flop clocks. The clock input to these gates is generated by gating the system clock with ROM40. ROM40 is an output from the CPU control read-only memory which is true during a CRU output operation.

The CRU module contains 16 output storage flip-flops to which the least significant bit (LSB) of the SR is applied as a data input. The flip-flops are clocked by the gated clocks that are described above.

At the end of a clock signal period, SR bit 15 is clocked into the selected flip-flop, the SR is shifted right one position, and the CA is incremented. At the end of the next clock period, the line address decoder enables a clock

Figure 2-2. CRU Channel Functional Diagram

to the next output flip-flop in sequence and it is loaded with the content of SR bit 15. This process continues until the entire data field is loaded in consecutive storage flip-flops. The outputs of the storage flip-flops are the CRU output lines. The number of bits in the data field is determined by a 4-bit field in the instruction.

Figure 2-3 illustrates the transfer of a 10-bit field from memory to field of CRU output lines.

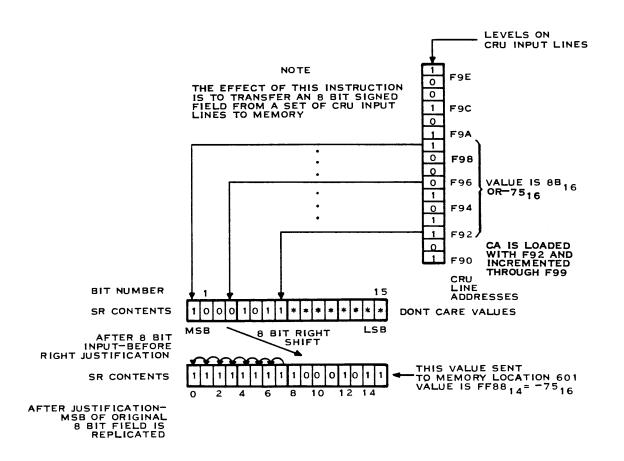

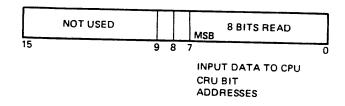

2.1.1.2 STORE CRU (STCR). The STCR instruction causes the information present on a group of 1 to 16 consecutive CRU input lines to be transferred to the CPU and stored, justified right in a memory location. The instruction word contains fields specifying the starting CRU line address, the storage location, and the number of bits to be transferred.

The CRU interface module select decoder functions as described for the LDCR instruction. The CRU input multiplexer in the CRU module is enabled by the module select signal and addressed by CA12 through CA15. Thus, the first CRU input line is selected through the multiplexer and routed to the most significant bit input of the SR. At the end of each clock period the CA is incremented causing the next input in sequence to be enabled through the multiplexer, and the SR is shifted right one position. This process continues until the specified number of bits has been loaded into the leftmost bits of the SR. If the transferred number of bits is less than 16, the CRU input to the SR is inhibited and the SR shifts right, always forcing the serial input to be the MSB, until the input data is justified right with the sign bit of the original field extended. The contents of the SR is then stored in the specified register or memory location under program control. During an STCR instruction, both the line address decoder and the input multiplexer in the CRU module are enabled. However, the output storage flip-flops are not clocked because the output clock enable signal (ROM40) is false during a store operation.

Figure 2-4 illustrates the transfer of an 8-bit field from a set of CRU input lines to a memory location.

- 2.1.1.3 SET BIT (SETB). The SETB instruction word contains a field which specifies a CRU output line and a bit (V1) which contains a value to be transferred to the addressed output. When this instruction is executed, the CRU channel operates as described for the LDCR instruction except that V1, rather than SR bit 15, is selected to the CPU DATAOUT line and only the one bit is transferred.

- 2.1.1.4 TEST INPUT BIT AND SET OUTPUT BIT OR SWITCH MODES (TSBX). The TSBX instruction word contains fields specifying a CRU input line and a CRU output line, a comparison bit (V1), and an output bit (V2). Execution of this instruction causes the value on the selected input line to be

(A)128532

Figure 2-3. Load CRU Instruction

(A)128533

Figure 2-4. Store CRU Instruction

compared to V1. If the test fails, a program mode change is forced. If the test succeeds, the value stored in V2 is transferred to the specified CRU output line.

- 2.1.1.5 SWITCH MODES IF BIT NOT EQUAL (XBNE). The XBNE instruction word contains a CRU input line address field and a comparison bit (V1). The specified CRU input line is read into the CPU and compared to V1. If the comparison fails, a program mode change is forced.

- 2.1.1.6 BRANCH IF BIT NOT EQUAL (BBNE). The BBNE instruction word contains fields which specify a CRU input line address, a program branch address, and a comparison bit (V1). The data on the specified CRU input line is read into the CPU and compared to V1. If the comparison fails, the branch is executed. The branch address is the contents of register 5 added to a 10-bit field from the instruction.

#### 2.1.2 INTERRUPTS

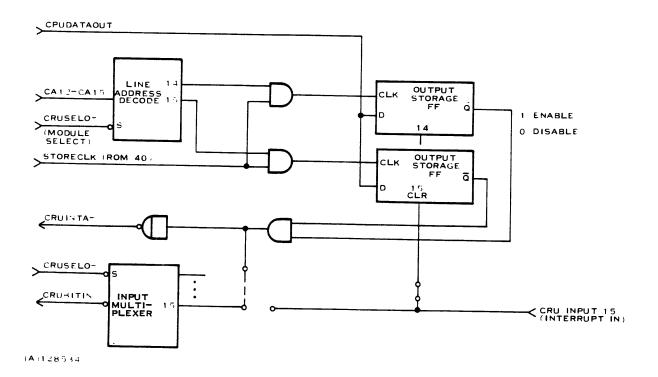

Some CRU modules have interrupt capability. Figure 2-5 shows in simplified form how two of the output storage flip-flops in a CRU module can be connected for interrupt and mask storage.

Figure 2-5. CRU Module Interrupt and Mask

The CRU input line 15 is disconnected from the input multiplexer and connected to the clear input of output storage flip-flop 15. The outputs of flip-flops 14 and 15 are gated together. Thus, flip-flop 14 serves as a mask for the interrupt flip-flop.

For a CRU interrupt to be enabled, the mask must be set by a CRU output instruction. Then, when an interrupt condition occurs on CRU input line 15, the interrupt flip-flop is set. Thus, interrupt signal (CRUINTA) to the CPU goes low. The CRUINTA- signal is bussed to all CRU modules in the system. The true interrupt signal that is generated by the mask gate is connected to input 15 of the input multiplexer. To determine the source of a CRU interrupt, instructions must be executed to test CRU input lines serving as interrupts.

The interrupt flip-flop may also be set under program control by executing a CRU output instruction. Once the interrupt flip-flop has been set to the interrupt state, the interrupt can be cleared only be executing a CRU output instruction.

A CRU interrupt module is available with 16 storage flip-flops. This configuration is implemented as 8 interrupt storage flip-flops and 8 masks.

#### 2.1.3 CRU SIGNAL DISTRIBUTION

As described in paragraph 2.1.1, a discrete module select signal is generated for each CRU module in a system. All other CRU module inputs and outputs are bussed in parallel to all modules in the system. The module interrupt and data output signals are generated by open collector gates. The data output gate is enabled only on a selected module, while the data output gate of all other modules remains high.

The interrupt output gates are not gated with the module select signal; therefore, an interrupt or one or more modules will pull the CRUINTA- line low.

#### 2.2 CRU MODULES

This section introduces the currently available CRU modules and describes the functional characteristics of each module with brief programming examples. Further detail is included in the Texas Instruments' User's Manuals which are listed in Section I of this manual.

All CRU modules have an 80-pin bottom edge connector tab which plugs into the mainframe or into a CRU expansion unit. This connection completes the interface to the address, data, clock, and interrupt signals which are processed to and from the CPU. A 72-pin top edge connector tab on the module is connected to a cable to complete the interface to peripheral or process equipment. An unwired connector that plugs to the top edge of the module is available as TI Part No. 217081-0001. See figure 2-6 for pin nomenclature.

#### MODULE SOLDER SIDE

| 3 | 6 | 35 | 34 | 33 | 32 | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1                       |

|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|-------------------------|

| F | ١ | P  | N  | M  | ī  | ĸ  | J  | Ħ  | Ē  | Ē  | ō  | ċ  | B  | Ā  | Z  | Y  | х  | w  | ٧  | U  | Т  | S  | R  | Ρ  | Ν  | М  | L  | κ | J | Н | F | Ε | D | С | В | $\overline{\mathbf{A}}$ |

MODULE COMPONENT SIDE

CONNECTOR: PART NUMBER 231447-0800 (VIKING PART NUMBER 2VH-36/1CN-5)

HOOD: TI PART NUMBER 214080-0001

(A) 128536

Figure 2-6. Connector Kit (TI Part No. 217081-0001) Pin Assignment

The basic type of CRU module (data module) provides output storage flip-flops and/or buffered input circuits to the input multiplexer. Other module types contain additional circuitry which perform signal conversion. Each module is described in separate paragraphs which follow.

## 2.2.1 DATA MODULE, 16 INPUT/16 OUTPUT (TI PART NUMBER 214103)

This module provides two-way communication between the Communications Register Unit (CRU) and devices or transducers which are operated by, or generate discrete (on-off) control signals. The module (circuit board) may be plugged into any CRU port in the CPU chassis or any port in a CRU Expansion Unit.

A data module provides 16 inputs and 16 outputs. Each line (input or output) can be addressed as a single independent line, or as a member of a group of lines. Each output circuit contains a storage flip-flop that maintains the output until changed by the CPU. An alternate version of the data module is available which provides 15 normal input channels, 14 output channels, one interrupt mask, and one interrupt input channel.

- 2.2.1.1 SPECIFICATIONS. Specifications for this data module are listed in table 2-1.

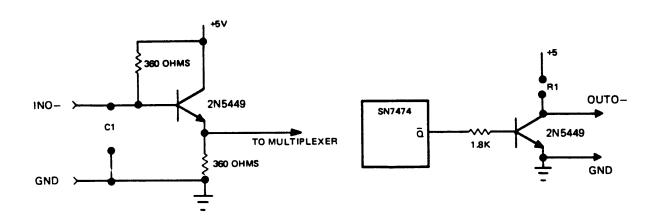

- 2.2.1.2 INTERFACE. The inputs and outputs are negative logic levels switching between 0 volts and a positive voltage. (See figure 2-7.) For each flip-flop buffered output, an open-collector output transistor is provided. The collector can be attached to an external pull-up resistor and power supply (up to 30 volts and 50 milliamperes) or resistors can be placed on the module itself for +5-volt output level. The inputs are to the base of emitter-follower transistors which operate at TTL levels. Filter capacitor pads for each input are provided on the module.

Table 2-1. Data Module (16 Input/16 Output) Specifications

| Characturistic      | Specification                                                                   |

|---------------------|---------------------------------------------------------------------------------|

| Inputs(16):         | 0V to 1.0V = Logic ONE<br>3.0V to 5.0V = Logic ZERO                             |

| Outputs(16):        | 0V to 0.4V = Logic ONE<br>Open = Logic ZERO                                     |

| Option:             | 15 inputs, 1 interrupt input<br>14 outputs, 1 interrupt mask, 1 interrupt clear |

| Power Requirements: | +5.0 Vdc @ 0.5A                                                                 |

INPUT

C1 DESIGNATES PADS FOR SMALL FILTER

CAPACITOR, IF REQUIRED.

OUTPUT

R1 DESIGNATES PADS FOR

COLLECTOR RESISTOR.

(A) 128535

Figure 2-7. Data Module Input and Output Buffers

An option allows the 16th input to be an interrupt. Jumper options allow this interrupt to be turned on by a ONE level, a ZERO level, or by a positive or negative level transition. This same option provides an output line as an interrupt mask, controlled by the computer.

Connections to the input or output lines are completed through an edge connector with pin assignments as listed in table 2-2.

| CRU<br>Output<br>Bit<br>Address*          | Function                                                                                          | Pin<br>Assignment<br>OUT-/GND                                                                                            | CRU<br>Input<br>Bit<br>Address*                                                    | Function                                                       | Pin<br>Assignment<br>IN-/GND                                                                                              |

|-------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | General-purpose output lines  General output or interrupt mask FF  General output or interrupt FF | T/K<br>F/E<br>B/A<br>X/W<br>T/S<br>N/M<br>J/H<br>D/C<br>32/31<br>28/27<br>24/23<br>20/19<br>16/15<br>12/11<br>8/7<br>4/3 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 | General-purpose input lines . General input or interrupt input | M/N<br>H/J<br>C/D<br>Y/Z<br>U/V<br>P/R<br>K/L<br>E/F<br>33/34<br>29/30<br>25/26<br>21/22<br>17/18<br>13/14<br>9/10<br>5/6 |

|                                           | *Add the CRU                                                                                      | port address f                                                                                                           | or actual j                                                                        | program address.                                               |                                                                                                                           |

Table 2-2. CRU Bit Functions for the Data Module

2.2.1.3 PROGRAMMING. The data module is the standard interface for paper tape readers and punches, line printers, and analog systems. Additionally the data module is part of many special purpose digital interfaces. Programming methods used on the data module are as diverse as the devices it is used with. As an example, consider the paper tape reader interface that is described as follows:

Input bits 0-7 are the data currently being read (ONE = hole; ZERO = no hole). Input bit 8 is character present (ONE = present; ZERO = not present). Input bit 9 is unit ready (ONE = ready; ZERO = not ready).

Bit values 1 and 0 represent data as contained in memory.

Only one output is used, bit 0. The data line associated with bit 0 must be normally 3 to 5 volts. The reader is advanced one character by generating a pulse on that data line of 0-0.4 volts for a minimum of 10 microseconds.

| READIN | L       | 7, CRUA      | Assume location CRUA contains CRU address of reader |

|--------|---------|--------------|-----------------------------------------------------|

|        | LA      | 4, BUF       | Location of BUF in Register 4                       |

|        | LA      | 5, READIN    | Set up Program Base Register - necessary for BBNE's |

|        | L       | 0, N         | Get number of characters to be read in Register 0   |

| LOOP   | BBNE    | 9, 1, LOOP   | Wait for Reader Ready                               |

|        | SETB    | 0, 1         | Cause output 0 to be 0 volts                        |

|        | NOP     |              | Delay of about 3 microseconds                       |

|        | SETB    | 0,0          | Cause output 0 to be 5 volts                        |

|        | BBNE    | 8,0,\$       | Wait for current character to go away               |

|        | BBNE    | 8, 1, \$     | Wait for new character                              |

|        | STCR    | (0,8),0      | Put character in memory                             |

|        | AA      | 4, 1         | Increment pointer to BUF                            |

|        | ARB     | -1, LOOP, 0  | Decrement loop counter and branch if not finished.  |

|        | Through | Remainder of | Lingiann                                            |

The preceding sequence identifies the most direct program for reading N characters from reader storage into memory one per word starting at location BUF. The following sequence causes a pulse of approximately 10 microseconds:

SETB 8,1

NOP

SETB 8,0

If longer pulses were required, a timing loop could be used.

In many programming situations it would be undesirable to wait for the character to appear, as this time amounts to many milliseconds. In such cases, the character present signal could be used to initiate a CRU interrupt and more sophisticated programs would be required to service the interrupt and execute the routine that reads data from the paper tape.

If the data module is used with the interrupt option, the instruction SETB 14, 1 enables input 15 to initiate an interrupt. The instruction SETB 14, 0 masks any such interrupt. Output flip-flop 14 is used as the interrupt on the data module. Output flip-flop 15 is used to retain the interrupt indication when the interrupt signal is a short pulse. This flip-flop may be cleared by a SETB 15, 0 or set by a SETB 15, 1. In both of these examples, the bit value for address 14 and 15 is important rather than the instruction SETB. An LDCR applying these values to 14 and 15 would serve as well.

## 2.2.2 DATA MODULE, 32 INPUT (TI PART NUMBER 217382)

This module provides 32 input data lines for one-way communication between the computer and devices or transducers which generate discrete (ON-OFF) signals. Each line can be addressed as a single line or as a member of group of lines. The input data module is particularly effective for use in applications where the number of input lines exceeds the number of output lines. Like the 16 I/O data module, this module may be plugged into any CRU port in the CPU chassis or any port in a CRU expansion unit.

2.2.2.1 SPECIFICATIONS. Specifications for this data module are listed in table 2-3.

Table 2-3. Data Module (32 Input) Specifications

| Characteristic      | Specification                                         |  |

|---------------------|-------------------------------------------------------|--|

| Inputs(32):         | 0V to 1.0V = Logic ONE<br>+3.0V to +5.0V = Logic ZERO |  |

| Power Requirements: | +5.0 Vdc @ 0.7A                                       |  |

- 2.2.2.2 INTERFACE. The inputs are negative logic TTL levels. (See figure 2-7.) An emitter-follower input circuit is used to increase noise margin. Connections to the input lines can be made through an edge connector. The pin assignments are listed in table 2-4.

- 2.2.2.3 PROGRAMMING. This module is addressable as two sets of 16-input lines. The addresses of each set are separated by  $100_{16}$ . This is further explained in the theory of operation section of this manual.

Table 2-4. CRU Bit Functions for the 32 Input Module

| 0 1                                                                                                                                 | CRU Input<br>Bit Address*  | Function                            |                                                                                        | Assignments<br>N-/GND                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 16 19/W 257 17 20/X 18 21/Y 19 22/Z 20 23/Ā 21 24/B 22 25/C 23 26/D 24 27/E 25 28/F 26 29/H 27 30/J 28 31/K 29 32/L 30 33/M 31 34/N | 1<br>•<br>•<br>•<br>•<br>• | 16 General-purpose input lines      | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13                      | 4/D<br>5/E<br>6/F<br>7/H<br>8/J<br>9/K<br>10/L<br>11/M<br>12/N<br>13/P<br>14/R<br>15/S<br>16/T<br>17/U               |

|                                                                                                                                     | 256 257                    | 16 More general-purpose input lines | 16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30 | 19/W<br>20/X<br>21/Y<br>22/Z<br>23/Ā<br>24/B<br>25/C<br>26/D<br>27/E<br>28/F<br>29/H<br>30/J<br>31/K<br>32/L<br>33/M |

#### 2.2.3 DATA MODULE, 32 OUTPUT (TI PART NUMBER 217380)

This module provides 32 output data lines for one-way communication between the computer and devices or transducers which are operated by discrete (ON-OFF) signals. Each line can be addressed as a single independent line or as a member of a group of lines. The output data module is particularly effective in applications where the number of output lines exceeds the number of input lines. Like the 16 I/O data module, each output circuit contains a storage flip-flop that maintains the output until changed by the CPU.

This module may be plugged into any CRU port in the CPU chassis or any port in a CRU expansion unit.

2.2.3.1 SPECIFICATIONS. Specifications for this data module are listed in table 2-5.

Table 2-5. Data Module (32 Output) Specifications

| Characteristic      | Specification                                               |

|---------------------|-------------------------------------------------------------|

| Outputs (32):       | 0.0V to 0.4V = Logic ONE                                    |

| Options:            | Open = Logic ZERO Collector Resistors to +5.0 Vdc on Module |

| Power Requirements: | or up to +30 V External Supply<br>+5.0 Vdc @ 0.7A           |

- 2.2.3.2 INTERFACE. The data module outputs are negative logic levels switching between 0 volts and a positive voltage. Each output line is driven by a transistor switching circuit which is controlled by its corresponding storage flip-flop. (See figure 2-7.) The circuit is capable of sinking up to 50 milliamps and holding off up to +30 Volts dc. An 0.25W resistor on the module can be inserted between the individual transistor collector output and a supply voltage +5V (or a customer supply of up to +30V). Connections to the output lines can be made through an edge connector. The pin assignments are listed in table 2-6.

- 2.2.3.3 PROGRAMMING. This module contains two 16-bit output registers. The addresses for each set are separated by 100<sub>16</sub>. This addressing scheme is explained in the theory of operation section of this manual.

## 2.2.4 DATA MODULE CONTACTOR (TI PART NUMBER 214111)

This module provides two-way communication between the computer and external relay-controlled devices. Isolated relay contacts are used for outputs. Isolated relay coils are used for inputs. There are eight inputs and eight outputs, each of which may be addressed as a single independent line, or as a member of a group of lines. Each output circuit contains a storage flip-flop that maintains the output until changed by the CPU. The module may be plugged into any CRU port; however, the module is thicker than a normal module. Therefore, this module should be used in a high profile CRU port.

2.2.4.1 SPECIFICATIONS. Specifications for this data module are listed in table 2-7.

Table 2-6. CRU Bit Functions for the 32 Output Module

| CRU Output<br>Bit Address*                               | Function                                   | Pin Assignments<br>OUT-/GND                                                                                   |

|----------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>•<br>•<br>•                                    | 16 General-purpose output lines            | 3/C<br>4/D<br>5/G<br>6/F<br>7/H<br>8/J<br>9/K<br>10/L<br>11/M<br>12/N<br>13/P<br>14/R<br>15/S<br>16/T<br>17/U |

| 15<br>256<br>257<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | 16 More general-purpose output lines       | 19/W 20/X 21/Y 22/Z 23/Ā 24/B 25/C 26/D 27/E 28/F 29/H 30/J 31/R 32/L 33/M 34/N                               |

| ,                                                        | Add the CRU port address for actual progra | m address.                                                                                                    |

Table 2-7. Data Module Contactor Specifications

| Characteristic      | Specification                                   |  |

|---------------------|-------------------------------------------------|--|

| Inputs (8):         | TRUE data is +4.5V to +6.0V across 200 OHM Coil |  |

| Outputs (8):        | SPST contact, 250 Vdc maximum, 3A maximum       |  |

| Power Requirements: | +5.0 Vdc @ 0.5A                                 |  |

2.2.4.2 INTERFACE. Isolated relay coils are used for inputs. A logic ONE is represented by 30 mA current and a logic ZERO represents no current. The input relays have operate and release times of approximately 1.0 millisecond and 0.85 millisecond, respectively. A diode is placed in parallel with each coil to protect the drive circuitry.

The outputs are used to drive external devices through isolated contacts. These output contacts are capable of handling 50 Watts at 250 Vdc maximum or current switched at 3.0 Amperes maximum. The approximate operate and release times for these output contacts are 3.0 milliseconds and 1.3 milliseconds, respectively. Each output is one SPST relay contact with a logic ONE closing the contact. Connections between the input/output relays and external devices can be made through an edge connector. Pin assignments are listed in table 2-8.

CRU CRU Output Pin Input Bit Pin Assignment Bit Assignment Address\* Function OUT/RTN Address\* Function IN/RTN\*\* 0 L/K 0 1  $\overline{M}/\overline{N}$ F/E 1 H/T 8 General-purpose output contacts  $\overline{B}/\overline{A}$ 8 General-purpose isolated inputs C/D X/W 7 Y/Z T/S 8 U/V N/M 8 P/R I/H K/L Not Used D/C Not Used E/F 15 15 \*Add the CRU port address for actual program address. \*\*IN must be positive with respect to RTN

Table 2-8. CRU Bit Functions for the Contactor Module

## 2.2.5 EIA DATA MODULE (TI PART NUMBER 966630)

The EIA data module provides a general-purpose 16-bit input and output interface between the CPU and external devices using interface levels that are compatible with EIA Standard RS232C. An output register is provided to hold the output data. The output registers only change on programmed instruction, and are not subject to the CPU master reset. Input data is not stored in register; therefore, the data sense during the time of interrogation will be stored in memory.

2.2.5.1 SPECIFICATIONS. Specifications for the EIA data module are listed in table 2-9.

Table 2-9. EIA Data Module Specifications

| Characteristics              | Specifications                              |

|------------------------------|---------------------------------------------|

| Input Signal Levels:         | ±25V absolute maximum                       |

| 1 0                          | ±15V recommended maximum                    |

|                              | ±3V minimum                                 |

| Output Signal Levels:        | ±8V typical                                 |

| 1 0                          | ±5V minimum                                 |

| Signal Polarity from Device: | Negative voltage equals a memory logic ONE  |

| ,                            | Positive voltage equals a memory logic ZERO |

| Power Requirements:          | +5Vdc @ 0.34A                               |

| 1                            | +15Vdc @ 0.11A                              |

|                              | - 15Vdc @ 0.07A                             |

- 2.2.5.2 INTERFACE. See figure 2-8 for pin assignments.

- 2.2.5.3 PROGRAMMING. The EIA data module is used in the same manner as the 16-input/output data module. Programming details are included in paragraph 2.2.1.3.

### 2.2.6 INTERVAL TIME MODULE (TI PART NUMBER 214114)

The interval timer module accepts a 14-bit binary number from the computer and counts it down to zero in pre-selected (1, 2, 4, or 8 milliseconds) time increments. An interval timer module is required when using the Process Automation Monitors (PAM and PAM/D). Normally, one timer module is sufficient for all time interval measurements in a process control application. The interval timer module plugs into any CRU port.

- 2.2.6.1 SPECIFICATIONS. Specifications for the interval timer module are listed in table 2-10.

- 2.2.6.2 INTERFACE. Normally external connections to the module are not made. The time increments are generated by dividing a 4096 KHz crystal oscillator. All submultiples of this clock, 1.024  $\mu$ s to 8 ms, are available at the top edge of the module. The input to the counter is also available there. Since the standard system software expects count intervals of 1.0 ms, this additional flexibility is only useful in special applications. The standard count intervals may be selected with wire jumpers on the component side of the module as follows:

1 ms E3-E5 4 ms E2-E5

2 ms E4-E5 8 ms E1-E5

|         | Memory<br>Data | Output<br>Register<br>Bit Address | Signature | Interface<br>Connector Pin |

|---------|----------------|-----------------------------------|-----------|----------------------------|

| (MSB)   | 0              | F                                 | OUT 15-   | В                          |

|         | 1              | E                                 | OUT 14-   | C                          |

|         | 2              | D                                 | OUT 13-   | F                          |

|         | 3              | С                                 | OUT 12-   | Н                          |

|         | 4              | В                                 | OUT 11-   | Ĺ                          |

|         | 5              | A                                 | OUT 10-   | M                          |

|         | 6              | 9                                 | OUT 9-    | x                          |

|         | 7              | 8                                 | OUT 8-    | Y                          |

|         | 8              | 7                                 | OUT 7-    | P                          |

|         | 9              | 6                                 | OUT 6-    | N                          |

|         | Α              | 5                                 | OUT 5-    | K                          |

|         | В              | 4                                 | OUT 4-    | j                          |

|         | С              | 3                                 | OUT 3-    | E                          |

|         | D              | 2                                 | OUT 2-    | D                          |

| <i></i> | Ε              | 1                                 | OUT 1-    | A                          |

| (LSB)   | F              | 0                                 | OUT 0-    | Z                          |

|       | Memory<br>Data | Input Bus<br>Bit Address | Signature | Interface<br>Connector Pin |

|-------|----------------|--------------------------|-----------|----------------------------|

| (MSB) | 0              | F                        | IN 15-    | 14                         |

|       | 1              | E                        | IN 14-    | P                          |

|       | 2              | D                        | IN 13-    | 13                         |

|       | 3              | С                        | IN 12-    | N.                         |

|       | 4              | 8                        | IN 11-    | 8                          |

|       | 5              | Α                        | IN 10-    | н                          |

|       | 6              | 9                        | IN 9-     | 7                          |

|       | 7              | 8                        | IN 8-     | F                          |

|       | 8              | 7                        | IN 7-     | C                          |

|       | 9              | 6                        | IN 6-     | 3                          |

| A     | Α              | 5                        | IN 5-     | В                          |

|       | В              | 4                        | IN 4-     | 2                          |

|       | С              | 3                        | IN 3-     | E                          |

|       | D              | 2                        | IN 2-     | 5                          |

|       | E              | 1                        | IN 1-     | D                          |

| (LSB) | F              | 0                        | IN 0-     | 4                          |

(A) 128537

Figure 2-8. CRU Bit Functions for EIA Data Module

Table 2-10. Interval Timer Module Specifications

| Characteristic                  | Specification                                                                                                                                     |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Resolution:                     | 1, 2, 4, or 8 milliseconds (selected by wire jumper)                                                                                              |

| Maximum Count:                  | 16,384 time increments                                                                                                                            |

| Interrupt:                      | At count = 0 timer causes interrupt, but continues to count negative to prevent any loss of real-time due to interrupt servicing by the computer. |

| Maximum Time Interval Measured: | Unlimited. Software can reset the timer periodically to keep time indefinitely.                                                                   |

| Power Requirements:             | +5.0 Vdc @ 0.5A                                                                                                                                   |

E1, E2, E3, E4, E5 are terminals staked to the board.

2.2.6.3 PROGRAMMING. The program-addressable input and output functions of the interval timer are listed in table 2-11 with applicable line addresses. The 14-bit initialization value may be transferred at any time. This 14-bit value immediately displaces the current counter contents. The CRU address assignment is such that the least significant bit (LSB) in the memory word VALUE selected by the instruction LDCR (1, 14), VALUE is considered to be the LSB of the count value. Similarly, the current counter contents ("Dynamic Count") may be read at any time with the LSB of the counter being the LSB in memory. This means that after the two instructions [LDCR (1, 14), VALUE and STCR (1, 15), COUNT] are executed, VALUE and COUNT will contain the same number. Fifteen bits are read in order that the last bit (15) will be zero, giving a 14-bit positive value in memory (memory bits 0, 1 = 0).

Table 2-11. CRU Bit Functions for the Interval Timer

| CRU Output<br>Bit Address* | Function                                                  | CRU Input<br>Bit Address* | Function                              |

|----------------------------|-----------------------------------------------------------|---------------------------|---------------------------------------|

| 0                          | 0 = Clear Interrupt                                       | 0 1                       | Timer Interrupt Status: 1 = Interrupt |

|                            | 14-Bit Count Initialization Value from CPU — Bit 1 is LSB |                           | 14-Bit Dynamic Count – Bit 1 is LSB   |

| 14 <i>)</i><br>15          | 1/0 = Start/Stop Control                                  | 15                        | Not used - Always = 0                 |

|                            | *Add the CRU port add                                     | ress for actual program   | n address.                            |

When the counter contains a count of ZERO, a CRU interrupt is generated. There is no mask for this interrupt on the module. The interrupt can be cleared by a SETB 0, 0 only if the counter is non-ZERO. The interrupt can also be set independent of the counter by a SETB 0, 1. The counter continues to decrement past zero in order to lose no count intervals. In real-time applications, this allows the program to determine how many count intervals have passed since the interrupt was generated.

#### 2.2.7 INTERRUPT MODULE (TI PART NUMBER 214087)

The interrupt module may be used in any CRU port to provide 8 interrupt flip-flops and 8 mask flip-flops. Additional modules may be used to provide up to 2048 interrupts (one module in every available CRU slot). Interrupt lines can be masked out individually (or in groups) by the computer to disable selected interrupts. When any unmasked interrupt line comes True (i.e., 0 Volts), the computer receives a CRU interrupt and can scan the interrupt lines to determine which interrupt has occurred.

#### NOTE

Each 16 I/O data module also has the capability of providing a single interrupt line and mask.

2.2.7.1 SPECIFICATIONS. Specifications for the interrupt module are listed in table 2-12.

Characteristic

Specification

Inputs:

8 buffered TTL level interrupts

0V to 1.0V = Logic ONE

3.0V to 5.0V = Logic ZERO

Outputs:

One interrupt active status line for connection to CRU data inputs. Facilitates fast interrupt scan when several interrupt modules are used.

Power Requirements:

+5.0 Vdc @ 0.5A

Table 2-12. Interrupt Module Specifications

2.2.7.2 INTERFACE. The interrupt inputs are negative logic TTL level signals. Zero volts is the "True" or interrupt-on level. Filter capacitor pads for each interrupt input are provided on the module as shown in figure 2-7. External connections to the interrupt lines are made at the top edge of the module through an edge connector. Pin assignments are listed in table 2-13.

| CRU<br>Output<br>Bit Address* | Function                   | CRU<br>Input<br>Bit Address* | Function                  | Pin Assignments IN-/GND                       |

|-------------------------------|----------------------------|------------------------------|---------------------------|-----------------------------------------------|

| 0                             | 1/0 = Set/Clear Interrupts | 0 )                          |                           | M/N                                           |

| • }                           | 0–7, respectively          | • \                          | Interrupt flip-flops 0-7, | $\overline{\mathbf{H}}/\overline{\mathbf{J}}$ |

| •                             |                            | • (                          | 1 = Interrupt             | <b>C</b> / <del>D</del>                       |

| 7ノ<br>8                       |                            | 7 🗸                          |                           | Y/Z                                           |

| 8 )                           | 1/0 = Enable/Mask          | 8                            |                           | U/V                                           |

| • /                           | interrupts 0-7,            | • (                          | Not used                  | P/R                                           |

| • (                           | Respectively               | • (                          | Not used                  | K/L                                           |

| ر 15                          | £ /                        | 15 )                         |                           | E/F                                           |

Table 2-13. CRU Bit Functions for the Interrupt Module

2.2.7.3 PROGRAMMING. Table 2-13 lists the CRU bit assignments for the interrupt module. Output addresses 0 through 7 are normally used to clear the interrupt flip-flops; however, these addresses may also be used to set the interrupt flip-flops under program control.

The interrupt flip-flop inputs, input addresses 0 through 7, may be read by any CRU input instruction. Only those interrupt lines that are enabled and have an interrupt stored will be read as interrupts.

#### 2.2.8 A/D CONVERTER-MULTIPLEXER (TI PART NUMBER 217690)

This module converts a single-ended analog voltage signal to a 12-bit, two's complement binary number. Basically, it consists of a 16-channel 12-bit analog-to-digital converter and data multiplexer logic which sequentially reads the converted value into the computer.

This A/D module must be installed in a CRU port wired for ±15 volts power in addition to the standard +5 volts. This module is thicker than normal, dictating that it be inserted in a high profile CRU port.

The A/D converter module is available in four optional configurations:

Option 1 - The basic converter with one input channel

Option 2 - Option 1 plus a sample and hold circuit

Option 3 - Option 2 plus an 8-channel input multiplexer

Option 4 - Option 2 plus a 16-channel input multiplexer

2.2.8.1 SPECIFICATIONS. Specifications for the A/D converter are listed in table 2-14.

Table 2-14. A/D Converter-Multiplexer Specifications

| Characteristic      | Specification                                     |

|---------------------|---------------------------------------------------|

| Input Signal Level: |                                                   |

| Option 1            | 0 to +10.0V, ±5.0V, ±5.0V, or ±10.0V single-ended |

| Option 2, 3, or 4   | 0 to + 10.0V, ±5.0V single-ended                  |

| Sample Aperture:    |                                                   |

| Option 1            | 25 microseconds maximum                           |

| Option 2, 3, or 4   | 500 nanoseconds maximum                           |

| Input Impedance:    |                                                   |

| Option 1            | 5K ohm (±5.0V inpur)                              |

|                     | 10K ohm (±10.0V input)                            |

| Option 2, 3, or 4   | > 10 megohm                                       |

| Conversion Time:    |                                                   |

| Option 1            | 25 microseconds                                   |

| Option 2, 3, or 4   | 225 microseconds                                  |

| Accuracy:           |                                                   |

| Option 1            | ±0.5%@ 25°C                                       |

| Option 2            | ±0.75%@ 25°C                                      |

| Option 3 or 4       | ±1.0%@ 25°C                                       |

|                     | NOTE                                              |

|                     | reference supply tolerances, quantization error,  |

|                     | , sample and hold and multiplexer transfer error. |

- 2.2.8.2 INTERFACE. All power and logic signal connections are made through the CRU connector on the bottom edge of the A/D card. Analog input signal connections are made using an edge connector at the top of the card. Table 2-15 lists the pin assignments.

- 2.2.8.3 PROGRAMMING. Table 2-16 lists the input and output address functions for the A/D module. The 16 CRU output lines of the CRU port (in which the A/D module is plugged) are used to address one of the 16 possible analog input channels and used to start a conversion. The instruction SETB 9, 1 causes channel 9 to be selected and converted. An LDCR instruction may also be used, provided that at least one bit is a ONE in the output field. If the field contains multiple ONES, the ONE going the lowest numbered CRU line is used to select the input channel. Once a conversion has started, the Busy/Ready line remains a ZERO until the conversion is complete. The 12-bit converted value may then be stored. Input bits 2 and 3 are a logic ONE to indicate full scale negative (800<sub>16</sub>) or full scale positive (7FF<sub>16</sub>) readings.

Table 2-15. Pin Assignments for A/D Converter Multiplexer Module

| Analog<br>Input Number | IN/GND       |

|------------------------|--------------|

| 0                      | M/Ñ          |

| 1                      | ਜੋ/ <u>J</u> |

| 2                      | ੋਂ ਹੋ        |

| 3                      | Y/Z          |

| 4                      | U/V          |

| 5                      | P/R          |

| 6                      | K/L          |

| 7                      | E/F          |

| 8                      | 33/34        |

| 9                      | 29/30        |

| 10                     | 25/26        |

| 11                     | 21/22        |

| 12                     | 17/18        |

| 13                     | 13/14        |

| 14                     | 9/10         |

| 15                     | 5/6          |

Table 2-16. CRU Bit Functions for the A/D Converter/Multiplexer Module

| CRU Output<br>Bit Address* | Function                          | CRU Input<br>Bit Address* | Function                          |

|----------------------------|-----------------------------------|---------------------------|-----------------------------------|

| 0                          | 1 = Sample and Convert Channel 0  | 0                         | Busy/Ready Status, 1 = Ready      |

| 1                          | 1 = Sample and Convert Channel 1  | 1                         | Not Used - Always = 0             |

| 2                          | 1 = Sample and Convert Channel 2  | 2                         | 1 = Overscale negative indication |

| 3                          | 1 = Sample and Convert Channel 3  | 3                         | 1 = Overscale positive indication |

| 4                          | 1 = Sample and Convert Channel 4  | 4                         | •                                 |

| 5                          | 1 = Sample and Convert Channel 5  | •                         |                                   |

| 6                          | 1 = Sample and Convert Channel 6  |                           |                                   |

| 7                          | 1 = Sample and Convert Channel 7  | . \                       | 12-bit converted value            |

| 8                          | 1 = Sample and Convert Channel 8  | • (                       | Bit 4 is LSB                      |

| 9                          | 1 = Sample and Convert Channel 9  | •                         | May be Two's complement signed    |

| 10                         | 1 = Sample and Convert Channel 10 |                           | value or straight binary          |

| 11                         | 1 = Sample and Convert Channel 11 |                           | depending on jumper option        |

| 12                         | 1 = Sample and Convert Channel 12 | 15                        | (See user's manual for details)   |

| 13                         | 1 = Sample and Convert Channel 13 | )                         | ()                                |

| 14                         | 1 = Sample and Convert Channel 14 |                           |                                   |

| 15                         | 1 = Sample and Convert Channel 15 |                           |                                   |

The following instruction sequence is adequate to cause a conversion on analog channel 3 and place the value in READING:

| SETB | 3, 1             | Start conversion on channel 3 |

|------|------------------|-------------------------------|

| BBNE | 0, 1, \$         | Wait for Ready                |

| STCR | (4, 12), READING | Get converter value           |

| BBNE | 2, 0, FSNEG      | Check for full scale          |

| BBNE | 3, 0, FSPOS      | Readings                      |

The last two instructions are not required unless the full scale tests are desired.

#### 2.2.9 D/A CONVERTER WITH REGISTERS (TI PART NUMBER 217686)

This module converts a 12-bit, two's complement binary number to a  $\pm 5$  volt,  $\pm 10$  volts, or 0 to  $\pm 10$  volt analog signal. The module is available with 1, 2, or 3 channel output options. Internal reference voltage supplies are included on the module.

The D/A card must be plugged into a CRU port wired for  $\pm 15$  volts in addition to the standard +5 volts. This module is thicker than normal, dictating that it be inserted in a high profile CRU port.

2.2.9.1 SPECIFICATIONS. Specifications for the D/A Converter are listed in table 2-17.

Table 2-17. D/A Converter Specifications

| Characteristic                 | Specifications                                          |  |

|--------------------------------|---------------------------------------------------------|--|

| Options                        | 1, 2, or 3 output analog voltages                       |  |

| Output Voltage Range           | ±5.0V @ 10.0 ma maximum                                 |  |

|                                | ±10.0V @ 10.0 ma maximum                                |  |

|                                | 0 to +10.0V @ 10.0 ma maximum                           |  |

| Output Accuracy                | ±0.5%@ 25°C                                             |  |

| ·                              | (includes reference supply variation and non-linearity) |  |

| Output Temperature Coefficient | ±30 ppm/°C                                              |  |

| Settling Time                  | 5 microseconds maximum to 0.01% of full scale           |  |

| Power Requirements:            |                                                         |  |

| Option 1 (1 channel)           | +5.0V @ 330 ma, ±15.0V @ 60 ma                          |  |

| Option 2 (2 channels)          | +5.0V @ 430 ma, ±15.0V @ 120 ma                         |  |

| Option 3 (3 channels)          | +5.0V @ 530 ma, ±15.0V @ 180 ma                         |  |

2.2.9.2 INTERFACE. All power and logic connections are made through the CRU connector on the bottom edge of the D/A card. Connections between the analog output terminals and the external devices are made with an edge connector on top of the D/A card. Table 2-18 lists the pin assignments for the analog output signals.

Table 2-18. Pin Assignments for D/A Module Outputs

| Converter<br>Number | OUT/GND                                       |

|---------------------|-----------------------------------------------|

| 0                   | $\overline{\mathtt{L}}/\overline{\mathtt{K}}$ |

| 1                   | L/K<br>芹/Ē                                    |

| 2                   | $\overline{\mathtt{B}}/\overline{\mathtt{A}}$ |

|                     |                                               |

2.2.9.3 PROGRAMMING. Table 2-19 lists the output address assignments for the D/A module. The input lines are not used. Output lines 1, 2, and 3 are used to enable one or more of the three converters. Any CRU output instruction addressed to the D/A Module will initiate conversion by the enabled converters. The following instruction sequence will reset the enable flip-flops and output 3 values to converter number 1:

|        | LDCR | (1, 3), ZERO    | Reset Enable FF's                       | 1 |

|--------|------|-----------------|-----------------------------------------|---|

|        | LDCR | (4, 12), VALUE1 | Set Up Value                            |   |

|        | SETB | (3, 1)          | ENABLE Converter 1 and Start Conversion | 1 |

|        | LDCR | (4, 12), VALUE2 | Convert Value 2                         |   |

|        | LDCR | (4, 12), VALUE3 | Convert Value 3                         |   |

|        | •    |                 |                                         |   |

|        | •    |                 |                                         |   |

|        | •    |                 |                                         |   |

| ZERO   | DATA | 0               | VALUES TO BE                            |   |

| VALUEI | DATA | 18              | CONVERTED                               |   |

| VALUE2 | DATA | 20              |                                         |   |

| VALUE3 | DATA | 27              |                                         |   |

Since the execution time for an LDCR on a 12-bit field is about 7.0  $\mu$ sec, this will cause three conversions about 7  $\mu$ sec apart. Converter 1 is not enabled until the SETB 3, 1 which also starts the first conversion. The end of the LDCR instruction causes conversion for VALUE2 and VALUE3. An alternative is to use instructions of the form LDCR (0, 16), VALUE where VALUE

Table 2-19. CRU Bit Functions for the D/A Module

| CRU Output<br>Bit Address*                            | Function                                     |  |

|-------------------------------------------------------|----------------------------------------------|--|

| 0                                                     | Not Used                                     |  |

| 1                                                     | 1 = Enable Channel 3 Converter               |  |

| 2                                                     | 1 = Enable Channel 2 Converter               |  |

| 3                                                     | 1 = Enable Channel 1 Converter               |  |

| 4                                                     | 12-bit value to be converted<br>Bit 4 is LSB |  |

| *Add the CRU port address for actual program address. |                                              |  |

contains the number to be converted in memory bits 0 through 11 and bits 12, 13, and 14 contain ones for each converter to be enabled. This enables the converters required, sets up the value to be converted, and starts conversion.

Another use, more typical perhaps, would be a LDCR (4, 12) to load value to be converted followed by SETBX, I then SETBX, 0 with X being desired channel; this will load in desired value for channel then <u>remove</u> enable so other values can be loaded for other channels.

#### 2.2.10 DATA COMMUNICATIONS MODULE (TI PART NUMBER 961642)

The communications interface module allows the computer to communicate, through the CRU, with peripheral devices whose interface is specified by EIA document RS232C. This module interfaces to datasets for phone line transmission as well as EIA compatible terminals. A TI ASR733 or KSR733 terminal, or a Teletypewriter ASR33 may be interfaced through this module as an option.

- 2.2.10.1 SPECIFICATIONS. Specifications for the data communications module are listed in table 2-20.

- 2.2.10.2 INTERFACE. Dataset connections to the module are made at the top edge of the card; cables are available for modem and EIA devices. Baud rates are selected by jumper wires on the module. The communications module may be used in any CRU port. The port must be wired for ±15V if the EIA functions are to be used. Table 2-21 lists the pin assignments for the interface signals.

Table 2-20. Data Communications Module Specifications

| Characteristic     | Specification                                                                           |

|--------------------|-----------------------------------------------------------------------------------------|

| Operating Modes:   | With Bell 103 (A or F)                                                                  |

|                    | With Bell 202 (C or D) datasets                                                         |

|                    | 110 baud                                                                                |

|                    | 150 baud                                                                                |

|                    | 300 baud                                                                                |

|                    | 1200 baud                                                                               |

|                    | 1200 baud, Bell 202 with reverse channel                                                |

|                    | 1760 baud                                                                               |

|                    | 1760 baud, Bell 202 with reverse channel                                                |