# TEXAS INSTRUMENTS

Improving Man's Effectiveness Through Electronics

# Model 980 Computer

Assembly Language Programmer's Reference Manual

MANUAL NO. 943013-9701

ORIGINAL ISSUE 15 DECEMBER 1974

REVISED AND REISSUED 1 MARCH 1975

INCLUDES

CHANGE 1...................1 MARCH 1976

## © Texas Instruments Incorporated 1976 All Rights Reserved

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

No disclosure of the information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments Incorporated.

# LIST OF EFFECTIVE PAGES

INSERT LATEST CHANGED PAGES DESTROY SUPERSEDED PAGES

Note: The portion of the text affected by the changes is indicated by a vertical bar in the outer margins of the page.

Model 980 Computer Assembly Language Programmer's Reference Manual (943013-9701)

Original Issue

...

15 December 1974

Revised and Reissued

...

1 March 1975 (ECN 388070)

Change 1

...

1 March 1976 (ECN 407116)

Total number of pages in this publication is 166 consisting of the following:

| PAGE CHAN                |                      | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. |

|--------------------------|----------------------|---------------|-------------|---------------|

| Cover                    | 1 4-20               | 1             |             | • •           |

| Effective Pages          | 1 4-21 - 4-22        | 0             |             |               |

|                          | O Appendix A Divider | _             |             |               |

| vi - viii                | 1 4 1 4 4            | 0             |             |               |

| 1-1 - 1-2                | 1 Appendix B Divider |               |             |               |

| 2-1 - 2-8                |                      | 0             |             |               |

| 3-1 - 3-7 (              | Appendix C Divider   | 0             |             |               |

| 3-8                      | C-1 - C-2            | 0             |             |               |

| 3-8A/3-8B                | User's Response.     | 0             |             |               |

| 3-9 - 3-55               | - dointoob reopry .  | 1             |             |               |

| 3-56                     | Cover Blank          | 0             |             | *             |

| 3-57 - 3-92              | Cover                | 0             |             |               |

| 3-93                     |                      |               |             |               |

| 3-94 - 3-96 0            |                      |               |             |               |

| $\frac{4-1}{4\cdot 2}$ 0 |                      |               |             |               |

| 4-2                      |                      |               |             |               |

| 4-2A/4-2B                |                      |               |             |               |

| 11 10                    |                      |               |             |               |

| 4-4 - 4-5 0              |                      |               |             |               |

| 4-8A/4-8B 1              |                      |               | •           |               |

| 4-9 - 4-10               |                      |               | •           |               |

| 4-11                     |                      |               |             |               |

| 4-12                     |                      |               |             |               |

| 4-12A/4-12B 1            |                      |               |             |               |

| 4-13 - 4-19 0            |                      |               |             |               |

# TABLE OF CONTENTS

| Paragraph                                     | Title                                            | Page                                          |

|-----------------------------------------------|--------------------------------------------------|-----------------------------------------------|

|                                               | SECTION I. GENERAL INFORMATION                   |                                               |

| 1.1<br>1.2                                    | Scope of Manual                                  | 1-1<br>1-1                                    |

|                                               | SECTION II. HARDWARE FEATURES                    |                                               |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | General                                          | 2-1<br>2-1<br>2-3<br>2-4<br>2-6<br>2-7<br>2-7 |

| SECTION                                       | N III. MACHINE INSTRUCTIONS AND CODING CONVENTIO | NS                                            |

| 3.1                                           | General                                          | 3-1                                           |

| 3.1.1                                         | Instruction Descriptions                         | 3 - 1                                         |

| 3.1.2                                         | Addressing Modes                                 | 3-5                                           |

| 3.1.3                                         | Extended Format Addressing                       | 3-8                                           |

| 3.2                                           | Load Instructions                                | 3-8                                           |

| 3.2.1                                         | Double Load Registers A and E (DLD)              | 3-8                                           |

| 3.2.2                                         | Load Register A (LDA)                            | 3-9                                           |

| 3.2.3                                         | Load Register E (LDE)                            | 3-10                                          |

| 3.2.4                                         | Load Register M (LDM)                            | 3-10                                          |

| 3.2.5                                         | Load Register X (LDX)                            | 3-11                                          |

| 3.2.6                                         | Load Register File (LRF)                         | 3-12                                          |

| 3.3                                           | Store Instructions                               | 3-13                                          |

| 3.3.1                                         | Double Store Registers A and E (DST)             | 3-13                                          |

| 3.3.2                                         | Store Register File (SRF)                        | 3-13                                          |

| 3.3.3                                         | Store Register A (STA)                           | 3-14                                          |

| 3.3.4                                         | Store Register E (STE)                           | 3-15                                          |

| 3.3.5                                         | Store Register X (STX)                           | 3-16                                          |

| 3.4                                           | Branch Instructions                              | 3-16                                          |

| 3.4.1                                         | Branch on Incremented Index (BIX)                | 3-17                                          |

| 3.4.2                                         | Branch and Link (BRL)                            | 3-18                                          |

| 3.4.3                                         | Branch Unconditional (BRU)                       | 3-19                                          |

| 3.4.4                                         | Idle (IDL)                                       | 3-20                                          |

# TABLE OF CONTENTS (Continued)

| Paragraph | Title                                   | Page |

|-----------|-----------------------------------------|------|

| 3.4.5     | Load Status Block and Branch (LSB)      | 3-21 |

| 3.4.6     | Load Status Block, Reset Interrupt, and |      |

|           | Branch (LSR)                            | 3-22 |

| 3.4.7     | Store Status Block and Branch (SSB)     | 3-23 |

| 3.5       | Arithmetic Instructions                 | 3-24 |

| 3.5.1     | Add to Register A (ADD)                 | 3-25 |

| 3.5.2     | Double Length Add (DAD)                 | 3-25 |

| 3.5.3     | Divide (DIV)                            | 3-26 |

| 3.5.4     | Double Length Subtract (DSB)            | 3-27 |

| 3.5.5     | Increment Memory by One (IMO)           | 3-28 |

| 3.5.6     | Multiply (MPY) ,                        | 3-29 |

| 3.5.7     | Register Add (RAD)                      | 3-30 |

| 3.5.8     | Register Complement (RCO)               | 3-31 |

| 3.5.9     | Register Decrement (RDE)                | 3-31 |

| 3.5.10    | Register Increment (RIN)                | 3-32 |

| 3.5.11    | Register Invert (RIV)                   | 3-33 |

| 3.5.12    | Register Subtract (RSU)                 | 3-34 |

| 3.5.13    | Subtract from Register A (SUB)          | 3-35 |

| 3.6       | Compare Instructions                    | 3-36 |

| 3.6.1     | Compare Logical Character String (CLC)  | 3-36 |

| 3.6.2     | Compare Algebraic (CPA)                 | 3-38 |

| 3.6.3     | Compare Logical (CPL)                   | 3-39 |

| 3.6.4     | Register Compare Algebraic (RCA)        | 3-40 |

| 3.6.5     | Register Compare Logical (RCL)          | 3-41 |

| 3.7       | Skip Instructions                       | 3-42 |

| 3.7.1     | Decrement Memory and Test (DMT)         | 3-42 |

| 3.7.2     | Skip on Equal (SEQ)                     | 3-43 |

| 3.7.3     | Skip on Even (SEV)                      | 3-44 |

| 3.7.4     | Skip on Greater than or Equal (SGE)     | 3-44 |

| 3.7.5     | Skip on Greater Than (SGT)              | 3-45 |

| 3.7.6     | Skip on Less Than or Equal (SLE)        | 3-46 |

| 3.7.7     | Skip on Less Than (SLT)                 | 3-47 |

| 3.7.8     | Skip on Minus (SMI)                     | 3-48 |

| 3.7.9     | Skip on No Carry (SNC)                  | 3-48 |

| 3.7.10    | Skip on Not Equal (SNE)                 | 3-49 |

| 3.7.11    | Skip on Not All Ones (SNO)              | 3-50 |

| 3.7.12    | Skip on No Overflow (SNV)               | 3-51 |

| 3.7.13    | Skip on Not All Zeros (SNZ)             | 3-52 |

| 3.7.14    | Skip on Carry (SOC)                     | 3-52 |

| 3.7.15    | Skip on Odd (SOD)                       | 3-53 |

| 3.7.16    | Skip on All Ones (SOO)                  | 3-54 |

# TABLE OF CONTENTS (Continued)

| Paragraph | ${f Title}$                              | Page          |

|-----------|------------------------------------------|---------------|

| 3.7.17    | Skip on Overflow (SOV)                   | 3-55          |

| 3.7.18    | Skip on Plus (SPL)                       | 3-55          |

| 3.7.19    | Skip on Sense Switch Equal (SSE)         | 3 <b>-</b> 56 |

| 3.7.20    | Skip on Sense Switch not Equal (SSN)     | 3 <b>-</b> 57 |

| 3.7.21    | Skip on Zero (SZE)                       | 3 <b>-</b> 58 |

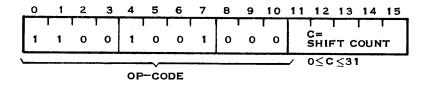

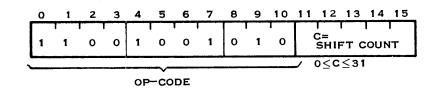

| 3.8       | Shift Instructions                       | 3-58          |

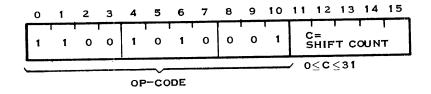

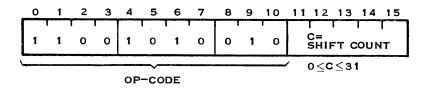

| 3.8.1     | Arithmetic Left Shift Register A (ALA)   | 3-59          |

| 3.8.2     | Arithmetic Left Shift Double (ALD)       | 3 <b>-</b> 59 |

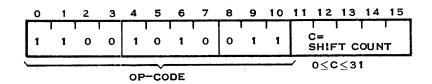

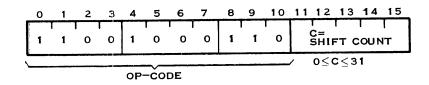

| 3.8.3     | Arithmetic Right Shift Register A (ARA)  | 3-60          |

| 3.8.4     | Arithmetic Right Shift Double (ARD)      | 3-61          |

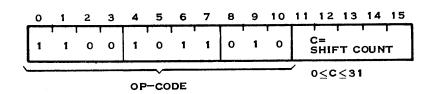

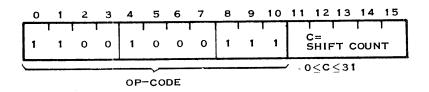

| 3.8.5     | Circular Left Shift Double (CLD)         | 3-62          |

| 3.8.6     | Circular Right Shift Register A (CRA)    | 3-62          |

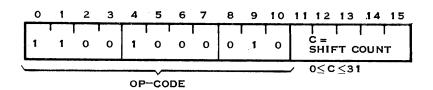

| 3.8.7     | Circular Right Shift Register B (CRB)    | 3-63          |

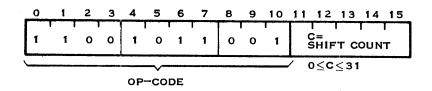

| 3.8.8     | Circular Right Shift Double (CRD)        | 3-64          |

| 3.8.9     | Circular Right Shift Register E (CRE)    | 3-64          |

| 3.8.10    | Circular Right Shift Register L (CRL)    | 3-65          |

| 3.8.11    | Circular Right Shift Register M (CRM)    | 3 <b>-</b> 66 |

| 3.8.12    | Circular Right Shift Register S (CRS)    | 3 <b>-</b> 66 |

| 3.8.13    | Circular Right Shift Register X (CRX)    | 3 <b>-67</b>  |

| 3.8.14    | Logical Left Shift Register A (LLA)      | 3 <b>-</b> 68 |

| 3.8.15    | Logical Left Shift Double (LLD)          | 3 <b>-</b> 68 |

| 3.8.16    | Logical Right Shift Register A (LRA)     | 3 <b>-</b> 69 |

| 3.8.17    | Logical Right Shift Double (LRD)         | 3-70          |

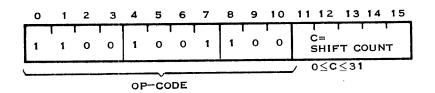

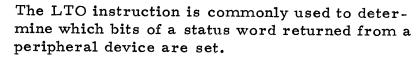

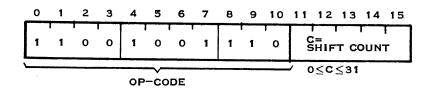

| 3.8.18    | Left Test for Ones in Register A (LTO)   | 3-70          |

| 3.8.19    | Left Test for Zeros in Register A (LTZ)  | 3-71          |

| 3.8.20    | Normalize (NRM)                          | 3-72          |

| 3.8.21    | Right Test for Ones in Register A (RTO)  | 3-73          |

| 3.8.22    | Right Test for Zeros in Register A (RTZ) | 3-74          |

| 3.9       | Logical Instructions                     | 3-75          |

| 3.9.1     | Logical AND with Register A (AND)        | 3-75          |

| 3.9.2     | Logical OR with Register A (IOR)         | 3-76          |

| 3.9.3     | Register AND (RAN)                       | 3-77          |

| 3.9.4     | Register Exclusive OR (REO)              | 3-77          |

| 3.9.5     | Register OR (ROR)                        | 3-78          |

| 3.10      | Bit Manipulation Instructions            | 3-79          |

| 3.10.1    | Set Register A Bit to One (SABO)         | 3-79          |

| 3.10.2    | Set Register A Bit to Zero (SABZ)        | 3-80          |

| 3.10.3    | Set Memory Bit to One (SMBO)             | 3-81          |

| 3.10.4    | Set Memory Bit to Zero (SMBZ)            | 3-82          |

| 3.10.5    | Test Register A Bit for One (TABO)       | 3-83          |

| 3.10.6    | Test Register A Bit for Zero (TABZ)      | 3-83          |

# TABLE OF CONTENTS (Continued)

| Paragraph | Title                                          | Page          |

|-----------|------------------------------------------------|---------------|

| 3.10.7    | Test Memory Bit for One (TMBO)                 | 3-84          |

| 3.10.8    | Test Memory Bit for Zero (TMBZ)                | 3-85          |

| 3.11      | Move Instructions                              | 3-86          |

| 3.11.1    | Move Character String (MVC)                    | 3-86          |

| 3.11.2    | Register Exchange (REX)                        | 3-88          |

| 3.11.3    | Register Move (RMO)                            | 3-88          |

| 3.12      | Input/Output Instructions                      | 3 <b>-</b> 89 |

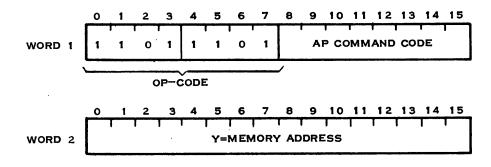

| 3.12.1    | Auxiliary Processor Initiate (API)             | 3 <b>-</b> 89 |

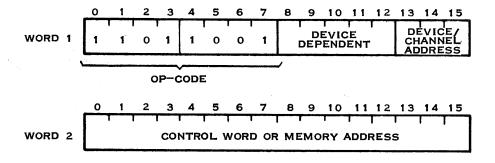

| 3.12.2    | Automatic Transfer Instruction (ATI)           | 3-91          |

| 3.12.3    | Read Direct Single (RDS)                       | 3-92          |

| 3.12.4    | Write Direct Single (WDS)                      | 3-94          |

| SECTI     | ON IV. ASSEMBLER CHARACTERISTICS AND DIRECTIVE | S             |

| 4.1       | General                                        | 4-1           |

| 4.2       | Symbolic Assembly Program (SAP)                | 4-1           |

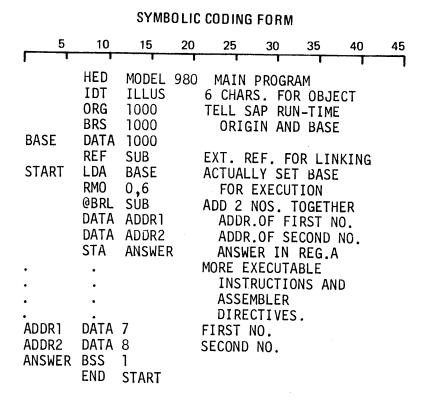

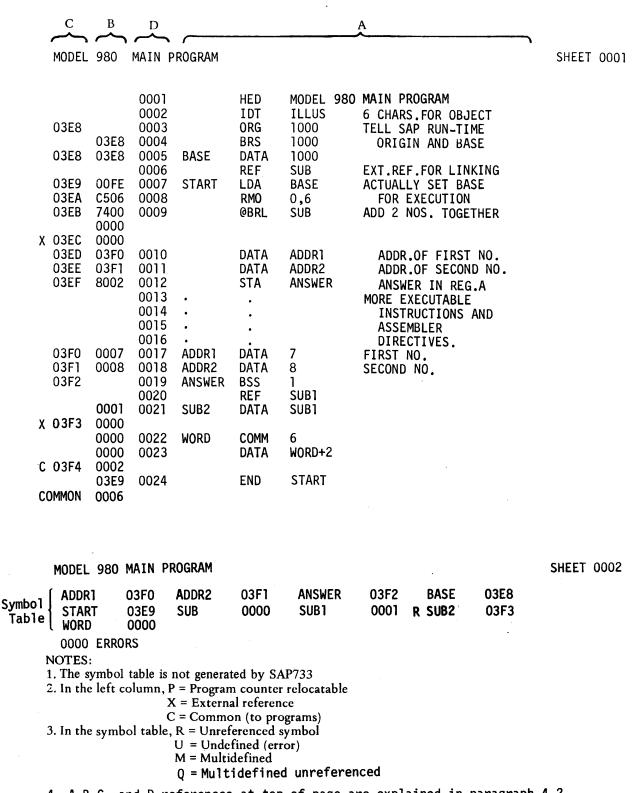

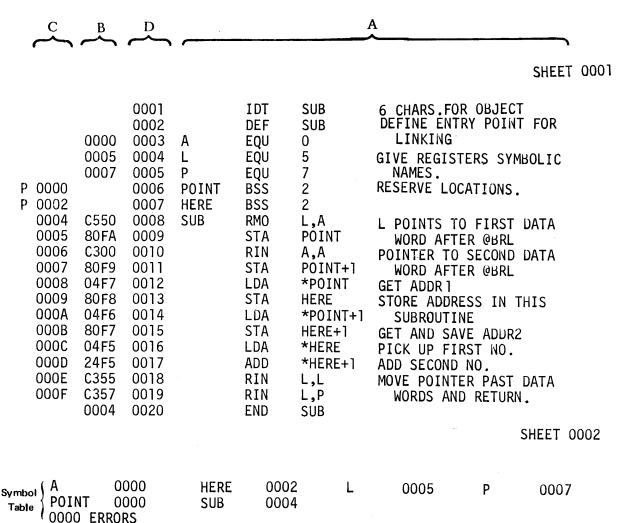

| 4.2.1     | SAP Coding Line Format                         | 4-5           |

| 4.2.2     | Segmented Source Programs                      | 4-7           |

| 4.2.3     | SAP Object Format                              | 4-8           |

| 4.2.4     | SAP Error Messages                             | 4-8           |

| 4.3       | Assembler Directives                           | 4-8           |

| 4.3.1     | Block Ending Symbol (BES)                      | 4-9           |

| 4.3.2     | Base Register Reset (BRR)                      | 4-10          |

| 4.3.3     | Base Register Set (BRS)                        | 4-10          |

| 4.3.4     | Block Starting Symbol (BSS)                    | 4-11          |

| 4.3.5     | Generate Byte Address (BYTE)                   | 4-12          |

| 4.3.6     | Blank Common (COMM)                            | 4-12          |

| 4.3.7     | Generate Word Address or Data (DATA)           | 4-13          |

| 4.3.8     | Define Entry Point Symbol (DEF)                | 4-13          |

| 4.3.9     | End of Source (END)                            | 4-15          |

| 4.3.10    | Equate (EQU)                                   | 4-16          |

| 4.3.11    | Flag Bit Address (FLAG)                        | 4-16          |

| 4.3.12    | Format a New Instruction (FRM)                 | 4-17          |

| 4.3.13    | Page Heading (HED)                             | 4-18          |

| 4.3.14    | Object Identifier (IDT)                        | 4-18          |

| 4.3.15    | Conditional Assembly (IF)                      | 4-18          |

| 4.3.16    | Start Listing (LIS)                            | 4-19          |

| 4.3.17    | Operation Define (OPD)                         | 4-19          |

| 4.3.18    | Origin (ORG),                                  | 4-21          |

| 4.3.19    | Page Eject (PEJ)                               | 4-21          |

| 4.3.20    | Referenced External Symbols (REF)              | 4-2.2         |

| 4.3.21    | Stop Listing (UNL)                             | 4-22          |

Appendix

# APPENDIXES

Title

| A<br>B<br>C                     | Instruction Execution Times                                         | A-1<br>B-1<br>C-1                 |

|---------------------------------|---------------------------------------------------------------------|-----------------------------------|

|                                 | LIST OF ILLUSTRATIONS                                               |                                   |

| Figure                          | $\mathtt{Title}$                                                    | Page                              |

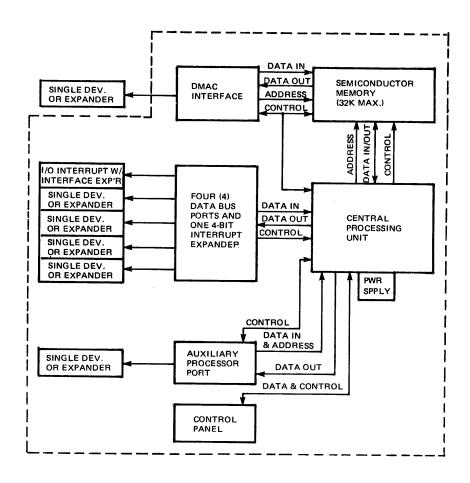

| 2-1                             | Model 980 Computer Block Diagram                                    | 2-1                               |

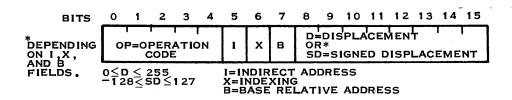

| 3-1                             | Register-Memory Instruction Fields                                  | 3-5                               |

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5 | Source Coded Main Program                                           | 4-1<br>4-2A<br>4-3<br>4-4<br>4-14 |

|                                 | LIST OF TABLES                                                      |                                   |

| Table                           | Title                                                               | Page                              |

| 1-1                             | Related Manuals                                                     | 1-1                               |

| 2-1<br>2-2<br>2-3<br>2-4        | Model 980 Computer Characteristics                                  | 2-2<br>2-4<br>2-5<br>2-8          |

| 3-1                             | Model 980 Computer Machine Instructions by                          | 2 1                               |

| 3-2                             | Functional Group                                                    | 3 <b>-</b> 1 3-5                  |

| 3-3                             | Register-Memory Instruction Addressing Modes and Coding Conventions | 3 <b>-</b> 6                      |

| 4-1<br>4-2                      | SAP Error Messages                                                  | <b>4-8A</b><br><b>4-</b> 9        |

|                                 |                                                                     |                                   |

Page

#### SECTION I

#### GENERAL INFORMATION

#### 1.1 SCOPE OF MANUAL

This is one of two manuals covering the Model 980 Computer assembly language. This manual describes all of the Model 980 Computer machine instructions and the associated symbolic assembly language coding conventions. Beginning with Section II, an overview of the Model 980 Computer is presented with specific information on the hardware features that affect assembly language. Section III presents the machine instructions and the symbolic coding conventions. Section IV follows with a general description of the Symbolic Assembly Program (SAP) and a list of assembler directives. Included in Section IV are sample assembly listings produced by SAP. The appendixes at the rear of the manual contain instruction execution times, an alphabetical and numerical listing of instruction operation codes, and a table of illegal operation codes.

## 1.2 REFERENCES

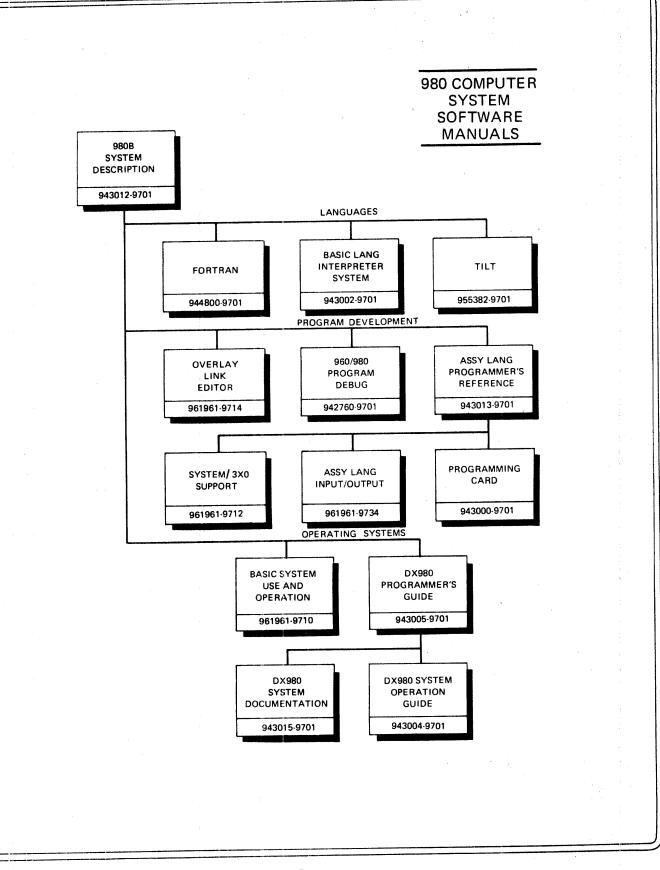

The second of the two manuals covering the Model 980 Computer assembly language is Model 980 Computer Assembly Language Input/Output. It provides the information necessary to program input/output devices available with the 980 at the assembly language level. The Model 980 Computer Basic System Use and Operation manual or the DX980 GPOS Programmer's Guide should be referenced for information on how to assemble, load, and execute an assembly language program. The related software manuals and their respective manual numbers are listed in table 1-1.

Table 1-1. Related Manuals

| Manual                                                         | Manual No.  |

|----------------------------------------------------------------|-------------|

| Model 980 Computer Assembly Language Input/Output              | 961961-9734 |

| Model 980 Computer Basic System Use and Operation              | 961961-9710 |

| Model 980 Computer Programming Card                            | 943000-9701 |

| DX980 General Purpose Operating System Pro-<br>grammer's Guide | 943005-9701 |

#### SECTION II

#### HARDWARE FEATURES

## 2.1 GENERAL

This section contains a brief block diagram discussion of the computer, a table of computer characteristics, and a list of programmable registers. Included is a bit-by-bit breakdown of the status register.

## 2.2 COMPUTER ORGANIZATION

The computer is functionally organized into a central processing unit (CPU), a memory, an input/output (I/O) unit, and a power supply. Figure 2-1 shows a block diagram of the basic system. The Direct Memory Access Channel (DMAC) is an I/O channel used for peripheral devices having a relatively fast

Figure 2-1. Model 980 Computer Block Diagram

rate of data transfer. The Data Bus is an I/O channel used for peripheral devices having a relatively slow rate of data transfer. An auxiliary processor (AP) is used to add to the standard 980 instruction set. For example, floating point arithmetic may be added or the instructions for another computer may be emulated. Expansion of the DMAC, Data Bus, and AP ports may be accomplished by using the optional twelve (12) connector chassis within the Model 980 mainframe and/or an expansion chassis external to the mainframe. Table 2-1 lists some of the more important characteristics of the computer.

Tabel 2-1. Model 980 Computer Characteristics

#### Organization

- Parallel operation

- Single level indirect addressing

- Two's complement arithmetic

- Eight addressable registers, plus status register

- Bipolar ROM control for CPU

## Memory

- Dynamic MOS/LSI semiconductor array memory

- 16-bit word length plus even parity (980A); 16-bit word length plus 6-bit error correction/detection code (980B)

- Capacity, in 4096-word increments (980A); in 8192-word increments (980B)

4096 words minimum (980A); 8192 words minimum (980B) 65536 words maximum (980A and 980B) 32768 in CPU chassis, 32768 external (980A); 65536 in CPU chassis (980B)

- All of memory can be directly addressed

- Power failure protection

- 750 nanosecond read or write cycle

- 500 nanosecond memory access

#### Input/Output

One direct memory access channel (DMAC) port, expandable to eight

Single word parallel transfer

One million words per second burst rate

# Table 2-1. Model 980 Computer Characteristics (Continued)

A processor-controlled data bus with 4 ports, expandable to 256 ports

One 4-bit interrupt expander

16-bit parallel transfer

• Three priority interrupts

Vectored interrupts (highest priority)

DMAC interrupts

Data bus interrupts (lowest priority)

#### Instruction set

• 99 basic instructions (covered in Section III)

#### Other features

- Memory protect/privileged instruction feature (standard)

- Vectored (priority) interrupt option, up to 32 hardware vectored interrupts (optional)

- Auxiliary Processor option (optional)

- Hardware bootstrap loader (standard)

- Internal expansion chassis for DMAC, data bus, and auxiliary processors (optional)

- Internal battery for maintaining memory contents when power is off (optional)

# 2.3 DATA AND INSTRUCTION FORMATS

Both the data and instruction words are 16 bits long. The bit positions within a word are numbered 0 (most significant bit) through 15 (least significant bit). Data is represented in binary two's complement form with bit 0 indicating the algebraic sign. A zero in the first bit indicates a positive sign. The range of integers representable in one 16-bit word is from  $-2^{15}$  to  $+2^{15}$  -1.

Double length operands such as products from multiplication, dividends for divides, and quantities for double-length arithmetic shifts have the following format:

| 0 | 1      | 15 16 17 | 31     |

|---|--------|----------|--------|

| s | 15 MSB | s        | 15 LSB |

Input, output, and status register related instructions are 32 bits long and occupy two consecutive 16-bit words. The register-to-memory instructions may be 16, 32, or 48 bits long.

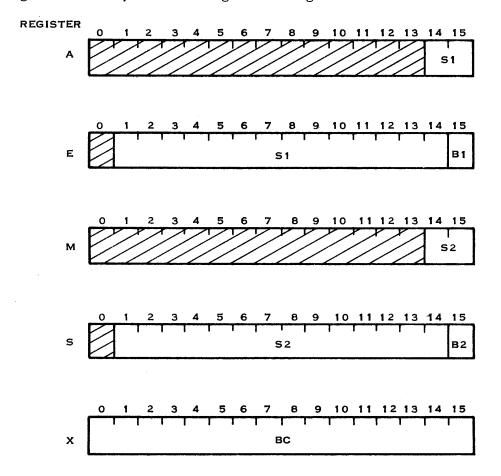

#### 2.4 REGISTER ORGANIZATION

Eight 16-bit registers are directly addressable via the instruction formats involving registers. These registers with their respective address, designation, and function are listed in table 2-2.

Table 2-2. Model 980 Computer Addressable Registers

| Register<br>Address | Designation | Function                                                     |

|---------------------|-------------|--------------------------------------------------------------|

| 0                   | A           | Primary arithmetic register.                                 |

| 1                   | E           | Secondary (extension) arithmetic register.                   |

| 2                   | ×           | Index register for operand address modi-<br>fication.        |

| 3                   | М           | Maintenance register for temporary storage.                  |

| 4                   | S           | Storage register for temporary storage.                      |

| 5                   | L           | Link register to hold return address for subroutine linkage. |

| 6                   | В           | Base register to hold base address for op-<br>erands.        |

| 7                   | PC          | Program counter to hold the address of the next instruction. |

In addition to these eight registers, the status register may be directly affected by the instruction set. The status register is used to hold the present condition of the computer and to enable or disable interrupts. The status register together with the program counter constitutes the "status block". The functions of the status register bits are listed in table 2-3.

Table 2-3. Status Register Bit Functions

| Bits | Function                                                                                                                                            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0,1  | Compare Indicators - Indicate the result of the last compare operation.                                                                             |

|      | 00 - less than 01 - equal to 10 - greater than 11 - unused bit setting                                                                              |

| 2    | Overflow Indicator - Turned on or off by those instructions that may result in a number that is outside of the range of the associated register(s). |

| 3    | Carry Indicator - Turned on or off by an add or subtract instruction that may result in a carry into the sign bit of a register.                    |

| 4    | Privileged Instruction and Memory Protect Interrupt Control                                                                                         |

|      | 0 - Disabled<br>1 - Enabled                                                                                                                         |

| 5    | Memory Protect Address Violation - May not be set under program control.                                                                            |

|      | 0 - No Violation<br>1 - Violation                                                                                                                   |

| 6    | PIF* Instruction Violation - May not be set under program control.                                                                                  |

|      | 0 - No Violation<br>1 - Violation                                                                                                                   |

| 7    | Data Bus Interrupt Control                                                                                                                          |

|      | 0 - Disabled<br>1 - Enabled                                                                                                                         |

| 8    | Vectored Interrupt Feature                                                                                                                          |

|      | 0 - Disabled<br>1 - Enabled                                                                                                                         |

|      | I - Enabled                                                                                                                                         |

<sup>\*</sup>PIF - Privileged Instruction Feature

Table 2-3. Status Register Bit Functions (Continued)

| Bits | Function                                                                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9    | PIF* Lower Limit Address Bias                                                                                                                        |

|      | 0 - Disabled<br>1 - Enabled                                                                                                                          |

| 10   | Index Control                                                                                                                                        |

|      | 0 - Post Indexing<br>1 - Pre-indexing                                                                                                                |

| 11   | Memory Parity Error Interrupt Control                                                                                                                |

|      | 0 - Disabled<br>1 - Enabled                                                                                                                          |

| 12   | DMAC Interrupt Control                                                                                                                               |

| ·    | 0 - Disabled<br>1 - Enabled                                                                                                                          |

| 13   | Not Used                                                                                                                                             |

| 14   | Memory Parity Error Indicator - May not be set under program control.                                                                                |

|      | 0 - No Error<br>1 - Error                                                                                                                            |

| 15   | Power Fail Indicator - One millisecond (980A) or 20 millisecond (980B) warning that power failure is imminent. May not be set under program control. |

|      | 0 - Power Up<br>1 - Power Failure Imminent                                                                                                           |

\*PIF - Privileged Instruction Feature

#### 2.5 MEMORY PROTECT/PRIVILEGED INSTRUCTION FEATURE

When enabled, the memory protect/privileged instruction feature (MP/PIF) allows program execution to occur only within a specified area of memory. It also causes certain instructions to be treated as illegal. This feature may be used to protect the operating environment from destruction during execution of an undebugged program.

The system may use this feature to prevent a user program from inadvertently storing data over a system program or another user program. The

MP/PIF can also prevent program execution from proceeding beyond the region that the given program occupies in memory; thus, a program cannot inadvertently branch into the middle of another program. Finally, when the MP/PIF is enabled, a user can neither disrupt input/output activity that the system has in progress nor bring the computer to an idle.

Before enabling the MP/PIF feature, it is first necessary to load the MP/PIF lower limit and upper limit registers that define the limits within which execution will be constrained. Both registers are loaded using the WDS instruction (refer to paragraph 3.12.4) just as if the MP/PIF registers were external to the computer. Register address zero defines the lower limit and register address one defines the upper limit. These boundary locations and all memory outside of the boundaries are protected by the MP/PIF feature. The MP/PIF feature is then enabled by setting bit 4 of the status register.

# 2.6 PROGRAM RELOCATION FEATURE

The program relocation feature (PRF) allows a program to be loaded any-where within the 980 memory, but to execute as though it were loaded starting at memory location zero. When used by a system program, this allows programs to be moved from one point in memory to another with no affect on the operation of the program. It also allows programs to be stored in an absolute rather than relocatable form, thus requiring less storage space.

The lower limit register used by the MP/PIF is also used by the PRF. If the system sets bit 9 of the status register at the time control is transferred to the user program, the contents of the lower limit register plus one is added into the address calculations for each memory access. For example, suppose a program is assembled as an absolute program with origin at location  $0000_{16}$ . Also, suppose that the entry point to the program is location  $0020_{16}$ , and that it is convenient for the system to load the program at location  $1000_{16}$ . The system loads the program starting at  $1000_{16}$ , places  $0FFF_{16}$  in the lower limit register, and performs an LSB instruction (refer to paragraph 3.4.5) to transfer to the program. The LSB must set bit 9 of the status register and load the program counter with  $0020_{16}$ . Note, that although the instruction executed is at  $1020_{16}$ , the program counter contains  $0020_{16}$ . If, for instance, a trap were to occur, the value  $0020_{16}$  in the program counter would be saved for the return.

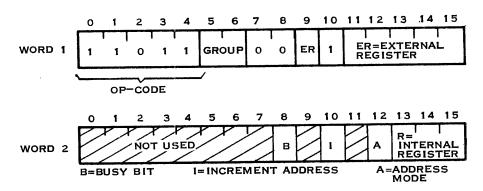

#### 2.7 PRIORITY INTERRUPT FEATURE

The Model 980 Computer responds to four different types of interrupts. These interrupts, in order of priority include: internal interrupt, vectored interrupt option, DMAC interrupt, and data bus interrupt. The three lower priority interrupts are input/output interrupts, and their occurrence depends on the system hardware configuration. The internal interrupts include the detection of imminent power failure, an illegal operation code, a memory parity error, a memory protect violation, and a privileged instruction violation. When any internal or input/output interrupt occurs, computer control

traps to low order memory as listed in table 2-4, assuming the proper status register bits are set to enable the interrupt. Note that the power failure and illegal operation code interrupts cannot be masked by the status register.

Table 2-4. Model 980 Computer Interrupts

|                                                                    | Trap                                 | Status Register Bits |                           |  |  |

|--------------------------------------------------------------------|--------------------------------------|----------------------|---------------------------|--|--|

| Interrupt Type                                                     | Address<br>(Hex)                     | Mask Bit             | Interrupt Bit             |  |  |

| Internal                                                           |                                      |                      |                           |  |  |

| Power fail Illegal op-code Parity error MP violation PIF violation | 0002<br>0002<br>0002<br>0002<br>0002 | -<br>11<br>4<br>4    | 15<br>- ①<br>14<br>5<br>6 |  |  |

| Vectored (Optional)                                                | 0008②<br>:<br>0046                   | 8                    | -                         |  |  |

| DMAC                                                               | 0004                                 | 12                   | -                         |  |  |

| Data Bus                                                           | 0006                                 | 7                    | -                         |  |  |

#### NOTES:

- The illegal op-code interrupt is detected when none of the other internal interrupts cause the trap to 0002<sub>16</sub>.

- The optional vectored interrupt feature may include up to 32 separate trap locations, beginning with the highest priorities at 0008<sub>16</sub>, 000A<sub>16</sub>, 000C<sub>16</sub>, etc. to the lowest priority at 0046<sub>16</sub>.

Programming all four types of interrupts is covered in detail in the Model 980 Computer Assembly Language Input/Output manual.

#### SECTION III

### MACHINE INSTRUCTIONS AND CODING CONVENTIONS

### 3.1 GENERAL

This section describes the machine instructions and the related assembly language coding conventions for the Model 980 Computer. Table 3-1 groups the 99 instructions by function, and references a separate paragraph on each instruction for more detailed information. Appendix B contains an alphabetical and hexadecimal index to these same paragraph numbers. General coding conventions applicable to the label, operation, operand, and comment fields of the symbolic assembly language are covered in Section IV of this manual.

#### 3.1.1 INSTRUCTION DESCRIPTIONS

Each instruction description referenced in table 3-1 contains the following information about the instruction:

- Instruction word field breakdown

- Description of instruction execution

- Status register bits affected by instruction execution

- Execution time

- Assembly language coding conventions

- Instruction example

Table 3-1. Model 980 Computer Machine Instructions by Functional Group

| Mnemonic            | Description                    | Paragraph No.  |  |  |

|---------------------|--------------------------------|----------------|--|--|

| • Load Instruction  | 5                              | 3.2            |  |  |

| DLD                 | Double Load Registers A and E  | 3.2.1          |  |  |

| LDA                 | Load Register A                | 3.2.2<br>3.2.3 |  |  |

|                     | $f LDE f Load \ Register \ E$  |                |  |  |

| LDM                 | LDM Load Register M            |                |  |  |

| LDX                 | LDX Load Register X            |                |  |  |

| LRF                 | Load Register File             | 3.2.6          |  |  |

| • Store Instruction | <u>s</u>                       | 3.3            |  |  |

| DST                 | Double Store Registers A and E | 3.3.1          |  |  |

| SRF                 | Store Register File            | 3.3.2          |  |  |

| STA                 | Store Register A               | 3.3.3          |  |  |

| STE                 | Store Register E               | 3.3.4          |  |  |

| STX                 | Store Register X               | 3.3.5          |  |  |

Table 3-1. Model 980 Computer Machine Instructions by Functional Group (Continued)

| Mnemonic                             | Description                      | Paragraph No.  |

|--------------------------------------|----------------------------------|----------------|

| <ul> <li>Branch Instructi</li> </ul> | ons                              | 3.4            |

| BIX                                  | Branch on Incremented Index      | 3.4.1          |

| $\mathtt{BRL}$                       | Branch and Link                  | 3.4.2          |

| BRU                                  | Branch Unconditional             | 3.4.3          |

| $\mathtt{IDL}$                       | $\operatorname{Idle}$            | 3.4.4          |

| LSB                                  | Load Status Block and Branch     | 3.4.5          |

| LSR                                  | Load Status Block, Reset In-     |                |

|                                      | terrupt, and Branch              | 3.4.6          |

| SSB                                  | Store Status Block and Branch    | 3.4.7          |

| <ul> <li>Arithmetic Instr</li> </ul> | uctions                          | 3.5            |

| ADD                                  | Add to Register A                | 3.5.1          |

| DAD                                  | Double Length Add                | 3.5.2          |

| DIV                                  | Divide                           | 3.5.3          |

| DSB                                  | Double Length Subtract           | 3.5.4          |

| IMO                                  | Increment Memory by One          | 3.5.5          |

| MPY                                  | Multiply                         | 3.5.6          |

| RAD                                  | Register Add                     | 3.5.7          |

| RCO                                  | Register Complement              | 3.5.8          |

| RDE                                  | Register Decrement               | 3.5.9          |

| RIN                                  | Register Increment               | 3.5.10         |

| RIV                                  | Register Invert                  | 3.5.11         |

| RSU                                  | Register Subtract                | 3.5.12         |

|                                      | Subtract from Register A         | 3.5.13         |

| SUB                                  | -                                |                |

| • Compare Instru                     | ctions                           | 3.6            |

| CLC                                  | Compare Logical Character String | 3.6.1          |

| CPA                                  | Compare Algebraic                | 3.6.2          |

| $\mathtt{CPL}$                       | Compare Logical                  | 3.6.3          |

| RCA                                  | Register Compare Algebraic       | 3.6.4          |

| RCL                                  | Register Compare Logical         | 3.6.5          |

| • Skip Instruction                   | <u>s</u>                         | 3.7            |

| $\mathtt{DMT}$                       | Decrement Memory and Test        | 3.7.1          |

| SEQ                                  | Skip on Equal                    | 3.7.2          |

| SEV                                  | Skip on Even                     | 3.7.3          |

| SGE                                  | Skip on Greater Than or Equal    | 3.7.4          |

| SGT                                  | Skip on Greater Than             | 3 <b>.7.</b> 5 |

| SLE                                  | Skip on Less Than or Equal       | 3.7.6          |

| SLT                                  | Skip on Less Than                | 3.7.7          |

Table 3-1. Model 980 Computer Machine Instructions by Functional Group (Continued)

| Mnemonic             | Description                        | Paragraph No. |

|----------------------|------------------------------------|---------------|

| • Skip Instructions  | (Continued)                        |               |

| SMI                  | Skip on Minus                      | <b>3.7.</b> 8 |

| SNC                  | Skip on No Carry                   | 3.7.9         |

| . SNE                | Skip on Not Equal                  | 3.7.10        |

| SNO                  | Skip on Not All Ones               | 3.7.11        |

| SNV                  | Skip on No Overflow                | 3.7.12        |

| $\operatorname{SNZ}$ | Skip on Not All Zeros              | 3.7.13        |

| SOC                  | Skip on Carry                      | 3.7.14        |

| SOD                  | Skip on Odd                        | 3.7.15        |

| SOO                  | Skip on All Ones                   | 3.7.16        |

| sov                  | Skip on Overflow                   | 3.7.17        |

| $\mathtt{SPL}$       | Skip on Plus                       | 3.7.18        |

| SSE                  | Skip on Sense Switch Equal         | 3.7.19        |

| SSN                  | Skip on Sense Switch Not Equal     | 3.7.20        |

| SZE                  | Skip on Zero                       | 3.7.21        |

| • Shift Instructions | <u>1</u>                           | 3.8           |

| ALA                  | Arithmetic Left Shift Register A   | 3.8.1         |

| $_{ m ALD}$          | Arithmetic Left Shift Double       | 3.8.2         |

| ARA                  | Arithmetic Right Shift Register A  | 3.8.3         |

| ARD                  | Arithmetic Right Shift Double      | 3.8.4         |

| $\mathtt{CLD}$       | Circular Left Shift Double         | 3.8.5         |

| CRA                  | Circular Right Shift Register A    | 3.8.6         |

| CRB                  | Circular Right Shift Register B    | 3.8.7         |

| CRD                  | Circular Right Shift Double        | 3.8.8         |

| CRE                  | Circular Right Shift Register E    | 3.8.9         |

| CRL                  | Circular Right Shift Register L    | 3.8.10        |

| CRM                  | Circular Right Shift Register M    | 3.8.11        |

| CRS                  | Circular Right Shift Register S    | 3. 8. 12      |

| CRX                  | Circular Right Shift Register X    | 3.8.13        |

| $_{ m LLA}$          | Logical Left Shift Register A      | 3.8.14        |

| $_{ m LLD}$          | Logical Left Shift Double          | 3.8.15        |

| LRA                  | Logical Right Shift Register A     | 3.8.16        |

| LRD                  | Logical Right Shift Double         | 3.8.17        |

| LTO                  | Left Test for Ones in Register A   | 3. 8. 18      |

| $\mathtt{LTZ}$       | Left Test for Zeros in Register A  | 3.8.19        |

| NRM                  | Normalize                          | 3. 8. 20      |

| RTO                  | Right Test for Ones in Register A  | 3.8.21        |

| RTZ                  | Right Test for Zeros in Register A |               |

|                      |                                    |               |

Table 3-1. Model 980 Computer Machine Instructions by Functional Group (Continued)

| Mnemonic           | Description                    | Paragraph No. |

|--------------------|--------------------------------|---------------|

| • Logical Instruct | ions                           | 3.9           |

| AND                | Logical AND with Register A    | 3.9.1         |

| IOR                | Logical OR with Register A     | 3.9. <b>2</b> |

| RAN                | Register AND                   | 3.9.3         |

| REO                | Register Exclusive OR          | 3.9.4         |

| ROR                | Register OR                    | 3.9.5         |

| Bit Manipulation   | Instructions                   | 3.10          |

| SABO               | Set Register A Bit to One      | 3.10.1        |

| SABZ               | Set Register A Bit to Zero     | 3.10.2        |

| SMBO               | Set Memory Bit to One          | 3.10.3        |

| SMBZ               | Set Memory Bit to Zero         | 3.10.4        |

| TABO               | Test Register A Bit for One    | 3.10.5        |

| TABZ               | Test Register A Bit for Zero   | 3.10.6        |

| TMBO               | Test Memory Bit for One        | 3.10.7        |

| TMBZ               | Test Memory Bit for Zero       | 3.10.8        |

| Move Instruction   | ns                             | 3.11          |

| MVC                | Move Character String          | 3.11.1        |

| REX                | Register Exchange              | 3.11.2        |

| RMO                | Register Move                  | 3.11.3        |

| • Input/Output Ins | tructions                      | 3.12          |

| API                | Auxiliary Processor Initiate   | 3.12.1        |

| ATI                | Automatic Transfer Instruction | 3.12.2        |

| RDS                | Read Direct Single             | 3.12.3        |

| WDS                | Write Direct Single            | 3.12.4        |

The status register bits are defined in table 2-3. The symbols used in presenting the instruction assembly language coding formats and the symbols used in presenting an abbreviated form of instruction execution are listed in table 3-2. The symbols and directives used in the instruction examples are explained in Section IV.

Table 3-2. Assembly Language Coding Format and Instruction Execution Symbols

|                              | Symbol                                | Definition                                    |

|------------------------------|---------------------------------------|-----------------------------------------------|

| Instruction                  | ( )                                   | Contents of enclosed register or ad-<br>dress |

| Execution  Assembly Language | <b>→</b>                              | Replaces                                      |

|                              | *                                     | Indirect addressing                           |

|                              | @                                     | Extended format                               |

|                              | =                                     | Immediate operand                             |

| Coding                       | [ ]                                   | Optional item                                 |

| Format                       | Lower case alpha-<br>betic characters | User supplied item                            |

| Ĺ                            | ₩                                     | Required blank space (one or more)            |

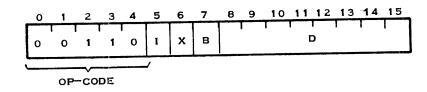

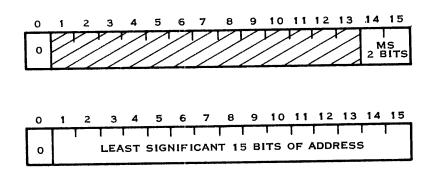

#### 3.1.2 ADDRESSING MODES

The computer instruction set can be broken down into a number of different format types. The addressing modes associated with all but one of the format types are straightforward, and are included in the individual instruction descriptions. The remaining instruction format type, register-memory instructions, is more involved and is described in this paragraph and referenced by the instruction descriptions when applicable.

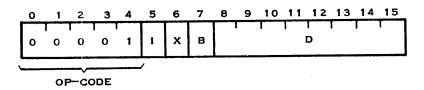

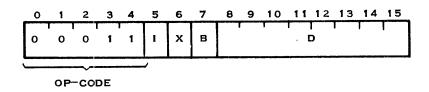

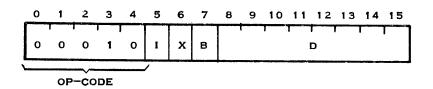

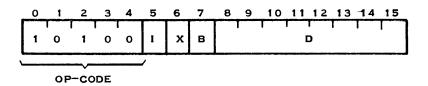

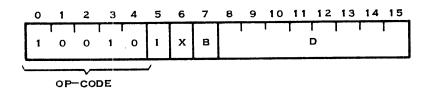

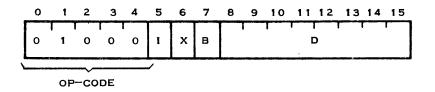

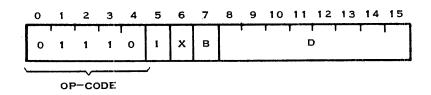

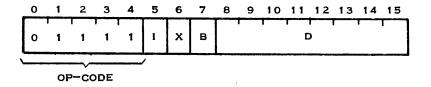

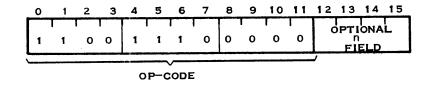

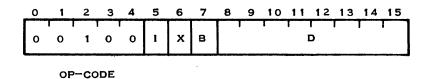

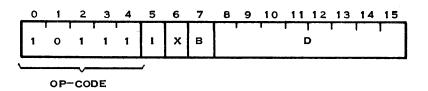

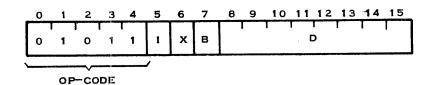

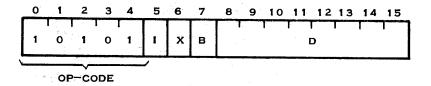

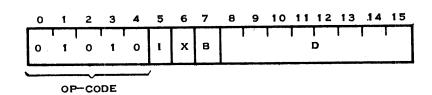

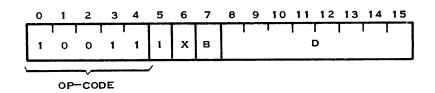

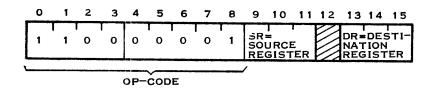

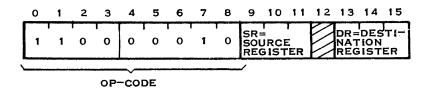

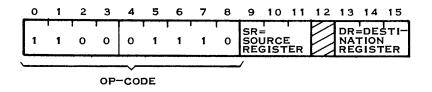

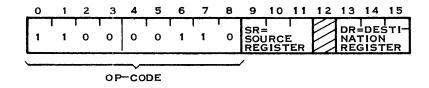

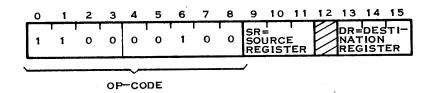

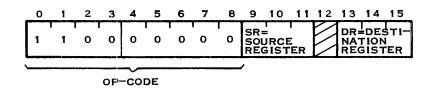

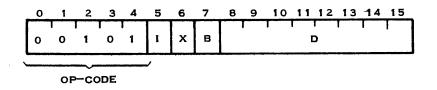

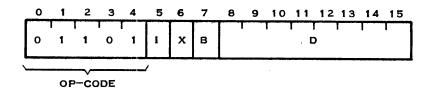

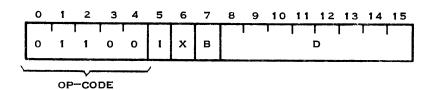

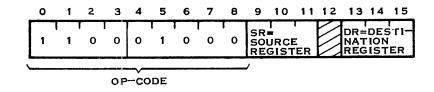

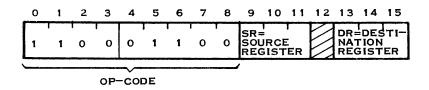

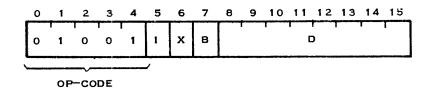

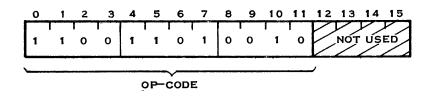

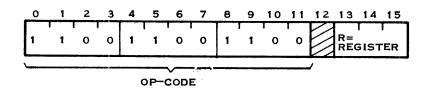

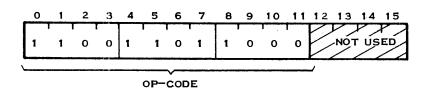

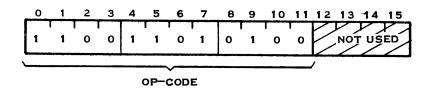

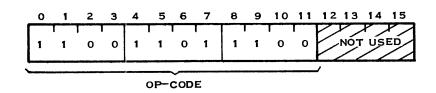

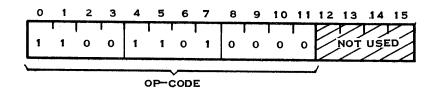

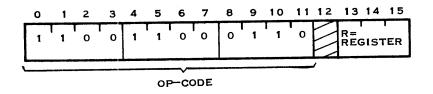

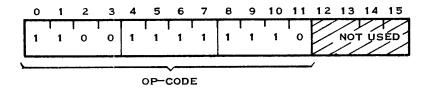

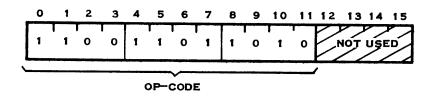

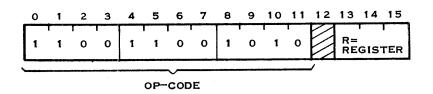

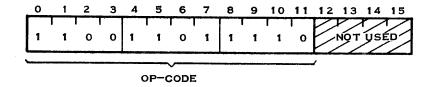

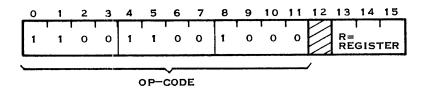

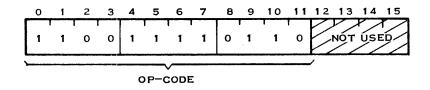

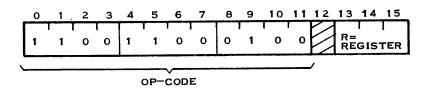

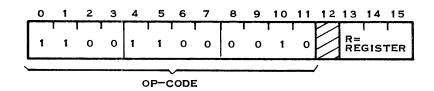

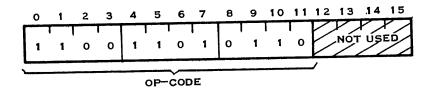

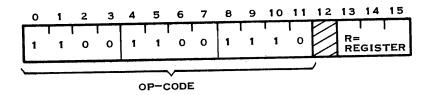

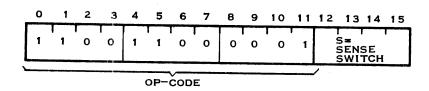

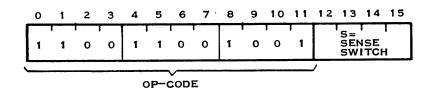

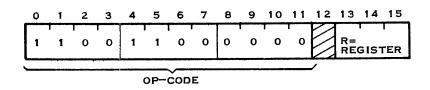

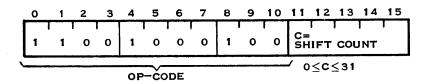

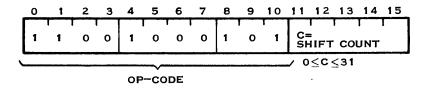

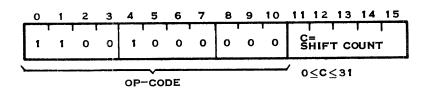

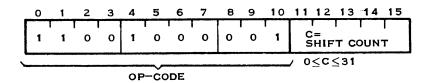

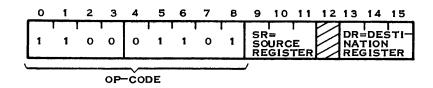

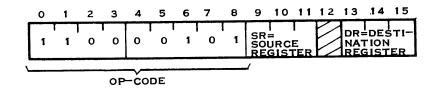

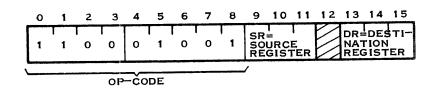

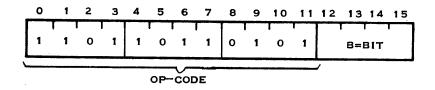

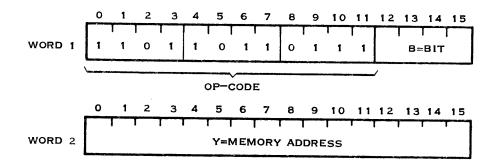

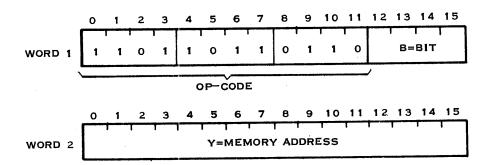

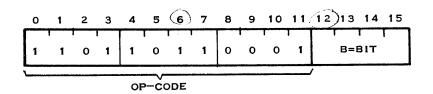

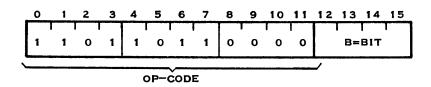

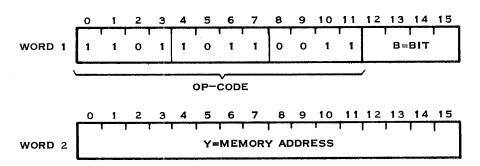

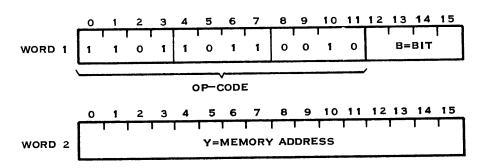

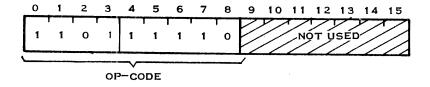

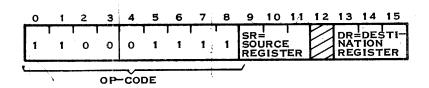

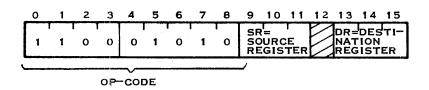

The format of register-memory instructions is shown in figure 3-1. The addressing mode is determined by the I, X, and B fields as shown in table 3-3.

Figure 3-1. Register-Memory Instruction Fields

Table 3-3. Register-Memory Instruction Addressing Modes and Coding Conventions

| IXB  | Effective Operand                              | Symbolic Coding<br>Conventions |                                                 | Addressing                            |  |

|------|------------------------------------------------|--------------------------------|-------------------------------------------------|---------------------------------------|--|

| Bits | Bits Address, EOA                              |                                | Operand                                         | Mode                                  |  |

| 000  | (PC) + SD                                      | UNMM<br>@WNU<br>@WNU<br>UNM    | ADRS (2)<br>= NUM (3), (5)<br>NUM, 7 (5)        | PC relative                           |  |

| 001  | (B)Û + D                                       | MNU<br>MNU                     | ADRS,1<br>ADRS                                  | Base register<br>relative             |  |

| 010  | (PC) + (X)  + SD                               | MNU                            | ADRS, 2                                         | Indexed PC<br>relative                |  |

| 011  | (B) + (X) + D                                  | MNU<br>MNU                     | ADRS, 3<br>ADRS, 2                              | Indexed base<br>register<br>relative  |  |

| 100  | ((PC) + SD)                                    | MNU<br>MNU<br>MNU<br>@MNU      | *ADRS<br>*ADRS, 4<br>ADRS, 4<br>ADRS            | Indirect PC<br>relative               |  |

| 101  | ((B) + D)                                      | MNU<br>MNU<br>MNU<br>MNU       | *ADRS, 1 *ADRS, 5 ADRS, 5 *ADRS.                | Indirect base<br>register<br>relative |  |

| 110  | ((PC) + SD) + (X) (7)<br>((PC) + (X) + SD) (8) | MNU<br>MNU<br>MNU<br>@MNU      | *ADRS, 6<br>*ADRS, 2<br>ADRS, 6<br>ADRS, 2 ⑤, ⑥ | Indirect,<br>indexed,<br>PC relative  |  |

| 111  | Immediate value<br>is the SD                   | MNU<br>MNU                     | = NUM<br>NUM, 7                                 | Immediate                             |  |

#### NOTES:

- PC Program Counter (points to next instruction); B Base Register;

X Index Register; MNU Instruction Mnemonic.

- ② Symbolic name of address.

- 3 Number, literal, or address.

- 4 Under BRS directive.

- (5) All extended format instructions are regarded as PC relative because the assembler zeros the SD field. This means the computer must add the PC to the zeroed SD to locate the extended data/address. Note that the computer increments the PC to the next location before the instruction is executed.

- 6 Post-indexing, regardless of status register bit 10.

- 7 Post-indexing if status register bit 10 = 0.

- 8 Pre-indexing if status register bit 10 = 1.

#### NOTE

To fully understand table 3-3, all of paragraph 3.1.2 and 3.1.3 must be read.

In general, calculation of the Effective Operand Address (EOA) of the memory data involved in the instruction includes indirect addressing if bit I is set, indexing if bit X is set, and base relative addressing if bit B is set. If all three of these bits are set, an immediate operand is assumed by the computer. If immediate addressing is specified for a load, add, subtract, or algebraic compare instruction, the displacement field (D) is treated as an 8-bit signed quantity and bit eight is extended through bits 0 to 7 to provide a 16-bit operand. If immediate addressing is specified for a store instruction, D is treated as the EOA.

The index control bit in the status register permits optional pre-indexing or post-indexing. This controls the relation of indexing to indirect addressing. If the index control bit is one, indexing precedes indirect addressing. If the index control bit is zero, indexing follows indirect addressing. If indirect addressing is not involved, the two modes are equivalent. Additional addressing capability is available with the optional memory protect/privileged instruction feature. If status register bit 9 is set, the lower limit address is added to the computer calculated address for every memory access.

Table 3-3 also lists the symbolic coding conventions available with register-memory instructions, and hence shows the transliteration process performed by the assembler in developing the I, X, and B fields. In order to translate the operand address expression of a register-memory instruction, the assembler first evaluates the expression as a 16-bit number and then modifies the expression in one of the following ways:

- For program counter relative instructions, a number one greater than the assembler location counter is subtracted.

- For base register relative instructions, the base register value or the number associated with a BRS directive (refer to Section IV of this manual) is subtracted.

- For extended format instructions (described in next paragraph), the expression remains unmodified.

- For single length immediate instructions, or base register relative instructions under the BRR directive (refer to Section VII of this manual), the expression is truncated to an eight-bit value.

- If the resulting address is unattainable under the defined conditions, a field size error is indicated by the assembler.

## 3.1.3 EXTENDED FORMAT ADDRESSING

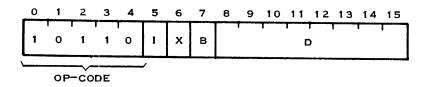

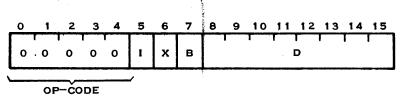

It is possible to extend the format of certain register-memory instructions and to include data or indirect addresses within these instructions. When this feature is used, the instruction is referred to as an extended format instruction. The extended format instruction coding forms are flagged by note 5 in table 3-3. The assembler interprets the coded instruction and fills the I, X, B and SD fields as follows:

- If the I, X, B, and SD fields are 0, 0, 0, 0, respectively, the next sequential location in memory is used for the operand, and the program counter is incremented a second time. (The first increment is normal to locate the next word in memory). If the instruction is of the double precision type, such as DLD, DST, DAD, or DSB, the next two sequential memory locations are used for the operand, and the program counter is incremented a third time. The assembler, in this case, generates only one word of data for these double-length instructions. The programmer must supply the second word, typically with a DATA directive.

- If the I, X, B, and SD fields are 1, 0, 0, 0, respectively, the effective address is obtained from the next sequential location in memory, and the program counter is incremented a second time.

- If the I, X, B, and SD fields are 1, 1, 0, 0, respectively, the content of the next sequential memory location is added to the content of the index register to form the effective address, and the program counter is incremented a second time.

#### NOTE

The indexing is unconditionally performed as postindexing for double-word instructions; bit 10 of the status word is ignored in this case.

### 3.2 LOAD INSTRUCTIONS

The load instructions listed in table 3-1 are described in the following paragraphs.

# 3.2.1 DOUBLE LOAD REGISTERS A AND E (DLD)

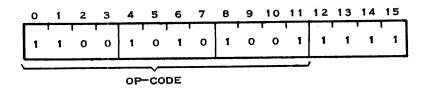

#### Machine Format:

Instruction Execution:  $(EOA, EOA+1) \rightarrow (A, E)$  where EOA is developed in accordance with table 3-3.

<u>Description</u>: Register A is loaded with the contents of the effective operand address, EOA, and register E is loaded with the contents of the EOA plus one. If the IXB fields are 7<sub>16</sub> (immediate addressing), load E with the sign extended displacement field, D, and load A with the extended sign (all zeros or all ones).

Status Affected: None

Execution Time: 1.00 to 4.00 microseconds (refer to Appendix A)

Symbolic Coding: Refer to table 3-3 for the assembly language coding formats available with the DLD instruction. The DLD mnemonic replaces the MNU operation field (in table 3-3) and optional label and comment fields may be used.

| Examples: |             |                       |                  |   | $\underline{\mathtt{Before}}$            | After                                    |

|-----------|-------------|-----------------------|------------------|---|------------------------------------------|------------------------------------------|

|           | DLD<br>DATA | \$+1<br>>AE30,>3239 ⇒ | · ·              | = | $^{0054}_{16}$ $^{16}$                   | AE30 <sub>16</sub><br>3239 <sub>16</sub> |

|           |             |                       | (EOA)<br>(EOA+1) |   | AE30 <sub>16</sub><br>3239 <sub>16</sub> | No change<br>No change                   |

|           | @DLD        | BASE                  |                  |   |                                          |                                          |

|           |             | ⇒                     | (A)              | = | CC45 <sub>16</sub>                       | 1064 <sub>16</sub>                       |

| BASE      | DATA        | >1064, >7558          | (E)              | = | A0A0 <sub>16</sub>                       | 755816                                   |

|           |             | <b>:</b><br>-         | (EOA)<br>(EOA+1) |   | $1064_{16} \\ 7558_{16}$                 | No change<br>No change                   |

#### 3.2.2 LOAD REGISTER A (LDA)

## Machine Format:

<u>Instruction Execution</u>: (EOA)—(A) where EOA is developed in accordance with table 3-3.

<u>Description</u>: Register A is loaded with the contents of the effective operand address, EOA. If the IXB fields are 7<sub>16</sub> (immediate addressing), load A with the sign extended displacement field, D.

Status Affected: None

Execution Time: 0.75 to 2.75 microseconds (refer to Appendix A)

Symbolic Coding: Refer to table 3-3 for the assembly language coding formats available with the LDA instruction. The LDA mnemonic replaces the MNU operation field (in table 3-3) and optional label and comment fields may be used.

| Examples: |     |             |   |               | Before                                   | After                           |

|-----------|-----|-------------|---|---------------|------------------------------------------|---------------------------------|

|           | LDA | = <b>-1</b> | ⇒ | (A)<br>(EOA)  | 05A3 <sub>16</sub><br>07FF <sub>16</sub> | FFFF <sub>16</sub><br>No change |

| HERE      | LDA | \$          | ⇒ | (A)<br>(HERE) | F6EF <sub>16</sub>                       | 00FF <sub>16</sub><br>No change |

### 3.2.3 LOAD REGISTER E (LDE)

## Machine Format:

<u>Instruction Execution:</u> (EOA) — (E) where EOA is developed in accordance with table 3-3.

<u>Description</u>: Register E is loaded with the contents of the effective operand address, EOA. If the IXB fields are 7<sub>16</sub> (immediate addressing), load E with the sign extended displacement field, D.

Status Affected: None

Execution Time: 0.75 to 2.75 microseconds (refer to Appendix A)

Symbolic Coding: Refer to table 3-3 for the assembly language coding formats available with the LDE instruction. The LDE mnemonic replaces the MNU operation field (in table 3-3) and optional label and comment fields may be used.

| Example: |          |          |          |            |   | Before                                   | $\underline{\text{After}}$      |

|----------|----------|----------|----------|------------|---|------------------------------------------|---------------------------------|

|          | LDE<br>: | BOT,2    | <b>⇒</b> | (E)<br>(X) |   | A6B7 <sub>16</sub><br>0001 <sub>16</sub> | 0333 <sub>16</sub><br>No change |

| вот      | DATA     | >F,>0333 |          | (EOA)      | = | 033316                                   | No change                       |

#### 3.2.4 LOAD REGISTER M (LDM)

## Machine Format:

Instruction Execution: (EOA) —— (M) where EOA is developed in accordance with table 3-3.

<u>Description</u>: Register M is loaded with the contents of the effective operand address, EOA. If the IXB fields are 7<sub>16</sub> (immediate addressing), load M with the sign extended displacement field, D.

Status Affected: None

Execution Time: 0.75 to 2.75 microseconds (refer to Appendix A)

Symbolic Coding: Refer to table 3-3 for the assembly language coding formats available with the LDM instruction. The LDM mnemonic replaces the MNU operation field (in table 3-3) and optional label and comment fields may be used.

| Example: |                      |         |            | Before             | $\underline{\text{After}}$ |

|----------|----------------------|---------|------------|--------------------|----------------------------|

| EXEC     | @LDM                 | =PRB => | (M) =      | 1124 <sub>16</sub> | Address of<br>PRB          |

| PRB      | DATA<br>DATA<br>DATA |         | (EXEC+1) = | Address<br>of PRB  | No change                  |

## 3.2.5 LOAD REGISTER X (LDX)

#### Machine Format:

<u>Instruction Execution:</u> (EOA) — (X) where EOA is developed in accordance with table 3-3.

<u>Description</u>: Register X is loaded with the contents of the effective operand address, EOA. If the IXB fields are 7<sub>16</sub> (immediate addressing), load X with the sign extended displacement field, D.

Status Affected: None

Execution Time: 0.75 to 2.75 microseconds (refer to Appendix A)

Symbolic Coding: Refer to table 3-3 for the assembly language coding formats available with the LDX instruction. The LDX mnemonic replaces the MNU operation field (in table 3-3) and optional label and comment fields may be used.

| Example: |     |       |    |          | <b>Before</b> | After     |

|----------|-----|-------|----|----------|---------------|-----------|

| CHCT     | LDX | = -32 | => | \        | 10            |           |

|          | •   |       |    | (CHCT) = | $17E0_{16}$   | No change |

## 3.2.6 LOAD REGISTER FILE (LRF)

#### Machine Format:

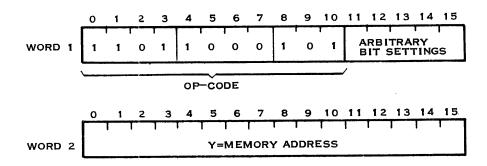

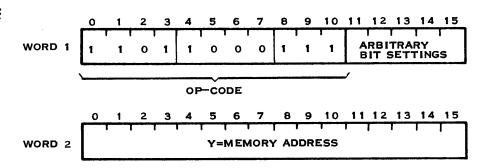

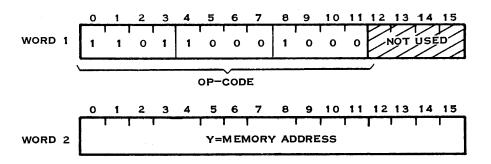

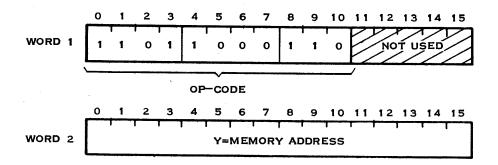

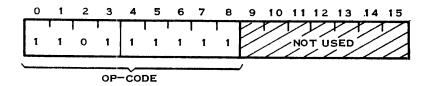

Instruction Execution:  $(Y, Y+1, Y+2, Y+3, Y+4, Y+5, Y+6) \rightarrow (A, E, X, M, S, L, B)$

Description: Registers A, E, X, M, S, L, and B (the register file) are loaded from sequential memory locations starting at the address specified by Y (second word of the instruction).

Status Affected: None

Execution Time: 7.00 microseconds

Symbolic Coding: The assembly language coding formats for the LRF instructions are as follows:

|                                                            | Comment               | Operand | 1       | Operation   | ( | Label                |

|------------------------------------------------------------|-----------------------|---------|---------|-------------|---|----------------------|

| where "adrs" is the<br>symbolic name of a<br>16-bit memory | <pre></pre>           | adrs    | b<br>or | @LRF        | Þ | [label]              |

| address.                                                   | [comment] % [comment] | adrs    | R<br>R  | LRF<br>DATA |   | [ label]<br>[ label] |

#### Example:

@LRF MEMA

MEMA DATA >0300, >06AA, >FFE0, >1A61, >0000, >1121, >8A04

|               | Before (Hex)                                                                                   | After (Hex)                                          |  |

|---------------|------------------------------------------------------------------------------------------------|------------------------------------------------------|--|

| Register file | (A) = 0000<br>(E) = 0002<br>(X) = FFFF<br>(M) = 200D<br>(S) = 0C00<br>(L) = FA00<br>(B) = 0601 | 0300<br>06AA<br>FFE0<br>1A61<br>0000<br>1121<br>8A04 |  |

|               | • •                                                                                            |                                                      |  |

#### 3.3 STORE INSTRUCTIONS

The store instructions listed in table 3-1 are described in the following paragraphs.

## 3.3.1 DOUBLE STORE REGISTERS A AND E (DST)

## Machine Format:

Instruction Execution:  $(A, E) \rightarrow (EOA, EOA+1)$  where I

where EOA is developed in accordance with table 3-3.

<u>Description</u>: Store the contents of register A into the contents of the effective operand address, EOA, and store the contents of register E into the contents of EOA plus one. If the IXB fields are 7<sub>16</sub> (immediate addressing), the displacement field, D, is the EOA.

Status Affected: None

Execution Time: 2.75 to 4.00 microseconds (refer to Appendix A)

Symbolic Coding: Refer to table 3-3 for the assembly language coding formats available with the DST instruction. The DST mnemonic replaces the MNU operation field (in table 3-3) and optional label and comment fields may be used.

#### Example:

DST TOP

$$\underbrace{\text{Before}}_{\text{(A, E)}} = \underbrace{\text{4441}_{16}, \text{4D4E}_{16}}_{\text{No change}}$$

TOP BSS 2 (TOP, TOP+1) =  $4\text{C55}_{16}, 434\text{B}_{16}$  4441<sub>16</sub>,  $4\text{D4E}_{16}$

#### 3.3.2 STORE REGISTER FILE (SRF)

#### Machine Format:

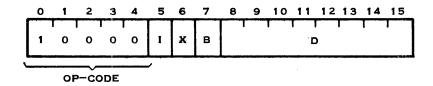

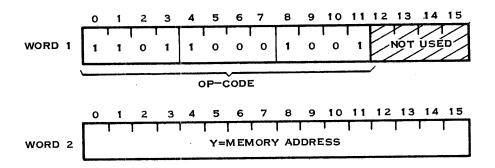

Instruction Execution:  $(A, E, X, M, S, L, B) \longrightarrow (Y, Y+1, Y+2, Y+3, Y+4, Y+5, Y+6)$

<u>Description</u>: Store the contents of registers A, E, X, M, S, L, and B (register file) into sequential memory locations starting at the address specified by Y (second word of the instruction).

Status Affected: None

Execution Time: 7.00 microseconds

Symbolic Coding: The assembly language coding formats for the SRF instruction are as follows:

| Label   |   | Operation |          | Operand |   | Comment   |                                                            |

|---------|---|-----------|----------|---------|---|-----------|------------------------------------------------------------|

| [label] | R | @SRF      | b<br>or  | adrs    | Ŗ | [comment] | where "adrs" is the<br>symbolic name of a<br>16-bit memory |

| [label] | - |           | 18<br>18 | adrs    | ĸ | [comment] | address.                                                   |

#### Example:

#### 3.3.3 STORE REGISTER A (STA)

#### Machine Format:

<u>Instruction Execution</u>: (A) — (EOA) where EOA is developed in accordance with table 3-3.

<u>Description</u>: Store the contents of register A into the contents of the effective operand address, EOA. If the IXB fields are 7<sub>16</sub> (immediate addressing), the displacement field, D, is the EOA.

Status Affected: None

Execution Time: 2.00 to 3.00 microseconds (refer to Appendix A)

Symbolic Coding: Refer to table 3-3 for the assembly language coding formats available with the STA instruction. The STA mnemonic replaces the MNU operation field (in table 3-3) and optional label and comment fields may be used.

# Example: STA DEST. 1 =>

DEST, 1

$$\Rightarrow$$

(A) =  $\frac{\text{Before}}{\text{D8C0}_{16}}$   $\frac{\text{After}}{\text{No change}}$

$$(DEST) = 0642_{16}$$

# D8C0<sub>16</sub>

#### 3.3.4 STORE REGISTER E (STE)

#### Machine Format:

Instruction Execution: (E)  $\rightarrow$  (EOA) where EOA is developed in accordance with table 3-3.

<u>Description</u>: Store the contents of register E into the contents of the effective operand address, EOA. If the IXB fields are 7<sub>16</sub> (immediate addressing), the displacement field, D, is the EOA.

Status Affected: None

Execution Time: 2.00 to 3.00 microseconds (refer to Appendix A)

Symbolic Coding: Refer to table 3-3 for the assembly language coding formats available with the STE instruction. The STE mnemonic replaces the MNU operation field (in table 3-3) and optional label and comment fields may be used.

#### Example:

STE =6

$$\Rightarrow$$

$\frac{\text{Before}}{\text{(E)}} = \frac{\text{After}}{1\text{AE}9_{16}}$  No change (Memory location 6) =  $788B_{16}$   $1\text{AE}9_{16}$

#### 3.3.5 STORE REGISTER X (STX)

## Machine Format:

Instruction Execution:  $(X) \rightarrow (EOA)$  where EOA is developed in accordance with table 3-3.

Description: Store the contents of register X into the contents of the effective operand address, EOA. If the IXB fields are 7<sub>16</sub> (immediate addressing), the displacement field, D, is the EOA.

Status Affected: None

Execution Time: 2.00 to 3.00 microseconds (refer to Appendix A)

Symbolic Coding: Refer to table 3-3 for the assembly language coding formats available with the STX instruction. The STX mnemonic replaces the MNU operation field (in table 3-3) and optional label and comment fields may be used.

## Example:

@STX FARAWY, 2

$$\Rightarrow$$

Before After (X) =  $0002_{16}$  No change (FARAWY+2) =  $1007_{16}$  0002<sub>16</sub>

#### NOTE

The content of register X is both stored and used as the index.

## 3.4 BRANCH INSTRUCTIONS

The branch instructions listed in table 3-1 are described in the following paragraphs.

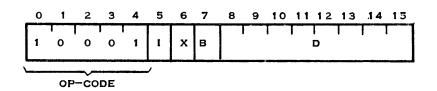

### 3.4.1 BRANCH ON INCREMENTED INDEX (BIX)

### Machine Format:

Instruction Execution:  $(X)+1 \longrightarrow (X)$ ; if  $(X) \neq 0$ , EOA  $\longrightarrow$  PC if (X) = 0, PC is not affected where EOA is developed in accordance with table 3-3.

Description: Increment the contents of register X by one: if the resulting X register value is non-zero, place the effective operand address, EOA, in the program counter and continue execution from that point; if the resulting X register value is zero, continue execution with the next sequential instruction. If the IXB fields are  $7_{16}$  (immediate addressing), the displacement field, D, is the EOA. The BIX instruction is commonly used in loop control where register X contains a negative loop count.

#### NOTE

The extended format BIX instruction is allowed since an extra program counter increment occurs on the fall through condition. If the BIX instruction is single length, the IXB bits are zero, and the displacement field is zero, the next word is skipped when the X register is incremented to zero. When the X register is incremented to a non-zero quantity, the next word is executed.

Status Affected: None

Execution Time: 1.25 to 2.25 microseconds (refer to Appendix A)

Symbolic Coding: Refer to table 3-3 for the assembly language coding formats available with the BIX instruction. The BIX mnemonic replaces the MNU operation field (in table 3-3) and optional label and comment fields may be used.

Example:

BIX DOG  $\Rightarrow$  (X) =  $\frac{\text{Before}}{\text{FFA6}_{16}}$   $\frac{\text{After}}{\text{FFA7}_{16}}$  where the BIX instruction is at  $1B64_{16}$  and DOG is at  $1B20_{16}$ .

The following instruction application example illustrates use of the BIX instruction to sum a buffer's contents.

#### 3.4.2 BRANCH AND LINK (BRL)

### Machine Format:

Instruction Execution: (PC)  $\rightarrow$  (L); EOA  $\rightarrow$  (PC) where EOA is developed in accordance with table 3-3.

Description: Load the contents of the program counter into the link register, L, place the effective operand address, EOA, in the program counter, and continue execution from that point. If the IXB fields are 7<sub>16</sub> (immediate addressing), the displacement field, D, is the EOA. The BRL instruction is commonly used for subroutine linkage. To return, the subroutine typically uses either an RMO L, P or REX L, P instruction. The return may also be accomplished by storing the contents of the link register in memory and branching indirectly through that memory location with a BRU instruction.

#### NOTE

The extended format BRL instruction places the address of the first word beyond the double-length BRL instruction in the link register.

Status Affected: None

Execution Time: 1.50 to 2.50 microseconds (refer to Appendix A)

Symbolic Coding: Refer to table 3-3 for the assembly language coding formats available with the BRL instruction. The BRL mnemonic replaces the MNU operation field (in table 3-3) and optional label and comment fields may be used.

Example:  $\frac{\text{Before}}{\text{BRL}} \quad \frac{\text{Before}}{\text{CAREA}} = \frac{\text{After}}{032A_{16}} \quad \frac{\text{After}}{055E_{16}} \quad \text{where CAREA is at}$

$^{OC}$ ) = 055D<sub>16</sub> 0580<sub>16</sub> 0580<sub>16</sub> and in the range  $^{OS}$  -128  $^{OS}$  PC  $^{OS}$  2127.

The following instruction application example illustrates use of the BRL instruction to execute a subroutine.

(Main program)

BRL WRITE